# SYSTEMASTER II TECHNICAL REFERENCE MANUAL

#### COPYRIGHT NOTICE

Copyright (c) 1984 by TELETEK ENTERPRISES, INC

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of TELETEK ENTERPRISES, INC.

#### DISCLAIMER

TELETEK ENTERPRISES, INC. makes no warranties with respect to the contents of this document and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose.

TELETEK ENTERPRISES, INC. reserves the right to change or modify this document without obligation of TELETEK ENTERPRISES, INC to notify any person or organization of such revision or change.

This document may contain technical inaccuracies or typographical errors. Changes are made periodically to the information herein; these changes will be incorporated in new editions of this document.

First Edition December 1984

TELETEK ENTERPRISES, INC 4600 Pell Drive Sacramento. California 95838 Made in U.S.A.

## TABLE OF CONTENTS

## PART ONE: GETTING STARTED

| l. | INTRO                                                | DUCTION TO THIS MANUAL                                                                                                                                     | • •                                   | •        |                                       | •   | •   | •  | • | • | • | • | • | 1-1                                    |

|----|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------|---------------------------------------|-----|-----|----|---|---|---|---|---|----------------------------------------|

|    | 1.1<br>1.2<br>1.3<br>1.4                             | Purpose and Scope Organization Terminology and Conven Related Documents                                                                                    | tio                                   | ns       | • •                                   | •   | •   | •  | • | • | • | • | • | 1-1<br>1-1<br>1-1<br>1-2               |

| 2. | INTRO                                                | DUCTION TO THE SYSTEMAS                                                                                                                                    | TER                                   | II       | •                                     | •   | •   | •  | • | • | • | • | • | 2-1                                    |

| 3. | INSTA                                                | LLATION                                                                                                                                                    |                                       | •        |                                       | •   | •   | •  | • | • | • | • | • | 3-1                                    |

|    | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8 | Standard Installation Visual Inspection Correct Configuration? Bus Organization Cooling Peripheral Connections Preparing Your Softwar In Case of Trouble . | • • • • • • • • • • • • • • • • • • • | •        | • • • • • • • • • • • • • • • • • • • | •   | •   | •  | • | • | • | • | • | 3-1<br>3-2<br>3-3<br>3-3<br>3-4<br>3-6 |

|    |                                                      | PART TWO: TECHNI                                                                                                                                           | CAL                                   | IN       | FOR                                   | MA! | rio | ON |   |   |   |   |   |                                        |

| 4. | CPU A                                                | ND CONTROL LOGIC                                                                                                                                           | • •                                   | •        | • •                                   | •   | •   | •  | • | • | • | • | • | 4-1                                    |

|    | 4.5                                                  | I/O Map                                                                                                                                                    | ates                                  | •        | • •                                   | •   | •   | •  | • | • | • | • | • | 4-3<br>4-4<br>4-5<br>4-5               |

|    | 4.6<br>4.7                                           | Read Write Control Por                                                                                                                                     | t                                     | 。<br>( D | <br>Τλα                               | ٠,  | •   | •  | • | • | • | • | • | 4-6                                    |

| 5. | MEMORY                         |

|----|--------------------------------|

|    | 5.1 Memory Maps                |

|    | 5.2 RAM                        |

|    | 5.2.4 Parity Clear/Disable     |

| 6. | CHARACTER INPUT/OUTPUT 6-1     |

|    | 6.1 Serial I/O                 |

|    | 6.2 Parallel I/O               |

| 7. | FLOPPY DISK INPUT/OUPUT        |

|    | 7.1 WD2797-02 Disk Controller  |

| 8. | DIRECT MEMORY ACCESS (DMA) 8-1 |

|    | 8.1 CPU to DMA interface       |

| 9.   | INTER                                          | RUPTS                                                         |                                     | • •                              | • •                                      |                               | • •                                          | •                    |     | •   | • | • | •   | • | • | 9-1                                    |

|------|------------------------------------------------|---------------------------------------------------------------|-------------------------------------|----------------------------------|------------------------------------------|-------------------------------|----------------------------------------------|----------------------|-----|-----|---|---|-----|---|---|----------------------------------------|

|      | 9.1                                            | Interr<br>Interr<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4<br>9.2.4 | upt Co<br>CPU<br>Inte<br>UIC<br>UIC | ontr<br>to<br>erru<br>Sof<br>Reg | olle:<br>UIC ]<br>pt as<br>tware         | nter<br>Inter<br>Ssign<br>Int | facenment                                    | e<br>t<br>ace<br>fin | iti | ons | • | • | • • | • | • | 9-1<br>9-4<br>9-4<br>9-4<br>9-5<br>9-6 |

| 10.  | IEEE 6                                         | 596 (S-                                                       | 100) I                              | BUS                              | INTE                                     | RFACE                         | E .                                          | •                    |     | •   | • | • | • • | • | • | 10-1                                   |

|      |                                                | Power<br>Perman<br>10.2.1<br>10.2.2<br>10.2.3<br>10.2.4       | ent Ma<br>Stai<br>Coni<br>Addi      | aste<br>tus<br>trol<br>cess      | r Int<br>Bus<br>Bus<br>and               | Data                          | ice<br>• • • • • • • • • • • • • • • • • • • | s                    |     | •   | • | • |     | • | • | 10-2<br>10-3                           |

| APPE | NDICIES                                        | 3                                                             |                                     |                                  |                                          |                               |                                              |                      |     |     |   |   |     |   |   |                                        |

|      | Append<br>Append<br>Append<br>Append<br>Append | lix B<br>lix C<br>lix D                                       | - Boa<br>- Sch<br>- Bib             | ard<br>nema<br>olio              | icati<br>Layou<br>tic I<br>graph<br>ry . | it Di<br>Diagr<br>Ny .        | agra<br>ams                                  | •                    | • • | •   | • | • | • • | • | • | A-1<br>B-1<br>C-1<br>D-1<br>E-1        |

| C | $\smallfrown$ | K1 | m | F | N  | T | C |

|---|---------------|----|---|---|----|---|---|

| • | _             | L  | _ | Ľ | LV | _ |   |

(this page intentionally blank)

PART ONE: GETTING STARTED

(this page intentionally blank)

#### CHAPTER 1 - INTRODUCTION TO THIS MANUAL

#### 1.1 PURPOSE AND SCOPE

This manual was designed to explain everything you need to know to own. install, operate, evaluate, customize. or write software for the Teletek Systemaster II. Both introductory and advanced information on the hardware is included. This is a hardware manual only, and does not cover the use of any of the currently available software.

This manual is valid for Revision 2 boards.

#### 1.2 ORGANIZATION

This manual consists of two main parts.

PART ONE: GETTING STARTED explains in simple terms how to configure and install your Systemaster II. The information is easy to read and avoids technical jargon as much as possible. If you just want to plug in your new board and start using it, this part is for you.

PART TWO: TECHNICAL INFORMATION covers the architecture of the Systemaster II in explicit detail. The information is by nature very technical. A much greater knowledge of electronics and computer terminology is assumed.

At the back of the manual, several appendicies cover general information not required in the reading. A specification summary and a series of supplementary diagrams are included.

#### 1.3 TERMINOLOGY AND CONVENTIONS

Throughout this manual, signal names that have a leading slash ("/name") represent active low signals on the CPU side of the S-100 bus. Signal names with a trailing asterisk ("name\*") denote active low signals on the S-100 bus.

The terms "IEEE 696" and "S-100" apply to the same standard bus specification. They are used interchangeably throughout this manual.

Most of the abbreviations and part numbers used in this manual are defined in "Appendix E - Glossary".

#### 1.4 RELATED DOCUMENTS

A bibliography is provided in the APPENDICIES section. The suggested literature will provide more complete information on the major integrated circuits used on this board

#### CHAPTER 2 - INTRODUCTION TO THE SYSTEMASTER II

The Teletek Systemaster II is the next evolutionary step in Teletek's line of S-100 master processors. Systemaster II is an 8-bit, full function single board computer consisting of 85 integrated circuits on a four-layer S-100 board. At the heart of Systemaster II is the powerful Zilog Z80H microprocessor. High speed, high performance, and greater memory density are achieved on a standard-size S-100 board through use of the latest LSI support circuitry.

Systemaster II may be used as a dedicated single user computer or as a bus master in a multiprocessor/multitasking system. This flexibility is possible because the Systemaster II contains all of the features required for most applications These features include:

- \* 2 Serial ports.

- \* 2 Parallel ports.

- \* Flexible disk interface.

- \* 64K or 128K bytes of dynamic RAM.

- \* Reconfigurable EPROM pads for high density integrated circuits.

- \* DMA capabilities, fully programmable.

- \* Interrupt controller, 8 individual vectors.

- \* Optional adapters for IEEE 488 or SCSI control.

With the above capabilities Systemaster II can provide high performance computing power in:

- \* Word processing.

- \* Data base management.

- \* Dedicated industrial control.

- \* Laboratory and instrumentation control.

(this page intentionally blank)

#### CHAPTER 3 - INSTALLATION

## 3.1 STANDARD INSTALLATION PROCEDURE

Installing the Systemaster II is straightforward. Most installations will require the following steps:

- 1. Inspect the Systemaster II for shipping damage.

- 2. Ensure that the Systemaster II is configured correctly.

- 3. Make any necessary hardware modifications.

- 4. Plug the board into the S-100 mainframe slot.

- 5. Attach the floppy drive cable.

- 6. Attach the local console cable.

- 7. Attach any other serial devices.

- 8. Attach any parallel devices.

- 9. Turn on and boot the system.

- Make copies of operating system diskettes.

- 11. Configure the operating system.

#### 3.2 VISUAL INSPECTION

Upon receipt of the Systemaster II, check the shipping package for any signs of abuse while in transit. If you suspect that the package has been dropped or pierced notify the shipping company immediately.

Inspect the circuit board for loose components, excessive moisture or anything that might not be normal. If any diskettes were shipped with the Systemaster II, check them for damage such as bending, or signs of a sharp object being placed against them. Diskettes are quite fragile and any damage to the media surface will render them inoperative. Again, notify the shipping company if you find any damage.

#### 3.3 CORRECT CONFIGURATION?

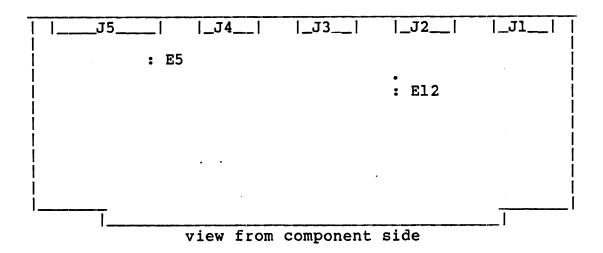

With the component side of the board up and the connector facing you. verify that the following options are correct:

- E5 These two option pins are used only while testing the floppy disk controller. For normal operation, the two pins should not be connected.

- El2 These three option pins determine the source for the timing signal CPUCLK. On a 6 MHz board the top two pins should be connected. On an 8 MHz board the bottom two pins should be connected.

#### NOTE:

Any other modifications to your board will violate your warranty unless you have been authorized by Teletek to make those modifications.

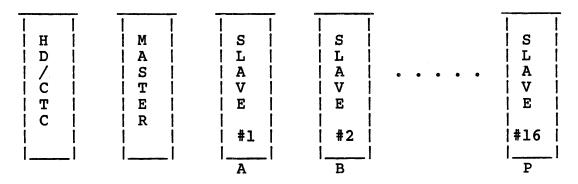

#### 3.4 BUS ORGANIZATION

Which slot you plug into is quite arbitrary unless you will be running six or more slaves and a hard disk controller such as Teletek's HD/CTC. To provide good bus flow and minimize bus noise in an application such as this. the following bus organization is recommended:

address slaves sequentially---->

#### 3.5 COOLING

The Systemaster II needs to be in a well ventilated area due to the high density of integrated circuits on the board Ideally, the board should be mounted vertically in a stream of air which is moving accross its face. Ensure that the fan is close to the card cage for maximum cooling. Whatever the position, forced air cooling is mandatory.

#### 3.6 PERIPHERAL CONNECTIONS

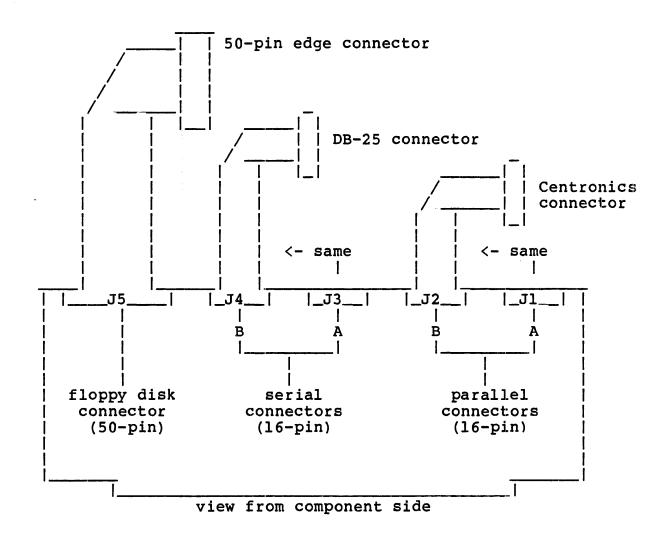

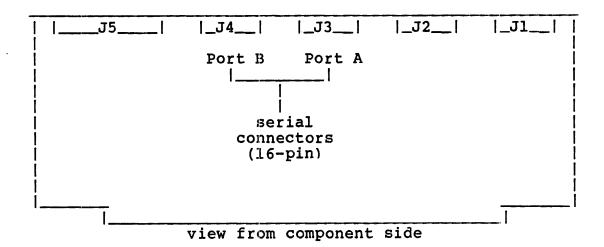

In most cases, the peripheral connections need only be flat ribbon cables with the appropriate crimp style connectors. The location of each of the header connectors is shown below and in "Appendix B - Board Layout Diagram". All these header connectors are male, allowing the use of similar female connectors on each of the cables. Make sure that pin 1 of each cable is toward the left edge of the board when the cable is installed

Bring peripheral cables neatly away from the board with enough slack to prevent any tension being applied to the cable. Too much tension may cause the cable to separate from its crimp connection and cause intermittent problems.

It is possible to order pre-assembled cables meeting your specifications directly from Teletek. Contact Teletek for pricing and shipping information.

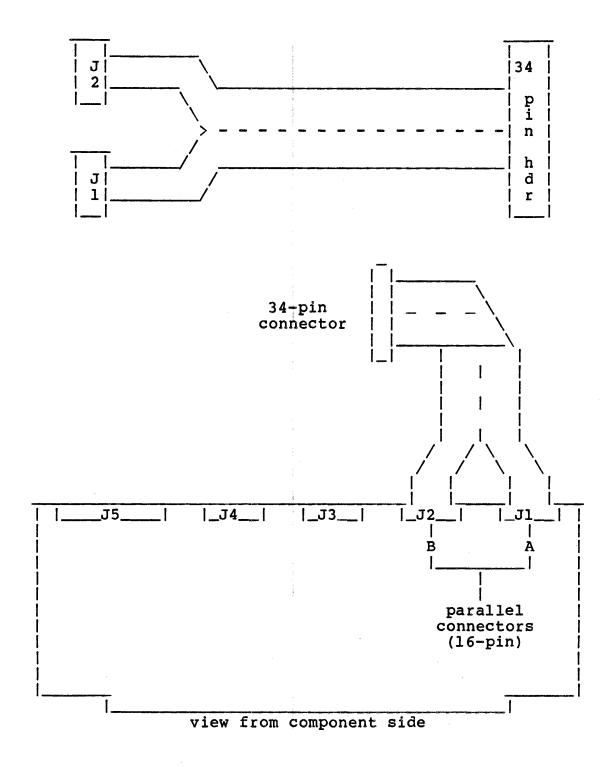

## Connector options

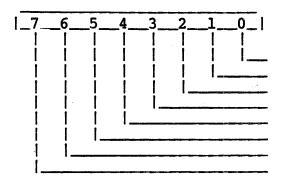

It is possible to configure the two 8-bit parallel ports into one 16-bit port. Depending on the application, it may be advantageous to build a split connector to accomodate this as shown:

#### 3.7 PREPARING YOUR SOFTWARE

If you have not yet made backup copies of your software diskettes, do so now.

To configure your operating system, refer to the software documentation enclosed with your diskettes.

#### 3.8 IN CASE OF TROUBLE

If the Systemaster II does not respond the first time it is connected, relax. Due to the complexity of the board there are many areas that may have inadvertantly been overlooked. Take the time to read the manual thoroughly, especially the "Peripheral Connections" section. The following trouble-shooting guide lists the most common problems

- 1. Are both your system and your console plugged in? Are they both turned on? Is your boot diskette in the correct drive? Is the drive door shut?

- 2. Check the console cable and verify the handshaking signals.

Make sure the console is set at the proper baud rate.

- 3. If the Systemaster II was originally shipped without RAM, make sure the memory chips are installed correctly. Remember that the RAM devices must use the 128 cycle refresh mode in order to be compatible with the Systemaster II's refresh circuit.

- 4. Check the disk drive cable and the disk drive configuration. Has the write precompensation been correctly adjusted for your particular disk drives?

- 5. Have the correct options or modifications been added to the board for the operating system being used? Are you using an operating system designed to work on the Systemaster II?

- 6. If the console and cable are working properly, the correct RAM is installed. the diskette circuitry is configured properly, the correct hardware option modifications have been added. and the operating system has been correctly configured. the Systemaster II itself may be faulty. Try another Systemaster II if one is available. Otherwise, return the board to your dealer for check-out. (If you purchased your Systemaster II directly from Teletek obtain a Return Merchandise Authorization (RMA) number from the factory before shipping the board.)

PART TWO: TECHNICAL INFORMATION

| P | Δ                | RT   | 'IWO |

|---|------------------|------|------|

| - | $\boldsymbol{r}$ | 11.1 | TIV  |

(this page intentionally blank)

## CHAPTER 10 - IEEE 696 (S-100) BUS INTERFACE

Although the S-100 bus interface has been a defacto standard since 1975, many compatibility problems have been solved by the recent (1982) adoption of the IEEE 696 standard specification. The following is a description of the IEEE 696 (S-100) signals as implemented on the Systemaster II.

#### 10.1 POWER AND GROUND

Systemaster II has the following power requirements:

5 volts at 2.0 amps +12 volts at 40.0 milliamps -12 volts at 40.0 milliamps

Onboard voltage is regulated and power supply decoupling is provided both at the card edge and distributed throughout the board.

#### 10.2 PERMANENT MASTER INTERFACE

Systemaster II is configured as a permanent master. This means that it can transfer device-dependent messages to and from all bus slaves. It is also responsible for generating the timing for all bus cycles. Another board in the system may become a temporary master by asserting the HOLD signal on the bus. Once the temporary master has completed its task, it must return control to the permanent master, in this case the Systemaster II.

Systemaster II echos all of its states to the bus by means of timing signals. Please note that the 8 MHz version makes no attempt to slow down to the 6 MHz maximum bus speed described in the IEEE standard specification. The only way to meet the IEEE maximum speed requirement with a faster CPU is by adding wait states and slowing down all transitions, all the time. This lowers the performance of the 8 MHz master by a significant percentage. Teletek chose to provide a full performance 8 MHz master for those applications which require this high speed. For applications which require the board to stay within the IEEE specifications, Teletek recommends the 6 MHz Systemaster II.

The following is a description of the Systemaster II IEEE 696/S-100 interface signals.

## 10.2.1 Status Bus

The status bus consists of seven signals which identify the nature of the bus cycle in progress, and qualify the nature of the address on the address bus. Each of these seven signals are three-state lines which may be disabled by asserting the status disable signal SDSB\* on the S-100 bus.

| SMEMR | memory read           |

|-------|-----------------------|

| sMl   | Operation code fetch  |

| sINP  | Input                 |

| SOUT  | Output                |

| swo*  | Write cycle           |

| SINTA | Interrupt acknowledge |

| SHLTA | Halt acknowledge      |

|       |                       |

#### 10.2.2 Control Bus

The control bus consists of five output control signals (denoted by the lowercase p) and five input control signals.

The five output control signals determine the timing and movement of data during any bus cycle. These signals are typically monitored by slave or controller boards on the bus.

| psync  | Start of new bus cycle       |

|--------|------------------------------|

| pSTVAL | Address and status are valid |

| PDBIN  | Generalized read strobe      |

| pWR*   | Generalized write strobe     |

| PHLDA  | Hold acknwoledge signal      |

The five input control signals allow bus slaves to request operations of the Systemaster II and to synchronize the operation of the master with conditions internal to the slave.

| RDY   | Slave RDY                   |

|-------|-----------------------------|

| XRDY  | Front panel RDY             |

| INT*  | Interrupt line              |

| NMI*  | Non-maskable interrupt line |

| HOLD* | Hold request                |

#### 10.2.3 Address and Data Bus

Systemaster II provides the Z80's 16-bit address bus to the S-100 interface. This means that a linear addressing range of 64K bytes is possible. The refresh address functions of the Z80 may also be used by bus devices since the RFSH\* (refresh) signal is also provided on the bus. The address lines are buffered by three state drivers which may be disabled by the S-100 address disable signal ADSB\*.

A0 through A15 Address bus

Data transfers into Systemaster II pass through octal three state buffers. Systemaster II will only allow data onto its internal bus when qualified bus devices are detected and no onboard memory or I/O read is occurring.

DIO through DI8 Input data bus

Data transfers out of the Systemaster II also pass through a three state driver which may be selectively disabled by bus devices using the data out disable signal DODSB\*.

DOO through DO8 Output data bus

#### 10.2.4 Interrupt and Reset Functions

Bus devices that wish to use Systemaster II's vectored interrupt controller have access to five interrupt lines. The interrupt lines are connected to the 9519 and their use is at the user's discretion unless otherwise specified.

V10\* through V14\* Vectored interrupt lines

Systemaster II contains a power up clear/reset circuit that insures that the CPU and all logic are correctly initialized. A reset is generated automatically on power up or can be caused by a front panel reset. To insure a proper reset, whenever the board is powered down allow a minimum of 30 seconds before powering up again. This lets the reset circuit come to a known condition and be armed for a power up reset.

POC\* Power on clear. Automatic on power up.

Slave Clr\* Reset all slaves. Automatic on power up.

Reset\* Master reset. Typically connected to a front panel reset switch.

(this page intentionally blank)

#### CHAPTER 4 - CPU AND CONTROL LOGIC

The Systemaster II control logic consists of a Zilog Z80B or Z80H CPU, running at 6 MHz or 8 MHz respectively, and several bipolar and MOS LSI integrated circuits. Programmable logic arrays (PLAs) are used to reduce random logic and therefore pack more features onto the board.

#### 4.1 CLOCKS

All clocks are provided by two TTL crystal oscillators running at 16 MHz and 24 MHz (U23 and U30 respectively). The appropriate frequencies are derived at U24 (a 74LS393). Their values are as follows:

| Mnemonic |   | Value          |    |   |                |  |  |  |  |

|----------|---|----------------|----|---|----------------|--|--|--|--|

|          |   |                |    |   |                |  |  |  |  |

| CPUCLK   | 8 | MHz            | or | 6 | MHz            |  |  |  |  |

| DMACLK   | 4 | MHz            | or | 3 | $\mathtt{MHz}$ |  |  |  |  |

| FDCLK2M  | 2 | MHz            |    |   |                |  |  |  |  |

| FDCLKlM  | 1 | $\mathtt{MHz}$ |    | • |                |  |  |  |  |

| PCLK     | 6 | MHz            |    |   |                |  |  |  |  |

Since the clock inputs to the Z80 CPU and the DMA controller require strict levels typical of MOS devices, two HCT parts are used to guarantee the minimum and maximum clock level inputs to these devices. A 74HCT74 (U19) and a 74HCT00 (U20) provide the high speed rail to rail MOS clock interface to the DMA and CPU respectively. Any field replacement of these components must be with HCT devices. LS or S devices cannot provide the voltage levels and the transition times required by the MOS devices.

The Systemaster II is factory configured for either 8 or 6 MHz operation. If you change the operating frequency yourself, you must ensure that the correct clocks are chosen at jumper El2, the correct LSI controllers and components are installed and the correct board modifications are made. Contact Teletek for more information.

#### 4.2 WAIT STATES

As technology advances, CPUs are breaking speed barriers and making more stringent demands of the support circuitry that surrounds them. Faster CPUs such as the Z80B and Z80H require faster memory and peripherals. Where faster support chips are either not available or prohibitively expensive, the CPU must be slowed down instead.

Wait states are a technique of stalling the CPU for a specific number of clock cycles.

Systemaster II uses wait states to slow down for RAM, EPROM and I/O operations. The following table gives the number of wait states for each operation:

| Number of | Wait St | ates  |

|-----------|---------|-------|

| Operation | 6 MHz   | 8 MHz |

| RAM       | 0       | 1     |

| EPROM     | 2       | 3     |

| 1/0       | 2       | 2     |

l wait state = l clock cycle

= 1 x CPUCLK

= 166.7 ns for 6 MHz

= 125.0 ns for 8 MHz

## 4.2.1 Memory Wait States

Memory wait states are provided by U36 (a 74LS164) and U28 (the FDC PLA). The 74LS164 is a shift register and is used to provide a variety of shifted /MREQ signals to be used as gates for different wait state lengths. Pin 3 (MlWS) is used to gate one wait state for RAM. Pin 5 (M3WS) provides the gate for three waits. The FDC PLA does an internal multiplex so that when RAM is active the correct number of wait states for RAM are inserted and when PROM is active, the correct number of wait states for PROM are inserted.

Memory wait state configuration is quite flexible. The Systemaster II is capable of providing up to eight wait states in individual combinations for RAM and EPROM. This is done by connecting the appropriate signal from U36 to pin 7 of the FDC PLA for RAM wait states or to pin 8 of the same PLA for PROM wait states.

When changing the Systemaster II from one speed to the other in the standard configurations. a different FDC PLA is required Consult Teletek if your application requires this

The following figures will help when calculating additional wait states. These figures are provided for general information only!

| Critical Z80 Tim no external dela no external dela no calculated wi | ys conside | ered)  |

|---------------------------------------------------------------------|------------|--------|

| Parameter                                                           | 6 MHz      | 8 MHz  |

| Memory Fetch (time from /M1)                                        | 203 ns     | 140 ns |

| Memory Read/Write<br>  (time from /MREQ)                            | 203 ns     | 150 ns |

#### 4.2.2 I/O Wait States

I/O wait states serve to synchronize the CPU interaction with the ASCC, CIO, DMA and interrupt controller. Both the 6 and 8 MHz versions of Systemaster II use two I/O wait states, so no alterations are necessary to change from one speed to the other.

I/O wait states are generated by U38 (a 74LS164 shift register) and U17 (a 74LS32). Since the shift register provides seven usable taps, it is possible to add as many as seven wait states to I/O operations. However, while there is no limit on the maximum number of wait states, there is a required minimum for proper operation. Systemaster II requires two wait states. Fewer than two will not guarantee proper onboard device access.

If your application requires additional wait states, these can be added by replacing the signal going to Ul7 pin 13 with the proper tap output from U38. Refer to the following table and to "Appendix C - Schematic Diagrams".

| I                       | /0<br>              | WAIT                       | STATE | ES FROM               | U38 | TAPS                |

|-------------------------|---------------------|----------------------------|-------|-----------------------|-----|---------------------|

| pin pin pin pin pin pin | 6<br>10<br>11<br>12 | 2<br>3<br>4<br>5<br>6<br>7 | wait  | states<br>"<br>"<br>" |     | tandard) ptional) " |

|                         |                     |                            |       |                       |     |                     |

## 4.3 I/O DECODER

I/O addresses for onboard devices are decoded by U44 (a 74LS138). Onboard I/O functions occupy four addresses per port, except for the CONTROL LATCH, which uses eight. Onboard I/O decoding is disabled for all non-I/O operations. effectively eliminating I/O noise. The following is a brief description of the decoded ports:

```

/CTL0 - Control 0

/CTL1 - Control 1

/CIOEN - CIO ENable

/ASCCEN - ASCC ENable

/UICEN - Universal Interrupt Controller Enable

/FDCEN - Floppy Disk Controller Enable

/DMAEN - DMA ENable

/RWPORT - Read Write PORT

```

#### 4.4 I/O MAP

Onboard I/O devices occupy 32 consecutive addresses ranging from 00h to 1Fh. as shown in the table below. The remaining I/O addresses (20h to FFh) may be used for other boards such as slaves and disk controllers. When setting the address on other boards, make sure that none of the addresses conflict.

| <br>  Onboard | I/O Addresses    |

|---------------|------------------|

| Ports         | Use              |

|               |                  |

| 00h - 07h     | Control Latch    |

| 08h - 0Bh     | CIO (Z8536)      |

| 0Ch - 0Fh     | ASCC (Z8531)     |

| 10h - 13h     | UIC (9519)       |

| 14h - 17h     | FDC (WD2797)     |

| 18h - 1Bh     | DMA              |

| 1Ch - 1Fh     | RWPORT           |

| 20h - FFh     | not used onboard |

#### 4.5 CONTROL LATCH

Onboard control is implemented with U3, a 74LS259 addressable latch. The latch is bit addressable. This means that individual bits may be set or cleared without affecting the rest of the bits.

Writing a one or zero to an address between 00h and 07h sets or clears a bit as defined in the following table:

| Address           | Mnemonic                        | State                                                                             |  |  |

|-------------------|---------------------------------|-----------------------------------------------------------------------------------|--|--|

| 00h<br>01h<br>02h | OFFBOARD<br>BANK-0/1<br>FDMOTOR | 0= onboard RAM l= offboard RAM<br>0= bank 0 l= bank 1<br>0= motor off l= motor on |  |  |

| 03h<br>04h        |                                 | <del></del> -                                                                     |  |  |

|                   |                                 | 0 0 = drive 0<br>0 1 = drive 1<br>1 0 = drive 2<br>1 1 = drive 3                  |  |  |

| 05h<br>06h<br>07h | FD-D/S<br>FD-5/8<br>/PROMEN     | <pre>0= double density    l= single density 0= 5.25 inch</pre>                    |  |  |

#### 4.6 READ WRITE CONTROL PORT

One additional port is used for two special control signals An I/O operation to any port between 1Ch and 1Fh will access this port.

Any write clears the parity error interrupt.

Any read brings in the status of the floppy drive Dual Side signal in bit 0. Bit 0 = 0 means the diskette is single sided. Bit 0 = 1 means the diskette is double sided

#### 4.7 PROGRAMMABLE LOGIC ARRAYS (PLAS)

Rapid advances in semiconductor technology have resulted in ever larger and more powerfull integrated circuits. One of the fruits of these advancements are PLAs - programmable logic arrays. PLAs are integrated circuits that can be programmed in much the same manner as PROMs. In brief, the PLA contains an array of OR and AND gates that can be selectively fused (connected) together to implement combinatorial functions. The result is that, once programmed one PLA device may contain the equivalent of up to ten discrete MSI circuits.

Systemaster II makes use of PLAs to implement functions that would have required extensive discrete logic. Other reasons for using PLAs are:

- it is an easy way to program hardware

- hardware modification is easier

- the space savings is tremendous

The following paragraphs explain each of the four PLAs used on the Systemaster II and give their output signal definitions.

FDC PLA - The Floppy Disk Control PLA (U28) is used to provide drive selects and clock control to the floppy disk controller. It also gates onboard I/O decodes and generates memory wait states. Note: This PLA must be changed when the CPU speed is changed

```

Signals:

```

FDCCLK - Floppy Disk Controller CLock

DS0 - Drive Select 0

DS1 - Drive Select 1

DS2 - Drive Select 2

DS3 - Drive Select 3

/MWAIT - Memory WAIT states

/IOEN - I/O ENable

RAM PLA - The RAM PLA (U22) is used to initiate RAM access cycles, control bank switching. and keep track of all RAM operations. This PLA defines the common boundary and must be changed when the memory map is changed.

```

Signals:

```

/RAMOFF - Informs additional logic of type of

onboard or offboard RAM access.

/BANKOSW - Control signal for enabling bank 0.

/BANKISW - Control signal for enabling bank 1.

/REFRESH - Informs RAM logic of refresh.

/START - Begins RAM timing at the start of cycles.

WAIT PLA - The WAIT PLA (U35) is used to multiplex the proper wait signals to the CPU. It also generates RAM and EPROM select signals and RAM parity control.

Signals:

/ON - RAM transceiver control signal.

PDOUT - Gated parity data for input to parity IC-

/RAMRD - Parity read clock.

/WAIT - Combination of all the wait states.

A15 - CPU aaddress 15 /PROMSEL - PROM select.

S-100 PLA - The S-100 PLA (U55) generates all the appropriate signals to the S-100 bus.

Signals:

SOUT - Output operation in progress

SINP - Input operation in progress

SMEMR - Generalized memory read

SINTA - Interrupt acknowledge in progress

SWO\* - Generalized memory write

/STRB - Strobes S-100 cycle initiates /PHLDA - Hold acknowledge in progress DIDSB - Disable the input data buffers

Normally there will be no need to change PLAs unless you suspect that your board has a faulty device or you want to change to a faster CPU speed, different number of wait states, different size of common area, etc.

All of the PLAs on Systemaster II are available only from Teletek and should be handled with care to prevent static damage.

#### CHAPTER 5 - MEMORY

Systemaster II is designed with many storage features that make it ideal for single and multiuser environments.

#### 5.1 MEMORY MAPS

## 5.1.1 Standard Memory Map

| FFFFh |                               |                                      |  |

|-------|-------------------------------|--------------------------------------|--|

| F800h | 2K RAM<br>COMMON              | 2K RAM<br>COMMON                     |  |

|       | 62K RAM  <br>BANK 0           | 62K RAM  <br>  62K RAM  <br>  BANK 1 |  |

| 8000h |                               | !!                                   |  |

| 00005 | 32K<br>  phantom  <br>  EPROM | 32K  <br>  phantom  <br>  EPROM      |  |

| 0000h |                               |                                      |  |

## 5.1.2 Optional Memory Map

| FFFFh    |                                 |                       |

|----------|---------------------------------|-----------------------|

| F000h    | 4K RAM<br>COMMON                | 4K RAM<br>COMMON      |

| 1        | 60K RAM  <br>BANK 0             | 60K RAM  <br>BANK 1   |

| 8000h    | ,                               |                       |

| 0000h    | 32K  <br>  phantom  <br>  EPROM | 32K   phantom   EPROM |

| UUUUN I. |                                 |                       |

#### 5.2 RAM

Onboard memory is implemented with 64K x 1 dynamic RAM devices. These RAMs make use of the Z80 CPU refresh capabilities and hence are specified as having a 128 row/2 ms refresh cycle. A 6 MHz board requires 150 ns RAM devices, while an 8 MHz board requires 120 ns devices. If you substitute any RAM yourself, you must use devices of the correct refresh type and operating speed (See "Appendix A - Specifications".)

#### 5.2.1 Bank Control

Bank control is done with the BANK-0/1 and OFFBOARD bits of the control latch. There is no memory management hardware.

The RAM PLA determines a memory address called the common boundary. All writes and and reads above the common boundary are directed to onboard memory, regardless of the state of the OFFBOARD control signal. Writes above the common boundary go to both onboard memory banks, resulting in duplicate copies of common at the top of each bank. Reads above the common boundary come from the onboard bank last selected with BANK-0/1.

Below the common boundary, memory accesses are more normal. If the OFFBOARD bit is set to zero, reads and writes act on the onboard bank last selected with BANK-0/1. If the OFFBOARD bit is set to one, reads and writes act on an offboard bank.

#### 5.2.2 Parity Checking

An added feature of the Systemaster II is its use of parity as a memory error detection mechanism. The Systemaster II is set up to check for even parity. and because it has an even parity bus (8 bits), the operation is easy to understand-

Parity checking is done with U41 (a 74LS280) and each RAM bank has an individual RAM used to store parity information. The following action takes place when doing a write to RAM:

- If the byte to be written conains an even number of one bits, then the output of the parity checker is a zero. This zero is written to the parity RAM along with the byte, leaving the total number of one bits unchanged.

- If the byte to be written contains an odd number of one bits, then the output of the parity checker is a one. This one is written to the parity RAM along with the byte, making the total number of one bits even.

As you can see, any byte that does not contain an even number of ones is forced to be even by the parity checker. We can therefore be sure that all bytes written to RAM are of even parity. This means that if no errors occur to the data while in memory, every byte we read back will be even. If any byte is not even, the parity checker will detect the error. Additional support circuitry will then post the parity error interrupt.

## 5.2.3 Parity Initialization

There are no set procedures for initializing parity since this is strictly a hardware function. However, one traditional action is to write zeros to all of RAM and then read them back. This checks your RAM for bad cells and at the same time starts you out with a clean slate (all locations set to zero).

#### 5.2.4 Parity Clear/Disable

The parity interrupt signal /PARINT is connected to request 0 of the interrupt controller. When necessary, this individual interrupt may be masked out in the interrupt controller, effectively disabling parity.

Once a parity error has been handled by an interrupt routine, the parity interrupt should be cleared by doing a dummy write to any address at /RWPORT (1Ch to 1Fh).

#### 5.3 EPROM

EPROM operation on Systemaster II is very flexible. Upon power up or reset condition, the PROM is automatically enabled at location 0000h. In this condition, the memory map is partitioned with the lower 32K (0000h to 8000h) as PROM area. While the PROM is enabled, it is still possible to write to the RAM in the same address range as the PROM (the lower 32K). Writes to an address in the lower 32K will go to the RAM, while reads from the lower 32K come from the PROM. This switching is done automatically in hardware.

The PROM can be disabled under software control. This is done with the /PROMEN bit of the control latch. When the PROM is disabled, it is effectively removed from the memory map. This means that now the entire addressing range may be used to address RAM.

#### 5.3.1 Density options

In the past, the size of onboard firmware has been limited by the size of the EPROM standard on the board. Systemaster II overcomes this limitation by providing a fully approved JEDEC EPROM socket with the capability to handle 2K to 32K devices (2716 to 27256). This means that custom firmware may be implemented in an appropriately sized EPROM by simply modifying the socket pads.

The diagram on the next page shows the JEDEC approved INTEL universal site for EPROMS which Systemaster II uses. It shows an EPROM whose pins on either side have different classifications. For example, to find the required signals for 2716s, simply read the 2716 column on either side. The illustration clearly shows which signals change between densities.

|                                        | JED                                     | EC A                                                                                | APPRO                                                                 | OVED                                                                  | INTEL                                                    | UNIVER         | SAL SIT                                                     | E FOR                                                                     | R EPI                              | ROMS                                                                                    |                                                                                         |

|----------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------|----------------|-------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 2  <br>7  <br>2  <br>5  <br>6          | 2  <br>7  <br>1  <br>2  <br>8           | 2<br>7<br>6<br>4                                                                    | 2<br>  7<br>  3<br>  2                                                | 2<br>  7<br>  1<br>  6                                                |                                                          |                | 2<br>  7<br>  1<br>  6                                      | 2  <br>  7  <br>  3  <br>  2                                              | 2<br>7<br>6<br>4                   | 2<br>  7<br>  1<br>  2<br>  8                                                           | 2  <br>  7  <br>  2  <br>  5  <br>  6                                                   |

| A7 A A A A A A A A A A A A A A A A A A | A12<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2 | VPP<br>A12<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0<br>D0<br>D1<br>D2<br>GND | A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0<br>D0<br>D1<br>D2<br>GND | A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0<br>D0<br>D1<br>D2<br>GND | 1<br> 2<br> 3<br> 4<br> 5<br> 6<br> 7<br> 8<br> 9<br> 10 | 18<br>17<br>16 | VCC<br>A8<br>A9<br>VPP<br>OE<br>A10<br>CE<br>D7<br>D6<br>D5 | VCC<br>A8<br>A9<br>A11<br>/OE<br>A10<br>/CE<br>D7<br>D6<br>D5<br>D4<br>D3 | /PG A8 A9 A11 /OE A10 /CE D7 D6 D5 | VCC<br>/PG<br>A13<br>A8<br>A9<br>A11<br>/OE<br>A10<br>/CE<br>D7<br>D6<br>D5<br>D4<br>D3 | VCC<br>A14<br>A13<br>A8<br>A9<br>A11<br>/OE<br>A10<br>/CE<br>D7<br>D6<br>D5<br>D4<br>D3 |

The standard Systemaster II is configured for a 2K EPROM. The table below lists the steps necessary to convert a standard board to accept an EPROM of a different size. (The locations of the "E" pads are shown in "Appendix B - Board Layout Diagram".)

| EPROM      | Disconnect                                         | Connect                                      |

|------------|----------------------------------------------------|----------------------------------------------|

| 2732, 4K   | E3-2 from E3-1                                     | E3-2 to E3-3                                 |

| 2764, 8K   | E3-2 from E3-1                                     | E3-2 to E3-3                                 |

| 27128, 16K | E3-2 from E3-1<br>E2-3 from E3-1                   | E3-2 to E3-3<br>E2-2 to E2-3                 |

| 27256, 32K | E3-2 from E3-1<br>E2-3 from E3-1<br>E1-2 from E1-1 | E3-2 to E3-3<br>E2-2 to E2-3<br>E1-2 to E1-3 |

(this page intentionally blank)

## CHAPTER 6 - CHARACTER INPUT/OUTPUT

Any computer is virtually useless unless you can communicate with it through some kind of interface. Once provided with such an interface, you can interact with the computer and program it to do useful work.

Systemaster II provides both serial and parallel interfaces that are completely reprogrammable and can be configured for a variety of applications.

## 6.1 ASCC SERIAL PORT CONTROLLER

Serial ports on the Systemaster II are controlled through a Zilog Asynchronous Serial Communications Controller (ASCC). The ASCC is a dual channel serial tramsmitter and receiver, and is an upgrade of the Zilog SIO. It provides two very powerful serial ports.

### 6.1.1 CPU to ASCC Interface

The CPU communicates with the ASCC via programmed I/O. The ASCC looks like four port addresses to the CPU. Each channel (A or B) has its own control register and its own data register. Internally, the ASCC contains 14 write registers and 7 read registers

Each channel's write register set includes the following:

- 10 registers used for control

- 2 registers used for sync character generation

- · 2 registers used for baud rate generation

Each channel's read register set is composed of:

- 4 registers used for status functions

- 2 registers used by the baud rate generator

- 1 register for the receive buffer

### 6.1.2 ASCC Software Interface

The ASCC contains two independent asynchronous serial channels. each with its own baud rate generator. Each channel has a set of internal read registers (RRx) and write registers (WRx), and two external ports called the control and data ports to access these registers. The control and data port addresses for the ASCC channels are shown below. Several of the internal ASCC registers are common to both channels and can be accessed through either channel's control port.

| ASCC | Port | Ac | dresses |

|------|------|----|---------|

| 0Ch  | Port | В  | control |

| 0Dh  | Port | В  | data    |

| 0Eh  | Port | A  | control |

| 0Fh  | Port | A  | data    |

The ASCC internal registers are accessed in a two-step process, using a pointer register to address the internal register. To access a particular register, the pointer bits must be set by writing to WRO. WRO is common to both channels and a write to either channel's control port will set the pointer bits in WRO. After the pointer bits are set, the next read or write operation with the selected channel's control port will access the desired internal register for that channel. After this read or write operation, the pointer bits are reset to zeros, and the next write to either control port will access WRO. If the state of the pointer bits is unknown, then a read from either channel's control port will reset them to zeros. Also, each channel's internal transmit data buffer register WR8 and internal receive data register RR8 can be accessed directly by a read or write operation with the desired channel's data port.

Each ASCC channel is initialized by writing a stream of bytes to the control port for that channel. This stream of bytes contains pointer register values followed by register content values for loading the internal registers needed to configure the channel's operation mode. A separate stream of bytes is send to each ASCC channel.

Each channel is initialized with respect to three areas:

- asynchronous mode format

- baud rate generation

- interrupt operation

The asynchronous mode configuration allows specification of the following parameters:

- 5, 6, 7 or 8 bits per character

- 1, 1.5 or 2 stop bits for transmitter

- Odd. even, or disabled parity generation

- Times 1, 16, 32 or 64 clock rates

- Hardware CTS\*/DCD\* handshaking via Auto Enables option

- Selection of transmit and receive clock sources from RTYC\* pin

RTxC\* pin TRxC\* pin

Baud Rate Generator Output

Each channel contains a baud rate generator to provide the transmit and/or receive clock(s). The baud rate generator consists of a two-byte down counter and some multiplexing logic. Given an input clock source (either the PCLK pin or RTxC\* pin), the baud rate generator will divide this source by the value in the baud rate Time Constant registers to produce a clock for the transmit and/or receive section. The PCLK pin is driven by a 6 MHz clock and the RTxC\* pin is driven by a 24 MHz clock.

The ASCC allows vectored interrupts for all internal interrupting sources using the Vector-Includes-Status mode. In this mode, the base interrupt vector held in WR9 has certain bits modified to produce a response vector that identifies which internal interrupt source is being acknowledged WR9 is common to both channels and can be accessed through either channel's control port. Each internal interrupt source in the ASCC can be enabled or disabled individually. The internal interrupt sources in the ASCC are as follows:

- Ch B Transmit Buffer empty

- Ch B External/Status Change

Zero Count of Baud Rate generator DCD\* pin transition SYNC\* pin transition CTS\* pin transition Break detection

- Ch B Receive Character Available

- Ch B Special Receive Condition

Parity Error Overrun error Framing Error

- Ch A Transmit Buffer empty

- Ch A External/Status Change

- Ch A Receive Character Available

- Ch A Special Receive Condition

#### Usage Notes:

- The number of transmit stop bits can be selected but the receiver always checks for one stop bit.

- The ASCC contains both a receive data FIFO and a receive error FIFO so that receive errors can be stacked along with the associated receive characters. The act of reading the data pops both the data and error FIFOs. If status is needed it must be read before reading the data.

- The ASCC provides both Local-Loopback and Auto-Echo modes for diagnostic purposes.

- Each channel's baud rate generator output can be routed out to the associated TRxC\* pin for diagnostic uses.

- Since the pointer bits in WRO are always reset to zeros after an access. writes to WRO and reads from RRO can be done without first setting the pointer bits.

- When reading RR2, Channel A returns the base interrupt vector and Channel B returns a vector which includes status information.

- RR3, the interrupt pending register, can only be read from Channel A.

- All ASCC interrupt service routines should end with a RESET HIGHEST IUS command to the proper ASCC channel. In addition, if an error condition is present (such as Parity Error) then an ERROR RESET command should also be sent.

- The ASCC supports the generation of a BREAK signal in WR5, and detection of a break signal in RR0.

- WR5 controls the levels of the DTR\* and RTS\* pins on the ASCC device and at the serial connector if that is the function specified for those pins. These lines should be considered when handshaking problems are present.

## 6.1.3 Asynchronous and Synchronous Transfers.

The ability to transfer serial data to other computers and peripherals is one of the features that make Systemaster II a true single board computer. This is further enhanced by the ability to communicate with both asynchronous and synchronous protocols

Asynchronous transmissions is defined as transmitting the smallest unit of data (one byte) independent of any other unit of data. Each byte is tagged with a start and a stop bit and also parity information. This type of transmission is used with slow speed devices such as terminals, printers and low speed modems. Systemaster II when equipped with the ASCC can provide all the intelligence needed for asynchronous transmissions in a variety of baud rates.

Synchronous transmissions are intended for high speed transfers as might be required when two computers are communicating. Synchronous transfers are a bit more complicated because they involve the transfer of a packet of bytes and special trailer and header characters depending on the protocol. Instead of transmitting a byte at a time, the data can now be packaged and transmitted in blocks at a very fast rate. This type of communications is also possible with Systemaster II. In order to do this, the ASCC is replaced with a SCC which is a part that handles synchronous protocols. Provisions for receiving a remote clock are provided onboard.

### 6.1.4 Serial Connectors

Systemaster II uses RS232-C to communicate serially to the outside world. RS232-C is a standard for connecting a defined set of wires from one computer to another or from computer to modem. The standard also defines the signal voltage transitions (+12 to -12) and the maximum distance (50 feet).

The ports on the ASCC are translated to RS232-C by U6 and U5 both of which are 75188 level translators. Signals coming from the connector are translated to TTL by U7 and U4 (75189s). The connectors on Systemaster II are 16-pin straight headers which are typically connected to a DB-25 connector through a ribbon cable. Pins on the DB-25 are aligned with the header by ensuring that pin 1 on the header plug is pin 1 of the DB-25.

Serial channels 0 and 1 are on connectors J3 and J4 respectively, as shown:

The following table shows the signal connections for each serial port and how they relate to the EIA pins. Both connectors have the same signal connections.

| Header | DB-25 |                   | Direction   |

|--------|-------|-------------------|-------------|

| Pin    | Pin   | EIA Signal        | from master |

|        |       |                   |             |

| 3      | 2     | Transmitted data  | In          |

| 5      | 3     | Received data     | Out         |

| 7      | 4     | Request to send   | In          |

| 9      | 5     | Clear to send     | Out         |

| 11     | 6     | Data set ready    | Out         |

| 13     | 7     | Signal ground     |             |

| 14     | 20    | Data terminal rdy | In          |

The Systemaster II is considered a DCE (Data Communications Equipment) if you have problems communicating with another device make sure that the appropriate connections are made and that they are facing the correct direction.

## 6.2 CIO PARALLEL PORT CONTROLLER

Systemaster II provides two parallel ports controlled by a Zilog Counter/Timer and Parallel I/O Controller (CIO). The CIO is a parallel communications controller with additional interrupt and counter/timer capabilities.

## 6.2.1 CPU To CIO Interface

The CIO is I/O mapped and looks like four I/O ports to the Systemaster II as shown below:

| CIO | Port Address |

|-----|--------------|

| 08h | Port C data  |

| 09h | Port B data  |

| 0Ah | Port A data  |

| 0Bh | Control      |

The CIO is operated at its full speed of 6Mhz. Communication with either a 6 or 8 MHz Systemaster II is ensured by dedicated logic that synchronizes both.

#### 6.2.2 CIO Software Interface

The Z8536-CIO contains two 8-bit parallel ports, one 4-bit parallel port, three 16-bit counter/timers, and a set of internal registers to configure and control these parallel ports and counter/timers. The CIO has an external control port through which all internal registers are accessed. The CIO also has three external data ports, one for the data register associated with each parallel port.

Accessing the CIO internal registers is done with a state machine and a pointer register. The pointer register holds a value that addresses one of the CIO's internal registers. The state machine determines if accesses to the CIO control port are to the pointer register or to an internal register. The Zilog Z8036 Z-CIO/Z8536 CIO Counter/Timer and Parallel I/O Unit Technical Manual gives a good discussion of the state machines operation. In general, after a reset operation the CIO is left in State 0. Reads from the control port in State 0 leave the state machine in State 0 and access the internal register currently addressed by the pointer register. Writes to the control port in State 0 update the pointer register and put the state machine into State 1. A read or write in State 1 accesses the internal register addressed by the pointer register and places the state machine back into State 0.

Each CIO parallel port or counter/timer is initialized by writing a stream of bytes to the control port. This stream of bytes contains pointer register values followed by register content values for loading the internal registers needed to configure the various operation mode.

The CIO supports a multitude of parallel port operating modes. The CIO parallel ports are used to support parallel printers and will be discussed in that context. Port A and Port B will each support one parallel printer. Port C provides the additional lines required to support handshaking. Port A and Port B allow specification of the following operating modes:

- Output Port with handshake modes

- Interlock Handshake

- Strobed Handshake

- Pulsed Handshake (in conjunction with Counter/Timer 3)

- Three-Wire Handshake

- Variable Deskew timing of the DAV handshake line

- Single or Double buffered mode

- Interrupts on one or two bytes

- Data line polarity

- Normal

- Inverted

- Data line drivers

- Normal Output

- Open Drain Output

- Pattern matching

- AND or OR matching

- Pattern Polarity (Normal/Inverted)

- Pattern Transition

- Pattern Match Mask

- Port A.and Port B can be linked to operate as a 16-bit port

CIO interrupts are generated by Port A. Port B, and each of the three counter/timers. Each interrupt source has an associated control register and the CIO also has a Master Interrupt Control Register. Port A. and Port B each have a separate interrupt response vector. The counter/timers share one interrupt response vector. The CIO identifies the internal interrupt source being acknowledged by encoding status information into the returned interrupt response vector. At the end of any CIO interrupt service routine a RESET IUS command should be issued to the internal CIO source that generated the interrupt.

# 6.2.3 CIO Counter/Timers

A added feature of the CIO is the provision of three independent 16-bit counter/timers. Each counter/timer is fully programmable for down count, time constant and mode of count.

Each of the CIO's three counter/timers allow the following operating modes to be specified:

- Continuous or Single-Cycle mode

- Output Waveform

- Pulse

- One-Shot

- Square-Wave

- Retrigger of counter in the middle of a coundown

- External access to

- Counter Output

- Counter Enable

- Count Input

- Trigger Input

- Gate Input

- Counter/Timer 1 (CT1) and Counter/Timer 2 (CT2) can be linked to form a 32-bit counter with the options of:

- CTl's output gates CT2

- CT1's output triggers CT2

- CT1's output is CT2's count input

### 6.2.4 Parallel Connectors

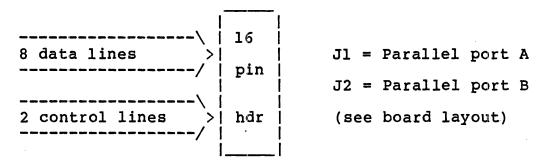

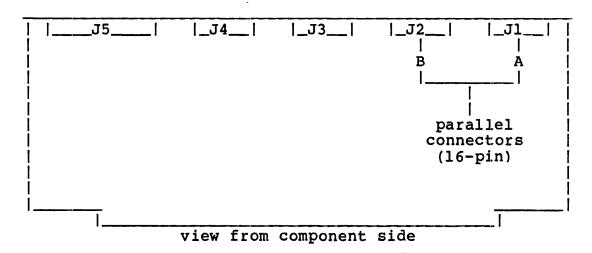

The parallel ports on Systemaster II exit to the outside world through two 16-pin headers, each. in the following fashion:

As shown in the illustration, each port is configured (standard product) as an 8-bit output port with a data strobe and a acknowledge input. The typical devices attached to these ports are Centronics-type printers and peripherals. In most cases the cable required is a 16-conductor flat ribbon cable with a header plug on one end and a cinch connector on the other. An alternative to making your own cables is to order them from Teletek. The tables on the next page give the pinouts for each port and show their relation to the Centronics connector.

The following illustration shows the location of the parallel connectors

Port A Signals

|                                                                                                                         |                                                    | ~~~~~~~                                             |                                             |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------|---------------------------------------------|

| Signal Name                                                                                                             | CIO                                                | Header                                              | Centronics                                  |

|                                                                                                                         | pin                                                | pin                                                 | pin                                         |

| Port A data 0 Port A data 1 Port A data 2 Port A data 3 Port A data 4 Port A data 5 Port A data 6 Port A data 7 /ACKINA | 33<br>32<br>31<br>30<br>29<br>28<br>27<br>26<br>21 | 15<br>13<br>11<br>9<br>7<br>5<br>3<br>1<br>14<br>16 | 2<br>3<br>4<br>5<br>6<br>7<br>8<br>not used |

| +5 volt                                                                                                                 |                                                    | 6                                                   | not used                                    |

| Ground                                                                                                                  |                                                    | 8                                                   | 19-30                                       |

Port B Signals

| Signal Name   | CIO<br>pin | Header<br>pin | Centronics<br>pin |

|---------------|------------|---------------|-------------------|

| Port B data 0 | 8          | . 15          | 2                 |

| Port B data 1 | 9          | 13            | 3                 |

| Port B data 2 | 10         | 11            | 4                 |

| Port B data 3 | 11         | 9             | 5                 |

| Port B data 4 | 12         | 7             | 6                 |

| Port B data 5 | 13         | 5             | 7                 |

| Port B data 6 | 14         | 3             | 8                 |

| Port B data 7 | 15         | 1             | not used          |

| /ACKINB       | 19         | 14            | 10                |

| /DAVB         | 20         | 16            | 1                 |

| +5 volt       |            | 6             | not used          |

| Ground        |            | 8             | 19-30             |

It is important to note that the parallel ports are not buffered. This limits the distance that a peripheral can be located from the Systemaster II. This should not cause any problems as long as this distance is less than 15 feet. Should your application require longer cable lengths, Teletek recommends the addition of an external board containing single ended or differential drivers. Teletek's PPD board is available for this purpose.

| CU | A | D | λ | CTEF | ) T / | 'n |

|----|---|---|---|------|-------|----|

| V  | _ |   | ~ |      |       | ., |

(this page intentionally blank)

## CHAPTER 7 - FLOPPY DISK INPUT/OUTPUT

Floppy disks are at present the most affordable and the most popular non-volatile storage medium in use with computers. As floppy densities rise and drive electronics become more sophisticated it is quite clear that the floppy subsystem will be with us for a long time.

## 7.1 DISK CONTROLLER

Systemaster II makes use of the latest technology in disk controllers by using the Western Digital WD2797-02 Floppy Disk Controller. This integrated circuit is very dense. The overall reliability of the floppy disk section is enhanced because this chip contains an internal data recovery circuit. Two external potentiometers and one trim capacitor are all that is required to adjust the circuit for operation with a large variety of disk drives.

## 7.2 CPU to FDC INTERFACE

The following are the floppy disk I/O port assignments:

|                          | DISK CON'<br>ASSIGNM      |                            |

|--------------------------|---------------------------|----------------------------|

| Address                  | Read                      | Write                      |

| 14h<br>15h<br>16h<br>17h | Status<br>Track<br>Sector | Command<br>Track<br>Sector |

| 1Ch-1Fh                  | Data<br>Sides             | Data<br>-                  |

The first four ports are defined by the Western Digital WD2797 floppy disk controller. The last four addresses are the Read Write Control Port. (See section 4.6) Reading from any of the last four ports brings in the status of the floppy drive Dual Side signal on bit 0:

Bit 0 = 0 The disk is single sided Bit 0 = 1 The disk is double sided

## 7.3 FDC SOFTWARE INTERFACE

The CPU communicates with the FDC (floppy disk controller) via programmed I/O reads and writes. All of the internal registers are programmed and checked for status in this manner. It is possible to poll the FDC for data transfers; however, the Systemaster II makes use of DMA and interrupts to maximize the transfer rate.

The FDC DMA request pin FDRQ is connected to the DMA RDY input. This signal is used by the FDC to request the initiation of a DMA transfer. The DMA is programmed to accept RDY as a high voltage level.

FDCINT is the FDC interrupt request signal that is used to post an interrupt to the 9519 controller. The 9519 accepts this signal as interrupt request #2 and uses the active low level option.

Other floppy disk drive control functions are implemented with an onboard control latch. These auxiliary control functions are drive select, disk density (FM or MFM), drive size (5.25 or 8 inch), and drive motor on/off. For more details on the control latch, see Section 4.4 of this manual.

# 7.3.1 Disk Controller Command Summary

(Programming Summary for WD 2797 FDC)

## STATUS REGISTER

Busy

Index detected or DMA request

Track 0 or Lost data (under/over run)

CRC error

Seek error or Record not found

Head loaded or Record type (read)

Write protected

Not ready

| Rl I | R0 | Ste | p r | ate |

|------|----|-----|-----|-----|

| 0    | 0  | _   | or  | -   |

| 0 :  | 1  | 6   | or  | 12  |

| 1 1  | 0  | 10  | or  | 20  |

| 1 1  | 1  | 15  | or  | 30  |

| Ì    |    |     |     |     |

| length | Sector | length |

|--------|--------|--------|

| 0      | 128    | bytes  |

| 1      |        | bytes  |

| 2      | 512    | bytes  |

| 3      | 1024   | bytes  |

|        |        |        |

| <br>  Flag  | Value  | Action                                    |

|-------------|--------|-------------------------------------------|

| E           | 0      | No head load delay<br>Delay 15/30 ms      |

| H<br>H      | 0<br>1 | Unload head<br>Load head                  |

| L           | 0<br>1 | Sector size times 2<br>Normal sector size |

| M           | 0      | Single sector<br>Multiple sectors         |

| ָ<br> <br>  | 0<br>1 | Select disk side 0<br>Select disk side l  |

| <br>  V<br> | 0<br>1 | No verify<br>Verify destination track     |

```

FDC COMMANDS

Force interrupt > 1101 I3 I2 I1 I0

ACTION: terminate current command and interrupt on condition

INPUT: IO not-ready to ready condition

Il ready to not-ready condition

12 every index pulse

I3 immediate interrupt

Rezero ----> 0000 H V R1 R0

(recalibrate)

ACTION: issues up to 255 step pulses until "zero" signal

OUTPUT: loads track with 0

Seek ----> 0001 H V R1 R0

INPUT: track register contains current track

data register contains track to seek

OUTPUT: track register contains new current track

Read address --> 11000 E 00

(read id)

OUTPUT: 6 bytes of data: 0 Track number

1 Side number

2 Sector number

3 Sector length

4,5 CRC 1 and 2

also puts track number in sector register

Read sector ---> 100 M L E U 0

INPUT: track register, sector register, side select

OUTPUT: sector data, status in status register

Write sector --> 101 M L E U 0

INPUT: track reg., sector reg., side select, sector data

OUTPUT: status in status register

Write track ---> 11110 E U 0

(format track)

INPUT: selected track. all track format bytes

```

## 7.4 DISK CONTROLLER ADJUSTMENT

Adjustment of the floppy disk controller is not complicated Results are easily achieved if the procedure given here is followed. Nevertheless, these adjustments are recommended for qualified people only and should be done with reliable equipment.

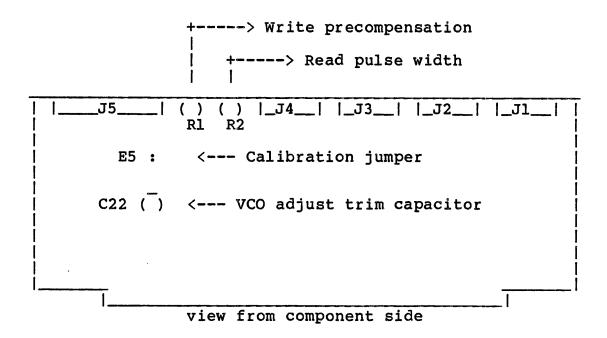

The following diagram shows the locations of the test jumper pins (E5) and the discrete components used for adjustment of write precomensation and the data separator.

Head load timing is controlled by Ull, a 74LS221 one shot. The standard head load timing is set at approximately 40 ms and will work fine with most drives. If a different value is required, use the formula below to derive the value of either the resistor or the capacitor for the new time desired. Then replace the component with one of the new value.

Head load time =  $0.7 \times R4 \times C3$

# Write Precompensation Adjustment

- 1. Set /Test (pin 22) to a logic high. This is done by insuring that jumper E5 is out.

- 2. Strobe /MR (pin 19). On systems with front panel reset, simply reset. If your system does not have a front panel reset, momentarily short /MR to ground.

- 3. Set /TEST (pin 22) to a logic low. This is done by installing jumper E5.

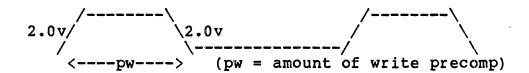

- 4. Observe pulse width on WD (pin 31) -

- 5. Adjust WPW (pin 33) for the desired precompensation value. This is done by monitoring the pulse width on pin 31 and adjusting pot Rl for the desired value. Measure the pulse width at TTL high levels.

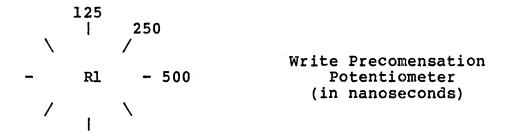

It is possible to set the write precompensation even if you do not have an oscilloscope. Before each board leaves the factory. pot Rl is calibrated and has the three most common write precompensation settings marked on it. Simply refer to the drawing below and set the pot for the desired value. Note that the drawing is an approximation only; the location of the marks will vary from board to board

6. Set /TEST (pin 22) to logic high. This is done by removing the jumper at E5.

# Data Separator Adjustment

- 1. Set /Test (pin 22) to a logic high. This is done by insuring that jumper E5 is out.

- 2. Strobe /MR (pin 19). On systems with front panel reset, simply reset. If your system does not have a front panel reset, momentarily short /MR to ground.

The disk controller must be adjusted for 8 inch double density. Once this is done the internal logic takes care of internal divides for the correct density and data rates. Therefore, it is very important that the size and density control bits are set correctly: FD-5/8 = 1, FD-D/S = 0. If these control signals are not correctly set, the test signals will be meaningless.

- 3. Set /TEST (pin 22) to a logic low. This is done by installing jumper E5.

- 4. Observe pulse width on TG43 (pin 29). Make all observations at TTL high levels.

- 5. Adjust pot R2 for 1/8 of the read clock (250 ns).

- 6. Observe frequency of DIRC (pin 16) -

- 7. Adjust VCO trim pot C22 for the correct data rate (500 KHz).

- 8. Set /TEST (pin 22) to a logic high. This is done by removing the jumper at E5.

The following table is included for your convenience:

|                   | 5.25 inch |         | 8 inch  |         |

|-------------------|-----------|---------|---------|---------|

|                   | FM        | MFM     | FM      | MFM     |

|                   |           |         |         |         |

| Data Rate         | 125 Khz   | 250 Khz | 250 Khz | 500 Khz |

| Read Clock        | 8 us      | 4 us    | 4 us    | 2 us    |

| 1/8 of Read Clock | l us      | 500 ns  | 500 ns  | 250 ns  |

#### \*\* WARNING \*\*

Ensure that jumper E5 is removed after all the adjustments have been made. While this jumper is installed the disk controller echoes its internal signals to several output pins including the data bus. This will definitely cause problems with the CPU.

### 7.5 DISK DRIVE INTERFACE

The drive interface consists mainly of signal conditioning logic. Signals to the drive are driven by high current sinking schottky drivers. Signals from the drive are received through schmitt devices which clean up the signal before it reaches the disk controller.

### 7.5.1 Drive Connector

The floppy disk controller interfaces to the disk drive via J5, a 50-pin header. The header conforms to the ANSI standard for 8 inch drives, as follows:

| Ground      | Signal |          |

|-------------|--------|----------|

| Pin         | Pin    | Signal   |

|             |        |          |

| 1           | 2.     | /TG43    |

| 3<br>5<br>7 | 4      | not used |

| 5           | 6      | not used |

|             | 8      | /TG43    |

| 9           | 10     | /DS      |

| 11          | 12     | not used |

| 13          | 14     | /sso     |

| 15          | 16     | not used |

| 17          | 18     | /HLD     |

| 19          | 20     | /IP      |

| 21          | 22     | /READY   |

| 23          | 24     | not used |

| 25          | 26     | /DSEL0   |

| 27          | 28     | /DSEL1   |

| 29          | 30     | /DSEL2   |

| 31          | 32     | /DSEL3   |

| 33          | 34     | /DIR     |

| 35          | 36     | /STEP    |

| 37          | 38     | /WD      |

| 39          | 40     | /WG      |

| 41          | 42     | /TR00    |

| 43          | 44     | /WPRT    |

| 45          | 46     | /RRD     |

| 47          | 48     | not used |

| 49          | 50     | /MOTOR   |

Connector J5 is a standard 50-pin header for 8 inch drives. To hook up 5.25 inch drives it will be necessary to transpose the signals to a 34-pin header. If you build this connector yourself make sure it conforms to the ANSI standard and refer to the schematics. Optionally, you may order an assembled and fully tested connector from Teletek.

# 7.4.2 Drive Signal Definition

The following is a brief description of the meaning and purpose of the drive interface signals. For a more explicit description of these signals, refer to the manual for your particular drives.

| Signal | Direction | Meaning                                                                                         |

|--------|-----------|-------------------------------------------------------------------------------------------------|

| /TG43  | out       | Track Greater than 43. An active low signal means a track above 43 is being accessed.           |

| /DS    | in        | Double sided. An active low signal tells the controller the drive contains a double sided disk. |

| /sso   | out       | Side Select Output. Selects either side of the diskette.                                        |

| /HLD   | out       | Head LoaD. Controls the loading of the Read/ Write against the media.                           |

| /IP    | in        | Index Pulse. Informs the controller an index hole has been sensed.                              |

| /READY | in        | Drive READY. This input indicates the drive is ready for access.                                |

| /DSEL0 | out       | Drive SELect 0. Selects drive 0.                                                                |

| /DSEL1 | out       | Drive SELect 1. Selects drive 1.                                                                |

| /DSEL2 | out       | Drive SELect 2. Selects drive 2.                                                                |

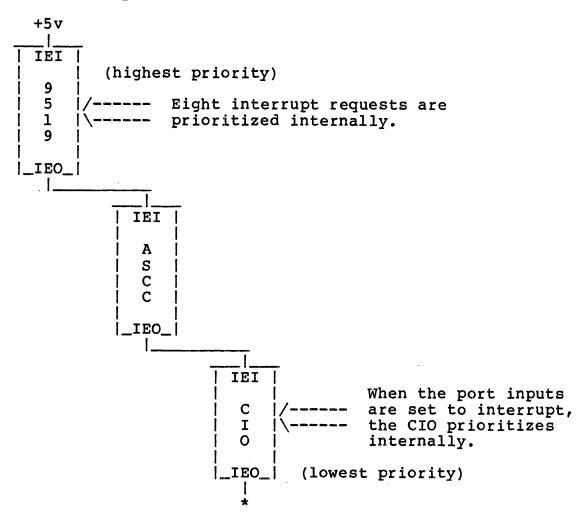

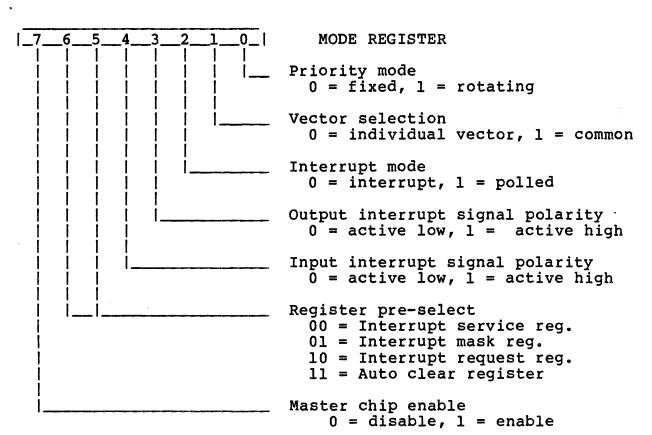

| /DSEL3 | out       | Drive SELect 3. Selects drive 3.                                                                |