# SST-96 (a.k.a. Voodoo Rush<sup>TM</sup>)

# VOODOO GRAPHICS FOR WINDOWS

Revision 2.2 November 30, 1999 Copyright © 1997 3dfx Interactive, Inc. All Rights Reserved

# 3Dfx Interactive, Inc.

4435 Fortran Drive Phone: (408) 935-4400 Fax: (408) 262-8602 www.3dfx.com

# **Copyright Notice:**

[English translations from legalese in brackets]

©1996-1999, 3Dfx Interactive, Inc. All rights reserved

This document may be reproduced in written, electronic or any other form of expression only in its entirety.

[If you want to give someone a copy, you are hereby bound to give him or her a complete copy.]

This document may not be reproduced in any manner whatsoever for profit.

[If you want to copy this document, you must not charge for the copies other than a modest amount sufficient to cover the cost of the copy.]

## **No Warranty**

THESE SPECIFICATIONS ARE PROVIDED BY 3DFX "AS IS" WITHOUT ANY REPRESENTATION OR WARRANTY, EXPRESS OR IMPLIED, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, NONINFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS, OR ARISING FROM THE COURSE OF DEALING BETWEEN THE PARTIES OR USAGE OF TRADE. IN NO EVENT SHALL 3DFX BE LIABLE FOR ANY DAMAGES WHATSOEVER INCLUDING, WITHOUT LIMITATION, DIRECT OR INDIRECT DAMAGES, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE SPECIFICATIONS, EVEN IF 3DFX HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

[You're getting it for free. We believe the information provided to be accurate. Beyond that, you're on your own.]

| COF  | PYRIGHT NOTICE:                                                                  | 2  |

|------|----------------------------------------------------------------------------------|----|

| No V | Warranty                                                                         | 2  |

| 1.   | INTRODUCTION                                                                     | 5  |

| 1.1  | System Diagram                                                                   | 5  |

| 1.2  | System Features                                                                  |    |

| 1.3  | SYSTEM RESOLUTIONS                                                               |    |

| 1.4  | System Performance                                                               |    |

| 2.   | MEMORY MAP                                                                       | 10 |

| 3.   | COMMAND FIFO                                                                     | 11 |

| 4.   | 3D REGISTERS                                                                     | 13 |

| 5.   | TEXTURE MEMORY                                                                   | 14 |

| 6.   | RENDER AND REFRESH                                                               | 15 |

| 7.   | 3D REGISTER MAP                                                                  | 19 |

| 8.   | REGISTER DEFINITIONS                                                             | 23 |

| 8.1  | STATUS REGISTER                                                                  | 23 |

| 8.2  | VERTEX AND FVERTEX REGISTERS                                                     | 24 |

| 8.3  | STARTR, STARTG, STARTB, STARTA, FSTARTR, FSTARTG, FSTARTB, AND FSTARTA REGISTERS | 24 |

| 8.4  | STARTZ AND FSTARTZ REGISTERS                                                     |    |

| 8.5  | STARTS, STARTT, FSTARTS, AND FSTARTT REGISTERS                                   | 25 |

| 8.6  | STARTW AND FSTARTW REGISTERS                                                     |    |

| 8.7  | DRDX, DGDX, DBDX, DADX, FDRDX, FDGDX, FDBDX, AND FDADX REGISTERS                 | 26 |

| 8.8  | DZDX AND FDZDX REGISTERS                                                         |    |

| 8.9  | DSDX, DTDX, FDSDX, AND FDTDX REGISTERS                                           | 26 |

| 8.10 |                                                                                  |    |

| 8.11 | DRDY, DGDY, DBDY, DADY, FDRDY, FDGDY, FDBDY, AND FDADY REGISTERS                 |    |

| 8.12 |                                                                                  |    |

| 8.13 |                                                                                  |    |

| 8.14 |                                                                                  |    |

| 8.15 | TRIANGLECMD AND FTRIANGLECMD REGISTERS                                           | 29 |

| 8.16 | NOPCMD REGISTER                                                                  | 29 |

| 8.17 | FASTFILLCMD REGISTER                                                             | 29 |

| 8.18 | SWAPBUFFERCMD REGISTER                                                           | 30 |

| 8.19 | SWAPPENDCMD REGISTER                                                             | 30 |

| 8.20 | fbzColorPath Register                                                            | 32 |

| 8.21 |                                                                                  |    |

| 8.22 |                                                                                  |    |

| 8.23 |                                                                                  |    |

| 8.24 |                                                                                  | 46 |

| 8.25 |                                                                                  |    |

| 8.26 | color1 Register                                                                  | 46 |

| 8.27 | FOGCOLOR REGISTER                                                                   | 46 |

|------|-------------------------------------------------------------------------------------|----|

| 8.28 | ZACOLOR REGISTER                                                                    | 46 |

| 8.29 | CHROMAKEY REGISTER                                                                  | 48 |

| 8.30 | CHROMARANGE REGISTER                                                                | 48 |

| 8.31 | COLBUFFERSETUP AND AUXBUFFERSETUP REGISTERS                                         | 49 |

| 8.32 | CLIPLEFTRIGHTO, CLIPTOPBOTTOMO, CLIPLEFTRIGHT1 AND CLIPTOPBOTTOM1 REGISTERS         | 50 |

| 8.33 | FOGTABLE REGISTER                                                                   | 51 |

| 8.34 | FBIJRINITO, FBIJRINIT1, FBIJRINIT2, FBIJRINIT3, FBIJRINIT4 AND FBIJRINIT5 REGISTERS | 52 |

| 8.35 | FBIJR VERSION REGISTER                                                              | 56 |

| 8.36 | FBIPIXELSIN REGISTER                                                                | 56 |

| 8.37 | FBICHROMAFAIL REGISTER                                                              | 56 |

| 8.38 | FBIZFUNCFAIL REGISTER                                                               | 56 |

| 8.39 | FBIAFUNCFAIL REGISTER                                                               | 57 |

| 8.40 | FBIPIXELSOUT REGISTER                                                               | 57 |

| 8.41 | TEXCHIPSEL REGISTER                                                                 | 57 |

| 8.42 | TEXTUREMODE REGISTER                                                                | 58 |

| 8.43 | TLOD REGISTER                                                                       | 60 |

| 8.44 | TDETAIL REGISTER                                                                    | 62 |

| 8.45 | TEXBASEADDR, TEXBASEADDR1, TEXBASEADDR2, AND TEXBASEADDR38 REGISTERS                | 62 |

| 8.46 | TREXINITO REGISTER                                                                  | 63 |

| 8.47 | TREXINIT1 REGISTER                                                                  | 63 |

| 8.48 | NCCTABLEO AND NCCTABLEO REGISTERS                                                   | 63 |

| 9.   | CHANGES FROM SST-1                                                                  | 65 |

| 10.  | REVISION HISTORY                                                                    | 66 |

# 1. Introduction

The SST-96 graphics subsystem combines the high performance graphics of 3Dfx Interactive (3D) with the proven performance of an industry standard windows accelerator (2D). This union creates an extremely cost effective and uncompromising multimedia solution. The 2D engine provides a PCI system interface, VGA, 2D and Video features and the 3D engine adds windowed 3Dfx "**Voodoo Graphics**".

SST-96 connects the 2D and 3D graphics engines through the "Voodoo Rush" (VR) interface. The VR interface consist of a shared frame buffer memory interface and a 3D control interface. The shared frame buffer interface defines a Pseudo Unified Memory Architecture (PUMA) which connects the 2D/3D devices through the pins of the frame buffer memory and the 3D control interface defines signals which coordinate efficient 2D/3D operation.

The SST-96 PUMA interface supports shared access to the frame buffer memory through a request and grant arbitration protocol based on VUMA (VESA Unified Memory Arbitration). PUMA defines the 2D device as the requester and the 3D device as the grantor. As the requester, the 2D device may generate low priority requests for general frame buffer accesses and high priority requests for video/memory refresh accesses.

The SST-96 3D control interface provides for an efficient 2D/3D operation through swap, vsync and status connections. The swap/vsync connections provide for a polling-free 3D-render/2D-refresh buffer swap mechanism and the status connection provides 3D status to the PCI though the 2D chip.

# 1.1 System Diagram

Error! Not a valid link.

## 1.2 System Features

#### **Interface**

- Low-cost industry-standard 2D/VGA Windows Accelerator.

- High performance "Voodoo Graphics" quality 3Dfx Accelerator.

- Minimum interface overhead:

- 3-pin Pseudo Unified Memory Architecture (REQ, GNT & CLK),

- 2-Pin buffer management (SWAP & VSYNC),

- 1-Pin system status (STATUS).

#### **2D**

- PUMA client interface.

- 2 or 4 MB linearly mapped frame buffer memory

- VGA compliance.

- BLTs & ROPs.

- Draw & fill.

- Scrolling, clipping & scaling.

- Video In & Video Out.

- Optional MPEG attachment.

- Video refresh.

- DRAM refresh.

#### **3D**

- PUMA core interface.

- 1 to 4 MB of texture memory.

- Triangle raster engine with sub-pixel correction to .4 x .4 resolution.

- Linearly interpolated Gouraud-shaded rendering.

- Perspective-corrected texture-mapped rendering with iterated RGB modulation/addition.

- Texture filtering: point-sampling, bilinear, and tri-linear filtering with mip-mapping.

- Texture formats: 8-bit RGB(3-3-2), 8-bit intensity, 8-bit alpha, 8-bit narrow channel YIQ(4-2-2), 8-bit alpha-intensity(4-4), 16-bit RGB(5-6-5), 16-bit ARGB (1-5-5-5), 16-bit ARGB (4-4-4-4), 16-bit ARGB (8-3-3-2), 16-bit narrow channel AYIQ (8-4-2-2), 16-bit alpha-intensity (8-8).

- Texture decompression: 8-bit "narrow channel" YIQ.

- Transparency with dedicated color mask.

- Source/Destination pixel alpha blending.

- Linearly interpolated 16-bit Z-buffer rendering.

- Perspective-corrected 16-bit floating point W-buffer rendering.

- 24-bit color dithering to native 16-bit RGB buffer using 4x4 or 2x2 ordered dither matrix.

- Non-linear table driven fog.

# 1.3 System Resolutions

SST-96 supports any resolution which fits in the frame buffer memory, is less than 2K by 2K in X/Y rendering dimension and is supported by the refresh engine of the 2D chip. Full-screen 3D requires the memory space of the front/back 3D buffers, while windowed 3D requires the additional memory space of the 2D desktop. Windowed 3D overlays 3D data onto the desktop from off-screen buffers utilizing either two off-screen buffers (out-of-place 3D) or one on-screen buffer and one off-screen buffer (in-place 3D -- requires equal 2D and 3D color depths).

The following tables detail the memory byte requirements for full-Screen and windowed resolutions. Numbers indicated in light gray require a 4MB frame buffer and numbers indicated in dark gray do not fit within SST-96.

# Full Screen 3D

| 3D                   | 3D Color | Auxiliary | Color    | Color    | Auxiliary | Total      | CMDFIFO   |

|----------------------|----------|-----------|----------|----------|-----------|------------|-----------|

| Resolution           | Depth    | Depth     | Buffer 1 | Buffer 2 | Buffer    | of Buffers | Space     |

| 16-bit Full Screen 3 |          | Вериг     | Bullet 1 | Burier 2 | Burrer    | of Bullets | Брасс     |

| 640x480              | 16       | 0         | 614400   | 614400   | 0         | 1228800    | 868352    |

| 0.10%.100            | 16       | 8         | 614400   | 614400   | 307200    | 1536000    | 561152    |

|                      | 16       | 16        | 614400   | 614400   | 614400    | 1843200    | 253952    |

| 800x600              | 16       | 0         | 960000   | 960000   | 0         | 1920000    | 177152    |

|                      | 16       | 8         | 960000   | 960000   | 480000    | 2400000    | 1794304   |

|                      | 16       | 16        | 960000   | 960000   | 960000    | 2880000    | 1314304   |

| 1024x768             | 16       | 0         | 1572864  | 1572864  | 0         | 3145728    | 1048576   |

|                      | 16       | 8         | 1572864  | 1572864  | 786432    | 3932160    | 262144    |

|                      | 16       | 16        | 1572864  | 1572864  | 1572864   | 4718592    | (524288)  |

| 1152x864             | 16       | 0         | 1990656  | 1990656  | 0         | 3981312    | 212992    |

|                      | 16       | 8         | 1990656  | 1990656  | 995328    | 4976640    | (782336)  |

|                      | 16       | 16        | 1990656  | 1990656  | 1990656   | 5971968    | (1777664) |

| 1280x1024            | 16       | 0         | 2621440  | 2621440  | 0         | 5242880    | (1048576) |

|                      | 16       | 8         | 2621440  | 2621440  | 1310720   | 6553600    | (2359296) |

|                      | 16       | 16        | 2621440  | 2621440  | 2621440   | 7864320    | (3670016) |

| 1600x1200            | 16       | 0         | 3840000  | 3840000  | 0         | 7680000    | (3485696) |

|                      | 16       | 8         | 3840000  | 3840000  | 1920000   | 9600000    | (5405696) |

|                      | 16       | 16        | 3840000  | 3840000  | 3840000   | 11520000   | (7325696) |

| 8-bit Full Screen 3D | )        |           |          |          |           |            |           |

| 640x480              | 8        | 0         | 307200   | 307200   | 0         | 614400     | 1482752   |

|                      | 8        | 8         | 307200   | 307200   | 307200    | 921600     | 1175552   |

|                      | 8        | 16        | 307200   | 307200   | 614400    | 1228800    | 868352    |

| 800x600              | 8        | 0         | 480000   | 480000   | 0         | 960000     | 1137152   |

|                      | 8        | 8         | 480000   | 480000   | 480000    | 1440000    | 657152    |

|                      | 8        | 16        | 480000   | 480000   | 960000    | 1920000    | 177152    |

| 1024x768             | 8        | 0         | 786432   | 786432   | 0         | 1572864    | 524288    |

|                      | 8        | 8         | 786432   | 786432   | 786432    | 2359296    | 1835008   |

|                      | 8        | 16        | 786432   | 786432   | 1572864   | 3145728    | 1048576   |

| 1152x864             | 8        | 0         | 995328   | 995328   | 0         | 1990656    | 106496    |

|                      | 8        | 8         | 995328   | 995328   | 995328    | 2985984    | 1208320   |

|                      | 8        | 16        | 995328   | 995328   | 1990656   | 3981312    | 212992    |

| 1280x1024            | 8        | 0         | 1310720  | 1310720  | 0         | 2621440    | 1572864   |

|                      | 8        | 8         | 1310720  | 1310720  | 1310720   | 3932160    | 262144    |

|                      | 8        | 16        | 1310720  | 1310720  | 2621440   | 5242880    | (1048576) |

| 1600x1200            | 8        | 0         | 1920000  | 1920000  | 0         | 3840000    | 354304    |

|                      | 8        | 8         | 1920000  | 1920000  | 1920000   | 5760000    | (1565696) |

|                      | 8        | 16        | 1920000  | 1920000  | 3840000   | 7680000    | (3485696) |

| 2D & 3D             | 3D Color          | Auxiliary          | Color             | Color              | Auxiliary    | Total      | CMDFIFO       |

|---------------------|-------------------|--------------------|-------------------|--------------------|--------------|------------|---------------|

| Resolution          | Depth             | Depth              | Buffer 1          | Buffer 2           | Buffer       | of Buffers | Space         |

| 8-bit Desktop and 1 |                   |                    | o off-screen 3D b | ouffers)           |              |            | •             |

| 1024x768            | 0                 | 0                  | 0                 | 0                  | 0            | 786432     | na            |

| 640x480             | 16                | 0                  | 614400            | 614400             | 0            | 2105232    | 81920         |

| 0407400             | 16                | 8                  | 614400            | 614400             | 307200       | 2322432    | 1871872       |

|                     | 16                | 16                 | 614400            | 614400             | 614400       | 2629632    | 1564672       |

| 1152x864            | 0                 | 0                  | 0                 | 0                  | 014400       | 995328     | na            |

| 640x480             | 16                | 0                  | 614400            | 614400             | 0            | 2224128    | 1970176       |

| 0408460             | 16                | 8                  | 614400            | 614400             | 307200       | 2531328    | 1662976       |

|                     | 16                | 16                 | 614400            | 614400             | 614400       | 2838528    | 1355776       |

| 1280x1024           | 0                 | 0                  | 0                 | 0                  | 0            | 1310720    |               |

| 640x480             | 16                | 0                  | 614400            | 614400             | 0            | 2539520    | na<br>1571168 |

| 040x480             |                   | 8                  | 614400            | 614400             | 307200       | 2846720    | 1263968       |

|                     | 16                | 8<br>16            |                   |                    | 614400       | 3153920    |               |

| 1600 1200           | 16                |                    | 614400            | 614400             |              |            | 956768        |

| 1600x1200           | 0                 | 0                  | 0                 | 0                  | 0            | 192000     | na            |

| 640x480             | 16                | 0                  | 614400            | 614400             | 0            | 3148800    | 1045504       |

|                     | 16                | 8                  | 614400            | 614400             | 307200       | 3456000    | 736403        |

|                     | 16                | 16                 | 614400            | 614400             | 614400       | 3763200    | 431104        |

| 16-bit Desktop and  | 16-bit 640x480 Ii | n-Place 3D (one o  | n-screen 3D buffe | er & one off-scree | n 3D buffer) |            |               |

| 1024x768            | 0                 | 0                  | 0                 | 0                  | 0            | 1572864    | na            |

| 640x480             | 16                | 0                  | 0                 | 614400             | 0            | 2187264    | 2007040       |

|                     | 16                | 8                  | 0                 | 614400             | 307200       | 2492264    | 1702040       |

|                     | 16                | 16                 | 0                 | 614400             | 614400       | 2799464    | 1394840       |

| 1152x864            | 0                 | 0                  | 0                 | 0                  | 0            | 1990656    | na            |

| 640x480             | 16                | 0                  | 0                 | 614400             | 0            | 2605056    | 1896448       |

|                     | 16                | 8                  | 0                 | 614400             | 307200       | 2912256    | 1282048       |

|                     | 16                | 16                 | 0                 | 614400             | 614400       | 3219456    | 974848        |

| 1280x1024           | 0                 | 0                  | 0                 | 0                  | 0            | 2621440    | na            |

| 640x480             | 16                | 0                  | 0                 | 614400             | 0            | 3235840    | 958464        |

|                     | 16                | 8                  | 0                 | 614400             | 307200       | 3543040    | 651264        |

|                     | 16                | 16                 | 0                 | 614400             | 614400       | 3850240    | 344064        |

| 8-bit Desktop and 1 | 6-bit 320x200 Οι  | it-of-Place 3D (tw | o off-screen 3D b | ouffers)           |              |            |               |

| 1024x768            | 0                 | 0                  | 0                 | 0                  | 0            | 786432     | na            |

| 320x200             | 16                | 0                  | 128000            | 128000             | 0            | 1042432    | 1054720       |

|                     | 16                | 8                  | 128000            | 128000             | 64000        | 1106432    | 990720        |

|                     | 16                | 16                 | 12800             | 128000             | 128000       | 1170432    | 926720        |

| 1152x864            | 0                 | 0                  | 0                 | 0                  | 0            | 995328     | na            |

| 320x200             | 16                | 0                  | 128000            | 128000             | 0            | 1251328    | 845824        |

|                     | 16                | 8                  | 128000            | 128000             | 64000        | 1315328    | 781824        |

|                     | 16                | 16                 | 128000            | 128000             | 128000       | 1379328    | 717824        |

| 1280x1024           | 0                 | 0                  | 0                 | 0                  | 0            | 1310720    | na            |

| 320x200             | 16                | 0                  | 128000            | 128000             | 0            | 1566720    | 530432        |

| 520A200             | 16                | 8                  | 128000            | 128000             | 64000        | 1630720    | 466432        |

|                     | 16                | 16                 | 128000            | 128000             | 128000       | 1694720    | 402432        |

| 1600x1200           | 0                 | 0                  | 0                 | 0                  | 0            | 1920000    | na            |

| 320x200             | 16                | 0                  | 128000            | 128000             | 0            | 2176000    | 2018304       |

| 3208200             | 16                | 8                  | 128000            | 128000             | 64000        | 2240000    | 1954304       |

|                     | 16                | 16                 | 128000            | 128000             | 128000       | 2304000    | 1890304       |

|                     | 10                | 10                 | 120000            | 120000             | 120000       | 2304000    | 1090304       |

# 1.4 System Performance

The performance of SST-96 approximates the performance of SST-1. However, modification to the memory architecture resulting from the 2D engine partnership alter the command and rendering interfaces with a slight degradation in performance. Changes come from the additional command traffic across the PUMA frame buffer interface and modifications to the frame buffer memory packing and tiling organizations.

The following table estimates the performance of SST-1 and SST-96 from an architectural simulator. The numbers represent systems rendering depth checked color and no alpha blend at 50MHz system. The simulator assumptions include a never-idle triangle engine (best-case) and full triangle parameter delivery (120 bytes) for each triangle (worst-case) and 15% overhead for memory/display refresh. Additional assumptions include, an efficient command transport from the 2D device (8x64 bits in 11 cycles) and an efficient UMA arbitration overhead (1 dead cycle).

| Pixels Per Triangle / 12 CZ Rendering Ktris/Mpix |     | _  | 2<br>Ktris/l | 4<br>Mpixs | 49 112<br>Ktris/Mpixs Ktris/Mpixs |    |     | ., 112   200 |     |    | 511<br>Ktris/Mpixs |    |

|--------------------------------------------------|-----|----|--------------|------------|-----------------------------------|----|-----|--------------|-----|----|--------------------|----|

| SST-1 (direct)                                   | 996 | 12 | 894          | 21         | 533                               | 26 | 266 | 29           | 158 | 31 | 65                 | 33 |

| SST-1 (memory fifo)                              | 626 | 7  | 501          | 12         | 359                               | 17 | 214 | 24           | 138 | 27 | 62                 | 31 |

| SST-96 (memory fifo)                             | 511 | 6  | 414          | 10         | 293                               | 14 | 179 | 20           | 119 | 23 | 56                 | 28 |

| Pixels Per Triangle /<br>Rendering Mode | Ktri | 0<br>/Mpi<br>ĸ | Ktri | .5<br>/Mpi<br>x | Ktri | 0<br>/Mpi<br>ĸ | Ktri | 00<br>/Mpi<br>x | Ktri | 00<br>/Mpi<br>x | Ktri | 00<br>/Mpi<br>ĸ |   | 000<br>Mpix |

|-----------------------------------------|------|----------------|------|-----------------|------|----------------|------|-----------------|------|-----------------|------|-----------------|---|-------------|

| C - color only                          | 787  | 7              | 694  | 17              | 586  | 29             | 409  | 40              | 83   | 41              | 41   | 41              | 8 | 41          |

| CA - color & blend                      | 580  | 5              | 466  | 11              | 339  | 16             | 232  | 23              | 70   | 35              | 39   | 39              | 8 | 41          |

| CZ - color & depth                      | 557  | 5              | 439  | 10              | 307  | 15             | 204  | 20              | 58   | 29              | 31   | 31              | 6 | 34          |

| CAZ - blend & depth                     | 444  | 4              | 335  | 8               | 335  | 11             | 143  | 14              | 38   | 19              | 21   | 21              | 4 | 22          |

The SST-96 performance loss at the rendering interface is a result of changes to the packing and tiling organization of pixels within frame buffer memory. SST-96 packs pixel quads of color or depth onto separate mapped memory pages while SST-1 packs pixel pairs of color and depth within a memory word. Additionally, SST-96 tiles pixels of color/depth onto linear strides of memory while SST-1 tiles pixels of color/depth onto rectangular strides of memory. These memory organization differences result in less access efficiency for small polygons in, more page miss penalties for small polygons and more page misses between color/depth accesses.

| pixels/triangle | 12  | 24  | 49  | 112 | 200 | 511 |

|-----------------|-----|-----|-----|-----|-----|-----|

| KT Packing Loss | 37% | 24% | 17% | 11% | 9%  | 4%  |

| KT Tiling Loss  | 23% | 19% | 17% | 15% | 12% | 6%  |

# 2. Memory Map

SST-96 requires 4 or 8 Mbytes of PCI address space. The 8MB space consists of a 4 MB region for the frame buffer, a 2 MB region for the 3D control registers and a 2 MB region for the 3D texture memory. Alternatively, a 4MB space consists of a 2 MB region for the frame buffer, a 1 MB region for the 3D control registers and a 1 MB region for the 3D texture memory. The following table defines the ordering of these regions within the space of SST-96.

## **Address Table**

| Address           | Description                       |

|-------------------|-----------------------------------|

| 0x000000-0x3fffff | SST-96 frame buffer memory (4 MB) |

| 0x400000-0x5fffff | SST-96 3D control register (2 MB) |

| 0x600000-0x7fffff | SST-96 3D texture memory (2 MB)   |

| <or></or>         |                                   |

| 0x000000-0x1fffff | SST-96 frame buffer memory (2 MB) |

| 0x200000-0x2fffff | SST-96 3D control register (1 MB) |

| 0x300000-0x3fffff | SST-96 3D texture memory (1 MB)   |

The three regions of the PCI address space define the shared frame buffer memory space of the PUMA interface. Accesses across this interface are performed as EDO DRAM read or write operations. As a result, SST-96 provides page mapped read access of the 3D control registers but does not provide read access of texture memory.

The following three tables describe the address maps supported by SST-96. The first map is the preferred map of SST-96, however, the second and third maps may be configured through external control on the 3D device. For each configuration, the address map indicates the PUMA memory signals associated with the PUMA address space.

## 8MB Address Map

| PUMA    | DRAM       | DATA[  | [63:0]                                                                   |

|---------|------------|--------|--------------------------------------------------------------------------|

| Signals |            | CAS[7: | [0] (byte enables)                                                       |

| RAS0    | WE0<br>OE0 | 2MB    | Frame Buffer Dram Linear read/write access, rendering and refresh.       |

|         | WE1<br>OE1 | 2MB    |                                                                          |

| RAS1    | WE0<br>OE0 | 2MB    | 3D Registers Double word aligned write access. Page aligned read access. |

|         | WE1<br>OE1 | 2MB    | 3D Texture Memory Write Only.                                            |

# 3. Command FIFO

A 3D control command FIFO (CMDFIFO) may be established by software within the DRAM of the frame buffer memory. Initialization registers of FBIjr define the CMDFIFO as a circular space of 1 to 512 4KB pages. Once established, software loads commands into the FIFO through linear frame buffer writes and the 3D engine seeks commands out of the FIFO through the PUMA interface.

Software must write the CMDFIFO through consecutive 32-bit LFB addresses filling full 64-bit quad words.

## **FIFO Management**

Hardware manages the CMDFIFO emptiness. The 3D engine maintains a read pointer and an entries count for the CMDFIFO. Writes to the CMDFIFO increment the entries count and reads from the CMDFIFO decrement the entries count while incrementing the read pointer. Then, as the entry count is greater than zero, the 3D engine arbitrates for PUMA access and reads from the CMDFIFO.

Software manages CMDFIFO fullness. To assist, hardware provides read access of the CMDFIFO entries count and a fullness status. From the entries count and knowledge of the CMDFIFO size, software may determine the exact fullness. Alternatively, the status registers within the 2D and 3D chips indicate a fullness measurement based on the comparison to a programmable fullness count. Software is encouraged to manage fullness through read of the 2D serial status as access to the 2D chip does not tax the frame buffer bandwidth.

# **FIFO Data**

The CMDFIFO data controls the 3D engine through non-grouped and grouped write packets. Each packet type contains an even number of 32-bit 8-byte aligned data words which command write operations to PUMA 4-byte word addresses. Non-grouped write packets modify a single address with a single 32-bit data word and grouped-write packets modify up to 32 addresses with as many pieces of 32-bit data words.

The non-grouped write packet consists of an address in the lower word and data in the upper word. Similarly, the grouped write packet begins with an address in the lower double-word but follows the address with a mask control word and up to 32 32-bit data words.

The address of the grouped write format sets the base address of the write and the mask determines the sequence and volume of data to be written. From LSB to MSB of the mask, a "1" enables the write and a "0" disables the write. The sequence of 32-bit data words following the address and mask modify addresses equaling the base address plus N when the mask bit N equals "1" as N goes from 0 to 31.

#### **Non-grouped Write Packet**

• 2 64-bit aligned 32-bit words.

| 63                              | 32 | 31 |           | 0                                |

|---------------------------------|----|----|-----------|----------------------------------|

| Data[31:0] (written to Address) |    | 0  | rsvd[9:0] | Address[20:0]                    |

|                                 |    |    |           | (PCI address [22:2] of register) |

Example: write to triangleCMD register.

| 63 32                                 | 31 |            | 0         |

|---------------------------------------|----|------------|-----------|

| <trianglecmd_data></trianglecmd_data> | 0  | 0000000000 | 0x10_0020 |

Writes PUMA address = 0x10 0020 with data = <triangleCMD data>

• 2 to 34 even numbered 32-bit words.

| 63 32                                                              | 31    |                    |                                        | 0 |

|--------------------------------------------------------------------|-------|--------------------|----------------------------------------|---|

| Mask[31:0] (Mask[N]=1 enables write to BaseAddress+N)              | 1     | rsvd[9:0]          | BaseAddress[20:0]                      |   |

|                                                                    |       |                    | (PCI address [22:2] of first register) |   |

| 32-bit data words equaling the count of Mask[N]=1 as N goes from 0 | to 31 | (0 to 31 32-bit da | ata words)                             |   |

Example: set triangle vertex, RGBW start, dX and dY parameters, and triangleCMD registers (19 registers).

| 63 32                                     | 2 31 |                                       | 0                               |  |

|-------------------------------------------|------|---------------------------------------|---------------------------------|--|

| 0x3803_ffff                               | 1    | 0000000000                            | 0x10_0002                       |  |

| <vertexay_data></vertexay_data>           |      |                                       | <vertexax_data></vertexax_data> |  |

| <vertexby_data></vertexby_data>           |      |                                       | <vertexbx_data></vertexbx_data> |  |

| <vertexcy_data></vertexcy_data>           |      |                                       | <vertexcx_data></vertexcx_data> |  |

| <drdx_data></drdx_data>                   |      |                                       | <startr_data></startr_data>     |  |

| <startg_data></startg_data>               |      |                                       | <drdy_data></drdy_data>         |  |

| <dgdy_data></dgdy_data>                   |      |                                       | <dgdx_data></dgdx_data>         |  |

| <dbdx_data></dbdx_data>                   |      |                                       | <startb_data></startb_data>     |  |

| <startw_data></startw_data>               |      |                                       | <dbdy_data></dbdy_data>         |  |

| <dwdy_data></dwdy_data>                   |      |                                       | <dwdx_data></dwdx_data>         |  |

| 0xXXXX_XXXX (filler data must be written) |      | <trianglecmd_data></trianglecmd_data> |                                 |  |

- 1. Writes PUMA address = 0x10\_0002 with data = <vertexAx\_data>

- 2. Writes PUMA address = 0x10\_0003 with data = <vertexAy\_data>

- 3. Writes PUMA address =  $0x10\_0004$  with data =  $\langle vertexBx\_data \rangle$

- 4. Writes PUMA address = 0x10\_0005 with data = <vertexBy\_data>

- 5. Writes PUMA address = 0x10\_0006 with data = <vertexCx\_data>

- 6. Writes PUMA address =  $0x10\_0007$  with data =  $\langle vertexCy\_data \rangle$

- 7. Writes PUMA address =  $0x10\_0008$  with data =  $\langle startR\_data \rangle$

- 8. Writes PUMA address =  $0x10\_0009$  with data =  $<dRdX\_data>$

- 9. Writes PUMA address =  $0x10_000a$  with data =  $<dRdY_data>$

- 10. Writes PUMA address =  $0x10\_000b$  with data =  $\langle startG\_data \rangle$

- 11. Writes PUMA address =  $0x10\_000c$  with data =  $<dGdX\_data>$

- 12. Writes PUMA address =  $0x10\_000d$  with data =  $< dGdY\_data >$

- 13. Writes PUMA address = 0x10\_000e with data = <startB\_data>

- 14. Writes PUMA address =  $0x10\_000f$  with data =  $<dBdX\_data>$

- 15. Writes PUMA address =  $0x10\_0010$  with data =  $<dBdY\_data>$

- 16. Writes PUMA address = 0x10\_001d with data = <startW\_data>

- 17. Writes PUMA address =  $0x10\_001e$  with data =  $<dWdX\_data>$

- 18. Writes PUMA address =  $0x10\_001f$  with data =  $<dWdY\_data>$

- 19. Writes PUMA address =  $0x10\_0020$  with data =  $\langle trangleCMD\_data \rangle$

# 4. 3D Registers

SST-96 defines 256 3D control registers mapped onto 1MB of the PUMA address space. Within this space, write addresses pack the registers within the first DRAM page and read addresses spread the registers onto separate DRAM pages. This arrangement allows for efficient bursts when writing registers and DRAM emulation when reading registers. The following table defines the address sub-fields mapping the registers for read and write access.

| Type    |       | PCI Address 19:0 (1MB) |       |          |      |  |  |  |  |

|---------|-------|------------------------|-------|----------|------|--|--|--|--|

| write   | 19:16 | 15:12                  | 11:10 | 9:2      | 1:0  |  |  |  |  |

| address | chip  | wrap                   | 00    | register | byte |  |  |  |  |

| read    | 1     | 9:12                   |       | 11:2     | 1:0  |  |  |  |  |

| address | re    | gister                 |       | X        | byte |  |  |  |  |

The **register** field selects 1 of 256 3D registers defined by the register table of the 3D registers map section.

The **chip** field selects one or more of the SST-96 3D chips (FBI, TREX0, TREX1 or TREX2) to be accessed. Each bit in this field selects a chip for writing. The LSB selects the FBI and the higher order bits select the higher order TREX chips. The value of "0000" also selects all chips. Software controls write data presented to the individual chips through this field. Reads ignore this field as data is always read from FBI. The following table defines the mapping of this field:

| Chip Field | SST-96 Chip Selected |       |       |     |  |  |  |  |  |

|------------|----------------------|-------|-------|-----|--|--|--|--|--|

| chip[3:0]  | TREX2                | TREX1 | TREX0 | FBI |  |  |  |  |  |

| 0000       | Yes                  | Yes   | Yes   | Yes |  |  |  |  |  |

| 0001       | No                   | No    | No    | Yes |  |  |  |  |  |

| 0010       | No                   | No    | Yes   | No  |  |  |  |  |  |

| 0011       | No                   | No    | Yes   | Yes |  |  |  |  |  |

| 0100       | No                   | Yes   | No    | No  |  |  |  |  |  |

| 0101       | No                   | Yes   | No    | Yes |  |  |  |  |  |

| 0110       | No                   | Yes   | Yes   | No  |  |  |  |  |  |

| 0111       | No                   | Yes   | Yes   | Yes |  |  |  |  |  |

| 1000       | Yes                  | No    | No    | No  |  |  |  |  |  |

| 1001       | Yes                  | No    | No    | Yes |  |  |  |  |  |

| 1010       | Yes                  | No    | Yes   | No  |  |  |  |  |  |

| 1011       | Yes                  | No    | Yes   | Yes |  |  |  |  |  |

| 1100       | Yes                  | Yes   | No    | No  |  |  |  |  |  |

| 1101       | Yes                  | Yes   | No    | Yes |  |  |  |  |  |

| 1110       | Yes                  | Yes   | Yes   | No  |  |  |  |  |  |

| 1111       | Yes                  | Yes   | Yes   | Yes |  |  |  |  |  |

The **wrap** field aliases the memory mapped registers to 16 locations. This field allows software to avoid write compression within processors such as the Digital Alpha AXP and the Pentium Pro. These processors contain large write-buffers that collapse multiple writes to the same address.

The **byte** field defines the byte alignment of the register access. This field must be 0x0 for all register accesses. Register accesses are restricted to 4-byte word aligned 32-bit accesses. No byte (8-bit) or half word (16-bit) accesses are allowed. To modify individual bits of a 32-bit register, the entire 32-bit word must be written with valid bits in all positions.

# 5. Texture Memory

SST-96 defines 2MB of PUMA address space for loading texture memory. Through this space, software may load from 1 to 8 MB of texture memory. Software loads texture memory by setting up the texture write before writing the texture through the PUMA interface. Software sets the texture base address register and various other texture control registers which define the texture packing scheme. Then, software writes the S and T data for each LOD of the texture.

The 21-bit PUMA address of the 2MB PUMA texture space defines the LOD, S and T of the texture through the mapping defined in the following table (S[1] is set to 0 for 8-bit textures).

| PCI Address[20:0] | 20 17    | 16 9   | 8 2    | 1 0 |

|-------------------|----------|--------|--------|-----|

| Texture Fields    | LOD[3:0] | T[7:0] | S[7:1] | 00  |

The 32-bit PUMA data word defines the data of the LSBs of S, for 16-bit and 8-bit textures, through the mapping defined in the following table.

| PCI Data[31:0] | 31 2      | 4 23   | 16        | 15 8      | 7 0       |  |

|----------------|-----------|--------|-----------|-----------|-----------|--|

| 16-bit Texture |           | S[0]=1 |           | S[0]=0    |           |  |

| 8-bit Texture  | S[1:0]=11 |        | S[1:0]=10 | S[1:0]=01 | S[1:0]=00 |  |

Texture loads of LODs smaller than the extent of S and T ignore the unused MSBs of S and T within the PUMA address and data. The write of a single texel wide 16-bit texture inhibits the write to the upper two bytes of data. The write of a double texel wide 8-bit texel inhibits the write to the upper two bytes of data. Additionally, the write of a single texel wide 8-bit texel inhibits the write to the upper three bytes of data.

The following TREX registers, defining the data packing of the texture, must be set prior to writing a texture.

**texBaseAddr** - These registers determine the 8 byte aligned base address of the texture within the 1-8MB space of texture memory. Addressing from the base address assumes that the texture uses all LOD levels. LOD0 is stored first and each of the higher numbered LODs are stored contiguously after.

**texureMode.tformat** - This register field defines the format of the texels. From the standpoint of texture load, this register defines the volume of bytes per texel.

**tLOD.lod\_split** - This register field defines split textures. Split textures load only the relevant even or odd textures as defined by the **tLOD.lod\_odd** register field.

**tLOD.lod\_aspect** - This register field defines the  $2^{**}N$  aspect ratio of the texture. Valid values range from 0b00 to 0b11. These values set the following aspect ratios: 00=1to1, 01=2to1, 10=4to1 & 11=8to1.

Efficient packing of textures, with a minimum LOD number greater than 0, requires software mapping of the base address which assumes the low numbered LODs are written. Software must set the base address below the intended write address to account for the space of the unused LODs. The space of an LOD can be determined from the bytes/texel, texels/LOD and LODs/texture (small LODs consume a minimum of 4 bytes (2-3 unused bytes)).

# 6. Render and Refresh

The SST-96 architecture presents two synchronization issues resulting from the PUMA connection and the shared duties of the 2D and 3D chips. One problem occurs as order-of-evaluation may be lost when the 2D and 3D engines simultaneously render into the memory of the PUMA interface and a second problem occurs as the 2D engine performs display refresh of images rendered by the 2D and 3D engines.

## **RENDER**

Command ordering may become problematic as 3D commands are tossed across the PUMA interface to the 3D device. Within the SST-96 architecture, 2D accesses may over step 3D activities and 3D direct accesses may over step 3D CMD FIFO activities. To ensure proper order of evaluation, software must coordinate these activities through polling for 3D engine idleness and 3D command FIFO emptiness. 3D direct accesses must poll for 3D CMD FIFO emptiness and 2D accesses (BLTs, LFBs & ROPs) must additionally poll for 3D CMD FIFO emptiness.

# **Windowed Rendering**

All rendering, clipping and fast-fill activities of the 3D engine are in window relative coordinates. The hardware translates window relative X and Y drawing coordinates to Linear Frame Buffer (LFB) addresses through the **colBufferSetup** and **AuxBufferSetup** registers.

The color and auxiliary buffer setup registers define separate base address and X stride values for each of the buffers. The base address field defines the LFB base address of the buffer and the X stride field defines the number of pixels between rows of the 3D data. The X strides are restricted to strides which is evenly divisible by 4 pixels and the base addresses must be set with the same quad pixel alignment between the color and auxiliary buffers.

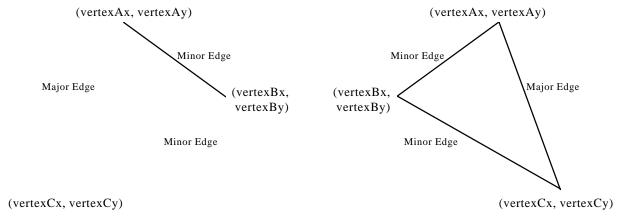

Determination of the LFB address depends on the state of the Y-flip mode (**fbzMode**[17]). For the non-flipped case, X stride is added to the base address for each window Y address and, for the flipped case, X stride is subtracted from the base address for each window Y address. The following diagram illustrates the calculation of LFB address for the non-flipped and flipped window origin rendering modes.

Error! Not a valid link.

Swap coordination within SST-96 requires a swap command, a swap pending increment command and commands to initialize the next buffer. The following command sequence illustrates this process.

- 1. Rendering Commands

- 2. Swap Pending Increment Command

- 3. Swap Command

- 4. Set Next Buffer Pointers Registers

- 5. Fast Fill Buffer Commands

- 6. Repeat

# **Tiling or BLTing**

SST-96 swaps buffers rendered by the 3D engine and refreshed by the 2D engine through "tiling" or "BL

Tile swapping occurs automatically through hardware. Software sets up a mapping of rectangular regions of the 3D image onto rectangular regions of the display and the hardware synchronizes swaps to VSYNC. Tile data is overlaid onto the display as a back-end process during refresh. No additional frame buffer bandwidth is incurred over regular refresh. Other advantages include bilinear magnification and source-to-destination format conversion (e.g. 16-bit 3D-RGB to 8-bit 2D-RGB).

BLTing occurs through software. Software must poll after every swap command before BLTing data between buffers. The BLT adds two frame buffer accesses per pixel. An additional disadvantage exists as the data formats of the 2D and 3D engines must be equivalent.

Alliance provides 12 tiles. In general, each tile maps data of onto the display during refresh. Multi-buffering requires the assignment of tiles to frames. Double buffering assigns tiles to frames A and B, triple buffering assigns tiles to frames A, B and C and stereo buffering assigns tiles to frames A, B, C and D. Full screen 3D requires ONE tile per frame, 3D in a window requires TWO tiles per frame and 3D in a window with a simple pull down menu requires FOUR tiles per frame (can't be done in stereo quad buffering). More complicated applications require a greater number of tiles per frame and thus limit the number of frames which may be supported. For more tiling information see the Video Window documentation on the 2D chip from Alliance.

Double buffered monaural 3D requires a 2D engine which displays the front buffer as the 3D engine renders into the back buffer. As the 3D engine completes rendering the current back buffer, the 3D engine initiates a swap request and suspends execution until the request is fulfilled. Then, with the next VSYNC (exceeding the minimum VSYNC count), the 2D chip swaps (tiles) in the new front buffer allowing the 3D engine to render into the new back buffer.

Triple buffered monaural 3D requires a 2D engine which displays the front buffer as the 3D engine renders into two back buffers. As the 3D engine completes rendering the first back buffer, the 3D engine initiates a swap request and continues rendering into the second back buffer. Meanwhile, with every VSYNC (exceeding the minimum VSYNC count), the 2D chip swaps (tiles) in the new front buffer allowing the 3D engine to render into another back buffer.

Error! Not a valid link.

Double buffered stereo requires a 2D engine which displays the left and right images at the frame rate as the 3D engine renders the opposite images within the frame rate. This configuration precludes 3D rendering which may fall behind the refresh rate of the 2D engine.

Quadruple buffered stereo requires a 2D engine which displays the left and right images at the frame rate as the 3D engine renders the next left and right images. Software renders left and right image pairs with a singular swap command. Each swap command switches in a new set of left and right image pairs at even numbered VSYNC pulses. If the 3D engine gets behind the 3D engine, the 3D engine continues rendering as the 2D engine refreshes the display with the previous left and right images.

Error! Not a valid link.

# 7. 3D Register Map

The following register map defines the 3D control registers of SST-96. The map describes the **name**, the **address** and the number of **bits** of each of the 3D control registers. The address indicates the 8-bit register number for both read and write addresses. For read accesses, the address of this table reflects bits 9:2 of the PCI address and for write accesses the address of reflects bits 19:12 of the PCI address.

In addition, the register map includes the following chip, RW and Sync/Fifo columns.

- The **chip** column indicates the chips that the registers are stored in (F = FBIjr & T = TREX). A "%" indicates that the registers are unconditionally written to the chips of the chip field regardless of the chip address.

- The **RW** column indicates the read and write capability of individual registers. Reading from a register which is "write only" returns undefined data. Writing a register which is "read only" does nothing.

- The **sync** column identifies registers which may cause the graphics processor to stall. A "yes" indicates that the graphics processor will wait for a flush of the data pipeline before loading the register. Loading these registers results in a small performance degradation when compared to registers which do not need synchronization.

- The **FIFO** column identifies registers whose writes will be pushed into the MEM FIFO. Care must be taken when writing to those registers not pushed into the FIFO. Writes to these registers may complete out-of-order relative to pending writes which have been FIFOed. Also, reads are never FIFOed, therefore reading FIFOed registers will return the current value of the register, irrespective of writes to the register pending in the FIFO.

The register map defines the registers of SST-96 while highlighting modifications from SST-1. Registers which have been modified or added since SST-1 are highlighted in light gray. Additionally, unlike SST-1, the SST-96 map defines only one mapping for the triangle parameter registers. SST-96 defines the triangle parameter registers (start, delta-x and delta-y) grouped by parameter type (R, G, B, A, Z, S and T) only. This grouping was the alternate grouping of SST-1.

| Name                  | Address<br>w:[9:2]<br>r:[19:12] | Bits         | Chip         | RW | Sync?<br>/Fifo? | Description                                                                                      | p# |

|-----------------------|---------------------------------|--------------|--------------|----|-----------------|--------------------------------------------------------------------------------------------------|----|

| status                | 0x000                           | 15:0         | F            | R  | na              | Status Register                                                                                  | 23 |

| reserved              | 0x001                           | na           |              |    |                 | 19                                                                                               |    |

| vertexAx              | 0x002                           | 15:0         | F+T%         | W  | N/Y             | Vertex A x-coordinate location (12.4 format)                                                     | 24 |

| vertexAy              | 0x003                           | 15:0         | F+T%         | W  | N/Y             | Vertex A y-coordinate location (12.4 format)                                                     |    |

| vertexBx              | 0x004                           | 15:0         | F+T%         | W  | N/Y             | Vertex B x-coordinate location (12.4 format)                                                     |    |

| vertexBy              | 0x005                           | 15:0         | F+T%         | W  | N/Y             | Vertex B y-coordinate location (12.4 format)                                                     |    |

| vertexCx              | 0x006                           | 15:0         | F+T%         | W  | N/Y             | Vertex C x-coordinate location (12.4 format)                                                     |    |

| vertexCy              | 0x007                           | 15:0         | F+T%         | W  | N/Y             | Vertex C y-coordinate location (12.4 format)                                                     |    |

| ,                     |                                 |              |              |    |                 | , , ,                                                                                            |    |

| startR                | 0x008                           | 23:0         | F            | W  | N/Y             | Starting Red parameter (12.12 format)                                                            | 24 |

| dRdX                  | 0x009                           | 23:0         | F            | W  | N/Y             | Change in Red with respect to X (12.12 format)                                                   |    |

| dRdY                  | 0x00a                           | 23:0         | F            | W  | N/Y             | Change in Red with respect to Y (12.12 format)                                                   |    |

| startG                | 0x00b                           | 23:0         | F            | W  | N/Y             | Starting Green parameter (12.12 format)                                                          |    |

| dGdX                  | 0x00c                           | 23:0         | F            | W  | N/Y             | Change in Green with respect to X (12.12 format)                                                 |    |

| dGdY                  | 0x00d                           | 23:0         | F            | W  | N/Y             | Change in Green with respect to Y (12.12 format)                                                 |    |

| startB                | 0x00e                           | 23:0         | F            | W  | N/Y             | Starting Blue parameter (12.12 format)                                                           |    |

| dBdX                  | 0x00f                           | 23:0         | F            | W  | N/Y             | Change in Blue with respect to X (12.12 format)                                                  |    |

| dBdY                  | 0x010                           | 23:0         | F            | W  | N/Y             | Change in Blue with respect to Y (12.12 format)                                                  |    |

| startZ                | 0x011                           | 31:0         | F            | W  | N/Y             | Starting Z parameter (20.12 format)                                                              |    |

| dZdX                  | 0x012                           | 31:0         | F            | W  | N/Y             | Change in Z with respect to X (20.12 format)                                                     |    |

| dZdY                  | 0x013                           | 31:0         | F            | W  | N/Y             | Change in Z with respect to Y (20.12 format)                                                     |    |

| startA                | 0x014                           | 23:0         | F            | W  | N/Y             | Starting Alpha parameter (12.12 format)                                                          |    |

| dAdX                  | 0x015                           | 23:0         | F            | W  | N/Y             | Change in Alpha with respect to X (12.12 format)                                                 |    |

| dAdY                  | 0x016                           | 23:0         | F            | W  | N/Y             | Change in Alpha with respect to Y (12.12 format)                                                 |    |

| startS                | 0x017                           | 31:0         | T            | W  | N/Y             | Starting S/W parameter (14.18 format)                                                            |    |

| dSdX                  | 0x017                           | 31:0         | T            | W  | N/Y             | Change in S/W with respect to X (14.18 format)                                                   |    |

| dSdY                  | 0x019                           | 31:0         | T            | W  | N/Y             | Change in S/W with respect to Y (14.18 format)                                                   |    |

| startT                | 0x019                           | 31:0         | T            | W  | N/Y             | Starting T/W parameter (14.18 format)                                                            |    |

| dTdX                  | 0x01b                           | 31:0         | T            | W  | N/Y             | Change in T/W with respect to X (14.18 format)                                                   |    |

| dTdY                  | 0x01c                           | 31:0         | T            | W  | N/Y             | Change in T/W with respect to Y (14.18 format)                                                   |    |

| startW                | 0x01d                           | 31:0         | F+T          | W  | N/Y             | Starting 1/W parameter (2.30 format)                                                             |    |

| dWdX                  | 0x01e                           | 31:0         | F+T          | W  | N/Y             | Change in 1/W with respect to X (2.30 format)                                                    |    |

| dWdY                  | 0x01f                           | 31:0         | F+T          | W  | N/Y             | Change in 1/W with respect to Y (2.30 format)                                                    |    |

| uwuı                  | 0x011                           | 31.0         | Γ+1          | VV | 1N/ 1           | Change in 1/ w with respect to 1 (2.30 format)                                                   |    |

| triangleCMD           | 0x020                           | 31           | F+T%         | W  | N/Y             | Execute TRIANGLE command (sign bit)                                                              | 29 |

| ,                     | 0x020                           |              | 1.1.7        | ** | 1 N/ 1          | Execute Triangle confiniant (sign on)                                                            | 29 |

| reserved<br>fvertexAx | 0x021<br>0x022                  | 31:0         | F+T%         | W  | N/Y             | Vertex A x-coordinate location (floating point)                                                  | 24 |

|                       |                                 |              | F+T%         | W  | N/Y             | Vertex A y-coordinate location (floating point)  Vertex A y-coordinate location (floating point) | ∠4 |

| fvertex Ay            | 0x023<br>0x024                  | 31:0<br>31:0 | F+T%         | W  | N/Y             | Vertex B x-coordinate location (floating point)  Vertex B x-coordinate location (floating point) |    |

| fvertexBx             |                                 |              |              |    | N/Y<br>N/Y      |                                                                                                  |    |

| fvertexBy             | 0x025                           | 31:0<br>31:0 | F+T%<br>F+T% | W  | N/Y<br>N/Y      | Vertex B y-coordinate location (floating point)  Vertex C x-coordinate location (floating point) |    |

| fvertexCx             | 0x026                           |              |              |    | _               | Vertex C y-coordinate location (floating point)  Vertex C y-coordinate location (floating point) |    |

| fvertexCy             | 0x027                           | 31:0         | F+T%         | W  | N/Y             | vertex C y-coordinate location (floating point)                                                  |    |

| fstartR               | 0x028                           | 31:0         | F            | W  | N/Y             | Starting Red parameter (floating point)                                                          | 25 |

| fdRdX                 | 0x029                           | 31:0         | F            | W  | N/Y             | Change in Red with respect to X (floating point)                                                 |    |

| fdRdY                 | 0x023                           | 31:0         | F            | W  | N/Y             | Change in Red with respect to Y (floating point)                                                 |    |

| fstartG               | 0x02b                           | 31:0         | F            | W  | N/Y             | Starting Green parameter (floating point)                                                        |    |

| <b>V41</b>              |                   |             |        |            |            |                                                    |    |

|-------------------------|-------------------|-------------|--------|------------|------------|----------------------------------------------------|----|

| fdGdX                   | 0x02c             | 31:0        | F      | W          | N/Y        | Change in Green with respect to X (floating point) |    |

| fdGdY                   | 0x02d             | 31:0        | F      | W          | N/Y        | Change in Green with respect to Y (floating point) |    |

| fstartB                 | 0x02e             | 31:0        | F      | W          | N/Y        | Starting Blue parameter (floating point)           |    |

| fdBdX                   | 0x02f             | 31:0        | F      | W          | N/Y        | Change in Blue with respect to X (floating point)  |    |

| fdBdY                   | 0x030             | 31:0        | F      | W          | N/Y        | Change in Blue with respect to Y (floating point)  |    |

| fstartZ                 | 0x031             | 31:0        | F      | W          | N/Y        | Starting Z parameter (floating point)              |    |

| fdZdX                   | 0x032             | 31:0        | F      | W          | N/Y        | Change in Z with respect to X (floating point)     |    |

| fdZdY                   | 0x033             | 31:0        | F      | W          | N/Y        | Change in Z with respect to Y (floating point)     |    |

| fstartA                 | 0x034             | 31:0        | F      | W          | N/Y        | Starting Alpha parameter (floating point)          |    |

| fdAdX                   | 0x035             | 31:0        | F      | W          | N/Y        | Change in Alpha with respect to X (floating point) |    |

| fdAdY                   | 0x036             | 31:0        | F      | W          | N/Y        | Change in Alpha with respect to Y (floating point) |    |

| fstartS                 | 0x037             | 31:0        | Т      | W          | N/Y        | Starting S/W parameter (floating point)            |    |

| fdSdX                   | 0x038             | 31:0        | T      | W          | N/Y        | Change in S/W with respect to X (floating point)   |    |

| fdSdY                   | 0x039             | 31:0        | T      | W          | N/Y        | Change in S/W with respect to Y (floating point)   |    |

| fstartT                 | 0x03a             | 31:0        | T      | W          | N/Y        | Starting T/W parameter (floating point)            |    |

| fdTdX                   | 0x03b             | 31:0        | T      | W          | N/Y        | Change in T/W with respect to X (floating point)   |    |

| fdTdY                   | 0x03c             | 31:0        | T      | W          | N/Y        | Change in T/W with respect to Y (floating point)   |    |

| fstartW                 | 0x03d             | 31:0        | F+T    | W          | N/Y        | Starting 1/W parameter (floating point)            |    |

| fdWdX                   | 0x03e             | 31:0        | F+T    | W          | N/Y        | Change in 1/W with respect to X (floating point)   |    |

| fdWdY                   | 0x03f             | 31:0        | F+T    | W          | N/Y        | Change in 1/W with respect to Y (floating point)   |    |

| 101101                  | 0.1021            | 51.0        |        | 1,,        | 1,7,1      | change in 17 with respect to 1 (froming point)     |    |

| ftriangleCMD            | 0x040             | 31          | F+T%   | W          | N/Y        | Execute TRIANGLE command (floating point)          | 29 |

| reserved                | 0x041             | na          | 111    | 1,,        | 11/1       | Required CMD spacer for SST-96.                    |    |

| nopCMD                  | 0x042             | 0           | F+T%   | W          | Y/Y        | Execute NOP command                                |    |

| reserved                | 0x043             | na          | 111    | 1,,        | 1/1        | Required CMD spacer for SST-96.                    |    |

| fastfillCMD             | 0x044             | na          | F      | W          | Y/Y        | Execute FASTFILL command                           |    |

| reserved                | 0x045             | na          | 1      | 1,,        | 1/1        | Required CMD spacer for SST-96.                    |    |

| swapbufferCMD           | 0x046             | 8:0         | F      | W          | Y/Y        | Execute SWAPBUFFER command                         |    |

| reserved                | 0x047             | na          | -      | ,,         | 1/1        | Required CMD spacer for SST-96                     |    |

| swappendCMD             | 0x048             | na          | F      | W          | N/N        | Increments swap pending count                      |    |

| reserved                | 0x049             | na          | -      | ,,         | 11/11      | Required CMD spacer for SST-96.                    |    |

| reserved                | 0x04a to<br>0x04f | na          |        |            |            | Trequires ciriz spacer for BB1 700                 |    |

| fla = C = l = = D = 4la | 0050              | 27.0        | E · Tv | D/W        | NI/X/      | EDI Calar Deth Cantral                             | 22 |

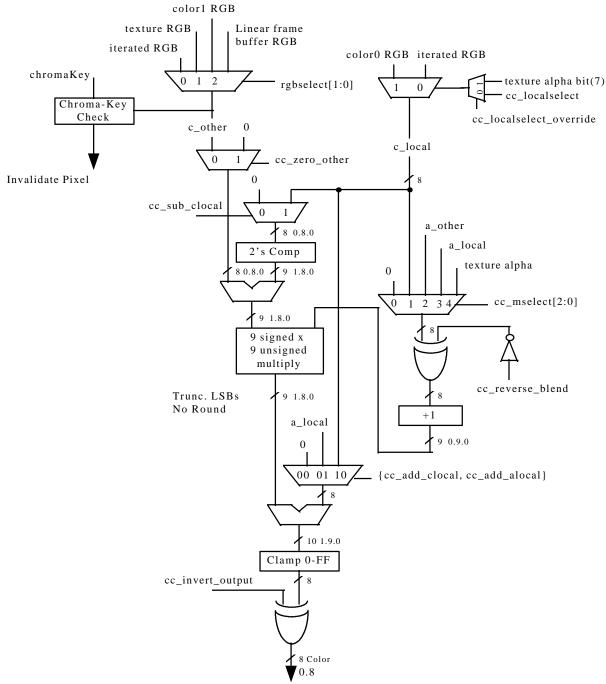

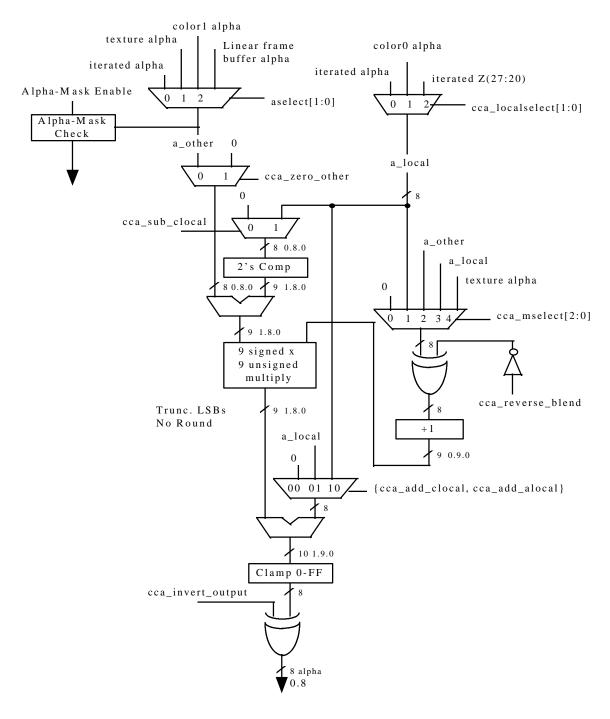

| fbzColorPath            | 0x050             | 27:0<br>5:0 | F+T%   | R/W<br>R/W | N/Y<br>N/Y | FBI Color Path Control Fog Mode Control            | 32 |

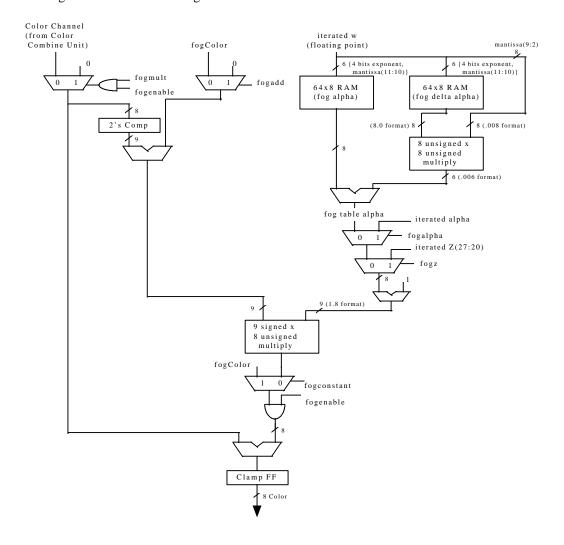

| fogMode                 | 0x051             |             | F      |            | _          | <u> </u>                                           |    |

| alphaMode               | 0x052             | 31:0        | F      | R/W        | N/Y        | Alpha Mode Control                                 |    |

| reserved                | 0x053             | na          | Б      | D/W        | 37/37      | Calama 1 A Time D ff a Cantral                     | 41 |

| fbzMode                 | 0x054             | 19:0        | F      | R/W        | Y/Y        | Color and Auxiliary Buffer Control                 | 41 |

| stipple                 | 0x055             | 31:0        | F      | R/W        | Y/Y        | Rendering Stipple Value                            | +  |

| color0                  | 0x056             | 31:0        | F      | R/W        | Y/Y        | Constant Color #0                                  | +  |

| color1                  | 0x057             | 31:0        | F      | R/W        | Y/Y        | Constant Color #1                                  | +  |

| fogColor                | 0x058             | 23:0        | F      | W          | Y/Y        | Fog Color Value                                    | +  |

| zaColor                 | 0x059             | 31:0        | F      | W          | Y/Y        | Constant Alpha/Depth Value                         | +  |

| chromaKey               | 0x05a             | 23:0        | F      | W          | Y/Y        | Chroma Key Compare Value                           |    |

| chromaRange             | 0x05b             | 28:0        | F      | W          | Y/Y        | Chroma Range Compare Values, Modes & Enable        |    |

| reserved                | 0x05c to          | na          | 1      | 1          | 1          |                                                    | 1  |

|                 |                   | 1            |   | 1   | 1   |                                                  |    |

|-----------------|-------------------|--------------|---|-----|-----|--------------------------------------------------|----|

| colBufferSetup  | 0x060             | 31:0         | F | R/W | Y/Y | Color Buffer Base Address, Stride and Mode       | 48 |

| auxBufferSetup  | 0x060             | 30:0         | F | R/W | Y/Y | Auxiliary Buffer Base Address and Stride         | 40 |

| clipLeftRight0  | 0x061<br>0x062    | 31:0         | F | R/W | Y/Y | Left and Right of Clipping Register 0            |    |

| clipTopBottom0  | 0x062<br>0x063    | 31:0         | F | R/W | Y/Y | Top and Bottom of Clipping Register 0            |    |

|                 | +                 | _            | F |     |     | 1 11 5 5                                         |    |

| clipLeftRight1  | 0x064             | 31:0         | F | R/W | Y/Y | Left and Right of Clipping Register 1            |    |

| clipTopBottom1  | 0x065<br>0x066 to | 31:0         | F | R/W | Y/Y | Top and Bottom of Clipping Register 1            |    |

| reserved        | 0x06f             | na           |   |     |     |                                                  |    |

| fogTable        | 0x070 to 0x08f    | 31:0         | F | W   | Y/Y | Fog Table                                        | 51 |

| fbijrInit0      | 0x090             | 17:0         | F | R/W | N/N | FBIjr Hardware Init 0 - General                  | 52 |

| fbijrInit1      | 0x091             | 24:0         | F | R/W | N/N | FBIjr Hardware Init 1 - PUMA                     |    |

| fbijrInit2      | 0x092             | 18:0         | F | R/W | N/N | FBIjr Hardware Init 2 - MEM FIFO Setup           |    |

| fbijrInit3      | 0x093             | 30:0         | F | R/W | N/N | FBIjr Hardware Init 2 - CMD FIFO Setup           |    |

| fbijrInit4      | 0x094             | 18:0         | F | R/W | N/N | FBIjr Hardware Init 4 - CMD FIFO Entry Count     |    |

| fbijrInit5      | 0x095             | 18:0         | F | R/W | N/N | FBIjr Hardware Init 5 - CMD FIFO Read Pointer    |    |

| reserved        | 0x096 to<br>0x09f | na           |   |     |     |                                                  |    |

| fbijrVersion    | 0x0a0             | 31:0         | F | R   | na  | FBIjr Version (company, device, & board)         | 56 |

| fbiPixelsIn     | 0x0a1             | 23:0         | F | R   | na  | Pixel Counter (Number pixels processed)          | 1  |

| fbiChromaFail   | 0x0a2             | 23:0         | F | R   | na  | Pixel Counter (Number pixels failed Chroma test) |    |

| fbiZfuncFail    | 0x0a3             | 23:0         | F | R   | na  | Pixel Counter (Number pixels failed Z test)      |    |

| fbiAfuncFail    | 0x0a4             | 23:0         | F | R   | na  | Pixel Counter (Number pixels failed Alpha test)  |    |

| fbiPixelsOut    | 0x0a5             | 23:0         | F | R   | na  | Pixel Counter (Number pixels drawn)              |    |

| reserved        | 0x0a6 to<br>0x0be | na           |   |     |     |                                                  |    |

| texChipSel      | 0x0bf             | 1:0          | F | R/W | N/Y | Texture Write Chip Select                        |    |

|                 |                   |              |   |     |     |                                                  |    |

| textureMode     | 0x0c0             | 30:0         | T | W   | N/Y | Texture Mode Control                             | 58 |

| tLOD            | 0x0c1             | 23:0         | T | W   | N/Y | Texture LOD Settings                             |    |

| tDetail         | 0x0c2             | 16:0         | T | W   | N/Y | Texture LOD Settings                             |    |

| texBaseAddr     | 0x0c3             | 18:0         | T | W   | N/Y | Texture Base Address                             |    |

| texBaseAddr_1   | 0x0c4             | 18:0         | T | W   | N/Y | Texture Base Address (supplemental LOD 1)        |    |

| texBaseAddr_2   | 0x0c5             | 18:0         | T | W   | N/Y | Texture Base Address (supplemental LOD 2)        |    |

| texBaseAddr_3_8 | 0x0c6             | 18:0         | T | W   | N/Y | Texture Base Address (supplemental LOD 3-8)      |    |

| TREXInit0       | 0x0c7             | 31:0         | T | W   | Y/Y | TREX Hardware Initialization (register 0)        |    |

| TREXInit1       | 0x0c8             | 31:0         | T | W   | Y/Y | TREX Hardware Initialization (register 1)        |    |

| nccTable0       | 0x0c9 to<br>0x0d4 | 31:0<br>26:0 | T | W   | Y/Y | Narrow Channel Compression Table 0 (12 entries)  |    |

| nccTable1       | 0x0d5 to 0x0e0    | 31:0<br>26:0 | Т | W   | Y/Y | Narrow Channel Compression Table 1 (12 entries)  |    |

| reserved        | 0x0e1 to<br>0x0ff | na           |   |     |     | ,                                                |    |

# 8. Register Definitions

# 8.1 status Register

The **status** register is a read only register which provides the CPU information on the current state of the graphics processor. The data of the register indicates idleness, swap activity and FIFO fullness. This information is available through both the status register of FBIjr and a status register within the 2D chip. Software is encouraged to acquire the status through the 2D chip as this access does not tax the frame buffer bandwidth. However, software must accept inaccuracies in 2D status resulting from an update latency of up to **TBD** (50+) memory clocks.

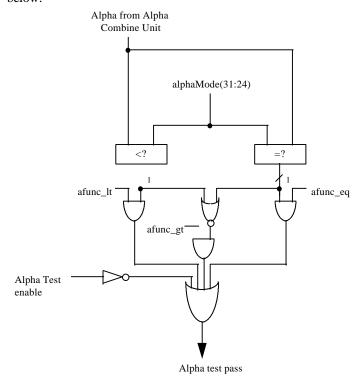

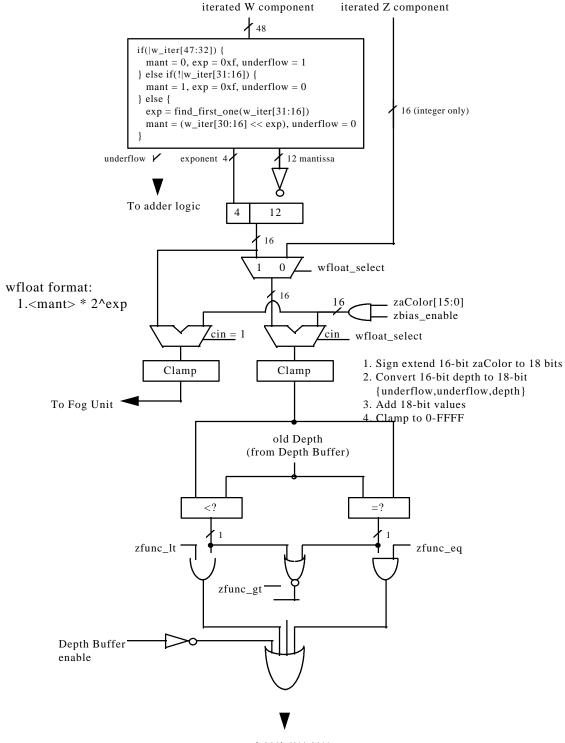

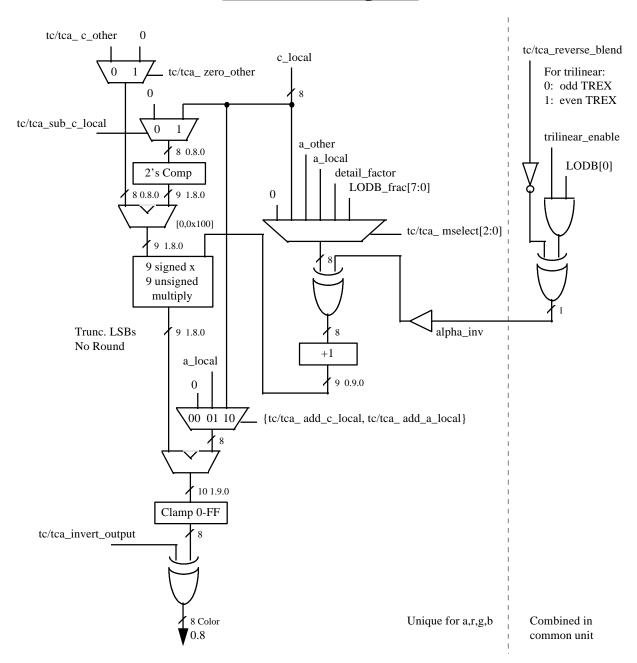

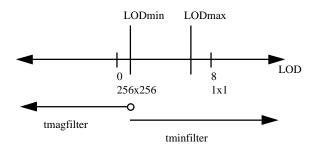

| Bit  | Description                                                                                                                                                        |