## Compression Expansion Processor Am7970A

**Technical Manual**

# **Advanced Micro Devices**

## Am7970 Compression Expansion Processor

The International Standard of Quality guarantees a 0.05% AQL on all electrical parameters, AC and DC, over the entire operating range.

© 1986 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The performance characteristics listed in this data book are guaranteed by specific tests, correlated testing, guard banding, design and other practices common to the industry. For specific testing details contact your local AMD sales representative. The company assumes no responsibility for the use of any circuits described herein.

> 901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

#### ACKNOWLEDGEMENTS:

This technical manual was written by James Williamson, Field Applications Engineer and Wolfgang Kemmler, Headquarters Applications Engineer. The Senior Technical Writer for this manual is Erland Kyllonen.

Section 4.2 was contributed by Deyoung Hong, Software Engineer.

Peter Alfke, Director of Applications and Joseph Brcich, Manager of Headquarters Applications contributed to the final revisions of this manual.

#### TABLE OF CONTENTS

| 1. | INT                      | RODU          | CTION1-1                                                                                                         |

|----|--------------------------|---------------|------------------------------------------------------------------------------------------------------------------|

|    | 1.1<br>1.2<br>1.3<br>1.4 | Featu<br>CCIT | ral Description       1-2         ures       1-2         Γ Standards       1-2         ment Definition       1-2 |

| 2. | FUI                      |               | NAL DESCRIPTION                                                                                                  |

|    | 2.1                      |               | tional Description                                                                                               |

|    |                          | 2.1.1         | Source Buffer Definition<br>Destination Buffer Definition<br>Attributes<br>Control Parameters                    |

|    |                          | 212           | Start Processing Procedures                                                                                      |

|    |                          |               | How to Use the Status Registers                                                                                  |

|    |                          |               | Interrupt Handling                                                                                               |

|    |                          | 215           | Stopping the CEP                                                                                                 |

|    | 2.2                      | Regis         | ter Description                                                                                                  |

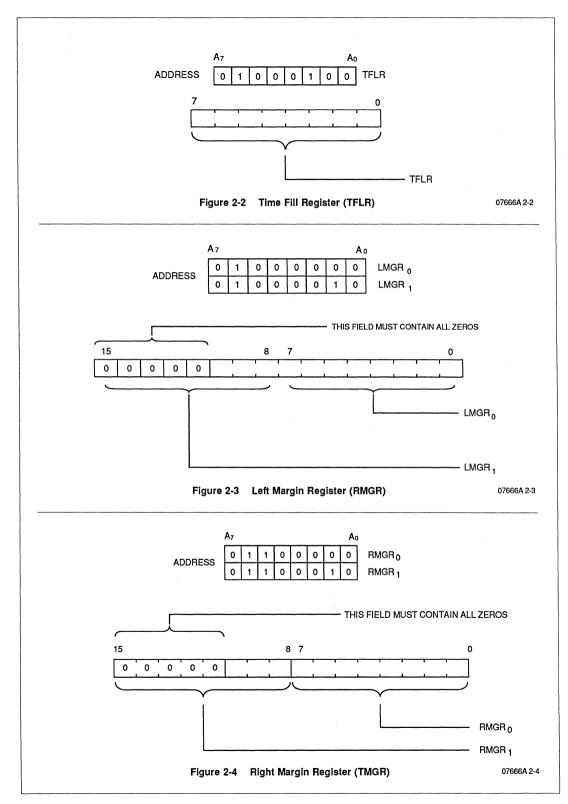

|    |                          |               | Time Fill Register (TFLR)                                                                                        |

|    |                          |               | Left Margin Register (LMGR)                                                                                      |

|    |                          |               | Right Margin Register (RMGR)2-9                                                                                  |

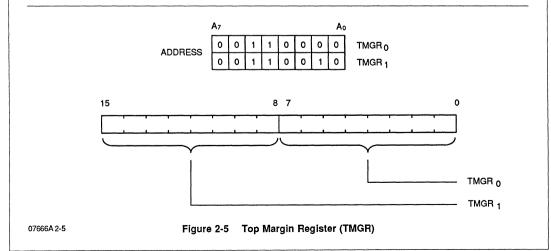

|    |                          |               | Top Margin Register (TMGR)                                                                                       |

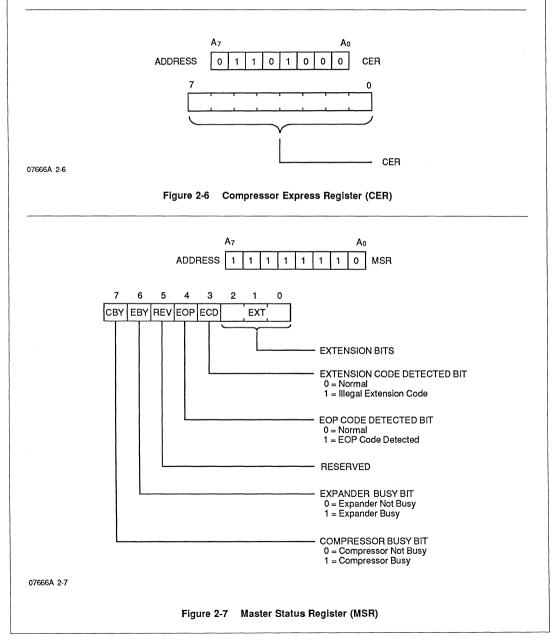

|    |                          |               | Compressor Express Register (CER) 2-10                                                                           |

|    |                          |               | Master Status Register (MSR) 2-10                                                                                |

|    |                          |               | EXT (Extension)                                                                                                  |

|    |                          |               | ECD (Extension Code Detected)                                                                                    |

|    |                          |               | EOP (End of Page)                                                                                                |

|    |                          |               | ID (Version I. D.)                                                                                               |

|    |                          |               | EBY (Expander Busy)                                                                                              |

|    |                          |               | CBY (Compressor Busy)                                                                                            |

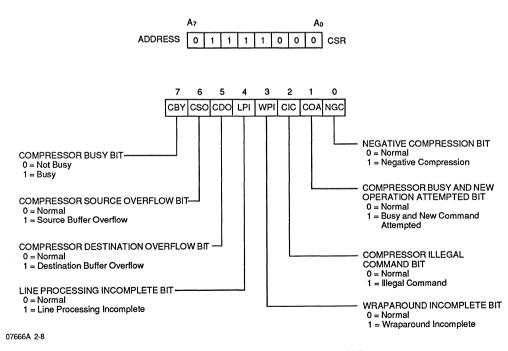

|    |                          | 2.2.7         | Compressor Status Register (CSR) 2-10                                                                            |

|    |                          |               | NGC–Negative Compression                                                                                         |

|    |                          |               | COA-Compressor Busy and New Operation Attempted                                                                  |

|    |                          |               | CIC–Compressor Illegal Command                                                                                   |

|    |                          |               | WPI–Wraparound Incomplete                                                                                        |

|    |                          |               | LPI-Line Processing Incomplete                                                                                   |

|    |                          |               | CDO–Compressor Destination Overflow                                                                              |

|    |                          |               | CSO–Compressor Source Overflow                                                                                   |

|    |                          |               | CBY–Compressor Busy                                                                                              |

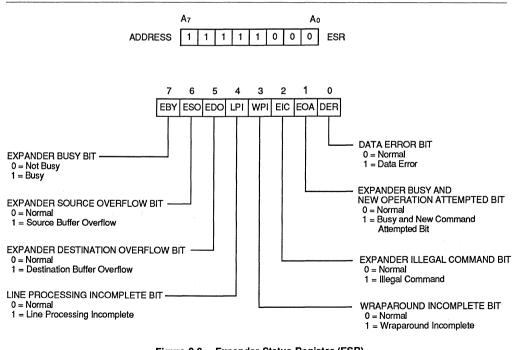

|    |                          | 2.2.8         | Expander Status Register (ESR) 2-14                                                                              |

|    |                          |               | DER-Data Error                                                                                                   |

|    |                          |               | EOA-Expander Busy and New Operation Attempted                                                                    |

|    |                          |               | EIC-Expander Illegal Command                                                                                     |

|    |                          |               | WPI-Wraparound Incomplete                                                                                        |

|    |                          |               | LPI-Line Processing Incomplete                                                                                   |

|    |                          |               | EDO-Expander Destination Overflow                                                                                |

|    |                          |               | ESO-Expander Source Overflow                                                                                     |

|    |                          |               | EBY–Expander Busy                                                                                                |

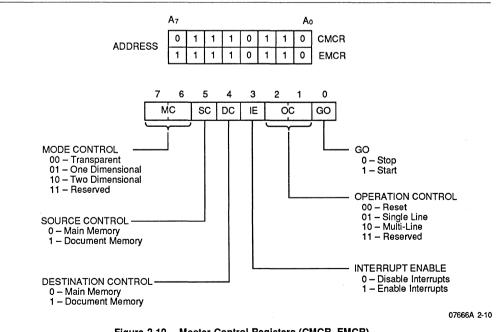

| 2.2.9 Master Control Registers (CMCR, EMCR)         |                            |

|-----------------------------------------------------|----------------------------|

| GO                                                  |                            |

| OC-Operation Control                                |                            |

| RESET (00)                                          |                            |

| SINGLE-LINE (01)                                    |                            |

| MULTI-LINE (10)                                     |                            |

| RESERVED (11)                                       |                            |

| IE-Interrupt Enable                                 |                            |

| DC-Destination Control                              |                            |

| SC-Source Control                                   |                            |

| MC-Mode Control                                     |                            |

| TRANSPARENT (00)<br>ONE-DIMENSIONAL (01)            |                            |

| TWO-DIMENSIONAL (10)                                |                            |

| RESERVED (11)                                       |                            |

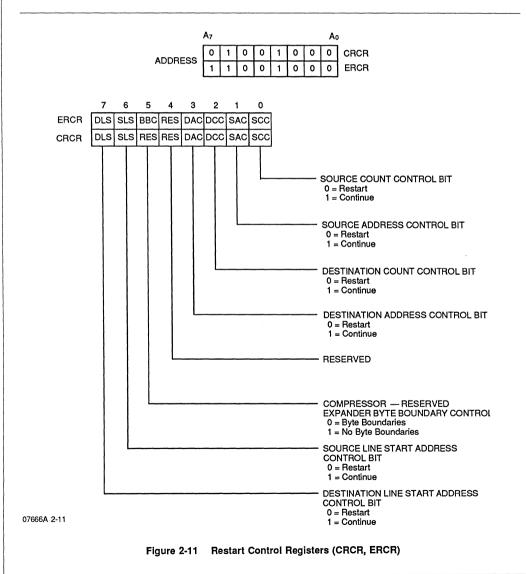

| 2.2.10 Compressor/Expander Restart Control Register | ers (CBCB_EBCB) 2-18       |

| SCC-Source Count Control                            |                            |

| SAC–Source Address Control                          |                            |

| DCC–Destination Count Control                       |                            |

| DAC–Destination Address Contro                      | l                          |

| RES-Reserved                                        |                            |

| BBC-Expander Byte Boundary C                        | ontrol                     |

| SLS-Source Line Start Address (                     | Control                    |

| DLS–Destination Line Start Addre                    |                            |

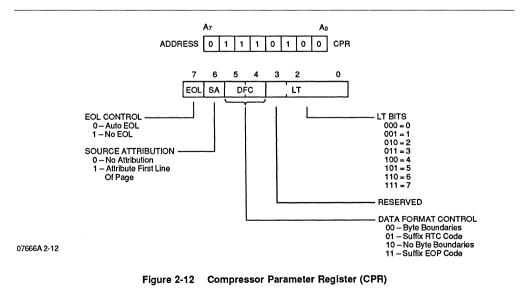

|                                                     | PR) 2-20                   |

| LT –Line Termination Parameter                      |                            |

| DFC–Data Format Control                             |                            |

| SA-Source Attribute                                 |                            |

| EOL-End of Line                                     |                            |

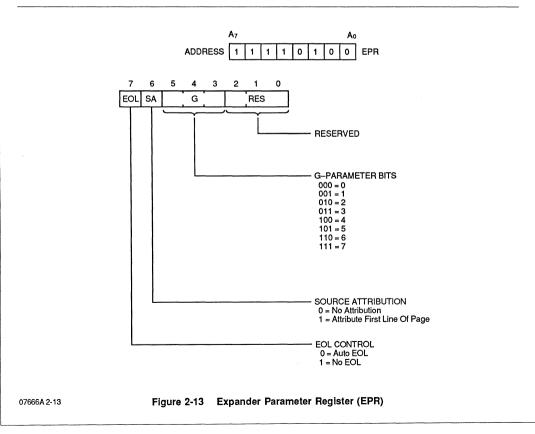

|                                                     | 3) 2-22                    |

| Reserved                                            |                            |

| G–Granularity                                       |                            |

| SA–Source Attribute<br>EOL                          |                            |

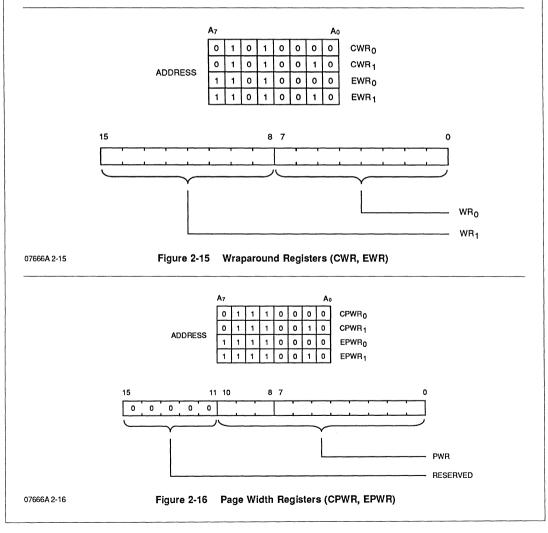

|                                                     | PR)                        |

|                                                     | i)                         |

| 2.2.15 Page Width Begisters (CPWB EPV               | VR) 2-24                   |

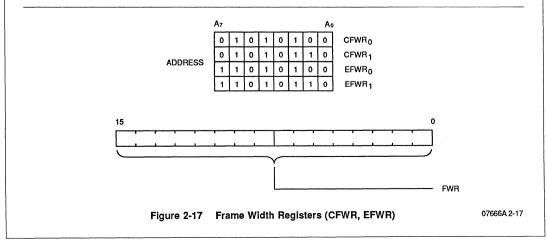

| 2.2.16 Frame Width Registers (CEWB EF)              | WR)                        |

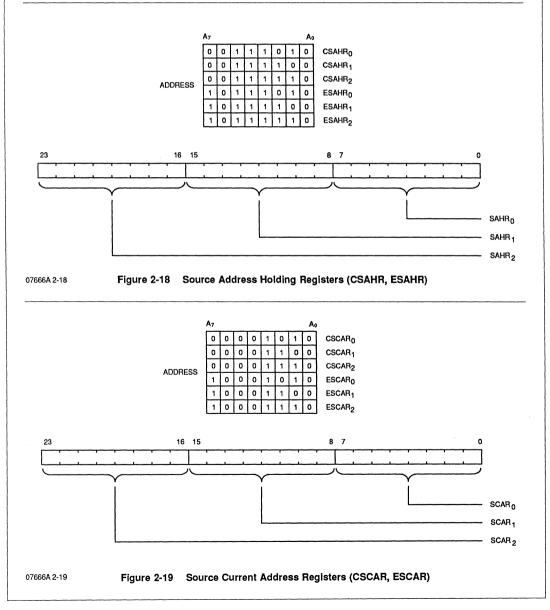

|                                                     | (CSAHR, ESAHR)             |

|                                                     | (CSCAR, ESCAR)             |

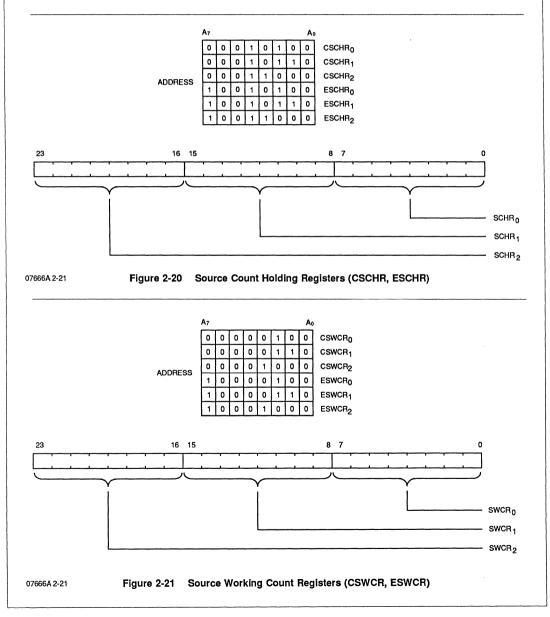

|                                                     | SCHR, ESCHR)               |

|                                                     | SWCR, ESWCR) 2-27          |

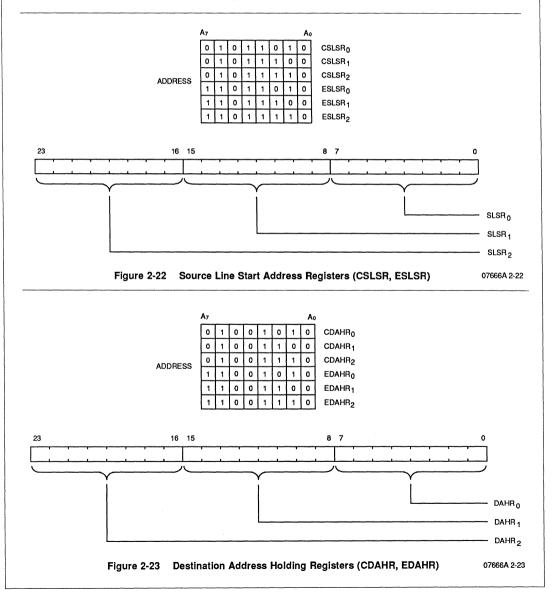

| 2.2.21 Source Line Start Address Register           | rs (CSLSR, ESLSR) 2-28     |

| 2.2.22 Destination Address Holding Regis            | ters (CDAHR, EDAHR) 2-28   |

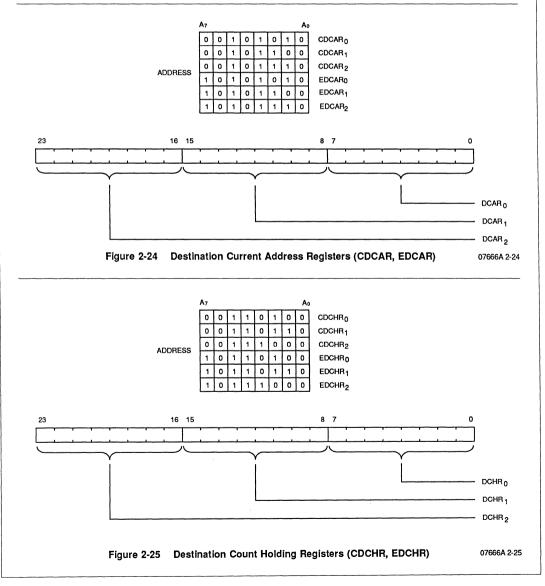

| 2.2.23 Destination Current Address Regist           | ters (CDCAR, EDCAR) 2-28   |

|                                                     | s (CDCHR, EDCHR) 2-28      |

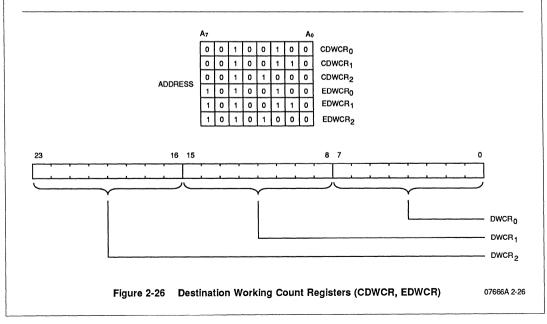

|                                                     | rs (CDWCR, EDWCR)          |

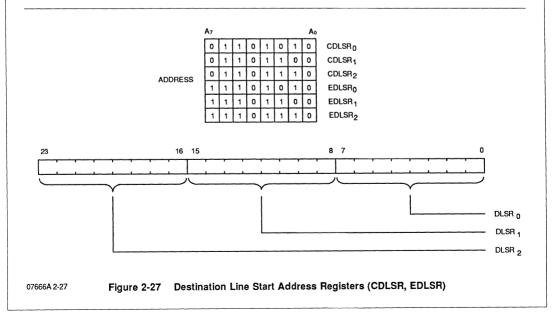

|                                                     | pisters (CDLSR,EDLSR) 2-31 |

|                                                     |                            |

|                                                     |                            |

| CLK Clock (Input)                                   |                            |

| RESET (Input)<br>RD Read (Input/Output, Active Lo   | w Throa-stata)             |

| WR Write (Input/Output, Active Lo                   |                            |

| CS Chip Select (Active Low, Input                   |                            |

| ALE Address Latch Enable (Out                       |                            |

| HRQ Hold Request (Output)                           |                            |

| HLDA Hold Acknowledge (Input)                       |                            |

| 3,1,7                                               |                            |

|         | READY (Input/Output, Three-state)                                                                                  |

|---------|--------------------------------------------------------------------------------------------------------------------|

|         | INTR Interrupt Request (Output)                                                                                    |

|         | A <sub>0</sub> -A <sub>15</sub> Lower Address, (Input, tri-state outputs)                                          |

|         | AD <sub>16</sub> -AD <sub>23</sub> Address-Data Bus (Input/Output, Three-state)                                    |

|         | DRD Document Store Read (Active Low, Output, Three-state)                                                          |

|         | DWR Document Store Write (Active Low, Output, Three-state)                                                         |

|         | DALE Document Store ALE (Output, Three-state)                                                                      |

|         | DREADY Ready (Input, Three-state)                                                                                  |

|         | DA0-DA15 Document Store Lower Address Bus (Output, Three-state)                                                    |

|         | DA16-DA23 Document Store Upper Address-                                                                            |

|         | Data Bus (Input/Output, Three-state)                                                                               |

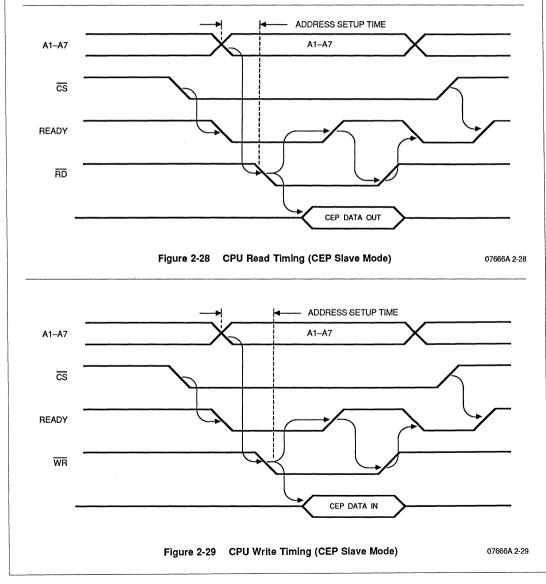

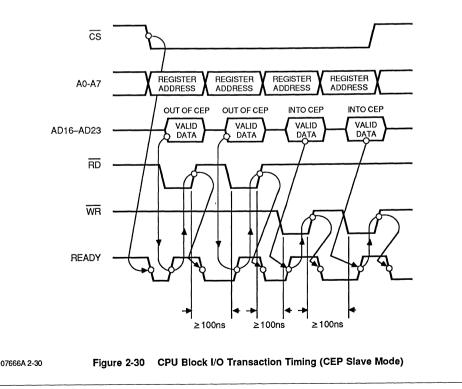

|         | 2.3.2 CPU Access Operations (CEP Slave Mode)                                                                       |

|         | Read Access Operation                                                                                              |

|         | Write Access Operation                                                                                             |

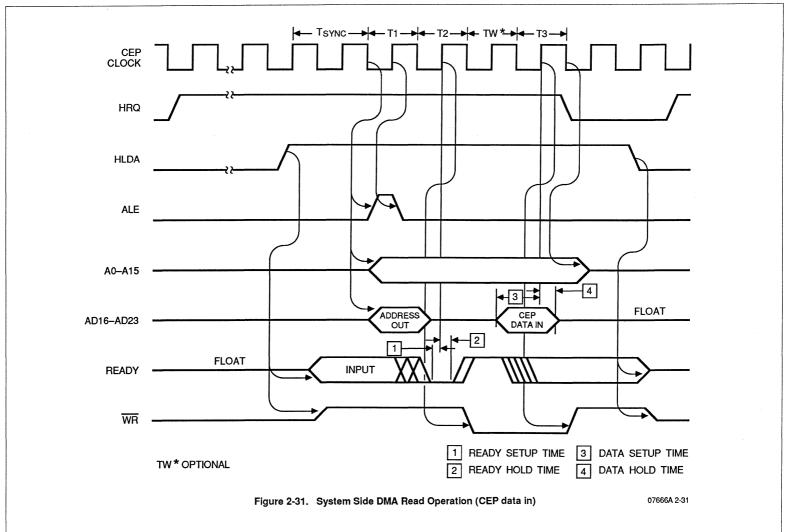

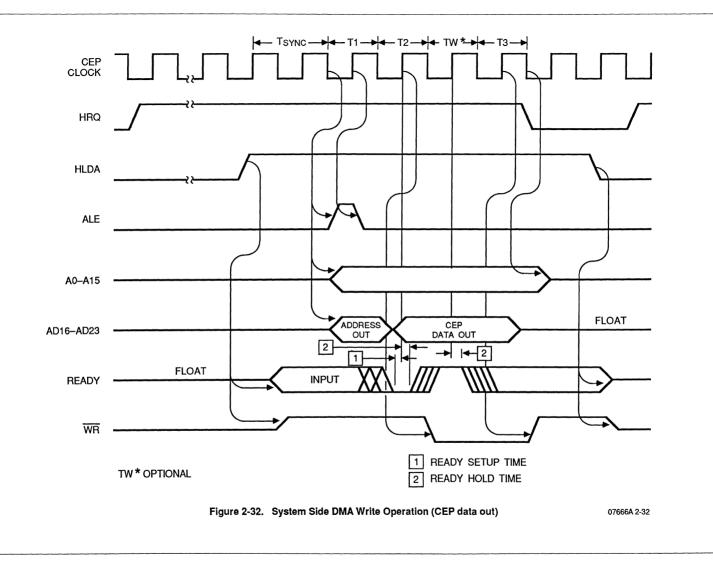

|         | 2.3.3 DMA Operation (CEP Master Mode)                                                                              |

|         | Read Access Operation                                                                                              |

|         | Write Access Operation                                                                                             |

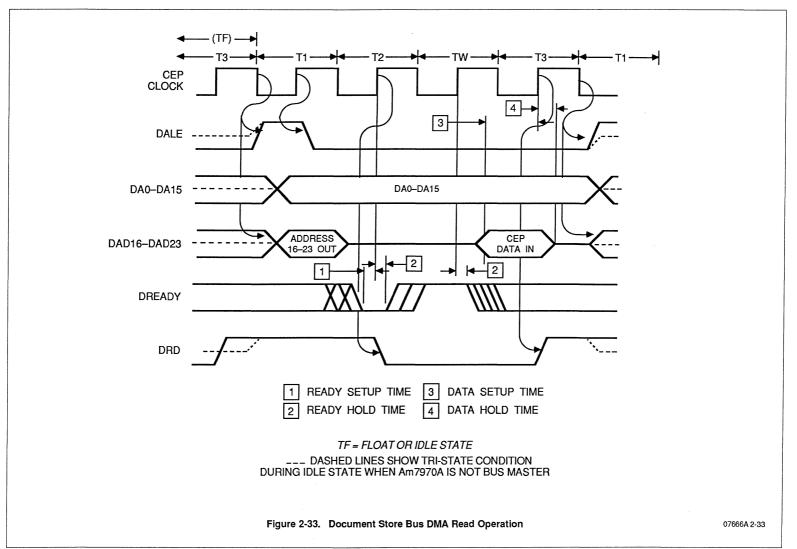

|         | 2.3.4 Document Bus Operation                                                                                       |

|         | Read Access Operation                                                                                              |

|         | Write Access Operation                                                                                             |

|         |                                                                                                                    |

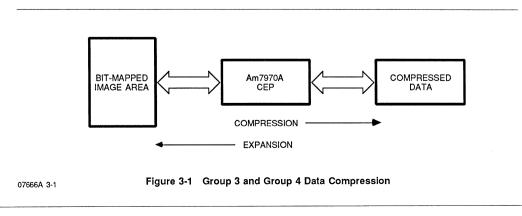

| 3. COD  | ING3-1                                                                                                             |

|         |                                                                                                                    |

| 3.1     | Coding Concente                                                                                                    |

| 5.1     | Coding Concepts                                                                                                    |

|         |                                                                                                                    |

|         | 3.1.2 Information Theory                                                                                           |

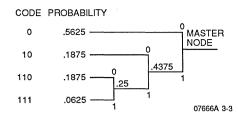

|         | 3.1.3 Huffman Coding                                                                                               |

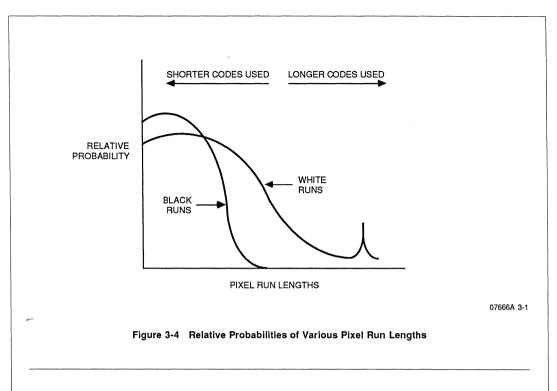

|         | 3.1.4 Modified Huffman Coding                                                                                      |

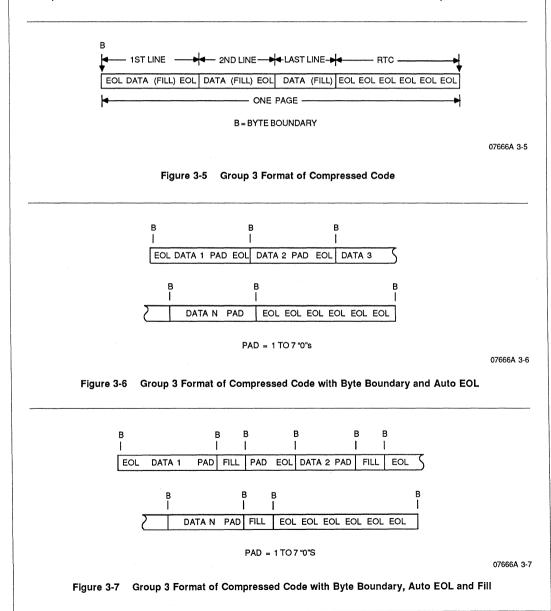

|         | 3.1.5 The CEP's One-Dimensional Mode                                                                               |

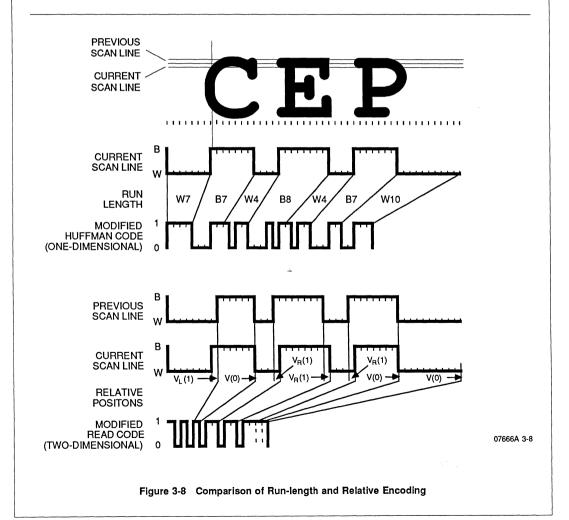

|         | 3.1.6         Modified READ Coding         3-9           3.1.7         The CEP's Two-Dimensional Mode         3-11 |

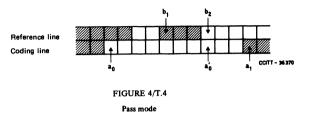

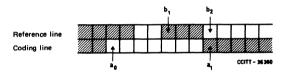

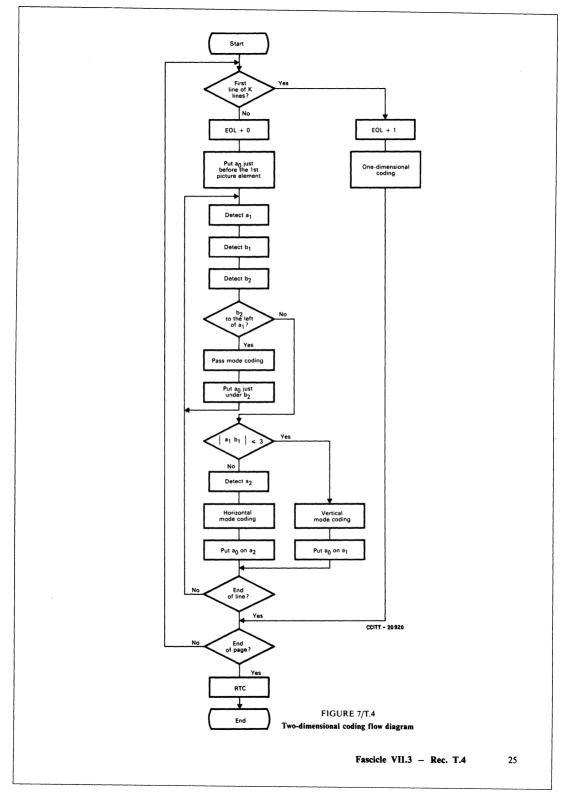

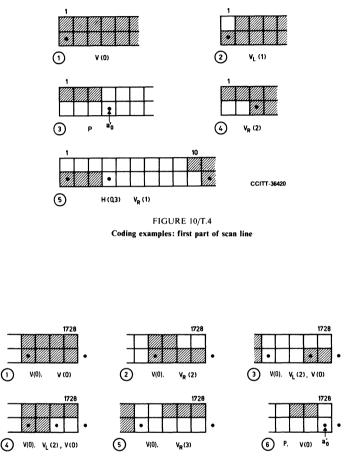

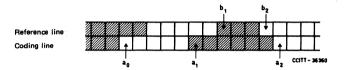

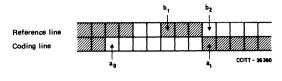

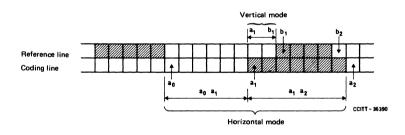

|         | Pass Mode                                                                                                          |

|         | Vertical Mode                                                                                                      |

|         | Horizontal Mode                                                                                                    |

|         | 3.1.8 Express Mode                                                                                                 |

|         | Granularity                                                                                                        |

|         | 3.1.9 Transparent Mode                                                                                             |

|         | 3.1.10 Uncompressed Data                                                                                           |

|         | 3.1.10 Uncompressed Data                                                                                           |

|         | 3-1/                                                                                                               |

| 4 PR(   | OGRAMMING                                                                                                          |

| 4. 1110 | 4-1                                                                                                                |

| 4.1     | Register Setup Routines                                                                                            |

|         | 4.1.1 Program Listing                                                                                              |

|         | Main Program                                                                                                       |

|         | Initialize CER, CWR, EWR, CCR, and ECR                                                                             |

|         | Load Time fill Register, TFLR                                                                                      |

|         | Load Paper Width Registers, CPWR/EPWR                                                                              |

|         | Load Margin Values into LMGR, RMGR, and TMGR                                                                       |

|         | Set G-Parameter into Register, EPR                                                                                 |

|         | Set K-Value into Registers, CPR/EPR                                                                                |

|         | Dump Registers                                                                                                     |

|         | Load Compressor Source Registers, CSCHR and CSWCR                                                                  |

|         | Load Compressor Destination Registers, CDCHR and CDWCR                                                             |

|         | Load Expander Destination Registers, EDCHR and EDWCR                                                               |

|         |                                                                                                                    |

|         |                                                                                                                    |

.

| 4.2   | Load Expander Source Registers, ESCHR and ESWCR         Register Address Evaluation         Port Number and Value, Both Registers         Port Number and Value, Expansion Register         Port Number and Value, Compression Register         Read a CEP Register         4.1.2         Error Return Messages         4-17         Image File Analysis Program Description         4-17         4.2.1         Header Declaration Section         4-18         4.2.3         Sub-Functions         4-18         4.2.4         Image Analysis Program Execution Report |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5. AF | PPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

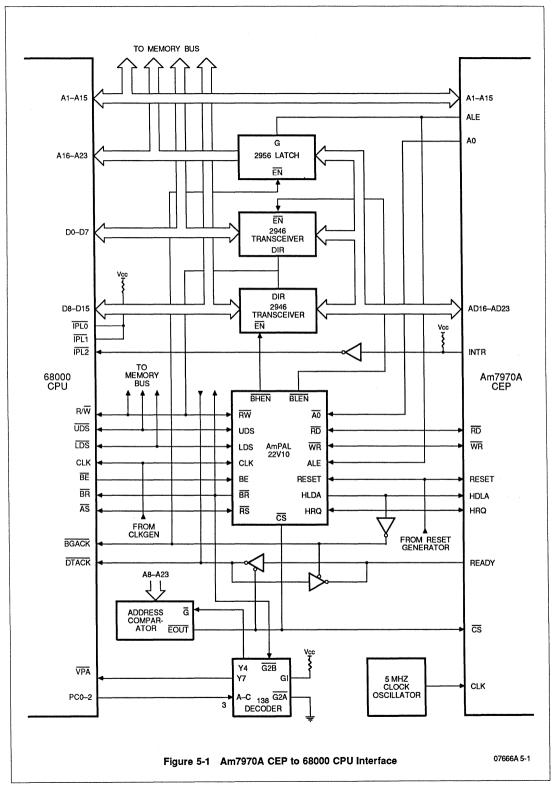

| 5.1   | Am7970A CEP Interface to the 68000 CPU5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 5.1.1 General Discussion 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | 5.1.2 Hardware Description 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | 5.1.3 Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | Interrupt Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | 68000 Accesses to the Am7970A CEP Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | (Slave Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | Am7970A CEP System Memory Access (Master Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

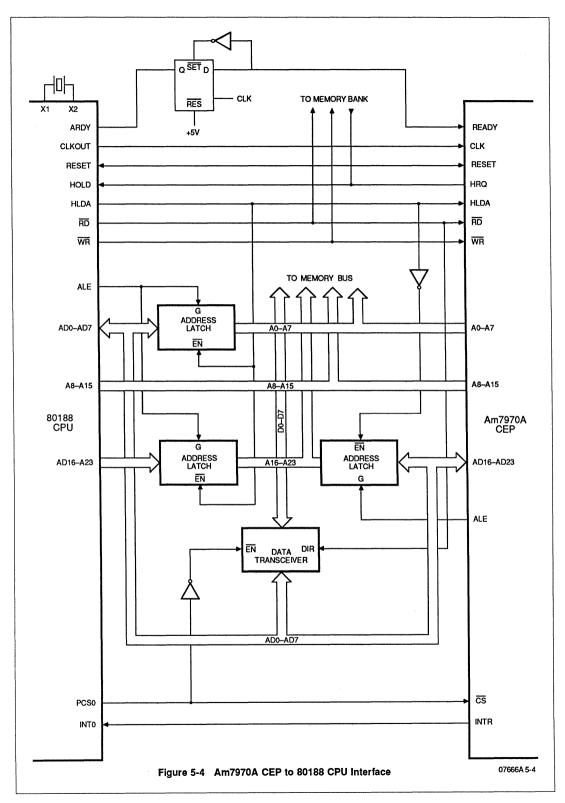

| 5.2   | Am7970A CEP Interface to the 80188 CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 5.2.1 General Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 5.2.2 Hardware Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

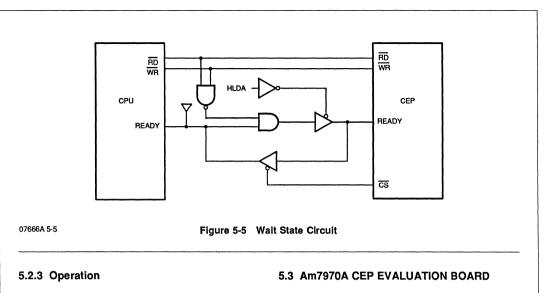

|       | 5.2.3 Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | 80188 CPU Access to the Am7970A CEP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | Am7970A CEP Access to the Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.3   | Am7970A CEP Evaluation Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | 5.3.1 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | 5.3.2 The CEP Evaluation Board in an IBM PC/XT 5-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | 5.3.3 The CEP Evaluation Board in an IBM AT 5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | 5.3.4 Evaluation Board PAL Device Equations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| APPEN | IDICES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Α.    | Throughout Performance, 5 MHz Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A. Ihroughput Performance, 5 MHz Clock              | A-1 |

|-----------------------------------------------------|-----|

| B. Image File Analysis Program Listing              |     |

| C. Glossary                                         |     |

| D. 7970A Differences Relative to 7970 Revision A/A' | D-1 |

| E. Am7970A CEP Design Hints                         | E-1 |

| F. CCITT Specifications T.4 and T.6                 | F-1 |

| G. Standard CCITT Compression Test Documents        | G-1 |

| H. Data Error Recovery Procedure                    | H-1 |

|                                                     |     |

#### INDEX

#### LIST OF FIGURES

| 1-1<br>1-2<br>1-3<br>1-4 | Document Margins<br>Document Storage                      | 1-5<br>1-6<br>1-6 |

|--------------------------|-----------------------------------------------------------|-------------------|

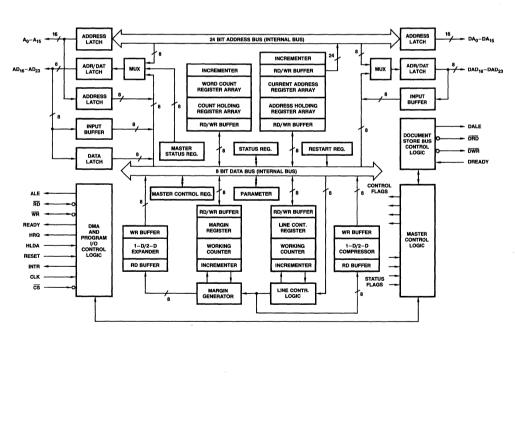

| 2-1                      | Am7970A (CEP) Block Diagram                               | 2-7               |

| 2-2                      | Time Fill Register (TFLR)                                 | 2-8               |

| 2-3                      |                                                           |                   |

| 2-4                      | Right Margin Register (RMGR)                              | 2-8               |

| 2-5                      | Top Margin Register (TMGR)                                | 2-9               |

| 2-6                      |                                                           | -11               |

| 2-7                      | Master Status Register (MSR)                              | -11               |

| 2-8                      | Compressor Status Register (CSR)                          |                   |

|                          | Expander Status Register (ESR)                            |                   |

| 2-10                     | ) Master Control Registers (CMCR, EMCR)                   | -17               |

| 2-11                     | Restart Control Registers (CRCR, ERCR)                    | -19               |

| 2-12                     | 2 Compressor Parameter Register (CPR)                     | -21               |

| 2-13                     | B Expander Parameter Register (EPR)2                      | -23               |

|                          | K Parameter Registers (CKPR, EKPR)                        |                   |

|                          | 5 Wraparound Registers (CWR, EWR)2                        |                   |

| 2-16                     | S Page Width Registers (CPWR, EPWR)2                      | -25               |

| 2-17                     | 7 Frame Width Registers (CFWR, EFWR)                      | -26               |

|                          | 3 Source Address Holding Registers (CSAHR, ESAHR)         |                   |

|                          | Source Current Address Registers (CSCAR, ESCAR)           |                   |

|                          | ) Source Count Holding Registers (CSCHR, ESCHR)           |                   |

| 2-21                     | Source Working Count Registers (CSWCR, ESWCR)             | -39               |

|                          | 2 Source Line Start Address Registers (CSLSR, ESLSR)      |                   |

|                          | 3 Destination Address Holding Registers (CDAHR, EDAHR)2   |                   |

|                          | Destination Current Address Registers (CDCAR, EDCAR)      |                   |

|                          | 5 Destination Count Holding Registers (CDCHR, EDCHR)      |                   |

| 2-26                     | 5 Destination Working Count Registers (CDWCR, EDWCR)      | -32               |

| 2-27                     | 7 Destination Line Start Address Registers (CDLSR, EDLSR) | -33               |

|                          | 3 CPU Read Timing (CEP Slave Mode)                        |                   |

|                          | OCPU Write Timing (CEP Slave Mode)                        |                   |

| 2-30                     | CPU Block I/O Transaction Timing (CEP Slave Mode)         | -39               |

| 2-3                      | 1 System Side DMA Read Operation (CEP data in)            | -40               |

| 2-32                     | 2 System Side DMA Write Operation (CEP data out)          | -41               |

|                          | 3 Document Store Bus DMA Read Operation                   |                   |

| 2-34                     | 4 Document Store Bus DMA Write Operation                  | -43               |

| 3-1                      | Group 3 and Group 4 Data Compression                      | 2.2               |

| 3-1                      |                                                           | 0.0               |

| 3-2                      |                                                           | 3-6               |

|                          | Relative Probabilities of Various Pixel Run Lengths       |                   |

| 3-4                      |                                                           | .0-0<br>2_1∩      |

| 3-5                      |                                                           | 2.10              |

| 3-0                      |                                                           | 8-10              |

| 3-7                      |                                                           | x-11              |

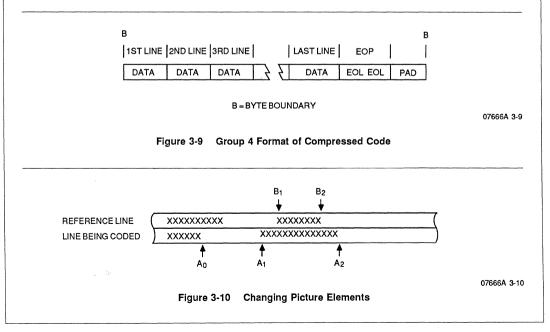

|                          | Group 4 Format of Compressed Code                         | 3-12              |

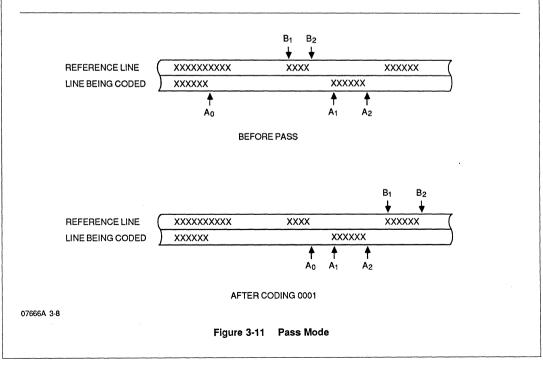

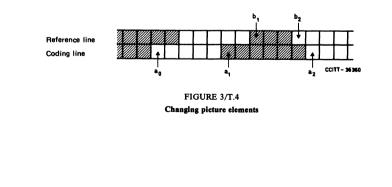

| 3_1/                     | 0 Changing Picture Elements                               | 3-12              |

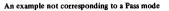

| 3.1                      | 1 Pass Mode                                               | 3-13              |

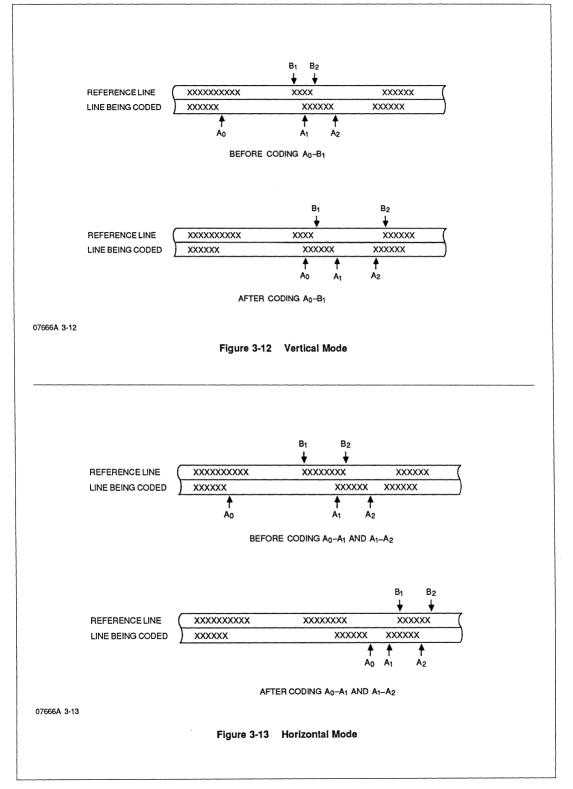

|                          | 2 Vertical Mode                                           |                   |

|                          | 3 Horizontal Mode                                         |                   |

| 2 10                     |                                                           |                   |

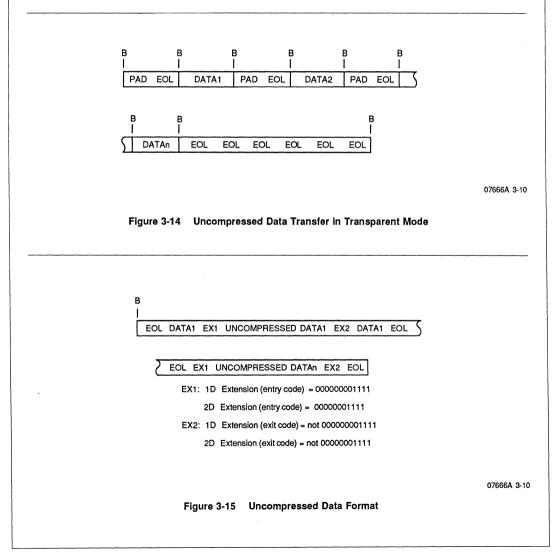

| <ul> <li>3-14 Uncompressed Data Transfer in Transparent Mode</li> <li>3-15 Uncompressed Data Format</li> <li>5-1 Am7970A CEP to 68000 CPU Interface</li> <li>5-2 Am7970A CEP to 68000 Interface Controller PAL Device</li> </ul> | 3-16<br>5-2<br>5-3 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 5-3 CEP to 68000 Interface Controller, Part B                                                                                                                                                                                    |                    |

| 5-4 Am7970A CEP to 80188 CPU Imterface<br>5-5 Wait State Circuit                                                                                                                                                                 |                    |

| 5-6 Evaluation Board System Memory Map                                                                                                                                                                                           |                    |

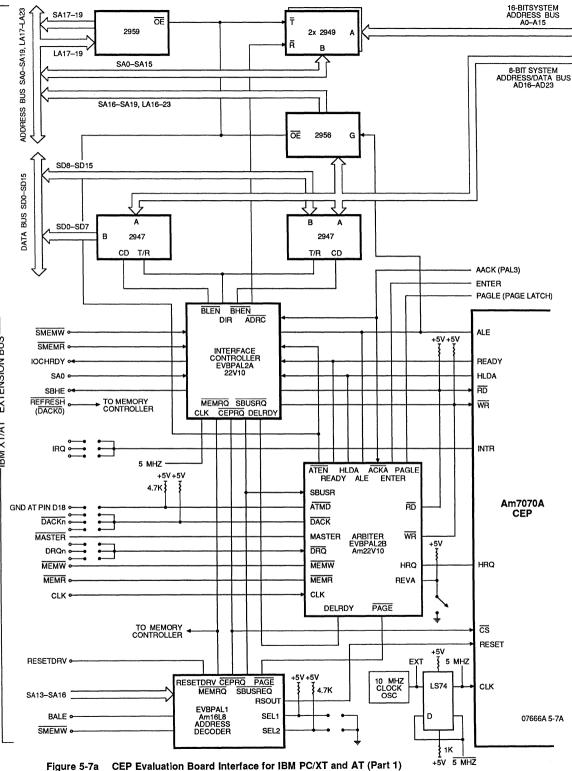

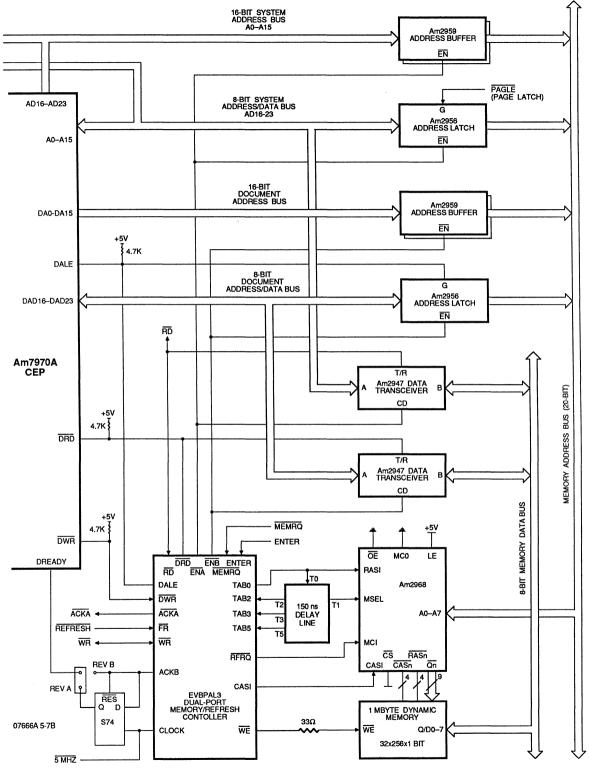

| 5-7 CEP Evaluation Board Interface for IBM PC/XT and AT                                                                                                                                                                          |                    |

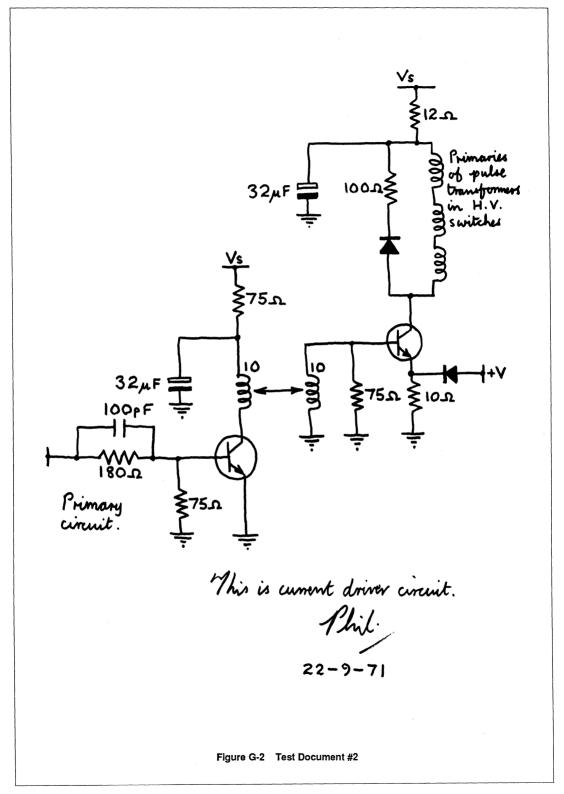

| G-1       Test Document #1         G-2       Test Document #2         G-3       Test Document #3         G-4       Test Document #4                                                                                              | G-2<br>G-3         |

| G-4 Test Document #4<br>G-5 Test Document #5                                                                                                                                                                                     |                    |

| G-6 Test Document #6                                                                                                                                                                                                             |                    |

| G-7 Test Document #7                                                                                                                                                                                                             | G-7                |

| G-8 Test Document #8                                                                                                                                                                                                             | G-8                |

| H-1 Error Recovery Flow Diagram                                                                                                                                                                                                  | H-1                |

#### LIST OF TABLES

|     | Compressor Registers                                                 |      |

|-----|----------------------------------------------------------------------|------|

|     | Summary of Standardized Parameters for Group 3 and Group 4 Equipment |      |

|     | Terminating Codes                                                    |      |

| 3-4 | Make-up Codes                                                        | .3-9 |

|     | Two-Dimensional Code Table                                           |      |

| 3-6 | Uncompressed Mode Code Words                                         | 3-17 |

#### 1.1 GENERAL DESCRIPTION

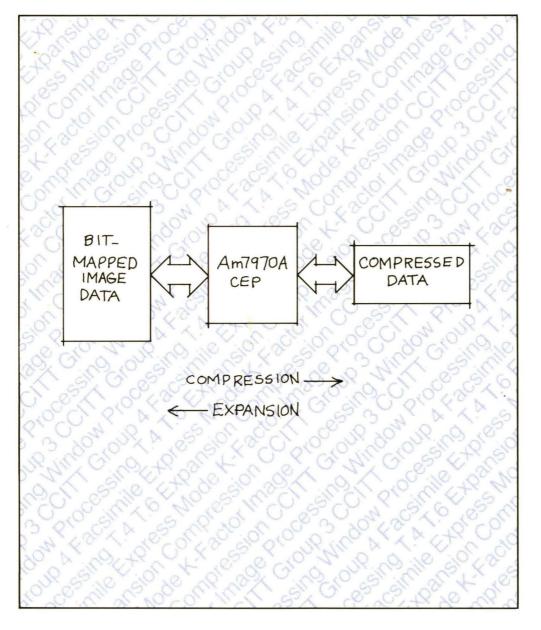

The Am7970A Compression/Expansion Processor (CEP) is a high-performance peripheral which compresses and expands two-tone bit image data in accordance with the International Telegraph and Telephone Consultative Committee (CCITT) recommendations. These image-preserving compression protocols allow highly efficient storage and transmission of two-tone pictures and documents without loss of information.

Using advanced one- and two-dimensional compression algorithms, the Am7970A is able to represent a one megabyte document in an average of 64K bytes of storage, a reduction ratio of 15:1. In many cases, the compression ratio is 30:1 and higher. In addition to the memory space saved, this compression applies the same saving to the transmission time. Thus, a document that requires 15 minutes to transmit at 9.6 kb/s requires less than one minute with compression. Typical compression of the eight CCITT test documents is 5x to 50x. The compression ratio varies with the compression mode and the amount of image detail on the document. Tables are presented in the discussion of the coding concepts to show the compression ratios that can be expected for various modes of operation.

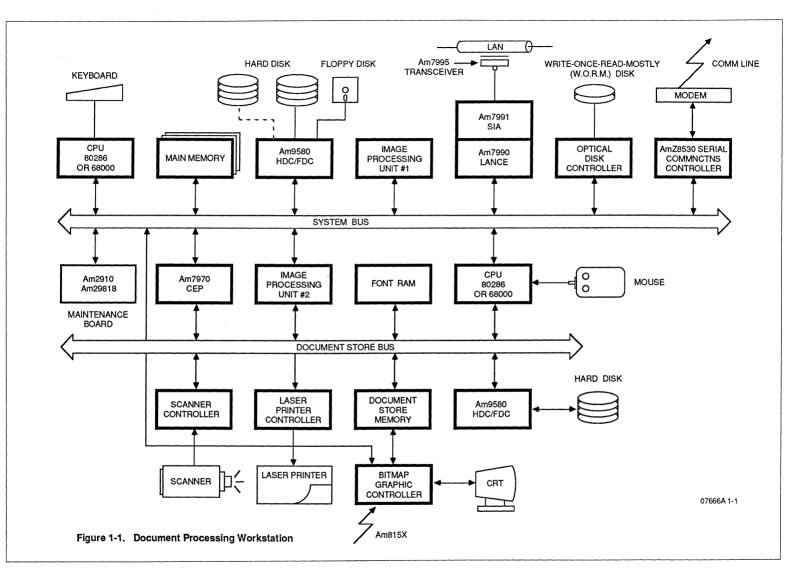

Paralleling the use of compression/decompression in the facsimile environment, there are image processing requirements in the commercial office. Generally speaking, these requirements have many similarities to those of facsimile. It is necessary to have the ability to create, capture, view, edit, print and communicate images. The communication of these images may take the form of "hard copy" (facsimile) or "display" via a CRT terminal. Further requirements of such systems are the ability to modify images in content, shape, and size, as well as, to incorporate image data with other forms of information (for instance text). Figure 1-1 shows a document processing workstation. It shows the environment in which the CEP may be used.

The CEP has a standard Am8088/8086-like microprocessor bus interface which is easily adapted to a regular microprocessor interface. CEP operation is set by programming internal control registers. CEP status is available through polled registers; exception conditions may be signaled using an external interrupt. The 42 on-

chip registers allow a simple and highly flexible system implementation. After initialization, the CEP processes data with minimal intervention by the host processor.

The Am7970A CEP includes a secondary, local Document Store bus for optional use in conjunction with the CPU bus. The local storage buffer is highly desirable within many system architectures to optimize CPU bus performance. The CEP can linearly address up to 16Mbytes of memory on each bus, for a total of 32 Mbytes. Starting address, buffer length, and current address for raw and processed data are stored within internal registers independently for both the Compressor and the Expander.

The Am7970A performs modified Huffman onedimensional coding or modified Relative Element Address Designate (READ) two-dimensional coding. This is compatible with CCITT recommendations T.4 and T.6 for Group 3 and Group 4 digital facsimile apparatus.

The Compressor and Expander, which operate in full-duplex, can be independently programmed for one-dimensional encoding/decoding, two-dimensional encoding/decoding, or transparent data transfer. In two-dimensional operation, the programmable K-Parameter defines the number of lines to be encoded in each two-dimensional coding sequence. For error-less systems (Group 4), "K = infinity" allows maximum compression by coding all lines two-dimensionally. Transparent Mode is provided to move data from one memory area to another using the DMA on the CEP.

Accelerated image processing is supported with a Compressor Express Mode which skips one line for every n lines compressed. The Expander counterpart is a Granularity Mode which duplicates the last line expanded after each n lines that are expanded. To expand the document to the same size as the original, the n value must be the same for both compression and expansion.

Document format controls include line length and margins. Line lengths or document widths of up to 16K picture elements may be selected. Programmable top, left, and right margins specify "white space" around image data, supporting both normal margin requirements and also "windowing", defined as overlaying of multiple image blocks or image blocks and character blocks.

#### 1.2 FEATURES

- Compression/Expansion of digital two-tone image data using run-length and relative coding.

- Compatible with CCITT recommendations T.4 and T.6 for Group 3 and Group 4 facsimile apparatus.

- One-Dimensional, Modified Huffman Coding with optional Wraparound Mode.

- Two-Dimensional, Modified READ Coding with programmable K-Parameter.

- General-purpose microprocessor interface.

- Optional local Document Store bus.

- On-chip, dual-bus DMA controller.

- Transparent transfer of unmodified data.

- 16-Mbyte physical addressing range on each bus.

- Programmable paper width up to 16K picture elements.

- Programmable top, left, and right margins.

- Window capability

- Optional Express Mode during compression and Granularity Mode during expansion.

- Full-duplex capability for simultaneous independent compression and expansion.

- High-performance 2 to 8 Mbps throughput with a 5-MHz clock.

The Am7970A is packaged in a 68-pin LCC or Pin Grid Array and uses a single +5 V power supply.

#### 1.3 CCITT STANDARDS

Standards for graphical data compression have been developed and agreed upon by the CCITT. These standards define the document representation. the codina alternatives. the encoding algorithms, and transmission requirements for Facsimile operation. Document definition is discussed in the next Section of this chapter. Chapter 3 is devoted to discussing coding concepts and encoding. These standards are also included as Appendix F.

The standards are divided into four groups to address various categories of equipment. Groups 1 and 2 are for old relatively slow analog equipment and are not discussed in this manual. Groups 3 and 4 provide for both one-dimensional and twodimensional digital coding, and the inclusion of uncompressed text.

The CEP (Am7970) adheres to the T.4 and T.6 standards recommendations set forth by the CCITT Group 3 and Group 4 committees, respectively. The recommendations establish compatibility among manufacturers of facsimile equipment.

The CCITT compression and expansion techniques are based on the modified Huffman and modified READ codes. In compressing the data, only the image redundancies are removed so that the image is preserved without degradation.

Group 3 (T.4) facsimile standards for document transmission specify the apparatus requirements to enable an ISO A4 document (similar to an 8 1/2 by 11 inch page) to be transmitted over a telephone-type circuit in less than one minute.

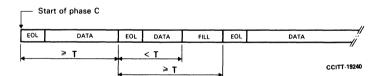

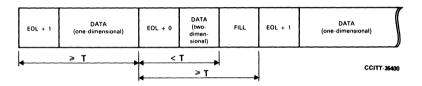

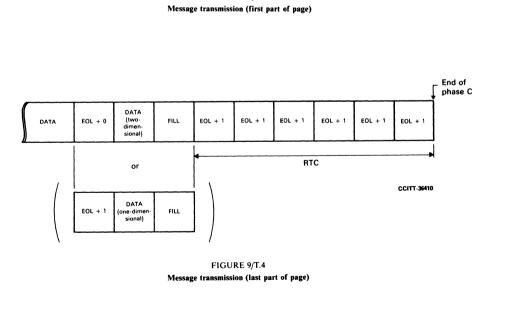

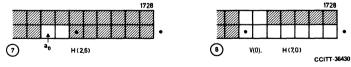

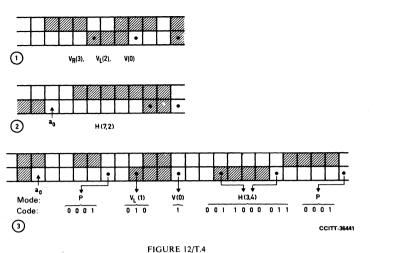

In Group 3, the total coded scan line is defined as the sum of the data bits plus any required fill bits (zeros) plus the EOL code (in one-dimensional coding). The EOL code is 00000000001. For two-dimensional coding, the scan line includes all of the above plus a tag bit to specify whether the next line is coded one-dimensionally or twodimensionally. A scan line is 1728 pixels long. Alternative optional lengths are provided as specified in detail under Document Definition.

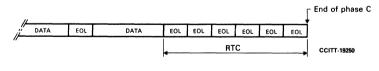

In Group 4, the total coded scan line is the sum of the data bits. Fill bits and EOLs are not used except for the last line which is terminated by a sequence of two EOLs and a pad of zeros as needed to end the document on a byte boundary. Coding formats are defined and explained in detail in Chapter 3.

The various transmission rates and communication handshakes for this equipment are specified in the CCITT recommendation T.30. This recommendation specifies modem bit rates according to V.27 for (4800/2400 bps) and/or V.29 (9600/7200 bps). T.30 also specifies V.21 (300 bps) initial interrogation between facsimile equipment to assure compatibility via a preliminary interchange of information.

The minimum transmission time of each total coded scan line is also specified in the CCITT recommendations (refer to Appendix F).

#### 1.4 DOCUMENT DEFINITION

Image data is rapidly becoming an important part of computer data storage and communication. The most common unit of image data is the document, an eight and a half by eleven inch area. This area is divided into many small areas called picture elements (pixels).

Picture elements are of uniform size and are scanned from left to right and from top to bottom as seen when viewing the document held in a vertical plane. The resolution possible is determined by the size of the picture elements. Each pixel is

<del>1</del>

represented as a single binary bit of color information or data in a document image. Therefore, colors are limited to two tones (black and white or other color pairs).

In memory, the bits representing the pixels are combined into bytes. The first pixel at the top left edge of the image must be stored as the least significant bit of the first byte in the memory buffer. This is also the first bit to be sent on a transmission line. The bits of each byte are transmitted serially. The compressed (coded) image follows the same rule. If this rule is violated, additional color changes may be created completely upsetting the compression statistics and reducing the compression ratio. There is no standardization on how a scanner has to present the data.

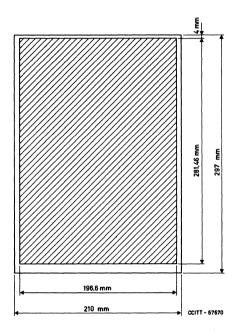

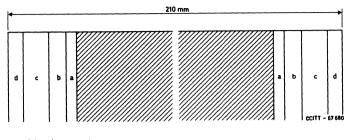

A standard scan line in a Group 4 document is 215 mm (8.46") long and contains 1728 pixels (same as Group 3). All scanning is from left to right and from top to bottom when viewing the document in a vertical plane. Optionally, the line may be 255 mm long and contain 2048 pixels or it may be 303 mm long and contain 2432 pixels.

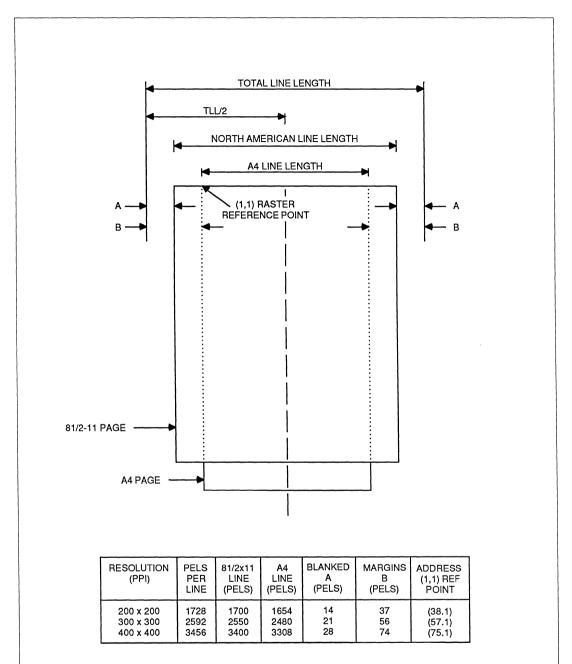

CCITT Group 4 standard sizes have been established for the pixels. There may be 200, 300, or 400 pixels per inch horizontally and from 100 to 400 pixels per inch vertically. The number of pixels per inch determines the resolution obtainable.

The Group 4 standard of 200 lines per inch means that a line containing 1728 pixels is 8.64 inches long whereas North American letter size paper is 8.5 inches wide.

In the vertical direction, the standard resolution is 100 lines/in (3.85 lines/mm) with an optional resolution of 200 lines/in (7.7 lines/mm). Resolutions of 300 and 400 lines/in. are also allowed in the vertical direction. For comparison, a television picture that is 8 1/2 inches wide and has a 4 MHz video bandwidth has a resolution of 60 to 90 pixels/in. Refer to Figure 1-2.

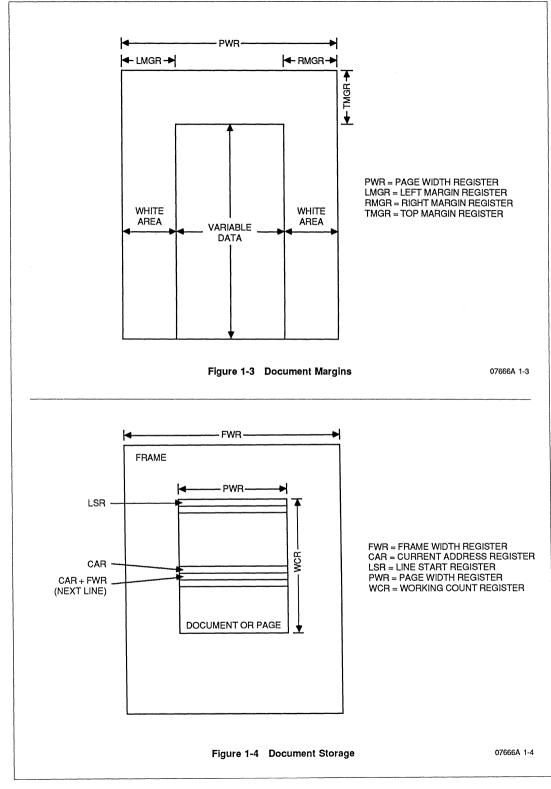

In addition to specifying the pixel size, one can also specify the left, right, and top margins. Thus, an area of information in an all white (or all black) field can be sent or stored by specifying the margins to include all of the white field above, to the left, and to the right of the image. Figure 1-3 shows the white margins that may be specified within a document.

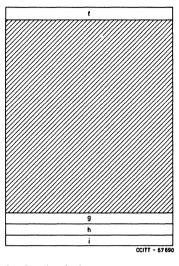

The memory used to store the document image is called a frame. It may be the same width as the document or it may be wider. Figure 1-4 shows the frame and the document or page within the frame. It shows some of the registers used to define the image area location within the frame. These registers are defined in Chapter 2.

The document is actually a window within the frame. This window may be moved within the frame by manipulating the registers defining its location. Thus, cutting and pasting of information on the display screen can be implemented efficiently.

07666A 1-2

Figure 1-2 Document Format

#### Chapter 2 FUNCTIONAL DESCRIPTION

This functional description includes the operational description, register description, and the interface description.

#### 2.1 OPERATIONAL DESCRIPTION

CEP operations consist of three phases: initialization, operation, and termination. In the first phase, the registers (compressor or expander processor) are initialized to specify and control the desired operation. In the second phase, the processing operation itself is started and performed. The final phase involves terminating the selected processor and performing any actions that are appropriate to that termination. These phases are described in detail in the following sections.

The Am7970A contains two separate buses—the System bus and Document Store bus. One DMA Controller on the CEP chip serves both buses. Therefore, DMA data transfers cannot take place on both buses at the same time. However, slave transfers can occur on the system bus while a DMA transfer is taking place on the Document Store Bus. Data transfers between the Am7970A and Main Memory take place on the System bus. Data transfers between the Am7970A and the Document Store Memory take place on the Document Store Bus.

The Am7970A processes two types of data; uncompressed or image data and coded or compressed data. Image data is stored in that portion of memory called the Image Buffer. Compressed data is stored in a portion of memory called a Code Buffer. In an Am7970A system, the Code and image Buffers are external to the CEP and each can be located in either the Main Memory or the Document Store in any combination.

Consideration should be given to the assignment of the buffers to memory. All control information exchanges between the Am7970A and the host processor take place on the System bus. Because of the high data rate of image data, it is recommended that the Image Buffer be placed in the Document Store so that it can be accessed without slowing down the CPU by contention for the DMA. For maximum performance, the Image buffer should be large enough to store one uncompressed document. The Code Buffer can be placed in the Main Memory so that the CPU can access it rapidly during transmission or reception of data. Since the compressed code is considerably smaller than the image data, it does not seriously slow down the system bus and thus impact the CPU.

The Am7970A contains registers to specify the starting address and assigned length of both the Image Buffer and the Code Buffer. The Am7970A Compressor is completely independent of the Expander. The Compressor takes image data from its Image Buffer and loads the resulting compressed data into its Code Buffer. The Am7970A Expander takes compressed data from its Code Buffer or processing and loads the resulting image data into its Image Buffer. In an Am7970A system, the Compressor can be operating from its Image and Code Buffers while the Expander is simultaneously using its own buffers.

For certain images (such as half tone), the compressed data representing a line may be longer than the original line of the image. This is called negative compression. The Am7970A checks for this condition after compressing a line and alerts the host processor via an interrupt and a status bit.

Each compressed line may be delimited by an End of Line (EOL) code according to the CCITT recommendation for Group 3 facsimile apparatus. However, this automatic EOL insertion can be suppressed by appropriate bit settings of the Am7970A (EOL=1).

The CCITT recommendation T.4 for Group 3 equipment requires that each coded line be a certain minimum length. Fill bits are added by the CEP to a shorter line when necessary to meet this requirement. The Am7970A contains a Time Fill Register to specify the minimum line lengths (including zero).

Data is vulnerable to modification by transmission errors. When erroneous data is expanded, the resulting image is very different from the original. The Am7970A checks the expanded line for the number of picture elements required by the specified paper width. If there is a discrepancy, the CPU is alerted via an interrupt. In Group 4 mode, error-free transmission is assumed.

#### 2.1.1 Initialization

The Am7970A has the following initialization requirements:

- Source Buffer definition

- Destination Buffer definition

- Attributes

- Control Parameters

These requirements are met by writing appropriate information into the 42 registers in the CEP. These registers are discussed in detail in this chapter. The following discussion is a summary of the information in these registers as it pertains to initialization. The system program should specify certain initial conditions before starting the operation of the Am7970.

#### Source Buffer Definition

A Source Buffer is defined by specifying which memory it is in (Main Memory or Document Store), the starting address, the width, and the capacity of the Source Buffer. To specify a source buffer in the Main Memory, the system program must load "0" into the CSC/ESC bit in the Compressor Master Control Register (CMCR)/Expander Master Control Register (EMCR). If a Source Buffer is located in the Document Store, the system program must load a "1" into the CSC/ESC bit. The width of the source buffer memory is stored in the Compressor Frame Width Register CFWR. The EFWR stores the width of the Expander Destination Buffer. Frame width is not applicable to data in the compressed form.

The system program must load a starting address into the Source Address Holding Registers (CSAHR, ESAHR) and the Source Current Address Registers (CSCAR, ESCAR). Also, the system program must load the negative two's complement of the length (in bytes) of the Source Buffer into the Source Count Holding Registers (CSCHR, ESCHR) and the Source Working Count Registers (CSWCR, ESWCR). Additional requirements of the Source Buffer are discussed under the specific source register sections in this chapter.

#### **Destination Buffer Definition**

The residency, the starting address, the width, and the capacity of the Destination Buffer must be An "0" in the CDC/EDC bit in the specified. specifies that the CMCR/EMCR reaister Destination Buffer is located in the Main Memory; a "1" specifies it is in the Document Store. The starting address is specified in the Destination Address Holding Registers (CDAHR, EDAHR) and Destination Current Address Registers (CDCAR, EDCAR). The width is stored in the Expander Frame Width Register EFWR. Destination buffer width is only meaningful for the Expander.

The negative two's complement of the length (in bytes) of the Destination Buffer must be loaded into the Destination Count Holding Registers (CDCHR, EDCHR) and the Destination Working Count Register (CDWCR, EDWCR). The length of the Destination Buffer has some conditions that are are discussed in detail later in this chapter. The system program should adhere to those recommendations.

#### Attributes

The system program must set the Source Attribute bit, SA, in the Parameter Registers (CPR/EPR) when the CEP is to process a new page. The Data Format Control (DFC) bits in the Parameter Register specifies the compressed data format (byte boundaries and the RTC and EOL suffix codes).

If the automatic insertion of an EOL code is required, the system program must load "0" into the EOL bit in the Compressor Parameter Register. If this bit is "1," automatic insertion of EOL is suppressed.

The system program must load "0" into the EOL bit in the Expander Parameter Register (EPR) when data with attached EOL is going to be expanded. If the data that is to be expanded contains no EOL codes (except at the end of a page), the system program must load "1" into the EOL bit in the EPR register.

The system program specifies the Wraparound, Express, and the Top, Left, and Right Margin options by loading the corresponding registers. The horizontal pixel count is specified in the Page Width Registers (CPWR, EPWR). The width of the memory buffer used to store the picture image is loaded into the Frame Width Registers (CFWR, EFWR). If window processing is used, the width of the window is stored in the Page Width register. Otherwise, the Frame Width Register and the Page Width Register have the same values.

#### **Control Parameters**

The operating mode, operation control, interrupt enable, and start/stop are loaded into the Master Control Registers (CMCR, EMCR). The operating modes are: One-dimensional, Two-dimensional, and Transparent. The K-Parameter is specified in the K-Parameter Register when Two-Dimensional processing is required. The granularity option, the G-Parameter, is specified in the Expander Parameter Register.

The GO bit combined with the OC field (bits 0, 1, and 2) in the CMCR or EMCR specify whether

compression or expansion processing or the reset operation for the compressor or expander is to be performed. If 001 is specified in bit positions 2, 1, and 0, the reset operation is executed. 101 specifies multi-line processing and 011 specifies that single-line processing is to begin. The minimum transmission time requirement is loaded into the Time Fill Register (TFLR).

A "1" in the Compressor Interrupt Enable bit (CIE) in the CMCR or in the Expander Interrupt Enable bit (EIE) in the EMCR specifies that an interrupt request is required upon CEP termination. A "0" in this location specifies that an interrupt request is not required.

Compression processing starts as soon as a "1" is loaded into the GO bit in the CMCR. Expansion processing starts as soon as a "1" is loaded into the GO bit in the EMCR.

The Restart Control Registers (CRCR, ERCR) specify whether to continue with the current values or to restore the starting values for the Source and Destination Current Address Registers, Working Count Registers, and Line Start Registers when a new processor operation is initiated.

Line Termination (LT) bits in the CPR are used to specify how many bits of terminating image to add to the end of each line after the last full byte of data. The termination bits for each line have the same value as the last bit of the last byte on that line.

All of the registers are described in detail in this chapter. The recommendations made in this chapter must be followed for initialization.

#### 2.1.2 Start Processing Procedures

The Am7970A has two different operating configurations. In the full-duplex mode, the Expander and the Compressor are operated simultaneously. In the half-duplex mode, either the Expander or the Compressor may be operated separately. A "1" in the GO bit of the CMCR initiates compression. A "1" in the GO bit of the EMCR initiates expansion. For full-duplex operation, load a "1" into the GO bit of each register.

Entire images may be compressed or expanded in one operation if the code buffer and the image buffer are both large enough to contain the entire image. In this case, each start is a start to process a new page and the system program must specify a RESET operation before each start. The reset operation flushes the internal pipeline, sets "busy" to zero, sets up the check for configuration errors, clears status and interrupt registers, and sets the GO bit to zero.

If the code buffer is not large enough during compression to contain the code for an entire image or page, the CEP will stop when the buffer is full. Then, after the coded data is saved, compression can continue without issuing a reset.

If the image buffer is not large enough during expansion to contain an entire image or page, the CEP will stop when the buffer is full. Then, after the image buffer data is saved, CEP processing is resumed without issuing a reset. Thus, compression and expansion are possible using buffers too small to store an entire page.

#### 2.1.3 How To Use The Status Registers

The CEP has three status registers: the Master Status Register (MSR), the Compressor Status Register (CSR), and the Expander Status Register (ESR). Bits 6 and 7 (EBY, CBY) in the MSR provide general status information to the CPU about both the Compressor and Expander. These bits are known as the Expander Busy (EBY) bit and the Compressor Busy (CBY) bits.

If interrupts have not been enabled, the system program should periodically poll EBY and CBY in the MSR register. If the system program is enabled to respond to an interrupt, it should test the EBY bit and the CBY bit in the MSR after a CEP interrupt occurs.

Bits 0 to 3 (EXT, ECD) in the MSR indicate whether a non-CCITT uncompressed mode entry code was detected during expansion. Bit 4 in the MSR indicates that the Expander detected an End of Page (EOP) code. If the system program requires detailed status information, it should test the CSR or the ESR directly.

#### 2.1.4 Interrupt Handling

The Am7970A will drive its interrupt line (INTR) High when the CBY bit in the CSR or the EBY bit in the ESR changes from "1" to "0" while the Compressor Interrupt Enable (CIE) bit in the CMCR or the Expander Interrupt Enable (EIE) bit in the EMCR has been set to "1." The INTR line will remain High until the MSR has been accessed by the system program. The system program may test the MSR register to distinguish Compressor interrupts from Expander interrupts. The system program should isolate the cause of the interrupt by reading the appropriate status register (CSR or ESR). Reading the status register clears the interrupt. The system program may then execute its interrupt service routine to respond to the interrupt.

#### Compressor Error Recovery Procedures

The Compressor detects several error conditions: a premature source overflow, a premature destination overflow or an illegal command. An error condition is also detected if a new command is attempted while the Compressor is busy or if negative compression occurs. A *premature* source or destination overflow is indicated by the Wraparound Incomplete (WPI) bit or the Line Processing Incomplete (LPI) bit of the Compressor Status Register (CSR).

The error recovery procedure for an LPI error must include the redefinition of the Source Buffer or the Destination Buffer as follows:

#### 1. Premature Source Overflow

#### 2. Premature Destination Overflow

where:

N = line count Hr = Horizontal resolution Apw = Actual page width

The error recovery procedure for a WPI error without an LPI error may include restarting the Source Buffer or the Destination Buffer without specifying Wraparound Restart (WRC) and/or Two-Dimensional Restart (TDC). If an illegal command is detected, the system program should load a Continue Operation into the CEP or issue a new command to the CEP when the Compressor or Expander Busy and New Operation Attempted error (COA or EOA) is detected. If negative compression is detected, the system program may load a Continue Operation command into the CEP to accept the data as is or the system program may replace the line with uncompressed data using the transparent mode in the CEP.

#### **Expander Error Recovery Procedures**

The Expander will detect several error conditions: a premature source overflow, a premature

destination overflow, an illegal command, an Expander Busy and New Operation Attempted error, a data error, or an undefined extension code. A premature source or destination overflow is indicated by the WPI bit and the LPI bit of the Expander Status Register (ESR). The error recovery procedure for a premature overflow requires that the Source Buffer and the Destination Buffer be redefined as follows:

1. Premature Source Overflow and LPI without WPI

2. Premature Destination Overflow and LPI without WPI

If the system program detects a premature overflow and the WPI error bit is set without the LPI error bit being set, the system program should restart the Source or Destination Buffer without loading the Wraparound Restart (WRC) and Two-Dimensional Restart (TDC) bit. If an illegal command is detected, the system program should load Continue Operation into the CEP or reissue a new command to the CEP when the Expander Busy and New Operation Attempted error EOA is detected.

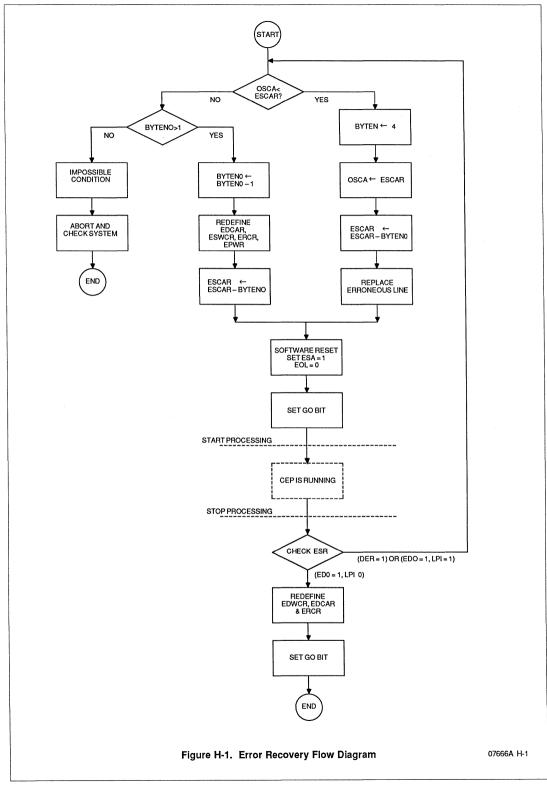

If a data error is detected, the system program should replace the error line with a copy of the previous line as follows:

```

New ESCAR = EDLSR N * Hr * Apw/8

N = EWR + 1

New ESWCR = 2's complement N * Hr * Apw/8

New EDCAR = EDLSR

New EDWCR = EDWCR - (EDCAR - EDLSR)

ERCR = All one (X'FF')

EMO and EM1 = 0 (Transparent Mode)

```

Appendix H gives additional information about expander error recovery.

#### 2.1.5 Stopping The Cep

The CEP compressor may be terminated by writing

to the Compressor Master Control Register while the CEP is busy (called a soft abort). The expander may be terminated by writing to the EMCR while the CEP is busy. The Compressor or Expander will terminate its operation as soon as the internal operation allows it. If the system program is required to stop immediately, the system program should assert the RESET input of the Am7970A. This is called a hardware stop. If the system program executes a hardware stop, the CEP will not save the current status. If the system program executes a software stop, the CEP will terminate its operation (as soon as its internal operation allows it) and keep the Compressor Busy and the New Operation Attempted (COA) or Expander Busy and New Operation Attempted (EOA) status bits: however, this is not a resumable operation.

#### 2.2 Register Description

The CPU cannot instantaneously or directly access the CEP internal registers because that would interfere with the CEP's internal operations Instead, a slave access is used to interrupt the internal microprogram. After that, all data transfers to and from the registers are performed by a microprogram. By holding READY Low, the CEP keeps the CPU waiting during this time. (The only exception is a read on the Master Status Register which is directly accessible by the CPU.)

The access time of the registers varies widely for two reasons:

- 1. The access time depends on the status of the operation that the CEP is currently performing.

- 2. Access times are optimized with respect to the probability of their usage.

The first statement means that register access time is unpredictable when the CEP is busy. This is important since the access time may be as long as 50 clock cycles. This may have an impact on system design considerations. Typical access times are:

Write Operation with CEP in Idle State:

Case 1, A single write once in a while:

4 clock cycles for all registers.

This write access is internally latched. The addressed register is loaded with the data long after the CPU is released.

Case 2, a sequence of consecutive slave write accesses:

16 clock cycles for paper width, parameter, and command registers.

14 clock cycles for all other registers.

Read Operation with CEP in Idle State:

All cases:

4 clock cycles = MSR only 10 clock cycles = status, parameter, command, and paper width registers. 12 clock cycles = all other registers.

All Operations with CEP Busy:

4 clock cycles for MSR read All other accesses take an unpredictable number of clock cycles up to 50 depending on the current operation being performed by the internal microprogram.

The block diagram for the Am7970A (CEP) is shown in Figure 2-1. Tables 2-1 and 2-2 list the Compressor and Expander registers respectively. The size and port access address of each register is listed. All CEP registers are located on even boundary addresses.  $A_0$  is completely disregarded for slave accesses.

Registers that are unique to the Compressor are discussed first. These are the Time Fill, Left Margin, Right Margin, Top Margin, and the Express Mode Registers. Then, the Master Status Register (MSR) which is common to both the Compressor and Expander, is discussed. This is followed by a discussion of pairs of registers one of which is in the Compressor and the other in the Expander starting with the Compressor Status Register and the Expander Status Register. The Compressor register is described first, and if the Expander register of the pair is different, the differences are then described. In most of these pairs of registers, the registers are identical. The registers are discussed in the order presented in the Compressor register table.

After initialization by the RESET input, the state of the Status Register, Master Status Register, and GO bits are "0", the status of other bits is not specified.

#### 2.2.1 Time Fill Register (TFLR)

The Time Fill Register, an 8-bit Compressor register, specifies the minimum length of a coded line expressed in bytes. If the compressed line has fewer bytes than this number, time fill bits must be added to meet this requirement. Time fill bits are simply all "0"s. Refer to Figure 2-2.

#### Table 2-1. Compressor Registers

| Abbr. | Name                                               | Size<br>(bits) | No. of<br>Bytes | Port Address(es)     |

|-------|----------------------------------------------------|----------------|-----------------|----------------------|

| TFLR  | Time Fill Register                                 | 8              | 1               | 44                   |

| LMGR  | Left Margin Register                               | 16             | 2               | 40 (LSB)/42 (MSB)    |

| RMGR  | Right Margin Register                              | 16             | 2               | 60 (LSB)/62 (MSB)    |

| TMGR  | Top Margin Register                                | 16             | 2               | 30 (LSB)/32 (MSB)    |

| CER   | Compressor Express Register                        | 8              | 1               | 68                   |