# Am2969

#### Memory Timing Controller with EDC Timing Control

#### **PRELIMINARY**

#### DISTINCTIVE CHARACTERISTICS

- Provides complete timing control for memory systems using 64K, 256K, 1M, or 4M DRAMs and AMD's Dynamic Memory Support chip set

- Interfaces directly with all 16-bit processors and supports most 32-bit processors

- Performs memory initialization (DRAMs up to 1M, including 1M x 4)

- WE output directly drives up to 88 DRAMs

- Arbitrates between refresh requests and memory access requests

- Refresh support: 128, 256, or 512 cycle burst refresh, distributed, scrubbing, automatic, or hidden modes

- · Refresh control: internal or external

- On-chip interval timer for automatic refresh

- Synchronous or asynchronous arbitration of memory cycles

- Supports bus-retry

- On-chip interrupt logic

- Supports word, long-word, and byte operations

- Controls AMD's Memory Support chip set to perform AMD's patented Scrubbing Refresh/EDC cycle

#### **GENERAL DESCRIPTION**

The Am2969 is a high-performance enhanced memory timing controller (MTC) that provides the timing control in AMD's Dynamic Memory Support chip set. The Am2969 MTC replaces much of the "glue" logic necessary in DRAM systems by generating all control signals for the Am2968A/Am29368 Dynamic Memory Controllers, Am2961/Am2960 Multiple EDC Bus Buffers, and the Am2960/Am2960A Error Detection and Correction Units. It manages Dynamic RAM access and refresh, processor interface, and error detection and correction (EDC) processes for the CPU. The chip can be configured for word, long-word, and byte operations (including the data controls for byte write with error correction).

The Am2969 coordinates the timing and control signals needed for a processor and memory to function interactively as a meaningful part of a computer system. The MTC chip takes advantage of AMD's "building block" approach by drawing on the Am2971 Programmable Event Generator (PEG™) chip as its timing reference. By using the PEG (or a delay line) the user can tailor the system to provide precise

timing, maximize system performance, and achieve greater design flexibility.

The Am2969 also provides an internal refresh interval timer to generate refresh requests independent of the CPU (distributed refreshes). This frees up valuable CPU time and makes the Dynamic RAM appear static. It also guarantees proper refresh timing under all combinations of CPU and DMA requests.

Additionally, the Am2969 acts as the arbiter between memory refresh requests and CPU Read/Write requests. Arbitration can be for either synchronous or asynchronous memory cycles. The chip also performs memory initialization, controls various timing and data flows, and handshakes with the CPU.

Other operations of the Am2969 include bus-retry, on-chip interrupt logic, and facilities for interfacing with a wide range of microprocessors. A single Am2969 can support the timing requirements for all 16-bit systems and most 32-bit systems.

#### **RELATED AMD PRODUCTS**

| Part No.   | Description                                              |

|------------|----------------------------------------------------------|

| Am29368    | Dynamic Memory Controller for 1M DRAMs                   |

| Am2960/A   | 16-Bit Error Detection and Correction Units              |

| Am29C60/A  | CMOS 16-Bit Error Detection and Correction Units         |

| Am2961     | Inverting EDC Multiple Bus Buffer                        |

| Am2962     | Non-Inverting EDC Multiple Bus Buffer                    |

| Am2968A    | Dynamic Memory Controller for 256K DRAMs                 |

| Am2970     | Memory Timing Controller (without EDC Control)           |

| Am2971/71A | Programmable Event Generators (PEG)                      |

| Am29827/28 | Non-Inverting High-Performance Three-State Buffers       |

| Am29845    | Inverting High-Performance Octal Bus Interface Latch     |

| Am29846    | Non-Inverting High-Performance Octal Bus Interface Latch |

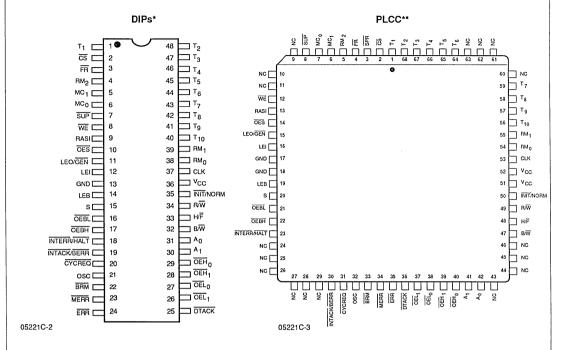

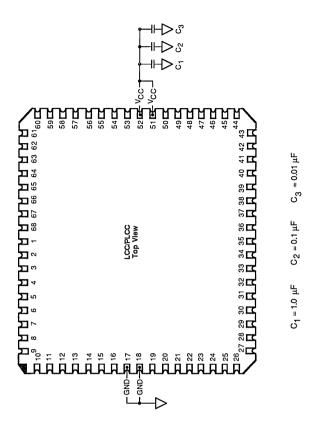

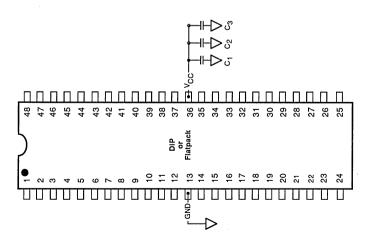

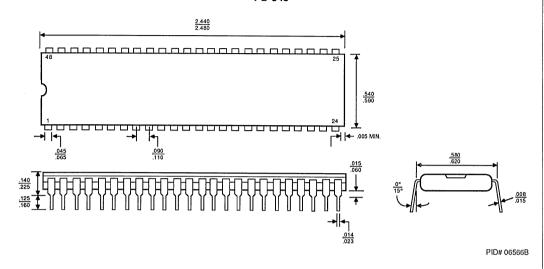

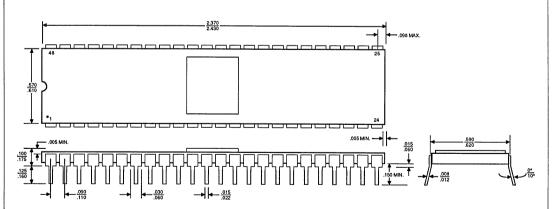

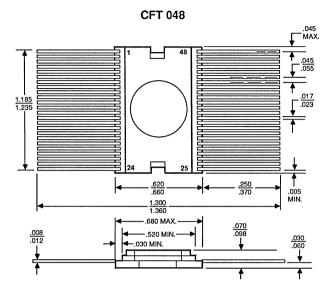

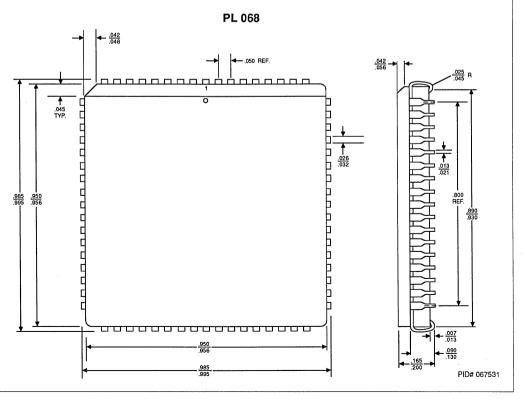

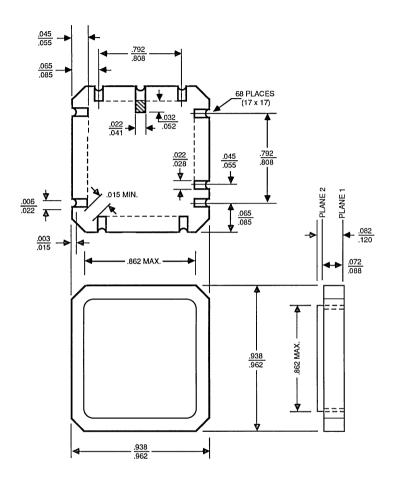

#### **CONNECTION DIAGRAMS**

Top View

Note: Pin 1 is marked for orientation.

- \* Also available in 48-pin Flatpack; pinout is identical to DIPs.

- \*\* Also available in 68-pin LCC; pinout is identical to PLCC.

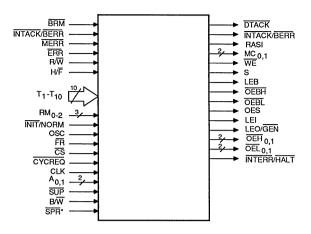

#### LOGIC SYMBOL

05221C-4

## Package and Chip Information

Die Size: 0.199" x 0.153" Gate Count: 450

| Parameter       | Ceramic<br>DIP | Plastic<br>DIP | Ceramic<br>LCC | Plastic<br>LCC | Ceramic<br>Flatpack | Unit |

|-----------------|----------------|----------------|----------------|----------------|---------------------|------|

| $\theta_{JA}$   | 37             | 55             | 31             | 35             | _                   | °C/W |

| θ <sub>JC</sub> | 10             | NA             | 6              | NA             | _                   | °C/W |

<sup>\*</sup>The function \$\overline{SPR}\$ is available as a pin on the surface-mount packages only. To implement this function in other packages, refer to the Functional Description.

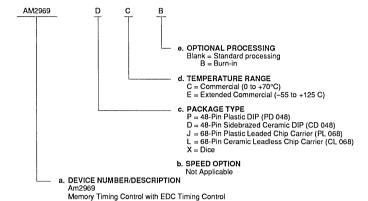

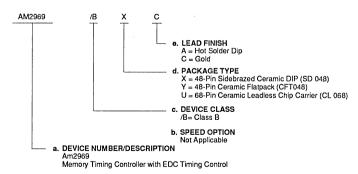

#### ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

d. Temperature Range

e. Optional Processing

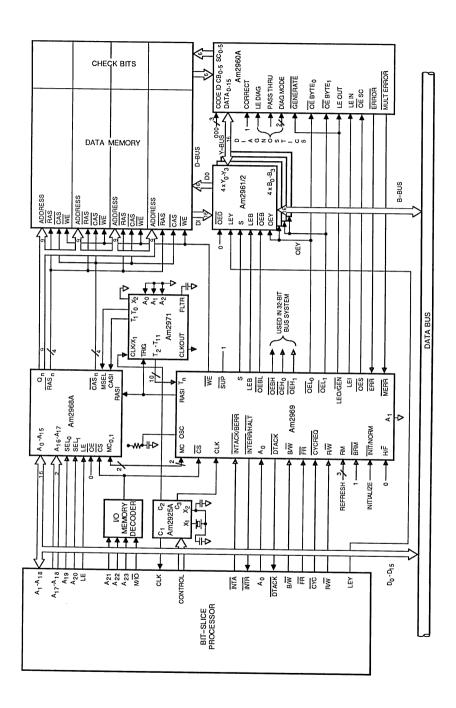

#### Valid Combinations

| Valid Combinations |                                                          |  |

|--------------------|----------------------------------------------------------|--|

| AM2969             | PC, PCB, DC,<br>DCB, JC, JCB,<br>LC, LCB, XC,<br>DE, DEB |  |

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### MILITARY ORDERING INFORMATION

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- Device Class

- d. Package Type

- Lead Finish Θ.

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released valid combinations.

#### **Group A Tests**

Group A tests consist of subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### PIN DESCRIPTION

#### A. Address Bits 0 and 1 (Inputs)

These are the two least significant bits of the CPU address. They are used to control byte and 16-bit word and 32-bit long-word operations. A<sub>o</sub> and A<sub>o</sub> are latched on the HIGH-to-LOW transition of CYCREQ.

#### BRM Bus Retry Mode (Input: Active LOW)

When this input is LOW, the Am2969 enters the Bus Retry Mode. In this mode, the INTERR and INTACK pins assume the HALT and BERR functions, respectively. This input should be tied HIGH if the processor does not support bus retry.

#### B/W Byte/Word (Input)

This input indicates a byte write operation is to be performed when HIGH and a word write operation when LOW. This signal is a "Don't Care" during read cycles.

#### CLK Clock (Input)

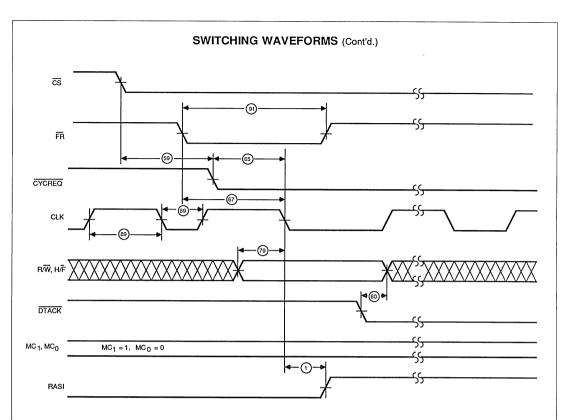

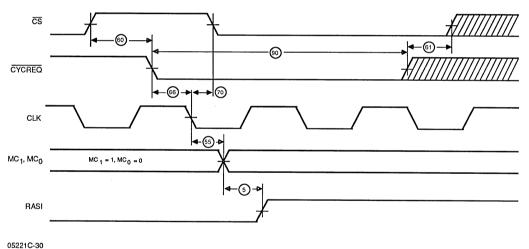

For systems requiring synchronous arbitration of memory access and refresh requests, this input receives the system clock. The falling edge of CLK causes RASI to go HIGH and  $\mathrm{MC}_{0,1}$  to switch. For asynchronous arbitration, this input must be tied HIGH.

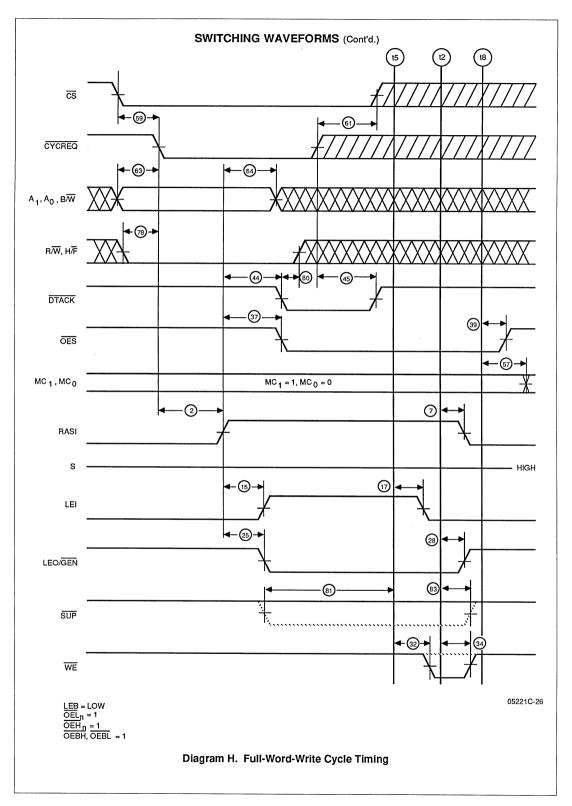

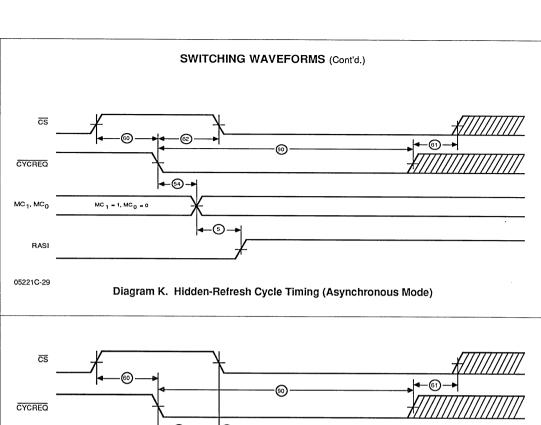

#### CS Chip Select (Input; Active LOW)

When  $\overline{CS}$  is LOW, the MTC is enabled. A memory read/write cycle can only be performed when  $\overline{CS}$  is active. Refresh cycles occur independent of  $\overline{CS}$ . When  $\overline{CS}$  is HIGH, all memory requests (HIGH-to-LOW transitions of  $\overline{CYCREQ}$ ) will be interpreted as refresh requests ("Hidden" refresh).

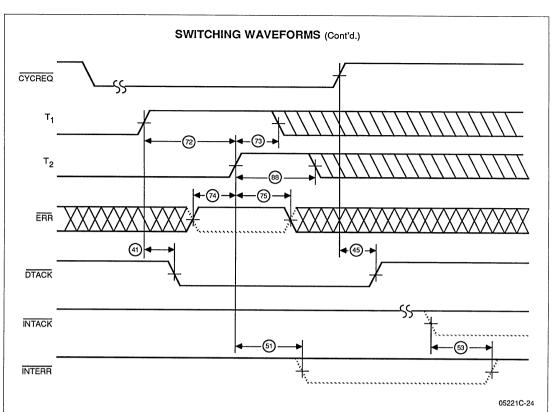

#### CYCREQ Cycle Request (Input; Active LOW)

When  $\overline{\text{CS}}$  is LOW, this input will generate an internal memory request for the Am2969 on a HIGH-to-LOW transition. When  $\overline{\text{CS}}$  is HIGH, a HIGH-to-LOW transition of  $\overline{\text{CYCREQ}}$  will generate a hidden refresh request.

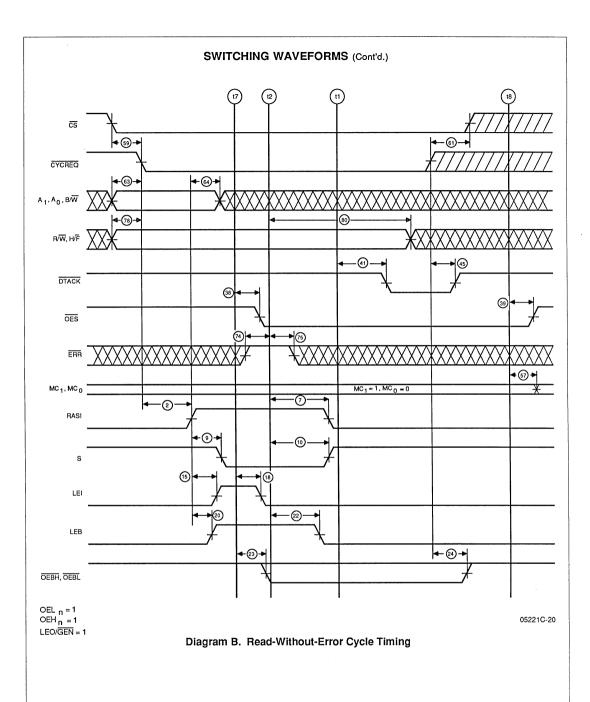

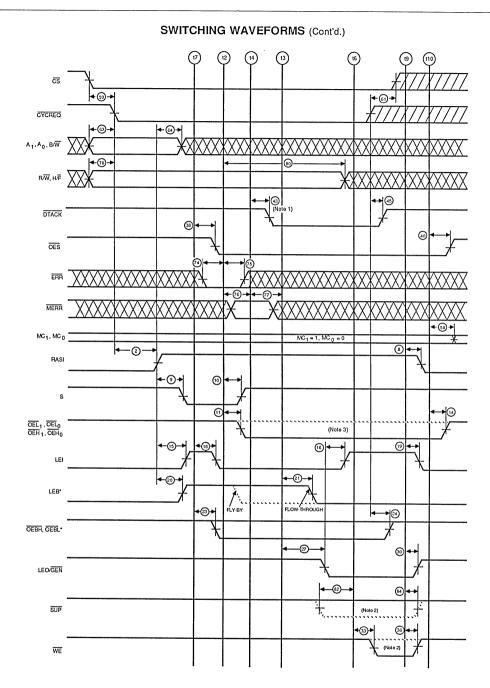

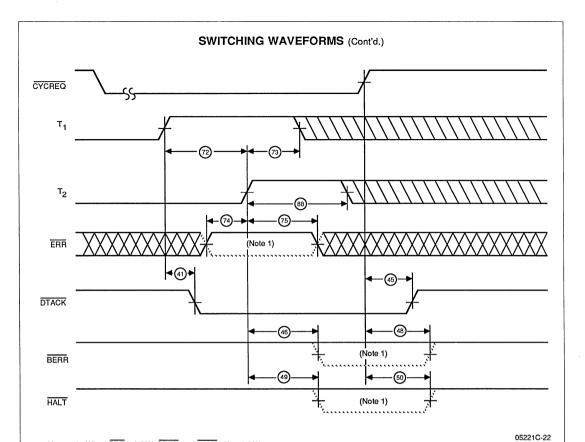

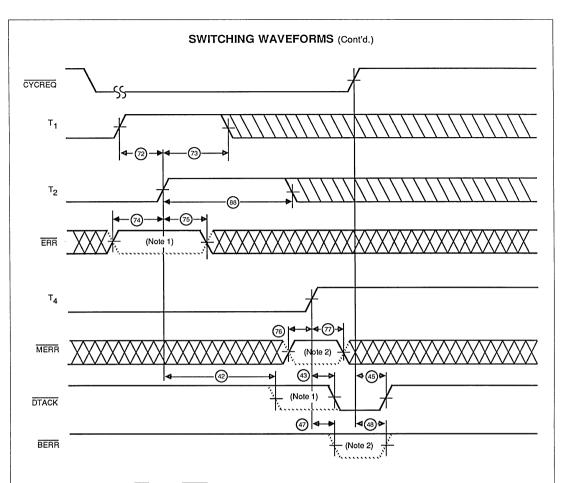

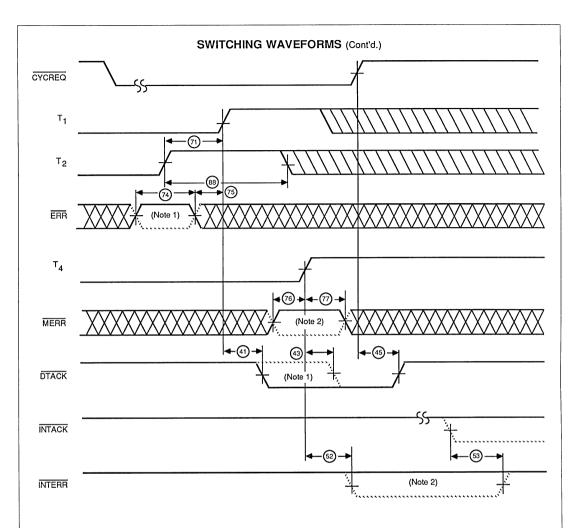

# DTACK Data Transfer Acknowledge (Output; Open Collector, Active LOW)

The HIGH-to-LOW transition of DTACK informs the CPU that a write cycle has begun, or that data will be on the system bus at the correct time during a read cycle. The time at which DTACK occurs is set at T, or T,.

#### ERR Error (Input; Active LOW)

When this signal goes LOW, it indicates that an error has occurred on a read cycle. This input should be connected to the ERR output of the EDC unit. This input is sampled at the rising edge of T<sub>a</sub>.

#### FR Forced Refresh (Input; Active LOW)

This input is used to force a refresh cycle at userdesignated times. The falling edge of FR latches an internal refresh request. If the memory is busy, the refresh is done at the completion of the current cycle.

#### GND +0-V Ground Reference

Refer to the connection diagrams for placement and number of GND pins. Refer to the Functional Description for information on proper decoupling.

#### H/F Half/Full (Input)

This input indicates the relative size of the system bus with respect to the memory bus. It is HIGH if the system bus is half the memory bus width, and LOW if the system bus width is equal to the memory bus width.

# INTACK/BERR Interrupt

Interrupt Acknowledge/Bus Error (Input; Active LOW/Output; Active LOW, Open Collector)

When INTACK goes LOW, it will reset the Interrupt Request (INTERR) output on the Am2969. In the Bus Retry Mode (BRM = LOW), this pin will act as the BUS ERROR output.

## INTERR/HALT

Interrupt Error/Halt (Output; Active LOW, Open Collector/Output; Active LOW, Open Collector)

When  $\overline{BRM}$  = HIGH, this output interrupts the processor if a single-bit error is detected in the Fly-By Mode or if a multiple-bit error is detected in the Flow-Thru Mode. CAUTION: If  $T_4$  occurs before  $\overline{INTACK}$ ,  $\overline{INTERR}$  will be reset by  $T_4$ . When  $\overline{BRM}$  = LOW, this pin is defined as  $\overline{HALT}$ . This is called Bus-Retry Mode, and the Am2969 will request the last cycle to be rerun by asserting a  $\overline{BERR}$  and  $\overline{HALT}$  simultaneously if a single-bit error occurs. If a multiple-bit error occurs, only  $\overline{BERR}$  will be asserted.

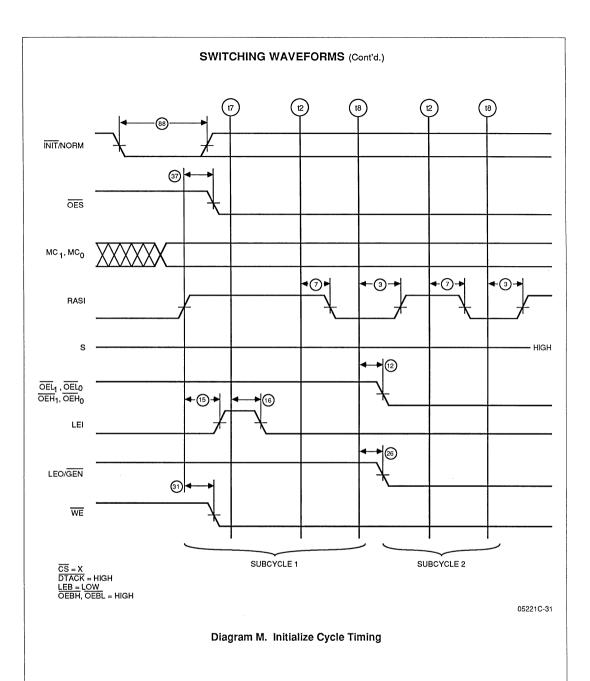

#### INIT/NORM Inititalize/Normal (Input)

When the Am2969 detects a falling edge on this input, it will enter the initialize mode of operation. This allows the memory to be initialized easily with a minimum of CPU overhead. When this input is HIGH, normal Read/Write and refresh cycles may be performed.

#### LEB Latch Enable Buffer (Output; Active HIGH)

This output is intended to be connected to the LEB input of the Am2961/Am2962 EDC Bus Buffers. It controls the latching of data going from the EDC Bus Buffers to the system bus. When LEB is HIGH, the latch is transparent; when LOW, the data is latched.

#### LEI Latch Enable In (Output; Active HIGH)

This output should be connected to the LEI input of the Am2960/Am2960A EDC Unit. It controls the latching of data (data and check bits) into the EDC unit. The latch is transparent when LEI is HIGH, and the data is latched in when LEI is LOW.

#### LEO/GEN Latch Enable Out/Generate (Output)

This output is intended to be connected to the LEO and GEN inputs of the Am2960/Am2960A EDC Unit. LEO OUT controls the latching of corrected data from the EDC unit into its output latch. GEN instructs the Am2960/Am2960A to generate check bits for the data in its input latch. When LEO/GEN is HIGH, the latch is transparent; when LOW, data is latched and the EDC unit goes into the Check Bit Generation Mode.

#### MC<sub>0.1</sub> Mode Control Bits 0 and 1 (Outputs: Active

These outputs are connected to the MC<sub>0.1</sub> inputs of the Am2968A/Am29368 DMC. They indicate the type of memory cycle to be performed. Possible combinations and mode descriptions appear in the Functional Description in Table 1.

#### MERR Multiple Error (Input; Active LOW)

This input identifies that a multiple error has been detected by the EDC unit. This input should be connected to the MERR (multiple error) output of the Am2960/ Am2960A.

#### OEBH, OEBL Output Enable Bus HIGH/LOW (Outputs: Active LOW)

These outputs are used when interfacing to a system bus, which can be either the same width as memory or half the width. They control the multiplexing of half-words onto the system bus from the EDC Bus Buffers. OEBH and OEBL are enabled as shown in Table 5 of the Functional Description. These outputs are to be connected to the appropriate OEB inputs of the Am2961/ Am2962. When they are HIGH, the system bus outputs of the Am2961/Am2962 are in the high-impedance state. When LOW, the Am2961/Am2962 system bus outputs are enabled.

#### OEH, OEL, Output Enable HIGH/LOW (Outputs; Active LOW)

These signals are used to select the appropriate output(s) from the EDC Bus Buffers and EDC Unit(s) on the Y-bus, when performing either byte writes or word writes when H/F is HIGH. A<sub>0,1</sub> are decoded so that the selected byte or word may be written into memory. These signals are intended to be connected to the corresponding OE Byte inputs of the Am2960/Am2960A and OEY inputs of the Am2961/Am2962. Table 3 of the Functional Description shows how these outputs are enabled.

#### OES Output Enable Syndromes (Output; Active

This output is intended to be connected to the OE SC input of the Am2960/Am2960A EDC Unit. It controls the feedback of the syndrome bits in the 32-bit mode.

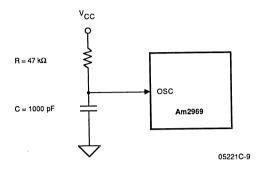

#### OSC Oscillator (Input)

The oscillator input signal is used to generate an internal refresh clock. It is this oscillator which initiates a refresh cycle if FR does not go active. The OSC signal comes from external components (illustrated in Figure 5 of the Functional Description).

#### RASI Row Address Strobe Input (Output: Active

This output is connected to the RASI input of the Am2968A/Am29368 DMC. It is used to start a memory access for the DMC. The RASI output is also connected to the TRIG input of the PEG or to a delay line to start the timing sequence. The rising edge of RASI initiates the memory access for the DMC, and the leading edge initiates the PEG (or delay line).

RM<sub>e.2</sub> Refresh Mode (inputs)

These inputs control the type of refresh cycle that the Am2969 will initiate. Table 4 of the Functional Description provides the valid input combinations and the resulting refresh mode selection.

#### R/W Read/Write (Input)

This input indicates a memory read request when HIGH. and a write request when LOW.

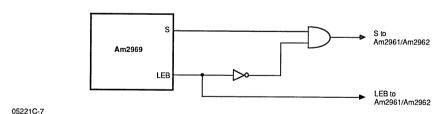

#### Select (Output)

The S output should be connected to the S input of the Am2961/Am2962 EDC Bus Buffers. It controls the source of data for the Am2960/Am2960A EDC Unit. When HIGH, data comes from the system bus; when LOW, data comes from the memory. Refer to Figure 3 of the Functional Description for a detailed description of the interface between the Am2969 and the Am2961/ Am2962 in the Fly-By mode.

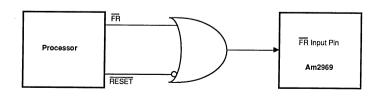

#### System Power-up Reset (Input; ActiveLOW)

SPR is an active-LOW signal and connects to the system RESET from the host processor. When the FR signal is HIGH, the HIGH-to-LOW edge for SPR causes a forced refresh request to occur. Once the SPR signal has gone LOW, all refresh requests made with the FR signal will be disabled. SPR must be kept LOW until FR can be guaranteed to be HIGH. This pin is available only on the surfacemount packages. To implement the function in a DIP or Flatpack package, refer to Figure 4 of the Functional Description.

#### SUP Suppress (Input; Active LOW)

When SUP is driven LOW, it will inhibit access to memory by disabling WE. It can be used to prevent illegal access in memory-access-protected systems.

#### Timing Taps (Inputs)

T<sub>1-10</sub> Timing Taps (inputs)

These inputs are positive-edge triggered timing tap outputs from the timing reference generator (PEG or delay line). They provide the necessary timing information for the Am2969 to control the sequence of events in any given cycle. Since T, is also sampled by T2, it must meet appropriate setup and hold times relative to T<sub>2</sub>. Definition of the ten timing taps is given in Table 2 of the Functional Description. The numbers T,-T, have no implication to the order in which they are used with the exceptions of T<sub>21</sub>  $T_{e}$ ,  $T_{g}$ , and  $T_{to}$ , which must appear in that order.

#### +5-V Positive Power Supply (Input)

Refer to the connection diagram for placement and number of V<sub>cc</sub> pins. Refer to the Functional Description for information on proper decoupling,

#### WE Write Enable (Output; Active LOW)

When WE is LOW, it causes data to be written into memory. WE is inhibited if SUP is LOW, or if a multiple error is encountered during a read-modify-write cycle.

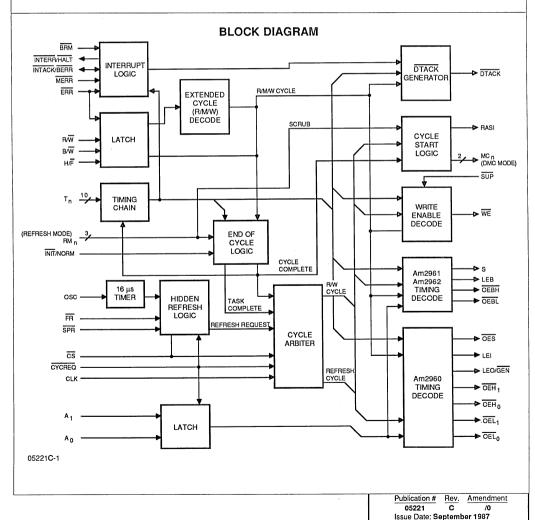

#### **FUNCTIONAL DESCRIPTION**

The functional description of the Am2969 is divided into several major sections to best explain the full function of the device. These sections are:

- Am2969 Chip-to-Chip Signals (beginning with a system overview)

- · Am2969 Chip Operating Modes

- Am2969 System Operating Modes

#### System Overview

The AMD approach to memory system design provides the designer with flexibility. AMD's building block approach separates system functions onto separate chips. These functions include Dynamic Memory Control, Memory Timing Control, Error Detection and Correction, and System Timing Generation. In this way, a designer can select the functionality and determine the performance to meet the system requirements.

The Am2969 is the building block which performs memory timing control in DRAM systems which use Error Detection and Correction. Its two main functions are to:

- Generate all control timing signals for an EDC memory system, and

- Perform arbitration between memory read/write accesses and refresh accesses.

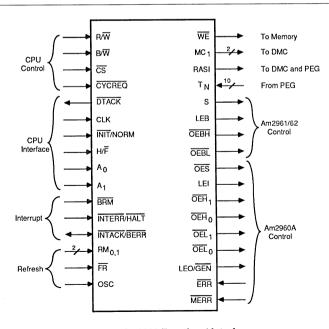

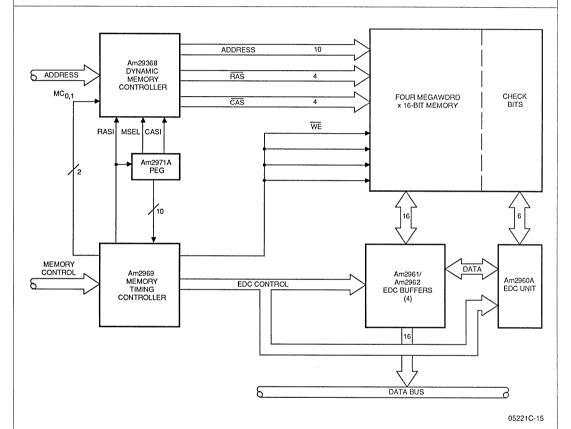

A DRAM system is shown in Figure 2 (a simplified diagram appears in the Applications section of this data sheet). Using this diagram, the reader can follow the chain of events through the chip set. In general terms, the processor will begin an event sequence by generating a cycle request. This input signal, CYCREQ, will cause the Am2969 to generate the RASI signal which in turn acts as the "trigger" to the system timing generator. In AMD's approach to system design, this could be the Am2971 Programmable Event Generator or a delay line of desired resolution. The system timing generator will initiate the timing sequences between chips at the desired system resolution, and therefore performance is user-definable.

The generated timing signals are defined as timing taps. The functional description of each tap is defined in Table 2. These taps, which are fed into the Am2969 and the DMC (Am2968A or Am29368) control the time at which the various control signals are generated by the Am2969. Control signals will vary depending upon which type of cycle has been requested (refresh, read, write, read-modify-write, etc.).

TABLE 1. MODE CONTROL SELECTION

| MC, | MC <sub>o</sub> | Mode                                        |

|-----|-----------------|---------------------------------------------|

| 0   | 0               | Refresh without Scrubbing                   |

| 0   | 1               | Refresh with Scrubbing or Memory Initialize |

| 1   | 0               | Read/Write                                  |

| 1   | 1               | Clear Refresh Counter                       |

## TABLE 2. TIMING TAP DEFINITIONS

| Tap No. | Description/Function                                                                                                                                                                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Controls when DTACK will go active during Fly-By, Flow-Thru with error, and first Bus-Retry cycles.                                                                                                                                                                                    |

| 2       | Identifies when the ERR flag is sampled during a read cycle. This timing tap controls the end of RASI for read, full-word-write, initialize, and read-without-scrubbing cycles.                                                                                                        |

| 3       | Indicates corrected data at the output of the EDC circuit during a read cycle (with a single-bit error) and partial-word-write cycles. Switches the EDC unit from check to generate mode. Latches data into the EDC in the Flow-Thru mode.                                             |

| 4       | Controls when $\overline{\text{DTACK}}$ will go active during read/modify/write cycles. Identifies when $\overline{\text{MERR}}$ is sampled.                                                                                                                                           |

| 5       | Asserts WE in full-word-write cycles and latches data into EDC circuit by making LEI LOW. Check bits and data must be valid at this time.                                                                                                                                              |

| 6       | Indicates when WE becomes active during read/modify/write cycles. At this time, corrected data and check bits must be available on the memory bus. Also applies to refresh-with-scrubbing cycles.                                                                                      |

| 7       | Indicates that valid memory data is available at inputs of EDC unit during all read cycles, partial-word-write cycles, and refresh-with-scrubbing cycles.                                                                                                                              |

| 8       | Identifies when a new memory cycle may begin after a read-without-error, full-word-write, initialize, or refresh-without-scrubbing cycle (includes precharge time). This timing tap is the End of Cycle for read-without-error, full-word-write, and refresh-without-scrubbing cycles. |

| 9       | Controls the end of RASI (RASI going HIGH to LOW) for read/modify/write cycles. Also applies to refresh-with-scrubbing cycles.                                                                                                                                                         |

| 10      | Identifies when a new memory cycle may begin after a read/modify/write cycle has been performed (includes precharge time). Also applies to refresh-with-scrubbing cycles.                                                                                                              |

#### System Interface

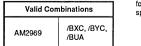

The following section of the functional description deals with the interface of the Am2969 to the rest of the chip set. Figure 1 provides a grouping of the Am2969 signals by function or chip interface. For additional reference, a detailed chip-to-chip interconnect diagram is shown in Figure 2.

#### Am2969 to DMC Interface

The Am2969 will control the type of mode that the DMC — either the Am2968A for systems using 256K x 1 or 256K x 4 DRAMs, or the Am29368 for systems using 1M x 1 or 1M x 4 DRAMs — will enter. The mode control signals (MC\_n) direct the DMC as to which type of cycle to perform. Mode Control functions are given in Table 1. In addition to the Mode Control signals, the RASI signal from the Am2969 acts as an input to the DMC. It initiates the selected cycle sequence for proper DMC control of the address path and generation of the RAS and  $\overline{\text{CAS}}$  signals to the DRAM array.

#### Am2969 to System Timing Generator Interface

The Am2969 generates a RASI signal after receiving a CYCREQ from the processor. In addition to the RASI signal going to the DMC, it also becomes an input to the system timing generator. The Am2971 PEG or a delay line, after being triggered by this RASI signal, will generate 12 timing taps. These taps, which are defined in Table 2, are fed back into the chip set to initiate the sequence of events. Ten of these taps are fed into the Am2969 at the user-defined time during the cycle operation, and control the output signals of the Am2969 dependent upon the type of cycle which has been started.

#### Am2969 to DRAM Array Interface

The Am2969 has only one signal which interfaces directly to the DRAM array. This signal,  $\overline{WE}$ , is capable of driving up to a 500-pF load and requires no external drivers or damping resistors.  $\overline{WE}$  is disabled when  $\overline{SUP}$  is used to prevent illegal memory accesses in an access-protected memory system. The  $\overline{WE}$  is also inhibited during a read/modify/write cycle if a multiple-error has been detected by the EDC circuit.

#### Am2969 to Processor Interface

The Am2969 is a general-purpose memory timing controller designed to interface with most processors. Two main handshake signals are used between the processor and the memory system.  $\overrightarrow{CYCREQ}$  is the request by the processor to the Am2969 to initiate a memory cycle.  $\overrightarrow{DTACK}$  is the acknowledgment sent to the processor by the Am2969 to indicate that a memory cycle is in progress. Several other signals are used to specify handling of bytes of data. These signals are used to specify handling of bytes of data. These signals are decoded using these inputs and also shows the decoding for half- and full-word enables using the A $_1$  and H/F signals. Under most conditions, several address signals are used by the processor to generate the chip select signal ( $\overrightarrow{CS}$ ). The Read/Write signal (R/W) from the processor is used to control read and write cycles of operation.

Other miscellaneous processor signals include an Initialize/ Normal signal for initialization of the DRAM array, and a Forced Refresh signal for performing refreshes controlled external to the Am2969. All refresh modes can be chosen by hardwiring the three Refresh Mode input lines as indicated in Table 4.

Figure 1. Am2969 Functional Interface

Figure 2. Detailed Chip Hook-Up

The INTERR signal interrupts the CPU when an error occurs, and the INTACK signal from the CPU acknowledges the interrupt.

When interfacing with the Motorola family of microprocessors, or newer generations of microprocessors such as the 80386 or the Am29000, the bus retry feature can be conveniently

used with the BRM input hardwired LOW. BERR and HALT signals are asserted simultaneously to indicate an error to the CPU. Under these conditions, the processor will cause the Am2969 to repeat the previous cycle, thus allowing for the correction of the error. This mode minimizes overhead and maximizes performance for CPUs that support this feature.

TABLE 3. OUTPUT ENABLE TRUTH TABLE

| H/F | B/W | A, | A <sub>o</sub> | OEH, | OEH <sub>₀</sub> | OEL, | OEL, | Cycle Type                            |

|-----|-----|----|----------------|------|------------------|------|------|---------------------------------------|

| 0   | 0   | 0  | 0              | 1    | 1                | 1    | 1    | Long-Word Write for 32-bit systems or |

| 0   | 0   | 0  | 1              | 1    | 1                | 1    | 1    | Word Write for 16-bit systems         |

| 0   | 0   | 1  | 0              | 1    | 1                | 1    | 1    |                                       |

| 0   | 0   | 1  | 1              | 1    | 1                | 1    | 1    |                                       |

| Х   | 1   | 0  | 0              | 0    | 0                | 0    | 1    | Byte Write                            |

| х   | 1   | 0  | 1              | 0    | 0                | 1    | 0    | ·                                     |

| x   | 1   | 1  | 0              | 0    | 1                | 0    | 0    |                                       |

| ×   | 1   | 1  | 1              | 1    | 0                | 0    | 0    |                                       |

| 1   | 0   | 0  | х              | 0    | 0                | 1    | 1    | Word Write for 32-bit systems         |

| 1   | 0   | 1  | х              | 1    | 1                | 0    | 0    | ·                                     |

| х   | х   | х  | х              | 0    | 0                | 0    | 0    | Read with Error                       |

| х   | х   | Х  | х              | 1    | 1                | 1    | 1    | Read without Error                    |

Key: X = Don't Care

TABLE 4. REFRESH MODE SELECT TABLE

| RM <sub>2</sub> | RM, | RM₀ | Refresh Mode                  |

|-----------------|-----|-----|-------------------------------|

| 0               | 0   | 0   | Non-Scrubbing/Non-Burst       |

| 0               | 0   | 1   | Non-Scrubbing/128-Cycle Burst |

| 0               | 1   | 0   | Non-Scrubbing/256-Cycle Burst |

| 0               | 1   | 1   | Non-Scrubbing/512-Cycle Burst |

| 1               | 0   | 0   | Scrubbing/Non-Burst           |

| 1               | 0   | 1   | Scrubbing/128-Cycle Burst     |

| 1               | 1   | 0   | Scrubbing/256-Cycle Burst     |

| 1               | 1   | 1   | Scrubbing/512-Cycle Burst     |

#### Am2969 to EDC Interface

The Am2969 also acts as the timing controller for the Am2960 family of EDC circuits and the Am2961/62 EDC Bus Buffers. These direct connections are shown in Figure 2. The ERR signal indicates the occurrence of a single-bit error in the DRAM array. If a double-bit (or multiple-bit) error is detected. both the ERR and MERR signals are activated. The LEI, LEO, and OE Byte signals are the data-latch and output enablecontrol signals. These control signals are generated at userspecified times during the different cycles. The GEN signal is used to generate the check-bits in the EDC circuit when in the generate mode. The OEL, OEL, OEH, and OEH, signals are used to enable the different bytes during byte operations. These signals connect to both the EDC circuit and to the EDC Bus Buffers to control the flow of data on the Y-Bus. The Y-Bus connects the EDC unit and the EDC Bus Buffers. When the OEL\_/OEH\_ control signals go LOW, the data flow is from the EDC circuit into the Bus Buffers along the Y-Bus. When HIGH, the data flows along the Y-Bus from the Bus Buffers into the EDC circuit. OEL OEH are connected to the OEY inputs of the Bus Buffers, and OE, Byte 0, 1 of the EDC circuit. The details of signal decoding are shown in Table 3.

#### Am2969 to EDC Bus Buffers Interface

05221C-8

The S signal is used to select whether data flow is from the DRAM array or the system bus. The  $\overline{\text{OEBL}}$  and  $\overline{\text{OEBH}}$  control the selection of the lower and higher half words of data from the system bus. LEB is the latch-enable signal for data flow between the EDC bus and the system bus. Decoding of  $\overline{\text{OEBL}}$  and  $\overline{\text{OEBH}}$  is shown in Table 5.

**TABLE 5. OEB TRUTH TABLE**

| H/F | A, | ÖEBH | OEBL |

|-----|----|------|------|

| 0   | х  | 0    | 0    |

| 1   | 0  | 1    | 0    |

| 1   | 1  | 0    | 1    |

Key: X = Don't Care

When the system has been set up for Read-Without-Error Cycles (Fly-By Mode), the S signal must be modified by external logic when the Am2961/62 Bus Buffers are used. This timing adjustment is required because the Am2969 propagation delay from  $T_2$  (timing tap) to S is faster than the delay from  $T_2$  to LEB. The adjustment is illustrated in Figure 3. Although this will also modify the S signal timing for other cycles, system timing will not be affected.

#### Am2969 Miscellaneous Signal Interface

System Power-On Reset (SPR) — The 68-lead surface-mount versions of the Am2969 have an SPR input pin which is normally connected to the system or host processor RESET. Actual initialization of the Am2969 is performed by an internal power-up initialization circuit. The purpose of the SPR pin is to inhibit Forced Refreshes from starting cycles before the rest of the system is completely initialized. As long as SPR is active, FR will be disabled.

When using a 48-pin DIP or 48-pin Flatpack, the SPR function must be generated externally as these packages are pin-limited. This simple hook-up is illustrated in Figure 4. In this case, the FR pin will be held HIGH to ensure proper functioning of the Am2969 during power-up.

Figure 3. S Signal Interface from Am2969 to Am2961/Am2962 in the Fly-By System Operating Mode

Figure 4. Implementation of SPR on a DIP or Flatpack Package

Oscillator Input (OSC) — The Am2969 has an on-chip interval timer for generation of refresh request signals in the Automatic Refresh Mode. The OSC input is connected to a simple resistor-capacitor network as shown in Figure 5. Suggested values are  $R=47~k\Omega$  and C=1000~pF.

Figure 5. OSC Input R-C Network

#### **Operational Modes**

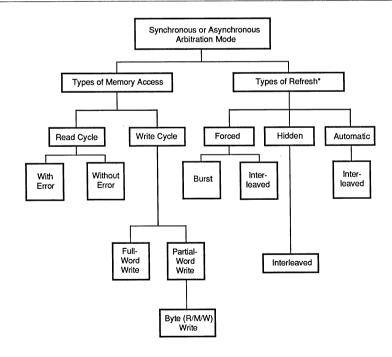

The basic types of operations handled by the Am2969 are read, write, and refresh cycles and arbitration. These operations can be performed in different modes.

The Am2969 can operate at the chip-level in the following modes:

- Asynchronous Arbitration

- Synchronous Arbitration

- · Memory Initialization

- · Read and Write Cycles

- · Refresh Cycles

Furthermore, the Am2969 can operate in the following system-level modes:

- Flow-Thru

- Fly-By

- Scrubbing

- Bus-Retry

These operating modes are illustrated in the Am2969 Functional Tree of Figure 6. This section of the data sheet will describe the chip-level and system-level modes of the Am2969.

05221C-10

\*Refresh cycles can be with or without scrubbing.

Figure 6. Am2969 Functional Operations Tree

#### **Chip-Level Modes of Operation**

#### Synchronous vs Asynchronous Arbitration

A primary function of the Am2969 is to arbitrate between CPU access requests (read/write) and refresh requests. The Am2969 arbitrates memory requests in either synchronous or asynchronous systems.

In either system mode of operation, the processor typically originates the read/write and refresh requests. However, the Am2969, through use of an internal timer, can generate refresh requests independent of the CPU. This frees CPU overhead from data management routines and also provides a "fail-safe" generator of refresh requests to guarantee the integrity of data.

Within the Am2969, arbitration logic decides which request is serviced first when both refresh and access requests are issued simultaneously. The state of the arbiter, in either a synchronous or an asynchronous system, determines when each cycle begins.

Synchronous Arbitration — The Am2969 can perform arbitration in a synchronous system by connection of the system clock signal to the CLK input. A cycle begins with the falling edge of the CLK signal. In the synchronous mode, the Am2969 samples the CYCREQ (read/write) and refresh inputs on the negative of CLK. Should both a refresh and processor-cycle request be issued prior to a negative CLK, both requests will be latched into the arbiter. If both cycle requests occur simultaneously, the arbiter services the processor request first, followed by the refresh request. With the exception of a Burst Refresh, the refresh request is serviced immediately upon completion of the processor cycle. It is not necessary to wait for another CLK edge. A Burst Refresh request is not executed until a falling CLK edge is encountered and there is no processor request. This delay in servicing a Burst Refresh request optimizes processor performance.

Asynchronous Arbitration — The arbiter of the Am2969 also operates in asynchronous systems. Under this condition, every memory request is latched into the arbiter inputs. An internal delay is intended to prevent possible metastable states.

The arbiter switches from synchronous to asynchronous when it detects the absence of transitions on the CLK input. The Am2969 decides that a clock is not present (and therefore operates asynchronously) in either of two ways. First, the asynchronous mode can be initiated by two HIGH-to-LOW transitions of the forced refresh input  $(\overline{FR})$ . Alternately, the asynchronous mode can be initiated by issuing three HIGH-to-LOW transitions followed by two LOW-to-HIGH transitions of the oscillator (OSC) input. This second method is accomplished by use of an on-chip 2-bit shift register that is clocked by the internal refresh clock. This register is reset when the CLK is LOW. This implementation allows the clock signal from a synchronous system to be interrupted while the clock is in the logic-HIGH state, and service the refresh request through the asynchronous arbiter.

Either method of initiating the asynchronous mode of arbitration causes the generation of an immediate refresh request. For asynchronous arbitration, the CLK input must be tied HIGH. It is recommended that either of the above-mentioned procedures be performed immediately upon power-up during the initialization of the memory. In the asynchronous mode, the arbiter services a processor request before a refresh request. If a processor cycle is being executed, any refresh request is latched into the refresh logic and executed when the current cycle ends. CYCREQ must be held LOW until the end of the current cycle.

Once the asynchronous mode of arbitration has been initiated, the Am2969 cannot switch to synchronous operation.

#### **Types of Memory Accesses**

#### Memory Initialization

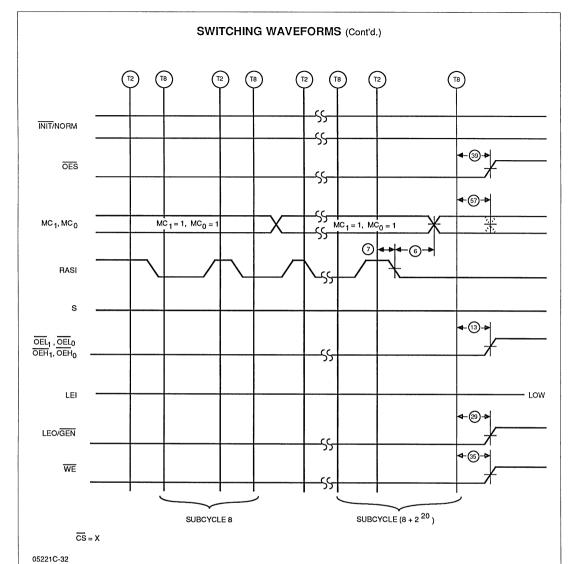

The Am2969 provides the necessary signals to perform memory initialization. Error-correcting memories must be initiated to a known state to avoid read errors associated with memory power-up. The Am2969 facilitates this procedure via the INIT/NORM input. The data pattern written into memory can be either all zeros (using the initialization mode of the Am29C60A), or any desired pattern present on the system bus during the first memory cycle of the initialization routine.

Upon entering the Initialize mode, the Am2969 performs eight "wake-up" cycles followed by 2°° write/refresh cycles. During this time the processor will remain in a wait state if it attempts to access the memory. Upon completion of the initialization, the Am2969 begins normal memory arbitration.

This initialization is given priority over either processor or refresh requests. The user is strongly urged to take precautions against an accidental initialization request during a normal processor or refresh cycle.

#### Read and Write Cycles

Following the Functional Tree of the Am2969, it can be observed that the Am2969 can control many types of processor requests (accesses). The two main accesses are read cycles and write cycles. Within the read cycles, the Am2969 can perform read-without-error and read-with-error cycles. Within the write cycles, the Am2969 can perform full-word-write, partial-word-write, and byte-write cycles. All of these cycles are normal read/write cycles except byte-write, which requires an extended read/modify/write cycle.

To initiate a memory access, the processor generates the following signals:  $\overline{\text{CS}}$ ,  $\overline{\text{CYCREO}}$ ,  $\overline{\text{B/M}}$ , and  $\overline{\text{R/M}}$ . The Am2969 subsequently generates the RASI (Row Address Strobe Input) and the MC<sub>1</sub> (Mode Control) signals. Based upon the interface signals, the Am2969 asserts the appropriate  $\overline{\text{WE}}$  (Write Enable) and  $\overline{\text{DTACK}}$  (Data Transfer Acknowledge) signals at the appropriate times. The Write-Enable output of the Am2969 is designed to directly drive up to 88 DRAMs, 500-pF load. To calculate loads exceeding 500 pF, refer to either the Am2968A or Am29368 data sheets.

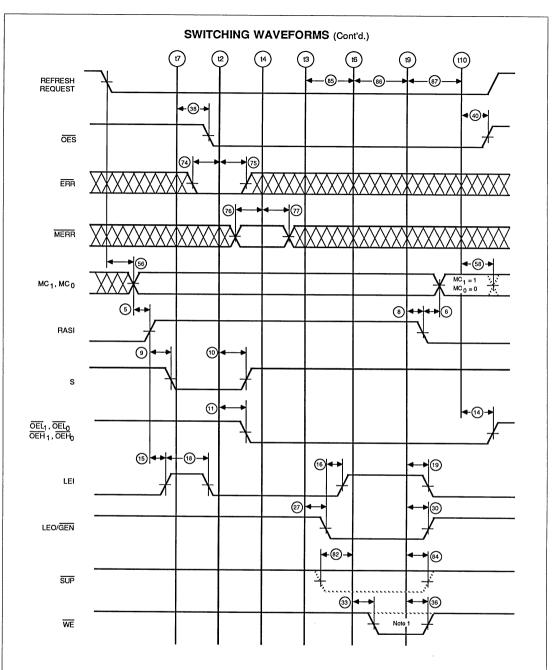

#### Refresh Cycles

The Am2969 can support a variety of refresh methods. The choice of refresh mode is controlled via the RM<sub>n</sub> inputs. The basic refresh modes which are supported by the Am2969 are forced, hidden, and automatic refresh. Within these modes there are two methods of execution: interleaved (or distributed) and burst. Burst refreshes can be 128, 256, or 512 cycles in duration.

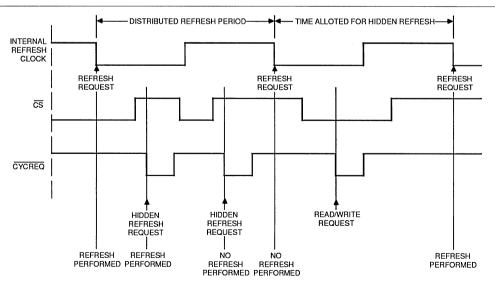

A forced refresh is an externally requested refresh executable in either the interleaved or burst mode. The refresh signal is generated by external logic which is under the control of the processor. Hidden refresh occurs when the processor is accessing other I/O devices. A hidden refresh can only be performed once every refresh clock period and occurs only as an interleaved refresh. Figure 7 illustrates the system timing for a hidden refresh. Finally, automatic refresh is an Am2969-generated refresh. This "fail-safe" method of refresh is generated every 15.6  $\mu s$  by an on-chip internal oscillator. The Am2969 effectively controls both internally (automatic) and externally (hidden or forced) refresh requests.

#### Forced and Automatic Refreshes

An internal refresh request (automatic) is controlled through either the  $\overline{FR}$  input or the internal oscillator.

In the burst mode of operation, the  $\overline{FR}$  input is always the refresh clock

The FR input can also be used as the refresh clock in the interleaved (distributed) mode. However, the internal oscillator takes over as the refresh clock if it goes through three cycles without a LOW level appearing on the FR input. Therefore, when a forced refresh is not requested within three

oscillator clock cycles, an automatic refresh is generated. This allows the primary refresh clock  $(\overline{FR})$  to be interrupted while it is in the HIGH logic state and causes refresh operations to commence at the 15.6  $\mu$ s internal oscillator rate.

Finally, it is possible to control the refresh requests through the use of the on-chip internal oscillator only when in the interleaved (distributed) mode. In this automatic (or fail-safe) mode, the FR input must be tied HIGH.

#### Hidden Refresh

The Am2969 can increase memory bandwidth by inserting refresh requests when the processor is accessing other devices or performing I/O operations ( $\overline{\text{CYCREQ}} = \text{LOW}$ ,  $\overline{\text{CS}} = \text{HIGH}$ ). When a hidden refresh is performed, the Am2969 will skip the next refresh request. Only one hidden refresh is allowed for each forced or automatic refresh. Two hidden refresh requests cannot be serviced in succession; they must be interleaved by a forced or automatic refresh request.

A hidden refresh could occur illegally if  $\overline{\text{CS}}$  goes LOW-to-HIGH when  $\overline{\text{CYCREQ}}$  is LOW. To avoid this condition, assert  $\overline{\text{CYCREQ}}$  HIGH before  $\overline{\text{CS}}$  goes HIGH. Figure 7 shows the timing involved to perform a hidden-refresh cycle.

Depending upon the system configuration, it is possible for the DRAM to appear "static" to the processor. The Am2969 will take over full control of refresh requests performing a hidden refresh on every clock cycle. Further system optimization (e.g., elimination of wait states) and avoidance of arbitration collisions between refresh and memory requests can be achieved by decoding the I/O status signals and forcing refreshes during I/O operations.

Figure 7. Hidden-Refresh Cycle

#### **System-Level Modes of Operation**

## Flow-Thru-Read Cycles

The simplest method to implement an error-correcting memory is to extend all read cycles long enough to have single errors detected before the Data Transfer Acknowledge (\overline{DTACK}) is asserted. The Am2960A Error Detection and Correction Circuit assumes every word is in error and completes a full correction routine. It is provided the time to complete this cycle because only read/modify/write cycles are used. When using this Flow-Thru system implementation, faster memory must be used to allow the single error flag to become valid prior to the assertion of \overline{DTACK}. If faster memory is unavailable or undesirable, the Am2969 will insert wait states into the read cycle. This will compromise memory bandwidth, although system timing is simplified.

#### Fly-By-Read Cycles

Fly-By systems provide the highest data throughput available in an error-correcting system. This is accomplished by assuming that all reads will result in correct data. DTACK is asserted earlier in the cycle and the processor is interrupted only if any error occurs (single-bit or mulitple-bit errors). The EDC circuit does not correct the errors, leaving the CPU to typically enter a recovery routine. Since the occurrence of errors is infrequent, memory bandwidth is improved.

Although Fly-By systems may have an increased number of interrupts sent to the processor, system throughput will be affected minimally as the occurrence of soft errors is generally low. However, a DRAM device failure (hard error) can cause every read to that bank of memory to result in an interrupt, severely affecting system performance. An error-logging function can flag the repeat occurrence and alert the operator of possible hard errors.

#### Flow-Thru vs Fly-By at the Chip Level

The Am2969 determines whether Flow-Thru or Fly-By has been implemented by the relationship between timing taps  $T_1$  and  $T_2$ . The Flow-Thru Mode is identified when  $T_2$  goes HIGH prior to  $T_1$ . Similarly, the Fly-By mode is selected if the Am2969 detects timing tap  $T_1$  going HIGH prior to  $T_2$ .

The Am2969 can be used in non-EDC systems. However, the Am2970 Memory Timing Controller is designed for such applications. The Am2970 will provide the same control, interval timing, and arbitration as the Am2969, but without the overhead and signals required for the control of the EDC circuit.

#### Scrubbing

Memory scrubbing is a housekeeping operation in which memory is checked for errors during normal refresh operations. The Am2969 is the only memory timing controller which can facilitate AMD's patented Scrubbing technique.

On each refresh-with-scrub cycle, one memory location is read, checked for errors, and if necessary, corrected before

being written back into memory. For a one-megaword memory ( $2^{\infty}$  locations) with one refresh every 16  $\mu$ s, the Am2969/Am2960A/Am29368 Memory Support chip set will "scrub" the entire memory of single-bit errors every 16 seconds. If multiple-bit errors are encountered during a scrub cycle,  $\overline{WE}$  is suppressed.

With the occurrence of an error, a read/modify/write (R/M/W) cycle is performed. The duration of a R/M/W cycle is typically longer than a normal read or write cycle. During refresh operations, a row in each bank is accessed by energizing the RAS line. This refreshes all the locations in that row. If an error is detected, a write operation is performed in that bank at the location of the error. This is accomplished by energizing the CAS line in that bank for that location. The entire checking operation is performed within the refresh cycle. A wait state may need to be issued to extend the cycle should an error be discovered. However, the system reliability will be increased because soft errors will not be able to accumulate in areas of memory that are not frequently accessed.

When performing refresh without scrubbing, all four  $\overline{RAS}$  lines go LOW but the  $\overline{CAS}$  lines remain HIGH or inactive. A refresh with scrubbing will activate all four  $\overline{RAS}$  lines as before and a single  $\overline{CAS}$  line. Errors that are detected during scrubbing cycles do not cause interrupts or bus-error ( $\overline{BERR}$ ) signal assertions.

#### **Bus Retry Mode**

The Am2969 has a special read access mode for system processors that can support a Bus-Retry request. Bus Retry is an efficient error correction mode usable in both Flow-Thru and Fly-By operations.

When Bus Retry is implemented, read cycles normally are performed as Fly-By. In this mode, the Am2969 does not interrupt the processor when a single-bit error is encountered. Instead, it requests that the last cycle be "re-run" by asserting BERR and HALT simultaneously. An internal-status flip-flop is set that reserves the next processor request for a read cycle to the same location. On this access, DTACK is delayed until the erroneous data is corrected. If a multiple-bit error is detected, BERR is asserted and the processor can enter an error-recovery subroutine.

The relationship of ERR, MERR, HALT, BERR, and various timing tap inputs are shown in the Switching Waveforms titled "Bus-Retry Mode, First-Access Timing Diagram" and "Bus-Retry Mode, Second-Access Timing Diagram."

The assertion of DTACK (LOW) can be summarized as follows:

• T, causes DTACK:

Flow-Thru with error cycles, all Fly-By cycles, and first Bus-Retry cycles.

T<sub>a</sub> causes DTACK:

Flow-Thru with error cycles.

• RASI causes DTACK: Full-word-write cycles.

T ----- DTACK: Cocond Bus E

T<sub>2</sub> causes DTACK:

Second Bus-Retry without error cycles.

In systems not using Bus Retry, INTERR is generated to interrupt the processor on the detection of a single-bit error in the Fly-By Mode or a multiple-bit error in the Flow-Thru Mode. After an interrupt request is made, INTACK is brought LOW to reset the INTERR output.

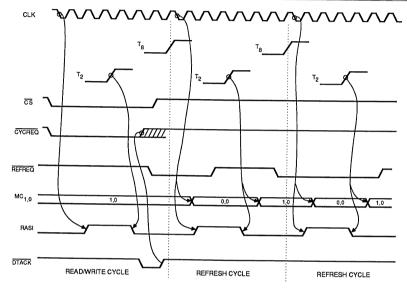

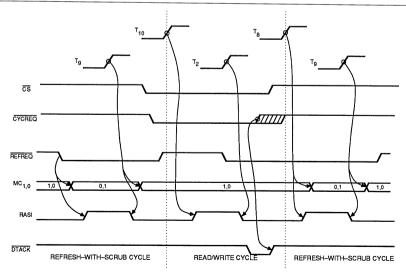

#### **Back-to-Back Cycles**

Situations may arise which cause repeated memory cycles, one immediately after the other. An example of such a

situation is a refresh request occurring during a memory read cycle. Figures 8 and 9 illustrate further examples of Back-to-Back cycles.

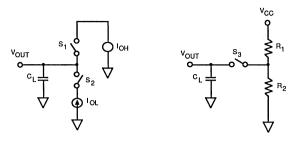

### **Device Decoupling**

Proper decoupling of the Am2969 is necessary for proper operation of the device. The recommended decoupling is illustrated in Figure 10.  $\rm C_1, \, C_2, \, and \, C_3$  should be monolithic capacitors. The capacitors should be mounted as close as possible to the  $\rm V_{cc}$  pin(s).

05221C-12

Figure 8. Back-to-Back Synchronous Cycles

Figure 9. Back-to-Back Asynchronous Cycles

#### **APPLICATIONS**

## **Timing Control**

To obtain optimum performance and maximum design flexibility, the timing and control logic for the memory system has been kept as a separate function. For systems implementing Error Detection and Correction, the Am2969 Memory Timing Controller (MTC) provides all the necessary control signals for

the Am29368, Am2961/62 EDC Bus Buffers, and the Am2960A EDC Unit. The Am2969 Memory Timing Controller uses an Am2972 PEG or delay lines to provide the most accurate timing reference from which the control signals are derived.

Figure 11. Four-Megaword Dynamic Memory with Error Detection and Correction

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                           | 65 to +150°C      |

|-----------------------------------------------|-------------------|

| Ambient Temperature with                      | 55 to 405 O       |

| Power Applied                                 | 55 to +125 C      |

| Supply Voltage to Ground Potential Continuous | 0 5 V to . 7 0 V  |

| DC Voltage Applied to Outputs for             | 0.5 V 10 +7.0 V   |

| HIGH Output State                             | -0.5 V to +V Max. |

| DC Input Voltage                              | –0.5 V to +5.5 V  |

| DC Input Current                              |                   |

| !                                             |                   |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commercial (C) Devices              |                    |

|-------------------------------------|--------------------|

| Ambient Temperature (T <sub>A</sub> | 0 to +70°C         |

| Supply Voltage (V <sub>cc</sub> )   | 5.0 V ±10%         |

| Min                                 |                    |

| Max                                 | 5.5 V              |

| Military* (M) and Extended Comme    | ercial (E) Devices |

| Casa Tamparatura (T.)               |                    |

| Military* (M) and Extended Comme   | ercial (E) Devices |

|------------------------------------|--------------------|

| Case Temperature (T <sub>c</sub> ) | 55 to +125°C       |

| Supply Voltage (V <sub>cc</sub> )  | 5.0 V ±10%         |

| Min                                |                    |

| Max                                | 5.5 V              |

Operating ranges define those limits between which the functionality of the device is guaranteed.

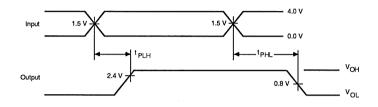

**DC CHARACTERISTICS** over operating range unless otherwise specified (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol | Parameter<br>Description                                                                                                                                                                           | Test Conditions (Note 1)                             | Min. | Max. | Unit |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------|------|------|

| V <sub>oн</sub>     | Output HIGH Voltage. All Outputs Except: INTACK/BERR, DTACK, and INTERP/HALT                                                                                                                       | V <sub>cc</sub> = Min.,<br>I <sub>oH</sub> = -1.0 mA | 2.4  |      | ٧    |

| V <sub>oL</sub>     | Output LOW Voltage. All Outputs Except: WE, S, and LEB                                                                                                                                             | V <sub>cc</sub> = Min.,<br>I <sub>oL</sub> = 8 mA    |      | 0.5  | ٧    |

|                     | Output LOW Voltage. S and LEB Outputs                                                                                                                                                              | V <sub>cc</sub> = Min.,<br>I <sub>oL</sub> = 16 mA   | >    | 0.5  | ٧    |

|                     | Output LOW Voltage. WE Output                                                                                                                                                                      | V <sub>cc</sub> = Min.,<br>I <sub>oL</sub> = 2.4 mA  |      | 0.5  | V    |

|                     |                                                                                                                                                                                                    | V <sub>cc</sub> = Min.,<br>I <sub>oL</sub> = 12 mA   |      | 0.8  | V    |

| V <sub>IH</sub>     | Input HIGH Level.                                                                                                                                                                                  |                                                      | 2.0  |      | ٧    |

| V <sub>IL</sub>     | Input LOW Level.                                                                                                                                                                                   |                                                      |      | 0.8  | ٧    |

| V,                  | Input Clamp Voltage.                                                                                                                                                                               | V <sub>cc</sub> = Min.,<br>I <sub>IN</sub> = -18 mA  |      | -1.2 | V    |

| I <sub>IL</sub>     | Input LOW Current. Inputs: ERR, MERR, T <sub>4</sub> , T <sub>1</sub> , T <sub>2</sub> , CS, RM <sub>2</sub> , SUP, CYCREQ, BRM, A <sub>0</sub> , A <sub>1</sub> , B/W, R/W, H/F, and SPR (Note 2) | $V_{CC} = Max.,$ $V_{IN} = 0.4 \text{ V}$            |      | -800 | μА   |

|                     | Input LOW Current. Inputs: FR, INTACK, INIT/NORM, CLK, RM <sub>o</sub> , RM <sub>1</sub> , T <sub>3</sub> , and T <sub>5</sub> -T <sub>10</sub>                                                    | V <sub>cc</sub> = Max.,<br>V <sub>IN</sub> = 0.4 V   |      | -400 | μА   |

| I <sub>IH</sub>     | Input HIGH Current. Inputs: ERR, MERR, T <sub>4</sub> , T <sub>5</sub> , T <sub>2</sub> , CS, RM <sub>2</sub> , SUP, CYCREQ, BRM, A <sub>6</sub> , A <sub>1</sub> , B/W, R/W, and H/F.             | V <sub>cc</sub> = Max.,<br>V <sub>IN</sub> = 2.7 V   |      | 40   | μА   |

|                     | Input HIGH Current. Inputs: FR, $\overline{\text{INTACK}}$ , $\overline{\text{INT/NORM}}$ , CLK, RM $_{\text{o}}$ , RM $_{\text{r}}$ , T $_{\text{3}}$ , and T $_{\text{5}}$ –T $_{\text{10}}$ .   | V <sub>cc</sub> = Max.,<br>V <sub>IN</sub> = 2.7 V   |      | 20   | μА   |

|                     | Input HIGH Current.<br>Input: SPR (Note 2)                                                                                                                                                         | V <sub>cc</sub> = Max.,<br>V <sub>IN</sub> = 2.7 V   |      | -250 | μА   |

<sup>\*</sup> Military Product 100% tested at  $T_{\rm c}$  = +25°C, +125°C, and -55 C.

## DC CHARACTERISTICS (Cont'd.)

| Parameter<br>Symbol | Parameter<br>Description                                                                       | Test Conditions (Note 1)                             | Min. | Max. | Unit |

|---------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------|------|------|------|

| 1,                  | Input HIGH Current.                                                                            | V <sub>cc</sub> = Max.,<br>V <sub>IN</sub> = 5.5 V   |      | 1.0  | mA   |

| l <sub>sc</sub>     | Output Short-Circuit Current. All Outputs Except: INTACK/BERR, DTACK, and INTERR/HALT (Note 3) | V <sub>cc</sub> = Max.,<br>V <sub>out</sub> = 0.0 V  | -60  | -200 | mA   |

| l <sub>ox</sub>     | Open-Collector Output Current. Outputs: INTERR/BERR, DTACK, and INTACK/HALT                    | V <sub>cc</sub> = Min.,<br>V <sub>oH</sub> = 5.5 V   |      | 250  | μА   |

| I <sub>cc</sub>     | Power Supply Current.<br>(Note 4)                                                              | $V_{cc} = 5.0 \text{ V}, T_{A} = 25^{\circ}\text{C}$ |      | 185  | ^    |

|                     | (1000)                                                                                         | V <sub>cc</sub> = Max.                               |      | 260  | mA   |

- Notes: 1. For conditions shown as Min. or Max., use the appropriate value specified under Operating Range for the applicable device type. No input tests are performed on the OSC input.

- 2. SPR is available only on surface-mount packages.

- 3. Not more than one output should be shorted together at a time. Duration of the short-circuit test should not exceed

- 4. Typical  $I_{cc}$  ( $V_{cc} = 5.0 \text{ V}$ ,  $T_A = 25 ^{\circ}\text{C}$ ) is neither tested nor guaranteed, but should be representative of a nominal unit.

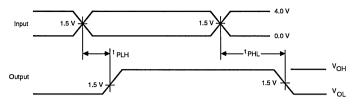

SWITCHING CHARACTERISTICS over operating range unless otherwise specified (for APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted) ( $C_L = 50 \text{ pF}$ )

| No. | Parameter<br>Symbol | Parameter<br>Description             | System Condition                                                    |                    | Min. | Max. | Unit |

|-----|---------------------|--------------------------------------|---------------------------------------------------------------------|--------------------|------|------|------|

| 1   | t <sub>PD</sub>     | CLK ↓ to RASI ↑                      | Synchronous R/W Cycles<br>(see Diagram A)                           |                    |      | 24   | ns   |

| 2   | t <sub>PD</sub>     | CYCREQ ↓ to RASI ↑                   | Asynchronous R/W Cycles<br>(see Diagram B)                          |                    |      | 28   | ns   |

| 3   | t <sub>PD</sub>     | T <sub>8</sub> ↑ to RASI ↑           | Asynchronous Back-to-Back R/W and Initialize Cycles (see Diagram M) |                    |      | 57   | ns   |

| 4   | t <sub>PD</sub>     | T₁₀ T̂ to RASI T̂                    | Asynchronous Back-to-Back R/W<br>Cycles                             |                    |      | 55   | ns   |

| 5   | t <sub>s</sub>      |                                      | All Refresh Cycles                                                  | COM'L              | 18   | 55   |      |

|     |                     | to RASI↑                             | (see Diagram I)                                                     | MIL and<br>E-COM'L | 18   | 58   | ns   |

| 6   | t <sub>H</sub>      | MC <sub>₀,1</sub> (Note 1) to RASI ↓ | All Refresh Cycles (see Diagra                                      | ım I)              | 5    |      | ns   |

| 7   | t <sub>PD</sub>     | T₂ ↑ to RASI ↓                       | All Short Cycles (see Diagram                                       | B)                 |      | 25   | ns   |

| 8   | t <sub>PD</sub>     | T <sub>9</sub> ↑ to RASI ↓           | All Long Cycles (see Diagram                                        |                    | 20   | ns   |      |

| 9   | t <sub>PD</sub>     | RASI ↑ to S ↓                        | All Cycles Except Full-Word-W<br>and Initialize (see Diagram B)     |                    | 10   | ns   |      |

| 10  | t <sub>PD</sub>     | T₂ ↑ to S ↑                          | All Cycles Except Full-Word-W<br>and Initialize (see Diagram B)     | rite               |      | 18   | ns   |

| No. | Parameter<br>Symbol | Parameter<br>Description                                              | Syster                                    | System Condition Min.             |                    |      |    |  |

|-----|---------------------|-----------------------------------------------------------------------|-------------------------------------------|-----------------------------------|--------------------|------|----|--|

| 11  | t <sub>PD</sub>     | $T_2 \uparrow to \overline{OEH}_n, \overline{OEL}_n \downarrow$       | All R/M/W Cycels                          | 33                                | ns                 |      |    |  |

| 12  | t <sub>PD</sub>     | $T_{a} \uparrow to \overline{OEH}_{n}, \overline{OEL}_{n} \downarrow$ | Initialize Cycles (s                      | Initialize Cycles (see Diagram M) |                    |      |    |  |

| 13  | t <sub>PD</sub>     | $T_s \uparrow to \overline{OEH}_n$ , $\overline{OEL}_n$               | Initialize Cycles (s                      | ee Diagram N)                     |                    | 37   | ns |  |

| 14  | t <sub>PD</sub>     | T <sub>10</sub> ↑ to ŌĒĦ <sub>n</sub> , ŌĒŪ <sub>n</sub> ↑            | All R/M/W Cycles                          | (see DiagramC                     | )                  | 37   | ns |  |

| 15  | t <sub>PD</sub>     | RASI ↑ to LEI ↑                                                       | R/M/W, Full-Word-<br>Initialize Cycles (s | -Write, and<br>ee Diagram C)      |                    | 12   | ns |  |

| 16  | t <sub>PD</sub>     | LEO/ <del>GEN</del> (Note 1) ↓<br>to LEI ↑                            | All R/M/W Cycles                          | (see Diagram (                    | 5                  |      | ns |  |

| 17  | t <sub>PD</sub>     | T₅ ↑ to LEI ↓                                                         | Full-Word-Write C                         | ycle (see Diagr                   | am H)              | 20   | ns |  |

| 18  | t <sub>PD</sub>     | T, ↑ to LEI ↓                                                         | All R/M/W Cycles                          | (see Diagram E                    | 3)                 | 20   | ns |  |

| 19  | t <sub>PD</sub>     | T₀ ↑ to LEI ↓                                                         | All R/M/W Cycles                          | (see Diagram (                    |                    | 37   | ns |  |

| 20  | t <sub>PD</sub>     | RASI ↑ to LEB ↑                                                       | (see Diagram B)                           | A                                 |                    | > 12 | ns |  |

| 21  | t <sub>PD</sub>     | T₃ ↑ to LEB ↓                                                         | Flow-Thru-Read C                          | Cycles (see Dia                   | gram C)            | 21   | ns |  |

| 22  | t <sub>PD</sub>     | T₂ ↑ to LEB ↓                                                         | Fly-By-Read Cycle                         | es (see Diagrar                   | m B)               | 30   | ns |  |

| 23  | t <sub>PD</sub>     | T, ↑ to OEBH, OEBL ↓                                                  | (see Diagram B)                           |                                   |                    |      | ns |  |

| 24  | t <sub>PD</sub>     | CYCREQ ↑ to OEBH,<br>OEBL ↑                                           |                                           | 27                                | ns                 |      |    |  |

| 25  | t <sub>PD</sub>     | RASI ↑ to LEO/GEN ↓                                                   | Full-Word-Write Cycle (see Diagram H)     |                                   |                    |      | ns |  |

| 26  | t <sub>PD</sub>     | T <sub>s</sub> ↑ to LEO/GEN ↓                                         | Initialize Cycle (see Diagram M)          |                                   |                    |      | ns |  |

| 27  | t <sub>PD</sub>     | T₃ ↑ to LEO/GEN ↓                                                     | All R/M/W Cycles (see Diagram C)          |                                   |                    |      | ns |  |

| 28  | t <sub>PD</sub>     | T₂ ↑ to LEO/GEN ↑                                                     | Full-Word-Write Cycle (see Diagram H)     |                                   |                    |      | ns |  |

| 29  | t <sub>PD</sub>     | T <sub>8</sub> ↑ to LEO/GEN ↑                                         | Initialize Cycle (se                      | ee Diagram N)                     |                    | 33   | ns |  |

| 30  | t <sub>PD</sub>     | T <sub>9</sub> ↑ to LEO/GEN ↑                                         | All R/M/W Cycles                          | (see Diagram                      | C)                 | 33   | ns |  |

| 31  | t <sub>PD</sub>     | RASI ↑ to WE ↓                                                        | Initialize Cycle                          | C <sub>L</sub> = 50 pF            |                    | 6    | ns |  |

|     |                     |                                                                       | (see Diagram M)                           | C <sub>L</sub> = 150 pF           |                    | 11   | ns |  |

|     |                     |                                                                       |                                           | C <sub>L</sub> = 500 pF           | COM'L              | 25   | ns |  |

|     |                     |                                                                       |                                           |                                   | MIL and<br>E-COM'L | 27   | ns |  |

| 32  | t <sub>PD</sub>     | T <sub>s</sub> ↑ to WE↓                                               | Full-Word-                                | C <sub>L</sub> = 50 pF            |                    | 15   | ns |  |

|     |                     |                                                                       | Write Cycle<br>(see Diagram H)            | C <sub>L</sub> = 150 pF           |                    | 22   | ns |  |

|     |                     |                                                                       |                                           | C <sub>L</sub> = 500 pF           | COM'L              | 36   | ns |  |

|     |                     |                                                                       |                                           |                                   | MIL and<br>E-COM'L | 39   | ns |  |

| No. | Parameter<br>Symbol | Parameter<br>Description                                                          |                                                         |                                   |                    |    | Max. | Uni |

|-----|---------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------|--------------------|----|------|-----|

| 33  | t <sub>PD</sub>     | $T_{\epsilon} \uparrow$ to $\overline{WE} \downarrow$                             | All R/M/W                                               | C <sub>L</sub> = 50 pF            |                    |    | 15   | ns  |

|     |                     |                                                                                   | Cycles (see<br>Diagram C)                               | C <sub>L</sub> = 150 pF           |                    |    | 22   | ns  |

|     |                     |                                                                                   |                                                         | C <sub>L</sub> = 500 pF           | COM'L              |    | 36   | ns  |

|     |                     |                                                                                   |                                                         |                                   | MIL and<br>E-COM'L |    | 39   | ns  |

| 34  | t <sub>PD</sub>     | T₂ ↑ to WE ↑                                                                      | Full-Word-<br>Write Cycle                               | C <sub>L</sub> = 50 pF            |                    |    | 35   | ns  |

|     |                     |                                                                                   | (see Diagram H)                                         | C <sub>L</sub> = 150 pF           |                    |    | 40   | ns  |

|     |                     |                                                                                   |                                                         | C <sub>L</sub> = 500 pF           | COM'L              |    | 60   | ns  |

|     |                     |                                                                                   |                                                         |                                   | MIL and<br>E-COM'L |    | 68   | ns  |

| 35  | t <sub>PD</sub>     | T <sub>8</sub> ↑ WE ↑                                                             | Initialize Cycle<br>(see Diagram N)                     | C <sub>L</sub> = 50 pF            |                    |    | 35   | ns  |

|     |                     |                                                                                   | (000 Blagfalli 11)                                      | C <sub>L</sub> = 150 pF           |                    |    | 40   | ns  |

|     | c                   | C <sub>L</sub> = 500 pF                                                           | COM'L                                                   |                                   | 60                 | ns |      |     |

|     |                     |                                                                                   |                                                         |                                   | MIL and<br>E-COM'L |    | 68   | ns  |

| 36  | t <sub>PD</sub>     | $t_{PD}$ $T_g \uparrow to \overline{WE} \uparrow$ All R/M/W $C_L = 50 \text{ pF}$ |                                                         |                                   | 35                 | ns |      |     |

|     |                     |                                                                                   | Cycles (see<br>Diagram C)                               | C <sub>L</sub> = 150 pF           |                    |    | 40   | ns  |

|     |                     |                                                                                   |                                                         | C <sub>L</sub> = 500 pF           | COM'L              |    | 60   | ns  |

|     |                     |                                                                                   |                                                         |                                   | MIL and<br>E-COM'L |    | 68   | ns  |

| 37  | t <sub>PD</sub>     | RASI ↑ to ŌES ↓                                                                   | Full-Word-Write and Initialize Cycles (see Diagram H)   |                                   |                    |    | 12   | ns  |

| 38  | t <sub>PD</sub>     | T <sub>7</sub> ↑ to OES ↓                                                         | (see Diagram B)                                         |                                   |                    |    | 38   | ns  |

| 39  | t <sub>PD</sub>     | T <sub>s</sub> ↑ to <del>OES</del> ↑                                              | (see Diagram B)                                         |                                   |                    |    | 33   | ns  |

| 40  | t <sub>PD</sub>     | T₁₀↑ to OES↑                                                                      | (see Diagram C)                                         |                                   |                    |    | 33   | ns  |

| 41  | t <sub>PD</sub>     | T, ↑ to DTACK ↓                                                                   | Fly-By, Flow-Thru<br>First-Bus-Retry Mo                 | -without-Error,<br>odes (see Diag | and<br>ram B)      |    | 15   | ns  |

| 42  | t <sub>PD</sub>     | T₂ ↑ to DTACK ↓                                                                   | Second-Bus-Retry Cycle<br>without Error (see Diagram E) |                                   |                    |    | 15   | ns  |

| 43  | t <sub>PD</sub>     | T₄ ↑ to DTACK ↓                                                                   | Flow-Thru with Error Cycles (see Diagram C)             |                                   |                    |    | 16   | ns  |

| 44  | t <sub>PD</sub>     | RASI ↑ to DTACK↓                                                                  | Full-Word-Write Cycle (see Diagram H)                   |                                   |                    |    | 17   | ns  |

| 45  | t <sub>PD</sub>     | CYCREQ ↑ to DTACK ↑                                                               | (see Diagram B)                                         |                                   |                    |    | 39   | ns  |

| No. | Parameter Parameter Symbol Description System Condition |                                                 | Min.                                           | Max. | Uni |    |

|-----|---------------------------------------------------------|-------------------------------------------------|------------------------------------------------|------|-----|----|

| 46  | t <sub>PD</sub>                                         | T₂↑ to BERR ↓                                   | First-Bus Access, ERR = LOW (see Diagram D)    |      | 16  | ns |

| 47  | t <sub>PD</sub>                                         | T₄↑ to BERR↓                                    | Second-Bus Access, MERR = LOW (see Diagram E)  |      | 16  | ns |

| 48  | t <sub>PD</sub>                                         | CYCREQ ↑ to BERR↑                               | (see Diagram D)                                |      | 40  | ns |

| 49  | t <sub>PD</sub>                                         | T₂ ↑ to ĦALT↓                                   | First-Bus Access, ERR = LOW (see Diagram D)    |      | 16  | ns |

| 50  | t <sub>PD</sub>                                         | CYCREQ ↑ to HALT ↑                              | (see Diagram D)                                |      | 37  | ns |

| 51  | t <sub>PD</sub>                                         | T₂ ↑ to INTERR↓                                 | Fly-By Mode, ERR = LOW (see<br>Diagram F)      |      | 16  | ns |

| 52  | t <sub>PD</sub>                                         | T₄ ↑ to INTERR↓                                 | Flow-Thru Mode, MERR = LOW<br>(see Diagram G)  |      | 16  | ns |

| 53  | t <sub>PD</sub>                                         | INTACK ↓ to INTERR ↑                            | (see Diagram F)                                |      | 40  | ns |

| 54  | t <sub>PD</sub>                                         | CYCREQ ↓ to MC <sub>0,1</sub>                   | Hidden-Refresh Cycles (see Diagram K)          |      | 46  | ns |

| 55  | t <sub>PD</sub>                                         | CLK ↓ to MC <sub>0,1</sub>                      | Refresh Cycles Only (see Diagram L)            |      | 24  | ns |