# Content Addressable Data Manager Am95C85

## **Technical Manual**

2

# **Advanced Micro Devices**

# Am95C85 (CADM) Content Addressable Data Manager

# **Technical Manual**

© 1986 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The performance characteristics listed in this technical manual are guaranteed by specific tests, correlated testing, guard banding, design and other practices common to the industry. For specific testing details contact your local AMD sales representative. The company assumes no responsibility for the use of any circuits described herein.

> 901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

#### ACKNOWLEDGEMENTS:

This technical manual was written by Sarosh Vesuna, Headquarters Applications Engineer. The Senior Technical Writer is Erland Kyllonen.

Contributions and assistance were provided by Dave Horton, Product Planning Manager, Rob Oliver, Senior Product Marketing Engineer, and Joseph Brcich, Headquarters Applications Manager.

### TABLE OF CONTENTS

| 1.1       Overview       1-1         1.2       Distinctive Characteristics       1-1         1.3       The Hardware Solution       1-1         1.4       Applications       1-1         1.4       Applications       1-1         1.4       Applications       1-1         1.4       Applications       1-1         2.5       FUNCTIONAL DESCRIPTION       2-1         2.1       General Description       2-1         2.2.1       Variable-Width Record       2-1         2.2.2       The Masking Option       2-1         2.2.3       Input Buffer Space       2-2         2.2.4       Remaining Space       2-3         2.3.1       Content Addressiable Array       2-3         2.3.2       Audressing Modes       2-3         2.3.3       Stack Access Mode       2-3         2.3.4       Sorting       2-4         2.5       Cascading Multiple CADMs       2-4         2.5.1       Cascading More Than 16 Am95C85s       2-4         2.6       Pin Description       2-6         2.6.1       Data Bus       2-6         D0-D7 Data Bus (Input/Output, 3-state)       2-6         2.6.1 <th>1.</th> <th>INTF</th> <th>ODUCTION</th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th>1-1</th>                                                                                                                       | 1. | INTF | ODUCTION                 |             |            |            |         |         |     | 1-1 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|--------------------------|-------------|------------|------------|---------|---------|-----|-----|

| 1.2       Distinctive Characteristics       1-1         1.3       The Hardware Solution       1-1         1.4       Applications       1-1         1.4       Applications       1-2         2.       FUNCTIONAL DESCRIPTION       2-1         2.1       General Description       2-1         2.2.1 Variable-Width Record       2-1         2.2.2 The Masking Option       2-1         2.2.2 The Masking Option       2-1         2.2.3 Input Buffer Space       2-3         2.3       Addressing Modes       2-3         2.3.1 Content Addressable Array       2-3         2.3.3 Stack Access Mode       2-3         2.3.4 Access Mode       2-3         2.3.5 Cascading Multiple CADMs       2-4         2.5.1 Cascading More Than 16 Am95C85s       2-4         2.5.2 Cascading More Than 16 Am95C85s       2-4         2.5.4 Data Bus       2-6         2.6 Pin Description       2-7         RST Reset (Input, Active LOW)       2-7         RST Reset (Input, Active LOW)       2-7         RST Reset (Input, Active LOW)       2-7         RE Read Enable (Input, Active LOW)       2-7         RE Read Enable (Input, Active LOW)       2-7                                                                                                                                                                                     |    | 1.1  | Overview                 |             |            |            |         |         |     | 1-1 |

| 1.3       The Hardware Solution       1-1         1.4       Applications       1-2         2.       FUNCTIONAL DESCRIPTION       1-2         2.1       General Description       1-2         2.2       Address Space       2-1         2.2.1       Variable-Width Record       2-1         2.2.1       Variable-Width Record       2-1         2.2.2       The Masking Option       2-1         2.2.3       Input Buffer Space       2-2         2.2.4       Remaining Space       2-3         2.3.1       Content Addressable Array       2-3         2.3.2       Auto-Increment Mode       2-3         2.3.3       Stack Access Mode       2-3         2.4       Sorting       2-4         2.5       Cascading Multiple CADMs       2-4         2.5.1       Cascading More Than 16 Am95C85s       2-4         2.5.2       Cascading More Than 16 Am95C85s       2-4         2.6.1       Interface Control       2-7         RST Reset (Input, Active LOW)       2-7         RST Reset (Input, Active LOW)       2-7         CC Command/Data (Input)       2-7         RST Reset (Input, Active LOW)       2-7         C.6                                                                                                                                                                                                             |    |      |                          |             |            |            |         |         |     |     |

| 1.4 Applications        1-2         2. FUNCTIONAL DESCRIPTION        2-1         2.1 General Description       2-1         2.2 Address Space       2-1         2.2.1 Variable-Width Record       2-1         2.2.2 The Masking Option       2-1         2.2.3 Input Buffer Space       2-1         2.2.4 Remaining Space       2-3         2.3 Addressing Modes       2-3         2.3.1 Content Addressable Array       2-3         2.3.3 Stack Access Mode       2-3         2.3.3 Stack Access Mode       2-3         2.4 Sorting       2-4         2.5.1 Cascading Mutiple CADMs       2-4         2.5.2 Cascading Mutiple CADMs       2-4         2.5.1 Cascading Mutiple CADMs       2-6         2.6.1 Data Bus       2-6         2.6.1 Description       2-7         RST Reset (Input/Active LOW)       2-7         RST Reset (Input, Active LOW)       2-7         CS Chip Select (Input, Active LOW)       2-7         CJ Command/Data (Input)       2-7         CJ Command/Data (Input)       2-7         CS Chip Select (Input, Active LOW)       2-7         CJ Command/Data (Input)       2-7         CJ Command/Data (Input)                                                                                                                                                                                               |    |      |                          |             |            |            |         |         |     |     |

| 2. FUNCTIONAL DESCRIPTION       2-1         2.1 General Description       2-1         2.2 Address Space       2-1         2.2.1 Variable-Width Record       2-1         2.2.2 The Masking Option       2-1         2.2.3 Input Buffer Space       2-1         2.2.4 Remaining Space       2-3         2.3 Addressing Modes       2-3         2.3 Addressing Modes       2-3         2.3.1 Content Addressable Array       2-3         2.3.3 Stack Access Mode       2-3         2.4 Sorting       2-4         2.5 Cascading Mutiple CADMs       2-4         2.5 Cascading More Than 16 Am95C85s       2-4         2.5 Cascading More Than 16 Am95C85s       2-4         2.5 Cascading More Than 16 Am95C85s       2-4         2.5 Chascading More Than 16 Am95C85s       2-4         2.6 Pin Description       2-7         RST Reset (Input, Active LOW)       2-7         RST Reset (Input, Active LOW)       2-7         C C Command/Data (Input)       2-7         C C Done Input/Output, Active LOW)       2-7         C C D Command/Data (Input)       2-7         C S Chip Select (Input, Active LOW)       2-7         C S Chip Select (Input, Active LOW)       2-7                                                                                                                                                             |    |      |                          |             |            |            |         |         |     |     |

| 2.1       General Description       2-1         2.2.1       Variable-Width Record       2-1         2.2.2       The Masking Option       2-1         2.2.3       Input Buffer Space       2-2         2.4       Remaining Space       2-3         2.3       Addressing Modes       2-3         2.3.1       Content Addressable Array       2-3         2.3.2       Auto-Increment Mode       2-3         2.3.3       Stack Access Mode       2-3         2.4       Sorting       2-4         2.5       Cascading Multiple CADMs       2-4         2.5       Cascading More Than 16 Am95C85s       2-4         2.5.1       Cascading More Than 16 Am95C85s       2-4         2.5.2       Cascading More Than 16 Am95C85s       2-4         2.5.1       Cascading More Than 16 Am95C85s       2-4         2.5.2       Cascading More Than 16 Am95C85s       2-6         2.6       Do-D7 Data Bus (Input/Output, 3-state)       2-6         2.6.1       Data Bus       2-7         RST Reset (Input, Active LOW)       2-7         RE Read Enable (Input, Active LOW)       2-7         WE Write Enable (Input, Active LOW)       2-7         C/D Command/Data (I                                                                                                                                                                          |    | 1.4  | Applications             | •••         | •••        | •••        | •••     | •••     | ••• | 1-2 |

| 2.1       General Description       2-1         2.2.1       Variable-Width Record       2-1         2.2.2       The Masking Option       2-1         2.2.3       Input Buffer Space       2-2         2.4       Remaining Space       2-3         2.3       Addressing Modes       2-3         2.3.1       Content Addressable Array       2-3         2.3.2       Auto-Increment Mode       2-3         2.3.3       Stack Access Mode       2-3         2.4       Sorting       2-4         2.5       Cascading Multiple CADMs       2-4         2.5       Cascading More Than 16 Am95C85s       2-4         2.5.1       Cascading More Than 16 Am95C85s       2-4         2.5.2       Cascading More Than 16 Am95C85s       2-4         2.5.1       Cascading More Than 16 Am95C85s       2-4         2.5.2       Cascading More Than 16 Am95C85s       2-6         2.6       Do-D7 Data Bus (Input/Output, 3-state)       2-6         2.6.1       Data Bus       2-7         RST Reset (Input, Active LOW)       2-7         RE Read Enable (Input, Active LOW)       2-7         WE Write Enable (Input, Active LOW)       2-7         C/D Command/Data (I                                                                                                                                                                          |    |      |                          |             |            |            |         |         |     |     |

| 2.2       Address Space           2-1         2.2.1       Variable-With Record         2-1         2.2.2       The Masking Option         2-1         2.2.3       Input Buffer Space         2-2         2.2.4       Remaining Space         2-3         2.3       Addressing Modes         2-3         2.3.1       Content Addressable Array        2-3         2.3.2       Auto-Increment Mode        2-3         2.3.3       Stack Access Mode        2-3         2.4       Sorting        2-4         2.5       Cascading Multiple CADMs        2-4         2.5.1       Cascading More Than 16 Am95C85s        2-4         2.5.2       Cascading More Than 16 Am95C85s        2-4         2.5.1       Cascading Mute Input/Active LOW)        2-7         RST Reset (Input, Active LOW)        2-7         RE Read Enable (Input, Active LOW)        2-7         CC Chip Select (Input, Active LOW)                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2. | FUN  | CTIONAL DESCRIPTION      | l.          |            |            |         |         |     | 2-1 |

| 2.2.1 Variable-Width Record       2.1         2.2.2 The Masking Option       2.1         2.2.3 Input Buffer Space       2.1         2.2.4 Remaining Space       2.3         2.3 Addressing Modes       2.3         2.3.1 Content Addressable Array       2.3         2.3.2 Auto-Increment Mode       2.3         2.3.3 Stack Access Mode       2.3         2.3.3 Stack Access Mode       2.3         2.4 Sorting       2.4         2.5 Cascading Multiple CADMs       2.4         2.5.1 Cascading Up To 16 Am95C85s       2.4         2.5.2 Cascading More Than 16 Am95C85s       2.4         2.5.2 Cascading More Than 16 Am95C85s       2.4         2.6.1 Data Bus       2.6         D0-D7 Data Bus (Input/Output, 3-state)       2.6         2.6.2 Interface Control       2.7         RST Reset (Input, Active LOW)       2.7         RE Read Enable (Input, Active LOW)       2.7         VE Write Enable (Input, Active LOW)       2.7         VE Write Enable (Input, Active LOW)       2.7         RE Read Enable (Input, Active LOW)       2.7         C Command/Data (Input)       2.7         C C Command/Data (Input)       2.7         C C Done (Input/Output, Active LOW, 3-state)       2.8 <td></td> <td>2.1</td> <td>General Description</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>2-1</td> |    | 2.1  | General Description      |             |            |            |         |         |     | 2-1 |

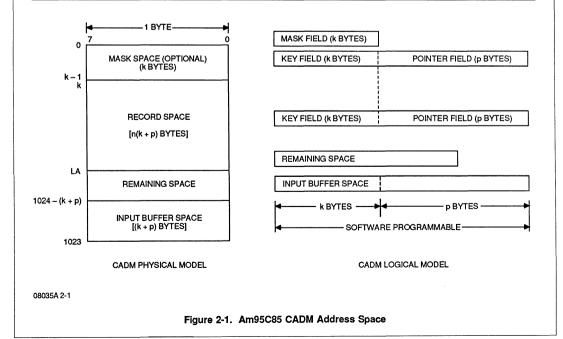

| 2.2.2 The Masking Option       2-1         2.2.3 Input Buffer Space       2-2         2.2.4 Remaining Space       2-3         2.3 Addressing Modes       2-3         2.3.1 Content Addressable Array       2-3         2.3.2 Auto-Increment Mode       2-3         2.3.3 Stack Access Mode       2-3         2.3.3 Stack Access Mode       2-3         2.4 Sorting       2-4         2.5 Cascading Multiple CADMs       2-4         2.5 Cascading More Than 16 Am95C85s       2-4         2.5.2 Cascading More Than 16 Am95C85s       2-4         2.6 Pin Description       2-6         2.6.1 Data Bus       2-7         RST Reset (Input, Active LOW)       2-7         RST Reset (Input, Active LOW)       2-7         RE Read Enable (Input, Active LOW)       2-7         RE Read Enable (Input, Active LOW)       2-7         C/D Command/Data (Input)       2-7         C/D Command/Data (Input)       2-7         C/D Command/Data (Input)       2-7         RE Read Enable (Input, Active LOW)       2-7         RE Read Enable (Input, Active LOW)       2-7         QC C/D Command/Data (Input)       2-7         QC D/D E Done (Input/Output, Active LOW, 3-state)       2-8 <tr< td=""><td></td><td>2.2</td><td>Address Space</td><td></td><td>•••</td><td></td><td></td><td></td><td></td><td>2-1</td></tr<>               |    | 2.2  | Address Space            |             | •••        |            |         |         |     | 2-1 |

| 2.2.3 Input Buffer Space       2.2         2.2.4 Remaining Space       2.3         2.3 Addressing Modes       2.3         2.3.1 Content Addressable Array       2.3         2.3.2 Auto-Increment Mode       2.3         2.3.3 Stack Access Mode       2.3         2.3.4 Ato-Increment Mode       2.3         2.3.5 Auto-Increment Mode       2.3         2.3.6 Ato-Increment Mode       2.3         2.3.7 Stack Access Mode       2.3         2.4 Sorting       2.3         2.5 Cascading Multiple CADMs       2.4         2.5 Cascading More Than 16 Am95C85s       2.4         2.5 Cascading More Than 16 Am95C85s       2.4         2.6 Pin Description       2.6         2.6.1 Data Bus (Input/Output, 3-state)       2.6         2.6.2 Interface Control       2.7         RE Reset (Input, Active LOW)       2.7         RE Read Enable (Input, Active LOW)       2.7         WE Write Enable (Input, Active LOW)       2.7         WE Write Enable (Input, Active LOW)       2.7         VE DONE Done (Input/Output, Active LOW)       2.7         VE DONE Done (Input/Output, Active LOW)       2.7         VE Transmit Up (Output, Active LOW, 3-state)       2.8         DONE Done (Input/Output, Active LOW,                                                                                                                 |    |      | 2.2.1 Variable-Width Red | cord        | •••        |            |         |         |     | 2-1 |

| 2.2.4 Remaining Space       2.3         2.3 Addressing Modes       2.3         2.3.1 Content Addressable Array       2.3         2.3.2 Auto-Increment Mode       2.3         2.3.3 Stack Access Mode       2.3         2.3.3 Stack Access Mode       2.3         2.4 Sorting       2.4         2.5 Cascading Multiple CADMs       2.4         2.5.1 Cascading Up To 16 Am95C85s       2.4         2.5.2 Cascading More Than 16 Am95C85s       2.4         2.5.2 Cascading More Than 16 Am95C85s       2.4         2.6.1 Data Bus       2.6         Do-D7 Data Bus (Input/Output, 3-state)       2.6         2.6.2 Interface Control       2.7         RST Reset (Input, Active LOW)       2.7         CS Chip Select (Input, Active LOW)       2.7         RE Read Enable (Input, Active LOW)       2.7         CD Command/Data (Input)       2.7         CD Command/Data (Input)       2.7         CD Command/Data (Input)       2.7         CD Commonication       2.7         RE Read Enable (Input, Active LOW)       2.7         CD Command/Data (Input)       2.7         CLK Clock (Input)       2.7         CLK Clock (Input)       2.7         CLK Clock (Input)                                                                                                                                                               |    |      | 2.2.2 The Masking Optio  | n           |            |            |         |         |     | 2-1 |

| 2.3       Addressing Modes         2.3         2.3.1       Content Addressable Array        2.3         2.3.2       Auto-Increment Mode        2.3         2.3.3       Stack Access Mode        2.3         2.3.3       Stack Access Mode        2.3         2.4       Sorting        2.4         2.5       Cascading Multiple CADMs        2.4         2.5.1       Cascading More Than 16 Am95C85s        2.4         2.5.2       Cascading More Than 16 Am95C85s        2.4         2.6.1       Data Bus         2.6         2.6.1       Data Bus (Input/Output, 3-state)        2.6         2.6.2       Interface Control         2.7         RST Reset (Input, Active LOW)        2.7       CS Chip Select (Input, Active LOW)       2.7         CS Chip Select (Input, Active LOW)        2.7       CS Chip Select (Input, Active LOW)       2.7         C/D Command/Data (Input)         2.7       CK Clock (Input)       2.7         C/D Commani/Data (Input, Active LOW)        2.7 <td></td> <td></td> <td>2.2.3 Input Buffer Space</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>2-2</td>                                                                                                                                                                                                              |    |      | 2.2.3 Input Buffer Space |             |            |            |         |         |     | 2-2 |

| 2.3.1 Content Addressable Array         2-3         2.3.2 Auto-Increment Mode         2-3         2.3.3 Stack Access Mode         2-3         2.3.3 Stack Access Mode         2-3         2.4 Sorting         2-4         2.5 Cascading Multiple CADMs        2-4         2.5.2 Cascading More Than 16 Am95C85s        2-4         2.5.2 Cascading More Than 16 Am95C85s        2-4         2.6 Pin Description         2-6         2.6.1 Data Bus         2-6         D0-D7 Data Bus (Input/Output, 3-state)        2-7         RST Reset (Input, Active LOW)        2-7         RE Read Enable (Input, Active LOW)        2-7         C/D Command/Data (Input)        2-8         T/R Transmit/Receive (Output)        2-8         <                                                                                                                                                                                                                                                                                                                                                                                                                  |    |      | 2.2.4 Remaining Space    |             |            |            |         |         |     | 2-3 |

| 2.3.1 Content Addressable Array         2-3         2.3.2 Auto-Increment Mode         2-3         2.3.3 Stack Access Mode         2-3         2.3.3 Stack Access Mode         2-3         2.4 Sorting         2-4         2.5 Cascading Multiple CADMs        2-4         2.5.2 Cascading More Than 16 Am95C85s        2-4         2.5.2 Cascading More Than 16 Am95C85s        2-4         2.6 Pin Description         2-6         2.6.1 Data Bus         2-6         D0-D7 Data Bus (Input/Output, 3-state)        2-7         RST Reset (Input, Active LOW)        2-7         RE Read Enable (Input, Active LOW)        2-7         C/D Command/Data (Input)        2-8         T/R Transmit/Receive (Output)        2-8         <                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 2.3  | Addressing Modes         |             |            |            |         |         |     | 2-3 |

| 2.3.2 Auto-Increment Mode       2.3         2.3.3 Stack Access Mode       2-3         2.4 Sorting       2-3         2.5 Cascading Multiple CADMs       2-4         2.5.1 Cascading Up To 16 Am95C85s       2-4         2.5.2 Cascading More Than 16 Am95C85s       2-4         2.6 Pin Description       2-4         2.6.1 Data Bus       2-4         2.6.2 Interface Control       2-6         2.6.2 Interface Control       2-7         RST Reset (Input, Active LOW)       2-7         CS Chip Select (Input, Active LOW)       2-7         CS Chip Select (Input, Active LOW)       2-7         CD Command/Data (Input)       2-7         CVD Command/Data (Input)       2-7 </td <td></td> <td></td> <td></td> <td>ole Array</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>2-3</td>                                          |    |      |                          | ole Array   |            |            |         |         |     | 2-3 |

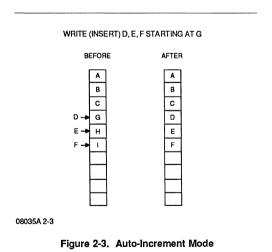

| 2.3.3 Stack Access Mode         2-3         2.4 Sorting         2-4         2.5 Cascading Multiple CADMs        2-4         2.5.1 Cascading Up To 16 Am95C85s        2-4         2.5.2 Cascading More Than 16 Am95C85s        2-4         2.6 Pin Description         2-6         2.6.1 Data Bus         2-6         2.6.2 Interface Control         2-7         RST Reset (Input, Active LOW)        2-7         RE Read Enable (Input, Active LOW)        2-7         RE Read Enable (Input, Active LOW)        2-7         CS Chip Select (Input, Active LOW)        2-7         RE Read Enable (Input, Active LOW)        2-7         C/D Command/Data (Input)        2-7         CLK Clock (Input)        2-7         CLK Clock (Input)        2-7         C.A.T Transmit/Receive (Output)        2-8         TAT Status (Output, Active LOW, 3-state)        2-8         STAT Status (Output, Active LOW, 3-state)        2-9         TUP Transm                                                                                                                                                                                                                                                                                                                                                                                  |    |      |                          | -           |            |            |         |         |     | 2-3 |

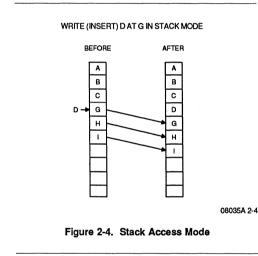

| 2.4       Sorting         2-4         2.5       Cascading Multiple CADMs         2-4         2.5.1       Cascading Up To 16 Am95C85s        2-4         2.5.2       Cascading More Than 16 Am95C85s        2-4         2.5.2       Cascading More Than 16 Am95C85s        2-4         2.6       Pin Description         2-6         2.6.1       Data Bus         2-6         2.6.1       Data Bus (Input/Output, 3-state)        2-7         RST       Reset (Input, Active LOW)        2-7         RST       Reset (Input, Active LOW)        2-7         RE       Read Enable (Input, Active LOW)        2-7         WE       Write Enable (Input, Active LOW)        2-7         C/D       Command/Data (Input)        2-7         C/LK       Clock (Input)        2-7         C/D       Command/Data (Input)        2-7         C/LK       Clock (Input)        2-7         C/D       Command/Data (Input, Active LOW, 3-state)       2-8                                                                                                                                                                                                                                                                                                                                                                                           |    |      |                          |             |            |            |         |         |     |     |

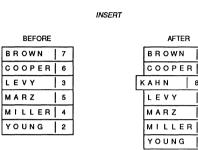

| 2.5       Cascading Multiple CADMs         2.4         2.5.1       Cascading Up To 16 Am95C85s        2.4         2.5.2       Cascading More Than 16 Am95C85s        2.4         2.6       Pin Description        2.6         2.6.1       Data Bus        2.6         D0-D7       Data Bus (Input/Output, 3-state)        2.6         2.6.2       Interface Control         2.7         RST       Reset (Input, Active LOW)        2.7         CS       Chip Select (Input, Active LOW)        2.7         WE       Write Enable (Input, Active LOW)        2.7         C/D       Command/Data (Input)        2.7         C/D       Comm                                                                                                                                                                                                                                                                                                                                                                                    |    | 2.4  |                          |             |            |            |         |         |     |     |

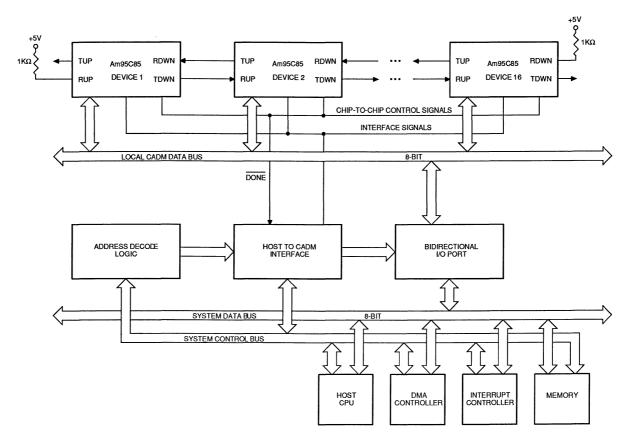

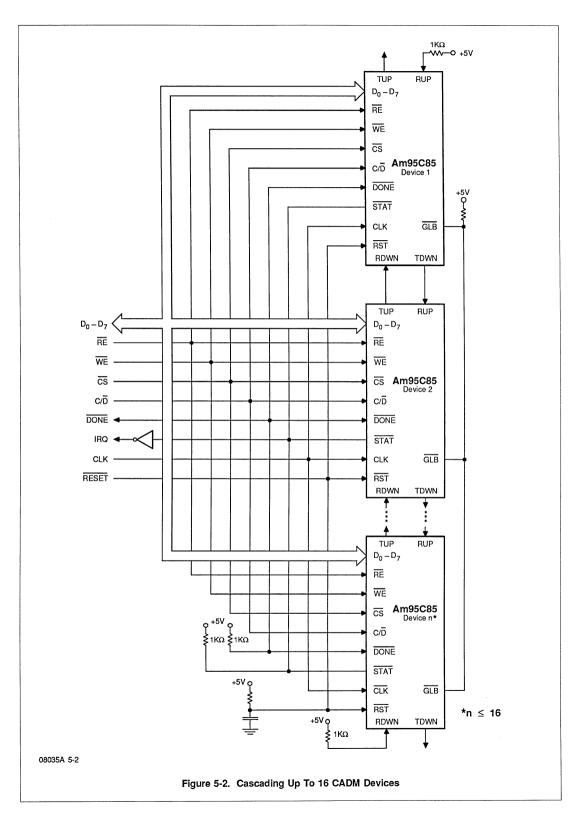

| 2.5.1 Cascading Up To 16 Am95C85s         2-4         2.5.2 Cascading More Than 16 Am95C85s        2-4         2.6 Pin Description         2-6         2.6.1 Data Bus         2-6         D0-D7 Data Bus (Input/Output, 3-state)        2-6         2.6.2 Interface Control            RST Reset (Input, Active LOW)        2-7         CS Chip Select (Input, Active LOW)        2-7         RE Read Enable (Input, Active LOW)        2-7         C/D Command/Data (Input)        2-7         C/D Command/Data (Input/Output, Active LOW)       2-7         C/D Command/Data (Input/Output, Active LOW, 3-state)       2-8         T/A Transmit Up (Output, Active LOW, 3-state)       2-9         TUP Transmit Up (Output, Active HIGH) <td></td>                                                                                                                                                                                                                  |    |      |                          |             |            |            |         |         |     |     |

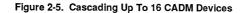

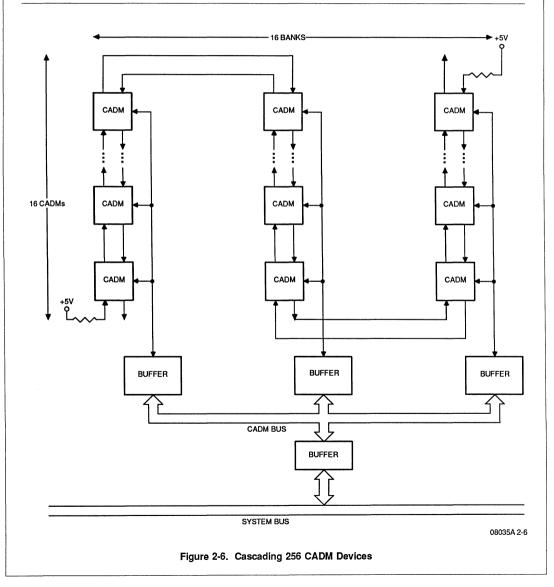

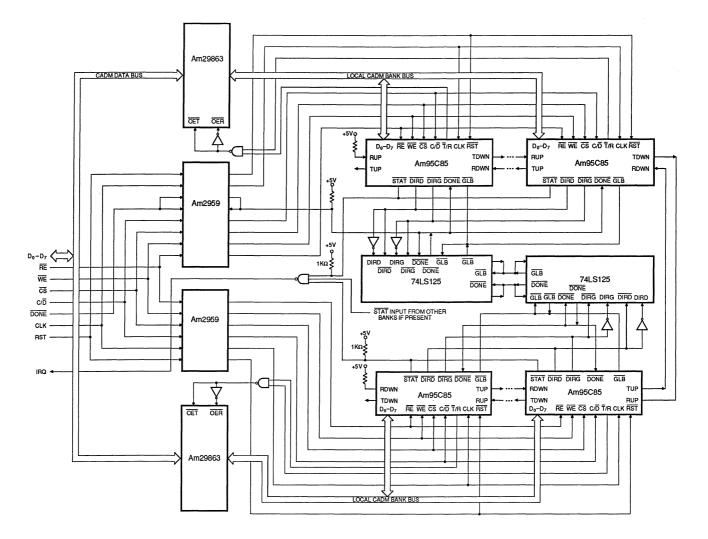

| 2.5.2 Cascading More Than 16 Am95C85s         2-4         2.6 Pin Description          2-6         2.6.1 Data Bus          2-6         D0-D7 Data Bus (Input/Output, 3-state)        2-6         2.6.2 Interface Control         2-7         RST Reset (Input, Active LOW)        2-7         CS Chip Select (Input, Active LOW)        2-7         RE Read Enable (Input, Active LOW)        2-7         WE Write Enable (Input, Active LOW)        2-7         C/D Command/Data (Input)        2-7         C/D Command/Data (Input)        2-7         C/LK Clock (Input)        2-8         T/R Transmit/Receive (Output, Active LOW, 3-state)       2-9         2.6.3 Chip to Chip Communication        2-9         TUP Transmit Down (Output, Activ                                                                                                                                                                                                                                                                                                                                                                                  |    |      |                          |             |            |            |         |         |     |     |

| 2.6 Pin Description           2-6         2.6.1 Data Bus          2-6         D0-D7 Data Bus (Input/Output, 3-state)         2-6         2.6.2 Interface Control          2-7         RST Reset (Input, Active LOW)         2-7         CS Chip Select (Input, Active LOW)         2-7         RE Read Enable (Input, Active LOW)         2-7         WE Write Enable (Input, Active LOW)         2-7         C/D Command/Data (Input)         2-7         C/D Command/Data (Input)         2-7         C/D Command/Data (Input)         2-7         CLK Clock (Input)         2-7         CLK Clock (Input)         2-8         T/R Transmit/Receive (Output)         2-8         STAT Status (Output, Active LOW, 3-state)        2-9         2.6.3 Chip to Chip Communication        2-9         TUP Transmit Down (Output, Active HIGH)        <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |      |                          |             |            |            |         |         |     |     |

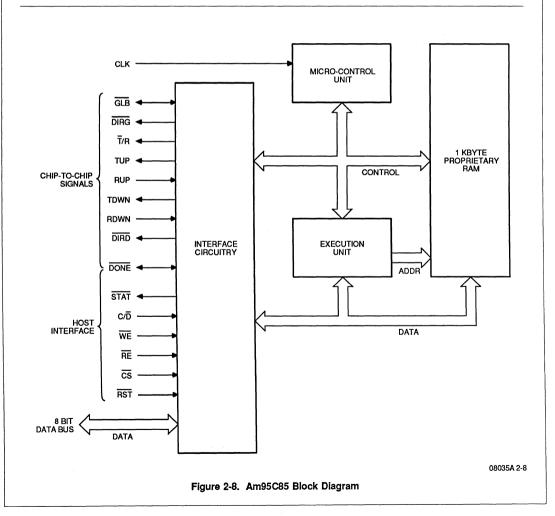

| 2.6.1 Data Bus          2-6         D0-D7 Data Bus (Input/Output, 3-state)         2-6         2.6.2 Interface Control         2-7         RST Reset (Input, Active LOW)         2-7         RST Reset (Input, Active LOW)         2-7         RE Read Enable (Input, Active LOW)         2-7         WE Write Enable (Input, Active LOW)         2-7         C/D Command/Data (Input)         2-7         C/D Command/Data (Input)         2-7         C/D Command/Data (Input)         2-7         C/D Command/Data (Input)         2-7         CLK Clock (Input)         2-7         CLK Clock (Input)         2-8         T/R Transmit/Receive (Output)         2-8         STAT Status (Output, Active LOW, 3-state)        2-9         TUP Transmit Up (Output, Active HIGH)        2-9         TUP Transmit Down (Output, Active HIGH)        2-9         RUP Receive                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 26   | •                        |             |            |            |         |         |     |     |

| D0-D7 Data Bus (Input/Output, 3-state)         2-6         2.6.2 Interface Control         2-7         RST Reset (Input, Active LOW)         2-7         CS Chip Select (Input, Active LOW)         2-7         RE Read Enable (Input, Active LOW)         2-7         WE Write Enable (Input, Active LOW)         2-7         C/D Command/Data (Input)         2-7         C/LK Clock (Input)         2-7         CLK Clock (Input)         2-7         CLK Clock (Input)         2-7         CLK Clock (Input)         2-7         CLK Clock (Input)         2-8         T/R Transmit/Receive (Output)         2-8         STAT Status (Output, Active LOW, 3-state)        2-9         TUP Transmit Up (Output, Active HIGH)        2-9         TUP Transmit Down (Output, Active HIGH)        2-9         RUP Receive from the Up Direction (Input, Active HIGH)        2-9         RDWN Receive from the Do                                                                                                                                                                                                                                                                                                                                                                                                                        |    | 2.0  | •                        |             |            |            |         |         |     |     |

| 2.6.2 Interface Control          2-7         RST Reset (Input, Active LOW)         2-7         CS Chip Select (Input, Active LOW)         2-7         RE Read Enable (Input, Active LOW)         2-7         WE Write Enable (Input, Active LOW)         2-7         WE Write Enable (Input, Active LOW)         2-7         C/D Command/Data (Input)         2-7         C/K Clock (Input)         2-7         CLK Clock (Input)         2-7         CLK Clock (Input)         2-7         CLK Clock (Input)         2-7         CLK Clock (Input)         2-8         T/R Transmit/Receive (Output)         2-8         STAT Status (Output, Active LOW, 3-state)        2-9         TUP Transmit Up (Output, Active HIGH)        2-9         TUP Transmit Down (Output, Active HIGH)        2-9         RUP Receive from the Up Direction (Input, Active HIGH)        2-9         RDWN Rece                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |      |                          |             |            |            |         |         |     |     |

| RST       Reset (Input, Active LOW)         2-7         CS       Chip Select (Input, Active LOW)         2-7         RE       Read Enable (Input, Active LOW)         2-7         WE       Write Enable (Input, Active LOW)         2-7         C/D       Command/Data (Input)         2-7         C/D       Command/Data (Input)         2-7         CLK       Clock (Input)         2-8         T/R       Transmit/Receive (Output)         2-8         STAT       Status (Output, Active LOW, 3-state)        2-9         TUP       Transmit Up (Output, Active HIGH)        2-9         TDWN Transmit Down (Output, Active HIGH)        2-9         RDWN Receive from the Down Direction (Input, Active HIGH)       <                                                                                                                                                                                                                                                                                                                                                                                                                               |    |      | •                        | •           | 1, 0-State |            |         |         |     |     |

| CS       Chip Select (Input, Active LOW)         2-7         RE       Read Enable (Input, Active LOW)         2-7         WE       Write Enable (Input, Active LOW)         2-7         C/D       Command/Data (Input)         2-7         C/D       Command/Data (Input)         2-7         CLK       Clock (Input)         2-8         T/R       Transmit/Receive (Output)         2-9         STAT       Status (Output, Active LOW, 3-state)        2-9         TUP       Transmit Up (Output, Active HIGH)        2-9         TDWN Transmit Down (Output, Active HIGH)        2-9         RDWN Receive from the Down Direction (Input, Active HIGH)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |      |                          |             | <br>W/\    |            |         |         |     |     |

| RE       Read Enable (Input, Active LOW)        2-7         WE       Write Enable (Input, Active LOW)        2-7         C/D       Command/Data (Input)         2-7         C/D       Command/Data (Input)         2-7         CLK       Clock (Input)         2-8         T/R       Transmit/Receive (Output)         2-8         STAT       Status (Output, Active LOW, 3-state)        2-9         TUP       Transmit Up (Output, Active HIGH)        2-9         TDWN Transmit Down (Output, Active HIGH)        2-9         RDWN Receive from the Up Direction (Input, Active HIGH)        2-9         GLB       Global (Input/Output, 3-state)         2-9                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |      |                          |             |            |            |         |         |     |     |

| WE       Write Enable (Input, Active LOW)        2-7         C/D       Command/Data (Input)         2-7         CLK       Clock (Input)         2-7         CLK       Clock (Input)         2-8         T/R       Transmit/Receive (Output)         2-8         DONE       Done (Input/Output, Active LOW, 3-state)        2-9         26.3       Chip to Chip Communication        2-9         TUP       Transmit Up (Output, Active HGH)        2-9         TUP Transmit Down (Output, Active HIGH)        2-9         RUP Receive from the Up Direction (Input, Active HIGH)        2-9         RDWN Receive from the Down Direction (Input, Active HIGH)        2-9         GLB       Global (Input/Output, 3-state)         2-9         DIRG       Direction of GLB Signal (Output, Active LOW, Open Dr.)       2-9       2-9         DIRD       Direction of DONE Signal (Output, Active LOW, Open Dr.)       2-9         QLR       State         2-9         ONR       State         2-9                                                                                                                                                                                                                                                                                                                                         |    |      |                          |             |            | •••        |         |         |     |     |

| C/D Command/Data (Input)         2-7         CLK Clock (Input)          2-8         T/R Transmit/Receive (Output)         2-8         DONE Done (Input/Output, Active LOW, 3-state)        2-8         STAT Status (Output, Active LOW, 3-state)        2-9         2.6.3 Chip to Chip Communication         2-9         TUP Transmit Up (Output, Active HIGH)        2-9         TDWN Transmit Down (Output, Active HIGH)        2-9         RUP Receive from the Up Direction (Input, Active HIGH)        2-9         RDWN Receive from the Down Direction (Input, Active HIGH)        2-9         GLB Global (Input/Output, 3-state)         2-9         DIRG Direction of GLB Signal (Output, Active LOW, Open Dr.)        2-9         DIRD Direction of DONE Signal (Output, Active LOW, Open Dr.)        2-9         QLR Supply Pins          2-9         OND Ownerdupt          2-9         DIRD Direction of DONE Signal (Output, Active LOW, Open Dr.)        2-9         OND Ownerdupt                                                                                                                                                                                                                                                                                                                                        |    |      |                          |             |            |            |         |         |     |     |

| CLK Clock (Input)           2-8           T/R         Transmit/Receive (Output)           2-8           DONE         Done (Input/Output, Active LOW, 3-state)          2-8           STAT         Status (Output, Active LOW, 3-state)          2-9           2.6.3         Chip to Chip Communication          2-9           TUP Transmit Up (Output, Active HIGH)          2-9           TDWN Transmit Down (Output, Active HIGH)          2-9           RUP Receive from the Up Direction (Input, Active HIGH)          2-9           RDWN Receive from the Down Direction (Input, Active HIGH)          2-9           GLB         Global (Input/Output, 3-state)           2-9           DIRG         Direction of GLB Signal (Output, Active LOW, Open Dr.)         2-9         2-9         2-9           DIRD         Direction of DONE Signal (Output, Active LOW, Open Dr.)          2-9         2-9           OLRO         Cower Supply           2-9         2-9                                                                                                                                                                                                                                                                                                                                                              |    |      |                          |             |            |            |         |         |     |     |

| T/R Transmit/Receive (Output)2-8DONE Done (Input/Output, Active LOW, 3-state)2-8STAT Status (Output, Active LOW, 3-state)2-92.6.3 Chip to Chip Communication2-9TUP Transmit Up (Output, Active HIGH)2-9TDWN Transmit Down (Output, Active HIGH)2-9RUP Receive from the Up Direction (Input, Active HIGH)2-9RDWN Receive from the Down Direction (Input, Active HIGH)2-9GLB Global (Input/Output, 3-state)2-9DIRG Direction of GLB Signal (Output, Active LOW, Open Dr.)2-9DIRD Direction of DONE Signal (Output, Active LOW, Open Dr.)2-9Vcc Power Supply2-9ONE Ownerd2-9ONE Ownerd2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |      |                          |             |            |            |         |         |     |     |

| DONEDone (Input/Output, Active LOW, 3-state)2-8STATStatus (Output, Active LOW, 3-state)2-92.6.3Chip to Chip Communication2-9TUPTransmit Up (Output, Active HIGH)2-9TDWNTransmit Down (Output, Active HIGH)2-9RUPReceive from the Up Direction (Input, Active HIGH)2-9RDWNReceive from the Down Direction (Input, Active HIGH)2-9GLBGlobal (Input/Output, 3-state)2-9DIRGDirection of GLB Signal (Output, Active LOW, Open Dr.)2-9DIRDDirection of DONE Signal (Output, Active LOW, Open Dr.)2-9VccPower Supply2-9ONDONDOND2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |      |                          |             |            |            |         |         |     |     |

| STAT Status (Output, Active LOW, 3-state)2-92.6.3 Chip to Chip Communication2-9TUP Transmit Up (Output, Active HIGH)2-9TDWN Transmit Down (Output, Active HIGH)2-9RUP Receive from the Up Direction (Input, Active HIGH)2-9RDWN Receive from the Down Direction (Input, Active HIGH)2-9GLB Global (Input/Output, 3-state)2-9DIRG Direction of GLB Signal (Output, Active LOW, Open Dr.)2-9DIRD Direction of DONE Signal (Output, Active LOW, Open Dr.)2-9Vcc Power Supply2-9OND Owned2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |      |                          |             |            |            |         |         | ••• |     |

| 2.6.3 Chip to Chip Communication         2-9         TUP Transmit Up (Output, Active HIGH)        2-9         TDWN Transmit Down (Output, Active HIGH)        2-9         RUP Receive from the Up Direction (Input, Active HIGH)        2-9         RDWN Receive from the Down Direction (Input, Active HIGH)        2-9         GLB Global (Input/Output, 3-state)         2-9         DIRG Direction of GLB Signal (Output, Active LOW, Open Dr.)        2-9         DIRD Direction of DONE Signal (Output, Active LOW, Open Dr.)        2-9         Vcc Power Supply          2-9         ONE Ownerd         2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |      |                          |             |            |            |         | •••     | ••• |     |

| TUP Transmit Up (Output, Active HIGH)2-9TDWN Transmit Down (Output, Active HIGH)2-9RUP Receive from the Up Direction (Input, Active HIGH)2-9RDWN Receive from the Down Direction (Input, Active HIGH)2-9GLB Global (Input/Output, 3-state)2-9DIRG Direction of GLB Signal (Output, Active LOW, Open Dr.)2-9DIRD Direction of DONE Signal (Output, Active LOW, Open Dr.)2-9Vcc Power Supply2-9OND Owned2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |      |                          |             |            |            |         |         | ••• |     |

| TDWN Transmit Down (Output, Active HIGH)        2-9         RUP Receive from the Up Direction (Input, Active HIGH)        2-9         RDWN Receive from the Down Direction (Input, Active HIGH)        2-9         GLB Global (Input/Output, 3-state)         2-9         DIRG Direction of GLB Signal (Output, Active LOW, Open Dr.)        2-9         DIRD Direction of DONE Signal (Output, Active LOW, Open Dr.)        2-9         Vcc Power Supply          2-9         OND Owned          2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |      |                          |             |            |            | •••     |         | ••• |     |

| RUP Receive from the Up Direction (Input, Active HIGH)        2-9         RDWN Receive from the Down Direction (Input, Active HIGH)        2-9         GLB Global (Input/Output, 3-state)         2-9         DIRG Direction of GLB Signal (Output, Active LOW, Open Dr.)        2-9         DIRD Direction of DONE Signal (Output, Active LOW, Open Dr.)        2-9         2.6.4 Supply Pins          2-9         Vcc Power Supply          2-9         OND Owned          2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |      |                          |             |            |            |         |         | ••• |     |

| RDWN Receive from the Down Direction (Input, Active HIGH)       2-9         GLB Global (Input/Output, 3-state)        2-9         DIRG Direction of GLB Signal (Output, Active LOW, Open Dr.)        2-9         DIRD Direction of DONE Signal (Output, Active LOW, Open Dr.)        2-9         Vcc Power Supply          2-9         OND Owned          2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |      |                          |             |            |            |         |         |     |     |

| GLB         Global (Input/Output, 3-state)           2-9           DIRG         Direction of GLB Signal (Output, Active LOW, Open Dr.)          2-9           DIRD         Direction of DONE Signal (Output, Active LOW, Open Dr.)          2-9           2.6.4         Supply Pins            2-9           Vcc         Power Supply            2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |      |                          |             |            |            |         |         |     |     |

| DIRG       Direction of GLB Signal (Output, Active LOW, Open Dr.)        2-9         DIRD       Direction of DONE Signal (Output, Active LOW, Open Dr.)        2-9         2.6.4       Supply Pins          2-9         Vcc       Power Supply          2-9         OND       Owner Supply          2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |      |                          |             |            |            |         | IGH)    |     |     |

| DIRD         Direction of DONE Signal (Output, Active LOW, Open Dr.)         2-9           2.6.4 Supply Pins           2-9           Vcc Power Supply           2-9           OND         Owner Supply           2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |      | GLB Global (Input        | /Output, 3- | state)     |            |         |         |     |     |

| 2.6.4 Supply Pins            2-9           Vcc Power Supply            2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |      |                          |             |            |            |         |         | ••• |     |

| Vcc Power Supply 2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |      |                          | DONE Sig    | nal (Outp  | ut, Active | LOW, Op | en Dr.) |     | 2-9 |

| Vcc Power Supply 2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |      |                          |             |            |            |         |         |     | 2-9 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |      |                          |             |            |            |         |         |     | 2-9 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |      | GND Ground               |             |            |            |         |         |     | 2-9 |

i

| (<br>(                                            | 3-1<br>3-1<br>3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12 |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| ····<br>····<br>····<br>····<br>···<br>···<br>··· | 3-1<br>3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11                              |

| ····<br>····<br>····<br>····<br>···<br>···<br>··· | 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11                                     |

| ····<br>···<br>···<br>···<br>···<br>···           | 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11                                     |

| ····<br>····<br>····<br>····<br>···               | 3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11                                            |

| ····<br>···<br>···<br>···<br>···<br>···           | 3-3<br>3-4<br>3-5<br>3-7<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11                                                   |

| ····<br>····<br>····<br>···                       | 3-4<br>3-5<br>3-7<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11                                                          |

| ····<br>····<br>····<br>····<br>····              | 3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11                                                                 |

| ····<br>····<br>··· {<br>··· {<br>··· {           | 3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11                                                                        |

| ····<br>····<br>··· {<br>··· {                    | 3-7<br>3-8<br>3-9<br>3-10<br>3-11                                                                               |

| ····<br>··· (<br>··· (<br>··· (                   | 3-8<br>3-9<br>3-10<br>3-11                                                                                      |

| ···· 6                                            | 3-9<br>3-10<br>3-11                                                                                             |

| 6                                                 | 3-10<br>3-11                                                                                                    |

| 6                                                 | 3-10<br>3-11                                                                                                    |

| (                                                 | 3-11                                                                                                            |

| (                                                 |                                                                                                                 |

| (                                                 | 0-12                                                                                                            |

|                                                   | 2 12                                                                                                            |

|                                                   | 3-13                                                                                                            |

|                                                   | 3-14                                                                                                            |

|                                                   | 3-15                                                                                                            |

|                                                   | 3-16                                                                                                            |

| :                                                 | 3-17                                                                                                            |

| ····                                              | 4-1<br>4-1                                                                                                      |

| •••                                               | 4-1                                                                                                             |

| •••                                               | 4-1                                                                                                             |

| •••                                               | 4-2                                                                                                             |

| •••                                               | 4-2                                                                                                             |

|                                                   | 4-3                                                                                                             |

|                                                   | 4-4                                                                                                             |

|                                                   | 4-4                                                                                                             |

|                                                   | 4-5                                                                                                             |

|                                                   | 4-5                                                                                                             |

|                                                   | 4-5                                                                                                             |

|                                                   | 4-5                                                                                                             |

|                                                   |                                                                                                                 |

|                                                   | 4-5                                                                                                             |

|                                                   | 4-5<br>4-5                                                                                                      |

|                                                   |                                                                                                                 |

|                                                   | 4-5<br>5-1                                                                                                      |

| ····<br>···                                       | 4-5<br>5-1<br>5-1                                                                                               |

|                                                   | 4-5<br>5-1<br>5-1<br>5-1                                                                                        |

| ····<br>···                                       | 4-5<br>5-1<br>5-1<br>5-1<br>5-1<br>5-1                                                                          |

| ····<br>····                                      | 4-5<br>5-1<br>5-1<br>5-1<br>5-1<br>5-2                                                                          |

| ····<br>····                                      | 4-5<br>5-1<br>5-1<br>5-1<br>5-1<br>5-2<br>5-2                                                                   |

| ····<br>···<br>···                                | 4-5<br>5-1<br>5-1<br>5-1<br>5-1<br>5-2<br>5-2<br>5-2<br>5-2                                                     |

| ····<br>···<br>···<br>···                         | 4-5<br>5-1<br>5-1<br>5-1<br>5-1<br>5-2<br>5-2                                                                   |

| ····<br>····<br>···<br>···                        | 4-5<br>5-1<br>5-1<br>5-1<br>5-1<br>5-2<br>5-2<br>5-2<br>5-2                                                     |

|                                                   | ····<br>···<br>···<br>···<br>···                                                                                |

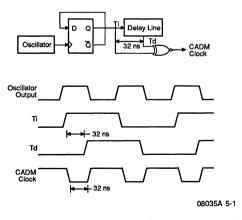

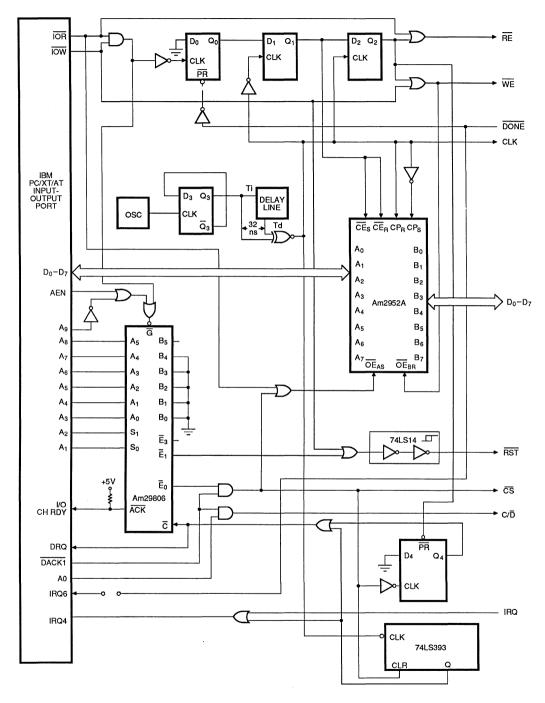

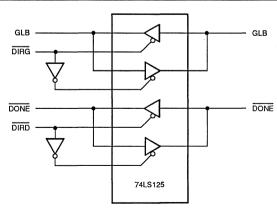

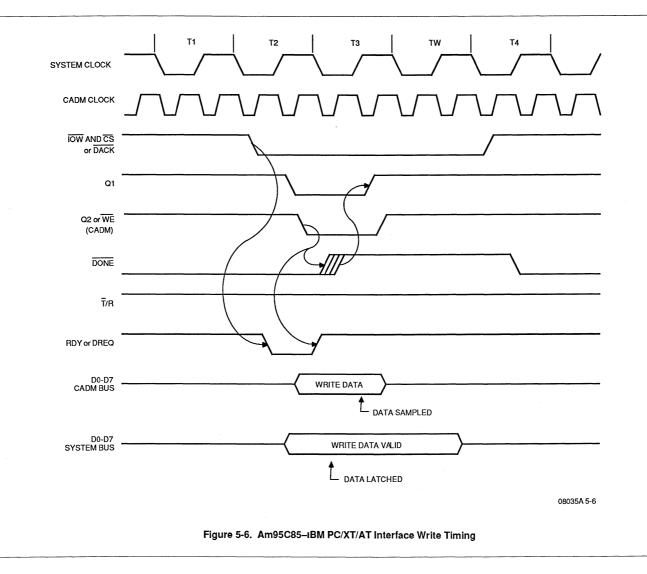

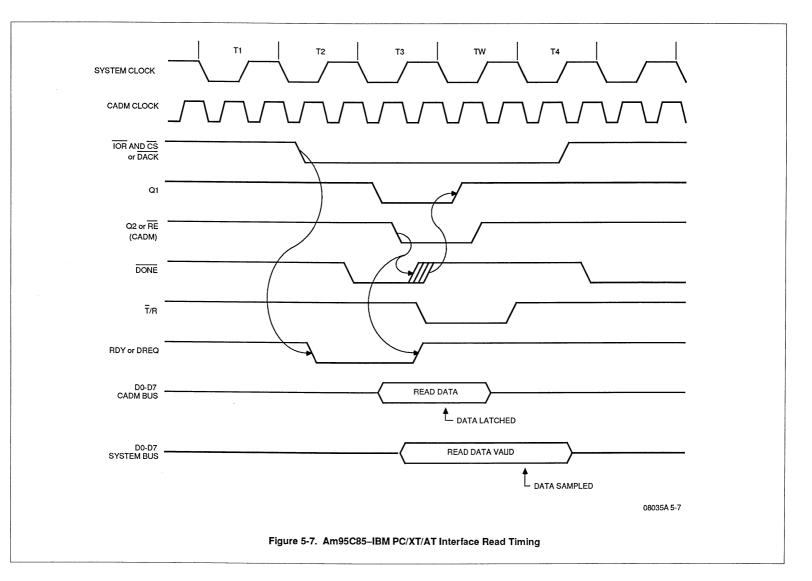

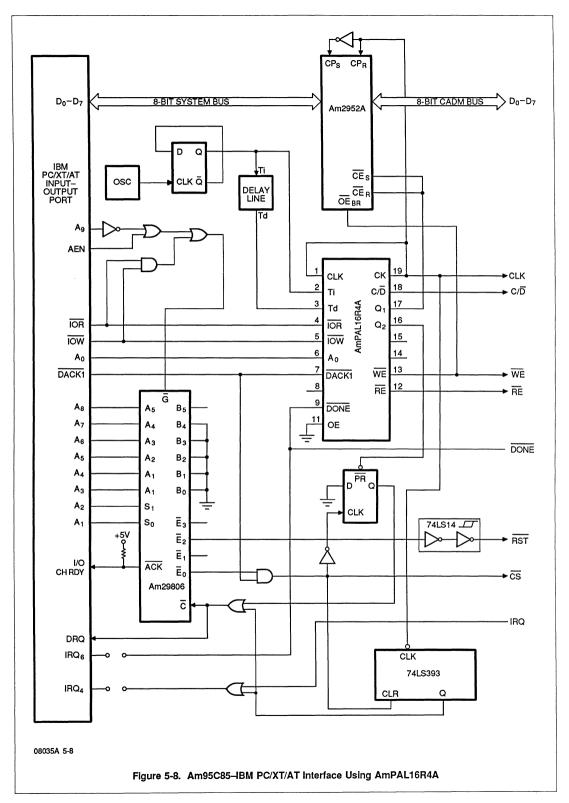

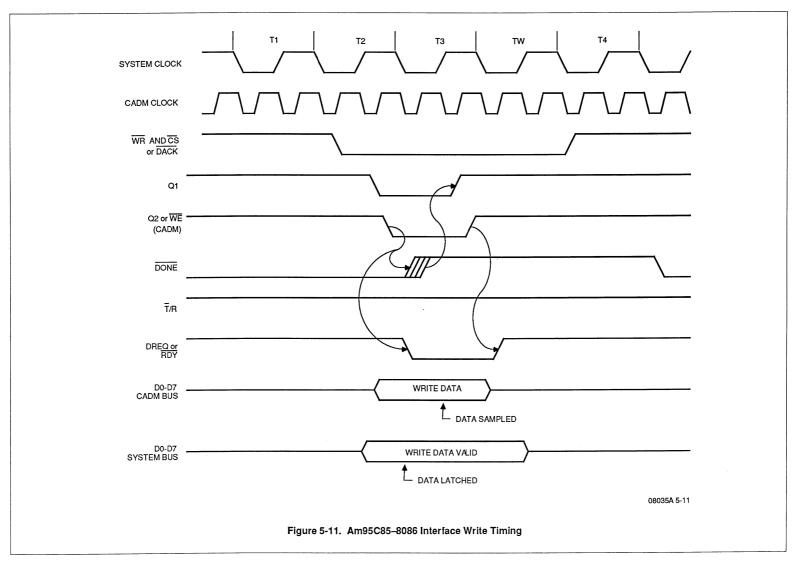

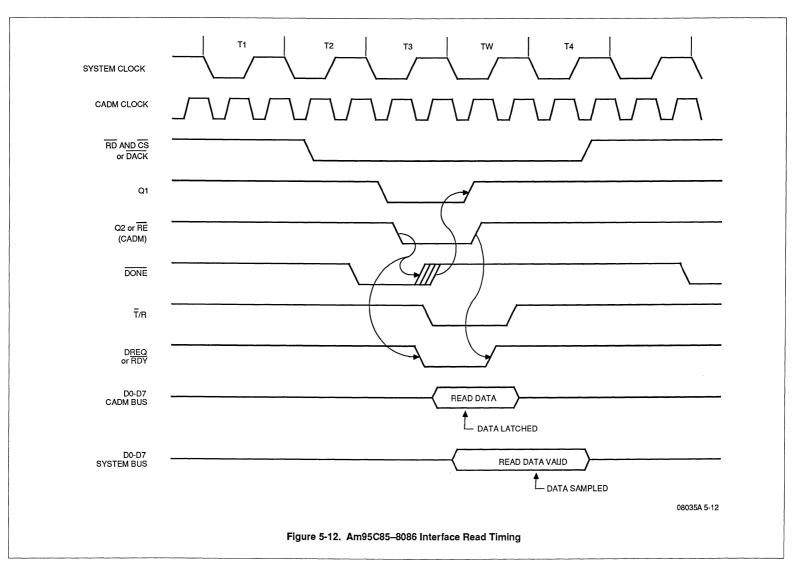

| 5.10.1 Synchronizing t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      | in IBM PC/X                          | T/AT   |                                                |                                         | 5-7                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------|------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |                                      |        |                                                |                                         | 5-7                                                                                            |

| 5.10.2 Chip Select Log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |                                      |        |                                                |                                         | 5-7                                                                                            |

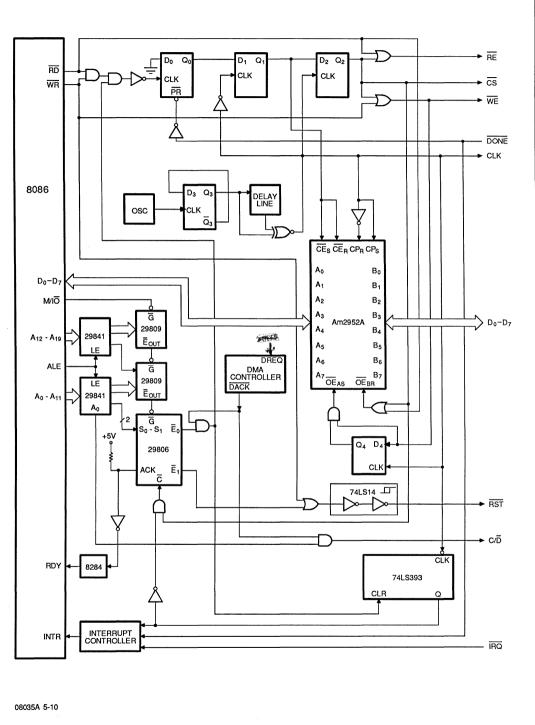

| 5.10.3 Generating the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Ready Signal                                                                                                                                                         | •••                                  |        |                                                |                                         | 5-10                                                                                           |