#### **PRELIMINARY**

#### DISTINCTIVE CHARACTERISTICS

- Expandable

- 8-bit slice, cascadable up to 16 bits

- Deep stack

- A 33-deep on-chip stack is used for subroutine linkage, interrupt handling, and loop control.

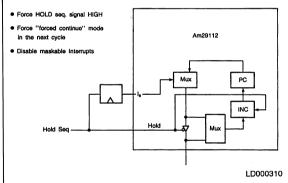

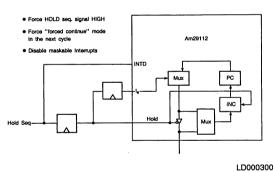

- Hold feature

- A hold pin facilitates multiple sequencer implementations

- Interruptible at the microprogram level Two kinds of interrupts: maskable and unmaskable.

- Powerful loop control

- When cascaded, two counters can act as a single 16-bit counter or two independent 8-bit counters.

- Powerful addressing modes

- Features direct, multiway, multiway relative, and program counter relative addressing.

#### **GENERAL DESCRIPTION**

The Am29112 is a high-performance interruptible microprogram sequencer intended for use in very high-speed microprogrammed machines and optimized for the new state-of-the-art ALUs such as the Am29116A 16-Bit Bipolar Microprocessor.

The Am29112 is designed to operate in 10-MHz microprogrammed systems.

It has an instruction set featuring relative and multiway branching, a rich variety of looping constructs, and provision for loading and unloading the on-chip stack.

Interrupts are accepted at the microcycle level and serviced in a manner completely transparent to the interrupted microcode.

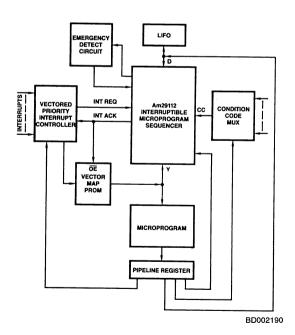

#### **BLOCK DIAGRAM\***

\*Typical System Diagram — Am29112 in a Single Pipelined System (See Figure 1 for Detailed Block Digram)

> Publication # Amendment Rev. 03657 Issue Date: July 1986

### **RELATED PRODUCTS**

| Part No.                | Description                                                           |  |  |  |

|-------------------------|-----------------------------------------------------------------------|--|--|--|

| Am29114                 | Vectored Priority Interrupt Controller                                |  |  |  |

| Am29116                 | A 16-Bit Bipolar Microprocessor                                       |  |  |  |

| Am29117                 | Two-Port Am29116                                                      |  |  |  |

| Am29118                 | 8-Bit Bidirectional I/O Port/Accumulator Fuse-Programmable Controller |  |  |  |

| Am29PL141               |                                                                       |  |  |  |

| Am2950A/<br>51A/52A/53A | 8-Bit Bidirectional I/O Port                                          |  |  |  |

| Am2925                  | System Clock Generator and Driver                                     |  |  |  |

| Am2904                  | Status and Shift Control Unit                                         |  |  |  |

| Am2940                  | DMA Address Generator                                                 |  |  |  |

| Am2942                  | Programmable Timer/Counter/DMA                                        |  |  |  |

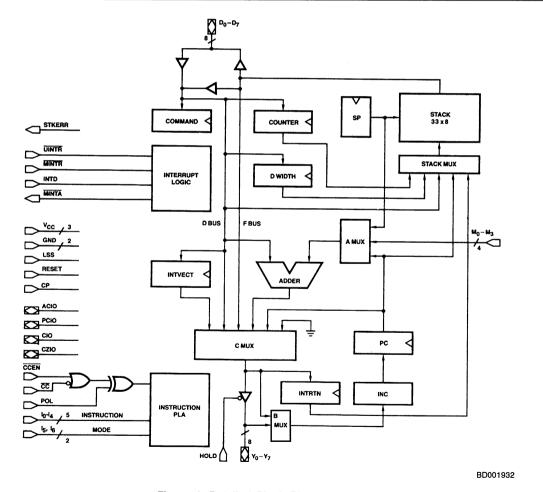

Figure 1. Detailed Block Diagram

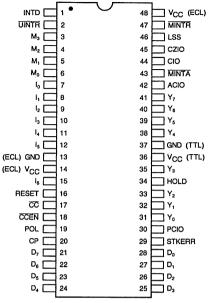

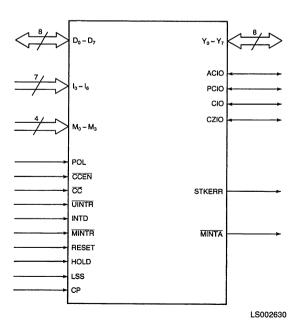

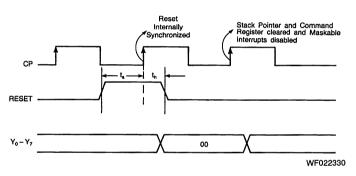

# CONNECTION DIAGRAM Top View

CD004891

Note: Pin 1 is marked for orientation.

#### LOGIC SYMBOL

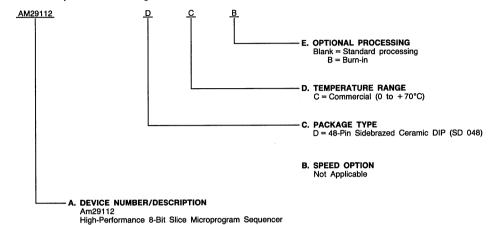

#### ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: **A. Device Number**

- B. Speed Option (if applicable)

- C. Package Type

- D. Temperature Range

- E. Optional Processing

| Valid Combinations |         |  |  |  |  |

|--------------------|---------|--|--|--|--|

| AM29112            | DC, DCB |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### PIN DESCRIPTION

#### D<sub>0</sub> - D<sub>7</sub> Data I/O Lines (8) (Input/Output)

Bidirectional bus inputs data to address multiplexer, counter, and other control registers and outputs stack.

#### Yn-Y7 Address I/O Lines (8) (Input/Output)

Bidirectional microprogram address bus outputs microprogram address and inputs interrupt vector.

## Multiway Inputs (4) (Input)

Multiway input pins for up to 16-way branches.

#### HOLD Hold Control Pin (Input)

When this signal is HIGH, the Y-Bus is three-stated and the carry-in to the program counter incrementer is forced LOW. Also, the CMUX output is selected at the incrementer input.

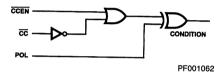

#### Condition Code Pin (Input)

Test condition input for the sequencer (see Table 2).

#### Condition Code Enable Pin (Input)

Test enable for the sequencer (see Table 2).

#### Polarity Pin (Input)

Polarity Input for the test (see Table 2).

#### Instruction Lines (5) (Input)

Used to select the instruction to be performed by the Am29112.

l5, l6 Instruction Lines (2) (Input) Mode control inputs. Selects one of three modes: normal, extended, or forced continue (see Table 1).

#### Stack Error Pin (Output)

Indicates stack overflow or underflow.

#### Unmaskable Interrupt Pin (Input)

Unmaskable interrupt request input. Needs to remain active for at least one cycle.

#### Maskable Interrupt Pin (Input)

Maskable interrupt request input. Needs to remain active for at least one cycle. May remain active during entire interrupt routine. MINTR should go inactive for at least one cycle before it can go active again.

#### Interrupt Disable Pin (Input) INTD

## Disable input for maskable interrupts.

Maskable Interrupt Acknowledge Pin (Output) Acknowledges to interrupting device that the Am29112 has been interrupted.

#### Least Significant Slice Pin (Input) 188

When LSS is HIGH, the Am29112 is programmed as the least significant slice. When LSS is LOW, the Am29112 is programmed as the most significant slice.

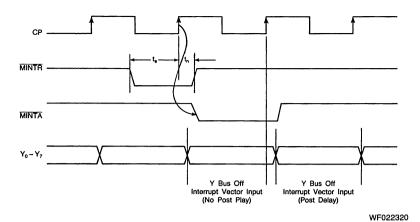

#### RESET Reset Pin (Input)

The reset input is registered and has no effect until the following cycle. On the second clock edge after reset, the stack pointer is reset, the command register is set to its default values, and maskable interrupts are disabled. A Jump-to-Zero is executed during the cycle following RESET becoming active.

#### Clock Pulse Pin (Input)

The clock input to the Am29112.

## Adder Carry I/O (Input/Output)

Carry I/O line for the adder for two cascaded Am29112s. When not cascading two Am29112s, leave unconnected.

# Program Counter I/O (Input/Output)

Carry I/O line for the program counter for two cascaded Am29112s. When not cascading two Am29112s, leave unconnected.

#### Counter I/O (Input/Output)

Carry I/O line for the counter for two cascaded Am29112s. When not cascading two Am29112s, leave unconnected.

# Counter Zero I/O (Input/Output)

Counter zero detect for two cascaded Am29112s. This is an open-collector output which should be OR-tied to another Am29112 using a 1K pull-up resistor. When not cascading two Am29112s, leave unconnected.

#### **FUNCTIONAL DESCRIPTION**

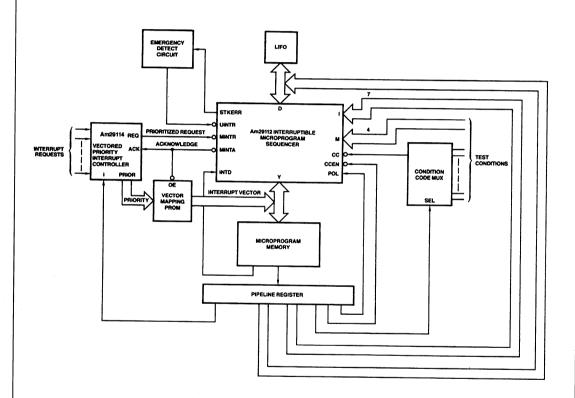

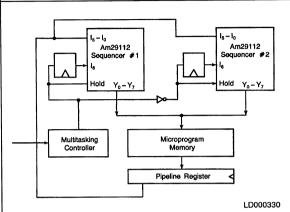

The Am29112 is designed for use in single-level pipelined systems. A typical configuration is shown in Figure 2.

Branch addresses and constants for the various registers are supplied to the Am29112 through the D port which is bidirectional to allow the stack to be unloaded onto an external LIFO. The next address generated by the sequencer is output on the Y port and directly drives the microprogram memory. A single pipeline register at the output of the microprogram memory contains the microinstruction being executed, while the next is being fetched. External conditions are applied to the  $\overline{CC}$  input of the Am29112 via the condition code MUX and also to the multiway inputs.

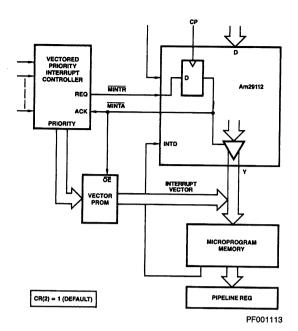

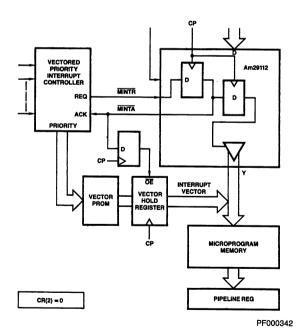

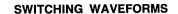

A vectored priority interrupt controller generates a prioritized interrupt request (MINTR) to the Am29112, which acknowl-

edges the request via the MINTA pin. Upon receiving the acknowledge, the priority interrupt controller puts out the encoded priority of the interrupt, which is translated to a vector by the vector mapping PROM. The MINTA output of the Am29112 turns on the PROM output and simultaneously switches the Y port from output to input, enabling the interrupt vector onto the microprogram address bus. In the Am29112, the next address of the interrupted sequence is automatically saved on the stack while the interrupt vector is transmitted through the Y port and incremented to form the next microprogram address.

The emergency detect circuit generates an unmaskable interrupt request upon power failure or stack error. On receiving an unmaskable interrupt, the sequencer branches to the unmaskable interrupt routine; the address of this routine is stored on the Am29112 in the INTVECT register. Detailed interrupt handling is discussed in a later section.

BD001922

Figure 2. Control Path in a Single Pipelined System Using the Am29112

#### Architecture of the Am29112

The internal organization of the Am29112 is shown in Figure 1. The most important control loop inside the sequencer consists of the CMUX, incrementer, and PC register. The CMUX selects the next microprogram address based on the instruction and condition code inputs. The next microprogram address is selected from the PC register for a continue, the D port for a

branch, the adder for relative and multiway branches, the

interrupt register for unmaskable interrupts, the stack for

subroutine returns or loop repeats, or all zeros for the JUMP ZERO instruction.

The Am29112 has many registers other than the PC register and the interrupt register. There is an 8-bit counter used for loop control; the DWIDTH register is a 4-bit register which programs the number of least significant bits of the D port that are added to the PC in relative addressing modes; the stack pointer is a 6-bit counter/register that points to the top of stack element; the 3-bit command register is used to program the

chip on reset for compatibility with the external hardware

configuration; finally, there is the INTRTN register which is used for saving the CMUX output on the stack when an interrupt occurs.

With the exception of the INTRTN register, the stack pointer, and the PC register, each of the above registers can be loaded directly from the D port of the Am29112.

directly from the D port of the Am29112.

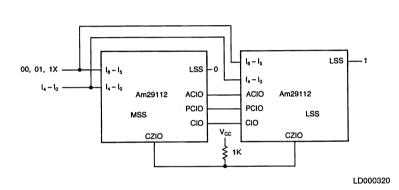

The Am29112 features a high-speed adder with full carry lookahead across 8-bits. The adder is used for PC relative addressing (branch address is PC+D), multiway relative addressing (branch address is D+M, where M is the 4-bit multiway input), and for testing the stack pointer against the D bus. In cascaded configurations (see Figure 3), carry ripples from the LSS adder to the MSS adder over the ACIO line. The on-chip stack is 33 deep, and the Am29112 has instructions to save the D inputs, counter, multiway register, and PC-register on the stack. The stack output bus is connected via three-state buffers to the D port. It is possible to pop the stack to the D port. It is also possible to push data from the D port onto the stack.

Figure 3. 16-Bit Configuration

#### Instruction Set of The Am29112

#### Mode Bits (I6, I5)

The Am29112 is controlled by five instruction inputs, two mode inputs, and the condition code. In typical applications it is expected that the instruction inputs are driven directly from the pipeline, whereas the mode inputs are either permanently wired high or low to select the desired operating mode, or driven indirectly via external logic. (In some applications it might be justifiable to drive the mode bits directly from the pipeline.) The two mode bits select among three operating modes: normal (00), extended (01), and forced continue (10 and 11). In the normal mode, the entire instruction set of the Am29112 applies.

TABLE 1. MODE CONTROLS

| 16, 15 | Mode               | Description                                                                 |

|--------|--------------------|-----------------------------------------------------------------------------|

| 00     | Normal             | For cascaded Am29112s, two independent 8-bit counters                       |

| 01     | Extended           | For cascaded Am29112s, one 16-bit counter                                   |

| 10     | Forced<br>Continue | The Am29112 executes a continue                                             |

| 11     |                    | instruction regardless of instruction, condition code, and multiway inputs. |

#### **Extended Mode**

The instruction set includes instructions that differentiate between upper and lower counters (when there are two cascaded Am29112s). In the normal mode, the two counters on cascaded Am29112s function independently, and it is possible to set up a doubly nested loop without having to save and restore counter values on the stack. In the extended mode, however, the counters on cascaded Am29112s behave like one 16-bit counter and instructions that differentiate between the counters degenerate into identical instructions. Hence in a system with only one Am29112 there is no use for the extended mode.

#### **Forced Continue Mode**

In the forced continue mode the Am29112 executes a continue in every cycle regardless of the instruction bits, condition code, and multiway inputs. The simplest application (if mode bits are driven directly from the pipeline) is to use forced continue for straight-line segments of code, thereby permitting most of the sequencer control fields of the pipeline

to be shared. The forced continue also has an important application in systems with a writable control store (WCS) where it is necessary to step through the addresses sequentially while loading the WCS.

The instructions of the Am29112 are classified into four groups:

- Branching and subroutine linkage

- Looping

- Stack and register

- Interrupt

The sequencer has an instruction repertoire of altogether thirtynine different instructions. In order to encode these instructions with only five instruction lines, the condition code is used in some cases to differentiate between two distinct instructions sharing the same opcode. This way of encoding is used for the stack and register, and interrupt groups of instructions. For these instructions, therefore, the condition code multiplexer is not used to select an external condition. However it is required to force the condition code to unconditional Pass or Fail. The condition code enable and polarity logic has been designed with this in mind. Using the enable and polarity, it is possible to generate both unconditional Pass and unconditional Fail (regardless of the condition code input). Hence the condition code for these instructions is like a sixth instruction line, and the condition code multiplexer field of the pipeline can be shared for these instructions (see Figure 4 and Table 2).

Figure 4. Condition Code Circuit.

TABLE 2. CONDITION CODE TABLE

| CCEN | CC  | POL | Condition |

|------|-----|-----|-----------|

| 0    | 0   | 0   | PASS      |

| 0    | 1   | 0   | FAIL      |

| 0    | 0   | 1   | FAIL      |

| 0    | 1 1 | 1   | PASS      |

| 1    | X   | 0   | PASS      |

| 1    | X   | 1   | FAIL      |

|                                   |                           | TABLE 3. Am2         | 29112 INSTRUCTION SET                           |

|-----------------------------------|---------------------------|----------------------|-------------------------------------------------|

| Opcode (I <sub>40</sub> )         | Condition                 | Mnemonic<br>(Note 1) | Description                                     |

| 00 (00 <sub>H</sub> )             | Unconditional             | JZ.U                 | Unconditional Jump Zero                         |

| 01 (01 <sub>H</sub> )             | Forced Pass               | PUSHD.P              | Push D (Pass)                                   |

| 01 (01 <sub>H</sub> )             | Forced Fail               | LDCMD.F              | Load Command Register from D (Fail)             |

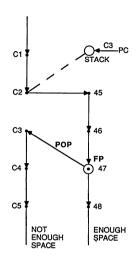

| 02 (02 <sub>H</sub> )             | Conditional               | POP.C                | Pop; Conditional Stack out to D                 |

| 03 (03 <sub>H</sub> )             | Conditional               | CJD.C                | Conditional Jump D                              |

| 04 (04 <sub>H</sub> )             | Conditional               | CJSD.C               | Conditional Jump Subroutine D                   |

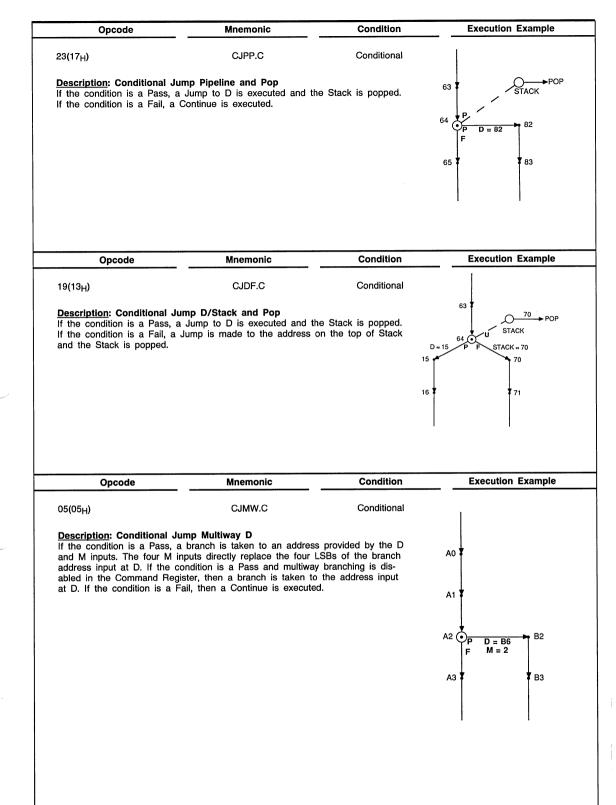

| 05 (05 <sub>H</sub> )             | Conditional               | CJMW.C               | Conditional Jump Multiway D                     |

| 06 (06 <sub>H</sub> )             | Conditional               | CJSMW.C              | Conditional Jump Subroutine Multiway D          |

| 07 (07 <sub>H</sub> )             | Conditional               | CRTN.C               | Conditional Return                              |

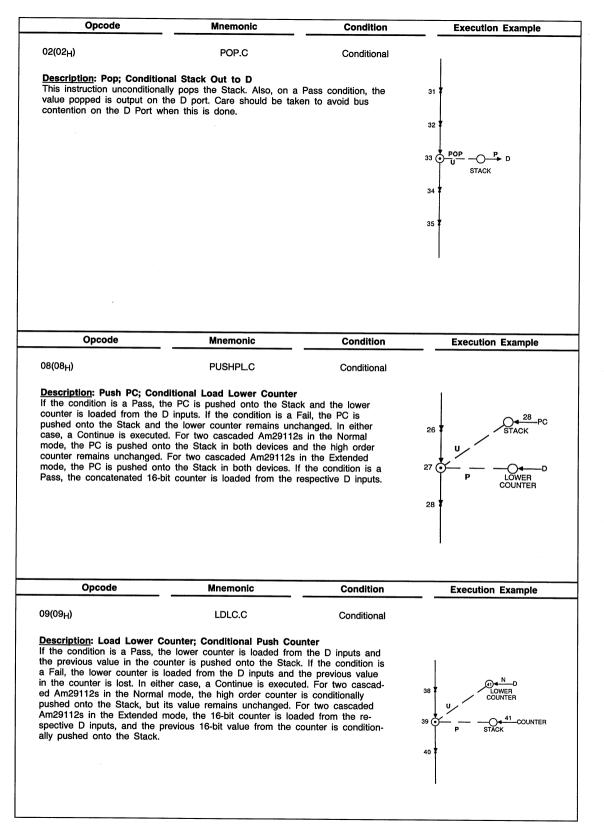

| 08 (08 <sub>H</sub> )<br>(Note 2) | Conditional               | PUSHPL.C             | Push PC; Conditional Load Lower Counter         |

| 09 (09 <sub>H</sub> )<br>(Note 3) | Conditional               | LDLC.C               | Load Lower Counter; Conditional Push Counter    |

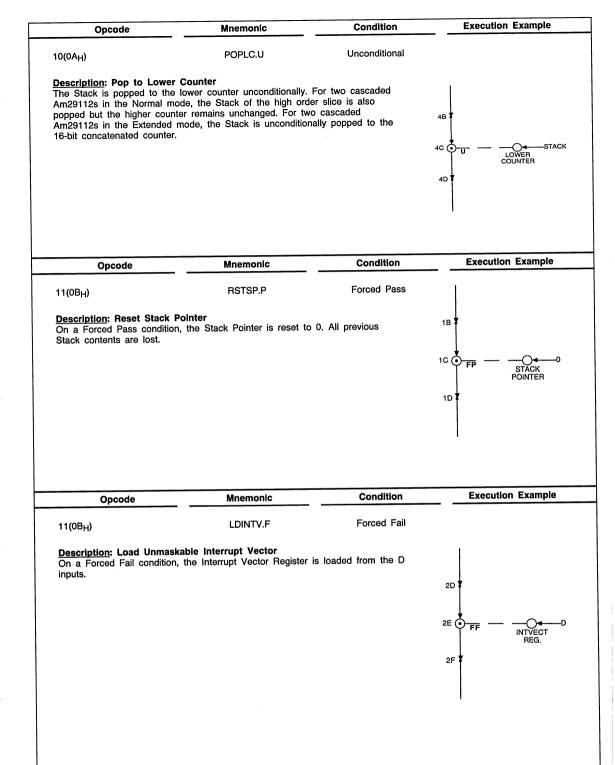

| 10 (0A <sub>H</sub> )             | Unconditional             | POPLC.U              | Pop to Lower Counter                            |

| 11 (0B <sub>H</sub> )             | Forced Pass               | RSTSP.P              | Reset Stack Pointer (Pass)                      |

| 11 (0B <sub>H</sub> )             | Forced Fail               | LDINTV.F             | Load Unmaskable Interrupt Vector (Fail)         |

| 12 (0C <sub>H</sub> )<br>(Note 4) | Forced Pass               | RFCTU.P              | Repeat Loop, Upper Counter ≠ 0 (Pass)           |

| 12 (0C <sub>H</sub> )<br>(Note 4) | Forced Fail               | RFCTL.F              | Repeat Loop, Lower Counter ≠ 0 (Fail)           |

| 13 (0D <sub>H</sub> )<br>(Note 5) | Forced Pass               | RPCTU.P              | Repeat Pipeline, Upper Counter ≠ 0 (Pass)       |

| 13 (0D <sub>H</sub> )<br>(Note 5) | Forced Fail               | RPCTL.F              | Repeat Pipeline, Lower Counter ≠ 0 (Fail)       |

| 14 (0E <sub>H</sub> )             | Conditional               | LOOP.C               | Test End Loop                                   |

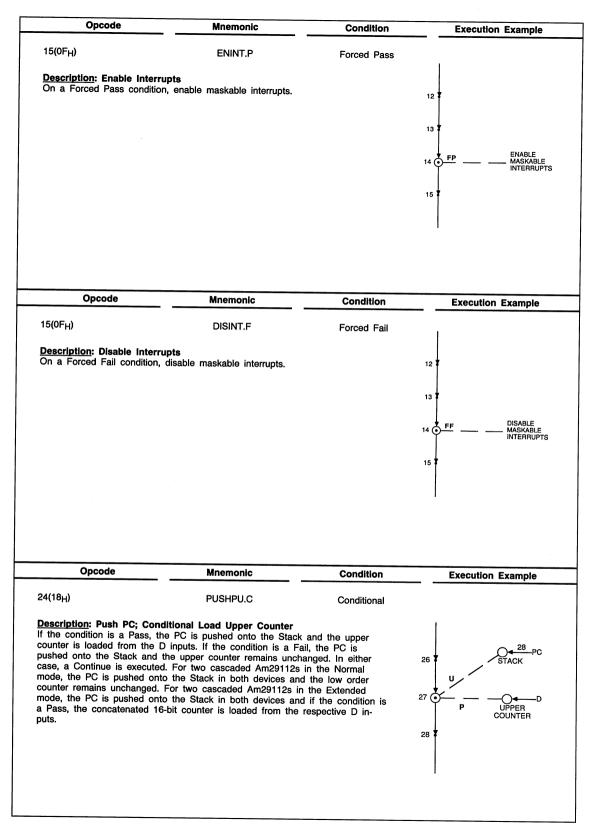

| 15 (0F <sub>H</sub> )             | Forced Pass               | ENINT.P              | Enable Interrupts (Pass)                        |

| 15 (0F <sub>H</sub> )             | Forced Fail               | DISINT.F             | Disable Interrupts (Fail)                       |

| 16 (10 <sub>H</sub> )<br>(Note 6) | Conditional               | TWBL.C               | Three-Way Branch, Lower Counter                 |

| 17 (11 <sub>H</sub> )<br>(Note 6) | Conditional               | TWBU.C               | Three-Way Branch, Upper Counter                 |

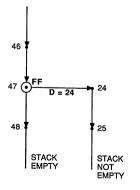

| 18 (12 <sub>H</sub> )             | Forced Pass               | TSTSP.P              | Test SP with D (Pass)                           |

| 18 (12 <sub>H</sub> )             | Forced Fail               | TSTMT.F              | Jump D if Stack not Empty                       |

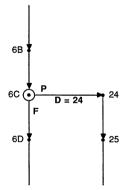

| 19 (13 <sub>H</sub> )             | Conditional               | CJDF.C               | Conditional Jump D/Stack and Pop                |

| 20 (14 <sub>H</sub> )             | Conditional               | CJSDF.C              | Conditional Jump Subroutine D/Stack and Pop     |

| 21 (15 <sub>H</sub> )             | Conditional               | CJMWR.C              | Conditional Jump Multiway Relative D            |

| 22 (16 <sub>H</sub> )             | Conditional               | CJSMWR.C             | Conditional Jump Subroutine Multiway Relative D |

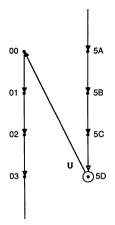

| 23 (17 <sub>H</sub> )             | Conditional               | CJPP.C               | Conditional Jump Pipeline and Pop               |

| 24 (18 <sub>H</sub> )<br>(Note 2) | Conditional               | PUSHPU.C             | Push PC; Conditional Load Upper Counter         |

| 25 (19 <sub>H</sub> )<br>(Note 3) | Conditional               | LDUC.C               | Load Upper Counter; Conditional Push Counter    |

| 26 (1A <sub>H</sub> )             | Forced Pass               | POPUC.P              | Pop to Upper Counter (Pass)                     |

| 26 (1A <sub>H</sub> )             | Forced Fail               | POPDW.F              | Pop to Displacement Width (DW) Register (Fail)  |

| 27 (1B <sub>H</sub> )             | Conditional               | LDDW.C               | Load DW Register; Conditional Push DW Register  |

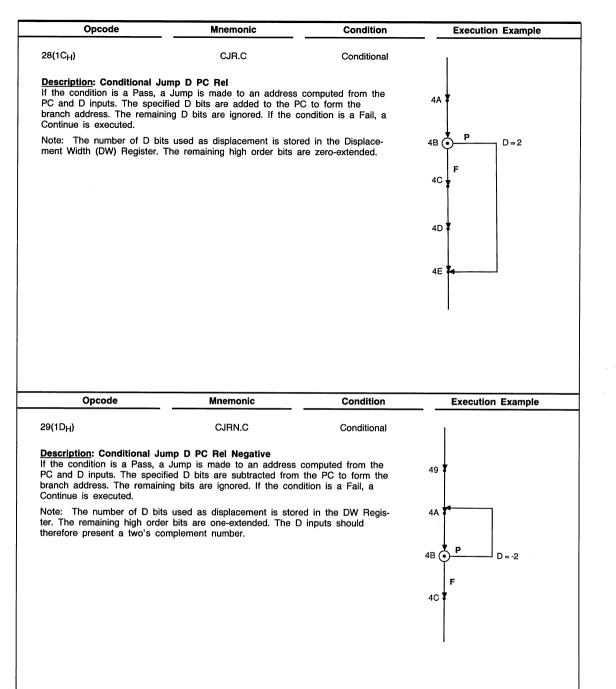

| 28 (1C <sub>H</sub> )             | Conditional               | CJR.C                | Conditional Jump D PC Rel                       |

| 29 (1D <sub>H</sub> )             | Conditional               | CJRN.C               | Conditional Jump D PC Rel Negative              |

| 30 (1E <sub>H</sub> )             | Conditional               | CJSR.C               | Conditional Jump Subroutine D PC Rel            |

| 31 (1F <sub>H</sub> )             | Conditional               | CJSRN.C              | Conditional Jump Subroutine D PC Rel Negative   |

| Notes: 1 Extension                | ns: II = I Inconditional: | C = Conditional: D   | = Pass Condition: F = Fail Condition.           |

Notes: 1. Extensions: U = Unconditional; C = Conditional; P = Pass Condition; F = Fail Condition.

- 2. For two cascaded Am29112s in the extended mode, the two instructions are identical.

3. For two cascaded Am29112s in the extended mode, the two instructions are identical.

4. For two cascaded Am29112s in the extended mode, the two instructions are identical.

5. For two cascaded Am29112s in the extended mode, the two instructions are identical.

- 6. For two cascaded Am29112s in the extended mode, the two instructions are identical.

| TABLE 4. JUMP INSTRUCTIONS |                |               |                       |           |                                                                 |       |  |

|----------------------------|----------------|---------------|-----------------------|-----------|-----------------------------------------------------------------|-------|--|

| Instruc                    | tion Functions | Mnemonic      | Opcode                | Condition | Y                                                               | Stack |  |

|                            |                | JZ.U (Note 1) | 00 (00 <sub>H</sub> ) | U         | 0                                                               | RESET |  |

| Direct                     |                | CIDC          | 00 (00.)              | Р         | D                                                               |       |  |

|                            | One-Way        | CJD.C         | 03 (03 <sub>H</sub> ) | F         | (PC)                                                            | ] -   |  |

|                            |                | O IDD O       | 00 (47.)              | Р         | D                                                               | Pop   |  |

|                            |                | CJPP.C        | 23 (17 <sub>H</sub> ) | F         | (PC)                                                            | _     |  |

|                            | Torra Maria    | CIDE C        | 40 (40 )              | Р         | D                                                               | Рор   |  |

|                            | Two-Way        | CJDF.C        | 19 (13 <sub>H</sub> ) | F         | (Stack)                                                         |       |  |

|                            | Multi-Way      | CJMW.C        | 05 (05 <sub>H</sub> ) | Р         | $Y_4 - Y_7 = D_4 - D_7,$<br>$Y_0 - Y_3 = M_0 - M_3$<br>(Note 2) | _     |  |

|                            |                |               |                       | F         | (PC)                                                            |       |  |

|                            |                | CJR.C         | 28 (1C <sub>H</sub> ) | Р         | (PC) + D\$<br>(Note 3)                                          | _     |  |

|                            | 0== 14/=       |               |                       | F         | (PC)                                                            |       |  |

| Relative                   | One-Way        | CJRN.C        | 29 (1D <sub>H</sub> ) | Р         | (PC) + D*<br>(Note 4)                                           | _     |  |

|                            |                |               |                       | F         | (PC)                                                            | 1     |  |

|                            | Multi-Way      | CJMWR.C       | 21 (15 <sub>H</sub> ) | Р         | D + M<br>(Note 5)                                               | _     |  |

|                            |                |               |                       | F         | (PC)                                                            | ]     |  |

Notes: 1. JZ.U also resets the Command Register and the interrupt logic.

2. Y<sub>0</sub> - Y<sub>7</sub> is as shown if CR<sub>1</sub> = 1. If CR<sub>1</sub> = 0, then Y<sub>0</sub> - Y<sub>7</sub> = D<sub>0</sub> - D<sub>7</sub>.

3. D\$ represents the number of D bits used as displacement; the remaining high-order bits are zero-extended.

4. D\* represents the number of D bits used as displacement; the remaining high-order bits are one-extended. D should be a two's-complement number.

5. Y<sub>0</sub> - Y<sub>7</sub> = D + M if CR<sub>1</sub> = 1. If CR<sub>1</sub> = 0, then Y<sub>0</sub> - Y<sub>7</sub> = D<sub>0</sub> - D<sub>7</sub>.

| TABLE 5. SUBROUTINE INSTRUCTIONS |                |            |                       |           |                                                                 |         |  |

|----------------------------------|----------------|------------|-----------------------|-----------|-----------------------------------------------------------------|---------|--|

| Instruc                          | tion Functions | Mnemonic   | Opcode                | Condition | Υ                                                               | Stack   |  |

|                                  |                | 0.100.0    | 04 (04 )              | Р         | D                                                               | Push    |  |

|                                  | 0              | CJSD.C     | 04 (04 <sub>H</sub> ) | F         | (PC)                                                            | -       |  |

|                                  | One-Way        | OPTNO      | 07 (07 )              | Р         | (Stack)                                                         | Pop     |  |

|                                  |                | CRTN.C     | 07 (07 <sub>H</sub> ) | F         | (PC)                                                            | -       |  |

| Direct                           | T . 144        | 0.1005.0   | 00 (14 )              | Р         | D                                                               | Pop and |  |

|                                  | Two-Way        | CJSDF.C    | 20 (14 <sub>H</sub> ) | F         | (Stack)                                                         | Push    |  |

|                                  | Multi-Way      | CJSMW.C    | 06 (06 <sub>H</sub> ) | Р         | $Y_4 - Y_7 = D_4 - D_7,$<br>$Y_0 - Y_3 = M_0 - M_3$<br>(Note 1) | Push    |  |

|                                  |                |            |                       | F         | (PC)                                                            | -       |  |

|                                  |                | CJSR.C     | 30 (1E <sub>H</sub> ) | Р         | (PC) + D\$<br>(Note 2)                                          | Push    |  |

|                                  | 0              |            | , ,,,                 | F         | (PC)                                                            | -       |  |

| Relative                         | One-Way        | CJSRN.C    | 31 (1F <sub>H</sub> ) | Р         | (PC) + D*<br>(Note 3)                                           | Push    |  |

|                                  |                |            | ""                    | F         | (PC)                                                            | -       |  |

|                                  | Multi-Way      | CJSMWR.C   | 22 (16 <sub>H</sub> ) | Р         | D + M<br>(Note 4)                                               | Push    |  |

|                                  |                | india via, | '"                    | F         | (PC)                                                            | _       |  |

| TABLE 6. REPEAT INSTRUCTIONS |                    |                       |                  |                |                |         |       |   |

|------------------------------|--------------------|-----------------------|------------------|----------------|----------------|---------|-------|---|

| Instruction<br>Functions     | Mnemonic           | Opcode                | Condition        | Upper<br>Count | Lower<br>Count | Υ       | Stack |   |

|                              | RFCTU.P            |                       | Р                | > 0            |                | (Stack) | T -   |   |

|                              | (Note 1)           | 10 (00)               | P                | = 0            |                | (PC)    | Pop   |   |

|                              | RFCTL.F            | 12 (0C <sub>H</sub> ) | F                |                | >0             | (Stack) |       |   |

|                              | (Note 1)           |                       | Г                |                | = 0            | (PC)    | Pop   |   |

| Loop                         | RPCTU.P            |                       | Р                | > 0            |                | D       |       |   |

| (Note 2)                     | 12 (00.1)          | F                     | = 0              |                | (PC)           | ] -     |       |   |

|                              | RPCTL.F            | RPCTL.F<br>(Note 2)   | 13 (ODH) [       | 13 (ADH)       | F              |         | >0    | D |

|                              | (Note 2)           |                       |                  |                | = 0            | (PC)    | ] -   |   |

|                              | LOOP.C             | 14 (0E <sub>H</sub> ) | Р                |                |                | (PC)    | Pop   |   |

|                              | LOOP.C             | 14 (OEH)              | F                |                |                | (Stack) | _     |   |

|                              |                    |                       | Р                |                |                | (PC)    | Pop   |   |

|                              | TWBU.C<br>(Note 3) | 17 (11 <sub>H</sub> ) | 1 <sub>H</sub> ) | > 0            |                | (Stack) | _     |   |

| Loop<br>and                  | (5.0 0)            |                       | F                | = 0            |                | D       | Pop   |   |

| Branch                       |                    |                       | Р                |                |                | (PC)    | Pop   |   |

|                              | TWBL.C<br>(Note 3) | 16 (10 <sub>H</sub> ) | F                |                | > 0            | (Stack) | _     |   |

|                              | (                  |                       | ٢                |                | = 0            | D       | Pop   |   |

Notes: 1. For two cascaded Am29112s in the extended mode, the two instructions are identical.

2. For two cascaded Am29112s in the extended mode, the two instructions are identical.

3. For two cascaded Am29112s in the extended mode, the two instructions are identical.

#### **TABLE 7. TESTING INSTRUCTIONS**

| Instruction Functions | Mnemonic | Opcode   | Condition             |             | Υ       | Stack |   |  |

|-----------------------|----------|----------|-----------------------|-------------|---------|-------|---|--|

| Test SP and Branch    | TSTSP.P  |          | р                     | SP + D ≤ 33 | (PC)    | _     |   |  |

|                       | 15155.5  | 40 (40 ) |                       | SP + D > 33 | (Stack) | Pop   |   |  |

|                       | TSTMT.F  |          | 18 (12 <sub>H</sub> ) | 10 (12H)    |         | SP≠0  | D |  |

|                       | 151M1.F  |          | -                     | SP = 0      | (PC)    | _     |   |  |

| Opcode                | Mnemonic             | Condition       | Functions                                  | Stack |

|-----------------------|----------------------|-----------------|--------------------------------------------|-------|

| 04 (04 )              | PUSHD.P              | Р               | D → Stack                                  | Push  |

| 01 (01 <sub>H</sub> ) | LDCMD.F              | F               | D → Command Register                       | _     |

| 00 (00 )              | 200.0                | P (Stack) → D   |                                            | Б     |

| 02 (02 <sub>H</sub> ) | POP.C                | F               |                                            | Pop   |

| 08 (08 <sub>H</sub> ) | PUSHPL.C<br>(Note 1) | Р               | (PC) → Stack D → Lower Counter             | Push  |

|                       |                      | F               | (PC) → Stack                               |       |

| 09 (09 <sub>H</sub> ) | LDLC.C<br>(Note 2)   | Р               | D → Lower Counter<br>(Counter) → Stack     | Pust  |

|                       |                      | F               | D → Lower Counter                          | _     |

| 10 (0A <sub>H</sub> ) | POPLC.U              | U               | (Stack) → Lower Counter                    | Pop   |

| 11 (OD. )             | RSTSP.P              | SP.P P Reset SP |                                            |       |

| 11 (0B <sub>H</sub> ) | LDINTV.F             | F               | D → Interrupt Vector Register              |       |

| 15 (OE.)              | ENINT.P              | Р               | Enable Maskable Interrupt                  |       |

| 15 (0F <sub>H</sub> ) | DISINT.F             | F               | Disable Maskable Interrupt                 | _     |

| 24 (18 <sub>H</sub> ) | PUSHPU.C<br>(Note 1) | Р               | (PC) → Stack D → Upper Counter             | Pust  |

|                       | (Note 1)             | F               | (PC) → Stack                               |       |

| 25 (19 <sub>H</sub> ) | LDUC.C<br>(Note 2)   | Р               | D → Upper Counter<br>(Counter) → Stack     | Push  |

|                       | (Note 2)             | F               | D → Upper Counter                          | -     |

| 26 (14.)              | POPUC.P              | Р               | (Stack) → Upper Counter                    | Don   |

| 26 (1A <sub>H</sub> ) | POPDW.F              | F               | (Stack) → Displacement Width (DW) Register | — Pop |

| 27 (1B <sub>H</sub> ) | LDDW.C               | Р               | D → DW Register<br>(DW Register) → Stack   | Push  |

| ,                     |                      | F               | D → DW Register                            | _     |

Notes: 1. For two cascaded Am29112s in the extended mode, the two instructions are identical. 2. For two cascaded Am29112s in the extended mode, the two instructions are identical.

#### **INSTRUCTION SET DEFINITION OF THE Am29112**

#### **Jump Instructions**

Key: ● = Other Instruction

⊙ = Instruction Being Described

o = Register in Part

P = Pass

F = Fail

U = Unconditional

FP = Forced Pass

FF = Forced Fail

Opcode Mnemonic Condition Execution Example

00(00<sub>H</sub>)

JZ.U

Unconditional

#### **Description: Unconditional Jump Zero**

This instruction causes an Unconditional Jump to address location 0. This instruction also resets the stack pointer and interrupt logic (maskable interrupt disabled), as well as setting the Command Register as follows:

$CR_0 = CR_1 = CR_2 = 1.$

Opcode Mnemonic Condition Execution Example

03(03<sub>H</sub>)

CJD.C

Conditional

#### **Description:** Conditional Jump D

Conditionally Jump to the address input on the D port. If the condition is a Pass, the next address is obtained from the D port. If the condition is a Fail, a Continue is executed.

| Opcode                                                                               | Mnemonic                                                                                                                                                                           | Condition                                           | Execution Example   |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------|

| 21(15 <sub>H</sub> )                                                                 | CJMWR.C                                                                                                                                                                            | Conditional                                         |                     |

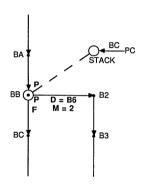

| D and M inputs. The constation orm the branch address. If disabled in the Command Re | mp Multiway Relative D branch is taken to an address nt on the M inputs is added to the condition is a Pass and m egister, then a branch is taken is a Fail, a Continue is execute | the D inputs to ultiway branching is to the address | A0 \$               |

|                                                                                      |                                                                                                                                                                                    |                                                     | 120                 |

|                                                                                      |                                                                                                                                                                                    |                                                     | A2 P D = B3 F M = 4 |

|                                                                                      |                                                                                                                                                                                    |                                                     | A3 B8               |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     | , ,                 |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

|                                                                                      |                                                                                                                                                                                    |                                                     |                     |

#### **INSTRUCTION SET DEFINITION OF THE Am29112**

#### **Subroutine Instructions**

Key: ● = Other Instruction

⊙ = Instruction Being Described

○ = Register in Part

P = Pass

F = Fail

U = Unconditional

FP = Forced Pass

FF = Forced Fail

Opcode

Mnemonic

Condition

Execution Example

04(04H)

CJSD.C

Conditional

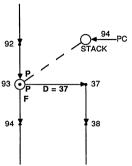

**Description:** Conditional Jump Subroutine D

Conditionally Jump to Subroutine. The subroutine address is input over the D port. If the condition is a Pass, the PC is saved on the Stack and a branch is taken to the subroutine address. If the condition is a Fail, a Continue is executed

Opcode Mnemonic Condition Execution Example

07(07<sub>H</sub>) CRTN.C Conditional

**Description:** Conditional Return

If the condition is a Pass, a return is executed from the Interrupt or Sub-routine. The return address is obtained from the Stack and the Stack is popped. If the condition is a Fail, a Continue is executed.

| Opcode  | Mnemonic | Condition   | Execution Example |   |

|---------|----------|-------------|-------------------|---|

|         |          |             |                   | _ |

| 20(14山) | CJSDF.C  | Conditional |                   |   |

<u>Description:</u> Conditional Jump Subroutine D/Stack and Pop If the condition is a Pass, a subroutine Jump to D is executed. The Stack is popped and PC is then pushed onto the Stack. If the condition is a Fail, a subroutine Jump is made to the address on the top of Stack. The Stack is popped and PC is then pushed onto the Stack.

| Opcode               | Mnemonic | Condition   | Execution Example |

|----------------------|----------|-------------|-------------------|

| 06(06 <sub>H</sub> ) | CJSMW.C  | Conditional |                   |

<u>Description</u>: Conditional Jump Subroutine Multiway D

If the condition is a Pass, a branch to subroutine is made. The subroutine

starting address is provided by the D and M inputs. The four M inputs directly

replace the four LSBs of the subroutine address input at D. If the condition is

a Pass and multiway branching is disabled in the Command Register, then a

subroutine call is made to the address input at D. In either case, the PC is

saved on the Stack as a return address. If the condition is a Fail, a Continue

is executed.

| Opcode               | Mnemonic                                                                                     | Condition   | Execution Example |

|----------------------|----------------------------------------------------------------------------------------------|-------------|-------------------|

| 30(1E <sub>H</sub> ) | CJSR.C                                                                                       | Conditional |                   |

|                      | Imp Subroutine D PC Rel<br>a subroutine call is made to an<br>The specified D bits are adder |             | 4A PC STACK       |

ue is executed.

Note: The number of bits of D used as displacement is stored in the DW Register. The remaining high order bits are zero-extended.

the subroutine starting address. The remaining D bits are ignored. The subrou-

tine Return Address is saved on the Stack. If the condition is a Fail, a Contin-

Opcode Mnemonic Condition Execution Example

31(1F<sub>H</sub>)

CJSRN.C

Conditional

**Description:** Conditional Jump Subroutine PC Rel Negative

If the condition is a Pass, a subroutine call is made to an address computed from the PC and D inputs. The specified D bits are subtracted from the PC to form the subroutine starting address. The remaining D bits are ignored. The subroutine Return Address is saved on the Stack. If the condition is a Fail, a Continue is executed.

Note: The number of bits of D used as displacement is stored in the DW Register. The remaining high order bits are one-extended. The D inputs should, therefore, present two's-complement number.

Opcode Mnemonic Condition Execution Example

22(16<sub>H</sub>)

CJSMWR.C

Conditional

Description: Condtional Jump Subroutine Multiway Relative D

If the condition is a Pass, a branch to subroutine is made. The subroutine starting address is computed from the D and M inputs. The constant on the M inputs is added to the D inputs to form the starting address. If the condition is a Pass and multiway branching is disabled in the Command Register, then a subroutine call is made to the address input at D. If the condition is a Fail, a Continue is executed.

#### **INSTRUCTION SET DEFINITION OF THE Am29112**

#### Repeat Instructions

Key: ● = Other Instruction

⊙ = Instruction Being Described

○ = Register in Part

P = Pass

16-bit concatenated counter.

F = Fail

U = Unconditional

FP = Forced Pass

FF = Forced Fail

| 1 1 455                                                                                  |                                                                                                                                                                         |                                                                 |                              |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------|

| Opcode                                                                                   | Mnemonic                                                                                                                                                                | Condition                                                       | Execution Example            |

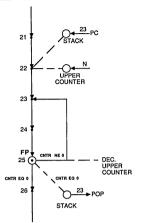

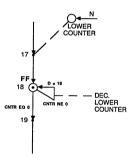

| 12(0C <sub>H</sub> )                                                                     | RFCTU.P                                                                                                                                                                 | Forced Pass                                                     | 23 00                        |

| equal to zero, execution bra<br>Stack and the counter is de<br>executed and the Stack is | Upper Counter ≠ 0  In, the upper counter value is anches to the address provide ecremented. If found equal to popped. For two cascaded Anoops back but its counter is a | d from the top of<br>zero, a Continue is<br>n29112s in the Nor- | 21 STACK  22 N UPPER COUNTER |

Note: The counter is checked before being decremented. A count of 1 causes two iterations.

cascaded Am29112s in the Extended mode, the instruction operates on the

| Opcode | Mnemonic | Condition | Execution Example |

|--------|----------|-----------|-------------------|

|        |          |           | 1                 |

|        |          |           |                   |

12(0C<sub>H</sub>)

RFCTL.F

Forced Fail

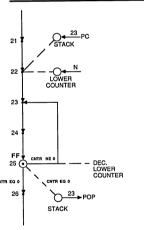

<u>Description:</u> Repeat Loop, Lower Counter ≠ 0

On a Forced Fail condition, the lower counter value is checked. If found not equal to zero, execution branches to the address provided from the top of Stack and the counter is decremented. If found equal to zero, a Continue is executed and the Stack is popped. For two cascaded Am29112s in the Normal mode, the upper slice loops back but its counter is unaffected. For two cascaded Am29112s in the Extended mode, the instruction operates on the 16-bit concatenated counter.

Note: The counter is checked before being decremented. A count of 1 causes two iterations.

Opcode Mnemonic Condition **Execution Example** 13(0DH)

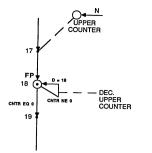

<u>Description</u>: Repeat Pipeline, Upper Counter  $\neq$  0

On a Forced Pass condition, the upper counter value is checked. If found not equal to zero, execution branches to the address provided from the D inputs and the counter is decremented. If found equal to zero, a Continue is executed. For two cascaded Am29112s in the Normal mode, the lower slice loops back but its counter is unaffected. For two cascaded Am29112s in the Extended mode, the instruction operates on the 16-bit concatenated counter.

RPCTU.P

Note: The counter is checked before being decremented. A count of 1 causes two iterations.

| Opcode | Mnemonic | Condition | Execution Example |

|--------|----------|-----------|-------------------|

|        |          |           |                   |

13(0D<sub>H</sub>)

RPCTL.F

Forced Fail

Forced Pass

<u>Description</u>: Repeat Pipeline, Lower Counter  $\neq$  0

On a Forced Fail condition, the lower counter value is checked. If found not equal to zero, execution branches to the address provided from the D inputs and the counter is decremented. If found equal to zero, a Continue is executed. For two cascaded Am29112s in the Normal mode, the upper slice loops back but its counter is unaffected. For two cascaded Am29112s in the Extended mode, the instruction operates on the 16-bit concatenated counter.

Note: The counter is checked before being decremented. A count of 1 causes two iterations.

Opcode Mnemonic Condition **Execution Example**

14(0E<sub>H</sub>)

LOOP.C

Conditional

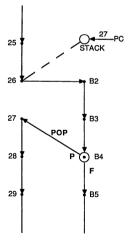

Description: Test End Loop If the condition is a Fail, program execution branches to the address obtained from the top of Stack. If the condition is a Pass, program execution continues and the Stack is popped.

Conditional

#### 17(11<sub>H</sub>) Description: Three-Way Branch, Upper Counter

If the condition is a Pass, a Continue is executed and the Stack is popped. If the condition is a Fail, the upper counter value is checked. If found not equal to zero, execution branches to the address provided from the top of Stack and the counter is decremented. If the counter is equal to zero, execution branches to the address provided from the D inputs and the Stack is popped. For two cascaded Am29112s in the Normal mode, the lower slice branches or loops back as the case may be, but its counter remains unaffected. For two cascaded Am29112s in the Extended mode, the instruction operates on the 16-bi t concatenated counter.

TWBU.C

Note: The counter is checked before being decremented. A count of 1 causes two iterations.

| Opcode | Mnemonic | Condition | Execution Example |

|--------|----------|-----------|-------------------|

|        |          |           |                   |

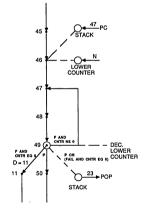

TWBL. 16(10<sub>H</sub>)

Conditional

Description: Three-Way Branch, Lower Counter

If the condition is a Pass, a Continue is executed and the Stack is popped. If the condition is a Fail, the lower counter value is checked. If found not equal to zero, execution branches to the address provided from the top of Stack and the counter is decremented. If the counter is equal to zero, execution branches to the address provided from the D inputs and the Stack is popped. For two cascaded Am29112s in the Normal mode, the upper slice branches or loops back as the case may be, but its counter remains unaffected. For two cascaded Am29112s in the Extended mode, the instruction operates on the 16-bit concatenated counter.

Note: The counter is checked before being decremented. A count of 1 causes two iterations.

#### **INSTRUCTION SET DEFINITION OF THE Am29112**

#### **Testing Instructions**

Key: ● = Other Instruction

⊙ = Instruction Being Described

○ = Register in Part

P = Pass

F = Fail

U = Unconditional

FP = Forced Pass

FF = Forced Fail

Opcode Mnemonic Condition Execution Example

18(12<sub>H</sub>)

TSTSP.P

Forced Pass

#### **Description:** Test SP with D

On a Forced Pass condition, the sequencer tests the Stack to see if there is enough space, as determined by a constant input at the D port. (The constant must be a hexadecimal number.) If the available number of Stack locations is greater than or equal to the constant, a Continue will be executed. If the available number of Stack locations is less than the constant, a Subroutine Return is executed.

| Opcode | Mnemonic | Condition | Execution Example |

|--------|----------|-----------|-------------------|

18(12<sub>H</sub>)

TSTMT.F

Forced Fail

#### **Description:** Jump D if Stack Not Empty

On a Forced Fail condition, the Stack is checked to see if it is empty. If empty, a Continue is executed. If not empty, a Jump to D is executed.

#### **INSTRUCTION SET DEFINITION OF THE Am29112**

#### Other Instructions

Key: ● = Other Instruction

⊙ = Instruction Being Described

○ = Register in Part

P = Pass

F = Fail

U = Unconditional

FP = Forced Pass

FF = Forced Fail

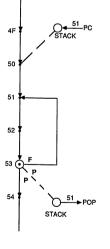

| Opcode                     | Mnemonic                     | Condition           | Execution Example |

|----------------------------|------------------------------|---------------------|-------------------|

| 1(01 <sub>H</sub> )        | PUSHD.P                      | Forced Pass         |                   |

| Description: Push D        | on of Stock under the Earned | Page condition. The | 50                |

| ext address is a Continue. | op of Stack under the Forced | rass condition. The | 51                |

|                            |                              |                     |                   |

|                            |                              |                     | 52 FP — O D STACK |

|                            |                              |                     | 53                |

|                            |                              |                     | 54 ¥              |

|                            |                              |                     |                   |

|                            |                              |                     | 1                 |

|                            |                              |                     |                   |

| Opcode | Mnemonic | Condition | Execution Example |

|--------|----------|-----------|-------------------|

|        |          |           |                   |

01(01<sub>H</sub>)

LDCMD.F

Forced Fail

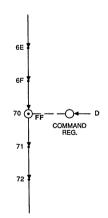

#### **Description:** Load Command Register from D

On a Forced Fail condition, the Command Register is loaded from the least significant three bits of the D input. The remaining bits on the D Port are "don't cares". The three bits of the Command Register are described below:

CR0 - Interrupt acknowledge on Stack full

CR<sub>0</sub> = 1 : inhibit acknowledge on Stack full (default)

CR<sub>0</sub> = 0 : generate acknowledge on Stack full

CR<sub>1</sub> — Multiway Enable

CR<sub>1</sub> = 1 : Enable multiway branching (default for LSS)

CR<sub>1</sub> = 0 : Disable multiway branching (default for MSS)

CR2 - Interrupt post-delay

CR2 = 1 : No post-delay (default)

CR<sub>2</sub> = 0 : Post-delay

Note: When CR<sub>0</sub> = 1, the Stack is checked for a minimum of five locations before acknowledging an interrupt.

|                                                                                                                                                                                                                                                                                                      | Mnemonic                                                                                                                                                                                                                            | Condition                                                                                                                         | Execution Example                      |

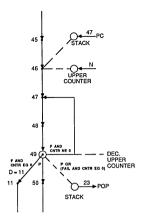

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Description: Load Upper Co If the condition is a Pass, the the previous value in the cou a Fail, the upper counter is le in the counter is lost. In eithe ed Am29112s in the Normal pushed onto the Stack, but it Am29112s in the Extended m spective D inputs and the pre ly pushed onto the Stack. | e upper counter is loaded from<br>nter is pushed onto the Stack<br>paded from the D inputs and<br>er case, a Continue is execut<br>mode, the low order counter<br>is value remains unchanged. I<br>lode, the 16-bit counter is load | m the D inputs and c. If the condition is the previous value ed. For two cascadis conditionally For two cascaded ded from the re- | 38 UUPPER COUNTER  39 41 COUNTER  40 V |

| Opcode                                                                                                                                                                                                                                                                                               | Mnemonic                                                                                                                                                                                                                            | Condition                                                                                                                         | Execution Example                      |

| 26(1A <sub>H</sub> )                                                                                                                                                                                                                                                                                 | POPUC.P                                                                                                                                                                                                                             | Forced Pass                                                                                                                       |                                        |

| Description: Pop to Upper (On a Forced Pass condition, two cascaded Am29112s in t is also popped but the low o                                                                                                                                                                                       | the Stack is popped to the under the Normal mode, the Stack of the counter remains unchanged.                                                                                                                                       | of the low order slice<br>ged. For two cascad-                                                                                    | 4B ¥                                   |

| ed Am29112s in the Extende is popped to the 16-bit conca                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                     | ondition, the Stack                                                                                                               | 4C FP UPPER COUNTER                    |

|                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                     | Condition                                                                                                                         | UPPER COUNTER                          |

| is popped to the 16-bit conca                                                                                                                                                                                                                                                                        | atenated counter.                                                                                                                                                                                                                   |                                                                                                                                   | 4D FP UPPER COUNTER                    |

| Opcode | Mnemonic | Condition | Execution Example |

|--------|----------|-----------|-------------------|

27(1B<sub>H</sub>)

LDDW.C

Conditional

####

The 4-bit Displacement Width (DW) Register is unconditionally loaded from the four LSBs of the D input. (The four MSBs of the D input are ignored.) If the condition is a Pass, the previous value of the Displacement Width Register is pushed onto the Stack. If the condition is a Fail, the previous value of the Displacement Width Register is lost.

#### **Branching Instructions**

#### **Direct Branching**

Instruction 0 is the unconditional jump to zero instruction. This instruction also executes an immediate reset (it is not delayed until the following clock cycle)

Direct branching is implemented by instruction 3 (COND JUMP D) and 4 (COND JSB D). The branch address is input through the D port. If the condition is PASS, the branch is taken, otherwise the sequencer executes a continue. Two-way direct branching is implemented by instruction 19 (COND JMP D/ STACK) and instruction 20 (COND JSB D/STACK). If the condition is Pass, the branch address is taken from the D input port, otherwise, the branch address is taken from the stack. In either case the stack is popped. This instruction assumes that the alternative address was pushed on the stack by a previous instruction. Jump to subroutine differs from JUMP in that the PC register is pushed on the stack. This enables the subroutine to use COND RETURN (7) to return to the point of call. Note that the two-way jump to subroutine (20) causes a simultaneous pop and push so that the stack pointer is unaffected but the top of stack element is replaced by the return address.

#### Relative Branching

In the relative branch instructions, a dynamically alterable subfield of the D inputs is added to the PC to form the branch address. The remaining most significant bits of the D inputs are ignored and internally converted to all 0's for forward branches and all 1's for backward branches. The displacement width (DW) Register in the Am29112 holds the number of least significant bits of D that participate in the relative branch as the displacement, and can be loaded from the lower four bits of the D port. In cascaded systems, the displacement width has to be loaded consistently in the two chips. For example, for a displacement width of 9, the lower order chip gets a displacement width of 8 and the higher order chip gets a displacement width of 1. As another example, if the lower order chip has a displacement width of less than 8 bits, the higher order chip must have a displacement width of zero. If the displacement width register is loaded with any value greater than 8, it is exactly as if it were loaded with 8.

Instruction 28 (29) is the relative jump (jump back) instruction, and instruction 30 (31) is the relative jump to subroutine (jump back to subroutine) instruction. For backward relative branches, the displacement must be coded as a two's complement negative number. When the displacement width is the same as the microaddress width the forward and backward relative branch instructions are identical. When the displacement width is less than the microaddress width, the more significant bits of D outside the displacement are forced to all zeros for positive branches and to all ones for negative branches. This is effectively sign extension except that the sign information is contained in the instruction rather than the displacement, and there is no need for sign information to propagate between cascaded chips since it is assumed that the displacement width registers in the two chips have been consistently loaded.

The disadvantage of having the sign information in the instruction rather than the displacement can be overcome by a judicious choice of instruction format. The opcodes for forward and backward relative branch instructions have been chosen to differ in the least significant bit position only, with a "0" in that bit for forward branches and a "1" for backward branches. If the sequencer instruction field is contiguous with and on the more significant side of the displacement field in the pipeline register, then the least significant instruction bit is like the sign bit for the displacement for relative branch instructions. This permits the assembler to use the same

opcode for forward and backward relative branch instructions, but overlap the displacement field (now declared to be one bit longer than the actual displacement field in the pipeline) with the sequencer instruction field by one bit. If the assembler now generates a negative displacement, the sequencer opcode formed is the backward branch; while if the displacement is positive, the sequencer opcode formed is forward branch.

When the instruction is executed, the PC already has been incremented and points to the next sequential instruction, hence a forward branch with a displacement of 0 causes the next sequential instruction to be executed.

#### **Multiway Branching**

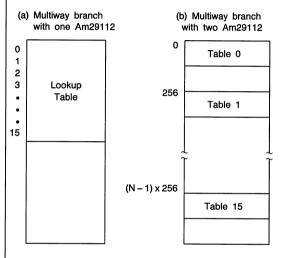

Two variants of multiway branching are available on the Am29112 – multiway substitute D (see Figure 5) and multiway relative D (see Figure 6). In multiway substitute D the 4 multiway inputs directly replace the 4 least significant bits of the branch address input at D. Instruction 5 is a conditional multiway branch and instruction 6 a conditional multiway subroutine call. In these instructions, the least significant 4 bits of the D input port are not used by the sequencer, and may be shared, for instance to select among different sets of multiway inputs.

- 1. Concatenation

- (a) With one Am29112

$$Y_7 - Y_0 = D_7 - D_4 \bullet M_3 - M_0$$

(b) With two Am29112

$$Y_{15} - Y_0 = D_{15} - D_{12} \bullet M_7 - M_4 \bullet D_7 - D_4 \bullet M_3 - M_0$$

(\*(dot) denotes concatenation)

Figure 5. Multiway Branch — Concatenation

2. Relative to data inputs

(a) With one Am29112

$$Y_7 - Y_0 = D_7 - D_0 + M_3 - M_0$$

(b) With two Am29112

$$Y_{15} - Y_8 = D_{15} - D_8 + M_7 - M_4 + ACIO$$

$$Y_7 - Y_0 = D_7 - D_0 + M_3 - M_0$$

Figure 6. Multiway Branch — Relative to Data Inputs

Multiway branching has the disadvantage that the jump table must be aligned on a 16-word boundary. This disadvantage is overcome in the Am29112 multiway relative branching instructions. In these instructions, the number input on the multiway pins is added to the branch address input at D. Instruction 21 is a conditional multiway relative branch and instruction 22 a conditional multiway relative subroutine call.

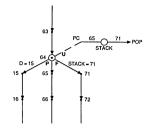

One of the advantages of multiway branching is that it enables a 16-way decision to be made in exactly one microcycle. However, the 16 target addresses are constrained to be contiguous in memory. Hence, if the target routines need more than one microword each, as is very likely, they are addressed indirectly through a table of 16 contiguous branch instructions. For very high-speed applications, the extra microcycle needed to branch indirectly off the jump table may not be acceptable. This penalty is avoidable if the multiway bits are offset with respect to the D inputs. When two cascaded Am29112s are used, there are two sets of 4-bit multiway inputs. The least significant chip has a multiway input with no offset, while the

most significant chip has a multiway input with an 8-bit offset. The Am29112 command register has a bit CR<sub>1</sub> that enables or disables multiway branching on the chip. In a system with two cascaded Am29112s, each chip has a command register bit. Multiway branching may be disabled in either chip by resetting the command register bit on that chip, or enabled by setting the command register bit. When multiway branching is disabled on a chip, for that chip both multiway and multiway relative branches are converted to direct branches, and the multiway inputs are a Don't Care. Multiway branching with an 8-bit offset is implemented by disabling multiway in the least significant slice and enabling it in the most significant slice. In this case, the 16 target addresses are dispersed in memory. separated by 256 locations each. Another useful configuration is obtained by enabling multiway on both chips. In this case, up to 16 sets of target addresses are dispersed in memory. separated by 256 locations each (see Figure 7).

Figure 7. Table Lookup Using Multiway

The Am29112 does not have an unconditional continue in its instruction set. This is not expected to be a drawback because the instruction set requires that both Unconditional Pass and Unconditional Fail are programmable by the sequencer to select among different instructions sharing the same opcode. Hence, a continue is obtained by executing instruction 3 (COND JUMP D) with a Forced Fail condition.

#### **Looping Instructions**

The looping instructions on the Am29112 are of two kinds: conditional, which depend on an external condition to signal loop termination, and iterative, which decrement the Am29112 counter and check for a count of zero. There is also a three-way branch instruction that combines the check for external condition with the check for count of zero in a single instruction.

All the looping instructions are similar in two respects. Firstly, the check for the loop condition is done at the end of the loop. This implies that the loop body is always executed at least once. Secondly, in the case that the loop has to be repeated, a backward branch to the loop head is made by using the address on top of stack. This frees the D inputs for other use, but makes it necessary to push the address of the start of the loop on the stack before entering the loop. Also, if the loop is iterative, it is necessary to load a count value in the counter at the same time. Instructions 24 (PUSH PC; COND LOAD UPPER COUNTER) and 8 (PUSH PC; COND LOAD LOWER COUNTER) combine both these requirements.