# Am29325

32-Bit Floating Point Processor

## **PRELIMINARY**

#### DISTINCTIVE CHARACTERISTICS

- Single VLSI device performs high-speed floating-point arithmetic

- Floating-point addition, subtraction and multiplication in a single clock cycle

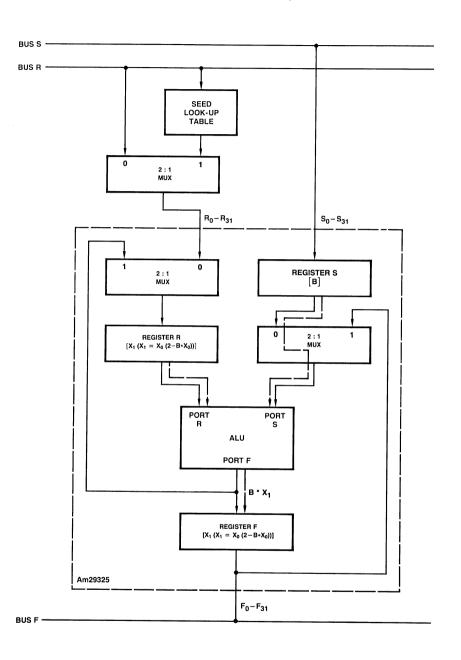

- Internal architecture supports sum-of-products, Newton-Raphson division

- 32-bit, 3-bus flow-through architecture

- Programmable I/O allows interface to 32- and 16-bit systems

- . IEEE and DEC formats

- Performs conversions between formats

- Performs integer → → floating point conversions

- Six flags indicate operation status

- Register enables eliminate clock skew

- Input and output registers can be made transparent independently

## GENERAL DESCRIPTION

The Am29325 is a high-speed floating-point processor unit. It performs 32-bit single-precision floating-point addition, subtraction, and multiplication operations in a single LSI integrated circuit, using the format specified by the proposed IEEE floating-point standard P754. The DEC single-precision floating-point format is also supported. Operations for conversion between 32-bit integer format and floating-point format are available, as are operations for converting between the IEEE and DEC floating-point formats. Any operation can be performed in a single clock cycle. Six flags—invalid operation, inexact result, zero, not-a-number, overflow, and underflow—monitor the status of operations.

The Am29325 has a 3-bus, 32-bit architecture, with two input buses and one output bus. This configuration provides

high I/O bandwidth, allows access to all buses and affords a high degree of flexibility when connecting this device in a system. All buses are registered, with each register having a clock enable. Input and output registers may be made transparent independently. Two other I/O configurations, a 32-bit, 2-bus architecture and a 16-bit, 3-bus architecture, are user-selectable, easing interface with a wide variety of systems. Thirty-two-bit internal feedforward data paths support accumulation operations, including sum-of-products and Newton-Raphson division.

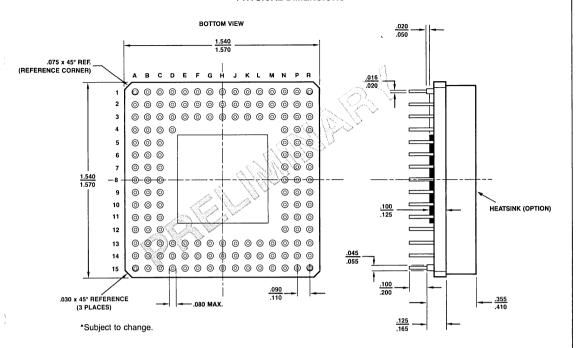

Fabricated with the high-speed IMOX™ bipolar process, the Am29325 is powered by a single 5-volt supply. The device is housed in a 144-pin pin-grid-array package.

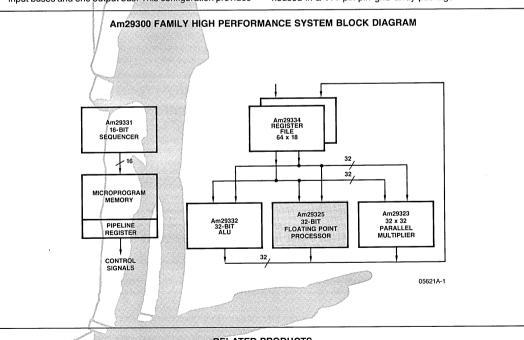

## RELATED PRODUCTS

- Am29323 32 x 32 Parallel Multiplier

- Am29332 32-Bit ALU

- Am29331 16-Bit Sequencer

Am29334 – 64 x 18 Four-Port Dual-Access Register File

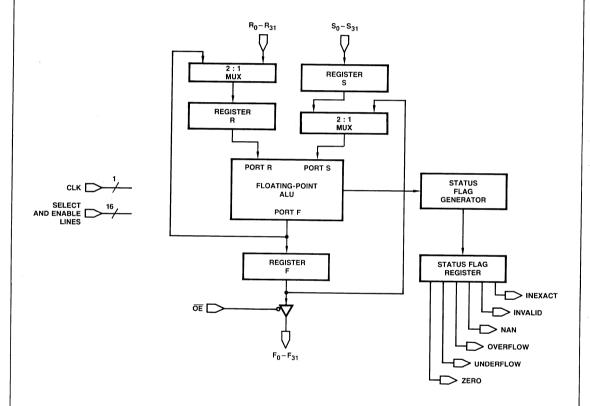

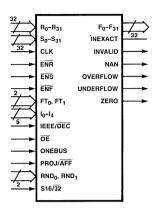

## BLOCK DIAGRAM Am29325

05621B-2

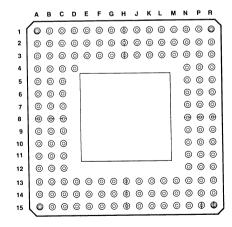

## PACKAGE INFORMATION

## PACKAGE PHOTOGRAPHS

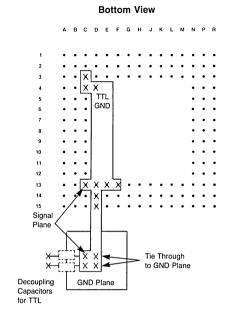

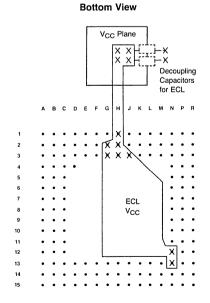

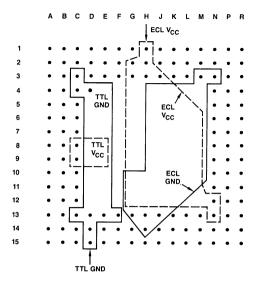

**Top View**

Lateral View

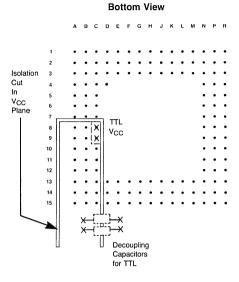

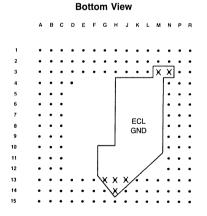

**Bottom View**

Isometric View

## Am29325 PINOUT

## **SORTED BY PIN NUMBER**

## SORTED BY FUNCTIONAL NAME

| Line #   | Pin #    | Functional Name                   |

|----------|----------|-----------------------------------|

| 1        | A1       | Inexact                           |

| 2        | A2       | Invalid                           |

| 3        | A3       | F <sub>29</sub>                   |

| 4        | A4       | F <sub>30</sub>                   |

| 5        | A5       | F <sub>23</sub>                   |

| 6        | A6       | F <sub>26</sub>                   |

| 7        | A7       | F <sub>21</sub>                   |

| 8        | A8       | F <sub>22</sub>                   |

| 9        | A9       | F <sub>17</sub>                   |

| 10       | A10      | F <sub>18</sub>                   |

| 11       | A11      | F <sub>13</sub>                   |

| 12       | A12      | F <sub>12</sub>                   |

| 13       | A13      | F <sub>7</sub>                    |

| 14       | A14      | F <sub>8</sub>                    |

| 15       | A15      | F <sub>5</sub>                    |

| 16       | B1       | l <sub>2</sub>                    |

| 17       | B2       | ÑAN                               |

| 18       | B3       | Zero                              |

| 19       | B4       | F <sub>31</sub>                   |

| 20       | B5       | Overflow                          |

| 21       | B6       | F <sub>27</sub>                   |

| 22       | B7       | F <sub>24</sub>                   |

| 23       | B8       | F <sub>19</sub>                   |

| 24       | B9       | F <sub>20</sub>                   |

| 25       | B10      | F <sub>15</sub>                   |

| 26       | B11      | F <sub>14</sub>                   |

| 27       | B12      | F <sub>9</sub>                    |

| 28       | B13      | F <sub>6</sub>                    |

| 29       | B14      | F <sub>3</sub>                    |

| 30       | B15      | F <sub>4</sub>                    |

| 31       | C1       | l <sub>1</sub>                    |

| 32       | C2       | I <sub>0</sub>                    |

| 33       | C3       | GND, TTL                          |

| 34       | C4       | GND, TTL                          |

| 35       | C5       | Underflow                         |

| 36       | C6       | F <sub>28</sub>                   |

| 37       | C7       | F <sub>25</sub>                   |

| 38       | C8       | V <sub>CC</sub> , TTL             |

| 39       | C9       | V <sub>CC</sub> , TTL             |

| 40       | C10      | F <sub>16</sub>                   |

| 41       | C11      | F <sub>11</sub>                   |

| 42       | C12      | F <sub>10</sub>                   |

| 43       | C13      | GND, TTL                          |

| 44       | C14      | F <sub>2</sub>                    |

| 45       | C15      | F <sub>1</sub><br>ENF             |

| 46       | D1       |                                   |

| 47       | D2       | IEEE/DEC                          |

| 48       | D3       | ENR<br>GND. TTL                   |

| 49       | D13      | GND, TTL<br>GND, TTL              |

| 50       | D14      | GND, TTL<br>GND, TTL              |

| 51       | D15      | 1                                 |

| 52<br>53 | E1<br>E2 | I <sub>4</sub><br>FT <sub>0</sub> |

| 53       | E3       | ENS                               |

|          | E13      | GND, TTL                          |

| 55<br>56 | E13      |                                   |

| 57       | E15      | F <sub>0</sub><br>PROJ/AFF        |

| 58       | F1       | ONEBUS                            |

| 59       | F2       | FT <sub>1</sub>                   |

| 60       | F3       | S16/32                            |

|          | _ гз     | 310/32                            |

| Functional Name                    | Pin #      |

|------------------------------------|------------|

| CLK<br>ENF                         | J1<br>D1   |

| ENR                                | D3         |

| ENS                                | E3         |

| F <sub>0</sub>                     | E14        |

| F <sub>1</sub>                     | C15        |

| F <sub>2</sub>                     | C14        |

| <u>F</u> 3                         | B14        |

| F <sub>4</sub>                     | B15        |

| F <sub>5</sub><br>F <sub>6</sub>   | A15<br>B13 |

| ' 6<br>F <sub>7</sub>              | A13        |

| F <sub>8</sub>                     | A14        |

| F <sub>9</sub>                     | B12        |

| F <sub>10</sub>                    | C12        |

| F <sub>11</sub>                    | C11        |

| F <sub>12</sub>                    | A12        |

| F <sub>13</sub>                    | A11        |

| F <sub>14</sub>                    | B11        |

| F <sub>15</sub><br>F <sub>16</sub> | B10<br>C10 |

| F <sub>17</sub>                    | A9         |

| F <sub>18</sub>                    | A10        |

| F <sub>19</sub>                    | B8         |

| F <sub>20</sub>                    | B9         |

| F <sub>21</sub>                    | A7         |

| F <sub>22</sub>                    | A8         |

| F <sub>23</sub>                    | A5<br>B7   |

| F <sub>24</sub><br>F <sub>25</sub> | C7         |

| F <sub>26</sub>                    | A6         |

| F <sub>27</sub>                    | B6         |

| F <sub>28</sub>                    | C6         |

| F <sub>29</sub>                    | A3         |

| <u>F</u> 30                        | A4         |

| F <sub>31</sub><br>FT <sub>0</sub> | B4<br>E2   |

| FT <sub>1</sub>                    | F2         |

| GND, ECL                           | N3         |

| GND, ECL                           | H14        |

| GND, ECL                           | G13        |

| GND, ECL                           | M3         |

| GND, ECL                           | H13        |

| GND, ECL                           | J13<br>D15 |

| GND, TTL<br>GND, TTL               | D13        |

| GND, TTL                           | E13        |

| GND, TTL                           | F13        |

| GND, TTL                           | C4         |

| GND, TTL                           | СЗ         |

| GND, TTL                           | D13        |

| GND, TTL                           | C13        |

| l <sub>0</sub>                     | C2<br>C1   |

| կ <sub>1</sub><br>կ <sub>2</sub>   | B1         |

| l <sub>3</sub>                     | P9         |

| 13<br>14                           | E1         |

| IEEE/DEC                           | D2         |

| Inexact                            | A1         |

| Invalid                            | A2         |

## Am29325 PINOUT (Cont)

## SORTED BY PIN NUMBER

## SORTED BY FUNCTIONAL NAME

|            | SORTED BY PIN | NUMBER                      |

|------------|---------------|-----------------------------|

| Line #     | Pin #         | Functional Name             |

| 61         | F13           | GND, TTL                    |

| 62         | F14           | S <sub>1</sub>              |

| 63         | F15           | S <sub>0</sub>              |

| 64         | G1            | ) ÖE                        |

| 65         | G2            | V <sub>CC</sub> , ECL       |

| 66         | G3            | V <sub>CC</sub> , ECL       |

| 67         | G13           | GND, ECL                    |

| 68         | G14           | S <sub>2</sub>              |

| 69         | G15           | S <sub>3</sub>              |

| 70         | H1            | V <sub>CC</sub> , ECL       |

| 71         | H2            | V <sub>CC</sub> , ECL       |

| 72         | H3            | V <sub>CC</sub> , ECL       |

| 73         | H13           | GND, ECL                    |

| 74         | H14           | GND, ECL                    |

| 75         | H15           | S <sub>5</sub>              |

| 76         | J1            | CLK                         |

| 77         | J2            | RND <sub>0</sub>            |

| 78         | J3            | V <sub>CC</sub> , ECL       |

| 79<br>80   | J13           | GND, ECL                    |

| 81         | J14<br>J15    | S <sub>4</sub>              |

| 82         | K1            | S <sub>7</sub>              |

| 83         | K2            | R <sub>31</sub><br>RND₁     |

| 84         | K3            | R <sub>29</sub>             |

| 85         | K13           | S <sub>8</sub>              |

| 86         | K14           | S <sub>9</sub>              |

| 87         | K15           | S <sub>6</sub>              |

| 88         | L1            | R <sub>30</sub>             |

| 89         | L2            | R <sub>27</sub>             |

| 90         | L3            | R <sub>26</sub>             |

| 91         | L13           | S <sub>13</sub>             |

| 92         | L14           | S <sub>10</sub>             |

| 93         | L15           | S <sub>11</sub>             |

| 94         | M1            | R <sub>25</sub>             |

| 95         | M2            | R <sub>28</sub>             |

| 96         | M3            | GND, ECL                    |

| 97         | M13           | S <sub>14</sub>             |

| 98         | M14           | S <sub>15</sub>             |

| 99         | M15           | S <sub>12</sub>             |

| 100<br>101 | N1<br>N2      | R <sub>24</sub>             |

| 102        | N3            | R <sub>23</sub><br>GND, ECL |

| 103        | N4            | R <sub>15</sub>             |

| 104        | N5            | R <sub>14</sub>             |

| 105        | N6            | R <sub>9</sub>              |

| 106        | N7            | R <sub>8</sub>              |

| 107        | N8            | R <sub>3</sub>              |

| 108        | N9            | R <sub>0</sub>              |

| 109        | N10           | S <sub>28</sub>             |

| 110        | N11           | S <sub>27</sub>             |

| 111        | N12           | V <sub>CC</sub> , ECL       |

| 112        | N13           | V <sub>CC</sub> , ECL       |

| 113        | N14           | S <sub>18</sub>             |

| 114        | N15           | S <sub>17</sub>             |

| 115        | P1            | R <sub>21</sub>             |

| 116        | P2            | R <sub>22</sub>             |

| 117        | P3            | R <sub>19</sub>             |

| 118        | P4            | R <sub>16</sub>             |

| 119<br>120 | P5            | R <sub>11</sub>             |

| 120        | P6            | R <sub>10</sub>             |

| SORTED BY FU                       | NCTIONAL NAME |

|------------------------------------|---------------|

| Functional Name                    | Pin #         |

| NAN                                | B2            |

| ŌĒ                                 | G1            |

| ONEBUS                             | F1            |

| Overflow                           | B5            |

| PROJ/AFF                           | E15           |

| R <sub>0</sub>                     | N9            |

| R₁                                 | R8            |

| R <sub>2</sub>                     | R9            |

| R <sub>3</sub>                     | N8            |

| R <sub>4</sub>                     | P8            |

| R <sub>5</sub>                     | P7            |

| R <sub>6</sub>                     | R7            |

| R <sub>7</sub>                     | R6            |

| R <sub>8</sub>                     | N7            |

| R <sub>9</sub>                     | N6            |

| R <sub>10</sub>                    | P6            |

| R <sub>11</sub>                    | P5            |

| R <sub>12</sub>                    | R5            |

| R <sub>13</sub>                    | R4            |

| R <sub>14</sub>                    | N5            |

| R <sub>15</sub>                    | N4            |

| R <sub>16</sub>                    | P4            |

| R <sub>17</sub>                    | R2            |

| R <sub>18</sub>                    | R3            |

| R <sub>19</sub>                    | P3            |

| R <sub>20</sub>                    | R1            |

| R <sub>21</sub>                    | P1            |

| R <sub>22</sub>                    | P2            |

| R <sub>23</sub>                    | N2            |

| R <sub>24</sub>                    | N1            |

| R <sub>25</sub>                    | M1            |

| R <sub>26</sub>                    | L3            |

| R <sub>27</sub><br>R <sub>28</sub> | L2            |

| Pos                                | M2            |

| R <sub>29</sub><br>R <sub>30</sub> | КЗ            |

| R <sub>31</sub>                    | L1            |

| RND <sub>0</sub>                   | K1            |

| RND <sub>1</sub>                   | J2            |

| S <sub>0</sub>                     | K2            |

| S <sub>1</sub>                     | F15<br>F14    |

| S <sub>2</sub>                     | G14           |

| S <sub>3</sub>                     | G14<br>G15    |

| S <sub>4</sub>                     | J14           |

| S <sub>5</sub>                     | H15           |

| S <sub>6</sub>                     | K15           |

| S <sub>7</sub>                     | J15           |

| S <sub>8</sub>                     | K13           |

| S <sub>9</sub>                     | K14           |

| S <sub>10</sub>                    | L14           |

| S <sub>11</sub>                    | L15           |

| S <sub>12</sub>                    | M15           |

| S <sub>13</sub>                    | L13           |

| S <sub>14</sub>                    | M13           |

| S <sub>15</sub>                    | M14           |

| S <sub>16</sub>                    | P15           |

| S16/ <del>32</del>                 | F3            |

| S <sub>17</sub>                    | N15           |

| S <sub>18</sub>                    | N14           |

| S <sub>19</sub>                    | R15           |

|                                    | •             |

## Am29325 PINOUT (Cont)

## **SORTED BY PIN NUMBER**

| Line # | Pin # | Functional Name |

|--------|-------|-----------------|

| 121    | P7    | R <sub>5</sub>  |

| 122    | P8    | R <sub>4</sub>  |

| 123    | P9    | l <sub>3</sub>  |

| 124    | P10   | S <sub>31</sub> |

| 125    | P11   | S <sub>26</sub> |

| 126    | P12   | S <sub>25</sub> |

| 127    | P13   | S <sub>22</sub> |

| 128    | P14   | S <sub>21</sub> |

| 129    | P15   | S <sub>16</sub> |

| 130    | R1    | R <sub>20</sub> |

| 131    | R2    | R <sub>17</sub> |

| 132    | R3    | R <sub>18</sub> |

| 133    | R4    | R <sub>13</sub> |

| 134    | R5    | R <sub>12</sub> |

| 135    | R6    | R <sub>7</sub>  |

| 136    | R7    | R <sub>6</sub>  |

| 137    | R8    | R <sub>1</sub>  |

| 138    | R9    | R <sub>2</sub>  |

| 139    | R10   | S <sub>30</sub> |

| 140    | R11   | S <sub>29</sub> |

| 141    | R12   | S <sub>24</sub> |

| 142    | R13   | S <sub>23</sub> |

| 143    | R14   | S <sub>20</sub> |

| 144    | R15   | S <sub>19</sub> |

## SORTED BY FUNCTIONAL NAME

| Functional Name       | Pin # |

|-----------------------|-------|

| S <sub>20</sub>       | R14   |

| S <sub>21</sub>       | P14   |

| S <sub>22</sub>       | P13   |

| S <sub>23</sub>       | R13   |

| S <sub>24</sub>       | R12   |

| S <sub>25</sub>       | P12   |

| S <sub>26</sub>       | P11   |

| S <sub>27</sub>       | N11   |

| S <sub>28</sub>       | N10   |

| S <sub>29</sub>       | R11   |

| S <sub>30</sub>       | R10   |

| S <sub>31</sub>       | P10   |

| Underflow             | C5    |

| V <sub>CC</sub> , ECL | J3    |

| V <sub>CC</sub> , ECL | G2    |

| V <sub>CC</sub> , ECL | G3    |

| V <sub>CC</sub> , ECL | H2    |

| V <sub>CC</sub> , ECL | N13   |

| V <sub>CC</sub> , ECL | N12   |

| V <sub>CC</sub> , ECL | H3    |

| V <sub>CC</sub> , ECL | H1    |

| V <sub>CC</sub> , TTL | C8    |

| V <sub>CC</sub> , TTL | C9    |

| Zero                  | B3    |

## **GRID ARRAY PIN CONFIGURATION**

## Am29325

## LOGIC SYMBOL

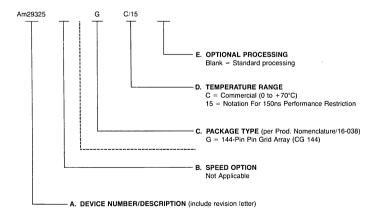

## ORDERING INFORMATION

## **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: **A. Device Number**

B. Speed Option (if applicable)

C. Dockers Time

C. Package Type

D. Temperature Range E. Optional Processing

## **Valid Combinations**

| Valid Combinations list configurations planned to be       |

|------------------------------------------------------------|

| supported in volume for this device. Consult the local     |

| AMD sales office to confirm availability of specific valid |

| combinations.                                              |

# Valid Combinations Am29325 GC/15

#### **DEFINITION OF TERMS**

#### AFFINE MODE

One of two modes affecting the handling of operations on infinities – see the **Operations with Infinities** section under **Operation in IEEE Mode** below.

#### BIASED EXPONENT

The true exponent of a floating-point number, plus a constant. For IEEE floating-point numbers, the constant is 127; for DEC floating-point numbers, the constant is 128. See also **True Exponent**.

## **BUS**

Data input or output channel for the floating-point processor.

#### DEC RESERVED OPERAND

A DEC floating-point number that is interpreted as a symbol and has no numeric value. A DEC reserved operand has a sign of 1 and a biased exponent of 0.

#### **DESTINATION FORMAT**

The format of the final result produced by the floating-point ALU. The destination format can be IEEE floating-point, DEC floating-point or integer.

#### FINAL RESULT

The result produced by the floating-point ALU.

## **FRACTION**

The twenty-three least-significant bits of the mantissa.

#### **INFINITELY PRECISE RESULT**

The result that would be obtained from an operation if both exponent range and precision were unbounded.

#### INPUT OPERANDS

The value or values on which an operation is performed. For example, the addition 2 + 3 = 5 has input operands 2 and 3.

#### MANTISSA

The portion of a floating-point number containing the number's significant bits. For the floating-point number 1.101 x  $2^{-3}$ , the mantissa is 1.101.

## NAN (Not-a-Number)

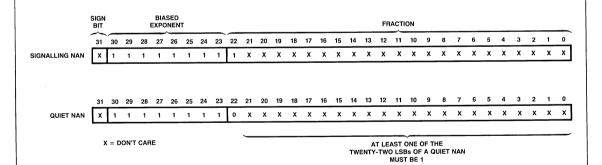

An IEEE floating-point number that is interpreted as a symbol, and has no numeric value. A NAN has a biased exponent of 255<sub>10</sub> and a non-zero fraction.

#### PORT

Data input or output channel for the floating-point ALU.

#### PROJECTIVE MODE

One of two modes affecting the handling of operations on infinities – see the **Operations with Infinities** section under **Operation in IEEE Mode** below.

#### **ROUNDED RESULT**

The result produced by rounding the infinitely precise result to fit the destination format.

## TRUE EXPONENT (or Exponent)

Number representing the power of two by which a floating-point number's mantissa is to be multiplied. For the floating-point number  $1.101 \times 2^{-3}$ , the true exponent is -3.

## PIN DESCRIPTION

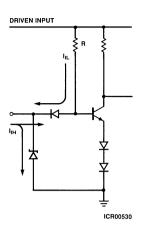

| PIN DESCI                       | RIPTION                                                                                                                                                                               |                                     |                                                                                                                                                                                                                                                     |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>0</sub> -R <sub>31</sub> | $\ensuremath{R}$ operand bus, input. $\ensuremath{R}_0$ is the least-significant bit.                                                                                                 | INVALID                             | Invalid operation flag, output. Active High—A HIGH indicates that the last operation per-                                                                                                                                                           |

| S <sub>0</sub> -S <sub>31</sub> | S operand bus, input. $S_0$ is the least-significant bit.                                                                                                                             | NAN                                 | formed was invalid, e.g., ∞ times 0.  Not-a-number flag, output. Active High—A                                                                                                                                                                      |

| F <sub>0</sub> -S <sub>31</sub> | $\mbox{\bf F}$ operand bus, output. $\mbox{\bf F}_0$ is the least-significant bit.                                                                                                    |                                     | HIGH indicates that the final result produced<br>by the last operation is not to be interpreted<br>as a number. The output in such cases is ei-                                                                                                     |

| CLK                             | Clock input for the internal registers.                                                                                                                                               |                                     | ther an IEEE Not-a-Number (NAN) or a DEC reserved operand.                                                                                                                                                                                          |

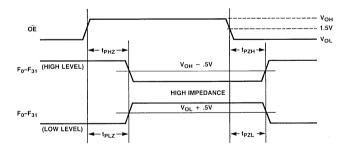

| ENR                             | Register R clock enable, input. Active Low—When ENR is LOW, register R is clocked on the LOW-to-HIGH transition of CLK. When ENR is HIGH, register R retains the previous contents.   | ŌE                                  | Output enable, input. Active Low—When $\overline{\text{OE}}$ is LOW, the contents of register F are placed on F <sub>0</sub> -F <sub>31</sub> . When $\overline{\text{OE}}$ is HIGH, F <sub>0</sub> -F <sub>31</sub> assume a high-impedance state. |

| ENS                             | Register S clock enable, input. Active Low—When ENS is LOW, register S is clocked on the LOW-to-HIGH transition of CLK. When ENS is HIGH, register S retains the previous contents.   | ONEBUS                              | Input bus configuration control, input. A LOW on ONEBUS configures the input bus circuitry for two-input bus operation. A HIGH on ONEBUS configures the input bus circuitry for single-input bus operation.                                         |

| ENF                             | Register F clock enable, input. Active Low—When ENF is LOW, register F is clocked on the LOW-to-HIGH transition of CLK. When ENF is HIGH, register F retains the previous             | OVERFLOW                            | Overflow flag, output. Active High—A HIGH indicates that the last operation produced a final result that overflowed the floating-point format.                                                                                                      |

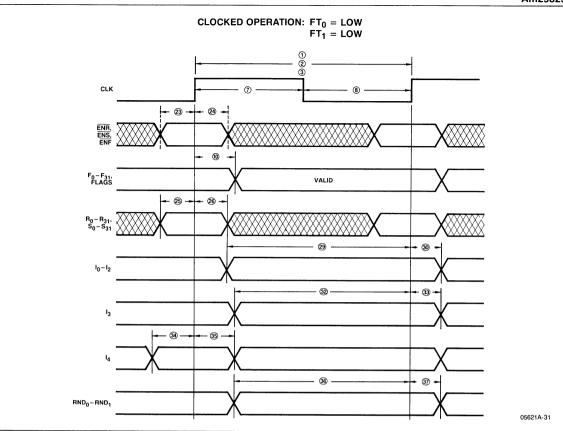

| FT <sub>0</sub>                 | contents.  Input register feedthrough control, input. Active High—When FT <sub>0</sub> is HIGH, registers R and S are transparent.                                                    | PROJ/AFF                            | Projective/affine mode select, input. Choice of projective or affine mode determines the way in which infinities are handled in IEEE mode. A LOW on PROJ/AFF selects affine mode; a HIGH selects projective mode.                                   |

| FT <sub>1</sub>                 | Output register feedthrough control, input. Active High—When $\mathrm{FT}_1$ is HIGH, register F and the status flag register are transparent.                                        | RND <sub>0</sub> , RND <sub>1</sub> | Rounding mode selects, inputs. RND <sub>0</sub> and RND <sub>1</sub> select one of four rounding modes. See the <b>Rounding Mode Select Table</b> for a list of                                                                                     |

| I <sub>0</sub> -I <sub>2</sub>  | Operation select lines, inputs. Used to select the operation to be performed by the ALU.                                                                                              |                                     | rounding modes and the corresponding control codes.                                                                                                                                                                                                 |

|                                 | See the <b>ALU Operation Select Table</b> for a list of operations and the corresponding codes.                                                                                       | S16/32                              | Sixteen- or thirty-two bit I/O mode select, input. A LOW on S16/32 selects the thirty-two-bit I/O mode; a HIGH selects the                                                                                                                          |

| l <sub>3</sub>                  | ALU S port input select, input. A LOW on $\rm I_3$ selects register S as the input to the ALU S port. A HIGH on $\rm I_3$ selects register F as the input to the ALU S port.          |                                     | sixteen-bit I/O mode. In thirty-two-bit mode, inputs and output buses are 32 bits wide. In sixteen-bit mode, input and output buses are sixteen bits wide, with the least and most significant portions of the thirty-two bit input and             |

| 14                              | Register R input select, input. A LOW on I <sub>4</sub> selects R <sub>0</sub> -R <sub>31</sub> as the input to register R. A HIGH selects the ALU F port as the input to register R. |                                     | output words being placed on the buses during the HIGH and LOW portions of CLK, respectively.                                                                                                                                                       |

| IEEE/DEC                        | IEEE/DEC mode select, input. When IEEE/DEC is HIGH, IEEE mode is selected. When IEEE/DEC is LOW, DEC mode is selected.                                                                | UNDERFLOW                           | Underflow flag, output. Active High—A HIGH indicates that the last operation produced a rounded result that underflowed the floating-point format.                                                                                                  |

| INEXACT                         | Inexact result flag, output. Active High—A HIGH indicates that the final result of the last operation was not infinitely precise, due to                                              | ZERO                                | Zero flag, output. Active High—A HIGH indicates that the last operation produced a final result of zero.                                                                                                                                            |

result of zero.

operation was not infinitely precise, due to

rounding.

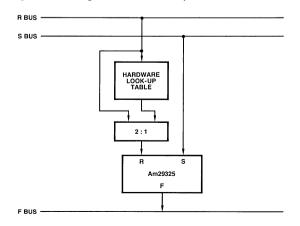

#### **ARCHITECTURE**

The Am29325 comprises a high-speed, floating-point ALU, a status flag generator, and a 32-bit data path.

#### Floating-Point ALU

The floating-point ALU performs 32-bit floating-point operations. It also performs floating-point-to-integer conversions, integer-to-floating-point conversions, and conversions between the IEEE and DEC floating-point formats. The ALU has two 32-bit input ports, R and S, and a 32-bit output port, F.

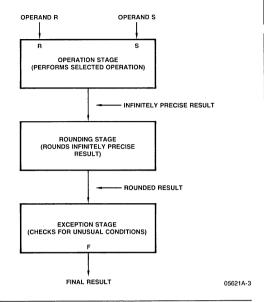

Conceptually, the process performed by the ALU can be divided into three stages — see Figure 1. The operation stage performs the arithmetic operation selected by the user; the output of this section is referred to as the infinitely precise result of the operation. The rounding stage rounds the infinitely precise result to fit in the destination format; the output of this stage is called the rounded result. The last stage checks for exceptional conditions. If no exceptional condition is found, the rounded result is passed through this stage. If some exceptional condition is found, e.g., overflow, underflow, or an invalid operation, this section may replace the rounded result with another output, such as  $+\infty$ ,  $-\infty$ , a NAN, or a DEC reserved operand. The output of this last stage appears on port F, and is called the final result.

The ALU performs one of eight operations; the operation to be performed is selected by placing the appropriate control code on lines  $I_0-I_2$ . The **ALU Operation Select Table** gives the control codes corresponding to each of the eight operations.

The floating-point addition operation (R PLUS S) adds the floating-point numbers on ports R and S, and places the floating-point result on port F. In IEEE mode (IEEE/ $\overline{\text{DEC}}$  = HIGH) the addition is performed in IEEE floating-point format; in DEC mode (IEEE/ $\overline{\text{DEC}}$  = LOW) the addition is performed in DEC format.

The floating-point subtraction operation (R MINUS S) subtracts the floating-point number on port S from the floating-point number on port R and places the floating-point result on port F. In IEEE mode (IEEE/ $\overline{\text{DEC}}$  = HIGH) the subtraction is performed in IEEE floating-point format; in DEC mode (IEEE/ $\overline{\text{DEC}}$  = LOW) the subtraction is performed in DEC format.

The floating-point multiplication operation (R TIMES S) multiplies the floating-point numbers on ports R and S, and places the floating-point result on port F. In IEEE mode (IEEE/DEC = HIGH)

Figure 1. Conceptual Model of the Process Performed by the Floating-Point ALU

the multiplication is performed in IEEE floating-point format; in DEC mode (IEEE/ $\overline{\text{DEC}}$  = LOW) the multiplication is performed in DEC format.

The floating-point constant subtraction (2 MINUS S) operation subtracts the floating-point value on port S from 2, and places the result on port F. The operand on port R is not used in this operation; its value will not affect the operation in any way. In IEEE mode (IEEE/ $\overline{\text{DEC}}$  = HIGH) the operation is performed in IEEE floating-point format; in DEC mode (IEEE/ $\overline{\text{DEC}}$  = LOW) the operation is performed in DEC format. This operation is used to support Newton-Raphson floating-point division; a description of its use appears in **Appendix C**.

The integer-to-floating-point conversion (INT-TO-FP) operation takes a 32-bit, two's complement integer on port R and places the equivalent floating-point value on port F. The operand on port S is not used in this operation; its value will not affect the operation in any way. In IEEE mode (IEEE/DEC = HIGH) the result is delivered in IEEE format; in DEC mode (IEEE/DEC = LOW) the result is delivered in DEC format.

#### ALU OPERATION SELECT TABLE

| 12 | 11 | l <sub>0</sub> | Operation                                        | Output Equation                  |

|----|----|----------------|--------------------------------------------------|----------------------------------|

| 0  | 0  | 0              | Floating-point addition (R PLUS S)               | F = R + S                        |

| 0  | 0  | 1              | Floating-point subtraction (R MINUS S)           | F = R - S                        |

| 0  | 1  | 0              | Floating-point multiplication (R TIMES S)        | F = R * S                        |

| 0  | 1  | 1              | Floating-point constant subtraction (2 MINUS S)  | F = 2 - S                        |

| 1  | 0  | 0              | Integer-to-floating-point conversion (INT-TO-FP) | F (floating-point) = R (integer) |

| 1  | 0  | 1              | Floating-point-to-integer conversion (FP-TO-INT) | F (integer) = R (floating-point) |

| 1  | 1  | 0              | IEEE-TO-DEC format conversion (IEEE-TO-DEC)      | F (DEC format) = R (IEEE format) |

| 1  | 1  | 1              | DEC-TO-IEEE format conversion (DEC-TO-IEEE)      | F (IEEE format) = R (DEC format) |

The floating-point-to integer conversion (FP-TO-INT) operation takes a floating-point number on port R and places the equivalent 32-bit, two's complement integer value on port F. The operand on port S is not used in this operation; its value will not affect the operation in any way. In IEEE mode (IEEE/ $\overline{\text{DEC}}$  = HIGH) the operand on port R is interpreted using the IEEE floating-point format; in DEC mode (IEEE/ $\overline{\text{DEC}}$  = LOW) it is interpreted using the DEC floating-point format.

The IEEE-to-DEC conversion operation (IEEE-TO-DEC) takes an IEEE-format floating-point number on port R and places the equivalent DEC-format floating-point number on port F. The operand on port S is not used in this operation; its value will not affect the operation in any way. The operation can be performed in either IEEE mode (IEEE/ $\overline{DEC} = HIGH$ ) or DEC mode (IEEE/ $\overline{DEC} = LOW$ ).

The DEC-to-IEEE conversion operation (DEC-TO-IEEE) takes a DEC-format floating-point number on port R and places the equivalent IEEE-format floating-point number on port F. The operand on port S is not used in this operation; its value will ned affect the operation in any way. The operation can be performed in either IEEE mode (IEEE/ $\overline{DEC} = HIGH$ ) or DEC mode (IEEE/ $\overline{DEC} = LOW$ ).

## Status Flag Generator

The status flag generator controls the state of six flags that report the status of floating-point ALU operations. The flags indicate when an operation is invalid (e.g., infinity times zero) or when an operation has produced an overflow, an underflow, a non-numerical result (e.g., a NAN or DEC reserved operand), an inexact result, or a result of zero. The flags represent the status of the most-recently-performed operation. Flag status is stored in the flag status register on the LOW-to-HIGH transition of CLK. When the output register feedthrough control FT<sub>1</sub> is HIGH, the flag status register is made transparent.

#### **Data Path**

The 32-bit data path consists of the R and S input buses, the F output bus, data registers R, S, and F, the register R input multiplexer, and the ALU port S input multiplexer.

Input operands enter the floating-point processor through the 32-bit R and S input buses,  $R_0-R_{31}$  and  $S_0-S_{31}$ . Results of operations appear on the 32-bit F bus,  $F_0-F_{31}$ . The F bus assumes a high-impedance state when output enable  $\overline{\text{OE}}$  is HIGH.

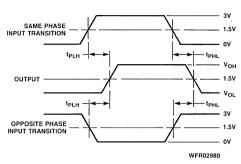

The R and S registers store input operands; the F register stores the final result of the floating-point ALU operation. Each register has an independent clock enable (ENR, ENS and ENF). When a register's clock enable is LOW, the register stores the data on its input at the LOW-to-HIGH transition of CLK; when the clock enable is HIGH, the register retains its current data. All data registers are fully edge-triggered — both the input data and the register enable need only meet modest setup and hold time requirements. Registers R and S can be made transparent by setting FT0, the input register feedthrough control, HIGH. Register F can be made transparent by setting FT1, the output register feedthrough control, HIGH.

The register R input multiplexer selects either the R input bus or the floating-point ALU's F port as the input to register R. Selection is controlled by  $\mathsf{I_4}-\mathsf{a}$  LOW selects the R input bus; a HIGH selects the ALU F port. The ALU port S input multiplexer selects either register S or register F as the input to the floating-point ALU's S port. Selection is controlled by  $\mathsf{I_3}-\mathsf{a}$  LOW selects register S; a HIGH selects register F.

Data selected by  $I_3$  and  $I_4$  is described in the **Mux Select Tables**. When registers R and S are transparent (FT $_0$  = HIGH) multiplexer select  $I_4$  must be kept LOW, so that the register R input multiplexer selects  $R_0-R_{31}$ . When register F is transparent (FT $_1$  = HIGH) multiplexer select  $I_3$  must be kept LOW, so that the ALU port S input multiplexer selects register S.

#### **MUX SELECT TABLES**

| l <sub>3</sub> | Data selected for floating-point ALU S port |

|----------------|---------------------------------------------|

| 0              | Register S                                  |

| 1              | Register F                                  |

| 14 | Data selected for register R input |

|----|------------------------------------|

| 0  | R bus                              |

| 1  | Floating-point ALU port F          |

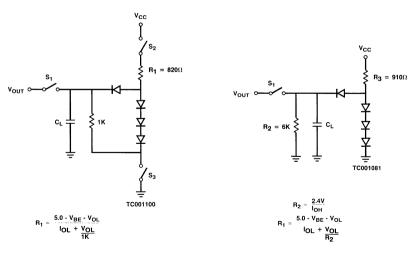

#### I/O MODES

The Am29325 data path can be configured in one of three I/O modes: a 32-bit, two-input-bus mode; a 32-bit, single-input-bus mode; and a 16-bit, two-input-bus mode. These modes affect only the manner in which data is delivered to and taken from the Am29325; operation of the floating-point ALU is not altered. The I/O mode is selected with the ONEBUS and S16/32 controls. The I/O Mode Selection Table lists the control codes needed to invoke each I/O mode.

I/O MODE SELECTION TABLE

| S16/32 | ONEBUS | I/O Mode                         |

|--------|--------|----------------------------------|

| 0      | 0      | 32-bit, two-input-bus mode       |

| 0      | 1      | 32-bit, single-input-bus mode(•) |

| 1      | 0      | 16-bit, two-input-bus mode(*)    |

| 1      | 1      | Illegal I/O mode selection value |

(\*)FT<sub>0</sub> must be held LOW in this mode (see text).

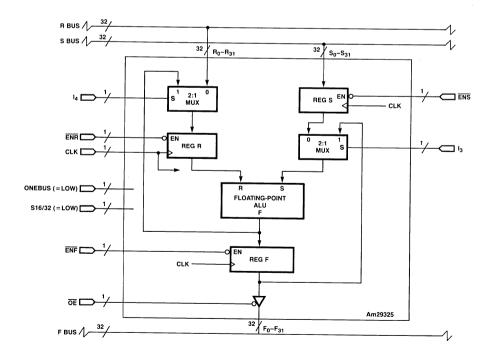

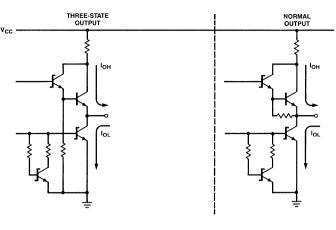

## 32-Bit, Two-Input-Bus Mode

In this I/O mode, the R and S buses are configured as independent 32-bit input buses, and the F bus is configured as a 32-bit output bus. Figure 2 is a functional block diagram of the Am29325 in this I/O mode

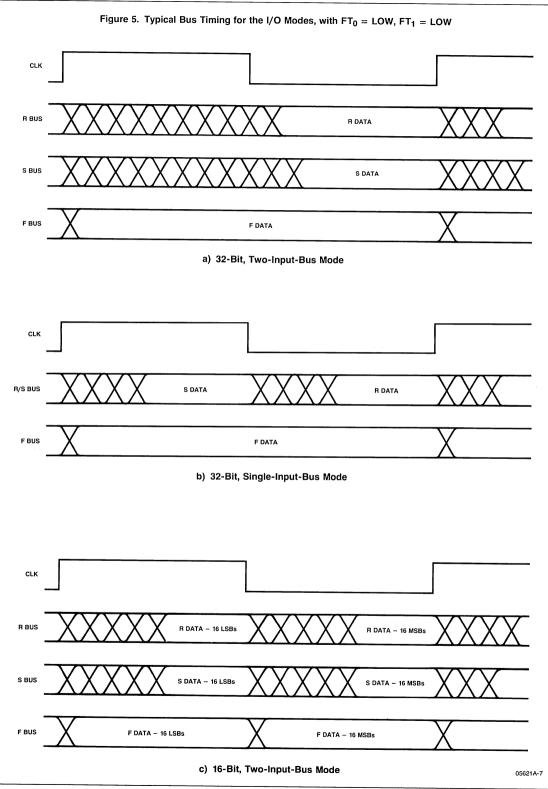

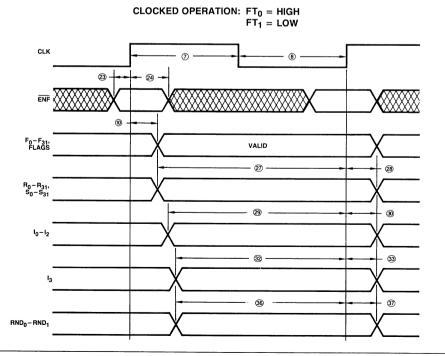

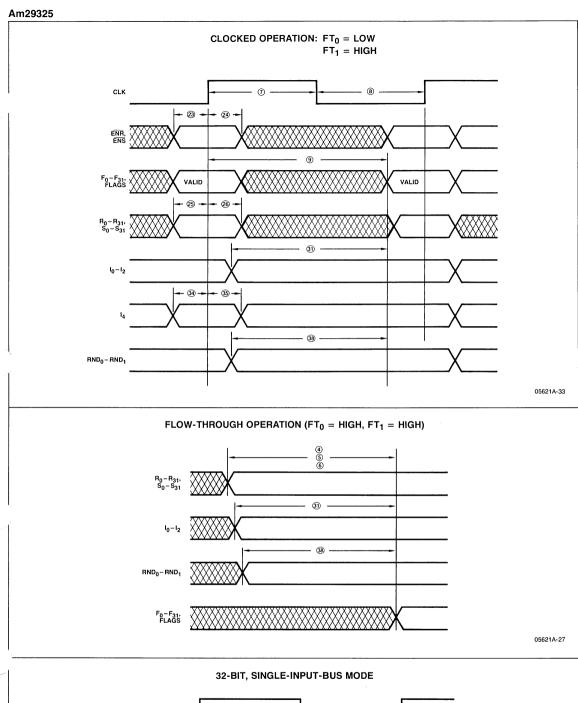

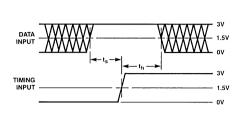

R and S operands are taken from their respective input buses and clocked into the R and S registers on the LOW-to-HIGH transition of CLK. Register F is also clocked on the LOW-to-HIGH transition of CLK. Figure 5(a.) depicts typical I/O timing in this mode.

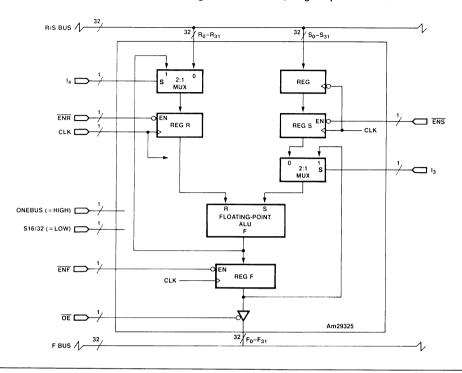

## 32-Bit, Single-Input-Bus Mode

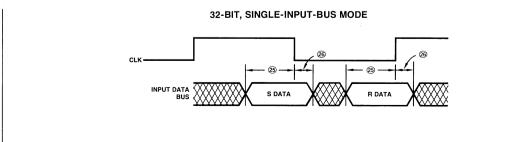

In this I/O mode, the R and S buses are connected to a single 32-bit multiplexed input data bus; the F bus is configured as an independent 32-bit output bus. Figure 3 is a functional block diagram of the Am29325 in this I/O mode. Note that both the R and S bus lines must be wired to the input bus.

R and S operands are multiplexed onto the input bus by the host system. The S operand is clocked from the input bus into a temporary holding register on the HIGH-to-LOW transition of CLK and is transferred to register S on the LOW-to-HIGH transition of CLK. The R operand is clocked from the input bus into register R on the LOW-to-HIGH transition of CLK. Register F is clocked on the LOW-to-HIGH transition of CLK. Figure 5(b.) depicts typical I/O timing in this mode.

When placed in this I/O mode, the data path will not function properly if the R and S registers are made transparent. Therefore input register feedthrough control  $FT_0$  must be held LOW in this mode.

Figure 2. Functional Block Diagram for the 32-Bit, Two-Input-Bus Mode

05621R-4

Figure 3. Functional Block Diagram for the 32-Bit, Single-Input-Bus Mode

05621A-5

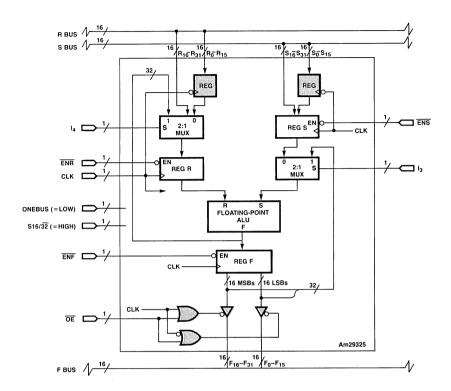

#### 16-Bit, Two-Input-Bus Mode

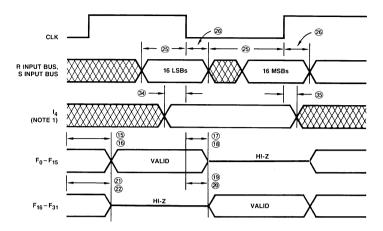

In this I/O mode, the R and S buses are configured as independent 16-bit input buses, and the F bus is configured as a 16-bit output bus. Figure 4 is a functional block diagram of the Am29325 in this I/O mode. Note that the 16 LSBs and 16 MSBs of the R, S and F buses must be wired to their respective system buses in parallel.

Thirty-two-bit operands are passed along the 16-bit data buses by time-multiplexing the 16 LSBs and 16 MSBs of each 32-bit word. For the R input bus, the host system multiplexes the 16 LSBs and 16 MSBs of the R operand onto the 16-bit R bus. The 16 LSBs of the R operand are stored in a temporary holding register on the HIGH-to-LOW transition of CLK. The 16 MSBs are clocked into register R on the LOW-to-HIGH transition of CLK; at the same time, the 16 LSBs are transferred from the temporary holding register to register R. Transfer of data from the S input bus to the S register takes place in a similar fashion. Register F is clocked on the LOW-to-HIGH transition of CLK. Circuitry internal to the Am29325 multiplexes data from register F onto the 16-bit output bus by enabling the 16 LSBs of the F output bus when CLK is HIGH, and enabling the 16 MSBs of the F output bus when CLK is LOW. Figure 5(c.) depicts typical I/O timing in this mode.

When placed in this I/O mode, the data path will not function properly if the R and S registers are made transparent. Therefore input register feedthrough control FT $_0$  must be held LOW in this mode. Caution must also be taken in controlling the register R input multiplexer control line, I $_4$ , in this I/O mode. I $_4$  should be changed only when CLK is HIGH, in addition to meeting the setup and hold time requirements given in the **Switching Characteristics** section.

## **OPERATION IN IEEE MODE**

When input signal IEEE/DEC is HIGH, the IEEE mode of operation is selected. In this mode the Am29325 uses the floating-point format set forth in the IEEE Proposed Standard for Binary Floating-Point Arithmetic, P754. In addition, the IEEE mode complies with most other aspects of single-precision floating-point operation outlined in the proposed standard — differences are discussed in Appendix A.

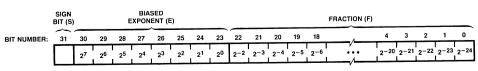

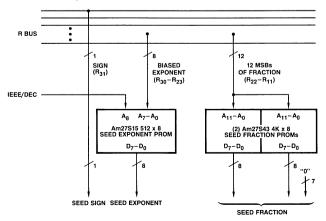

#### **IEEE Floating-Point Format**

The IEEE single-precision floating-point word is thirty-two bits wide, and is arranged in the format shown in Figure 6. The floating-point word is divided into three fields: a single-bit sign, an eight-bit biased exponent, and a 23-bit fraction.

The sign bit indicates the sign of the floating-point number's value. Non-negative values have a sign of 0; negative values, a sign of 1. The value zero may have either sign.

The biased exponent is an eight-bit unsigned integer field representing a multiplicative factor of some power of two. The bias value is 127. If, for example, the multiplicative factor for a floating-point number is to be  $2^a$ , the value of the biased exponent would be a+127; a is called the true exponent.

The fraction is a 23-bit unsigned fractional field containing the 23 least-significant bits of the floating-point number's 24-bit mantissa. The weight of fraction's most significant bit is  $2^{-1}$ ; the weight of the least-significant bit is  $2^{-23}$ .

Figure 4. Functional Block Diagram for the 16-Bit, Two-Input-Bus Mode

05621B-6

A floating-point number is evaluated or interpreted per the following conventions:

let s = sign bit

e = biased exponent

f = fraction

if

$$e = 0$$

and  $f = 0 \dots value = (-1)^{S_*}(0) (+0, -0)$

if

$$0 < e < 255$$

. . value =  $(-1)^{S_*}(2^{e-127})*(1.f)$  (normalized number)

if

$$e = 255$$

and  $f = 0$  ... value  $= (-1)^{S_*}(x)$   $(+x, -x)$

**Zero** – The value zero can have either a positive or negative sign. Rules for determining the sign of a zero produced by an operation are given in the **Sign Bit** section on page 12.

**Denormalized Number** – A denormalized number represents a quantity with magnitude less than  $2^{-126}$  but greater than zero.

**Normalized Number** – A normalized number represents a quantity with magnitude greater than or equal to  $2^{-126}$  but less than  $2^{128}$ .

## Example 1:

The number +3.5 can be represented in floating-point format as follows:

$$+3.5 = 11.1_2 \times 2^0$$

= 1.11<sub>2</sub> x 2<sup>1</sup>

biased exponent =

$$1_{10} + 127_{10} = 128_{10}$$

=  $10000000_2$

Concatenating these fields produces the floating-point word  $40600000_{16}$ .

Figure 6. IEEE Mode Single-Precision Floating-Point Format

05621A-8

#### Example 2:

The number –11.375 can be represented in floating-point format as follows:

$$-11.375 = -1011.011_2 \times 2^0$$

$$= -1.011011_2 \times 2^3$$

sign = 1

biased exponent =

$$3_{10} + 127_{10} = 130_{10}$$

=  $10000010_2$

Concatenating these fields produces the floating-point word C1360000<sub>16</sub>.

**Infinity** – Infinity can have either a positive or negative sign. The way in which infinities are interpreted is determined by the state of the projective/affine mode select, PROJ/ĀFF.

Not-a-Number — A not-a-number, or NAN, does not represent a numeric value, but is interpreted as a signal or symbol. NANs are used to indicate invalid operations, and as a means of passing process status information through a series of calculations. NANs arise in two ways: they can be generated by the Am29325 to indicate that an invalid operation has taken place (e.g., infinity times zero), or they can be provided by the user as an input operand. There are two types of NANs: signalling and quiet. These NANs have the formats shown in Figure 7.

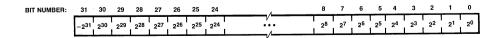

## **IEEE Mode Integer Format**

Integer numbers are represented as 32-bit, two's complement words; Figure 8 depicts the integer format. The integer word can represent a range of integer values from  $-2^{31}$  to  $2^{31}-1$ .

Figure 7. Signalling and Quiet NAN Formats

05621A-9

Figure 8. Thirty-Two-Bit Integer Format

#### **OPERATIONS**

All eight floating-point ALU operations discussed in the Functional Description section above can be performed in IEEE mode. Various exceptional aspects of the R PLUS S, R MINUS S, R TIMES S, 2 MINUS S, INT-TO-FP, and FP-TO-INT operations for this mode are described below. The IEEE-TO-DEC and DEC-TO-IEEE operations are discussed separately in the IEEE-TO-DEC and DEC-TO-IEEE Operations section on page 23.

Operations with NANs — NANs arise in two ways: they can be generated by the Am29325 to indicate that an invalid operation has taken place (e.g., infinity times zero), or they can be provided by the user as an input operand. There are two types of NANs: signalling and quiet. These NANs have the formats shown in Figure 7.

Signalling NANs set the invalid operation flag when they appear as an input operand to an operation. They are useful for indicating uninitialized variables, or for implementing user-designed extensions to the operations provided. The ALU never produces a signalling NAN as the final result of an operation.

Quiet NANs are generated for invalid operations. When they appear as an input operand, they are passed through most operations without setting the invalid flag, the floating-point-to-integer conversion operation being the exception.

The sign of any input operand NAN is ignored. All quiet NANs produced as the final result of an operation have a sign of 0.

When a NAN appears as an input operand, the final result of the operation is a quiet NAN that is created by taking the input NAN and forcing bit 22 LOW and bit 21 HIGH. If an operation has two NANs as input operands, the resulting quiet NAN is created using the NAN on the R port.

When a quiet NAN is produced as the final result of an invalid operation whose input operand or operands are not NANs, the resulting NAN will always have the value  $7FA00000_{16}$ .

The NAN flag will be HIGH whenever an operation produces a NAN as a final result.

#### Example 1:

Suppose the floating-point addition operation is performed with the following input operands:

R port: 3F800000<sub>16</sub> (1.0\*2<sup>0</sup>)

S port: 7FC12345<sub>16</sub> (signalling NAN)

Result: The signalling NAN on the S port is converted to a quiet NAN by forcing bit 22 LOW and bit 21 HIGH. The operation's final result will be 7FA12345<sub>16</sub>. Since one of the two input operands is a signalling NAN, the invalid flag will be HIGH; the NAN flag will also be HIGH.

Example 2

Suppose the floating-point multiplication operation is performed with the following input operands:

R port: FFF11111<sub>16</sub> (signalling NAN) S port: 7FC22222<sub>16</sub> (quiet NAN)

Result: Since both input operands are NANs, the NAN on the R port is chosen for output. In addition to forcing bit 22 LOW, the sign bit (bit 31) is set LOW (bit 21 is already HIGH, and need not be changed). The operation's final result will be 7FB11111<sub>16</sub>. Since one of the two input operands is a signalling NAN, the invalid flag is HIGH; the NAN flag will also be HIGH.

Example 3:

Suppose the floating-point subtraction operation is performed with the following input operands:

R port: FF800001<sub>16</sub> (quiet NAN)

S port:  $7F800000_{16} (+\infty)$

Result: To create the final result, the quiet NANs sign bit (bit 31) is forced LOW and bit 21 is forced HIGH (bit 22 is already LOW, and need not be changed). The final result will be 7FA00001<sub>16</sub>. The NAN flag will be HIGH.

Operations with Denormalized Numbers — The proposed IEEE standard incorporates denormalized numbers to allow a means of gradual underflow for operations that produce non-zero results too small to be expressed as a normalized floating-point number. The Am29325 does not support gradual underflow. If a floating-point operation produces a non-zero rounded result that is not large enough to be expressed as a normalized floating-point number, the final result will be a zero of the same sign; the inexact, underflow, and zero flags will be HIGH. If an input operand is a denormalized number, the floating-point ALU will assume that operand to be a zero of the same sign.

**Operations Producing Overflows** – If an operation has a finite input operand or operands, and if the operation produces a rounded result that is too large to fit in the destination format, that operation is said to have overflowed.

A floating-point overflow occurs if an R PLUS S, R MINUS S, R TIMES S, or 2 MINUS S operation with finite input operand(s) produces a result which, after rounding, has a magnitude greater than or equal to 2<sup>128</sup>. Positive or negative infinity will appear as the final result if the rounded result is positive or negative, respectively, and the overflow and inexact flags will be HIGH.

Integer overflow occurs when the floating-point-to-integer conversion operation attempts to convert a number which, after rounding, is greater than  $2^{31}-1$  or less than  $-2^{31}$ . The final result will be quiet NAN 7FA00000<sub>16</sub>, and the invalid operation and NAN flags will be HIGH. Note that the overflow and inexact flags remain LOW for integer overflow.

Operations Producing Underflows — If an operation produces a floating-point rounded result having a magnitude too small to be expressed as a normalized floating-point number, but greater than zero, that operation is said to have underflowed. Underflow occurs when an R PLUS S, R MINUS S, or R TIMES S operation produces a result which, after rounding, has a magnitude in the range:

$0 < magnitude < 2^{-126}$ .

In such cases, the final result will be  $\pm 0~(0000000_{16})$  if the rounded result is non-negative, and  $\pm 0~(8000000_{16})$  if the rounded result is negative. The underflow, inexact, and zero flags will be HIGH.

Underflow does not occur if the destination format is integer. If the infinitely precise result of a floating-point-to-integer conversion has a magnitude greater than 0 and less than 1 but the rounded result is 0, the underflow flag remains LOW.

Operations with Infinities — In most cases, positive and negative infinity are valid input arguments for the R PLUS S, R MINUS S, R TIMES S, and 2 MINUS S operations. Those cases for which infinities are not valid inputs for these operations are listed in the IEEE Mode Invalid Operations Table (see next page).

Infinities in IEEE mode can be handled either as projective or affine. The projective mode is selected when PROJ/AFF is HIGH;

the affine mode is selected when PROJ/AFF is LOW. The only differences between the modes that are relevant to Am29325 operation occur during the addition and subtraction of infinities:

| Operation | Affine<br>Mode | Projective Mode                                                      |

|-----------|----------------|----------------------------------------------------------------------|

| (+∞)+(+∞) | Output +∞      | Output 7FA00000 <sub>16</sub> (quiet NAN), set invalid and NAN flags |

| (-∞)+(-∞) | Output -∞      | Output 7FA00000 <sub>16</sub> (quiet NAN), set invalid and NAN flags |

| (+∞)-(-∞) | Output +∞      | Output 7FA00000 <sub>16</sub> (quiet NAN), set invalid and NAN flags |

| (-∞)-(+∞) | Output –∞      | Output 7FA00000 <sub>16</sub> (quiet NAN), set invalid and NAN flags |

If an R PLUS S, R MINUS S, R TIMES S, or 2 MINUS S operation has infinity as an input operand or operands, the final result, if valid, is presumed to be exact. For example, adding  $+\infty$  and 2.0 will produce a final result of  $+\infty$ ; since the result is considered exact, the inexact flag remains LOW.

Invalid Operations — If an input operand is invalid for the operation to be performed, that operation is considered invalid. When an invalid operation is performed, the floating-point ALU produces a quiet NAN as the final result, and the invalid operation flag goes HIGH. The IEEE Mode Invalid Operations Table lists the cases for which the invalid flag is HIGH in IEEE mode, and the final results produced for these operations.

## IEEE MODE INVALID OPERATIONS TABLE

| Operation                          | Input Operand                                                     | Final Result                          |

|------------------------------------|-------------------------------------------------------------------|---------------------------------------|

| R PLUS S                           | or $(-\infty)$ + $(+\infty)$                                      | 7FA00000 <sub>16</sub><br>(quiet NAN) |

| R PLUS S                           | $(+\infty) + (+\infty)$<br>or $(-\infty) + (-\infty)$ (Note 1)    | 7FA00000 <sub>16</sub><br>(quiet NAN) |

| R MINUS S                          | $(+\infty) - (+\infty)$<br>or $(-\infty) - (-\infty)$             | 7FA00000 <sub>16</sub><br>(quiet NAN) |

| R MINUS S                          | $(+\infty) - (-\infty)$<br>or $(-\infty) - (+\infty)$ (Note 1)    | 7FA00000 <sub>16</sub><br>(quiet NAN) |

| R TIMES S                          | (+0) • (+∞)<br>or (+0) • (-∞)<br>or (-0) • (+∞)<br>or (-0) • (-∞) | 7FA00000 <sub>16</sub><br>(quiet NAN) |

| R PLUS S<br>R MINUS S<br>R TIMES S | R or S is a signalling NAN                                        | (Note 2)                              |

| 2 MINUS S                          | S is a signalling NAN                                             | (Note 2)                              |

| FP-TO-INT                          | R is a signalling or quiet NAN                                    | (Note 2)                              |

| FP-TO-INT                          | $R > 2^{31} - 1$ or $R < - (2^{31})$                              | 7FA00000 <sub>16</sub><br>(quiet NAN) |

Notes: 1. These cases are invalid in projective mode only.

Results for these operations are described in the Operations with NANs section.

#### The Sign Bit

For most floating-point operations, the sign bit of the final result is unambiguous, i.e., there is only one sign bit value that yields a numerically correct result. Operations that produce an infinitely

precise result of zero, however, present a problem, as the IEEE floating-point format allows for representation of both +0 and -0. The following rules can be used to determine the signs of zero produced in such cases:

**R PLUS S** – The operations +x + (-x) and -x + (+x) produce a final result of zero; the sign of the zero is dependent on the rounding mode:

| Rounding Mode    | Sign of Final Result |

|------------------|----------------------|

| Round to nearest | 0                    |

| Round toward -∞  | 1                    |

| Round toward +∞  | 0                    |

| Round toward 0   | 0                    |

The operation +0 + (+0) produces a final result of +0; the operation -0 + (-0) produces a final result of -0.

**R MINUS S** – The operations +x - (+x) and -x - (-x) produce a final result of zero; the sign of the zero is dependent on the rounding mode:

| Rounding Mode    | Sign of Result |  |

|------------------|----------------|--|

| Round to nearest | 0              |  |

| Round toward -∞  | 1              |  |

| Round toward +∞  | 0              |  |

| Round toward 0   | 0              |  |

The operation +0 – (-0) produces a final result of +0; the operation -0 – (+0) produces a final result of -0.

R TIMES S — The sign of any multiplication result other than a NAN is the exclusive-OR of the signs of the input operands. Therefore, if x is non-negative,

+0 times +x produces a final result of +0,

+0 times -x produces a final result of -0,

-0 times +x produces a final result of -0, -0 times -x produces a final result of +0.

2 MINUS S – If S equals 2, the final result is -0 for the round toward  $-\infty$  mode, and +0 for all other rounding modes.

#### Rounding

Rounding is performed whenever an operation produces an infinitely precise result that cannot be represented exactly in the destination format. For example, suppose a floating-point operation produces the infinitely precise result

1.10101010101010101010101\01 x 23.

In this example, the fraction portion of the mantissa has twenty-five bits; the IEEE floating-point format can accommodate only twenty-three. The backslash (\) in the mantissa represents the boundary between the first twenty-three bits of the fraction and any remaining bits. Rounding is the process by which this result is approximated by a representation that fits the destination format.

There are four rounding modes in IEEE mode: round to nearest, round toward  $+\infty$ , round toward  $-\infty$ , and round toward 0. The rounding mode is chosen using the rounding mode select lines, RND<sub>0</sub> and RND<sub>1</sub>. **The Rounding Mode Select Table** lists the select states needed to obtain the desired rounding mode.

#### **ROUNDING MODE SELECT TABLE**

| RND <sub>1</sub> | RND <sub>0</sub> | Rounding Mode    |

|------------------|------------------|------------------|

| 0                | 0                | Round to nearest |

| 0                | 1                | Round toward -∞  |

| 1                | 0                | Round toward +∞  |

| 1                | 1                | Round toward 0   |

Round to Nearest — In this rounding mode the infinitely precise result of an operation is rounded to the closest representation that fits in the destination format. If the infinitely precise result is exactly halfway between two representations, it is rounded to the representation having an LSB of zero. Rounding is performed both for floating-point and integer destination formats.

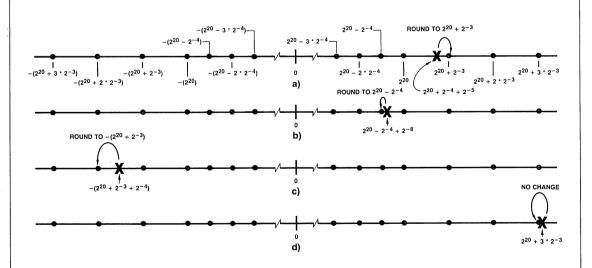

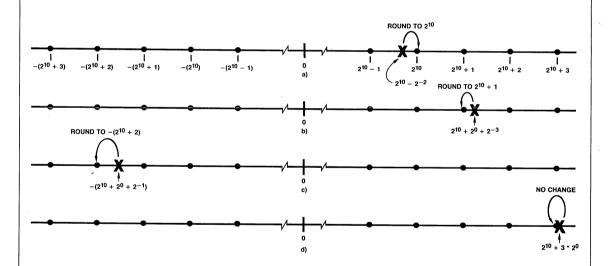

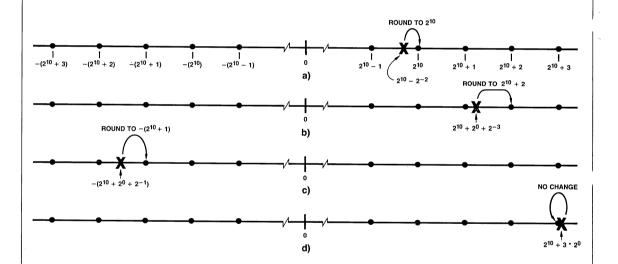

Figure 9 illustrates four examples of the round to nearest process for operations having a floating-point destination format. The infinitely precise result of an operation is represented by an X on the number line; the black dots on the number line indicate those values that can be represented exactly in the floating-point format

#### Example 1:

In Figure 9(a), the infinitely precise result of an operation is:  $2^{20}+2^{-4}+2^{-5}=1.00000000000000000000011 \times 2^{20}$ .

The result is rounded to the closest representable floating-point value.

#### Example 2:

This result is rounded to the closest representable floating-point value,

## Example 3:

In Figure 9(c), the infinitely precise result of an operation is:

$$-(2^{20}+2^{-3}+2^{-4})$$

= -1.000000000000000000001\1 x 2<sup>20</sup>.

This result is exactly halfway between two representable floating-point values. Accordingly, it is rounded to the closest representation with an LSB of zero, or

## Example 4:

In Figure 9(d), the infinitely precise result of an operation is:  $2^{20}+3\cdot2^{-3}=1.0000000000000000011 \times 2^{20}$ .

This result can be represented exactly in the floating-point format, and is left unaltered by the rounding process.

Figure 9. Floating-Point Rounding Examples for Round to Nearest Mode

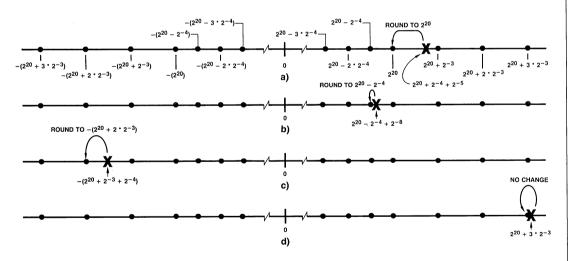

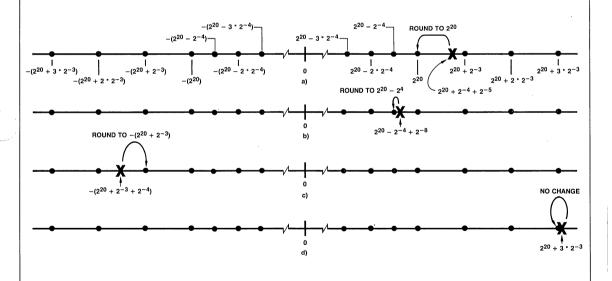

Figure 10 illustrates four examples of the round to nearest process for operations having an integer destination format. The infinitely precise result of an operation is represented by an X on the number line; the black dots on the number line indicate those values that can be represented exactly in the integer format.

#### Example 1:

In Figure 10(a), the infinitely precise result of an operation is:  $2^{10}-2^{-2}=00...0011111111111.11$ .

The result is rounded to the closest representable integer value,  $2^{10} = 00...0100000000000$ .

#### Example 2:

In Figure 10(b), the infinitely precise result of an operation is:  $2^{10}+2^{0}+2^{-3}=00...01000000001.001$ .

This result is rounded to the closest representable integer value,

$2^{10} + 2^{0} = 00...010000000001.$

#### Example 3:

In Figure 10(c), the infinitely precise result of an operation is:  $-(2^{10}+2^{0}+2^{-1}) = 11...1011111111110.1.$

This result is exactly halfway between two representable integer values. Accordingly, it is rounded to the closest representation with an LSB of zero, or

$$-(2^{10}+2*2^0) = 11...1011111111110.$$

#### Example 4:

In Figure 10(d), the infinitely precise result of an operation is:  $2^{10}+3\star2^0=00...010000000011$ .

This result can be represented exactly in the integer format, and is left unaltered by the rounding process.

Figure 10. Integer Rounding Examples for Round to Nearest Mode

**Round Toward**  $-\infty$  — In this rounding mode the result of an operation is rounded to the closest representation that is less than or equal to the infinitely precise result, and which fits the destination format. Rounding is performed both for floating-point and integer destination formats.

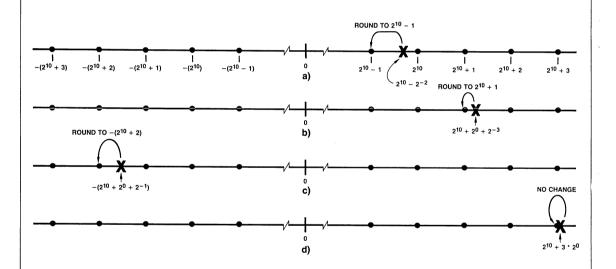

Figure 11 illustrates four examples of the round toward  $-\infty$  process for operations having a floating-point destination format. The infinitely precise result of an operation is represented by an X on the number line; the black dots on the number line indicate those values that can be represented exactly in the floating-point format.

#### Example 1:

In Figure 11(a), the infinitely precise result of an operation is:  $2^{20}+2^{-4}+2^{-5} = 1.00000000000000000000011 \times 2^{20}$ .

This result cannot be represented exactly in floating-point format, and is rounded to the next-smaller floating-point representation:

#### Example 2:

This result cannot be represented exactly in floating-point format, and is rounded to the next-smaller floating-point representation:

#### Example 3:

In Figure 11(c), the infinitely precise result of an operation is:

$$-(2^{20}+2^{-3}+2^{-4})$$

= -1.000000000000000000001\1 x 2<sup>20</sup>.

This result cannot be represented exactly in floating-point format, and is rounded to the next-smaller floating-point representation:

## Example 4:

In Figure 11(d), the infinitely precise result of an operation is:  $2^{20}+3*2^{-3}=1.00000000000000000011 \times 2^{20}$ .

This result can be represented exactly in the floating-point format, and is left unaltered by the rounding process.

Figure 11. Floating-Point Rounding Examples for Round Toward − ∞ Mode

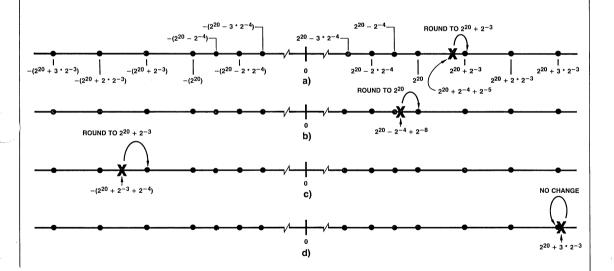

Figure 12 illustrates four examples of the round toward  $-\infty$  process for operations having an integer destination format. The infinitely precise result of an operation is represented by an X on the number line; the black dots on the number line indicate those values that can be exactly represented in the integer format.

#### Example 1:

In Figure 12(a), the infinitely precise result of an operation is:  $2^{10}-2^{-2}=00...00111111111111.11$ .

The result is rounded to the next-smaller representable integer value.

$2^{10}-2^0 = 00...0011111111111.$

## Example 2:

In Figure 12(b), the infinitely precise result of an operation is:  $2^{10}+2^{0}+2^{-3}=00...01000000001.001$ .

This result is rounded to the next-smaller representable integer value,

$2^{10} + 2^0 = 00...010000000001.$

## Example 3:

In Figure 12(c), the infinitely precise result of an operation is:

This result is rounded to the next-smaller representable integer value:

$-(2^{10}+2*2^0) = 11...1011111111110.$

#### Example 4:

In Figure 12(d), the infinitely precise result of an operation is:  $2^{10}+3*2^0=00...010000000011$ .

This result can be represented exactly in the integer format, and is unaltered by the rounding process.

Figure 12. Integer Rounding Examples for Round Toward  $-\infty$  Mode

**Round Toward**  $+\infty$  — In this rounding mode the result of an operation is rounded to the closest representation that is greater than or equal to the infinitely precise result, and which fits the destination format. Rounding is performed both for floating-point and integer destination formats.

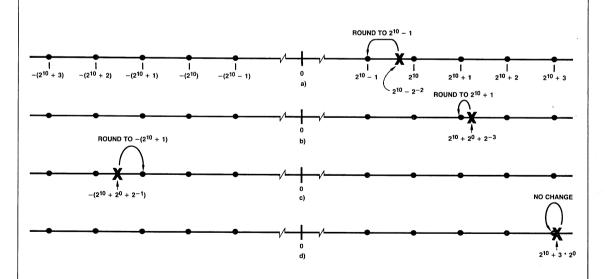

Figure 13 illustrates four examples of the round toward  $+\infty$  process for operations having a floating-point destination format. The infinitely precise result of an operation is represented by an X on the number line; the black dots on the number line indicate those values that can be represented exactly in the floating-point format.

#### Example 1:

In Figure 13(a), the infinitely precise result of an operation is:  $2^{20}+2^{-4}+2^{-5} = 1.000000000000000000000000011 \times 2^{20}$ .

This result cannot be represented exactly in floating-point format, and is rounded to the next-larger floating-point representation:

$$2^{20}+2^{-3} = 1.0000000000000000000001 \times 2^{20}$$

.

#### Example 2:

This result cannot be represented exactly in floating-point format, and is rounded to the next-larger floating-point representation:

#### Example 3:

In Figure 13(c), the infinitely precise result of an operation is:

$$-(220+2-3+2-4)$$

= -1.000000000000000000001\1 x 2<sup>20</sup>.

This result cannot be represented exactly in floating-point format, and is rounded to the next-larger floating-point representation:

#### Example 4:

In Figure 13(d), the infinitely precise result of an operation is:  $2^{20}+3\cdot2^{-3}=1.0000000000000000011 \times 2^{20}$ .

This result can be represented exactly in the floating-point format - no rounding takes place.

Figure 13. Floating-Point Rounding Examples for Round Toward  $+\infty$  Mode

Figure 14 illustrates four examples of the round toward  $+\infty$  process for operations having an integer destination format. The infinitely precise result of an operation is represented by an X on the number line; the black dots on the number line indicate those values that can be exactly represented in the integer format.

#### Example 1:

In Figure 14(a), the infinitely precise result of an operation is:  $2^{10}-2^{-2}=00...0011111111111.11$ .

The result is rounded to the next-larger representable integer value,

$2^{10} = 00...010000000000$ .

#### Example 2:

In Figure 14(b), the infinitely precise result of an operation is:  $2^{10}+2^{0}+2^{-3}=00...01000000001.001$ .

This result is rounded to the next-larger representable integer value,

$2^{10} + 2 * 2^0 = 00...010000000010.$

#### Example 3:

In Figure 14(c), the infinitely precise result of an operation is: -(210+20+2-1) = 11...101111111111.1

This result is rounded to the next-larger representable integer value:

$-(2^{10}+2^0) = 11...10111111111110.$

## Example 4:

In Figure 14(d), the infinitely precise result of an operation is:  $2^{10}+3*2^0=00...01000000011$ .

This result can be represented exactly in the integer format - no rounding takes place.

Figure 14. Integer Rounding Examples for Round Toward  $+\infty$  Mode

Round Toward 0 — In this rounding mode the result of an operation is rounded to the closest representation whose magnitude is less than or equal to the infinitely precise result, and which fits the destination format. Rounding is performed both for floating point and integer destination formats

floating-point and integer destination formats.

Figure 15 illustrates four examples of the round toward 0 process for operations having a floating-point destination format. The infinitely precise result of an operation is represented by an X on the number line; the black dots on the number line indicate those values that can be represented exactly in the floating-point format.

## Example 1:

Example 2:

This result cannot be represented exactly in floating-point format, and is rounded to:

Example 3:

In Figure 15(c), the infinitely precise result of an operation is:

$$-(220+2-3+2-4)$$

= -1.0000000000000000000001\1 x 2<sup>20</sup>.

This result cannot be represented exactly in floating-point format, and is rounded to:

$$-(2^{20}+2^{-3}) = -1.0000000000000000000001 \times 2^{20}.$$

Example 4:

In Figure 15(d), the infinitely precise result of an operation is:  $2^{20}+3*2^{-3}=1.0000000000000000011 \times 2^{20}$ .

This result can be represented exactly in the floating-point format, and is unaffected by the rounding process.

Figure 15. Floating-Point Rounding Examples for Round Toward 0 Mode

Figure 16 illustrates four examples of the round toward 0 process for operations having an integer destination format. The infinitely precise result of an operation is represented by an X on the number line; the black dots on the number line indicate those values that can be exactly represented in the integer format.

#### Example 1:

In Figure 16(a), the infinitely precise result of an operation is:  $2^{10}-2^{-2}=00...00111111111111.11$ .

The result is rounded to:

$2^{10}-2^{0} = 00...0011111111111.$

#### Example 2:

In Figure 16(b), the infinitely precise result of an operation is:  $2^{10}+2^{0}+2^{-3}=00...01000000001.001$ .

The result is rounded to:

$2^{10} + 2^0 = 00...010000000001.$

#### Example 3:

In Figure 16(c), the infinitely precise result of an operation is:  $-(2^{10}+2^{0}+2^{-1}) = 11...1011111111110.1$ .

This result is rounded to:

$-(2^{10}+2^0) = 11...1011111111111.$

#### Example 4:

In Figure 16(d), the infinitely precise result of an operation is:  $2^{10}+3*2^{0}=00...010000000011$ .

This result can be represented exactly in the integer format, and is unaffected by the rounding process.

## Flag Operation

The Am29325 generates six status flags to monitor floating-point processor operation. The following is a summary of flag conventions in IEEE mode:

Invalid Operation Flag – The invalid operation flag is HIGH when an input operand is invalid for the operation to be performed. The IEEE Mode Invalid Operations Table lists the cases for which the invalid operation flag is HIGH in IEEE mode, and the corresponding final result. In cases where the invalid operation flag is HIGH, the overflow, underflow, zero, and inexact flags are LOW; the NAN flag will be HIGH.

**Overflow Flag** — The overflow flag is HIGH if an R PLUS S, R MINUS S, R TIMES S, or 2 MINUS S operation with finite input operand(s) produces a result which, after rounding, has a magnitude greater than or equal to  $2^{128}$ . The final result will be  $+\infty$  or  $-\infty$ .

**Underflow Flag** – The underflow flag is HIGH if an R PLUS S, R MINUS S, or R TIMES S operation produces a result which, after rounding, has a magnitude in the range:

$$0 < \text{magnitude} < 2^{-126}$$

.

The final result will be +0 (00000000<sub>16</sub>) if the rounded result is non-negative, and -0 (80000000<sub>16</sub>) if the rounded result is negative.

Inexact Flag — The inexact flag is HIGH if the final result of an R PLUS S, R MINUS S, R TIMES S, 2 MINUS S, INT-TO-FP, or FP-TO-INT operation is not equal to the infinitely precise result. Note that if the underflow or overflow flag is HIGH, the inexact flag will also be HIGH.

**Zero Flag** – The zero flag is HIGH if the final result of an operation is zero. For operations producing an IEEE floating-point number, the flag accompanies outputs  $+0~(00000001_{16})$  and  $-0~(800000001_{16})$ . For operations producing an integer, the flag accompanies the output  $0~(000000001_{16})$ .

NAN Flag — The NAN flag is HIGH if an R PLUS S, R MINUS S, R TIMES S, 2 MINUS S, or FP-TO-INT operation produces a NAN as a final result.

#### **OPERATION IN DEC MODE**

When input signal IEEE/DEC is LOW, the DEC mode of operation is selected. In this mode the Am29325 uses the single-precision floating-point format (floating F) set forth in Digital Equipment Corporation's VAX Architecture Manual. In addition, the DEC mode complies with most other aspects of single-precision floating-point operation outlined in the manual — differences are discussed in Appendix B.

#### **DEC Floating-Point Format**

The DEC single-precision floating-point word is thirty-two bits wide, and is arranged in the format shown in Figure 17. The floating-point word is divided into three fields: a single-bit sign, an eight-bit biased exponent, and a 23-bit fraction.

The sign bit indicates the sign of the floating-point number's value. Non-negative values have a sign of 0, negative values a sign of 1.