## Am29331

16-Bit Microprogram Sequencer

#### **PRELIMINARY**

#### DISTINCTIVE CHARACTERISTICS

## • 16-Bits Address up to 64K Words Supports 80-90 ns microcycle time for a 32-bit high-

performance system when used with the other members of the Am29300 Family.

## Real-Time Interrupt Support Missa tran and interrupts are be

Micro-trap and interrupts are handled transparently at any microinstruction boundary.

#### Built-In Conditional Test Logic

Generates a full set of branch conditions from four ALU status bits. Has eight external test inputs plus a polarity input. Test multiplexer selects one out of 16 test inputs.

#### Break-Point Logic

Built-in address comparator allows break-points in the microcode for debugging and statistics collection.

#### Master/Slave Error Checking

Two sequencers can operate in parallel as a master and a slave. The slave generates a fault flag for unequal results.

#### • 33-Level Stack

Provides support for interrupts, loops, and subroutine nesting. It can be accessed through the D-bus to support diagnostics.

#### **GENERAL DESCRIPTION**

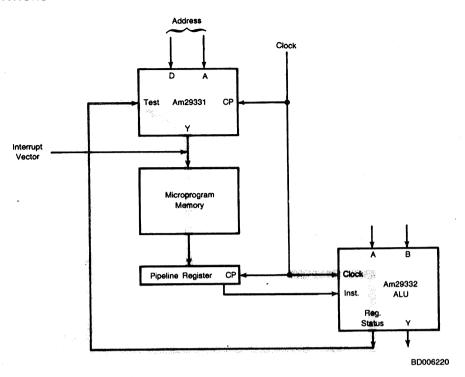

The Am29331 is a 16-bit wide, high-speed single-chip sequencer designed to control the execution sequence of microinstructions stored in the microprogram memory. The instruction set is designed to resemble high-level language constructs, thereby bringing high-level language programming to the micro level.

The Am29331 is interruptible at any microinstruction boundary to support real-time interrupts. Interrupts are handled transparently to the microprogrammer as an unexpected procedure call. Traps are also handled transparently at any microinstruction boundary. This feature allows researcution of the prior microinstruction. Two separate buses are provided to bring a branch address directly into the chip from two sources to avoid slow turn-on and turn-off times

for different sources connected to the data-input bus. Four sets of multiway inputs are also provided to avoid slow turnon and turn-off times for different branch-address sources. This feature allows implementation of table look-up or use of external conditions as part of a branch address. The thirty-three-deep stack provides the ability to support interrupts, loops, and subroutine nesting. The stack can be read through the D-bus to support diagnostics or to implement multitasking at the micro-architecture level. The master/ slave mode provides a complete function check capability for the device.

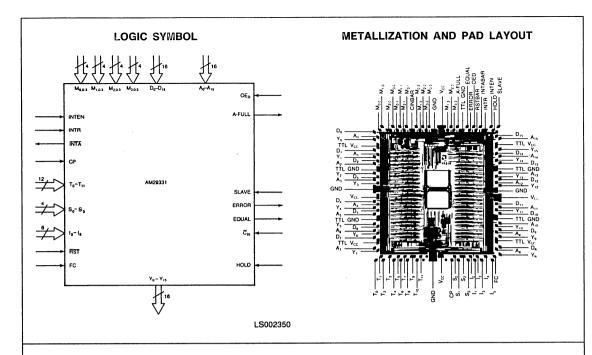

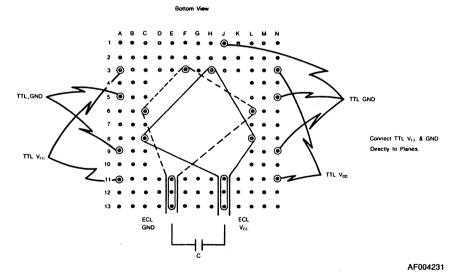

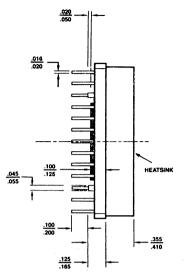

The Am29331 is designed with the IMOX<sup>TM</sup> process which allows internal ECL circuits with TTL-compatible I/O. It is housed in a 120-lead pin-grid-array package.

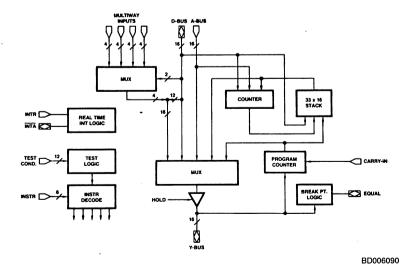

#### SIMPLIFIED BLOCK DIAGRAM

Publication # Rev. Amendment C /0 /0 |

Issue Date: April 1986

## **RELATED PRODUCTS**

| Part No. | Description                                  |

|----------|----------------------------------------------|

| Am29323  | 32 x 32 Parallel Multiplier                  |

| Am29325  | 32-Bit Floating Point Processor              |

| Am29332  | 32-Bit Extended-Function ALU                 |

| Am29334  | 64 x 18 Four-Port, Dual-Access Register File |

BD006101

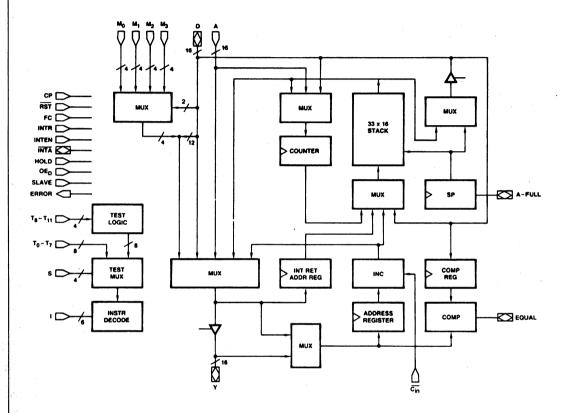

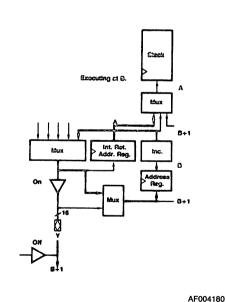

Figure 1. Am29331 Detailed Block Diagram

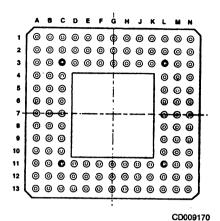

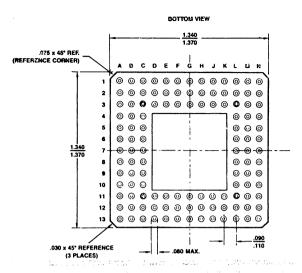

# CONNECTION DIAGRAM 120-Lead PGA\*

\*Pinout observed from pin side of package.

## PIN DESIGNATIONS (Sorted by Pin No.)

| PIN NO.    | PIN NAME          | PAD<br>NO. | PIN<br>NO. | PIN NAME                          | PAD<br>NO. | PIN<br>NO. | PIN NAME            | PAD<br>NO. | PIN<br>NO. | PIN NAME            | PAD<br>NO. |

|------------|-------------------|------------|------------|-----------------------------------|------------|------------|---------------------|------------|------------|---------------------|------------|

| -          | -                 | 99         | C-5        | Y <sub>2</sub>                    | 115        | H-2        | Мз, з               | 10         | M-5        | A <sub>13</sub>     | 80         |

| -          | -                 | 97         | C-6        | ECL GND                           | 113        | H-3        | ECL VCC             | 68         | M-6        | D <sub>12</sub>     | 81         |

| -          | -                 | 39         | C-7        | A <sub>4</sub>                    | 52         | H-11       | lo                  | 34         | M-7        | Y <sub>12</sub>     | 82         |

| 1 -        |                   | 37         | C-8        | ECL V <sub>CC</sub>               | 53         | H-12       | S <sub>1</sub>      | 95         | M-8        | Y11                 | 25         |

| A-1        | Mo, o             | 1          | C-9        | Y <sub>5</sub>                    | 109        | H-13       | S <sub>3</sub>      | 94         | M-9        | A <sub>10</sub>     | 86         |

| A-2        | D <sub>0</sub>    | 120        | C-10       | Y <sub>6</sub>                    | 48         | J-1        | TTL GND             | 11         | M-10       | D <sub>9</sub>      | 87         |

| A-3        | TTL VCC           | 59         | C-11       | Тз                                | 44         | J-2        | EQUAL               | 71         | M-11       | D <sub>8</sub>      | 89         |

| A-4        | A <sub>1</sub>    | 58         | C-12       | T <sub>2</sub>                    | 104        | J-3        | A-FULL              | 70         | M-12       | A <sub>8</sub>      | 30         |

| A-5        | TTL GND           | 56         | C-13       | T <sub>9</sub>                    | 41         | J-11       | ECL V <sub>CC</sub> | 38         | M-13       | 15                  | 91         |

| A-6        | Аз                | 114        | D-1        | M <sub>2, 1</sub>                 | 4          | J-12       | ECL VCC             | 38         | N-1        | D <sub>15</sub>     | 16         |

| A-7        | Yз                | 54         | D-2        | M1. 1                             | 63         | J-13       | ECL VCC             | 38         | N-2        | A <sub>15</sub>     | 76         |

| A-8        | D <sub>5</sub>    | 51         | D-3        | M <sub>0, 1</sub>                 | 3          | K-1        | RST                 | 13         | N-3        | TTL VCC             | 17         |

| A-9        | TTL GND           | 50         | D-11       | T <sub>6</sub>                    | 102        | K-2        | OED                 | 72         | N-4        | Y <sub>14</sub>     | 19         |

| A-10       | D <sub>6</sub>    | 49         | D-12       | T <sub>5</sub>                    | 43         | K-3        | ERROR               | 12         | N-5        | TTL GND             | 20         |

| A-11       | TTĽ VCC           | 47         | D-13       | T <sub>4</sub><br>C <sub>in</sub> | 103        | K-11       | l <sub>3</sub>      | 92         | N-6        | Y <sub>13</sub>     | 21         |

| A-12       | A <sub>7</sub>    | 106        | E-1        | C <sub>in</sub>                   | 5          | K-12       | l <sub>2</sub>      | 33         | N-7        | D <sub>11</sub>     | 24         |

| A-13       | Y <sub>7</sub>    | 46         | E-2        | M <sub>0, 2</sub>                 | 65         | K-13       | 11                  | 93         | N-8        | A <sub>11</sub>     | 84         |

| B-1        | M <sub>1, 0</sub> | 61         | E-3        | M <sub>3, 1</sub>                 | 64         | L-1        | INTR                | 14         | N-9        | TTL GND             | 26         |

| B-2        | A <sub>0</sub>    | 60         | E-11       | ECL GND                           | 98         | L-2        | INTEN               | 74         | N-10       | A <sub>9</sub>      | 28         |

| B-3        | Y <sub>0</sub>    | 119        | E-12       | ECL GND                           | 98         | L-3        | INTA                | 73         | N-11       | TTL V <sub>CC</sub> | 29         |

| B-4        | Y <sub>1</sub>    | 117        | E-13       | ECL GND                           | 98         | L-4        | D <sub>14</sub>     | 18         | N-12       | Y <sub>8</sub>      | 90         |

| B-5        | A <sub>2</sub>    | 116        | F-1        | M <sub>1, 2</sub>                 | 6          | L-5        | D <sub>13</sub>     | 79         | N-13       | FČ                  | 31         |

| B-6        | D <sub>3</sub>    | 55         | F-2        | M <sub>2, 2</sub>                 | 66         | L-6        | ECL GND             | 23         |            | 1                   |            |

| B-7        | D <sub>4</sub>    | 112        | F-3        | ECL GND                           | 8          | L-7        | A <sub>12</sub>     | 22         |            |                     |            |

| B-8        | Y4                | 111        | F-11       | T <sub>10</sub>                   | 100        | L-8        | ECL V <sub>CC</sub> | 83         |            |                     |            |

| B-9        | A <sub>5</sub>    | 110        | F-12       | T <sub>7</sub>                    | 42         | L-9        | D <sub>10</sub>     | 85         |            |                     | 1          |

| B-10       | A <sub>6</sub>    | 108        | F-13       | T <sub>8</sub>                    | 101        | L-10       | Y <sub>10</sub>     | 27         |            |                     | İ          |

| B-11       | <u>D</u> 7        | 107        | G-1        | М1, з                             | 9          | L-11       | Y <sub>9</sub>      | 88         |            |                     |            |

| B-12       | <u>T</u> 1        | 45         | G-2        | Мо, з                             | 67         | L-12       | 14                  | 32         |            |                     |            |

| B-13       | T <sub>0</sub>    | 105        | G-3        | M <sub>3, 2</sub>                 | 7          | L-13       | S <sub>2</sub>      | 35         |            |                     |            |

| C-1        | M <sub>2, 0</sub> | 2          | G-11       | T <sub>11</sub>                   | 40         | M-1        | SLAVE               | 75         |            |                     |            |

| C-2        | M3, 0             | 62         | G-12       | S <sub>0</sub>                    | 36         | M-2        | HOLD                | 15         |            |                     |            |

| C-3<br>C-4 | D <sub>1</sub>    | 118        | G-13       | CP                                | 96         | M-3        | Y <sub>15</sub>     | 77         |            |                     | j          |

| C-4        | D <sub>2</sub>    | 57         | H-1        | М <sub>2, 3</sub>                 | 69         | M-4        | A <sub>14</sub>     | 78         |            |                     | İ          |

## PIN DESIGNATIONS (Sorted by Pin Name)

| PIN NAME        | PIN<br>NO. | PAD<br>NO. | PIN NAME        | PIN<br>NO. | PAD<br>NO. | PIN NAME           | PIN<br>NO. | PAD<br>NO. | PIN NAME            | PIN<br>NO. | PAD<br>NO. |

|-----------------|------------|------------|-----------------|------------|------------|--------------------|------------|------------|---------------------|------------|------------|

| _               |            | 37         | D <sub>8</sub>  | M-11       | 89         | INTEN              | L-2        | 74         | Т6                  | D-11       | 102        |

| _               | _          | 39         | D <sub>9</sub>  | M-10       | 87         | INTR               | L-1        | 14         | Т7                  | F-12       | 42         |

| _               | _          | 97         | D <sub>10</sub> | L-9        | 85         | Mo. c              | A-1        | 1          | T <sub>8</sub>      | F-13       | 101        |

| _               | _          | 99         | D <sub>11</sub> | N-7        | 24         | Mo, 1              | D-3        | 3          | T <sub>9</sub>      | C-13       | 41         |

| A-FULL          | J-3        | 70         | D <sub>12</sub> | M-6        | 81         | M <sub>0, 2</sub>  | E-2        | 65         | T <sub>10</sub>     | F-11       | 100        |

| Ao              | B-2        | 60         | D <sub>13</sub> | L-5        | 79         | M <sub>0, 3</sub>  | G-2        | 67         | T <sub>11</sub>     | G-11       | 40         |

| A <sub>1</sub>  | A-4        | 58         | D <sub>14</sub> | L-4        | 18         | M <sub>1, 0</sub>  | B-1        | 61         | TTL GND             | J-1        | 11         |

| A <sub>2</sub>  | B-5        | 116        | D <sub>15</sub> | N-1        | 16         | M <sub>1, 1</sub>  | D-2        | 63         | TTL GND             | N-5        | 20         |

| A3              | A-6        | 114        | ECL GND         | E-12       | 98         | M <sub>1, 2</sub>  | F-1        | 6          | TTL GND             | A-9        | 50         |

| Aa              | C-7        | 52         | ECL GND         | E-13       | 98         | M <sub>1, 3</sub>  | G-1        | 9          | TTL GND             | N-9        | 26         |

| A <sub>5</sub>  | B-9        | 110        | ECL GND         | E-11       | 98         | M <sub>2, 0</sub>  | C-1        | 2          | TTL GND             | A-5        | 56         |

| A <sub>6</sub>  | B-10       | 108        | ECL GND         | F-3        | 8          | M <sub>2, 1</sub>  | D-1        | 4          | TTL V <sub>CC</sub> | N-3        | 17         |

| A <sub>7</sub>  | A-12       | 106        | ECL GND         | L-6        | 23         | M <sub>2, 2</sub>  | F-2        | 66         | TTL VCC             | N-11       | 29         |

| A <sub>8</sub>  | M-12       | 30         | ECL GND         | C-6        | 113        | M <sub>2. 3</sub>  | H-1        | 69         | TTL VCC             | A-3        | 59         |

| Ag              | N-10       | 28         | ECL VCC         | J-13       | 38         | M <sub>3, 0</sub>  | C-2        | 62         | TTL VCC             | A-11       | 47         |

| A <sub>10</sub> | M-9        | 86         | ECL VCC         | H-3        | 68         | M <sub>3</sub> , 1 | E-3        | 64         | Y <sub>0</sub>      | B-3        | 119        |

| A <sub>11</sub> | N-8        | 84         | ECL VCC         | C-8        | 53         | M <sub>3, 2</sub>  | G-3        | 7          | Y <sub>1</sub>      | B-4        | 117        |

| A <sub>12</sub> | L-7        | 22         | ECL VCC         | L-8        | 83         | M <sub>3, 3</sub>  | H-2        | 10         | Y <sub>2</sub>      | C-5        | 115        |

| A <sub>13</sub> | M-5        | 80         | ECL VCC         | J-12       | 38         | OED                | K-2        | 72         | Y <sub>3</sub>      | A-7        | 54         |

| A <sub>14</sub> | M-4        | 78         | ECL VCC         | J-11       | 38         | RST                | K-1        | 13         | Y4                  | B-8        | 111        |

| A <sub>15</sub> | N-2        | 76         | EQUAL           | J-2        | 71         | S <sub>0</sub>     | G-12       | 36         | Y <sub>5</sub>      | C-9        | 109        |

| Cin             | E-1        | 5          | ERROR           | K-3        | 12         | S <sub>1</sub>     | H-12       | 95         | Y <sub>6</sub>      | C-10       | 48         |

| CP              | G-13       | 96         | FC              | N-13       | 31         | S <sub>2</sub>     | L-13       | 35         | Y <sub>7</sub>      | A-13       | 46         |

| D <sub>0</sub>  | A-2        | 120        | HOLD            | M-2        | 15         | S <sub>3</sub>     | H-13       | 94         | Y <sub>8</sub>      | N-12       | 90         |

| D <sub>1</sub>  | C-3        | 118        | 10              | H-11       | 34         | SLAVE              | M-1        | 75         | Y <sub>9</sub>      | L-11       | 88         |

| D <sub>2</sub>  | C-4        | 57         | 111             | K-13       | 93         | T <sub>0</sub>     | B-13       | 105        | Y <sub>10</sub>     | L-10       | 27         |

| D <sub>3</sub>  | B-6        | 55         | 12              | K-12       | 33         | T <sub>1</sub>     | B-12       | 45         | Y <sub>11</sub>     | M-8        | 25         |

| D <sub>4</sub>  | B-7        | 112        | 13              | K-11       | 92         | T <sub>2</sub>     | C-12       | 104        | Y <sub>12</sub>     | M-7        | 82         |

| D <sub>5</sub>  | A-8        | 51         | 14              | L-12       | 32         | T <sub>3</sub>     | C-11       | 44         | Y <sub>13</sub>     | N-6        | 21         |

| D <sub>6</sub>  | A-10       | 49         | 15              | M-13       | 91         | T <sub>4</sub>     | D-13       | 103        | Y <sub>14</sub>     | N-4        | 19         |

| D <sub>7</sub>  | B-11       | 107        | INTA            | L-3        | 73         | T <sub>5</sub>     | D-12       | 43         | Y <sub>15</sub>     | M-3        | 77         |

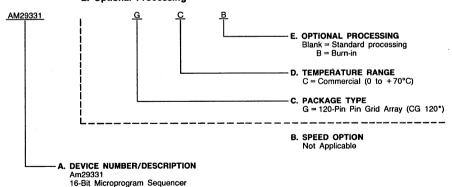

#### ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: A. Device Number

B. Speed Option (if applicable)

C. Package Type

D. Temperature Range E. Optional Processing

\* Preliminary. Subject to Change.

| Valid Combinations |         |  |  |  |  |  |

|--------------------|---------|--|--|--|--|--|

| AM29331            | GC, GCB |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

#### PIN DESCRIPTION

#### D<sub>0</sub> - D<sub>15</sub> Data (Bidirectional, Three-State)

Input to address multiplexer, counter, stack, and comparator register. Output for stack and stack pointer.

#### A<sub>0</sub> - A<sub>15</sub> Alternate Data (Input)

Input to address multiplexer and counter.

#### M<sub>0-3, 0-3</sub> Multiway (Input)

Four sets of multiway inputs providing 16-way branches. The first index refers to the set number.

#### Y<sub>0</sub> - Y<sub>15</sub> Address (Bidirectional, Three-State)

Output of microcode address, Input for interrupt address.

#### $I_0 - I_5$ Instruction (Input)

Selects one of sixty-four instructions.

#### T<sub>0</sub>-T<sub>11</sub> Test (Input)

Provides external test inputs.

#### So-S3 Select (Input)

Selects one of sixteen test conditions.

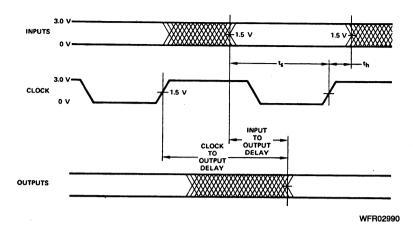

### CP Clock Pulse (Input)

Clocks sequencer at the LOW-to-HIGH transition.

#### RST Reset (Input. Active LOW)

Resets the sequencer.

#### FC Force Continue (Input)

Overrides instruction with CONTINUE.

#### INTR Interrupt Request (Input)

Requests the sequencer to interrupt execution.

#### INTEN Interrupt Enable (Input)

Enables interrupts.

#### INTA Interrupt Acknowledge (Bidirectional, Three-State, Active LOW)

Indicates that an interrupt is accepted.

#### HOLD Hold (Input)

Stops the sequencer and three-states the outputs.

#### OED Output Enable - D-Bus (Input)

Enables the D-bus driver, provided that the sequencer is not in the hold or slave mode.

#### SLAVE Slave (Input)

Makes the sequencer a slave.

#### ERROR Error (Output, Three-State)

Indicates a master/slave error in the slave mode. Indicates a malfunctioning driver or contention of any output in the master mode.

#### Cin Carry In (Input, Active LOW)

Carry-in to the incrementer.

#### A-FULL Almost Full (Bidirectional, Three-State)

Indicates that  $SP \ge 28$  (meaning there are five or less empty locations left on stack).

#### EQUAL Equal (Bidirectional, Three-State)

Indicates that the address comparator is enabled and has found a match.

#### **FUNCTIONAL DESCRIPTION**

#### **Architecture**

The major blocks of the sequencer are the address multiplexer, the address register (AR), the stack (with the top of stack denoted TOS), the counter (C), the test multiplexer with logic, and the address comparison register (R) (Figure 1). The bidirectional D-bus provides branch addresses and iteration counts; it also allows access to the stack from the outside. The A-bus may be used for map addresses. There are four sets of four-bit multiway branch inputs (M). The bidirectional Y-bus either ouputs microprogram addresses or inputs interrupt addresses. The buses are all 16 bits wide. Figure 1 shows a detailed block diagram of the sequencer.

#### **Address Multiplexer**

The address multiplexer can select an address from any of five sources:

- 1) A branch address supplied by the D-bus

- 2) A branch address supplied by the A-bus

- 3) A multiway-branch address

- 4) A return or loop address from the top of stack

- 5) The next sequential address from the incrementer

#### **Multiway Branch Address**

A multiway-branch address is formed by substituting the lower four bits of the address on the D-bus  $(D_3D_2D_1D_0)$  with one of the four sets  $(M_0,\ M_1,\ M_2\ or\ M_3)$  of four-bit multiway-branch addresses. The multiway-branch set is selected by the number  $D_1D_0$ , while the bits  $D_3$  and  $D_2$  are "don't cares."

#### **Address Register**

The address register contains the current address. It is loaded from the interrupt multiplexer and feeds the incrementer. The incrementer is inhibited if  $\overline{C_{IN}}$  is taken HIGH.

#### Stack

A 33-word-deep and 16 bit-wide stack provides first-in last-out storage for return addresses, loop addresses, and counter values. Items to be pushed come from the incrementer, the interrupt-return-address register, the counter, or the D-bus. Items popped go to the address multiplexer, the counter, or the D-bus.

The access to the stack via the D-bus may be used for context switching, stack extension, or diagnostics. As the stack is only accessible from the top, stack extension is done by temporarily storing the whole or some lower part of the stack outside the sequencer. The save and the later restore are done with pop and push operations respectively, at balanced points in the microprogram, for example, points with the same stack depth. The internal D-bus driver must be turned on when popping an item to the D-bus; if the driver is off, the item will be unstacked instead. The driver is normally turned on when the Output Enable signal is asserted and the sequencer is not being reset (OED = 1,  $\overline{\text{RST}} = 1$ ).

The stack pointer is a modulo 64 counter, which is incremented on each push and decremented on each pop. The stack pointer is reset to zero when the sequencer is reset, but the pointer may also be reset by instruction. Thus, the stack pointer indicates the number of items on the stack as long as stack overflow or underflow has not occurred. Overflow happens when an item is pushed onto a full stack, whereby the item at the bottom of the stack is overwritten. Underflow happens when an item is popped from an empty stack, in this case the item is undefined.

The contents of the stack pointer is present on the D-bus for all instructions except POP D, provided the driver is turned on. The output signal, A-FULL, is defined as  $SP \ge 28$ .

#### Counter

The counter may be used as a loop counter. It may be loaded from the D-bus, the A-bus, or via a pop from the stack. Its contents may also be pushed onto the stack.

A normal for-loop is set up by a FOR instruction, which loads the counter from the D- or A-bus with the desired number of iterations; the instruction also pushes onto the stack a loop address, that points to the next sequential instruction. The end of the loop is given by an unconditional END FOR instruction, which tests the counter value against the value one and then decrements the counter. If the values differ, the loop is repeated by selecting the address at the stack as the next address. If the values are equal, the loop is terminated by popping the stack, thereby removing the loop address, and selecting the address from the incrementer as the next address. The number of iterations is a 16-bit unsigned number, except that the number zero corresponds to 65,536 iterations. By pushing and popping counter values it is possible to handle nested loops.

#### **Address Comparison**

The sequencer is able to compare the address from the interrupt multiplexer with the contents of the comparator register. The instruction SET loads the comparator register with the address on the D-bus and enables the comparison, while CLEAR disables it. The comparison is disabled at reset. A HIGH is present at the output EQUAL if the comparison is enabled and the two addresses are equal. The comparison is useful for detection of a break point or counting the number of times a microinstruction at a specific address is executed.

#### Instruction Set

The sequencer has 64 instructions that are divided into four classes of 16 instructions each. The instruction lines  $I_0 - I_5$  use  $I_5$  and  $I_4$  to select a class and  $I_0 - I_3$  to select an instruction within a class. The classes are:

- l<sub>5</sub> l<sub>4</sub> Classes

- 0 O Conditional sequence control,

- Conditional sequence control with inverted polarity,

- 1 0 Unconditional sequence control, and

- 1 1 Special function with implicit continue.

Note that for the first three classes  $I_5$  forces the condition to be true and  $I_4$  inverts the condition. The basic instructions of

the first three classes are shown in Table 1 and the instructions of the fourth class in Table 2.

Structured microprogramming is supported by sequencer instructions that singly or in pairs correspond to high-level-language control constructs. Examples are FOR I: = D DOWN TO 1 DO... END FOR and CASE N OF... END CASE. The instructions have been given high-level language names where appropriate. Figure 2 shows how to microprogram important control constructs; the high-level language is on the left and the microcode on the right.

#### **Test Conditions**

The condition for a conditional instruction is supplied by a test multiplexer, which selects one out of sixteen tests with the select lines  $S_0-S_3$ . Twelve of these are supplied directly by the inputs  $T_0-T_{11}$ , while the remaining four tests are generated by the test logic from the inputs  $T_8-T_{11}$ . The following table shows the assignments.

| S <sub>0</sub> - S | 3 Test                           | Intended Use                |

|--------------------|----------------------------------|-----------------------------|

| 0-7                | T <sub>0</sub> – T <sub>7</sub>  | General                     |

| 8                  | T <sub>8</sub>                   | C (Carry)                   |

| 9                  | · T <sub>9</sub>                 | N (Negative)                |

| 10                 | T <sub>10</sub>                  | V (Overflow)                |

| 11                 | T <sub>11</sub>                  | Z (Zero or equal)           |

| 12                 | T <sub>8</sub> + T <sub>11</sub> | C + Z (Unsigned less        |

|                    |                                  | than or equal, borrow mode) |

| 13                 | T <sub>8</sub> + T <sub>11</sub> | C + Z (Unsigned less        |

|                    |                                  | than or equal)              |

| 14                 | T <sub>9</sub> ⊕ T <sub>10</sub> | N ⊕ V (Signed less than)    |

| 15                 | $(T_9 \oplus T_{10}) + T_{11}$   | (N ⊕ V) + Z (Signed less    |

|                    |                                  | than or equal)              |

#### **Force Continue**

The sequencer has a force continue (FC) input, which overrides the instruction inputs  $l_0-l_5$  with a CONTINUE instruction. This makes it possible to share the microinstruction field for the sequencer instruction with some other control or to initialize a writable control store.

#### Reset

In order to start a microprogram properly the sequencer must be reset. The reset works like an instruction overriding both the instruction input and the force continue input. The reset selects the address 0 at the address multiplexer, forces the EQUAL output to LOW, and disregards a potential interrupt request. It synchronously disables the address comparison and initializes the stack pointer to 0.

TABLE 1. INSTRUCTION SET for  $1_51_4 = 00$ , 01, 10

| I <sub>5</sub> – I <sub>0</sub> | Instruction      | Cond.<br>Y | .: False*<br>Stack | Con<br>Y | id.: True*<br>Stack | Counter        | Comp.        | D-Mux |

|---------------------------------|------------------|------------|--------------------|----------|---------------------|----------------|--------------|-------|

| 00, 10, 20                      | Goto D           | INC        | _                  | D        | _                   | _              | _            | SP    |

| 01, 11, 21                      | Call D           | INC        | _                  | D        | Push INC            | -              | _            | SP    |

| 02, 12, 22                      | Exit D           | INC        | -                  | D        | Pop                 | _              | -            | SP    |

| 03, 13, 23                      | End for D, C≠1   | INC        | -                  | D        | -                   | C←C−1<br>C←C−1 | -            | SP    |

|                                 | End for D. C = 1 | INC        | _                  | INC      | -                   | C←C – 1        | -            | SP    |

| 04, 14, 24                      | Goto A           | INC        | _                  | Α        | l –                 | _              | -            | SP    |

| 05, 15, 25                      | Call A           | INC        | _                  | Α        | Push INC            | _              | _            | SP    |

| 06, 16, 26                      | Exit A           | INC        | _                  | Α        | Pop                 | _              |              | SP    |

| 07, 17, 27                      | End for A, C≠1   | INC        | _                  | A        | - '                 | C←C – 1        | _            | SP    |

| ,,                              | End for A, C = 1 | INC        | _                  | INC      | _                   | C←C-1          | -            | SP    |

| 08, 18, 28                      | Goto M           | INC        |                    | D:M      | i _                 | -              | -            | SP    |

| 09, 19, 29                      | Call M           | INC        | l –                | D:M      | Push INC            | _              | -            | SP    |

| 0A, 1A, 2A                      | Exit M           | INC        | _                  | D:M      | Pop                 | -              | -            | SP    |

| 0B, 1B, 2B                      | End for M, C≠1   | INC        | -                  | D:M      | -                   | C←C - 1        | -            | SP    |

| 12, 12, 12                      | End for M, C = 1 | INC        | _                  | INC      | _                   | C←C – 1        |              | SP    |

| 0C, 1C, 2C                      | End Loop         | INC        | Pop                | TOS      | _                   | -              | _            | SP    |

| 0D, 1D, 2D                      | Call Coroutine   | INC        |                    | TOS      | TOS←INC             | -              | -            | SP    |

| 0E, 1E, 2E                      | Return           | INC        |                    | TOS      | Pop                 | _              | -            | SP    |

| 0F, 1F, 2F                      | End for, C≠1     | INC        | Pop                | TOS      | -"                  | C←C – 1        | *** <b>-</b> | SP    |

| 3.,, 2.                         | End for, C = 1   | INC        | Pop                | INC      | Pop                 | C←C – 1        |              | SP    |

Cond. = (Test [S] OR I<sub>5</sub>) XOR I<sub>4</sub> : = Concatination

= Counter

= Output of Incrementer = AR + 1 (if  $\overline{C_{in}}$  = LOW)

\* For instructions 00 to 0F, these two columns are as marked. For instructions 10 to 1F, these two columns have inverted polarity; i.e., left column is test true, right column is test false. For instructions 20 to 2F, execution is unconditional and the right column is always used.

TABLE 2. INSTRUCTION SET for  $I_5I_4 = 11$

| l5 - l0 | Instruction   | Y   | Stack    | Counter | Comp.       | D-Mux |

|---------|---------------|-----|----------|---------|-------------|-------|

| 30      | Continue      | INC | -        | -       | _           | SP    |

| 31      | For D         | INC | Push INC | C←D     | -           | SP    |

| 32      | Decrement     | INC | _        | C←C – 1 | -           | SP    |

| 33      | Loop          | INC | Push INC | -       | i <b>-</b>  | SP    |

| 34      | Pop D         | INC | Pop      | -       | -           | TOS   |

| 35      | Push D        | INC | Push D   | _       | _           | SP    |

| 36      | Reset SP      | INC | SP←0     | -       | -           | SP    |

| 37      | For A         | INC | Push INC | C←A     | -           | SP    |

| 38      | Pop C         | INC | Pop      | C←TOS   | -           | SP    |

| 39      | Push C        | INC | Push C   | _       | -           | SP    |

| 3A      | Swap          | INC | TOS←C    | C←TOS   | -           | SP    |

| 3B      | Push C Load D | INC | Push C   | C←D     | -           | SP    |

| 3C      | Load D        | INC | _        | C←D     | -           | SP    |

| 3D      | Load A        | INC | _        | C←A     | -           | SP    |

| 3E      | Set           | INC | -        | -       | R←D, Enable | SP    |

| 3F      | Clear         | INC | -        | -       | Disable     | SP    |

R = Comp. Register

#### Interrupts

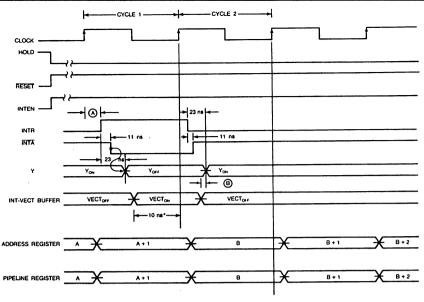

The sequencer may be interrupted at the completion of the current microcycle by asserting the interrupt request input INTR. The return address of the interrupted routine is saved on the stack, so that nested interrupts can be easily implemented. An interrupt is accepted if interrupts are enabled and the sequencer is not being reset or held (INTEN = HIGH,  $\overline{\text{RST}} = \text{HIGH}$ , and HOLD = LOW). The interrupt-acknowledge output (INTA) goes LOW when an interrupt is accepted.

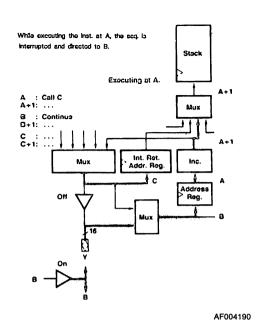

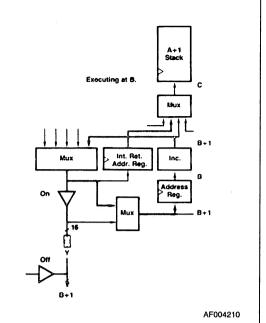

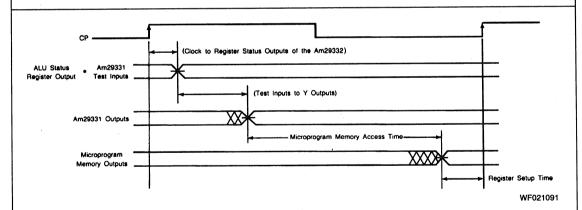

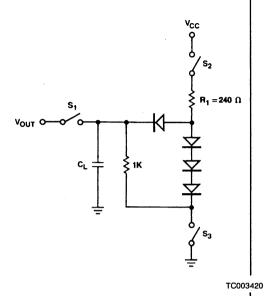

When there is no interrupt, addresses go from the address multiplexer to the Y-bus via the driver and to the address register and the comparator via the interrupt multiplexer. When there is an interrupt, the driver of the sequencer is turned off, an external driver is turned on, and the interrupt multiplexer is switched. The interrupt address is supplied via the external driver to the Y-bus, the address register and the comparator (Figure 3). In order to save the address from the address multiplexer, the address is stored in the interrupt return address register, which for simplicity is clocked every cycle. The next microinstruction is the first microinstruction of the interrupt routine (Figure 4).

In this cycle the address in the interrupt return address register is automatically pushed onto the stack. Therefore the microinstruction in this cycle must not use the stack; if a stack operation is programmed, the result is undefined. The instructions that do not use the stack are GOTO D, GOTO A, GOTO M, CONTINUE, DECREMENT, LOAD D, LOAD A, SET and CLEAR. A RETURN instruction terminates the interrupt routine and the interrupted routine is resumed. Interrupts only work with a single-level control path.

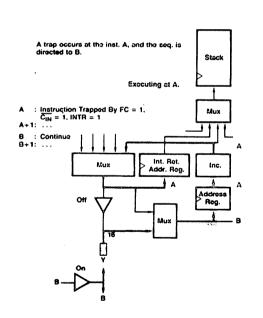

#### Traps

A trap is an unexpected situation linked to current microinstruction, that must be handled before the microinstruction completes and changes the state of the system. An example of such a situation is an attempt to read a word from memory across a word boundary in a single cycle. When a trap occurs, the current microinstruction must be aborted and re-executed after the execution of a trap routine, which in the meantime will take corrective measures. An interrupt, on the other hand, is not linked directly to the current microinstruction that can complete safely before an interrupt routine is executed.

Execution of a trap requires that the sequencer ignores the current microinstruction, selects the trap return address at the address multiplexer, and initiates an interrupt. This will save the trap return address on the stack and issue the trap address from an external source (Figure 5). The address register contains the address of the microinstruction in the

pipeline register, thus the address register already contains the trap return address when a trap occurs. This address can be selected by the address multiplexer by disabling the incrementer  $(\overline{C_{|N}}=1)$ , and using the force continue mode (FC = 1). In this mode the sequencer ignores the current microinstruction. The remaining part of the trap handling is done by the interrupt (Figure 6). Thus the section on interrupts also applies to traps. There is one exception, however. The interrupt enable cannot be used as a trap enable as it does not control the force continue mode and the carry-in to the

## incrementer. Hold Mode

The sequencer has a hold mode in which the operation is suspended.

When the HOLD signal goes active, the outputs (Y, NTA, A-FULL & EQUAL) are disabled and the sequencer enters the hold mode after the current cycle. While the sequencer is in this mode, the internal state is left unchanged and the D-bus is disabled. When the HOLD signal goes inactive, the outputs (Y, NTA, A-FULL & EQUAL) are enabled again and the sequencer leaves the hold mode after the cycle.

In a time multiplexed multi-microprocess system there may be one sequencer for all processes with microprogrammed context save and restore, or there may be one sequencer per microprocess permitting fast process switch. In the latter case the Y-buses of the sequencers are tied together and connected to a single microprogram store. A control unit decides on a cycle by cycle basis, what sequencer should be running and activates the HOLD signal to the remaining sequencers. The hold mode has higher priority than interrupts, and works independently of the reset. The hold mode can only be used with a single-level control path.

#### Master/Slave Configuration

In some systems reliability is very important. The master/slave configuration, that consists of two sequencers operated in parallel, is able to detect faults in both the interconnect and the internal function of the sequencers. One sequencer is the master and operates normally. The other is slave, i.e., all outputs except the signal ERROR are turned into inputs and connected to the outputs of the master. Since the slave is operated in parallel with the master, it can compare its result with the result of the master and signal an error if they differ. The error signal from the master indicates a malfunctioning driver or contention. Because a TTL output goes HIGH when power is missing, the ERROR signal also indicates power failure.

#### **High-Level Language Constructs**

An example of high-level language constructs using Am29331 instructions is given in Figure 2 (2-1, 2-2, 2-3, and 2-4).

REPEAT

LOOP

UNTIL CC

END LOOP NOT CC

WHILE CC DO

LOOP

IF NOT CC THEN EXIT L

-END WHILE END LOOP

L:

LOOP

LOOP

IF CC THEN EXIT

IF CC THEN EXIT L

**END LOOP**

END LOOP

**:**

Figure 2-1. Loops with Unknown Number of Iterations

FOR CNT: = 10 DOWN TO 1 DO FOR D 10

- - - - - - - - - - - - - - - - END FOR END FOR

Figure 2-2. Loop with Known Number of Iterations

```

PUSH D B

CASE I OF

GOTO M

0: -

A:

-, RETURN (TO B)

A + 2: -

1: -

-, RETURN (TO B)

2: -

A + 4: -

-, RETURN (TO B)

3: -

A + 6: -

-. RETURN

END CASE

```

Figure 2-3. Case Statement (with D =  $A_{15}$  . . .  $A_4$ XX00 and  $M_{0,\ 0-3} = A_3 I_1 I_0 0$  during the GOTO M instruction.  $A_1 A_0$  must be 00, and X signifies a don't care.)

PUSH D C IF NOT X THEN GOTO A IF X THEN IF NOT Y THEN GOTO B IF Y THEN -, RETURN (TO C) **ELSE** -, RETURN (TO C) END IF **ELSE** IF NOT Z THEN GOTO D IF Z THEN -, RETURN (TO D) D: **ELSE** -. RETURN (TO C) END IF END IF C:

Figure 2-4. Double-Nested If Statement

Figure 3. Am29331 Interrupt Cycle 1

Figure 4. Am29331 Interrupt Cycle 2

Figure 5. Am29331 Traps Cycle 1

Figure 6. Am29331 Traps Cycle 2

AF004200

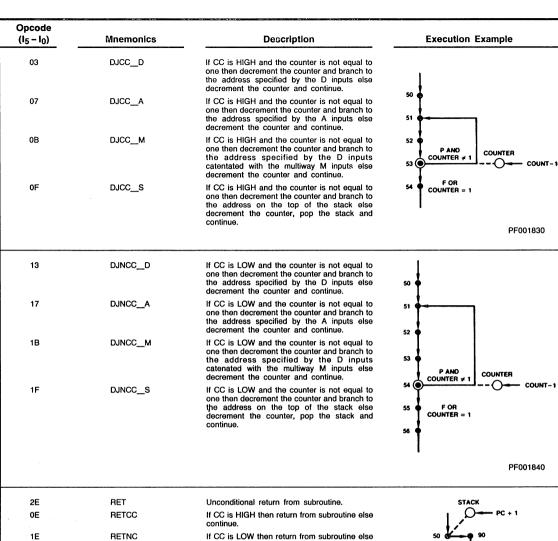

## Instruction Set Definition

Legend: ● = Other instruction

= Instruction being described

$CC = (Test [S_3 - S_0] OR I_5) XOR I_4$

P = Test pass

F = Test fail

O = Register in part

| Opcode<br>(I <sub>5</sub> – I <sub>0</sub> ) | Mnemonics | Description                                                                                                                                                | Execution Example              |

|----------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| 20                                           | BRA_D     | Go to D. Unconditional branch to the address specified by the D inputs.                                                                                    |                                |

| 24                                           | BRA_A     | Go to A. Unconditional branch to the address specified by the A inputs.                                                                                    | 50                             |

| 28                                           | BRA_M     | Go to M. Unconditional branch to the address specified by the D inputs catenated with the multiway M inputs.                                               | 51 90                          |

| 2C                                           | BRA_S     | Go to TOS. Unconditional branch to the address on the top of the stack. Also End Loop when used to terminate WHILE ENDWHILE loops.                         | 91                             |

|                                              |           |                                                                                                                                                            | PF001730                       |

| 00                                           | BRCC_D    | If CC is HIGH then branch to the address specified by the D inputs else continue.                                                                          |                                |

| 04                                           | BRCC_A    | If CC is HIGH then branch to the address specified by the A inputs else continue.                                                                          | 50                             |

| 08                                           | BRCC_M    | If CC is HIGH then branch to the address specified by the D inputs catenated with the multiway M inputs else continue.                                     | 51 <b>6</b> 52 <b>6</b> F      |

| ос                                           | BRCC_S    | If CC is HIGH then branch to the address on the top of the stack else pop the stack and continue. Also End Loop when used to terminate REPEAT UNTIL loops. | 53 @ p 90                      |

|                                              |           |                                                                                                                                                            | 91                             |

|                                              |           |                                                                                                                                                            | PF001810                       |

| 10                                           | BRNC_D    | If CC is LOW then branch to the address specified by the D inputs else continue.                                                                           | 1                              |

| 14                                           | BRNC_A    | If CC is LOW then branch to the address specified by the A inputs else continue.                                                                           | 50                             |

| 18                                           | BRNC_M    | If CC is LOW then branch to the address specified by the D inputs catenated with the multiway M inputs else continue.                                      | 51 <b>•</b><br>52 <b>•</b> ) F |

| 1C                                           | BRNC_S    | If CC is LOW then branch to the address on the top of the stack else pop the stack and continue. Also End Loop when used to terminate REPEATUNTIL loops.   | 53 @ p 90                      |

|                                              |           |                                                                                                                                                            | ♠ 92                           |

|                                              |           |                                                                                                                                                            | PF001750                       |

| Opcode                             |           | _                                                                                                                                                             |                        |

|------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| (l <sub>5</sub> – l <sub>0</sub> ) | Mnemonics | Description                                                                                                                                                   | Execution Example      |

| 21                                 | CALL_D    | Call D. Unconditional branch to the subroutine address specified by the D inputs and push the PC on the stack.                                                | 50                     |

| 25                                 | CALL_A    | Call A. Unconditional branch to the subroutine address specified by the A inputs and push the PC on the stack.                                                | 51 STACK 51 PC + 1     |

| 29                                 | CALL_M    | Call M. Unconditional branch to the surbroutine<br>address specified by the D inputs catenated<br>with the multiway M inputs and push the PC on<br>the stack. | 52 90                  |

| 2D                                 | CALL_S    | Call TOS. Exchange PC and TOS. Also call coroutine.                                                                                                           | 54 92                  |

|                                    |           |                                                                                                                                                               | <b>I</b><br>PF00176    |

| 01                                 | CCC_D     | If CC is HIGH then call the subroutine address specified by the D inputs else continue.                                                                       |                        |

| 05                                 | CCC_A     | If CC is HIGH then call the subroutine address specified by the A inputs else continue.                                                                       | 50                     |

| 09                                 | CCC_M     | If CC is HIGH then call the subroutine address specified by the D inputs catenated with the multiway M inputs else continue.                                  | 51 STACK 52 S F PC + 1 |

| 0D                                 | ccc_s     | If CC is HIGH then call the address on the top<br>of the stack else continue. Also used for<br>conditional coroutine calls.                                   | 53 P 90                |

|                                    |           |                                                                                                                                                               | 54 🖍 🕯 91              |

|                                    |           |                                                                                                                                                               | 55 92                  |

|                                    |           |                                                                                                                                                               | 56                     |

|                                    |           |                                                                                                                                                               | PF00177                |

| 11 '                               | CNC_D     | If CC is LOW then call the address specified by the D inputs else continue.                                                                                   |                        |

| 15                                 | CNC_A     | If CC is LOW then call the address specified by the A inputs else continue.                                                                                   | 50                     |

| 19                                 | CNC_M     | If CC is LOW then call the address specified by<br>the D inputs catenated with the multiway M<br>inputs else continue.                                        | STACK                  |

| 1D                                 | CNC_S     | If CC is LOW then call the address on the top of the stack else continue. Also a conditional coroutine call.                                                  | 52 OF PC + 1           |

|                                    |           |                                                                                                                                                               | 54 91                  |

|                                    |           |                                                                                                                                                               | 55 92                  |

|                                    |           |                                                                                                                                                               | . PF00178              |

| 22                                 | EXIT_D    | Exit to D. Unconditional branch to the address specified by the D inputs and pop the stack.                                                                   | l                      |

| 26                                 | EXIT_A    | Exit to A. Unconditional branch to the address specified by the A inputs and pop the stack.                                                                   | 50 🛉                   |

| 2A                                 | EXIT_M    | Exit to M. Unconditional branch to the address specified by the D inputs catenated with the multiway M inputs and pop the stack.                              | 51 90                  |

| 2E                                 | EXIT_S    | Exit to TOS. Unconditional branch to the address specified by the TOS and pop the stack. Also a return.                                                       | STACK 92               |

| Opcode<br>(I <sub>5</sub> – I <sub>0</sub> ) | Mnemonics | Description                                                                                                                                                             | Execution Example |

|----------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 02                                           | XTCC_D    | If CC is HIGH then exit to the address specified<br>by the D inputs and pop the stack else continue<br>with no pop.                                                     | STACK PC + 1      |

| 06                                           | XTCC_A    | If CC is HIGH then exit to the address specified by the A inputs and pop the stack else continue with no pop.                                                           | 50 51             |

| OA                                           | XTCC_M    | If CC is HIGH then exit to the address specified<br>by the D inputs catenated to the multiway M<br>inputs and pop the stack else continue with no<br>pop.               | STACK 51 F        |

| 0E                                           | xtcc_s    | If CC is HIGH then exit to the address specified by the TOS and pop the stack else continue with no pop. Also RETCC.                                                    | 53                |

|                                              |           |                                                                                                                                                                         | 54<br>55          |

|                                              |           |                                                                                                                                                                         | 56                |

|                                              |           |                                                                                                                                                                         | 4                 |

|                                              |           |                                                                                                                                                                         | PF001800          |

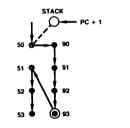

| 12                                           | XTNC_D    | If CC is LOW then exit to the address specified by the D inputs and pop the stack else continue.                                                                        | STACK PC + 1      |

| 16                                           | XTNC_A    | If CC is LOW then exit to the address specified by the A inputs and pop the stack else continue.                                                                        | 50 <b>*</b>       |

| 1A                                           | XTNC_M    | If CC is LOW then exit to the address specified<br>by the D inputs catenated with the multiway M<br>inputs and pop the stack else continue.                             | STACK 51 F        |

| 1E                                           | XTNC_S    | If CC is LOW then exit to the address specified by the TOS and pop the stack else continue. Also RETNC.                                                                 | 53                |

|                                              |           |                                                                                                                                                                         | L                 |

|                                              |           |                                                                                                                                                                         | 55                |

|                                              |           |                                                                                                                                                                         |                   |

|                                              |           |                                                                                                                                                                         | PF001810          |

| 23                                           | DJMP_D    | If the counter is not equal to one then decrement the counter and branch to the address specified by the D inputs else continue.                                        | •                 |

| 27                                           | DJMP_A    | If the counter is not equal to one then decrement the counter and branch to the address specified by the A inputs else continue.                                        | 50                |

| 2B                                           | DJMP_M    | If the counter is not equal to one then decrement the counter and branch to the address specified by the D inputs catenated with the multiway M inputs else continue.   | 52 COUNTER # 1    |

| 2F                                           | DJMP_S    | If the counter is not equal to one then decrement the counter and branch to the address on the top of the stack else decrement the counter, pop the stack and continue. | 53 COUNTER = 1    |

|                                              |           |                                                                                                                                                                         | PF001820          |

|                                              |           |                                                                                                                                                                         |                   |

continue.

PF001850

| Opcode<br>(I <sub>5</sub> – I <sub>0</sub> ) | Mnemonics | Description                                                                                                                                  | Execution Example |

|----------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 31                                           | FOR_D     | Initialize loop. Push the PC on the stack, load the counter with the value of the D inputs and continue. Use with DJMP_S for FOR NEXT loops. | 50 STACK PC + 1   |

| 37                                           | FOR_A     | Initialize loop. Push the PC on the stack, load the counter with the value of the A inputs and continue. Use with DJMP_S for FOR NEXT loops. | 51 COUNTER S2     |

| 33                                           | LOOP      | Initialize loop. Push the PC and continue. Use with BRCC_S for REPEAT UNTIL loops or with XTCC_D and BRA_S for WHILE ENDWHILE loops.         | STACK 50 PC + 1   |

|                                              |           |                                                                                                                                              | 51 (19)           |

|                                              |           |                                                                                                                                              | •                 |

|                                              |           |                                                                                                                                              | PF001860          |

| 34                                           | POP_D     | Pop the stack, output the value on the D outputs and continue.                                                                               | 1                 |

| 38                                           | POP_C     | Pop the stack, place the value in the counter and continue.                                                                                  | STACK             |

| 35                                           | PUSH_D    | Push the D inputs on the stack and continue.                                                                                                 | 51                |

| 39                                           | PUSH_C    | Push the counter on the stack and continue.                                                                                                  |                   |

| <b>3A</b><br>- 1. 44 % 14 - 4                | SWAP      | Exchange the counter and the top of stack and continue.                                                                                      | 52                |

|                                              |           |                                                                                                                                              | 1                 |

|                                              |           |                                                                                                                                              | 50 STACK          |

|                                              |           |                                                                                                                                              | 51                |

|                                              |           |                                                                                                                                              | 52                |

|                                              |           |                                                                                                                                              |                   |

|                                              |           |                                                                                                                                              | STACK             |

|                                              |           |                                                                                                                                              | 51 0              |

|                                              |           |                                                                                                                                              | COUNTER           |

PF001870

| 30 CONT Continue.  32 DECR Decrement the counter and continue.  36 RESET_SP Reset the stack pointer and continue.  50 COUNTER  51 COUNTER  52 COUNTER  53 COUNTER  54 COUNTER  55 COUNTER  56 COUNTER  57 COUNTER  58 COUNTER  59 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  51 COUNTER  52 COUNTER  53 COUNTER  54 COUNTER  55 COUNTER  56 COUNTER  57 COUNTER  58 COUNTER  59 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  51 COUNTER  52 COUNTER  53 COUNTER  54 COUNTER  55 COUNTER  56 COUNTER  57 COUNTER  58 COUNTER  59 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  51 COUNTER  52 COUNTER  55 COUNTER  56 COUNTER  57 COUNTER  58 COUNTER  59 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  51 COUNTER  52 COUNTER  53 COUNTER  54 COUNTER  55 COUNTER  56 COUNTER  57 COUNTER  58 COUNTER  59 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  50 COUNTER  | Opcode<br>(I <sub>5</sub> – I <sub>0</sub> ) | Mnemonics | Description                                                                                  | Execution Example          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------|----------------------------------------------------------------------------------------------|----------------------------|

| 3C LOAD_D Load the counter with the value of the D inputs and continue.  3D LOAD_A Laad the counter with the value of the A inputs 3C CONT Continue.  3D CONT Continue.  3D DECR Decrement the counter and continue.  3E RESET_SP Reset the stack pointer and continue.  3D COUNTER  3D COUNTER  4D COUNTER  5D CO | 3В                                           | STACK_C   | Push the counter on the stack, load the counter with the value of the D inputs and continue. | STACK                      |

| DECR Decrement the counter and continue.  COUNTER  COUNTE | 3C                                           | LOAD_D    | Load the counter with the value of the D inputs                                              | 1,0                        |

| PF00188  30 CONT Continue. 32 DECR Decrement the counter and continue. 36 RESET_SP Reset the stack pointer and continue.  50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 51 COUNTER 52 COUNTER 52 COUNTER 53 COUNTER 54 COUNTER 55 COUNTER 56 COUNTER 57 COUNTER 58 COUNTER 59 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER 50 COUNTER | 3D                                           | LOAD_A    | Load the counter with the value of the A inputs                                              | COUNTER                    |

| 30 CONT Continue.  32 DECR Decrement the counter and continue.  36 RESET_SP Reset the stack pointer and continue.  50 COUNTER  51 COUNTER  52 COUNTER  53 COUNTER  54 COUNTER  55 COUNTER  56 CLEAR  57 CLEAR  58 Disable the comparator and continue.  59 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  51 COMPARE  52 COMPARE  53 COMPARE  54 COMPARE  55 COMPARE  56 COMPARE  57 COMPARE  58 COMPARE  59 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  51 COMPARE  51 COMPARE  52 COMPARE  53 COMPARE  54 COMPARE  55 COMPARE  56 COMPARE  57 COMPARE  58 COMPARE  59 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  51 COMPARE  51 COMPARE  52 COMPARE  53 COMPARE  54 COMPARE  55 COMPARE  56 COMPARE  57 COMPARE  58 COMPARE  58 COMPARE  59 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  51 COMPARE  52 COMPARE  53 COMPARE  54 COMPARE  55 COMPARE  56 COMPARE  57 COMPARE  57 COMPARE  58 COMPARE  59 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  51 COMPARE  52 COMPARE  53 COMPARE  54 COMPARE  55 COMPARE  55 COMPARE  56 COMPARE  57 COMPARE  58 COMPARE  58 COMPARE  59 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  50 COMPARE  51 COMPARE  51 COMPARE  52 COMPARE  53 COMPARE  54 COMPARE  55 COMPARE  55 COMPARE  56 COMPARE  57 COMPARE  57 COMPARE  57 COMPARE  58 COMPARE  58 COMPARE  58 COMPARE |                                              |           |                                                                                              | 50 D D                     |

| 32 DECR Decrement the counter and continue.  36 RESET_SP Reset the stack pointer and continue.  50 DECR RESET_SP Reset the stack pointer and continue.  50 DECR RESET_SP Reset the stack pointer and continue.  51 DECR RESET_SP Reset the stack pointer and continue.  52 DECR RESET_SP Reset the stack pointer and continue.  53 DECR RESET_SP Reset the stack pointer and continue.  54 DECR RESET_SP Reset the stack pointer and continue.  55 DECR RESET_SP Reset the stack pointer and continue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |           |                                                                                              | PF001880                   |

| SET  Load the comparison register with the value of the D inputs, enable the comparator and continue.  SET  Load the comparison register with the value of the D inputs, enable the comparator and continue.  SO  COMPARE  50  51  52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32                                           | DECR      | Decrement the counter and continue.                                                          | 51 © COUNTER COUNT-1 51 ©  |