## Am29117

#### **DISTINCTIVE CHARACTERISTICS**

- Optimized for High-Performance Controllers

Architecture and instruction set optimized for high-performance, intelligent controllers

- Flow-Through Architecture

Separate input and output ports avoid bus turn around for higher throughput

- Fast

Supports 100 ns microcycle time/10 MHz data rate

for all instructions

- 16-Bit Barrel Shifter

- 32 Working Registers

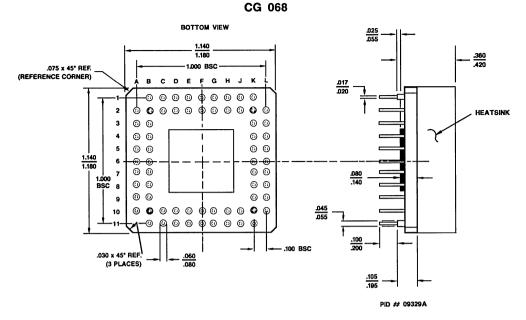

- 68-Pin Pin Grid Array Package

#### **GENERAL DESCRIPTION**

The Am29117 is a microprogrammable 16-bit bipolar microprocessor whose architecture and instruction set are identical to the Am29116's except for the I/O bus structure. Since the device has separate input and output ports, designers can avoid quick bus turnaround requirements.

The architecture and instruction set are not only optimized for high-performance peripheral controllers, but also suit-

able for microprogrammed processor applications when combined with the Am29517A 16 x 16 Multiplier.

The instruction set contains unique functions besides ordinary logic and arithmetic functions: bit manipulation instructions (set, reset and test), rotate merge/compare instructions, prioritize instruction and CRC instruction.

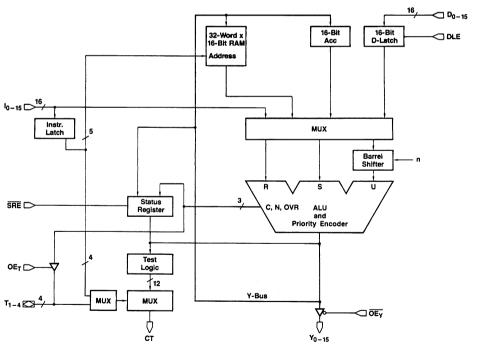

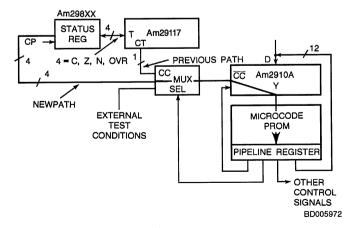

#### **BLOCK DIAGRAM**

BD001972

Publication # Rev. Amendment D /0

Issue Date: April 1987

#### **RELATED AMD PRODUCTS**

| Part No.                  | Description                                                                                    |

|---------------------------|------------------------------------------------------------------------------------------------|

| Am29112                   | High-Performance 8-Bit Slice Microprogram Sequencer                                            |

| Am29114                   | Eight-Level Real-Time Interrupt Controller                                                     |

| Am29116                   | High-Performance Single-Port Bipolar Microprocessor                                            |

| Am29116A                  | Speed-Enhanced Version of the Am29116 (Supports up to 76-ns Microcycle Times)                  |

| Am29L116A                 | Low-Power Version of the Am29116 (25% Lower Power Dissipation)                                 |

| Am29C117                  | CMOS Version of the Am29117                                                                    |

| Am29118                   | 8-Bit Am29116 I/O Support                                                                      |

| Am29130                   | 16-Bit Barrel Shifter                                                                          |

| Am29PL141                 | Fuse-Programmable Controller                                                                   |

| Am29516/Am29517<br>Family | 16 x 16-Bit Parallel Multipliers (High-Speed Bipolar,<br>Low-Power Bipolar, and CMOS Versions) |

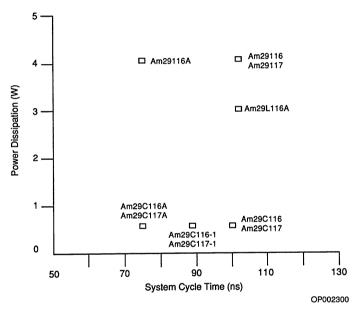

The following diagram is a summary of devices within the Am29116 Family showing performance versus power:

Am29116 Family (Performance vs. Power)

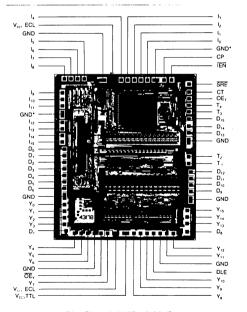

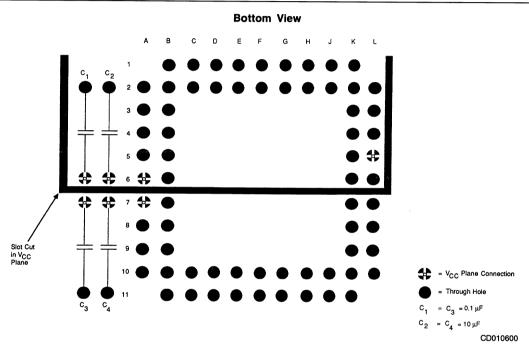

#### CONNECTION DIAGRAM PIN GRID ARRAY Bottom View

A B C D E F G H J K L

|    | _    |            |     |     |     |     |     |     |     |     |      |

|----|------|------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| 1  |      | Y1         | GND | D5  | D3  | D1  | D0  | 114 | l12 | 110 |      |

| 2  | Y3   | Y2         | Y0  | D6  | D4  | D2  | 115 | 113 | l11 | 19  | 18   |

| 3  | Y4   | D7         |     |     |     |     |     |     |     | 17  | 16   |

| 4  | Y6   | <b>Y</b> 5 |     |     |     |     |     |     |     | 15  | GND  |

| 5  | ŌEY  | GND        |     |     |     |     |     |     |     | 14  | VCCE |

| 6  | VCCE | Y7         |     |     |     |     |     |     |     | 13  | 12   |

| 7  | VCC1 | Y8         |     |     |     |     |     |     |     | 10  | 11   |

| 8  | Y9   | Y10        |     |     |     |     |     |     |     | ĪĒN | СР   |

| 9  | DLE  | GND        |     |     |     |     |     |     |     | СТ  | SRE  |

| 10 | Y11  | Y12        | Y13 | Y15 | D9  | D12 | T2  | D13 | D15 | T4  | OET  |

| 11 |      | D8         | Y14 | GND | D10 | D11 | T1  | GND | D14 | ТЗ  |      |

|    |      |            |     |     |     |     |     |     |     | _   |      |

CD010610

Note: Notch indicates orientation.

# DO-D15 IO-I15 YO-Y15 IEN SRE T1-T4 DLE

СТ

LS002610

LOGIC SYMBOL

ŒY

OE<sub>T</sub>

#### **METALLIZATION AND PAD LAYOUT**

Die Size: 0.285" x 0.334"

Gate Count: 2500 Equivalent Gates

\*These GND pads are internally connected inside the package, therefore they do not have external pin numbers.

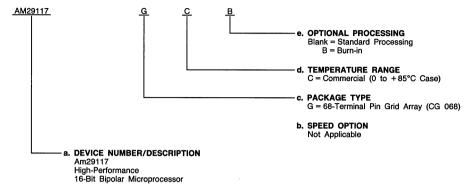

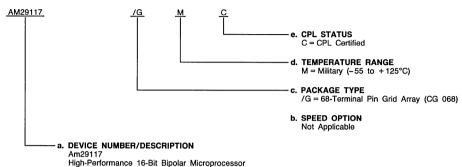

## ORDERING INFORMATION Standard Products

AMD products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. **Device Number**

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

| Valid Combinations AM29117 GC, GCB |  |         |  |

|------------------------------------|--|---------|--|

| AM29117                            |  | GC, GCB |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

## ORDERING INFORMATION (Cont'd.) CPL Products

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. CPL (Controlled Products List) products are processed in accordance with MIL-STD-883C, but are inherently non-compliant because of package, solderability, or surface treatment exceptions to those specifications. The order number (Valid Combination) for APL products is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

|         | Valid Co | mbinations |  |

|---------|----------|------------|--|

| AM29117 |          | /GMC       |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### Group A Tests

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### PIN DESCRIPTION

#### CP Clock Pulse (Input)

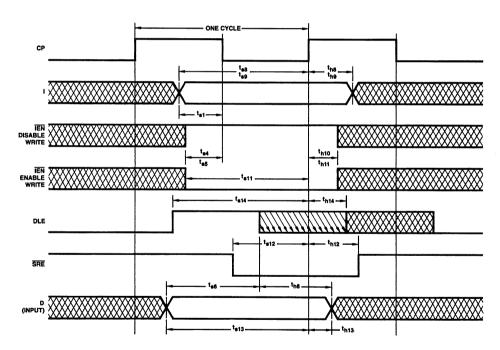

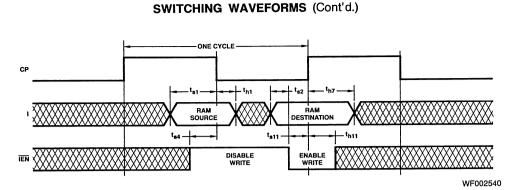

The clock input to the Am29117. The RAM latch is transparent when the clock is HIGH. When the clock goes LOW, the RAM output is latched. Data is written into the RAM during the LOW period of the clock, provided IEN is LOW, and if the instruction being executed designates the RAM as the destination of operation. The Accumulator and Status Register will accept data on the LOW-to-HIGH transition of the clock if IEN is also LOW. The instruction latch becomes transparent when it exits an immediate instruction mode during a LOW-to-HIGH transition of the clock.

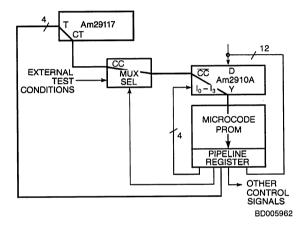

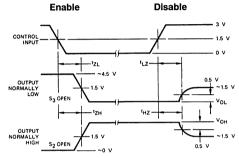

#### CT Conditional Test (Output)

The condition code multiplexer selects one of the twelve condition code signals and places it on the CT output. A HIGH on the CT output indicates a passed condition and a LOW indicates a failed condition.

#### D<sub>0</sub> - D<sub>15</sub> Data Input Lines (Input)

Data Input Lines,  $D_0$  –  $D_{15}$ , are used as external data inputs which allow data to be directly loaded into the 16-bit data latch.

#### DLE Data Latch Enable (Input)

When DLE is HIGH, the 16-bit data latch is transparent and is latched when DLE is LOW.

#### I<sub>0</sub>-I<sub>15</sub> Instruction Inputs (Input)

Sixteen Instruction Inputs, used to select the operation to be performed in the Am29117. Also used as data inputs while performing immediate instructions.

#### IEN Instruction Enable (Input)

When IEN is LOW, data can be written into RAM when the clock is LOW. The Accumulator can accept data during the LOW-to-HIGH transition of the clock. Having IEN LOW, the Status Register can be updated when SRE is LOW. When IEN is HIGH, the conditional test output, CT, is disabled as a function of the instruction inputs.

#### OET Output Enable (Output)

When OE<sub>T</sub> is LOW, 4-bit T outputs are disabled (high impedance); when OE<sub>T</sub> is HIGH, the 4-bit T outputs are enabled (HIGH or LOW).

#### OEy Output Enable (Input)

When  $\overline{OE}_{Y}$  is HIGH, the 16-bit Y outputs are disabled (high impedance); when  $\overline{OE}_{Y}$  is LOW, the 16-bit Y outputs are enabled (HIGH or LOW).

#### SRE Status Register Enable (Input)

When SRE and IEN are both LOW, the Status Register is updated at the end of all instructions with the exception of NO-OP, Save Status and Test Status. Having either SRE or IEN HIGH will inhibit the Status Register from changing.

#### T<sub>1</sub>-T<sub>4</sub> Test I/O Pins (Input/Output)

Under the control of  $OE_T$ , the four lower status bits, Z, C, N and OVR, become outputs on  $T_1 - T_4$ , respectively, when  $OE_T$  goes HIGH. When  $OE_T$  is LOW,  $T_1 - T_4$  are used as inputs to generate the CT output.

#### Yo - Y<sub>15</sub> Data Output Lines (Output)

Data Output lines. When  $\overline{\text{OE}}_Y$  is HIGH, the 16-bit Y outputs are disabled (high impedance); having  $\overline{\text{OE}}_Y$  LOW allows the ALU data to be output on  $Y_0 - Y_{15}$ .

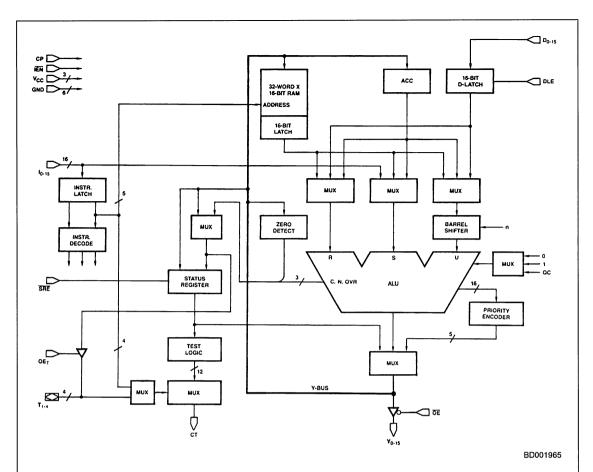

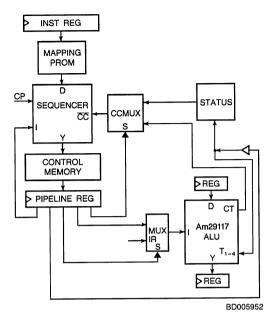

Figure 1. Detailed Block Diagram

#### **FUNCTIONAL DESCRIPTION**

#### Architecture of the Am29117

The Am29117 is a high-performance, microprogrammable 16-bit bipolar microprocessor.

As shown in the Detailed Block Diagram (Figure 1), the device consists of the following elements interconnected with 16-bit data paths.

- 32-Word by 16-Bit RAM

- Accumulator

- Data Latch

- Barrel Shifter

- Arithmetic Logic Unit (ALU)

- Priority Encoder

- Status Register

- Condition-Code Generator/Multiplexer

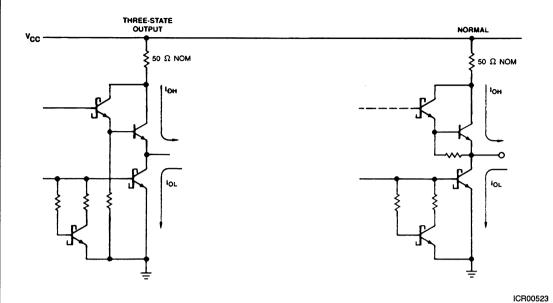

- Three-State Output Buffers

- Instruction Latch and Decoder

#### 32-Word by 16-Bit RAM

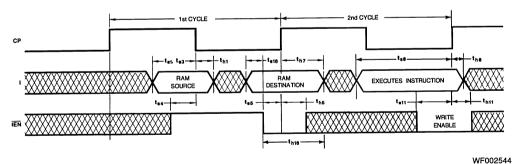

The 32-word by 16-bit RAM is a single-port RAM with a 16-bit latch at its output. The latches are transparent when the clock input (CP) is HIGH and latched when the clock input is LOW. Data is written into the RAM while the clock is LOW if the  $\overline{\rm IEN}$  input is also LOW and if the instruction being executed defines the RAM as the destination of the operation. For byte instructions, only the lower eight RAM bits are written into; for word instructions, all 16 bits are written into. With the use of an external multiplexer on five of the instruction inputs, it is possible to select separate read and write addresses for the same instruction.

#### **Accumulator**

The 16-bit Accumulator is an edge-triggered register. The Accumulator accepts data on the LOW-to-HIGH transition of the clock input if the  $\overline{\text{IEN}}$  input is LOW and if the instruction being executed defines the Accumulator as the destination of the operation. For byte instructions, only the lower eight bits of the Accumulator are written into; for word instructions, all 16 bits are written into.

#### **Data Latch**

The 16-bit Data Latch holds the data input to the Am29117 on the D bus. The latch is transparent when the DLE input is HIGH and latched when the DLE input is LOW.

#### Barrel Shifter

A 16-bit Barrel Shifter is used as one of the ALU inputs. This permits rotating data from either the RAM, the Accumulator or the Data Latch up to 15 positions. In the word mode, the Barrel Shifter rotates a 16-bit word; in the byte mode, it rotates only the lower eight bits.

#### Arithmetic Logic Unit

The Am29117 contains a 16-bit ALU with full carry lookahead across all 16 bits in the arithmetic mode. The ALU is capable of operating on either one, two or three operands, depending upon the instruction being executed. It has the ability to execute all conventional one and two operand operations, such as pass, complement, two's complement, add, subtract, AND, NAND, OR, NOR, EXOR, and EX-NOR. In addition, the ALU can also execute three-operand instructions such as rotate and merge, and rotate and compare with mask. All ALU operations can be performed on either a word or byte basis, with byte operations being performed on the lower eight bits only.

The ALU produces three status outputs, C (carry), N (negative) and OVR (overflow). The appropriate flags are generated at

the byte or word level, depending upon whether the device is executing in the byte or word mode. The Z (zero) flag, although not generated by the ALU, detects zero at both the byte and word level.

The carry input to the ALU is generated by the Carry Multiplexer which can select an input of zero, one, or the stored carry bit from the Status Register, QC. Using QC as the carry input allows execution of multiprecision addition and subtractions.

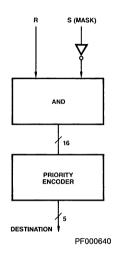

#### **Priority Encoder**

The Priority Encoder produces a binary-weighted code to indicate the locations of the highest order ONE at its input. The input to the Priority Encoder is generated by the ALU which performs an AND operation on the operand to be prioritized and a mask. The mask determines which bit locations to eliminate from prioritization. In the word mode, if no bit is HIGH, the output is a binary zero. If bit 15 is HIGH, the output is a binary one. Bit 14 produces a binary two, etc. Finally, if only bit 0 is HIGH, a binary 16 is produced.

In the byte mode, bits 8 through 15 do not participate. If none of bits 7 through 0 are HIGH, the output is a binary zero. If bit 7 is HIGH a binary one is produced. Bit 6 produces a binary two, etc. Finally, if only bit 0 is HIGH, a binary 8 is produced.

#### Status Register

The Status Register holds the 8-bit status word. With the Status-Register Enable ( $\overline{SRE}$ ) input LOW and the  $\overline{IEN}$  input LOW, the Status Register is updated at the end of all instructions except NO-OP, Save-Status and Test-Status instructions.  $\overline{SRE}$  going HIGH or  $\overline{IEN}$  going HIGH inhibits the Status Register from changing.

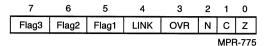

The lower four bits of the Status Register contain the ALU status bits of Zero (Z), Carry (C), Negative (N), and Overflow (OVR). The upper four bits contain a Link bit and three user-definable status bits (Flag 1, Flag 2, Flag 3).

With SRE LOW and IEN LOW, the lower four status bits are updated after each instruction except those mentioned above, NO-OP, Save Status, Status Test and the Status Set/Reset instruction for the upper four bits. Under the same conditions, the upper four status bits are changed only during their respective Status Set/Reset instructions and during Status Load instructions in the word mode. The Link-Status bit is also updated after each shift instruction.

The Status Register can be loaded from the internal Y-bus, and can also be selected as a source for the internal Y-bus. When the Status Register is loaded in the word mode, all 8-bits are updated; in the byte mode, only the lower 4 bits (Z, C, N, OVR) are updated.

When the Status Register is selected as a source in the word mode, all eight bits are loaded into the lower byte of the destination; the upper byte of the destination is loaded with all zeros. In the byte mode, the Status Register again loads into the lower byte of the destination, but the upper byte remains unchanged. This Store and Load combination allows saving and restoring the Status Register for interrupt and subroutine processing. The four lower status bits (Z, C, N, OVR) can be read directly via the bidirectional T bus. These four bits are available as outputs on the  $T_{1-4}$  outputs whenever  $\text{OE}_{\text{T}}$  is HIGH

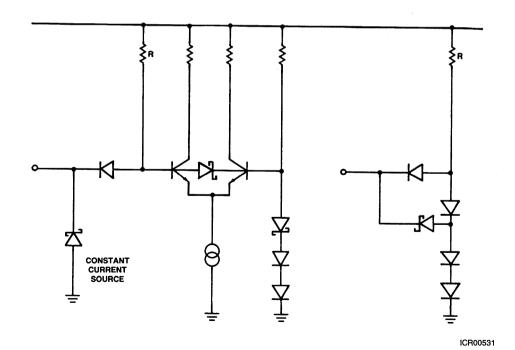

#### Condition-Code Generator/Multiplexer

The Condition-Code Generator/Multiplexer contains the logic necessary to develop the 12 condition-code test signals. The multiplexer portion can select one of these test signals and place it on the CT output for use by the microprogram sequence. The multiplexer may be addressed in two different

ways. One way is through the Test Instruction. This instruction specifies the test condition to be placed in the CT output, but does not allow an ALU operation at the same time. The second method uses the bidirectional T bus as an input. This requires extra bits in the microword, but provides the ability to simultaneously test and execute. The test instruction lines,

I<sub>0-4</sub>, have priority over T<sub>1-4</sub>, for testing status.

#### Three-State Output Buffers

There are two sets of Three-State Output Buffers in the Am29117. One set controls the 16-bit Y bus. These outputs are enabled by placing a LOW on the OEY input. A HIGH puts the Y outputs in the high-impedance state.

The second set of Three-State Output Buffers controls the bidirectional 4-bit T bus and is enabled by placing a HIGH on the OE<sub>T</sub> input. This allows storing the four internal ALU status bits (Z, C, N, OVR) externally. A LOW OET input forces the T outputs into the high-impedance state. External devices can then drive the T bus to select a test condition for the CT output.

#### Instruction Latch and Decoder

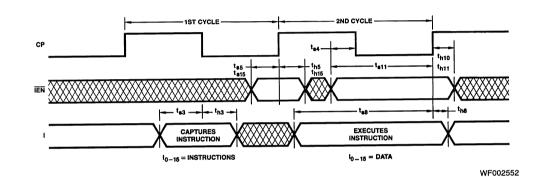

The 16-bit Instruction Latch is normally transparent to allow decoding of the Instruction Inputs by the Instruction Decoder into the internal control signals for the Am29117. All instructions except Immediate Instructions are executed in a single clock cycle.

Immediate instructions require two clock cycles for execution. During the first clock cycle, the Instruction Decoder recognizes that an Immediate Instruction is being specified and captures the data on the Instruction Inputs in the Instruction Latch. During the second clock cycle, the data on the Instruction Inputs is used as one of the operands for the function specified during the first clock cycle. At the end of the second clock cycle, the Instruction Latch is returned to its transparent

#### Instruction Set

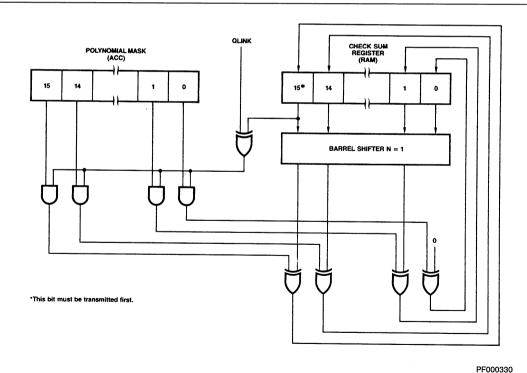

The instruction set of the Am29117 is very powerful. In addition to the single and two operand logical and arithmetic instructions, the Am29117 instruction set contains functions particularly useful in controller applications: bit set, bit reset, bit test, rotate and merge, rotate and compare, and cyclic-

Three data types are supported by the Am29117.

redundancy-check (CRC) generation.

- Bit

- Byte

- Word (16-bit)

and the upper half is unchanged. The special case is when the status register is specified as the destination. In the byte mode the LSH (OVR, N, C, Z) of the status register is updated and in the word mode all eight bits of the status register are updated. The status register does not change for save status and test status instructions. In the test status instructions the CT output has the result and the Y-bus is undefined.

In the byte mode data is written into the lower half of the word

The Am29117 Instruction Set can be divided into eleven types of instructions. These are:

- Single Operand Two Operand

- Single Bit Shift Rotate and Merge

- Bit Oriented Rotate by n Bits

- Prioritize Cyclic-Redundancy-Check Status

- No-Op

Rotate and Compare

dressing modes and can be used together with the OP CODES to distinguish the instructions. The following pages describe each of the instruction types in detail. Table 1 illustrates Operand Source-Destination Combinations for each instruction type.

Each instruction type is arbitrarily divided into quadrants. Two

of the sixteen instruction lines decode to four quadrants

labelled from 0 to 3. The quadrants were defined mainly for

convenience in classification of the instruction set and ad-

TABLE 1. OPERAND SOURCE-DESTINATION COMBINATIONS

|                       |                                  |                                  | THATE COULT                                        |

|-----------------------|----------------------------------|----------------------------------|----------------------------------------------------|

| Instruction Type      | Operan                           | d Combinati                      | ons (Note 1)                                       |

|                       | Source                           | (R/S)                            | Destination                                        |

| Single Operand        | A(<br>I<br>D()<br>D()            | Note 2)<br>CC<br>D<br>0E)<br>SE) | RAM<br>ACC<br>Y Bus<br>Status<br>ACC and<br>Status |

|                       | Source (R)                       | _                                | Destination                                        |

| Two Operand           | RAM<br>RAM<br>D<br>D<br>ACC<br>D | ACC<br>I<br>RAM<br>ACC<br>I      | RAM ACC Y Bus Status ACC and Status                |

|                       | Source                           | e (U)                            | Destination                                        |

| Single Bit Shift      | RA<br>AG<br>AG                   | AM<br>CC<br>CC<br>CC             | RAM<br>ACC<br>Y Bus<br>RAM<br>ACC<br>Y Bus         |

|                       | Source                           | e (U)                            | Destination                                        |

| Rotate n Bits         | AC                               | OC<br>OM                         | RAM<br>ACC<br>Y Bus                                |

|                       | Source                           | (R/S)                            | Destination                                        |

| Bit Oriented          | RA<br>AC<br>I                    | CC                               | RAM<br>ACC<br>Y Bus                                |

|                       | Rotated<br>Source (U)            | Mask (S)                         | Non-Rotated<br>Source/<br>Destination (R)          |

| Rotate and Merge      | D<br>D<br>D<br>ACC<br>RAM        | RAM<br> <br>ACC<br>              | ACC<br>ACC<br>RAM<br>RAM<br>RAM<br>ACC             |

| Potato and            | Rotated<br>Source (U)            | Mask (S)                         | Non-Rotated<br>Source/<br>Destination (R)          |

| Rotate and<br>Compare | D<br>D<br>D<br>RAM               | I<br>I<br>ACC<br>I               | RAM<br>RAM<br>ACC                                  |

| Instruction Type    | Operand         | d Combination                                | ons (Note 1)                |

|---------------------|-----------------|----------------------------------------------|-----------------------------|

|                     | Source (R)      | Mask (S)                                     | Destination                 |

| Prioritize (Note 3) | RAM<br>ACC<br>D | RAM<br>ACC<br>I<br>0                         | RAM<br>ACC<br>Y Bus         |

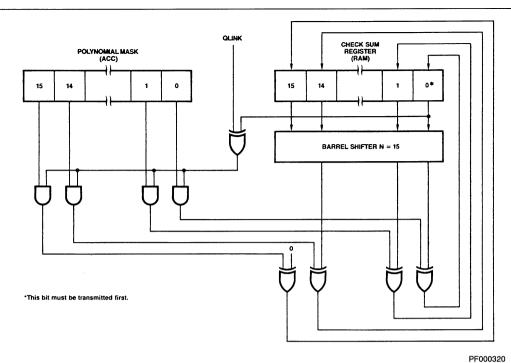

| Cyclic              | Data In         | Destination                                  | Polynomial                  |

| Redundancy<br>Check | QLINK           | RAM                                          | ACC                         |

| No Operation        |                 | _                                            |                             |

|                     |                 | Bits Affect                                  | ted                         |

| Set Reset Status    |                 | OVR, N, C<br>LINK<br>Flag1<br>Flag2<br>Flag3 | s, Z                        |

|                     | Sou             | ırce                                         | Destination                 |

| Store Status        | Sta             | tus                                          | RAM<br>ACC<br>Y Bus         |

|                     | Source (R)      | Source (S)                                   | Destination                 |

| Status Load         | D               | ACC<br>I                                     | Status<br>Status and<br>ACC |

|                     | D               | 1                                            |                             |

|                     | Te              | est Condition                                | n (CT)                      |

|                     |                 | (N⊕OVR) -<br>N⊕OVR                           |                             |

|                     |                 | Z<br>OVR                                     |                             |

| Test Status         |                 | Low                                          |                             |

|                     |                 | C<br>Z+ C                                    |                             |

|                     |                 | N                                            |                             |

|                     |                 | LINK                                         |                             |

|                     |                 | Flag 1<br>Flag 2                             |                             |

|                     |                 | Flag 3                                       |                             |

Notes: 1. When there is no dividing line between the R&S OPERAND or SOURCE and DESTINATION, the two must be used as a given pair. But where there exists such a separation, any combination of them is possible.

- In the SINGLE OPERAND INSTRUCTION, RAM cannot be used when both ACC and STATUS are designated as a DESTINATION.

- 3. In the PRIORITIZE INSTRUCTION, OPERAND and MASK must be different sources.

#### Single Operand Instructions

The Single Operand Instructions contain four indicators: byte or word mode, opcode, source and destination. They are further subdivided into two types. The first type uses RAM as a source or destination or both, and the second type does not use RAM as a source or destination. Both types have different instruction formats as shown below. Under the control of instruction inputs, the desired function is performed on the source and the result is either stored in the specified destina-

tion or placed on the Y-bus or both. For a special case where

8-bit to 16-bit conversion is needed, the Am29117 is capable of extending sign bit (D(SE)) or binary zero (D(0E)) over 16-bits in the word mode. The least significant four bits of the Status Register (OVR, N, C, Z) are affected by the function performed in this category. The most significant bits of status register (FLAG1, FLAG2, FLAG3, LINK) are not affected. The only limitation in this type is that the RAM cannot be used as a source when both ACC and the Status Register are specified as a destination.

#### SINGLE OPERAND FIELD DEFINITIONS

|      | 15  | 14 13 | 12 9   | 8 5      | 4 0         |

|------|-----|-------|--------|----------|-------------|

| SOR  | B/W | Quad  | Opcode | SRC-Dest | RAM Address |

|      |     |       |        |          |             |

| SONR | B/W | Quad  | Opcode | SRC      | Dest        |

#### SINGLE OPERAND INSTRUCTION

|                          | 15               | 14 13             | 12 9                         |                            |                                                              | 8 5                                                                  |                                                                                |                                      |                                                                         | 4 0                              |                           |                                                                 |

|--------------------------|------------------|-------------------|------------------------------|----------------------------|--------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------|----------------------------------|---------------------------|-----------------------------------------------------------------|

| Instruction <sup>1</sup> | B/W <sup>2</sup> | Quad <sup>3</sup> |                              | Opc                        | ode                                                          | R/S <sup>4</sup> Dest <sup>4</sup>                                   |                                                                                |                                      | RAM Address                                                             |                                  |                           |                                                                 |

| SOR                      | 0 = B<br>1 = W   | 10                | 1100<br>1101<br>1110<br>1111 | MOVE<br>COMP<br>INC<br>NEG | SRC → Dest<br>SRC → Dest<br>SRC + 1 → Dest<br>SRC + 1 → Dest | 0000<br>0010<br>0011<br>0100<br>0110<br>0111<br>1000<br>1001<br>1010 | SORA<br>SORY<br>SORS<br>SOAR<br>SODR<br>SOIR<br>SOZR<br>SOZER<br>SOSER<br>SORR |                                      | ACC<br>Y Bus<br>Status<br>RAM<br>RAM<br>RAM<br>RAM<br>RAM<br>RAM<br>RAM | 00000                            | R00<br><br>R31            | RAM Reg 00<br><br>RAM Reg 31                                    |

| Instruction              | B/W              | Quad              |                              | Opc                        | ode                                                          |                                                                      |                                                                                | R/S <sup>4</sup>                     |                                                                         |                                  | Desti                     | nation                                                          |

| SONR                     | 0 = B<br>1 = W   | 11                | 1100<br>1101<br>1110<br>1111 | MOVE<br>COMP<br>INC<br>NEG | SRC → Dest<br>SRC → Dest<br>SRC + 1 → Dest<br>SRC + 1 → Dest | 0100<br>0110<br>0111<br>1000<br>1001<br>1010                         | SOA<br>SOD<br>SOI<br>SOZ<br>SOZE<br>SOSE                                       | ACC<br>D<br>I<br>0<br>D(0E)<br>D(SE) | ;                                                                       | 00000<br>00001<br>00100<br>00101 | NRY<br>NRA<br>NRS<br>NRAS | Y Bus<br>ACC<br>Status <sup>5</sup><br>ACC, Status <sup>5</sup> |

- Notes: 1. The instruction mnemonic designates different instruction formats used in the Am29117. They are useful in microcode assembly.

- B = Byte Mode, W = Word Mode.

- 3. See Instruction Set description.

- 4. R = Source; S = Source; Dest = Destination.

- 5. When status is destination,

Status i ← Yi i = 0 to 3 (Byte mode) i = 0 to 7 (Word mode)

#### Y BUS AND STATUS - SINGLE OPERAND INSTRUCTIONS

| Instruction | Opcode | Description   | B/W   | Y — Bus    | Flag3 | Flag2 | Flag1 | LINK | OVR | N | С | Z |

|-------------|--------|---------------|-------|------------|-------|-------|-------|------|-----|---|---|---|

| SOR         | MOVE   | SRC→Dest      | 0 = B | Y ← SRC    | NC    | NC    | NC    | NC   | 0   | U | 0 | U |

| SONR        | COMP   | SRC → Dest    | 1 = W | Y ← SRC    | NC    | NC    | NC    | NC   | 0   | U | 0 | U |

|             | INC    | SRC +1 → Dest |       | Y ← SRC +1 | NC    | NC    | NC    | NC   | U   | U | U | U |

|             | NEG    | SRC +1 → Dest |       | Y ← SRC +1 | NC    | NC    | NC    | NC   | U   | U | U | U |

SRC = Source

U = Update

NC = No Change

0 = Reset

1 = Set

i = 0 to 15 when not specified

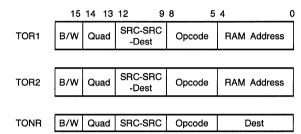

#### Two Operand Instructions

The Two Operand Instructions contain five indicators: byte or word mode, opcode, R source, S source, and destination. They are further subdivided into two types. The first type uses RAM as the source and/or destination and the second type does not use RAM as source or destination. The first type has two formats; the only difference is in the quadrant. Under the control of instruction inputs, the desired function is performed on the specified sources and the result is stored in the

specified destination or placed on the Y-bus or both. The least significant four bits of the status register (OVR, N, C, Z) are affected by the arithmetic functions performed and only the N and Z bits are affected by the logical functions performed. The OVR and C bits of the status register are forced to ZERO for logical functions. Add with carry and Subtract with carry instructions are useful for Multiprecision Add or Subtract.

#### TWO OPERAND FIELD DEFINITIONS

#### TWO OPERAND INSTRUCTIONS

| Instruction | B/W            | Quad |                                                                |                                                                               | R <sup>1</sup>                                 | S <sup>1</sup>                                        | Dest <sup>1</sup>                                          |                                                                                              | Opcode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       | RAM            | Address                      |

|-------------|----------------|------|----------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------|------------------------------|

| TOR1        | 0 = B<br>1 = W | 00   | 0000<br>0010<br>0011<br>1000<br>1010<br>1011<br>11100<br>11110 | TORAA<br>TORIA<br>TODRA<br>TORAY<br>TORIY<br>TODRY<br>TORAR<br>TORIR<br>TODRR | RAM<br>RAM<br>D<br>RAM<br>RAM<br>D<br>RAM<br>D | ACC<br>I<br>RAM<br>ACC<br>I<br>RAM<br>ACC<br>I<br>RAM | ACC<br>ACC<br>ACC<br>Y Bus<br>Y Bus<br>Y Bus<br>RAM<br>RAM | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1010<br>1011 | SUBR S minus R SUBRC2 S minus R with carry SUBS R minus S SUBSC2 R minus S ADDC R plus S with carry AND R • S EXOR R • B • S OR R + S OR R + S EXOR R ⊕ S                                                                                                                                                                                                                                                                                                                              | 00000 | R00<br><br>R31 | RAM Reg 00<br><br>RAM Reg 31 |

| Instruction | B/W            | Quad |                                                                |                                                                               | R <sup>1</sup>                                 | S <sup>1</sup>                                        | Dest <sup>1</sup>                                          |                                                                                              | Opcode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       | RAM            | Address                      |

| TOR2        | 0 = B<br>1 = W | 10   | 0001<br>0010<br>0101                                           | TODAR<br>TOAIR<br>TODIR                                                       | D<br>ACC<br>D                                  | ACC I                                                 | RAM<br>RAM<br>RAM                                          | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1010         | SUBR S minus R SUBRO2 S minus R with carry SUBS R minus S SUBSC2 R minus S ADDC R plus S ADDC R Plus S NAND R S SUBSC2 NOR R S SUBSC2 R minus S R Plus S R Plus S NAND R S SUBSC2 R R R S SUBSC2 R R R S SUBSC2 R R R S S SUBSC2 R R R R S S S R R R R R R R R R R R R | 00000 | R00<br><br>R31 | RAM Reg 00<br><br>RAM Reg 31 |

Notes: 1. R = Source

S = Source

Dest = Destination

2. During subtraction the carry is interpreted as borrow.

#### TWO OPERAND INSTRUCTIONS

| Instruction               | B/W                                                    | Quad                                                                       |                                                                           |                                        | R <sup>1</sup> | S <sup>1</sup> |                                                                                      | Op                                                           | code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                  | Des                       | tination                                                        |

|---------------------------|--------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------|----------------|----------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------|-----------------------------------------------------------------|

| TONR                      | 0 = B<br>1 = W                                         | 11                                                                         | 0001<br>0010<br>0101                                                      | TODA<br>TOAI<br>TODI                   |                | ACC I          | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0111<br>1000<br>1001<br>1010<br>1011 | SUBR SUBSC <sup>3</sup> ADD ADDC  AND NAND EXOR NOR OR EXNOR | S minus R S minus R with carry R minus S with carry R plus S with carry R plus S with carry R s S R minus S with carry R S R S R R S R R S R R S R R S R R S R R S R R S R R S R R S R R S R S R R S R R S R R S R R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S R S | 00000<br>00001<br>00100<br>00101 | NRY<br>NRA<br>NRS<br>NRAS | Y Bus<br>ACC<br>Status <sup>2</sup><br>ACC, Status <sup>2</sup> |

| 2. V<br>S<br>3. D<br>4. C | = Sourd<br>then status it<br>tatus it<br>turing second | ce<br>atus is c<br>- Y <sub>i</sub> i = 0<br>i = 0<br>ubtraction<br>8   C7 | lestination<br>to 3 (By<br>to 7 (Wo<br>n the car<br>(Byte mon<br>5 (Word) | te mode<br>ord mod<br>ry is int<br>de) | le)            | d as bo        | orrow.                                                                               |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                  |                           |                                                                 |

#### Y BUS AND STATUS CONTENTS - TWO OPERAND INSTRUCTIONS

| Instruction  | Opcode | Description          | B/W   | Y - Bus                             | Flag3 | Flag2 | Flag<br>1 | LINK | OVR | N | С | z |

|--------------|--------|----------------------|-------|-------------------------------------|-------|-------|-----------|------|-----|---|---|---|

|              | SUBR   | S minus R            | 0 = B | Y←S+R+1                             | NC    | NC    | NC        | NC   | U   | U | U | U |

|              | SUBRC  | S minus R with carry | 1 = w | Y ← S + R + QC                      | NC    | NC    | NC        | NC   | υ   | U | U | υ |

|              | SUBS   | R minus S            |       | Y←R+S+1                             | NC    | NC    | NC        | NC   | U   | U | U | U |

| TOR1<br>TOR2 | SUBSC  | R minus S with carry |       | Y ← R + S + QC                      | NC    | NC    | NC        | NC   | U   | U | U | U |

| TONR         | ADD    | R plus S             |       | Y←R+S                               | NC    | NC    | NC        | NC   | U   | U | U | U |

|              | ADDC   | R plus S with carry  |       | Y ← R + S + QC                      | NC    | NC    | NC        | NC   | υ   | U | U | U |

|              | AND    | R∙S                  |       | Y←R <sub>i</sub> AND S <sub>i</sub> | NC    | NC    | NC        | NC   | 0   | U | 0 | U |

|              | NAND   | R·S                  |       | Yi←Ri NAND Si                       | NC    | NC    | NC        | NC   | 0   | C | 0 | U |

|              | EXOR   | R⊕S                  |       | Yi←Ri EXOR Si                       | NC    | NC    | NC        | NC   | 0   | C | 0 | С |

|              | NOR    | R+S                  |       | Yi←Ri NOR Si                        | NC    | NC    | NC        | NC   | 0   | U | 0 | U |

|              | OR     | R+S                  |       | Yi←Ri OR Si                         | NC    | NC    | NC        | NC   | 0   | U | 0 | U |

|              | EXNOR  | R⊕S                  |       | Yi←Ri EXNOR Si                      | NC    | NC    | NC        | NC   | 0   | 0 | 0 | U |

U = Update

NC = No Change

0 = Reset

1 = Set

i = 0 to 15 when not specified

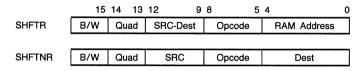

#### Single Bit Shift Instructions

The Single Bit Shift Instructions contain four indicators: byte or word mode, direction and shift linkage, source and destination. They are further subdivided into two types. The first type uses RAM as the source and/or destination and the second type does not use RAM as source or destination. Under the control of the instruction inputs, the desired shift function is performed on the specified source and the result is stored in the specified destination or placed on the Y-bus or both. The direction and shift linkage indicator defines the direction of the shift (up or down) as well as what will be shifted into the vacant bit. On a shift-up instruction, the LSB may be loaded with ZERO, ONE,

or the Link-Status bit (QLINK). The MSB is loaded into the Link-Status bit as shown in Figure 2. On a shift-down instruction, the MSB may be loaded with ZERO, ONE, the contents of the Status Carry flip-flop, (QC), the Exclusive-OR of the Negative-Status bit and the Overflow-Status bit (QN  $\oplus$  QOVR) or the Link-Status bit. The LSB is loaded into the Link-Status bit as shown in Figure 3. The N and Z bits of the Status register are affected but the OVR and C bits are forced to ZERO. The Shift-Down with QN  $\oplus$  QOVR is useful for Two's Complement multiplication.

#### SINGLE BIT SHIFT FIELD DEFINITIONS:

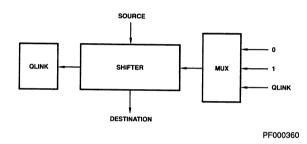

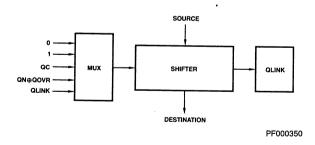

Figure 2. Shift Up Function

Figure 3. Shift Down Function

#### SINGLE BIT SHIFT INSTRUCTIONS

#### SINGLE BIT SHIFT

| Instruction | B/W            | Quad |              |              | U <sup>1</sup> | Dest <sup>1</sup> |                                                              | Орс                                                                   | ode                                                    |                                                     |                    | RAM            | Address                      |  |  |

|-------------|----------------|------|--------------|--------------|----------------|-------------------|--------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------|--------------------|----------------|------------------------------|--|--|

| SHFTR       | 0 = B<br>1 = W | 10   | 0110<br>0111 | SHRR<br>SHDR | RAM<br>D       | RAM<br>RAM        | 0000<br>0001<br>0010<br>0100<br>0101<br>0110<br>0111<br>1000 | SHUPZ<br>SHUP1<br>SHUPL<br>SHDNZ<br>SHDN1<br>SHDNL<br>SHDNC<br>SHDNOV | Up<br>Up<br>Up<br>Down<br>Down<br>Down<br>Down<br>Down | QC                                                  | 00000<br><br>11111 | R00<br><br>R31 | RAM Reg 00<br><br>RAM Reg 31 |  |  |

| Instruction | B/W            | Quad |              |              | U <sup>1</sup> |                   |                                                              | Орс                                                                   | ode                                                    |                                                     |                    | Des            | stination                    |  |  |

| SHFTNR      | 0 = B<br>1 = W | 11   | 0110<br>0111 | SHA<br>SHD   | ACC<br>D       |                   | 0000<br>0001<br>0010<br>0100<br>0101<br>0110<br>0111<br>1000 | SHUPZ<br>SHUP1<br>SHUPL<br>SHDNZ<br>SHDN1<br>SHDNL<br>SHDNC<br>SHDNOV | Up<br>Up<br>Up<br>Down<br>Down<br>Down<br>Down<br>Down | 0<br>1<br>QLINK<br>0<br>1<br>QLINK<br>QC<br>QN⊕QOVR | 00000<br>00001     | NRY<br>NRA     | Y Bus<br>ACC                 |  |  |

Note 1. U = Source Dest = Destination

#### Y BUS AND STATUS - SINGLE BIT SHIFT INSTRUCTIONS

| Instruction | Opcode                   | Description                           | B/W   | Y - Bus                                                                                                                                                  | Flag3 | Flag2 | Flag1 | LINK               | OVR | N                 | С | z |

|-------------|--------------------------|---------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------------------|-----|-------------------|---|---|

| 1.4.1.499   | SHUPZ<br>SHUP1           | Up 0<br>Up 1                          | 1 = W | $Y_i \leftarrow SRC_{i-1}$ , $i = 1$ to 15;<br>$Y_0 \leftarrow Shift$ Input                                                                              | NC    | NC    | NC    | SRC <sub>15*</sub> | 0   | SRC <sub>14</sub> | 0 | U |

| SHR<br>SHNR | SHUPL                    | Up QLINK                              | 0 = B | $Y_i \leftarrow SRC_{i-1}$ , $i = 1$ to 7;<br>$Y_0 \leftarrow Shift Input$ ;<br>$Y_8 \leftarrow SRC_7$ , $Y_i \leftarrow SRC_{i-9}$<br>for $i = 9$ to 15 | NC    | NC    | NC    | SRC <sub>7*</sub>  | 0   | SRC <sub>6</sub>  | 0 | U |

|             | SHDNZ<br>SHDN1           | Down 0<br>Down 1                      | 1 = W | $Y_i \leftarrow SRC_{i+1}$ , $i = 0$ to 14;<br>$Y_{15} \leftarrow Shift Input$                                                                           | NC    | NC    | NC    | SRC <sub>0</sub> ∗ | 0   | Shift<br>Input    | 0 | U |

|             | SHDNL<br>SHDNC<br>SHCNOV | Down QLINK<br>Down QC<br>Down QN⊕QOVF | 0 = B | $Y_i - SRC_{i+1}$ , $i = 0$ to 6;<br>$Y_i - SRC_{i-7}$ , $i = 8$ to 14;<br>$Y_{7.15} - Shift$ Input                                                      | NC    | NC    | NC    | SRC <sub>0</sub> ∗ | 0   | Shift<br>Input    | 0 | υ |

\*Shifted Output is loaded into the QLINK.

SRC = Source

U = Update

NC = No Change

0 = Reset

1 = Set

i = 0 to 15 when not specified

#### **Bit Oriented Instructions**

The Bit Oriented Instructions contain four indicators: byte or word mode, operation, source/destination, and the bit position of the bit to be operated on (Bit 0 is the least significant bit). They are further subdivided into two types. The first type uses the RAM as both source and destination and has two kinds of formats which differ only by quadrant. The second type does not use the RAM as a source or a destination. Under the control of the instruction inputs, the desired function is performed on the specified source and the result is stored in the specified destination or placed on the Y-bus or both. The operations which can be performed are: Set Bit n which forces the n<sup>th</sup> bit to a ONE leaving other bits unchanged: Reset Bit n

which forces the  $n^{th}$  bit to ZERO leaving the other bits unchanged; Test Bit n, which sets the ZERO Status Bit depending on the state of bit n leaving all the bits unchanged; Load  $2^n$ , which loads ONE in Bit position n and ZERO in all other bit positions; Load  $\overline{2}^n$  which loads ZERO in bit position and ONE in all other bit positions; increment by  $2^n$ , which adds  $2^n$  to the operand; and decrement by  $2^n$  which subtracts  $2^n$  from the operand. For all the Load, Set, Reset and Test instructions, the N and Z bits are affected and OVR and C bit of the Status register are forced to ZERO. For all arithmetic instructions the LSH (OVR, C, N, Z bits) of the Status register is affected.

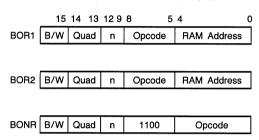

#### **BIT ORIENTED FIELD DEFINITIONS**

#### **BIT ORIENTED INSTRUCTIONS**

| Instruction | B/W            | Quad | n        |                              | (                               | Opcode                                                                                                      |                                                                                                          | RAM                                                                                 | Address                                                                                                                                                                                                                                                                                                     |  |

|-------------|----------------|------|----------|------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BOR1        | 0 = B<br>1 = W | 11   | 0 to 15. | 1101<br>1110<br>1111         | SETNR<br>RSTNR<br>TSTNR         | Set RAM, bit n<br>Reset RAM, bit n<br>Test RAM, bit n                                                       | 00000<br><br>11111                                                                                       | R00<br><br>R31                                                                      | RAM Reg 00<br><br>RAM Reg 31                                                                                                                                                                                                                                                                                |  |

| Instruction | B/W            | Quad | n        |                              |                                 | Opcode                                                                                                      |                                                                                                          | RAM Address                                                                         |                                                                                                                                                                                                                                                                                                             |  |

| BOR2        | 0 = B<br>1 = W | 10   | 0 to 15  | 1100<br>1101<br>1110<br>1111 | LD2NR<br>LDC2NR<br>A2NR<br>S2NR | 2 <sup>n</sup> →RAM<br>2 <sup>n</sup> →RAM<br>RAM plus 2 <sup>n</sup> →RAM<br>RAM minus 2 <sup>n</sup> →RAM | 00000<br><br>11111                                                                                       | R00<br><br>R31                                                                      | RAM Reg 00<br><br>RAM Reg 31                                                                                                                                                                                                                                                                                |  |

| Instruction | B/W            | Quad | n        |                              |                                 |                                                                                                             |                                                                                                          | Opcode                                                                              |                                                                                                                                                                                                                                                                                                             |  |

| BONR        | 0 = B<br>1 = W | 11   | 0 to 15  | 1100                         |                                 |                                                                                                             | 00000<br>00001<br>00010<br>00100<br>00101<br>00111<br>10000<br>10001<br>10100<br>10101<br>10110<br>10110 | TSTNA RSTNA RSTNA A2NA S2NA LD2NA LD2NA LDC2NA TSTND RSTND RSTND A2NDY S2NDY LDC2NY | Test ACC, bit n Reset ACC, bit n Set ACC, bit n ACC plus 2 <sup>n</sup> → ACC ACC minus 2 <sup>n</sup> → ACC 2 <sup>n</sup> → ACC 2 <sup>n</sup> → ACC Test D, bit n Reset D, bit n Set D, bit n D plus 2 <sup>n</sup> → Y BUS D minus 2 <sup>n</sup> → Y Bus 2 <sup>n</sup> → Y Bus 2 <sup>n</sup> → Y Bus |  |

#### **BIT ORIENTED INSTRUCTIONS** Y BUS AND STATUS - BIT ORIENTED INSTRUCTIONS

| Instruction | Opcode         | Description                       | B/W | Y - Bus                                                                                                                    | Flag3    | Flag2    | Flag1    | LINK     | OVR | N | С | z |

|-------------|----------------|-----------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|-----|---|---|---|

| BOR1        | SETNR<br>RSTNR | Set RAM Bit n<br>Reset RAM, Bit n |     | Y <sub>i</sub> ←RAM <sub>i</sub> for i≠n; Y <sub>n</sub> ←1<br>Y <sub>i</sub> ←RAM <sub>i</sub> for i≠n; Y <sub>n</sub> ←0 | NC<br>NC | NC<br>NC | NC<br>NC | NC<br>NC | 0   | U | 0 | 0 |

|             | TSTNR          | Test RAM, Bit n                   |     | Y <sub>i</sub> ←0 for i≠n; Y <sub>n</sub> ←SRC <sub>n</sub>                                                                | NC       | NC       | NC       | NC       | 0   | U | 0 | U |

|             | LD2NR          | 2 <sup>n</sup> →RAM               |     | $Y_i \leftarrow 0$ for $i \neq n$ ; $Y_n \leftarrow 1$                                                                     | NC       | NC       | NC       | NC       | 0   | U | 0 | 0 |

| BOR2        | LDC2NR         | 2 <sup>n</sup> → RAM              |     | $Y_i \leftarrow 1$ for $i \neq n$ ; $Y_n \leftarrow 0$                                                                     | NC       | NC       | NC       | NC       | 0   | J | 0 | 0 |

| BUH2        | A2NR           | RAM + 2 <sup>n</sup> → RAM        |     | Y←RAM + 2 <sup>n</sup>                                                                                                     | NC       | NC       | NC       | NC       | U   | U | J | U |

|             | S2NR           | RAM – 2 <sup>n</sup> → RAM        |     | Y←RAM – 2 <sup>n</sup>                                                                                                     | NC       | NC       | NC       | NC       | U   | U | U | U |

|             | TSTNA          | Test ACC, Bit n                   |     | $Y_i \leftarrow 0$ for $i \neq n$ ; $Y_n \leftarrow ACC_n$                                                                 | NC       | NC       | NC       | NC       | 0   | כ | 0 | U |

|             | RSTNA          | Reset ACC, Bit n                  |     | $Y_i \leftarrow ACC_i$ for $i \neq n$ ; $Y_n \leftarrow 0$                                                                 | NC       | NC       | NC       | NC       | 0   | כ | 0 | U |

|             | SETNA          | Set ACC, Bit n                    |     | $Y_i \leftarrow ACC_i$ for $i \neq n$ ; $Y_n \leftarrow 1$                                                                 | NC       | NC       | NC       | NC       | 0   | ט | 0 | 0 |

|             | A2NA           | ACC + 2 <sup>n</sup> →ACC         |     | Y←ACC + 2 <sup>n</sup>                                                                                                     | NC       | NC       | NC       | NC       | U   | ح | ح | U |

|             | S2NA           | ACC – 2 <sup>n</sup> → ACC        |     | Y ← ACC – 2 <sup>n</sup>                                                                                                   | NC       | NC       | NC       | NC       | U   | כ | כ | U |

|             | LD2NA          | 2 <sup>n</sup> →ACC               |     | $Y_i \leftarrow 0$ for $i \neq n$ ; $Y_n \leftarrow 1$                                                                     | NC       | NC       | NC       | NC       | 0   | ט | 0 | 0 |

| BONR        | LDC2NA         | 2 <sup>Π</sup> → ACC              |     | $Y_i \leftarrow 1$ for $i \neq n$ ; $Y_n \leftarrow 0$                                                                     | NC       | NC       | NC       | NC       | 0   | ٦ | 0 | 0 |

| BONH        | TSTND          | Test D, Bit n                     |     | $Y_i \leftarrow 0$ for $i \neq n$ ; $Y_n \leftarrow D_n$                                                                   | NC       | NC       | NC       | NC       | 0   | J | 0 | U |

|             | RSTND          | Reset D, Bit n*                   |     | $Y_i \leftarrow D_i$ for $i \neq n$ ; $Y_n \leftarrow 0$                                                                   | NC       | NC       | NC       | NC       | 0   | ٥ | 0 | U |

|             | SETND          | Set D, Bit n*                     |     | $Y_i \leftarrow D_i$ for $i \neq n$ ; $Y_n \leftarrow 1$                                                                   | NC       | NC       | NC       | NC       | 0   | J | 0 | 0 |

|             | A2NDY          | D + 2 <sup>n</sup> → Y Bus        | 1   | Y←D + 2 <sup>n</sup>                                                                                                       | NC       | NC       | NC       | NC       | U   | ٦ | ٦ | U |

|             | S2NDY          | D-2 <sup>n</sup> →Y Bus           | 1   | Y ← D − 2 <sup>n</sup>                                                                                                     | NC       | NC       | NC       | NC       | U   | ٦ | ٥ | U |

|             | LD2NY          | 2 <sup>n</sup> →Y Bus             | 1   | $Y_i \leftarrow 0$ for $i \neq n$ ; $Y_n \leftarrow 1$                                                                     | NC       | NC       | NC       | NC       | 0   | ح | 0 | 0 |

|             | LDC2NY         | 2 <sup>Π</sup> →Y Bus             | 1   | $Y_i \leftarrow 1$ for $i \neq n$ ; $Y_n \leftarrow 0$                                                                     | NC       | NC       | NC       | NC       | 0   | ٦ | 0 | 0 |

SRC = Source

U = Update

NC = No Change

0 = Reset

1 = Set

i = 0 to 15 when not specified

<sup>\*</sup>Destination is not D Latch but Y Bus.

#### Rotate by n Bits Instructions

The Rotate by n Bits Instructions contain four indicators; byte or word mode, source, destination and the number of places the source is to be rotated. They are further subdivided into two types. The first type uses RAM as a source and/or a destination and the second type does not use RAM as a source or destination. The first type has two different formats and the only difference is in the quadrant. The second type has only one format as shown in the table. Under the control of instruction inputs, the n indicator specifies the number of bit positions the source is to be rotated up (0 to 15), and the result

is either stored in the specified destination or placed on the Ybus or both. An example of this instruction is given in Figure 4. In the Word mode, all 16 bits are rotated up; while in the Byte mode, only the lower 8 bits (0-7) are rotated up. In the Word mode, a rotate up by n bits is equivalent to a rotate down by (16-n) bits. Similarly, in the Byte mode a rotate up by n bits is equivalent to a rotate down by (8-n) bits. The N and Z bits of the Status Register are affected and OVR and C bits are forced to ZERO.

| EXAMPLE: | n = 4. | Word | Mode |

|----------|--------|------|------|

|----------|--------|------|------|

| Source<br>Destination | 0001<br>0011 | 0011<br>0111 | 0111<br>1111 | 1111<br>0001 |

|-----------------------|--------------|--------------|--------------|--------------|

| EXAMPLE: r            | 1 = 4, Byte  | e Mode       |              |              |

| Source                | 0001         | 0011         | 0111         | 1111         |

| Destination           | 0001         | 0011         | 1111         | 0111         |

#### ROTATE BY n BITS FIELD DEFINITIONS

|       | 15  | 14 13 | 12 9 | 8 5      | 4 0         |

|-------|-----|-------|------|----------|-------------|

| ROTR1 | B/W | Quad  | n    | SRC-Dest | RAM Address |

|       |     |       |      |          |             |

ROTR2 B/W Quad SRC-Dest RAM Address

Figure 4. Rotate by n Example

| ROTNR | B/W | Quad | n | 1100 | SRC-Dest |

|-------|-----|------|---|------|----------|

|       |     |      |   |      |          |

#### ROTATE BY n BITS INSTRUCTIONS

| Instruction | B/W            | Quad | n       |                      |                      | U <sup>1</sup>    | Dest <sup>1</sup>   |                                  | RAM                          | Address              | S                            |

|-------------|----------------|------|---------|----------------------|----------------------|-------------------|---------------------|----------------------------------|------------------------------|----------------------|------------------------------|

| ROTR1       | 0 = B<br>1 = W | 00   | 0 to 15 | 1100<br>1110<br>1111 | RTRA<br>RTRY<br>RTRR | RAM<br>RAM<br>RAM | ACC<br>Y Bus<br>RAM | 00000                            | R00<br>R31                   | RAM R                | ř.                           |

| Instruction | B/W            | Quad | n       |                      |                      | U <sup>1</sup>    | Dest <sup>1</sup>   | RAM Address                      |                              |                      | S                            |

| ROTR2       | 0 = B<br>1 = W | 01   | 0 to 15 | 0000<br>0001         | RTAR<br>RTDR         | ACC<br>D          | RAM<br>RAM          | 00000                            | R00<br><br>R31               | RAM R                | . ·                          |

| Instruction | B/W            | Quad | n       |                      |                      |                   |                     |                                  |                              | U <sup>1</sup>       | Dest <sup>1</sup>            |

| ROTNR       | 0 = B<br>1 = W | . 11 | 0 to 15 | 1100                 |                      |                   |                     | 11000<br>11001<br>11100<br>11101 | RTDY<br>RTDA<br>RTAY<br>RTAA | D<br>D<br>ACC<br>ACC | Y Bus<br>ACC<br>Y Bus<br>ACC |

Note: 1. U = Source Dest = Destination

#### Y BUS AND STATUS - ROTATE BY n BITS INSTRUCTIONS

| Instruction    | Op-<br>code | B/W   | Y – Bus                                                          | Flag3 | Flag2 | Flag1 | LINK | OVR | N                   | С | z |

|----------------|-------------|-------|------------------------------------------------------------------|-------|-------|-------|------|-----|---------------------|---|---|

| ROTR1          |             | 1 = W | Y <sub>i</sub> ←SRC <sub>(i-n)mod16</sub>                        | NC    | NC    | NC    | NC   | 0   | SRC <sub>15-n</sub> | 0 | U |

| ROTR2<br>ROTNR |             | 0 = B | $Y_{i} \leftarrow SRC_{i+8} = SRC_{(i-n)mod8}$<br>for i = 0 to 7 | NC    | NC    | NC    | NC   | 0   | SRC <sub>8-n</sub>  | 0 | U |

SRC = Source

U = No Change

0 = Reset

1 = Set

i = 0 to 15 when not specified

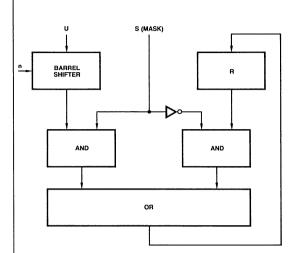

#### **Rotate and Merge Instruction**

byte or word mode, rotated source, non-rotated source/ destination, mask and the number of bit positions a source is to be rotated. The function performed by the Rotate and Merge instruction is illustrated in Figure 5. The rotated source, U, is rotated up by the Barrel Shifter n places. The mask input then selects, on a bit by bit basis, the rotated U input or R

The Rotate and Merge Instructions contain five indicators:

input. A ZERO in bit i of the mask will select the  $i^{th}$  bit of the R input as the  $i^{th}$  output bit, while ONE in bit i will select the  $i^{th}$  rotated U input as the output bit. The output word is stored in the non-rotated operand location. The N and Z bits are affected. The OVR and C bits of the Status register are forced to ZERO. An example of this instruction is given in Figure 6.

#### **ROTATE AND MERGE FIELD DEFINITIONS:**

#### EXAMPLE: n = 4. Word Mode

| U           | 0011 | 0001 | 0101 | 0110 |

|-------------|------|------|------|------|

| Rotated U   | 0001 | 0101 | 0110 | 0011 |

| R           | 1010 | 1010 | 1010 | 1010 |

| Mask (S)    | 0000 | 1111 | 0000 | 1111 |

| Destination | 1010 | 0101 | 1010 | 0011 |

|             |      |      |      |      |

Figure 6. Rotate and Merge Example

Figure 5. Rotate and Merge Function

#### ROTATE AND MERGE INSTRUCTION

PF000630

| Instruction | B/W            | Quad | n       |                                              |                                              | U                              | R/Dest                                 | S                    |                    | RAM A          | ddress                       |

|-------------|----------------|------|---------|----------------------------------------------|----------------------------------------------|--------------------------------|----------------------------------------|----------------------|--------------------|----------------|------------------------------|

| ROTM        | 0 = B<br>1 = W | 01   | 0 to 15 | 0111<br>1000<br>1001<br>1010<br>1100<br>1110 | MDAI<br>MDAR<br>MDRI<br>MDRA<br>MARI<br>MRAI | D<br>D<br>D<br>D<br>ACC<br>RAM | ACC<br>ACC<br>RAM<br>RAM<br>RAM<br>ACC | RAM<br>I<br>ACC<br>I | 00000<br><br>11111 | R00<br><br>R31 | RAM Reg 00<br><br>RAM Reg 31 |

U = Rotated Source

R/Dest = Non-Rotated Source and Destination

S = Mask

#### Y BUS AND STATUS - ROTATE AND MERGE INSTRUCTIONS

| Instruction | Opcode | B/W   | Y - Bus                                                                                                                   | Flag3 | Flag2 | Flag1 | LINK | OVR | N | С | Z |

|-------------|--------|-------|---------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|-----|---|---|---|

| ROTM        |        | 1=W   | Y <sub>i</sub> ←(Non Rot Op) <sub>i</sub> ·(mask) <sub>i</sub> +<br>(Rot Op) <sub>(i-n)mod 16</sub> ·(mask) <sub>i</sub>  | NC    | NC    | NC    | NC   | 0   | U | 0 | U |

| HOIM        |        | 0 = B | Y <sub>i</sub> ←(Non Rot Op) <sub>i</sub> ·(mask) <sub>i</sub> +<br>(Rot Op) <sub>(i - n)mod 8</sub> ·(mask) <sub>i</sub> | NC    | NC    | NC    | NC   | 0   | U | 0 | U |

U = Update

NC = No Change

0 = Reset

1 = Set

i = 0 to 15 when not specified

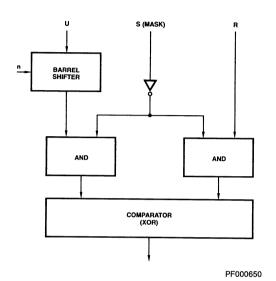

#### **Rotate and Compare Instructions**

The Rotate and Compare Instructions contain five indicators: byte or word mode, rotated source, non-rotated source, mask, and the number of bit positions the rotated source is to be rotated up. Under the control of instruction inputs, the function performed by the Rotate and Compare instruction is illustrated in Figure 7. The rotated operand is rotated by the Barrel Shifter n places. The mask is inverted and ANDed on a bit-by-bit basis with the output of the Barrel Shifter and R input. Thus, a ONE in the mask input eliminates that bit from the comparison. A ZERO allows the comparison. If the comparison passes, the Zero flag is set. If it fails, the Zero flag is reset. The N and Z bit are affected. The OVR and C bits of the Status register are forced to ZERO. An example of this instruction is given in Figure 8.

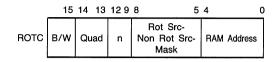

#### ROTATE AND COMPARE FIELD DEFINITIONS

EXAMPLE: n = 4, Word Mode

| U              | 0011 | 0001 | 0101 | 0110 |