# Am29C334

CMOS Four-Port Dual-Access Register File

#### DISTINCTIVE CHARACTERISTICS

• 64 x 18 Bit Wide Register File

The Am29C334 is a 64 x 18-bit, dual-access RAM with two read ports and two write ports.

- Pipelined Data Path

- The Am29C334 can be configured to support either a non-pipelined data path (similar to the Am29334) or a pipelined data path.

- Cascadable

The Am29C334 is cascadable to support either wider word widths, deeper register files, or both.

- Built in Forwarding Logic

- The Am29C334 provides simultaneous read/write access to the same address for double pipelined systems.

- Byte Parity Storage

- Width of 18 bits facilitates byte parity storage for each port and provides consistency with the Am29C332 32-bit ALU.

- Byte Write Capability

Individual byte-write enables allow byte or full word write.

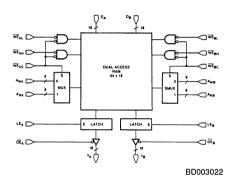

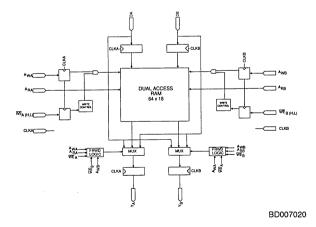

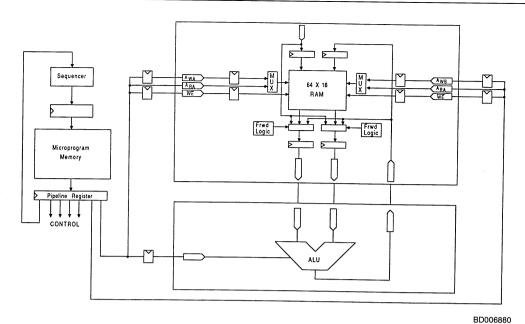

# **BLOCK DIAGRAMS**

Non-Pipelined Mode

**Pipelined Mode**

# **GENERAL DESCRIPTION**

The Am29C334 is a 64-word by 18-bit dual-access RAM with two read ports and two write ports. Two independent, simultaneous accesses are possible and each access can be either a read or a write. It is designed to be used in a system that requires as many as two reads and two writes in a single cycle. The device can be configured to support either a non-pipelined data path or a pipelined data path.

The Am29C334 is also fully compatible with the bipolar Am29334. When the device is connected to the pinout specified for the Am29334, it will appear as a 64-word by 18-bit array without support for pipelined operation. The pipelined operation of the Am29C334 is made possible because of the availability of unused power pins not required by the CMOS part. The pipelined operation is disabled by attaching the  $\overline{\text{PIPE}}$  pin to  $V_{CC}$ .

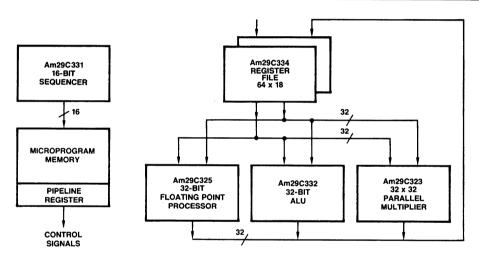

# RELATED AMD PRODUCTS

| Part No. | Description                                 |

|----------|---------------------------------------------|

| Am29C323 | CMOS 32-Bit Parallel Multiplier             |

| Am29325  | 32-Bit Floating Point Processor             |

| Am29C325 | CMOS 32-Bit Floating Point Processor        |

| Am29331  | 16-Bit Microprogram Sequencer               |

| Am29C331 | CMOS 16-Bit Microprogram Sequencer          |

| Am29332  | 32-Bit Extended Function ALU                |

| Am29C332 | CMOS 32-Bit Extended Function ALU           |

| Am29334  | 64 x 18 Four-Port Dual-Access Register File |

| Am29337  | 16-Bit Bounds Checker                       |

| Am29338  | 128 x 9 Byte Queue                          |

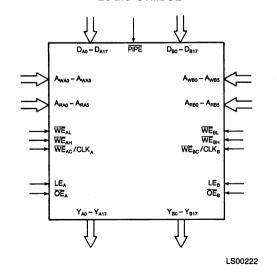

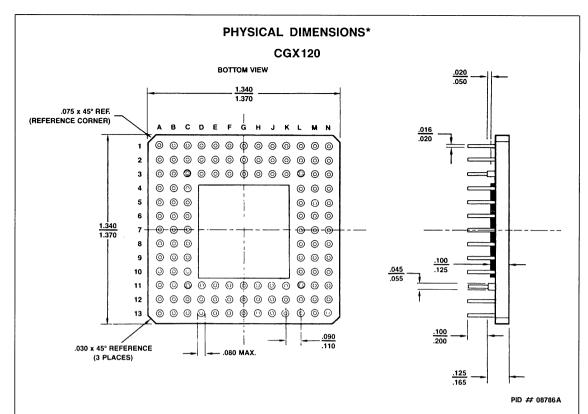

# **CONNECTION DIAGRAM**

120 Lead PGA\*

|    |      | В    | c    | D    | E    | F    | a    | н    | J    | ĸ    | L    | M    | N      |

|----|------|------|------|------|------|------|------|------|------|------|------|------|--------|

| 1  | AWA2 | ARA2 | AWA1 | DAGO | DA02 | DA04 | DAOS | DAGS | DA12 | DA16 | LEA  | WEAC | WEAL   |

| 2  | ARA3 | AWA3 | ARA1 | ARA0 | DA03 | DA05 | DA07 | DA10 | DA13 | DA15 | ARA5 | AWA5 | WEAH   |

| 3  | AWA4 | ARA4 | YB00 | AWAO | DA01 | GND  | DAGS | PIPE | DA11 | DA14 | DA17 | ARB4 | AWB4   |

| 4  | YB01 | YB02 | Y803 |      |      |      |      |      |      |      | YA00 | YAOI | YA02   |

| 5  | GNDA | YB04 | YBOS |      |      |      |      |      |      |      | YA03 | YA04 | GNDA   |

| •  | Y807 | YB06 | VCCA |      |      |      |      |      |      |      | ŌĒĀ  | YA06 | YAOS   |

| 7  | YBOS | YB09 | YB10 |      |      |      |      |      |      |      | YA07 | 80AY | YAOD   |

|    | YB12 | YB11 | ŌĒB  |      |      |      |      |      |      |      | VCCA | YA11 | YA10   |

| 9  | GNDA | YB13 | YB14 |      |      |      |      |      |      |      | YA12 | YA13 | GNDA   |

| 10 | Y815 | YB16 | YB17 |      |      |      |      |      |      |      | YA14 | YA15 | YA16   |

| 11 | WEBL | WEBH | DB01 | DB04 | vcc  | DBOS | DBOS | DB15 | GND  | ARBO | YA17 | ARB3 | AWB3   |

| 12 | WEBC | LEB  | DB00 | D803 | vcc  | DB05 | DB11 | DB12 | GND  | DB17 | AWBO | AWB2 | ARB2   |

| 13 | AWBS | ARBS | 0807 | D802 | vcc  | DB06 | D810 | D814 | GND  | DB16 | DB13 | ARB1 | AWB1   |

|    |      |      |      |      |      |      |      |      |      |      |      | CE   | 010320 |

CD010320

# TABLE OF INTERCONNECTIONS

(Sorted by Pin Name)

| PIN NAME         | PIN<br>NO. | PAD<br>NO. | PIN NAME         | PIN<br>NO. | PAD<br>NO. | PIN NAME                           | PIN<br>NO. | PAD<br>NO. | PIN NAME         | PIN<br>NO. | PAD<br>NO. |

|------------------|------------|------------|------------------|------------|------------|------------------------------------|------------|------------|------------------|------------|------------|

|                  |            |            | D <sub>A03</sub> | E02        | 65         | D <sub>B16</sub>                   | K13        | 93         | Y <sub>A05</sub> | N06        | 21         |

|                  |            |            | DA04             | F01        | 6          | D <sub>B17</sub>                   | K12        | 33         | YA06             | M06        | 81         |

|                  |            |            | D <sub>A05</sub> | F02        | 66         | GND                                | F03        | 8          | Y <sub>A07</sub> | L07        | 22         |

|                  |            |            | D <sub>A06</sub> | G03        | 7          | GND                                | J11        | 37         | Y <sub>A08</sub> | M07        | 82         |

| A <sub>RA0</sub> | D02        | 63         | D <sub>A07</sub> | G02        | 67         | GND                                | J12        | 38         | Y <sub>A09</sub> | N07        | 24         |

| ARA1             | C02        | 62         | D <sub>A08</sub> | G01        | 9          | GND                                | J13        | 39         | YA10             | N08        | 84         |

| ARA2             | B01        | 61         | D <sub>A09</sub> | H01        | 69         | GNDA                               | N05        | 20         | Y <sub>A11</sub> | M08        | 25         |

| ARA3             | A02        | 120        | DA10             | H02        | 10         | GNDA                               | N09        | 26         | YA12             | L09        | 85         |

| ARA4             | B03        | 119        | DA11             | J03        | 70         | GNDA                               | A09        | 50         | YA13             | M09        | 86         |

| A <sub>RA5</sub> | L02        | 74         | DA12             | J01        | 11         | GNDA                               | A05        | 56         | YA14             | L10        | 27         |

| A <sub>RB0</sub> | K11        | 92         | DA13             | J02        | 71         | LEA                                | L01        | 14         | YA15             | M10        | 87         |

| ARB1             | M13        | 91         | DA14             | K03        | 12         | LEB                                | B12        | 45         | YA16             | N10        | 28         |

| ARB2             | N12        | 90         | DA15             | K02        | 72         | OE <sub>A</sub>                    | L06        | 23         | Y <sub>A17</sub> | L11        | 88         |

| A <sub>RB3</sub> | M11        | 89         | D <sub>A16</sub> | K01        | 13         | OE <sub>B</sub>                    | C08        | 53         | Y <sub>B00</sub> | C03        | 118        |

| A <sub>RB4</sub> | M03        | 77         | D <sub>A17</sub> | L03        | 73         | PIPE                               | H03        | 68         | Y <sub>B01</sub> | A04        | 58         |

| ARB5             | B13        | 105        | D <sub>B00</sub> | C12        | 104        | Vcc                                | E11        | 97         | Y <sub>B02</sub> | B04        | 117        |

| AWAO             | D03        | 3          | D <sub>B01</sub> | C11        | 44         | Vcc                                | E12        | 98         | Y <sub>B03</sub> | C04        | 57         |

| AWA1             | C01        | 2          | D <sub>B02</sub> | D13        | 103        | Vcc                                | E13        | 99         | Y <sub>B04</sub> | B05        | 116        |

| AWA2             | A01        | 1          | D <sub>B03</sub> | D12        | 43         | VCCA                               | L08        | 83         | Y <sub>B05</sub> | C05        | 115        |

| Awa3             | B02        | 60         | D <sub>B04</sub> | D11        | 102        | VCCA                               | C06        | 113        | Y <sub>B06</sub> | B06        | 55         |

| AWA4             | A03        | 59         | D <sub>B05</sub> | F12        | 42         | WEAC/CLKA                          | M01        | 75         | Y <sub>B07</sub> | A06        | 114        |

| Awa5             | M02        | 15         | D <sub>B06</sub> | F13        | 101        | WEAH                               | N02        | 76         | Y <sub>B08</sub> | A07        | 54         |

| AWB0             | L12        | 32         | D <sub>B07</sub> | C13        | 41         | WEAL                               | N01        | 16         | YB09             | B07        | 112        |

| AWB1             | N13        | 31         | D <sub>B08</sub> | F11        | 100        | WE <sub>BC</sub> /CLK <sub>B</sub> | A12        | 106        | Y <sub>B10</sub> | C07        | 52         |

| AWB2             | M12        | 30         | D <sub>B09</sub> | G11        | 40         | WEBH                               | B11        | 107        | Y <sub>B11</sub> | B08        | 111        |

| AWB3             | N11        | 29         | D <sub>B10</sub> | G13        | 96         | WEBL                               | A11        | 47         | YB12             | A08        | 51         |

| AWB4             | N03        | 17         | DB11             | G12        | 36         | YA00                               | L04        | 18         | Y <sub>B13</sub> | B09        | 110        |

| AWB5             | A13        | 46         | D <sub>B12</sub> | H12        | 95         | YA01                               | M04        | 78         | YB14             | C09        | 109        |

| DA00             | D01        | 4          | D <sub>B13</sub> | L13        | 35         | YA02                               | N04        | 19         | YB15             | A10        | 49         |

| D <sub>A01</sub> | E03        | 64         | D <sub>B14</sub> | H13        | 94         | YA03                               | L05        | 79         | Y <sub>B16</sub> | B10        | 108        |

| DA02             | E01        | 5          | D <sub>B15</sub> | H11        | 34         | YA04                               | M05        | 80         | Y <sub>B17</sub> | C10        | 48         |

<sup>\*</sup>Pins facing up.

# TABLE OF INTERCONNECTIONS (Cont'd.)

(Sorted by Pin No.)

| PIN<br>NO.  | PIN NAME                           | PAD<br>NO. | PIN<br>NO. | PIN NAME         | PAD<br>NO. | PIN<br>NO. | PIN NAME                           | PAD<br>NO. | PIN<br>NO. | PIN NAME         | PAD<br>NO. |

|-------------|------------------------------------|------------|------------|------------------|------------|------------|------------------------------------|------------|------------|------------------|------------|

|             |                                    |            | C05        | Y <sub>B05</sub> | 115        | H02        | D <sub>A10</sub>                   | 10         | M05        | Y <sub>A04</sub> | 80         |

|             |                                    |            | C06        | VCCA             | 113        | H03        | PIPE                               | 68         | M06        | Y <sub>A06</sub> | 81         |

|             |                                    |            | C07        | Y <sub>B10</sub> | 52         | H11        | D <sub>B15</sub>                   | 34         | M07        | YA08             | 82         |

|             |                                    |            | C08        | ŌĒB              | 53         | H12        | D <sub>B12</sub>                   | 95         | M08        | YA11             | 25         |

| A01         | A <sub>WA2</sub>                   | 1          | C09        | Y <sub>B14</sub> | 109        | H13        | D <sub>B14</sub>                   | 94         | M09        | YA13             | 86         |

| A02         | A <sub>RA3</sub>                   | 120        | C10        | Y <sub>B17</sub> | 48         | J01        | D <sub>A12</sub>                   | 11         | M10        | YA15             | 87         |

| A03         | A <sub>WA4</sub>                   | 59         | C11        | D <sub>B01</sub> | 44         | J02        | D <sub>A13</sub>                   | 71         | M11        | A <sub>RB3</sub> | 89         |

| A04         | Y <sub>B01</sub>                   | 58         | C12        | D <sub>B00</sub> | 104        | J03        | D <sub>A11</sub>                   | 70         | M12        | Aw <sub>B2</sub> | 30         |

| A05         | GNDA                               | 56         | C13        | D <sub>B07</sub> | 41         | J11        | GND                                | 37         | M13        | A <sub>RB1</sub> | 91         |

| A06         | Y <sub>B07</sub>                   | 114        | D01        | D <sub>A00</sub> | 4          | J12        | GND                                | 38         | N01        | WEAL             | 16         |

| A07         | Y <sub>B08</sub>                   | 54         | D02        | A <sub>RA0</sub> | 63         | J13        | GND                                | 39         | N02        | WEAH             | 76         |

| A08         | YB12                               | 51         | D03        | Awao             | 3          | K01        | D <sub>A16</sub>                   | 13         | N03        | AWB4             | 17         |

| A09         | GNDA                               | 50         | D11        | D <sub>B04</sub> | 102        | K02        | D <sub>A15</sub>                   | 72         | N04        | Y <sub>A02</sub> | 19         |

| A10         | Y <u>B1</u> 5                      | 49         | D12        | D <sub>B03</sub> | 43         | K03        | D <sub>A14</sub>                   | 12         | N05        | GNDA             | 20         |

| A11         | WEBL                               | 47         | D13        | D <sub>B02</sub> | 103        | K11        | A <sub>RB0</sub>                   | 92         | N06        | Y <sub>A05</sub> | 21         |

| A12         | WE <sub>BC</sub> /CLK <sub>B</sub> | 106        | E01        | D <sub>A02</sub> | 5          | K12        | D <sub>B17</sub>                   | 33         | N07        | Y <sub>A09</sub> | 24         |

| A13         | A <sub>WB5</sub>                   | 46         | E02        | D <sub>A03</sub> | 65         | K13        | D <sub>B16</sub>                   | 93         | N08        | YA10             | 84         |

| B01         | A <sub>RA2</sub>                   | 61         | E03        | D <sub>A01</sub> | 64         | L01        | LEA                                | 14         | N09        | GNDA             | 26         |

| B02         | AWA3                               | 60         | E11        | Vcc              | 97         | L02        | A <sub>RA5</sub>                   | 74         | N10        | YA16             | 28         |

| B03         | A <sub>RA4</sub>                   | 119        | E12        | Vcc              | 98         | L03        | D <sub>A17</sub>                   | 73         | N11        | A <sub>WB3</sub> | 29         |

| B04         | Y <sub>B02</sub>                   | 117        | E13        | Vcc              | 99         | L04        | YA00                               | 18         | N12        | A <sub>RB2</sub> | 90         |

| <b>B</b> 05 | Ŷ <sub>B04</sub>                   | 116        | F01        | D <sub>A04</sub> | 6          | L05        | Y <sub>A03</sub>                   | 79         | N13        | A <sub>WB1</sub> | 31         |

| B06         | Y <sub>B06</sub>                   | 55         | F02        | D <sub>A05</sub> | 66         | L06        | <del>OE</del> A                    | 23         |            | ·                |            |

| B07         | Y <sub>B09</sub>                   | 112        | F03        | GND              | 8          | L07        | YA07                               | 22         |            |                  |            |

| B08         | Y <sub>B11</sub>                   | 111        | F11        | D <sub>B08</sub> | 100        | L08        | VCCA                               | 83         |            |                  |            |

| B09         | Y <sub>B13</sub>                   | 110        | F12        | D <sub>B05</sub> | 42         | L09        | YA12                               | 85         |            |                  |            |

| B10         | Y <sub>B16</sub>                   | 108        | F13        | D <sub>B06</sub> | 101        | L10        | YA14                               | 27         |            |                  |            |

| B11         | WE <sub>BH</sub>                   | 107        | G01        | D <sub>A08</sub> | 9          | L11        | YA17                               | 88         |            |                  |            |

| B12         | LEB                                | 45         | G02        | D <sub>A07</sub> | 67         | L12        | Aw Bo                              | 32         |            |                  |            |

| B13         | A <sub>RB5</sub>                   | 105        | G03        | D <sub>A06</sub> | 7          | L13        | D <sub>B13</sub>                   | 35         |            |                  |            |

| C01         | AWA1                               | 2          | G11        | D <sub>B09</sub> | 40         | M01        | WE <sub>AC</sub> /CLK <sub>A</sub> | 75         |            |                  |            |

| C02         | A <sub>RA1</sub>                   | 62         | G12        | D <sub>B11</sub> | 36         | M02        | Aw A5                              | 15         |            |                  |            |

| C03         | Y <sub>B00</sub>                   | 118        | G13        | D <sub>B10</sub> | 96         | M03        | A <sub>RB4</sub>                   | 77         |            |                  |            |

| C04         | Y <sub>B03</sub>                   | 57         | H01        | D <sub>A09</sub> | 69         | M04        | Y <sub>A01</sub>                   | 78         |            |                  |            |

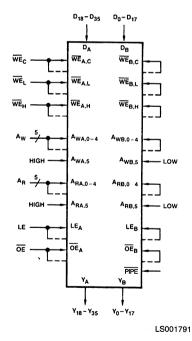

# LOGIC SYMBOL

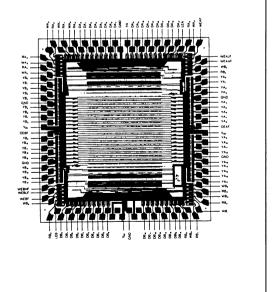

# METALLIZATION AND PAD LAYOUT

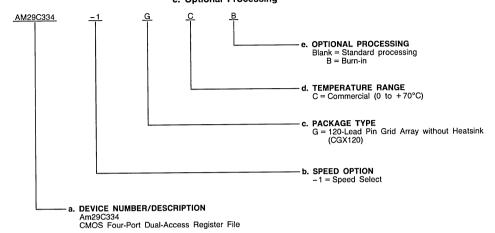

# ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range e. Optional Processing

### **Valid Combinations** AM29C334 GC, GCB

AM29C334-1

### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

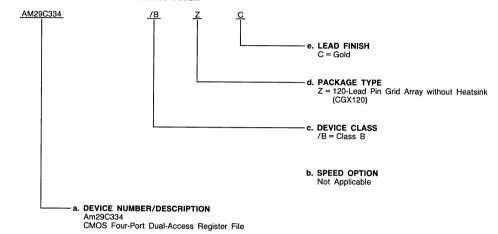

# **ORDERING INFORMATION** (Cont'd.)

### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: a. **Device Number**

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

| Valid    | Cor | mbinations |  |

|----------|-----|------------|--|

| AM29C334 |     | /BZC       |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

# PIN DESCRIPTION

# ARAO - ARA5 Read Address A-Side (Input)

The 6-bit read address input selects one of the 64 memory locations for output to the YA Data Latch.

# A<sub>RB0</sub> - A<sub>RB5</sub> Read Address B-Side (Input)

The 6-bit read address input selects one of the 64 memory locations for output to the Y<sub>B</sub> Data Latch.

### AWA0 - AWA5 Write Address A-Side (Input)

The 6-bit write address input selects one of the 64 memory locations for writing new data from the D<sub>A</sub> input.

### AWB0 - AWB5 Write Address B-Side (Input)

The 6-bit write address input selects one of the 64 memory locations for writing new data from the D<sub>B</sub> input.

#### DA0 - DA17 Data A-Side (Input)

New data is written into memory from this input, as selected by the  $A_{WA}$  address input.

# D<sub>B0</sub> - D<sub>B17</sub> Data B-Side (Input)

New data is written into memory from this input, as selected by the AWB address input.

#### GND, V<sub>CC</sub> Power

Power supply for the internal logic (0, 5 V).

### GNDA, V<sub>CCA</sub> Power

Power supply for the output drivers (0, 5 V).

### LEA YA Data Latch Enable (Input, Active HIGH)

The LEA input controls the latch for the YA output port. When LEA is HIGH, the latch is open (transparent) and data from the RAM, as selected by the ARA address inputs, is passed to the YA output. When LEA is LOW, the latch is closed and it retains the last data read from the RAM. LEA is disabled in the pipelined mode.

#### LEB YB Data Latch Enable (Input, Active HIGH)

The  $L\bar{E}_B$  input controls the latch for the  $Y_B$  output port. When  $LE_B$  is HIGH, the latch is open (transparent), and data from the RAM, as selected by the  $A_{RB}$  address inputs, is passed to the  $Y_B$  output. When  $LE_B$  is LOW, the latch is closed and it retains the last data read from the RAM.  $LE_A$  is disabled in the pipelined mode.

# $\overline{\text{OE}}_{\text{A}}$ Y<sub>A</sub> Output Enable (Input, Active LOW)

When  $\overline{OE}_A$  is LOW, data in the  $Y_A$  Data Latch is driven on the  $Y_A$  output. When  $\overline{OE}_A$  is HIGH,  $Y_A$  output is in the high-impedance (off) state.

# $\overline{\text{OE}}_{\text{B}}$ Y<sub>B</sub> Output Enable (Input, Active LOW)

When  $\overline{OE}_B$  is LOW, data in the  $Y_B$  Data Latch is driven on the  $Y_B$  outputs. When  $\overline{OE}_B$  is HIGH,  $Y_B$  output is in the high-impedance (off) state.

# PIPE Pipeline Enable (Input, Active LOW)

When PIPE is LOW, the input and output registers are enabled, allowing for pipelined operation. When HIGH, these registers are made transparent.

# WE<sub>AC</sub>/CLK<sub>A</sub> Write Enable A-Side Common (Input, Active LOW)

When  $\overline{WE}_{AC}$  is LOW together with  $\overline{WE}_{AH}$  or  $\overline{WE}_{AL}$ , new data is written into the location selected by the AWA address. When  $\overline{WE}_{AC}$  is HIGH, no data is written into the RAM through the A port.  $\overline{WE}_{AC}$  acts as a clock input in the pipeline mode for the A side.

# WE<sub>BC</sub>/CLK<sub>B</sub> Write Enable B-Side Common (Input, Active LOW)

When  $\overline{WE}_{BC}$  is LOW together with  $\overline{WE}_{BH}$  or  $\overline{WE}_{BL}$ , new data is written into the location selected by the AW<sub>B</sub> address. When  $\overline{WE}_{BC}$  is HIGH, no data is written into the RAM through the B port.  $\overline{WE}_{BC}$  acts as a clock input in the pipeline mode for the B side.

# WE<sub>AH</sub> High-Byte Write Enable A-Side (Input, Active LOW)

When  $\overline{WE}_{AH}$  is LOW together with  $\overline{WE}_{AC}$ , new data is written into the high byte of the location selected by the AW<sub>A</sub> address input. When  $\overline{WE}_{AH}$  is HIGH, no data is written into the high byte.

# WEBH High-Byte Write Enable B-Side (Input, Active

**LOW)** When  $\overline{WE}_{BH}$  is LOW together with  $\overline{WE}_{BC}$ , new data is written into the high byte of the location selected by the AW<sub>B</sub> address input. When  $\overline{WE}_{BH}$  is HIGH, no data is written into the high byte.

# WE<sub>AL</sub> Low-Byte Write Enable A-Side (Input, Active LOW)

When  $\overline{WE}_{AL}$  is LOW together with  $\overline{WE}_{AC}$ , new data is written into the low byte of the location selected by the AW<sub>A</sub> address input. When  $\overline{WE}_{AL}$  is HIGH, no data is written into the low byte.

# WE<sub>BL</sub> Low-Byte Write Enable B-Side (Input, Active LOW)

When  $\overline{WE}_{BL}$  is LOW together with  $\overline{WE}_{BC}$ , new data is written into the low byte of the location selected by the AW<sub>B</sub> address input. When  $\overline{WE}_{BL}$  is HIGH, no data is written into the low byte.

# YA0-YA17 Data Latch (Outputs, Three-State) The 18-bit YA Data Latch outputs.

Y<sub>B0</sub> - Y<sub>B17</sub> Data Latch (Outputs, Three-State) The 18-bit Y<sub>B</sub> Data Latch outputs.

### **FUNCTIONAL DESCRIPTION**

The heart of the Am29C334 is a high-speed 64-word by 18-bit dual RAM cell array. Six write enables permit the RAM word to be written in one or both of its 9-bit bytes. Data to be written is presented to each side of the RAM array through the two data ports ( $D_A$  and  $D_B$ ).

The remainder of the logic surrounding the RAM array supports pipelining the RAM access and providing a forwarding path for data around the RAM. This forwarding path is needed to eliminate the latency cycle associated with consecutive write/read accesses to the same memory location in a pipelined system.

Pipelining of the RAM is controlled by the PIPE pin. When not asserted (i.e., in non-pipelined mode) the registers on the inputs (write ports  $\mathrm{D}_{A/B}$ , write addresses  $\mathrm{A}_{WA/B}$ , and write enables  $\overline{\mathrm{WE}}_{AC/BC}$ ) are made fully transparent, while the registers at the outputs (the read ports  $\mathrm{Y}_{A/B}$ ) are turned into latches, controlled by the latch enables  $\mathrm{LE}_{A/B}$ .

In either mode of operation, each side of the RAM is controlled by its individual control signals. This means that the two sides of the RAM can operate at different clock rates to one another. In the pipelined mode, these clock rates must have a known relationship between each other.

In the non-pipelined mode, there is no need for a relationship between the clock rates. Two special cases of operation arise because of this. The first is where the location written to by one side is being read from the other side. In this case, known as A-to-B transparency, the value read is the value being written. The second occurs when two writes to the same location occur at the same time. In this case the value written can not be defined, but the operation is not harmful to the device.

The transparency mode (A-A or B-B) during a write  $(\overline{WE}_A = LOW)$  allows the data in  $(D_A)$  to not only be written into memory, but also to appear at the output  $(Y_A)$  when the output latch  $(LE_A)$  is HIGH and the output enable control  $(\overline{OE}_A)$  is LOW.

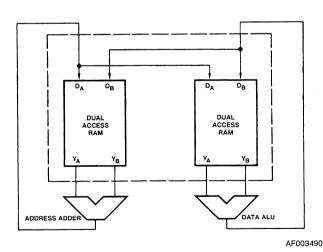

# Extensions to Four Read Ports and Two Write Ports

A RAM with four read ports and two write ports can be made by using two dual-access RAMs and connecting each of the write ports, write addresses, and write enables in parallel for the two devices. Figure 2 details this in a non-pipelined mode.

AF003482

Figure 1. Am29C300 CMOS Family High-Performance System Block Diagram

#### 32 Word x 36 Bit Single-Access RAM

It is possible to convert the 64 word x 18 bit dual-access RAM into a 32 word x 36 bit single-access RAM. This is performed by storing the upper half of the 36 bits in the upper half of the 64 words and addressing these from the A side, and storing the lower half of the 36 bits in the lower half of the 64 words and addressing these from the B side. This arrangement does not change the capacity of the RAM, but the dual access is lost (see Figure 4).

#### **Operational Modes**

The Am29C334 may be configured in a non-pipelined mode or in a pipelined mode by controlling the PIPE pin. This mode is selected via hardwiring the pin to either LOW or HIGH. This option should not be changed during operation.

#### Non-Pipelined Data Path

In non-pipelined mode ( $\overline{\text{PIPE}}=1$ ), the Am29C334 is a flow-through device; data is read out, used, and written back all in the same cycle. In this mode all the registers are made transparent except the registers at the two read ports that are configured as latches. The read port latches are controlled individually by the LEA and LEB, so that they are transparent when the latch enables are HIGH and retain the data when the latch enables are LOW. The ''forwarding logic'' incorporated to support the pipelined mode of operation is also disabled in this mode of operation (specifically, the address comparators are disabled).

In the non-pipelined mode of operation it is possible to simultaneously read two ports, read one port and write to the other, or write to two ports, concurrently. The read and write

addresses are internally multiplexed on each side. The selection of the read and write addresses is controlled by the exclusive-OR of the  $\overline{\text{PIPE}}$  pin and  $\overline{\text{WE}_{AC/BC}}$ . Normally, the  $\overline{\text{WE}_{AC/BC}}$  are connected to the system clock. With  $\overline{\text{PIPE}}$  deasserted, the read address will be selected in the high part of the clock cycle ( $\overline{\text{WE}_{AC/BC}}=1$ ) and the write address selected only in the low part. Byte selection for writing on either ports is controlled by the  $\overline{\text{WE}_{H/L}}$  pins.

Two interesting cases arise as a result of the dual access capability. The first occurs if a location is written into by one side while it is being read out by the other side. In this case, known as A-to-B transparency, the data being written will appear on the read port after the TransparencyAB time (if other read access time parameters are met). The second case of interest occurs if both sides write to the same location at the same time. The value written as a result of this operation cannot be defined.

### **Pipelined Data Path**

The Am29C334 can be configured in a pipelined system by asserting the  $\overline{\text{PIPE}}$  signal ( $\overline{\text{PIPE}}=0$ ) and adding an additional external register in the write address and the write control path on both A and B ports as shown in Figure 3. The registers on each side are controlled by separate clocks that are supplied over the  $\overline{\text{WE}}_{AC}$  and  $\overline{\text{WE}}_{BC}$  pins.

Typically, in a pipelined system a read - modify - write would span three cycles. In the second half of the first cycle, a read of the operand(s) is performed and the data is clocked into the output registers at the end of the cycle. In the second cycle, the operation is performed on the operands and the result is clocked into the data register on the write port at the end of the second cycle. In the first half of the third cycle, the data is written to the register file. Therefore, in any cycle, a pipelined system is writing the result of instruction n (in the first half).

executing instruction n+1, and reading the operands needed in instruction n+2. In any case, a write operation followed by a read operation is performed in the RAM in a cycle.

A special case arises if the data to be written by the previous instruction is needed in the next instruction as an operand. Due to the pipeline register being at its write port, the location is not written into until the next cycle, and hence only the previous value is available in the current cycle. To overcome this problem, "forwarding logic" is included as shown in the block diagram. This logic consists of three elements: an address comparator, an AND gate, and a three-to-one multiplexer, as shown. If the read address of the current instruction is the same as the write address of the previous instruction. and if the result is to be written, then the data to be written is forwarded by the forwarding multiplexer to the output registers. Since there are two write ports, forwarding paths on both ports are provided. As each write port has byte write capability, the forwarding is further broken into the upper and lower bytes.

Since each side has its own WE<sub>C</sub>/CLK control, it is possible to clock each side of the chip differently. However, if the part is used at different frequencies, the forwarding cannot be guaranteed unless the addresses compared are held valid long enough to allow for a comparison to be made and the results of the forwarding setup on the output register.

As mentioned earlier, it is necessary to use an external write address and write control registers in a pipelined system. These registers have not been included for two reasons. First, it is possible for the user to abort the writing before it fills the internal pipe. This situation may arise in cases such as in "traps." Second, by providing an external write address register it provides the flexibility of obtaining the write address from several sources by using an external multiplexer.

Figure 2. RAM with Four Read Ports and Two Write Ports for Non-pipelined Mode

Figure 3. System Diagram With the Am29C334 in a Double Pipelined Data Path

Figure 4. 32 x 36 RAM (Single Access) Using 64 x 18 Dual-Access RAM

# **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                                    |

|--------------------------------------------------------|

| Continuous                                             |

| DC Voltage Applied to Outputs                          |

| for HIGH Output State0.3 V to +V <sub>CC</sub> + 0.3 V |

| DC Input Voltage0.3 V to +V <sub>CC</sub> + 0.3 V      |

| DC Output Current, Into LOW Outputs30 mA               |

| DC Input Current10 mA to +10 mA                        |

| Stresses above those listed under ABSOLUTE MAXIMUM     |

RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

### **OPERATING RANGES**

| Commercial (C) Devices             |               |

|------------------------------------|---------------|

| Temperature (T <sub>A</sub> )      | 0 to +70°C    |

| Supply Voltage+ 4.7                |               |

| Military* (M) Devices              |               |

| Temperature (T <sub>A</sub> )      | 55 to +125°C  |

| Supply Voltage (V <sub>CC</sub> )+ | 4.5 to +5.5 V |

|                                    |               |

Operating ranges define those limits between which the functionality of the device is guaranteed.

\* Military product 100% tested at TA = +25°C, +125°C, and -55°C.

DC CHARACTERISTICS over operating range unless otherwise specified (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol | Parameter<br>Description               | Test Cor<br>(Note                                                                                        |                                            | Min. | Max.      | Unit  |

|---------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------|------|-----------|-------|

| V <sub>OH</sub>     | Output HIGH Voltage                    | $V_{CC} = Min.$ $V_{IN} = V_{IL} \text{ or } V_{IH}$ $I_{OH} = -4 \text{ mA}$                            |                                            | 2.4  |           | Volts |

| V <sub>OL</sub>     | Output LOW Voltage                     | V <sub>CC</sub> = Min.<br>V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub><br>I <sub>OL</sub> = 8 mA |                                            |      | 0.5       | Volts |

| V <sub>IH</sub>     | Input HIGH Level                       | Guaranteed Input Logical<br>HIGH Voltage (Note 2)                                                        |                                            | 2.0  |           | Volts |

| V <sub>IL</sub>     | Input LOW Level                        | Guaranteed Input Logical<br>LOW Voltage (Note 2)                                                         |                                            |      | 0.8       | Volts |

| lıL                 | Input LOW Current                      | V <sub>CC</sub> = Max.<br>V <sub>IN</sub> = 0.5 V                                                        |                                            |      | -10       | μΑ    |

| Iн                  | Input HIGH Current                     | V <sub>CC</sub> = Max.<br>V <sub>IN</sub> = V <sub>CC</sub> - 0.5 V                                      |                                            |      | 10        | μΑ    |

| lozн                | Off State (High-Impedance)             | VMov                                                                                                     | V <sub>O</sub> = 2.4 V                     |      | 10        |       |

| lozL                | Output Current                         | V <sub>CC</sub> = Max.                                                                                   | V <sub>O</sub> = 0.5 V                     |      | -10       | μΑ    |

| 1                   | Static Bayer Symphy Cornect            | V <sub>IN</sub> = V <sub>CC</sub> or GND                                                                 | T <sub>A</sub> = -55 to 125°C              |      | 80        | mA    |

| Icc                 | Static Power Supply Current            | $V_{CC} = Max$ $I_{O} = 0 \mu A$                                                                         | $T_A = 0 \text{ to } + 70^{\circ}\text{C}$ |      | 70        | mA    |

| C <sub>PD</sub>     | Power Dissipation Capacitance (Note 3) | V <sub>CC</sub> = 5.0 V<br>T <sub>A</sub> = 25°C No Load                                                 |                                            | 90   | 0 pF Typi | cal   |

- Notes: 1. V<sub>CC</sub> conditions shown as Min. or Max. refer to the commercial (±5%) V<sub>CC</sub> limits.

2. These input levels provide zero-noise immunity and should only be statically tested in a noise-free environment (not functionally

- 3. CpD determines the no-load dynamic current consumption: Icc (Total) = Icc (Static) + Cpp Vcc f, where f is the switching frequency of the majority of the internal nodes, normally one-half of the clock frequency. This specification is not tested.

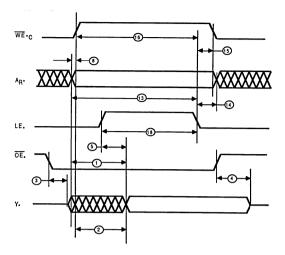

# SWITCHING CHARACTERISTICS over COMMERCIAL operating range unless otherwise specified NON-PIPELINED MODE (Note 1)

|     |                                   |                                                                                           |                                        | 29   | C334    | 290  | 334-1   | 290  | 334-2   |      |

|-----|-----------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------|------|---------|------|---------|------|---------|------|

| No. | Parameter                         | Description                                                                               | Test Conditions                        | Min. | Max.    | Min. | Max.    | Min. | Max.    | Unit |

| 1   | Access Time                       | A <sub>RA</sub> or A <sub>RB</sub> to Y <sub>A</sub> or Y <sub>B</sub>                    | LE <sub>A</sub> or LE <sub>B</sub> = H |      | 32      |      | 26      |      | 21      | ns   |

| 2   | Access Time                       | WE <sub>AC</sub> or WE <sub>BC</sub> to Y <sub>A</sub> or Y <sub>B</sub>                  | LE <sub>A</sub> or LE <sub>B</sub> = H |      | 30      |      | 25      |      | 20      | ns   |

| 3   | Turn-On Time                      | OEA or OEB I to YA<br>or YB Active                                                        |                                        | 0    | 20      | 0    | 16      | 0    | 16      | ns   |

| 4   | Turn-Off Time<br>(Note 2)         | OE <sub>A</sub> or OE <sub>B</sub> t to Y <sub>A</sub> or Y <sub>B</sub> = High Impedance |                                        | 0    | 20      | 0    | 16      | 0    | 16      | ns   |

| 5   | Enable Time                       | LEA or LEB t to YA or YB                                                                  |                                        | 0    | 16      | 0    | 14      | 0    | 14      | ns   |

| 6   | Transparency                      | WE <sub>A</sub> or WE <sub>B</sub> I to Y <sub>A</sub> or Y <sub>B</sub>                  | LE <sub>A</sub> or LE <sub>B</sub> = H |      | 39      |      | 33      |      | 27      | ns   |

| 7   | Transparency                      | DA or DB to YA or YB                                                                      | LEA or LEB = H,<br>WEA or WEB = L      |      | 39      |      | 33      |      | 27      | ns   |

| 8   | Write Recovery Time               | ARA or ARB to WEAC or WEBC                                                                | BAAA                                   |      | (2)-(1) |      | (2)-(1) |      | (2)-(1) | ns   |

| 9   | Data Setup Time                   | DA or DB to WEA or W                                                                      | E <sub>B</sub> t                       | 15   |         | 13   |         | 13   |         | ns   |

| 10  | Data Hold Time                    | D <sub>A</sub> or D <sub>B</sub> to WE <sub>A</sub> or W                                  | E <sub>B 1</sub>                       | 0    |         | 0    |         | 0    |         | ns   |

| 11  | Address Setup Time                | A <sub>WA</sub> or A <sub>WB</sub> to WE <sub>A</sub> o                                   | r <del>WE</del> B ↓                    | 2    |         | 2    |         | 2    |         | ns   |

| 12  | Address Hold Time                 | AWA or AWB to WEA o                                                                       | r <del>WE</del> B ↑                    | 1    |         | 1    |         | 1    |         | ns   |

| 13  | Address Setup Time                | A <sub>RA</sub> or A <sub>RB</sub> to LE <sub>A</sub> or                                  | LE <sub>B</sub> ;                      | 20   |         | 17   |         | 17   |         | ns   |

| 14  | Address Hold Time                 | A <sub>RA</sub> or A <sub>RB</sub> to LE <sub>A</sub> or                                  | LE <sub>B</sub> ↓                      | 1    |         | 1    |         | 1    |         | ns   |

| 15  | Latch Close Before<br>Write       | LE <sub>A</sub> or LE <sub>B</sub> to WE <sub>A</sub> or                                  | WE <sub>B</sub> ↓                      | 0    |         | 0    |         | 0    |         | ns   |

| 16  | Read Before Latch<br>Close        | WEAC or WEBC to LEA                                                                       | or LE <sub>B</sub> !                   | 20   |         | 16   |         | 16   |         | ns   |

| 17  | Write Pulse Width                 | WEA or WEB (LOW)                                                                          |                                        | 20   |         | 16   |         | 16   |         | ns   |

| 18  | Latch Data Capture<br>Pulse Width | LE <sub>A</sub> or LE <sub>B</sub> (HIGH)                                                 |                                        | 14   |         | 12   |         | 12   |         | ns   |

Notes: See notes following Military table.

**SWITCHING CHARACTERISTICS** over **MILITARY** operating range unless otherwise specified (for APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted)

# NON-PIPELINED MODE (Note 1)

|     |                                   |                                                                                 |                                                                                   | 290  | 334     |      |

|-----|-----------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------|---------|------|

| No. | Parameter                         | Description                                                                     | Test Conditions                                                                   | Min. | Max.    | Unit |

| 1   | Access Time                       | A <sub>RA</sub> or A <sub>RB</sub> to Y <sub>A</sub> or Y <sub>B</sub>          | LE <sub>A</sub> or LE <sub>B</sub> = H                                            |      | 40      | ns   |

| 2   | Access Time                       | WEAC or WEBC to YA or YB                                                        | LE <sub>A</sub> or LE <sub>B</sub> = H                                            | 0    | 37      | ns   |

| 3   | Turn-On Time                      | OE <sub>A</sub> or OE <sub>B</sub> ↓ to Y <sub>A</sub> or Y <sub>B</sub> Active |                                                                                   | 0    | 16      | ns   |

| 4   | Turn-Off Time<br>(Note 2)         | $\overline{OE}_A$ or $\overline{OE}_B$ to $Y_A$ or $Y_B$ = High Impedance       |                                                                                   | 0    | 25      | ns   |

| 5   | Enable Time                       | LE <sub>A</sub> or LE <sub>B</sub> † to Y <sub>A</sub> or Y <sub>B</sub>        |                                                                                   | 0    | 21      | ns   |

| 6   | Transparency                      | WE <sub>A</sub> or WE <sub>B</sub> ↓ to Y <sub>A</sub> or Y <sub>B</sub>        | LE <sub>A</sub> or LE <sub>B</sub> = H                                            | 0    | 47      | ns   |

| 7   | Transparency                      | D <sub>A</sub> or D <sub>B</sub> to Y <sub>A</sub> or Y <sub>B</sub>            | LE <sub>A</sub> or LE <sub>B</sub> = H,<br>WE <sub>A</sub> or WE <sub>B</sub> = L |      | 47      | ns   |

| 8   | Write Recovery Time               | A <sub>RA</sub> or A <sub>RB</sub> to WE <sub>AC</sub> or WE <sub>BC</sub>      |                                                                                   |      | (2)-(1) | ns   |

| 9   | Data Setup Time                   | D <sub>A</sub> or D <sub>B</sub> to WE <sub>A</sub> or WE <sub>B</sub>          | 1                                                                                 | 19   |         | ns   |

| 10  | Data Hold Time                    | D <sub>A</sub> or D <sub>B</sub> to WE <sub>A</sub> or WE <sub>B</sub>          | Ť                                                                                 | 2    |         | ns   |

| 11  | Address Setup Time                | AWA or AWB to WEA or W                                                          | Ē <sub>B</sub> ↓                                                                  | 4    |         | ns   |

| 12  | Address Hold Time                 | AWA or AWB to WEA or W                                                          | Ē <sub>B</sub> ↑                                                                  | 2    |         | ns   |

| 13  | Address Setup Time                | ARA or ARB to LEA or LEB                                                        | 1                                                                                 | 23   |         | ns   |

| 14  | Address Hold Time                 | ARA or ARB to LEA or LEB                                                        | 1                                                                                 | 1    |         | ns   |

| 15  | Latch Close Before<br>Write       | LEA or LEB to WEA or WE                                                         | В 1                                                                               | 0    |         | ns   |

| 16  | Read Before Latch<br>Close        | WEAC or WEBC to LEA or                                                          | LE <sub>B</sub> ;                                                                 | 24   |         | ns   |

| 17  | Write Pulse Width                 | WEA or WEB (LOW)                                                                |                                                                                   | 23   |         |      |

| 18  | Latch Data Capture<br>Pulse Width | LEA or LEB (HIGH)                                                               |                                                                                   | 17   |         | ns   |

Notes: 1. WE<sub>A</sub> = WE<sub>AC</sub> + WE<sub>AL</sub>/H

WE<sub>B</sub> = WE<sub>BC</sub> + WE<sub>BL</sub>/H

2. Y<sub>A</sub> and Y<sub>B</sub> are tested independently.

3. Minimum delays are not tested.

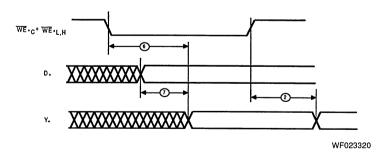

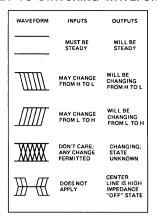

# SWITCHING WAVEFORMS NON-PIPELINED MODE

WF023330

Read Function (\* means A or B)

Write Function (\* means A or B)

**Transparency**

NOTE: LE = HIGH OE = LOW \* means A or B

# SWITCHING CHARACTERISTICS over COMMERCIAL operating range (Cont'd.)

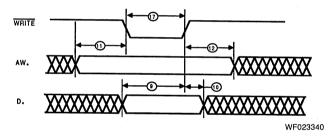

# PIPELINED MODE

|     |                             |                                                                              | 290  | 334                 | 29C3 | 334-1 | 29C3 | 334-2 |      |

|-----|-----------------------------|------------------------------------------------------------------------------|------|---------------------|------|-------|------|-------|------|

| No. | Parameter                   | Description                                                                  | Min. | Max.                | Min. | Max.  | Min. | Max.  | Unit |

| 19  | Write Data Setup Time       | D <sub>A</sub> or D <sub>B</sub> to CLK <sub>A</sub> or CLK <sub>B</sub> †   | 15   |                     | 13   |       | 13   |       | ns   |

| 20  | Write Data Hold Time        | D <sub>A</sub> or D <sub>B</sub> to CLK <sub>A</sub> or CLK <sub>B</sub> t   | 1    |                     | 1    |       | 1    |       | ns   |

| 21  | Write Address Setup<br>Time | AWA or AWB to CLKA or CLKB t                                                 | 23   | francis grand       | 20   |       | 20   |       | ns   |

| 22  | Write Address Hold<br>Time  | Awa or Awa to CLKa or CLKa                                                   | /o\\ | IH.                 | 0    |       | 0    |       | ns   |

| 23  | Write Enable Setup<br>Time  | WEH OF WEL TO CLKA OF CLKB                                                   | 20   |                     | 16   |       | 16   |       | ns   |

| 24  | Write Enable Hold Time      | WEH or WEL to CLKA or CLKB 1                                                 | 0    |                     | 0    |       | 0    |       | ns   |

| 25  | Read Address Setup<br>Time  | ARA or ARB to CLKA or CLKB t                                                 | 24   | 14                  | 20 \ |       | 20   |       | ns   |

| 26  | Read Address Hold<br>Time   | A <sub>RA</sub> or A <sub>RB</sub> to CLK <sub>A</sub> or CLK <sub>B</sub> 1 | 0    | rii test<br>Referen | o    |       | 0    |       | ns   |

| 27  | Minimum Clock Cycle         | CLK <sub>A</sub> or CLK <sub>B</sub> (LOW)                                   | 50   |                     | 40   |       | 40   |       | ns   |

| 28  | Minimum Clock Pulse         | CLK <sub>A</sub> or CLK <sub>B</sub> (HIGH)                                  | 17   |                     | 14   |       | 14   |       | ns   |

| 29  | Minimum Clock Pulse         | CLK <sub>A</sub> or CLK <sub>B</sub> (LOW)                                   | 17   |                     | 14   |       | 14   |       | ns   |

| 30  | Clock to Y                  | YA or YB to CLKA or CLKB                                                     | 14   |                     | 12   |       | 10   |       | ns   |

# SWITCHING CHARACTERISTICS over MILITARY operating range (Cont'd.)

# PIPELINED MODE

|     |                          |                                             | 290  | 334  |      |

|-----|--------------------------|---------------------------------------------|------|------|------|

| No. | Parameter                | Description                                 | Min. | Max. | Unit |

| 19  | Write Data Setup Time    | DA or DB to CLKA or CLKB †                  | 19   |      | ns   |

| 20  | Write Data Hold Time     | DA or DB to CLKA or CLKB †                  | 2    |      | ns   |

| 21  | Write Address Setup Time | AWA or AWB to CLKA or CLKB †                | 27   |      | ns   |

| 22  | Write Address Hold Time  | AWA or AWB to CLKA or CLKB 1                | 2    |      | ns   |

| 23  | Write Enable Setup Time  | WEH or WEL to CLKA or CLKB 1                | 23   |      | ns   |

| 24  | Write Enable Hold Time   | WEH or WEL to CLKA or CLKB ↑                | 2    |      | ns   |

| 25  | Read Address Setup Time  | ARA or ARB to CLKA or CLKB †                | 28   |      | ns   |

| 26  | Read Address Hold Time   | ARA or ARB to CLKA or CLKB †                | 0    |      | ns   |

| 27  | Minimum Clock Cycle      | CLK <sub>A</sub> or CLK <sub>B</sub> (LOW)  | 55   |      | ns   |

| 28  | Minimum Clock Pulse      | CLK <sub>A</sub> or CLK <sub>B</sub> (HIGH) | 20   |      | ns   |

| 29  | Minimum Clock Pulse      | CLK <sub>A</sub> or CLK <sub>B</sub> (LOW)  | 20   |      | ns   |

| 30  | Clock to Y               | YA or YB to CLKA or CLKB                    | 18   |      | ns   |

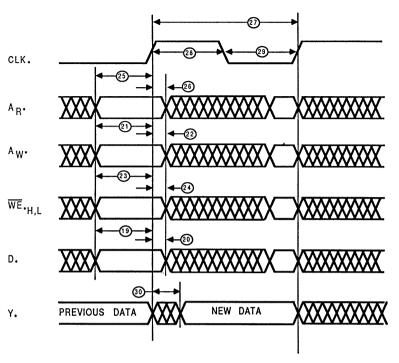

# SWITCHING WAVEFORMS (Cont'd.) PIPELINED MODE

WF023310

# \* means A or B

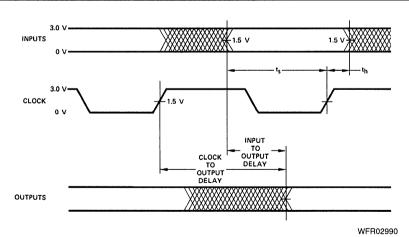

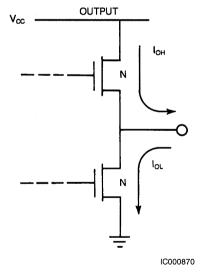

### SWITCHING TEST CIRCUIT

Notes: 1.  $C_L$  = 50pF includes scope probe, wiring and stray capacitances without device in test fixture.

- 2. S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub> are closed during functions tests and all AC tests except output enable tests.

- 3.  $S_1$  and  $S_3$  are closed while  $S_2$  is open for  $t_{PZH}$  test.  $S_1$  and  $S_2$  are closed while  $S_3$  is open for  $t_{PZL}$  test.

- 4. C<sub>1</sub> = TBD for output disable tests.

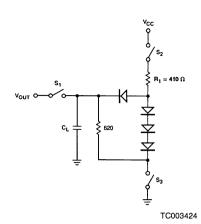

# **KEY TO SWITCHING WAVEFORMS**

KS000010

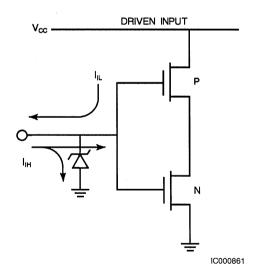

# INPUT/OUTPUT CIRCUIT DIAGRAMS

$C_l \approx 5.0$  pF, all inputs

$C_O \approx 5.0$  pF, all outputs

<sup>\*</sup> For reference only.

### ADVANCED MICRO DEVICES' U.S. SALES OFFICES

| ALABAMA        | (205) 882-9122 | KANSAS         | (913) 451-3115 |

|----------------|----------------|----------------|----------------|

|                | (203) 002-3122 |                |                |

| ARIZONA,       |                | MARYLAND       | (301) 796-9310 |

| Tempe          | (602) 242-4400 | MASSACHUSETTS  | (617) 273-3970 |

| CALIFORNIA.    |                | MINNESOTA      | (612) 938-0001 |

| Culver City    | (213) 645-1524 | MISSOURI       | (314) 275-4415 |

|                |                |                | (201) 299-0002 |

| Newport Beach  |                | NEW JERSEY     | (201) 299-0002 |

| San Diego      |                | NEW YORK,      |                |

| Santa Clara    | (408) 727-3270 | Liverpool      | (315) 457-5400 |

| Woodland Hills | (818) 992-4155 | Poughkeepsie   | (914) 471-8180 |

| COLORADO       | (303) 741-2900 | Woodbury       | (516) 364-8020 |

|                |                | NODTH CARCUINA |                |

| CONNECTICUT    | (203) 264-7800 | NORTH CAROLINA | (919) 847-8471 |

| FLORIDA,       |                | OREGON         | (503) 245-0080 |

| Clearwater     | (813) 530-9971 | OHIO           | (614) 891-6455 |

| Ft Lauderdale  |                | PENNSYLVANIA.  | (,             |

| Melbourne      |                | Allentown      | (215) 398-8006 |

|                |                |                |                |

| Orlando        |                | Willow Grove   | (215) 657-3101 |

| GEORGIA        | (404) 449-7920 | TEXAS,         |                |

| ILLINOIS.      |                | Austin         | (512) 346-7830 |

| Chicago        | (312) 773-4422 | Dallas         | (214) 934-9099 |

|                |                |                | (713) 785-9001 |

| Naperville     |                | Houston        |                |

| INDIANA        | (317) 244-7207 | WASHINGTON     | (206) 455-3600 |

|                |                | WISCONSIN      | (414) 792-0590 |

|                |                |                |                |

### ADVANCED MICRO DEVICES' INTERNATIONAL SALES OFFICES

| 5510004                         |                                      |

|---------------------------------|--------------------------------------|

| BELGIUM,                        | JAPAN,                               |

| Bruxelles TEL (02) 771 91 42    | Tokyo TEL (03) 345-8241              |

| FAX (02) 762 37 12              | FAX 3425196                          |

| TLX 61028                       | TLX J24064AMDTKOJ                    |

| CANADA, Ontario,                | Osaka TEL 06-243-3250                |

| Kanata TEL . (613) 592-0060     | FAX 06-243-3253                      |

| Willowdale                      | 17/77 00 240 0200                    |

| FAX . (416) 224-5193            | KOREA, Seoul TEL 82-2-784-7598       |

|                                 |                                      |

| FRANCE,                         | FAX 82-2-784-8014                    |

| Paris TEL (01) 49-75-10-10      | LATIN AMERICA,                       |

| FAX (01) 49-75-10-13            | Ft. Lauderdale (305) 484-8600        |

| TLX 263282F                     | FAX (305) 485-9736                   |

| GERMANY,                        | TLX 5109554261 AMDFTL                |

| Hannover area TEL (05143) 50 55 |                                      |

| FAX (05143) 55 53               | SWEDEN, Stockholm TEL (08) 733 03 50 |

| TLX 925287                      | FAX (08) 733 22 85                   |

| München TEL (089) 41 14-0       | TLX 11602                            |

| FAX (089) 406490                | ΤΕΧ 11002                            |

|                                 | TAIWAN TLX 886-2-7122066             |

| TLX 523883                      |                                      |

| Stuttgart                       | FAX 886-2-7122017                    |

| FAX (0711) 625187               | UNITED KINGDOM,                      |

| TLX 721882                      | Manchester area TEL (0925) 828008    |

| HONG KONG,                      | FAX (0925) 827693                    |

| Kowloon                         | TLX 628524                           |

| FAX 1234276                     | London area TEL (04862) 22121        |

| TLX 504260AMDAPHX               | FAX (04862) 22179                    |

|                                 | TLX859103                            |

| ITALY, Milano TEL (02) 3390541  | TLX 886-2-7122066                    |

| FAX (02) 3498000                | FAX                                  |

| TLX 315286                      | FAX 000-2-7122017                    |

| ILA 313200                      |                                      |

# NORTH AMERICAN REPRESENTATIVES

| CALIFORNIA                   |             | MICHIGAN                 |                |

|------------------------------|-------------|--------------------------|----------------|

| I <sup>2</sup> INC OEM (408  | ) 988-3400  | SAI MARKETING CORP       | (313) 750-1922 |

| DISTI (408                   | ) 498-6868  | MISSOURI                 |                |

| CANADA                       | ,           | LORENZ SALES             | (314) 997-4558 |

| Calgary, Alberta             |             | NEBRASKA                 | (,             |

| VITEL ELECTRONICS (403       | ) 278-5833  | LORENZ SALES             | (402) 475-4660 |

| Kanata, Ontario              | , 2, 0 0000 | NEW MEXICO               | (402) 470 1000 |

| VITEL ELECTRONICS (613       | \ E02 0000  | THORSON DESERT STATES    | (EOE) 202 OEEE |

|                              | ) 592-0090  |                          | (505) 293-6555 |

| Mississauga, Ontario         |             | NEW YORK                 | (045) 407 0040 |

| VITAL ELECTRONICS (416       | ) 6/6-9/20  | NYCOM, INC               | (315) 437-8343 |

| Quebec                       |             | OHIO                     |                |

| VITEL ELECTRONICS (514       | ) 636-5951  | Columbus                 |                |

| IDAHO                        |             | DOLFUSS ROOT & CO        | (614) 885-4844 |

| INTERMOUNTAIN TECH MKGT (208 | 888-6071    | Dayton                   | ` '            |

| INDIANA                      | ,           | DOLFUSS ROOT & CO        | (513) 433-6776 |

| SAI MARKETING CORP (317      | ) 253-1668  | Strongsville             | (0.0)          |

| IOWA                         | , 200 1000  | DOLFUSS ROOT & CO        | (216) 238-0300 |

| LORENZ SALES (319            | 377.4666    | PENNSYLVANIA             | (210) 200 0000 |

| KANSAS                       | ) 377-4000  | DOLFUSS ROOT & CO        | (410) 001 4400 |

|                              | 004 0550    |                          | (412) 221-4420 |

| LORENZ SALES (913            | ) 384-6556  | UTAH                     | (004) 505 0004 |

|                              |             | R <sup>2</sup> MARKETING | (801) 595-0631 |

Advanced Micro Devices reserves the right to make changes in its product without notice in order to improve design or performance characteristics. The performance characteristics listed in this document are guaranteed by specific tests, guard banding, design and other practices common to the industry. For specific testing details, contact your local AMD sales representative. The company assumes no responsibility for the use of any circuits described herein.