## Am29C509

#### 12 x 12-Bit CMOS Multiplier/Accumulator

#### DISTINCTIVE CHARACTERISTICS

- High-speed 1.6-μs CMOS Process

- 50-ns maximum clock rate supports real-time processing.

- o 27-Bit Product Accumulation Result

- Provides 24-bit product plus 3-bit extended product.

- Accumulator Function

- Supports LOAD, ADD, and SUBTRACT instructions.

- Output Register Preload

- A predetermined value can be loaded into the output register.

- Round Control

- The most significant 12 bits of the product can be rounded to the value nearest to the full 24-bit product.

- Accepts Two's-Complement or Unsigned Inputs

#### GENERAL DESCRIPTION

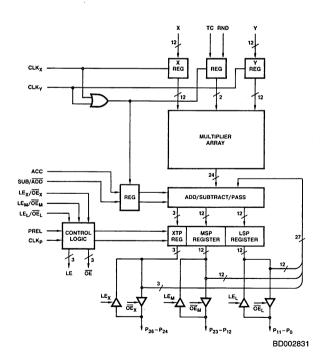

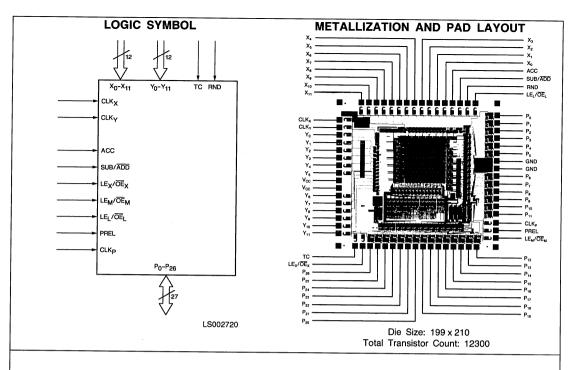

The Am29C509 is a high-speed 12 x 12-bit CMOS multiplier/accumulator (MAC). The X and Y input registers accept 12-bit inputs in two's-complement or unsigned magnitude format. A third register stores the Two's Complement (TC), Round (RND), Accumulate (ACC), and Subtraction (SUB/ADD) control bits. This register is clocked whenever the X or input registers are clocked.

The 27-bit accumulator/output register contains the full 24-bit multiplier output which is sign-extended or zero-filled based on the TC control bit. The accumulator can also be preloaded from an external source through the bidirectional P-port. The operation of the accumulator is controlled by the signals ACC, SUB/ADD, and PREL (Preload). Each of the input registers and the output register have independent clocks.

#### **BLOCK DIAGRAM**

Publication # Rev. Amendment

04986 E /0

Issue Date: January 1988

#### **RELATED AMD PRODUCTS**

| Part No.       | Description                                     |

|----------------|-------------------------------------------------|

| Am25S557/558   | 8 x 8 Multiplier                                |

| Am29C01        | CMOS 4-Bit Microprocessor Slice                 |

| Am29C03        | CMOS 4-Bit Super Slice                          |

| Am2904         | Status and Shift Controller                     |

| Am29C10A       | CMOS Microprogram Controller                    |

| Am29C101       | 16-Bit CMOS Microprocessor Slice                |

| Am29C111       | CMOS 16-Bit Microsequencer                      |

| Am29C116       | CMOS 16-Bit Microprocessor                      |

| Am29PL131      | 64 x 12-Bit Field-Programmable Controller       |

| Am29PL142      | 128 x 16-Bit Field Programmable Controller      |

| Am2914         | Vectored Interrupt Controller                   |

| Am2925         | Clock Generator                                 |

| Am29C331       | CMOS 16-Bit Microprogram Sequencer              |

| Am29C334       | CMOS 64 x 16 Register File                      |

| Am2940         | DMA Address Generator                           |

| Am29C516A/517A | CMOS 16 x 16 Parallel Multipliers               |

| Am2952A        | 8-Bit Bidirectional I/O Port                    |

| Am29C520       | CMOS 4-Deep Pipeline Register                   |

| Am29C525       | CMOS 16-Deep Pipeline Register                  |

| Am29800A       | High-Performance Bus Interface Family           |

| Am29C800       | High-Performance CMOS Bus Interface Family      |

| Am29818A       | SSR <sup>TM</sup> Diagnostics/Pipeline Register |

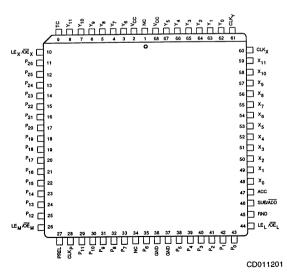

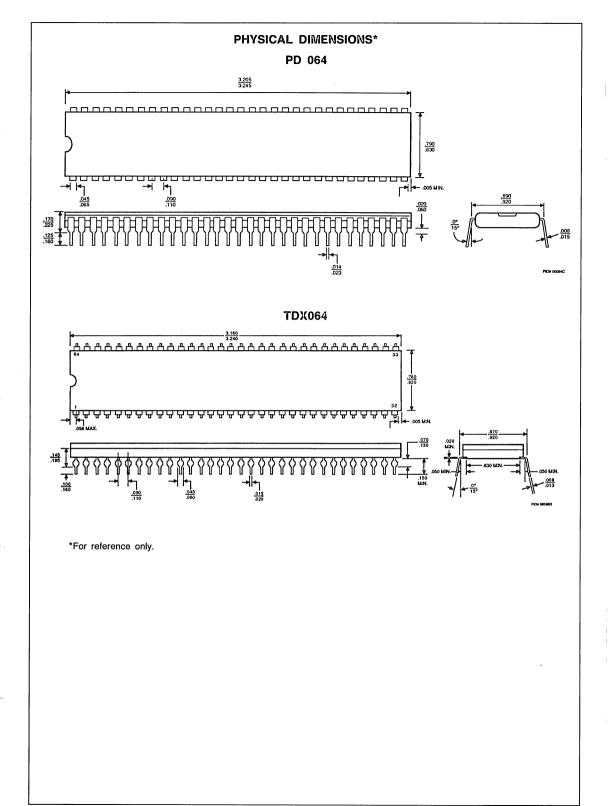

## CONNECTION DIAGRAMS Top View

DIPs

#### PLCC

Note: Pin 1 is marked for orientation.

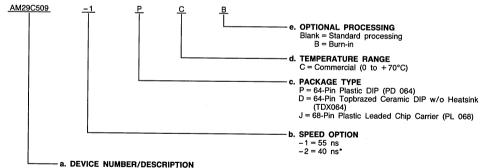

#### ORDERING INFORMATION

#### **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

Am29C509

12 x 12-Bit CMOS Multiplier/Accumulator

| Valid Combinations |                      |  |  |  |  |  |  |  |  |

|--------------------|----------------------|--|--|--|--|--|--|--|--|

| AM29C509           | PC, PCB, DC, DCB, JC |  |  |  |  |  |  |  |  |

| AM29C509-1         | DO DO 10             |  |  |  |  |  |  |  |  |

| AM29C509-2         | PC, DC, JC           |  |  |  |  |  |  |  |  |

\* Advance Information

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

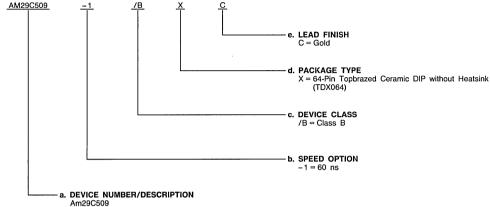

#### MILITARY ORDERING INFORMATION

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

12 x 12-Bit CMOS Multiplier/Accumulator

| Valid Cor  | mbinations |

|------------|------------|

| AM29C509   | /BXC       |

| AM29C509-1 | 7800       |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### PIN DESCRIPTION

#### ACC Accumulate (Input, Active HIGH)

When HIGH, the multiplier product is accumulated in the accumulator. When LOW, the multiplier product is written into the accumulator (see Table 2). The ACC control is loaded on the rising edge of CLKy or CLKy.

#### CLKp Clock (Input)

Loads data into the XTP, MSP, and LSP registers on the rising edge.

#### CLK<sub>X</sub>, CLK<sub>Y</sub> Clocks (Input)

Load X and Y data respectively and TC, RND, ACC, and SUB/ADD on the rising edge.

## LEL/OEL Load Enable Least/Output Enable Least (Input)

Active-HIGH Load Enable for the LSP-port during preloading. Active-LOW three-state control for the LSP-port during normal operation (see Table 1). (TSL\*)

## LE<sub>M</sub>/OE<sub>M</sub> Load Enable Most/Output Enable Most (Input)

Active-HIGH Load Enable for the MSP-port during preloading. Active-LOW three-state control for the MSP-port during normal operation (see Table 1). (TSM\*)

## LEX/OEX Load Enable Extended/Output Enable Extended (Input)

Active-HIGH Load Enable for the XTP-port during preloading. Active-LOW three-state control for the XTP-port during normal operation (see Table 1). (TSX\*)

#### PREL Preload (Input, Active HIGH)

When HIGH, data is preloaded into the specific output register when its respective load enable is HIGH. When LOW, the accumulator register is available at the P-port when the Output Enables are LOW (see Table 1).

\*TRW TDC1009 pin description.

## P<sub>0</sub>-P<sub>11</sub> Bidirectional Port (Input/Output, Three-State)

Product Output for the Least Significant Product (LSP) and input to preload the LSP register.

## P<sub>12</sub>-P<sub>23</sub> Bidirectional Port (Input/Output, Three-State)

Product Output for the Most Significant Product (MSP) and input to preload the MSP register.

## P<sub>24</sub> - P<sub>26</sub> Bidirectional Port (Input/Output, Three-State)

Product Output for Extended Product (XTP) and input to preload the XTP register.

#### RND Round (Input, Active HIGH)

When RND is HIGH, a bit with a weight of  $P_{11}$  is added to the multiplier product. This addition causes the MSP and XTP to be rounded toward positive infinity. RND is loaded on the rising edge of CLKx or CLKy.

#### SUB/ADD Subtraction/Addition (Input)

When HIGH, the accumulator contents are subtracted from the multiplier product and the result written back into the accumulator. When LOW, the multiplier product is added into the accumulator (see Table 2). The SUB/ADD control is loaded on the rising edge of CLKy or CLKy.

#### TC Two's Complement (Input, Active HIGH)

When HIGH, the X and Y inputs are defined as two's-complement data, or as unsigned data when TC is LOW. The TC control is loaded on the rising edge of  $CLK_X$  or  $CLK_Y$ .

## X<sub>0</sub> - X<sub>11</sub> Multiplier Data Input (Input, Active HIGH) Data is loaded into the X register on the rising edge of CLK<sub>X</sub>.

Y<sub>0</sub> - Y<sub>11</sub> Multiplier Data Input (Input, Active HIGH)

Data is loaded into the Y register on the rising edge of CLK<sub>Y</sub>.

#### **FUNCTIONAL DESCRIPTION**

The Am29C509 is a high-speed 12 x 12-bit CMOS multiplier/accumulator (MAC). It comprises a 12-bit parallel multiplier followed by a 27-bit accumulator. Two 12-bit input registers are provided for the X and Y operands. A third register stores two control bits, TC and RND. TC selects either a two's-complement or an unsigned magnitude format for both data inputs. The RND control, when HIGH, causes a bit to be added to the multiplier product with the weight of P<sub>11</sub>. This causes the most significant 12 bits of the product to be rounded to the value nearest to the full 24-bit product. Using the RND control once during an accumulation causes the most significant 15 bits of the accumulator to be rounded to the value nearest the full 27-bit accumulation. The TC/RND register is clocked whenever the X or Y input registers are clocked.

The 24-bit multiplier output is zero-filled or sign-extended as appropriate to provide a 27-bit input to the accumulator. The accumulator has four functions: the product may be loaded

into the accumulator, the product may be added into the accumulator value, the previous accumulator value may be subtracted from the product and the result stored in the accumulator, or the accumulator may be preloaded from an external source. The operation of the accumulator is controlled by the signals ACC, SUB/ADD, and PREL. ACC and SUB/ADD are stored in a register clocked whenever the X or Y registers are clocked. ACC in conjunction with SUB/ADD selects one of the first three accumulator functions (see Table 2). For output and preloading purposes, the accumulator is considered in three sections: Extended Product (XTP. P<sub>26</sub> - P<sub>24</sub>), controlled by LE<sub>X</sub>/OE<sub>X</sub>; Most Significant Product (MSP, P23-P12), controlled by LEM/OEM; and Least Significant Product (LSP, P<sub>11</sub> - P<sub>0</sub>), controlled by LE<sub>I</sub> /OE<sub>I</sub>. When PREL is LOW these controls are active-LOW Output Enables for the three-state output buffers. When PREL is HIGH, the output buffers automatically become high impedance, and the controls operate as active-HIGH Load Enables to the three sections of the accumulator to permit preloading of data applied to the bidirectional P-port, The P-port has 27 bits.

TABLE 1. PRELOAD FUNCTION

|      | LFv/                                 | I Fac/            | LE. /                                | Ou                                   | tput Regis                  | ster                          |

|------|--------------------------------------|-------------------|--------------------------------------|--------------------------------------|-----------------------------|-------------------------------|

| PREL | LE <sub>X</sub> /<br>OE <sub>X</sub> | LE <sub>M</sub> / | LE <sub>L</sub> /<br>OE <sub>L</sub> | ХТР                                  | MSP                         | LSP                           |

| 0    | 0                                    | 0                 | 0                                    | Q                                    | Q                           | Q                             |

| 0    | 0                                    | 0                 | 1 1                                  | Q                                    | Q                           | Z                             |

| 0    | 0                                    | 1                 | 0                                    | Q<br>Q                               | z                           | l a i                         |

| 0    | 0                                    | 1                 | 1                                    | l a                                  | Q<br>Q<br>Z<br>Z<br>Q       | Q<br>Z<br>Q<br>Z              |

| 0    | 1                                    | 0                 | 0                                    | z                                    | l a                         | l a l                         |

| 0    | 1                                    | 0                 | 1                                    | z                                    | ا م                         | Q<br>Z                        |

| 0    | 1                                    | 1                 | 0                                    | l z                                  | z                           | اما                           |

| 0    | 1                                    | 1                 | 1 1                                  | z                                    | z                           | ĺžĺ                           |

| 1    | 0                                    | 0                 | 0                                    | l z                                  | Q<br>Z<br>Z<br>Z<br>Z<br>PL | Q<br>Z<br>Z                   |

| 1 1  | 0                                    | 0                 | 1                                    | z                                    | z                           |                               |

| 1 1  | 0                                    | 1                 | 0                                    | z                                    | PL                          | z                             |

| 1 1  | 0                                    | 1                 | 1                                    | Q<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z | PL                          | PL                            |

| 1    | 1                                    | 0                 | 0                                    | PL                                   | PL<br>Z<br>Z                | PL<br>Z<br>PL<br>Z<br>PL<br>Z |

| 1    | 1                                    | 0                 | 1                                    | PL                                   | Z                           | PL I                          |

| 1 1  | 1                                    | 1                 | 0                                    | PL                                   | PL.                         | z                             |

| 1    | 1                                    | 1                 | 1                                    | PL                                   | PL                          | PL                            |

Key: Z = Output buffers at high impedance (disabled).

Q = Output buffers at low impedance. Contents of output register available through output ports.

PL = Output disabled. Preload data supplied to the output pins will be loaded into the output register at the rising edge of CLKp.

TABLE 2. ACCUMULATOR FUNCTION

| PREL | ACC | SUB/<br>ADD | P  | OPERATION |

|------|-----|-------------|----|-----------|

| L    | L   | X           | Q  | Load      |

| L    | Н   | L           | Q  | Add       |

| L    | Н   | Н           | Q  | Subtract  |

| Н    | Х   | Х           | PL | Preload   |

Key: H = HIGH L = LOW X = Don't Care

#### Am29C509 INPUT FORMATS

#### Fractional Two's-Complement Input

|                                        |   |    |    |                | X  | IN             |                |                |    |    |    |

|----------------------------------------|---|----|----|----------------|----|----------------|----------------|----------------|----|----|----|

| 11 10                                  | 0 | 9  | 8  | 7              | 6  | 5              | 4              | 3              | 2  | 1  | 0  |

| -2 <sup>11</sup> 2 <sup>1</sup> (Sign) | 0 | 29 | 28 | 2 <sup>7</sup> | 26 | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 22 | 21 | 20 |

#### **Unsigned Fractional Input**

|     |     |     |     |                 | X               | IN  |     |                 |                  |      |      |     |     |                 |     |                 | Y   | IN              |     |                 |                  |                  |                  |

|-----|-----|-----|-----|-----------------|-----------------|-----|-----|-----------------|------------------|------|------|-----|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|------------------|------------------|------------------|

| 11  | 10  | 9   | 8   | 7               | 6               | 5   | 4   | 3               | 2                | 1    | 0    | 11  | 10  | 9               | 8   | 7               | 6   | 5               | 4   | 3               | 2                | 1                | 0                |

| 2-1 | 2-2 | 2-3 | 2-4 | 2 <sup>-5</sup> | 2 <sup>-6</sup> | 2-7 | 2-8 | 2 <sup>-9</sup> | 2 <sup>-10</sup> | 2-11 | 2-12 | 2-1 | 2-2 | 2 <sup>-3</sup> | 2-4 | 2 <sup>-5</sup> | 2-6 | 2 <sup>-7</sup> | 2-8 | 2 <sup>-9</sup> | 2 <sup>-10</sup> | 2 <sup>-11</sup> | 2 <sup>-12</sup> |

### Unsigned Integer Input

|     |                 |    |    |    | X  | IN |    |    |    |    |    |

|-----|-----------------|----|----|----|----|----|----|----|----|----|----|

| 11  | 10              | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| 211 | 2 <sup>10</sup> | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 |

### Am29C509 **OUTPUT FORMATS** Two's-Complement Fractional Output

| ХТР                                           | MSP                                            | LSP                                                         |

|-----------------------------------------------|------------------------------------------------|-------------------------------------------------------------|

| 26 25 24                                      | 23 22 21 20 19 18 17 16 15 14 13 12            | 11 10 9 8 7 6 5 4 3 2 1 0                                   |

| -2 <sup>4</sup> 2 <sup>3</sup> 2 <sup>2</sup> | 21 20 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 2-10 | 2-11 2-12 2-13 2-14 2-15 2-16 2-17 2-18 2-19 2-20 2-21 2-22 |

| (Sign)                                        |                                                |                                                             |

#### Two's-Complement Integer Output

| XTP                                                     | MSP                                             | LSP                                   |

|---------------------------------------------------------|-------------------------------------------------|---------------------------------------|

| 26 25 24                                                | 23 22 21 20 19 18 17 16 15 14 13 12             | 11 10 9 8 7 6 5 4 3 2 1 0             |

| -2 <sup>26</sup> 2 <sup>25</sup> 2 <sup>24</sup> (Sign) | 223 222 221 220 219 218 217 216 215 214 213 212 | 211 210 29 28 27 26 25 24 23 22 21 20 |

#### **Unsigned Fractional Output**

|    | X٦                      | ΤP |    |     |     |     |     |     | MS  | SP. |     |     |      |      |      |      |      |                  |      |                  | LS   | P    |      |                  |      |      |                  |

|----|-------------------------|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------------------|------|------------------|------|------|------|------------------|------|------|------------------|

| 26 | 2                       | 25 | 24 | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  | 15  | 14   | 13   | 12   | 11   | 10   | 9                | 8    | 7                | 6    | 5    | 4    | 3                | 2    | 1    | 0                |

| 22 | 2 2                     | 21 | 20 | 2-1 | 2-2 | 2-3 | 2-4 | 2-5 | 2-6 | 2-7 | 2-8 | 2-9 | 2-10 | 2-11 | 2-12 | 2-13 | 2-14 | 2 <sup>-15</sup> | 2-16 | 2 <sup>-17</sup> | 2-18 | 2-19 | 2-20 | 2 <sup>-21</sup> | 2-22 | 2-23 | 2 <sup>-24</sup> |

|    | Unsigned Integer Output |    |    |     |     |     |     |     |     |     |     |     |      |      |      |      |      |                  |      |                  |      |      |      |                  |      |      |                  |

| ХТР         | MSP                                             | LSP                                                                           |

|-------------|-------------------------------------------------|-------------------------------------------------------------------------------|

| 26 25 24    | 23 22 21 20 19 18 17 16 15 14 13 12             | 11 10 9 8 7 6 5 4 3 2 1 0                                                     |

| 226 225 224 | 223 222 221 220 219 218 217 216 215 214 213 212 | $2^{11}$ $2^{10}$ $2^9$ $2^8$ $2^7$ $2^6$ $2^5$ $2^4$ $2^3$ $2^2$ $2^1$ $2^0$ |

|             |                                                 |                                                                               |

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65 to +150°C                           | ) |

|-----------------------------------------------------------|---|

| Case Temperature (T <sub>C</sub> ) Under Bias55 to +125°C | ) |

| Supply Voltage to Ground Potential                        |   |

| Continuous                                                | / |

| DC Voltage Applied to Outputs For                         |   |

| High Output State0.3 to +V <sub>CC</sub> + 0.3 V          | / |

| DC Input Voltage0.3 to +V <sub>CC</sub> + 0.3 V           | / |

| DC Output Current, Into LOW Outputs30 mA                  | ١ |

| DC Input Current10 to +10 mA                              | ١ |

|                                                           |   |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commercial (C) Devices                         |

|------------------------------------------------|

| Ambient Temperature (TA) 0 to +70°C            |

| Supply Voltage (VCC) 4.50 to 5.50 V            |

| Military* (M) Devices                          |

| Case Temperature (T <sub>C</sub> )55 to +125°C |

| Supply Voltage (Vcc) +4.5 V to +5.5 V          |

Operating ranges define those limits between which the functionality of the device is guaranteed.

\* Military product 100% tested at  $T_C = +25$ °C, +125°C, and

DC CHARACTERISTICS over operating range unless otherwise specified (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol                                           | Parameter<br>Description                                          | Tes                                                                             | Min.                      | Max.         | Unit |    |

|---------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------|--------------|------|----|

| V <sub>OH</sub>                                               | Output HIGH Voltage                                               | V <sub>CC</sub> = Min.,<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | I <sub>OH</sub> = -0.4 mA |              | 2.4  | ٧  |

| V <sub>OL</sub>                                               | Output LOW Voltage                                                | V <sub>CC</sub> = Min.,<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | I <sub>OL</sub> = 4.0 mA  |              | 0.5  | ٧  |

| V <sub>IH</sub>                                               | Guaranteed Input Logical HIGH<br>Voltage (Note 2)                 |                                                                                 |                           |              |      | V  |

| V <sub>IL</sub> Guaranteed Input Logical LOW Voltage (Note 2) |                                                                   |                                                                                 |                           |              | 0.8  | ٧  |

| l <sub>IL</sub>                                               | Input LOW Current V <sub>CC</sub> = Max., V <sub>IN</sub> = 0.5 V |                                                                                 | V                         |              | -10  | μΑ |

| lį                                                            | Input HIGH Current                                                | $V_{CC} = Max.$ , $V_{IN} = V_{CC} - 0.5 \text{ V}$                             |                           |              | 10   | μΑ |

| lozh                                                          | Off-State (High Impedance)                                        | V                                                                               | V <sub>O</sub> = 2.4 V    |              | 10   |    |

| lozL                                                          | Output Current                                                    | V <sub>CC</sub> = Max.                                                          | V <sub>O</sub> = 0.5 V    |              | 10   | μΑ |

| lcc                                                           | Static Power Supply Current (Note 3)                              | $V_{CC} = Max., V_{IN} = V_{CC}$<br>$I_O = 0 \mu A (CMOS)$                      |                           |              |      | mA |

| C <sub>PD</sub>                                               | Power Dissipation Capacitance<br>(Note 4)                         | V <sub>CC</sub> = 5.0 V, T <sub>A</sub> = 25°0<br>No Load                       | 89                        | 890 pF Typic |      |    |

Notes: 1. V<sub>CC</sub> conditions shown as Min. or Max. refer to the military (±10%) or commercial (±10%) V<sub>CC</sub> limits.

2. These input levels provide zero-noise immunity and should only be statically tested in a noise-free environment (not functionally tested).

3. Worst-case I<sub>CC</sub> is measured at the lowest temperature in the specified operating range.

CpD determines the no-load dynamic current consumption: I<sub>CC</sub> (Total) = I<sub>CC</sub> (Static) + CpD V<sub>CC</sub> f, where f is the switching frequency of the majority of the internal nodes, normally one-half of the clock frequency.

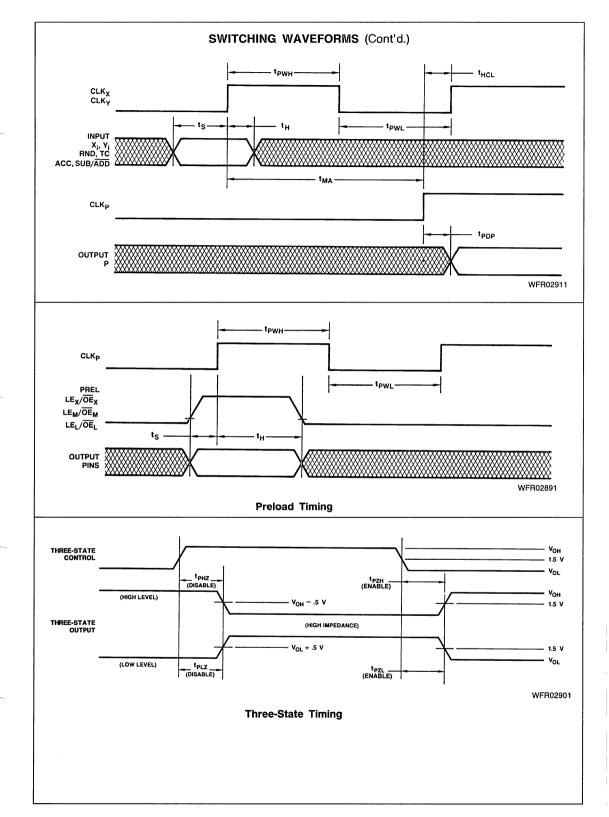

## SWITCHING CHARACTERISTICS over COMMERCIAL operating range

|     | Parameter Parameter |                                                                                                              | Test                                                                 | 29C509     |      | 29C509-1 |      | 29C509-2 |      |      |      |

|-----|---------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------|------|----------|------|----------|------|------|------|

| No. | Symbol              | Description                                                                                                  |                                                                      | Conditions | Min. | Max.     | Min. | Max.     | Min. | Max. | Unit |

| 1   | t <sub>MA</sub>     | Multiply Accumulate Time                                                                                     |                                                                      |            |      | 70       |      | 55       | Ш    | 40   | ns   |

| 2   | ts                  | X <sub>i</sub> , Y <sub>i</sub> , RND, TC, ACC, SUI<br>Setup Time                                            | B/ <del>ADD</del>                                                    |            | 16   |          | 14   |          | 12   | 2    | ns   |

| 3   | tH                  | X <sub>i</sub> , Y <sub>i</sub> , RND, TC, ACC, SUI<br>Hold Time                                             | X <sub>i</sub> , Y <sub>i</sub> , RND, TC, ACC, SUB/ADD<br>Hold Time |            | 3    |          | 3    |          | 3    |      | ns   |

| 4   | ts                  | PREL Setup Time                                                                                              |                                                                      |            | 19   |          | 16   |          | 13   |      | ns   |

| 5   | tн                  | PREL Hold Time                                                                                               |                                                                      |            | 0    |          | 0    |          | 0_   | 1    | ns   |

| 6   | t <sub>PWH</sub>    | Clock Pulse Width HIGH                                                                                       |                                                                      |            | 15   |          | 15   |          | 15   | Ŋ.   | ns   |

| 7   | tpwL                | Clock Pulse Width LOW                                                                                        |                                                                      |            | 15   |          | 15   |          | 15   |      | ns   |

| 8   | tPDP                | Output Clock to P                                                                                            |                                                                      |            |      | 26       |      | 24       |      | 🥬 20 | ns   |

| 9   | t <sub>PHZ</sub>    | LE <sub>X</sub> /OE <sub>X</sub> , LE <sub>M</sub> /OE <sub>M</sub> ,<br>LE <sub>I</sub> /OE <sub>I</sub> to | HIGH to Z                                                            |            |      | 25       |      | 20       |      | 17   | ns   |

| 10  | t <sub>PLZ</sub>    | P Disable Time                                                                                               | LOW to Z                                                             | 40 -5      |      | 25       |      | 20       | 52   | 17   | ns   |

| 11  | <sup>t</sup> PZH    | LEX/OEX, LEM/OEM,<br>LEL/OEL to                                                                              | Z to HIGH                                                            | 40 pF      |      | 30       |      | 25       |      | 22   | ns   |

| 12  | tPZL                | P Enable Time                                                                                                | Z to LOW                                                             |            |      | 30       |      | 25       |      | 22   | ns   |

| 13  | tHCL                | Relative Hold Time                                                                                           |                                                                      |            | 0    |          | 0    |          | 0    |      | ns   |

**SWITCHING CHARACTERISTICS** over **MILITARY** operating range (for APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted)

|     | Donomotor                                 | Doromotor                                                                                                    | Tool               | 29C509 |      | 29C509-1 |      |      |    |

|-----|-------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------|--------|------|----------|------|------|----|

| No. | Parameter Parameter<br>Symbol Description |                                                                                                              | Test<br>Conditions | Min.   | Max. | Min.     | Max. | Unit |    |

| 1   | t <sub>MA</sub>                           | Multiply Accumulate Time                                                                                     |                    |        |      | 75       |      | 60   | ns |

| 2   | ts                                        | X <sub>i</sub> , Y <sub>i</sub> , RND, TC, ACC, SUB/7                                                        | ADD                |        | 16   |          | 16   |      | ns |

| 3   | tH                                        | X <sub>i</sub> , Y <sub>i</sub> , RND, TC, ACC, SUB/7<br>Hold Time                                           |                    | 3      |      | 3        |      | ns   |    |

| 4   | ts                                        | PREL Setup Time                                                                                              | PREL Setup Time    |        |      |          | 16   |      | ns |

| 5   | tн                                        | PREL Hold Time                                                                                               |                    | 0      |      | 0        |      | ns   |    |

| 6   | tpwH                                      | Clock Pulse Width HIGH                                                                                       |                    | 20     |      | 15       |      | ns   |    |

| 7   | tpwL                                      | Clock Pulse Width LOW                                                                                        |                    | 20     |      | 15       |      | ns   |    |

| 8   | t <sub>PDP</sub>                          | Output Clock to P                                                                                            |                    |        | 30   |          | 25   | ns   |    |

| 9   | tpHZ                                      | LE <sub>X</sub> /OE <sub>X</sub> , LE <sub>M</sub> /OE <sub>M</sub> ,<br>LE <sub>L</sub> /OE <sub>L</sub> to | HIGH to Z          |        |      | 25       |      | 21   | ns |

| 10  | t <sub>PLZ</sub>                          | P Disable Time                                                                                               | LOW to Z           | 40 pF  |      | 25       |      | 21   | ns |

| 11  | tpzH                                      | LEX/OEX, LEM/OEM,                                                                                            | Z to HIGH          |        |      | 30       |      | 27   | ns |

| 12  | t <sub>PZL</sub>                          | LEL/OEL to P Enable Time                                                                                     | Z to LOW           |        |      | 30       |      | 27   | ns |

| 13  | tHCL                                      | Relative Hold Time                                                                                           |                    | 0      |      | 0        |      | ns   |    |

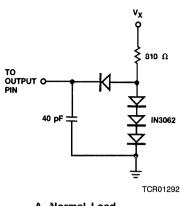

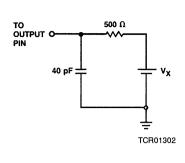

#### SWITCHING TEST CIRCUITS

#### A. Normal Load

B. Three-State Delay Load

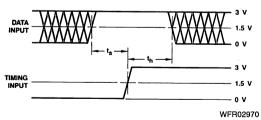

#### **SWITCHING TEST WAVEFORMS**

| Test                  | V <sub>X</sub> | Output Waveform — Measurement Level |

|-----------------------|----------------|-------------------------------------|

| All t <sub>PD</sub> s | Vcc            | V <sub>OH</sub> 1.5 V               |

| <sup>t</sup> PHZ      | 0.0 V          | VoH 0.5 V                           |

| t <sub>PLZ</sub>      | 2.6 V          | V <sub>OL</sub> 0.5 V 2.6 V         |

| <sup>t</sup> PZH      | 0.0 V          | 0.0 V ———— VOH                      |

| t <sub>PZL</sub>      | 2.6 V          | 2.6 V 1.5 V V <sub>OL</sub>         |

|                       |                | WFR02812                            |

## LOW-HIGH-LOW PULSE HIGH-LOW-HIGH PULSE WFR02851

**B. Pulse Width**

#### A. Setup and Hold Time

Notes: 1. Diagram shown for HIGH data only.

- Output transition may be opposite sense.

- 2. Cross hatched area is "Don't Care" condition.

#### Test Philosophy and Methods

The following points give the general philosophy that we apply to tests that must be properly engineered if they are to be implemented in an automatic environment. The specifics of what philosophies applied to which test are shown in the data sheet

- Ensure the part is adequately decoupled at the test head. Large changes in V<sub>CC</sub> current as the device switches may cause erroneous function failures due to V<sub>CC</sub> changes.

- 2. Do not leave inputs floating during any tests, as they may start to oscillate at high frequency.

- 3. Do not attempt to perform threshold tests at high speed. Following an output transition, ground current may change by as much as 400 mA in 5–8 ns. Inductance in the ground cable may allow the ground pin at the device to rise by hundreds of millivolts momentarily.

- 4. Use extreme care in defining input levels for AC tests. Many inputs may be changed at once, so there will be significant noise at the device pins which may not actually reach  $V_{IL}$  or  $V_{IH}$  until the noise has settled. AMD recommends using  $V_{IL} \leqslant 0$  V and  $V_{IH} \geqslant 3.0$  V for AC tests.

- To simplify failure analysis, programs should be designed to perform DC, Function, and AC tests as three distinct groups of tests.

- 6. Capacitive Loading for AC Testing

Automatic testers and their associated hardware have stray capacitance that varies from one type of tester to another but is generally around 50 pF. This makes it impossible to make direct measurements of parameters that call for smaller capacitive load than the associated stray capacitance. Typical examples of this are the so-called "float delays," which measure the propagation delays into the high-impedance state and are usually specified at a load capacitance of 5.0 pF. In these cases, the test is peformed at the higher load capacitance (typically 50 pF), and engineering correlations based on data taken with a bench setup are used to predict the result at the lower capacitance.

Similarly, a product may be specified at more than one capacitive load. Since the typical automatic tester is not capable of switching loads in mid-test, it is impossible to make measurements at <u>both</u> capacitances even though

they may both be greater than the stray capacitance. In these cases, a measurement is made at one of the two capacitances. The result at the other capacitance is predicted from engineering correlations based on data taken with a bench setup and the knowledge that certain DC measurements (I<sub>OH</sub>, I<sub>OL</sub>, for example) have already been taken and are within spec. In some cases, special DC tests are performed in order to facilitate this correlation.

#### 7. Threshold Testing

The noise associated with automatic testing (due to the long inductive cables) and the high gain of the tested device when in the vicinity of the actual device threshold, frequently give rise to oscillations when testing high-speed circuits. These oscillations are not indicative of a reject device, but instead, of an overtaxed test system. To minimize this problem, thresholds are tested at least once for each input pin. Thereafter, "hard" high and low levels are used for other tests. Generally this means that function and AC testing are performed at "hard" input levels rather than at  $V_{\rm IL}$  Max. and  $V_{\rm IH}$  Min.

#### 8. AC Testing

Occasionally parameters are specified that cannot be measured directly on automatic testers because of tester limitations. Data input hold times often fall into this category. In these cases, the parameter in question is guaranteed by correlating these tests with other AC tests that have been performed. These correlations are arrived at by the cognizant engineer using data from precise bench measurements in conjunction with the knowledge that certain DC parameters have already been measured and are within spec.

In some cases, certain AC tests are redundant since they can be shown to be predicted by other tests that have already been performed. In these cases, the redundant tests are not performed.

#### 9. Output Short-Circuit Testing

When performing  $I_{OS}$  tests on devices containing RAM or registers, great care must be taken that undershoot caused by grounding the high-state output does not trigger parasitic elements which in turn cause the device to change state. In order to avoid this effect, it is common to make the measurement at a voltage ( $V_{output}$ ) that is slightly above ground. The  $V_{CC}$  is raised by the same amount so that the result (as confirmed by Ohm's law and precise bench testing) is identical to the  $V_{OUT} = 0$ ,  $V_{CC} = Max$ . case.

#### SWITCHING WAVEFORMS

#### Key to Switching Waveforms

KS000010

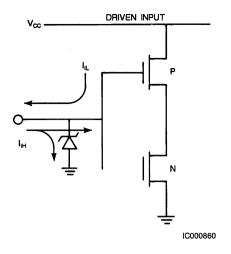

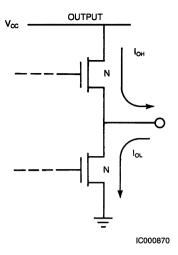

#### INPUT/OUTPUT CIRCUIT DIAGRAMS

$C_O \approx 5.0$  pF, all outputs

#

Advanced Micro Devices reserves the right to make changes in its product without notice in order to improve design or performance characteristics. The performance characteristics listed in this document are guaranteed by specific tests, correlated testing, guard banding, design and other practices common to the industry. For specific testing details, contact your local AMD sales representative. The company assumes no responsibility for the use of any circuits described herein.

PID # 06753I