# **Am29PL142**

Field-Programmable Controller (FPC)

#### DISTINCTIVE CHARACTERISTICS

- Implements complex state machines

- 8 conditional inputs, 16 outputs

- 128-word by 34-bit PROM

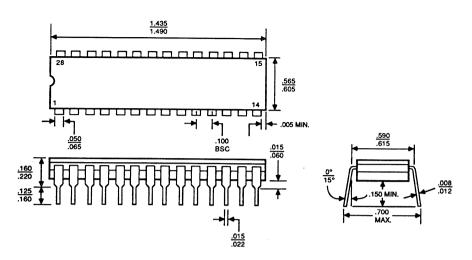

- Up to 20-MHz clock rate, 28-pin DIP

- 28 instructions

- Conditional branching

- Conditional looping

- Conditional subroutine call

- Multiway branch

- Output instruction presents counter contents at the control outputs for implementing a larger class of statemachine designs

- A controller-expansion (EXP) fuse provides address to external registered PROMs for more than 16 outputs

- SSR fuse configures Serial Shadow Register (SSR<sup>TM</sup>) diagnostics on chip

#### GENERAL DESCRIPTION

The Am29PL142 is a single-chip Field-Programmable Controller (FPC) that allows implementation of complex state machines and controllers by programming the appropriate sequence of instructions. Jumps, loops, and subroutine calls, conditionally executed based on the test inputs, provide the designer with powerful control flow primitives.

Intelligent control may be distributed throughout the system by using FPCs to control various self-contained functional units, such as register file/ALU, I/O, interrupt, diagnostic, and bus-control units.

An address sequencer, the heart of the FPC, provides the address to an internal 128-word by 34-bit PROM. The fuse programming algorithm is almost identical to that used for AMD's Programmable Array Logic family.

The Am29PL142 can be expanded to address external registered PROMs by using the EXP fuse option to output the program-memory address through the control output pins P[14:8].

A counter register is provided and an instruction is available to present the counter-register contents at the control outputs P[14:8]. Using this, the control outputs can be dynamically modified for implementing a larger class of state machines.

As an option, the Am29PL142 may be programmed to have on-chip SSR diagnostics capability. Instructions can be serially shifted in, executed, and the results shifted out to facilitate system diagnostics.

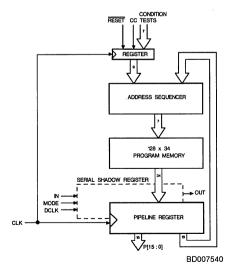

#### SIMPLIFIED BLOCK DIAGRAM

## **RELATED AMD PRODUCTS**

| Part No.      | Description                                                       |

|---------------|-------------------------------------------------------------------|

| Am29C01-1     | High-Speed CMOS 4-Bit Microprocessor Slice                        |

| Am29C10A-1    | High-Speed CMOS 12-Bit Sequencer                                  |

| Am29C101-1    | High-Speed CMOS 16-Bit Microprocessor                             |

| Am29114       | 8-Level Real-Time Interrupt Controller (Expandable)               |

| Am29116       | 16-Bit Bipolar Microprocessor (Supports 100 ns System Cycle Time) |

| Am29C116      | CMOS Version of Am29116                                           |

| Am29C116-1/-2 | High-Performance Versions of Am29C116                             |

| Am29117       | 2-Port Version of Am29116                                         |

| Am29C117      | CMOS Version of Am29117                                           |

| Am29C117-1/-2 | High-Performance Versions of Am29C117                             |

| Am29118       | 8-Bit Am29116 I/O Support                                         |

| Am29130       | 16-Bit Barrel Shifter (Expandable)                                |

| Am29PL131     | 24-Pin Slim DIP Version of the Am29PL141                          |

| Am29LPL131    | Low Power Version of Am29PL131                                    |

| Am2914        | Vectored Priority Interrupt Controller                            |

| Am29LPL141    | Low-Power Version of the Am29PL141                                |

| Am29PL141     | Field-Programmable Controller                                     |

| Am29CPL141    | CMOS Version of the Am29PL141                                     |

| Am29CPL144    | CMOS High-Density Field-Programmable Controller                   |

| Am29C325      | CMOS 32-Bit Floating Point Processor                              |

| Am29C327      | CMOS Double-Precision Floating Point Processor                    |

| Am29337       | 16-Bit Bounds Checker                                             |

| Am2940        | DMA Address Generator                                             |

| Am29C516A-1   | 35-ns CMOS 16 x 16 Multiplier                                     |

| Am29818       | SSR Diagnostics Pipeline Register                                 |

| Am29C818      | CMOS Version of the Am29818                                       |

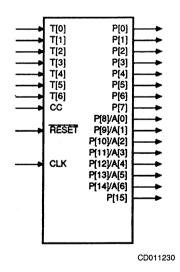

## **CONNECTION DIAGRAM Top View**

CD011100

Note: Pin 1 is marked for orientation.

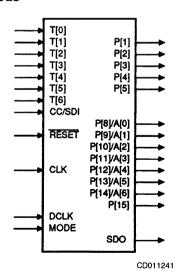

#### LOGIC SYMBOLS

**Normal Configuration**

**SSR Diagnostics Configuration**

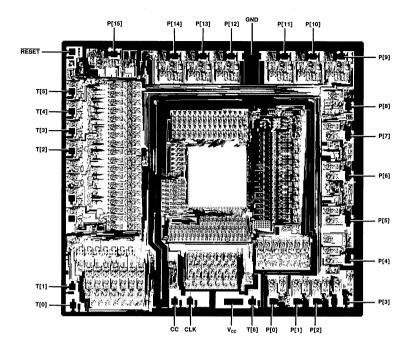

## **METALLIZATION AND PAD LAYOUT**

$\label{eq:Die Size: 0.261'' x 0.238''}$  Gate Count: 600 Equivalent Gates and 4K of PROM

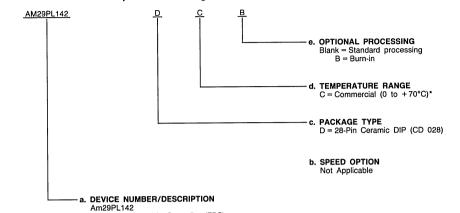

#### ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range e. Optional Processing

Field Programmable Controller (FPC)

#### Valid Combinations AM29PL142 DC, DCB

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

\*The Commercial Operating Range is 0 to +85°C Case temperature for the Leadless Chip Carrier Package, due to the power constraints of that particular package.

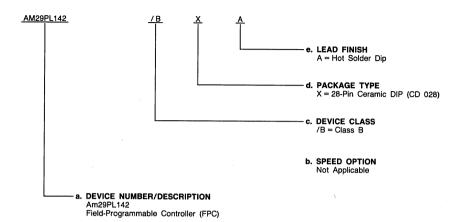

#### MILITARY ORDERING INFORMATION **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type e. Lead Finish

| Valid Combinations |       |  |  |  |  |

|--------------------|-------|--|--|--|--|

| AM29PL142          | / BXA |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### **Group A Tests**

Group A tests consists of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### PIN DESCRIPTION

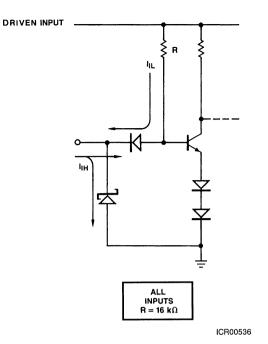

#### CC[SDI] Condition Code — TEST (Input)

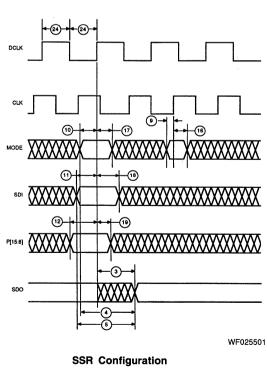

Internally synchronized condition code test input is selected through the 4-bit test-condition select field. In the SSR mode, CC is also the Serial Data Input (SDI).

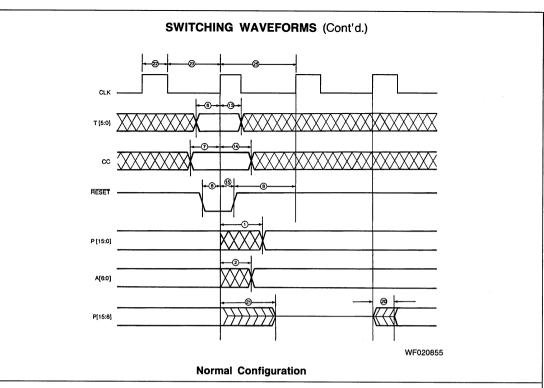

#### CLK Clock (Input)

The rising edge of the clock latches the PC register, count register, stack register, instruction-pipeline register, test-input register, CC register, reset register, and the EQ flag.

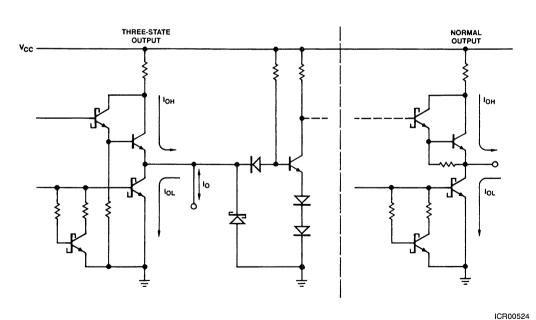

## P[15], P[14:8]/A[6:0] Upper General-Purpose Control (Outputs)

The upper eight general-purpose control outputs are enabled by the OE bit from the instruction-pipeline register. When OE is HIGH, these outputs are enabled; when OE is LOW, they are three stated.

A controller Expansion (EXP) fuse can be programmed to set pins P[14:8] to output the program address A[6:0] from the PC MUX. These can be used to address external registered PROMs to provide more control outputs.

The contents of the internal count register (CREG) can also be routed to the control output pins P[14:8], using the

OUTPUT instruction. Thus, the control outputs can be changed dynamically.

## P[7:0] Lower General-Purpose Control (Outputs)

The lower eight general-purpose control outputs are permanently enabled. In the SSR diagnostics mode, P[7] becomes the diagnostic clock input (DCLK), P[6] becomes the diagnostic control input (MODE), and P[0] becomes the Serial Data Output (SDO). Both SDO and SDI are clocked by DCLK under control of the MODE bit.

#### RESET Internally Synchronized Reset (Input)

After it goes LOW, RESET is latched internally on the first rising edge of the clock. During the first clock cycle, the PC MUX is set to all ones (address 127). On the next rising edge of the clock, the program-memory contents at location 127 are loaded into the pipeline register. The EQ flag is also cleared at this time.

#### Γ[6:0] Internally Synchronized Test (Inputs)

In conditional instructions, these inputs are selected according to the 4-bit test condition select field. The inputs T[6:0] can also be used either as a branch address or as a value to be loaded into CREG depending on the instruction.

#### **FUNCTIONAL DESCRIPTION**

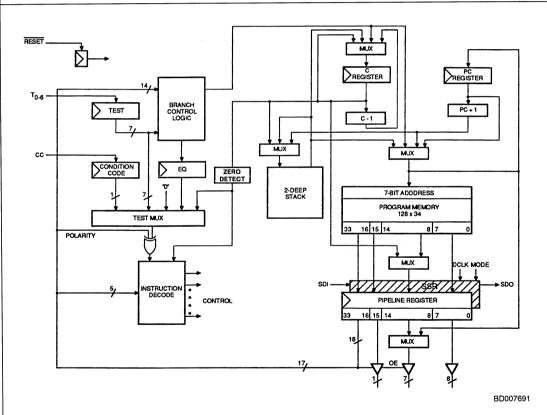

Figure 1, the detailed block diagram of the Am29PL142 FPC, shows logic blocks and interconnecting buses that permit parallel performance of different operations in a single instruction. The FPC consists of four main logic blocks: the program memory, address control logic, condition code selection logic, and instruction decode. A fifth optional block is the Serial Shadow Register (SSR).

The program memory contains the user-defined instruction flow and output sequence. The address control logic addresses the program memory. This control logic supports highlevel instruction functions including conditional branches, subroutine calls and returns, loops, and multiway branches. The condition code selection logic selects the condition code input to be tested when a conditional instruction is executed. The polarity of the selected condition code input is controlled by the POL bit in the microword. The instruction decode generates the control signals necessary to perform the instruction specified by the instruction part (P[33:16]) of the microword. The SSR enables in-system testing to isolate problems down to the IC level.

#### **Program Memory**

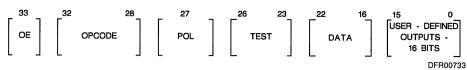

The FPC program memory is a 128-word by 34-bit PROM with a 34-bit pipeline register at its output. The upper 18 bits (P[33:16]) of the pipeline register are internal to the FPC and form the instruction to control address sequencing. The format for instructions is: a 1-bit synchronous Output Enable OE, a 5-bit OPCODE, a 1-bit test polarity select POL, a 4-bit TEST condition select field, and a 7-bit immediate DATA field. The DATA field is used to provide branch addresses, test input masks, and counter values.

The lower 16 bits (P[15:0]) of the pipeline register are brought out as user-defined, general purpose control outputs. The upper eight control outputs (P[15:8]) are three-stated when OE is programmed as a LOW. The lower eight control bits (P[7:0]) are always enabled.

Outputs P[14:8] will contain the next instruction address when the optional EXP fuse is programmed. The contents of the CREG can be sent to outputs P[14:8], regardless of whether the EXP fuse is programmed.

Figure 1. Am29PL142 Detailed Block Diagram

#### Address Control Logic

The address control logic consists of four logic blocks:

PC GRP – the program counter multiplexer (PC MUX), program counter register (PC) and combinatorial incrementer (PC + 1)

STACK – subroutine multiplexer (S MUX) with a 2-word by 7-bit-wide stack

CNTR - count register (CREG) with counter multiplexer (C MUX), combinatorial decrementer (CREG - 1), and zero detect on count register

GOTO - multifunction branch control logic

#### PC GRP

The PC GRP consists of a 4:1 multiplexer, a program counter (PC) register, and a 7-bit combinatorial incrementer (PC + 1). It selects the PC, PC + 1, the branch address, or the top of stack as the next instruction address input to the program memory and the PC.

RESET is latched internally on the first rising edge of the clock after it goes LOW. During the first clock cycle, the PC MUX is set to all ones (address 127). On the next rising edge of the clock, the program memory contents at location 127 are loaded into the pipeline register.

#### STACK

The stack block consists of a 3:1 multiplexer (S MUX) that stores the data into the topmost location of the stack. The S MUX chooses from three sources: PC + 1, count register, and the top of the stack (for holding). PC + 1 is the input source when doing subroutine calls. PC MUX is the output destination when a return-from-subroutine instruction is performed.

#### CNTR

The CNTR block consists of a 4:1 multiplexer (C MUX) feeding a 7-bit count register (CREG) which, in turn, outputs to a combinatorial decrementer (CREG – 1) and a zero-detect circuit. The CNTR block is typically used for timing functions and iterative loop counting.

The C MUX has the following input sources: top of stack, the branch-logic output, CREG - 1, and the CREG (for holding).

#### GOTO

The GOTO (branch control) logic block performs three functions:

It provides a 7-bit value directly from the DATA field in the instruction pipeline register.

It provides a 7-bit branch address from the TEST inputs T[6:0] masked by the DATA field from the instruction pipeline register.

It compares the TEST inputs T[6:0] (masked by the DATA field in the instruction pipeline register) with the constant field comparison (see Instruction Format) in the pipeline register.

The EQ flip-flop is set according to the following expression:

EQ = [(TEST .AND. DATA) .XNOR. constant] .OR. EQ

The EQ flag can be tested by the condition-code selection logic. Multiple tests of any group of T inputs in a manner analogous to sum-of-products can be performed, since a no-

match comparison does not reset the EQ flag. Any conditional branch on EQ will reset the EQ flag. Conditional returns on EQ will not change the EQ flag. RESET input LOW will reset the EQ flag.

NOTE: A zero in the DATA field blocks the corresponding bit in the TEST field; a one activates the corresponding bit.

The constant field bits that correspond to masked test field bits must be zero. A zero is substituted for masked test field bits. This masking operation is independent of the value of the POL bit.

#### **Condition Code Selection Logic**

The condition code selection logic consists of a 16:1 multiplexer. The 16 condition inputs are the seven test bits, the condition code input CC, the EQ flag, CREG ZERO status, and six UNCOND test conditions connected to zero for the unconditional mode. The TEST field in the pipeline register (P[26:23]) selects one of the 16 conditions. If one of the UNCOND is chosen, and the POL bit is a one, the instruction is executed with a "forced PASS" condition. If one of the UNCOND is chosen, and the POL bit is a zero, the instruction is executed with a "forced FAIL" condition. See opcode descriptions for more details.

The polarity bit POL in P[27] of the instruction pipeline register allows the user to test for either pass/true or fail/false condition. Refer to Table 2 for details.

#### Instruction Decode

The instruction decoder is a PLA that generates the control for 28 different instructions. The decoder inputs include the OPCODE field P[32:28], the zero detection flag from the CNTR, and the selected test condition code from the condition code select logic.

#### **Operational Modes**

The Am29PL142 operates as a 7-bit microcontroller in normal mode. By programming the EXP fuse, the output pins P[14:8] can be used as the program address for external registered PROMs. By using external registered PROMs in conjunction with the Am29PL142, control outputs wider than 16 bits can be obtained.

The SSR option provides on-chip diagnostic capabilities for insystem testing. This is accomplished by setting the appropriate conditions on the MODE control input. Note that this can only be done if the SSR diagnostics fuse has been programmed. See Table 1.

The SSR diagnostics configuration activates a 34-bit-wide, D-type register, called a "shadow" register, on the pipeline register inputs. The shadow register can be serially loaded from the SDI pin, parallel loaded from the pipeline register, or held. The pipeline register can be loaded from the program memory in normal operation or from the shadow register during diagnostics. A redefinition of four device pins is required to control the different diagnostics functions. CC also functions as the Serial Data Input (SDI), P[0] becomes the serial data output (SDO), P[7] becomes the diagnostic clock (DCLK), and P[6] becomes the diagnostic mode control (MODE). The various diagnostic and normal modes are shown in Table 1.

Serially loading a test instruction into the shadow register and parallel loading the shadow register contents into the pipeline register forces execution of the test instruction. The test result can then be clocked into the pipeline register, as in normal operation mode, parallel loaded into the shadow register, and serially shifted out for system diagnostics.

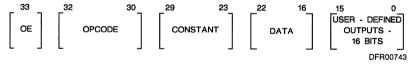

#### Am29PL142 General Instruction Format

WHERE:

OE = Synchronous Output Enable for P[15:8].

OPCODE

= A 5-bit opcode field for selecting one of the 27 single data-field instructions.

POL

A 1-bit test condition polarity select.0 = Test for true (HIGH) condition.

1 = Test for false (LOW) condition.

TEST

= A 4-bit test condition select.

| TEST[3:0]  0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 | UNDER TEST |

|--------------------------------------------------------------|------------|

| 0000                                                         | T[0]       |

| 0001                                                         | T[1]       |

| 0010                                                         | T[2]       |

| 0011                                                         | T[3]       |

| 0100                                                         | T[4]       |

| 0101                                                         | T[5]       |

| 0110                                                         | T[6]       |

| 0111                                                         | CC         |

| 1000                                                         | EQ         |

| 1001                                                         | CREG ZERO  |

| 1010-1111                                                    | UNCOND [0] |

The polarity bit POL in an instruction allows the user to test for a pass/true or fail/false condition as shown in Table 2. An unconditional true is set by selecting UNCOND and POL = 1.

DATA

= A 7-bit conditional branch address, test input mask, or counter value field designated as PL in instruction mnemonics.

The special two data field comparison instruction format is shown below:

## Am29PL142 Comparison Instruction Format

WHERE:

OE = Synchronous Output Enable for P[15:8].

OPCODE = Compare instruction (binary 100).

CONSTANT = A 7-bit constant for equal to comparison with  $T^*M$ .

DATA = A 7-bit mask field for masking the incoming T[6:0] inputs.

### TABLE 1.

|      |      |          |       |     | Outputs                                                  |                                   |                                                 |

|------|------|----------|-------|-----|----------------------------------------------------------|-----------------------------------|-------------------------------------------------|

|      | Inpi | uts      |       |     | Outputs                                                  |                                   |                                                 |

| SDI  | MODE | DCLK     | CLK   | SDO | Shadow<br>Register                                       | Pipeline<br>Register              | Operation                                       |

| D    | L    | <b>†</b> | H,L,↓ | So  | S <sub>i-1</sub> ← S <sub>i</sub><br>S <sub>31</sub> ← D | Hold                              | Serial Right Shift Register                     |

| CC** | L    | H,L,↓    | 1     | L   | Hold                                                     | P <sub>i</sub> ←PROM <sub>i</sub> | Load Pipeline Register from PROM                |

| L    | Н    | <b>†</b> | H,L,↓ | L   | S <sub>i</sub> ←P <sub>i</sub>                           | Hold                              | Load Shadow Register from Pipeline*<br>Register |

| Х    | н    | H,L,↓    | 1     | SDI | Hold                                                     | P <sub>i</sub> ←S <sub>i</sub>    | Load Pipeline Register from Shadow<br>Register  |

| Н    | Н    | 1        | H,L,↓ | Н   | Hold                                                     | Hold                              | Hold Shadow Register                            |

<sup>\*</sup> S7, S6 are undefined. If P[33] in the microword is a one, S15-S8 are loaded from the pipeline register. If P[33] in the microword is a zero,  $S_{15} - S_8$  are loaded from an external source.

#### **FUNCTION TABLE DEFINITIONS**

#### **INPUTS**

D = Serial Data

H = HIGH L = LOW

↑ = LOW-to-HIGH transition

X = Don't Care ↓ = HIGH-to-LOW transition

## TABLE 2.

| Input<br>Condition<br>Being Tested | POL | Condition |

|------------------------------------|-----|-----------|

| 0                                  | 0   | Fail      |

| 0                                  | 1   | Pass      |

| 1                                  | 0   | Pass      |

| 1                                  | 1   | Fail      |

<sup>\*\*</sup> During normal operation, this pin behaves as the CC test input.

## Am29PL142 INSTRUCTION SET DEFINITION

The stack consists of two registers; the top one is labeled Top of Stack (TOS), the bottom one is labeled Bottom of Stack (BOS).

• = Other instruction

P = Test Pass

- ⊙ = Instruction being described

- O = Register in part

F = Test Fail

X, Yare arbitrary values in the CREG or STACK

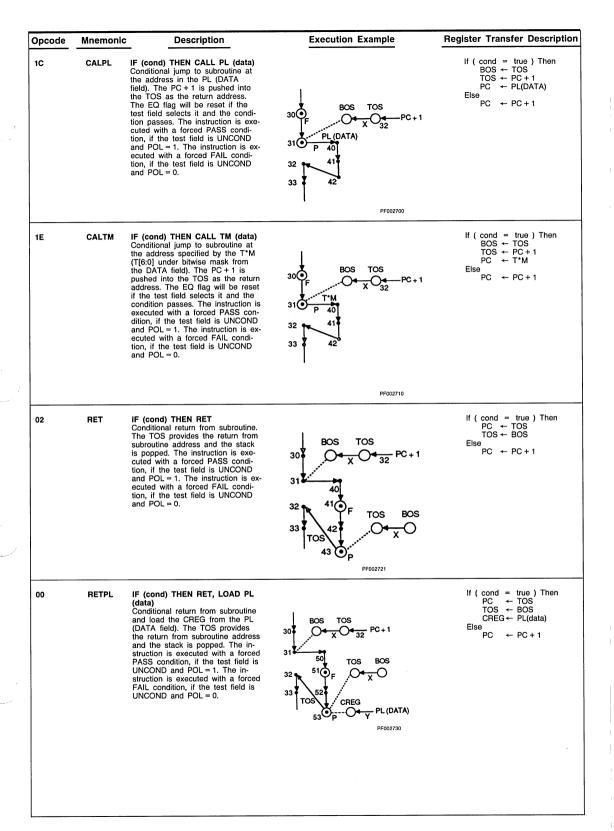

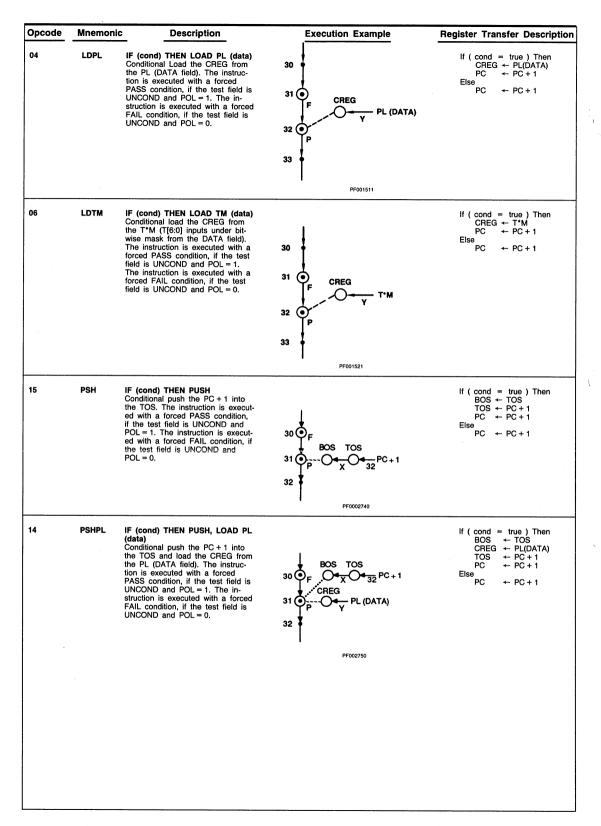

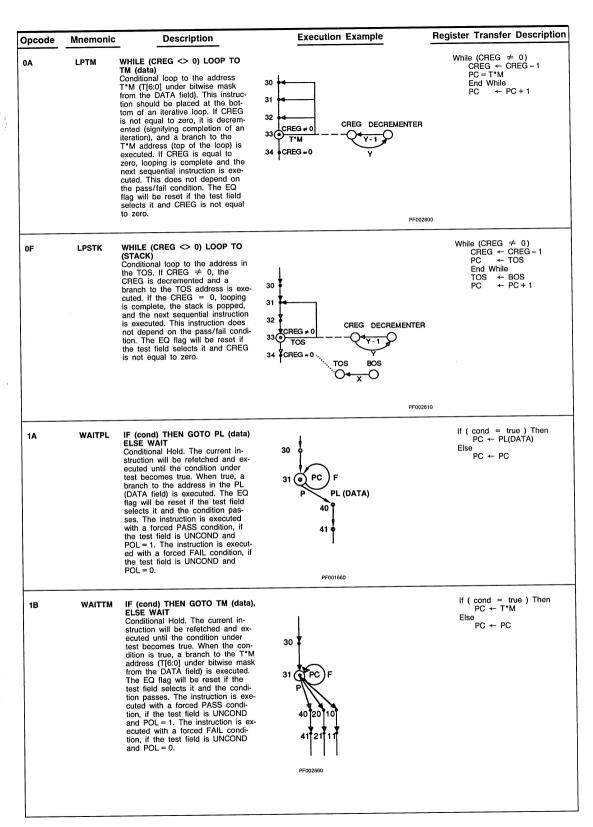

| Opcode | Mnemonio | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Execution Example                         | Register Transfer Description                          |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------|

| 19     | GOTOPL   | IF (cond) THEN GOTO PL (data) Conditional branch to the address in the PL (DATA field). The EQ flag will be reset if the test field selects it and the condition passes. The instruction is executed with a forced PASS condition, if the test field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition, if the test field is UNCOND and POL = 0.                                                                                                             | 30                                        | If ( cond = true ) Then PC ← PL(DATA) Else PC ← PC + 1 |

| 1F     | GOTOTM   | IF (cond) THEN GOTO TM (data) Conditional branch to the address defined by the T*M (T[6:0] under bitwise mask from the DATA field). This instruction is intended for multiway branches. The EQ flag will be reset if the test field se- lects it and the condition passes. The instruction is executed with a forced PASS condition, if the test field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition, if the test field is UNCOND and POL = 0.           | 30 F T*M 10 11 11 20 11 12 41 12 PF001441 | If ( cond = true ) Then PC ← T*M Else PC ← PC + 1      |

| 03     | GOTOSTK  | IF (cond) THEN GOTO (STACK) Conditional branch to the address at the top of the stack, or else continue. The EO flag will be reset if the test field selects it and the condition passes. The instruction is executed with a forced PASS condition if the test field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition if the test field is UNCOND and POL = 0.                                                                                              | 30 F<br>31 TOS<br>40<br>41                | If ( cond = true) Then PC ← TOS Else PC ← PC + 1       |

| 18     | FORK     | IF (cond) THEN GOTO PL (data) ELSE GOTO (STACK) Conditional branch to the address in the PL (DATA field) or the TOS. A branch to PL is taken if the condition is true and a branch to TOS if false. The EQ flag will be reset if the test field selects it and the condition passes. The instruction is executed with a forced PASS condition, if the test field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition, if the test field is UNCOND and POL = 0. | 30<br>31 F TOS<br>PL 40 51<br>(DATA) 41   | If ( cond = true ) Then PC ← PL(DATA) Else PC ← TOS    |

|                                                                                                                                                                                                                                                                                                                                                              | <del></del>                                                                                                                                                                                                                     | Register Transfer Description                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IF (cond) THEN PUSH, LOAD TM (data) Conditional push the PC+1 into the TOS and load the CREG from the T*M (T[6:0] under bitwise mask from the DATA field). The instruction is executed with a forced PASS condition, if the test field is UNCOND and POL=1. The instruction is executed with a forced FAIL condition, if the test field is UNCOND and POL=0. | BOS TOS 30 F                                                                                                                                                                                                                    | If ( cond = true ) Then  BOS + TOS  CREG + T*M  TOS + PC+1  PC + PC+1  Else  PC + PC+1                                                                                                                                                                                                        |

| IF (cond) THEN POP Conditional Pop the TOS. The instruction is executed with a forced PASS condition, if the test field is UNCOND and POL = 1. The in-                                                                                                                                                                                                       | 30 Ø <sub>F</sub>                                                                                                                                                                                                               | If ( cond = true ) Then                                                                                                                                                                                                                                                                       |

| struction is executed with a forced FAIL condition, if the test field is UNCOND and POL = 0.                                                                                                                                                                                                                                                                 | 31 PF002760                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                               |

| TR IF (cond) THEN PUSH (CREG) Conditional push CREG contents to top of stack. The instruction is executed with a forced PASS con- dition if the test field is UNCOND and POL = 1. The instruction is ex- ecuted with a forced FAIL condi- tion if the test field is UNCOND and POL = 0.                                                                      | BOS TOS CREG                                                                                                                                                                                                                    | If ( cond = true ) Then BOS ← TOS TOS ← CREG PC ← PC + 1 Else PC ← PC + 1                                                                                                                                                                                                                     |

| TR IF (cond) THEN POP TO (CREG) Conditional pop TOS into CREG. The instruction is executed with a forced PASS condition, if the test field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition, if the test field is UNCOND and POL = 0.                                                                                         | 30 © CREG TOS BOS 31 © P 32                                                                                                                                                                                                     | If ( cond = true ) Then                                                                                                                                                                                                                                                                       |

| IF (cond) THEN DEC Conditional decrement of the CREG. The instruction is executed with a forced PASS condition, if the test field is UNCOND and POL = 1. The instruction is execut- ed with a forced FAIL condition, if the test field is UNCOND and POL = 0.                                                                                                | 30 P CREG DECREMENTER 32 P Y-1 Y                                                                                                                                                                                                | If ( cond = true ) Then     CREG ← CREG − 1     PC ← PC + 1  Else     PC ← PC + 1                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                              | Conditional decrement of the CREG. The instruction is executed with a forced PASS condition, if the test field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition, if the test field is UNCOND and | IF (cond) THEN DEC Conditional decrement of the CREG. The instruction is executed with a forced PASS condition, if the test field is UNCOND and POL = 1. The instruction is execut- ed with a forced FAIL condition, if the test field is UNCOND and POL = 0.  31  F CREG DECREMENTER 32  Y-1 |

| Opcode | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Execution Example                                       | Register Transfer Description                                                                                  |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 0C     | DECPL    | WHILE (CREG <> 0) WAIT ELSE LOAD PL (data) Conditional Hold until the counter is equal to zero, then load CREG from the PL (DATA field). This instruction is intended for timing waveform generation. If the CREG is not equal to zero, the same instruction is refetched while CREG is decremented. Timing is complete when the CREG is equal to zero, causing the next instruction to be fetched and the CREG to be reloaded from PL. This instruction does not depend on the pass/fail condition.                                                                                                                                                                                                       | 31 PC CREG \$\neq 0\$  CREG V  CREG PL (DATA)           | While ( CREG ≠ 0)  CREG ← CREG − 1  PC ← PC  End While  CREG ← PL(DATA)  PC ← PC + 1                           |

| 0E     | DECTM    | WHILE (CREG <> 0) WAIT ELSE LOAD TM (data) Conditional Hold until the counter is equal to zero, then load CREG from the T*M (T[6:0] under bitwise mask from the DATA field). This instruction is intended for timing waveform generation. If the CREG is not equal to zero, the same instruction is refetched while the CREG is decremented. Timing is complete when the CREG is equal to zero, causing the next instruction to be refetched and the CREG to be reloaded from T*M. This instruction does not depend on the pass/fail condition.                                                                                                                                                            | CREG DECREMENTER  30  Y-1  31  PC  CREG  Y  CREG  T'M   | While ( CREG ≠ 0 ) CREG ← CREG − 1 PC ← PC End While CREG ← T*M PC ← PC + 1                                    |

| 1D     | DECGOPL  | IF (cond) THEN GOTO PL (data) ELSE WHILE (CREG <> 0) WAIT Conditional Hold/Count. The current instruction will be refetched and the CREG decremented until the condition under test becomes true or the counter is equal to zero. If the condition becomes true, a branch to the address in the PL (DATA field) is executed. If the counter becomes zero without the condition becoming true, a CONTINUE is executed. The EQ flag will be reset if the test field selects it and the condition passes. The instruction is executed with a forced PASS condition if the TEST field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition if the TEST field is UNCOND and POL = 0. | CREG DECREMENTER  Y-1  Y-1  Y-1  Y-1  Y-1  Y-1  Y-1  Y- | While ( cond = false )  If ( CREG ≠ 0 )  CREG ← CREG − 1  PC ← PC  Else  PC ← PC + 1  End While  PC ← PL(DATA) |

| 08     | LPPL     | WHILE (CREG <> 0) LOOP TO PL (data) Conditional loop to the address in the PL (DATA field). This instruction is intended to be placed at the bottom of an iterative loop. If the CREG is not equal to zero, it is decremented (signifying completion of an iteration), and a branch to the PL address (top of the loop) is executed. If the CREG is equal to zero, looping is complete and the next sequential instruction is executed. This instruction does not depend on the pass/fail condition. The EQ flag will be reset if the test field selects it and CREG is not equal to zero.                                                                                                                 | 33 CREG = 0  CREG DECREMENTER  Y-1  Y-1  PF001671       | While (CREG ≠ 0) CREG ← CREG-1 PC ← PL (DATA) End While PC ← PC+1                                              |

|                              | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Execution Example                                           | Register Transfer Description                                                           |

|------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| OD                           | CONT     | CONTINUE The next sequential instruction is fetched unconditionally. This instruction can also be used to reset the EQ flag by selecting EQ in the TEST field.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31 (0)                                                      | PC ← PC+1                                                                               |

|                              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PF001690                                                    |                                                                                         |

| 01                           | OUTPUT   | IF (cond) THEN OUTPUT The CREG contents will be output on pins P[14:8] during the next clock cycle. Care should be taken to ensure that the outputs are enabled for the next sequential instruction by setting the microcode bit OE = 1. The instruction is executed with a forced PASS condition, if the test field is UNCOND and POL = 1. The instruction is executed with a forced FAIL condition, if the test field is UNCOND and POL = 0.                                                                                                                                                                                                                                                                                                                                                                      | 30 F Pipeline Regiser CREG 31 P - P[14:8] \( \frac{C}{X} \) | If (cond = true) Then                                                                   |

| 10 – 13<br>(100XX<br>binary) |          | CMP TM (data) TO PL (data) This instruction performs bitwise exclusive-OR of T*M (T[6:0] under bitwise mask from the DATA field) with CONSTANT (P[29:23]). If T*M equals CONSTANT, the EQ flag is set to one, so that a branch may occur in a following instruction. If not equal, the EQ flag is unaffect- ed. This allows sequences of com- pares, in a manner analogous to sum-of-products, to be performed which can be followed by a single conditional branch if one or more of the comparisons were true. Note: The EQ flag is set to zero on reset or when EQ is selected as the test condition in a branch. Conditional returns on EQ leave the flag unchanged. Constant field bits that correspond to masked test-input bits must be zero. This instruction does not de- pend on the pass/fail condition. | 31                                                          | Compare T*M and PL(DATA) EQ = ((T [6:0] AND. DATA) .XNOR. CONSTANT) .OR. EQ PC ← PC + 1 |

## MICROINSTRUCTIONS BASED ON TEST CONDITIONS

|        |          |                                                    |           | Condition      | Pass        |            |           | Conditio | n Fail |            |       |

|--------|----------|----------------------------------------------------|-----------|----------------|-------------|------------|-----------|----------|--------|------------|-------|

| Opcode | Mnemonic | Assembler Statement                                | PC<br>MUX | STACK          | CREG        | EQ<br>FLAG | PC<br>MUX | STACK    | CREG   | EQ<br>FLAG | Notes |

| 00     | RETPL    | IF (cond) THEN RET, LOAD PL (data)                 | TOS       | Pop            | Load<br>PL  | NC         | PC + 1    | Hold     | Hold   | NC         | 5     |

| 01     | OUTPUT   | IF (cond) THEN OUTPUT                              | PC + 1    | Hold           | Hold        | NC         | PC + 1    | Hold     | Hold   | NC         | 1     |

| 02     | RET      | IF (cond) THEN RET                                 | TOS       | Pop            | Hold        | NC         | PC + 1    | Hold     | Hold   | NC         | 5     |

| 03     | дотостк  | IF (cond) THEN GOTO (STACK)                        | TOS       | Hold           | Hold        | Reset      | PC + 1    | Hold     | Hold   | NC         | 3     |

| 04     | LDPL     | IF (cond) THEN LOAD PL (data)                      | PC + 1    | Hold           | Load<br>PL  | NC         | PC + 1    | Hold     | Hold   | NC         |       |

| 05     | PSHCNTR  | IF (cond) THEN PUSH (CREG)                         | PC + 1    | Push<br>CREG   | Hold        | NC         | PC + 1    | Hold     | Hold   | NC         | 6     |

| 06     | LDTM     | IF (cond) THEN LOAD TM (data)                      | PC + 1    | Hold           | Load<br>TM  | NC         | PC + 1    | Hold     | Hold   | NC         |       |

| 07     | POP      | IF (cond) THEN POP                                 | PC + 1    | Pop            | Hold        | NC         | PC + 1    | Hold     | Hold   | NC         | 5     |

| 0B     | DEC      | IF (cond) THEN DEC                                 | PC + 1    | Hold           | DEC         | NC         | PC + 1    | Hold     | Hold   | NC         |       |

| 14     | PSHPL    | IF (cond) THEN PUSH,<br>LOAD PL (data)             | PC + 1    | Push<br>PC + 1 | Load<br>PL  | NC         | PC + 1    | Hold     | Hold   | NC         | 6     |

| 15     | PSH      | IF (cond) THEN PUSH                                | PC + 1    | Push<br>PC + 1 | Hold        | NC         | PC + 1    | Hold     | Hold   | NC         | 6     |

| 16     | PSHTM    | IF (cond) THEN PUSH,<br>LOAD TM (data)             | PC + 1    | Push<br>PC + 1 | Load<br>TM  | NC         | PC + 1    | Hold     | Hold   | NC         | 6     |

| 17     | POPCNTR  | IF (cond) THEN POP TO (CREG)                       | PC + 1    | Pop            | Load<br>TOS | NC         | PC + 1    | Hold     | Hold   | NC         | 5     |

| 18     | FORK     | IF (cond) THEN GOTO PL<br>(data) ELSE GOTO (STACK) | PL        | Hold           | Hold        | Reset      | тоѕ       | Hold     | Hold   | NC         | 3     |

| 19     | GOTOPL   | IF (cond) THEN GOTO PL (data)                      | PL        | Hold           | Hold        | Reset      | PC + 1    | Hold     | Hold   | NC         | 3     |

| 1A     | WAITPL   | IF (cond) THEN GOTO PL<br>(data) ELSE WAIT         | PL        | Hold           | Hold        | Reset      | PC        | Hold     | Hold   | NC         | 3     |

| 1B     | WAITTM   | IF (cond) THEN GOTO TM (data) ELSE WAIT            | ТМ        | Hold           | Hold        | Reset      | PC        | Hold     | Hold   | NC         | 3     |

| 1C     | CALPL    | IF (cond) THEN CALL PL (data)                      | PL        | Push<br>PC + 1 | Hold        | Reset      | PC + 1    | Hold     | Hold   | NC         | 3, 6  |

| 1E     | CALTM    | IF (cond) THEN CALL TM (data)                      | ТМ        | Push<br>PC + 1 | Hold        | Reset      | PC + 1    | Hold     | Hold   | NC         | 3, 6  |

| 1F     | GOТОТМ   | IF (cond) THEN GOTO TM (data)                      | TM        | Hold           | Hold        | Reset      | PC + 1    | Hold     | Hold   | NC         | 3     |

Key: TOS = Top of Stack

PC = Program Counter

CREG= Counter Register

PL = Pipeline (DATA) Field

TM = Test Inputs Marked by PL (DATA) Field

DEC = Decrement

BOS = Bottom of Stack

NC = No Change

Notes: See notes on next page.

#### MICROINSTRUCTION DEPENDENT ON CREG CREQ = 0CREG ≠ 0 PC EΩ PC EQ Opcode Mnemonic **Assembler Statement** MUX STACK CREG **FLAG** MUX CREG | FLAG STACK Notes WHILE (CREG<>0) LOOP 08 LPPL PC + 1 Hold Hold NC TO PL (data) ΡI Hold DEC Reset WHILE (CREG<>0) LOOP 0A LPTM PC + 1 Hold TO TM (data) Hold NC ТМ Hold DEC Reset WHILE (CREG<>0) WAIT 0C Load DECPL PC + 1 Hold NC PC Hold DEC NC ELSE LOAD PL (data) PL WHILE (CREG<>0) WAIT ELSE LOAD TM (data) 0E Load DECTM PC + 1 Hold NC PC Hold DEC NC TM WHILE (CREG<>0) LOOP 0F **LPSTK** PC + 1 Hold Pop NC TOS Hold DEC TO (STACK) Recet

## MICROINSTRUCTION DEPENDENT ON TEST CONDITION AND CREG VALUE

|        |          |                                  |                 |           | Condition | Pass |            |           | Conditio | n Fail |            |       |

|--------|----------|----------------------------------|-----------------|-----------|-----------|------|------------|-----------|----------|--------|------------|-------|

| Opcode | Mnemonic | Assembler<br>Statement           | CREG<br>Content | PC<br>MUX | STACK     | CREG | EQ<br>FLAG | PC<br>MUX | STACK    | CREG   | EQ<br>FLAG | Notes |

| 1D     | DECGOPL  | IF (cond) THEN<br>GOTO PL (data) | ≠0              | PL        | Hold      | Hold | Reset      | PC        | Hold     | DEC    | NC         | 3     |

|        |          | ELSE WHILE<br>(CREG<>0) WAIT     | = 0             | PL        | Hold      | Hold | Reset      | PC + 1    | Hold     | Hold   | NC         | 3     |

#### **UNCONDITIONAL MICROINSTRUCTIONS**

| Opcode                     | Mnemonic | Assembler Statement        | PC<br>MUX | STACK | CREG | EQ<br>FLAG | Notes |

|----------------------------|----------|----------------------------|-----------|-------|------|------------|-------|

| 0D                         | CONT     | CONTINUE                   | PC + 1    | Hold  | Hold | NC         | 2     |

| 10-13<br>(100XX)<br>Binary | СМР      | CMP TM (data) TO PL (data) | PC + 1    | Hold  | Hold | Set        | 7     |

Key: TOS = Top of Stack

BOS = Bottom of Stack

PC = Program Counter

CREG= Counter Register

PL = Pipeline (DATA) Field

TM = Test Inputs Marked by PL (DATA) Field

DEC = Decrement

NC = No Change

Notes: 1. If Condition Passes, Output CREG contents on next clock cycle.

- 2. If Condition = EQ, reset EQ flag.

- 3. If Condition = EQ and Condition Passes, reset EQ flag.

- 4. If Condition = EQ and CREG ≠ 0, reset EQ flag.

- 5. When Stack is popped, BOS is transferred to TOS.

- 6. When Stack is pushed, TOS is transferred to BOS before value is written into TOS.

- 7. Set EQ Flag if CONST field = T\*M.

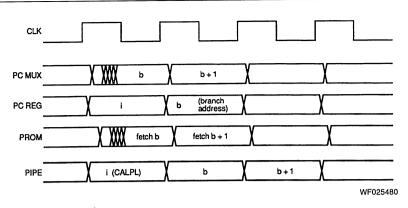

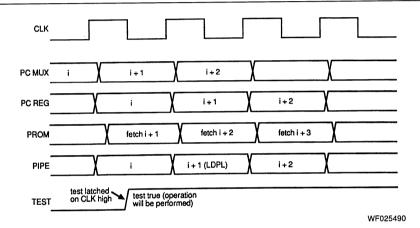

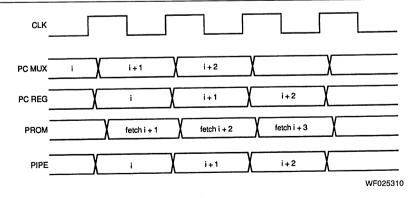

Figure 2. Conditional Branch/Jump Instruction (Example: CALPL)

Figure 3. Conditional Instruction (Example: LDPL)

Figure 4. Unconditional Instruction (Example: CONT)

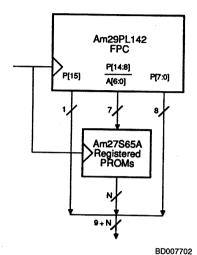

# Using The Am29PL142 To Address External Registered PROM

When the EXP fuse is programmed, the program memory MUX is output over pins P[14:8]/A[6:0]. This feature can be used to extend the width of the output control word when external registered PROMs are used. In Figure 5 below, the Am29PL142 addresses external registered PROMs to provide

an output control word (9 + N) bits wide (where N is the bit width of the PROMs).

When the OUTPUT instruction is executed, the CREG contents are output over pins P[14:8]/A[6:0] on the following cycle. Consequently, if the CREG contents must be read after programming the EXP fuse, the system design should be modified to handle this exception.

Figure 5. Using Am29PL142 to Address External Registered PROMs

#### **PROGRAMMING**

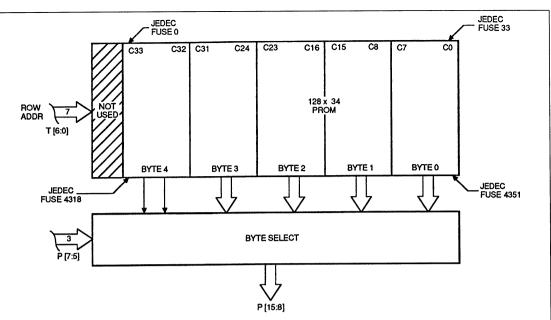

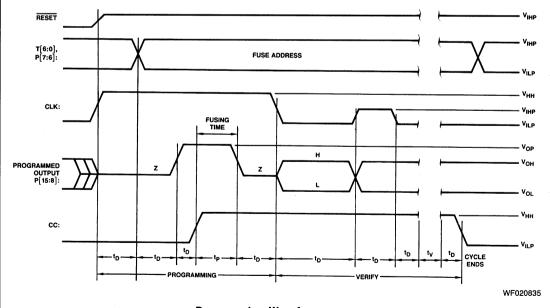

The Am29PL142 FPC is programmed and verified using a simple algorithm that is almost identical to that used for AMD's Programmable Array Logic family. The internal programmable array of the Am29PL142 is organized as a 128-word by 34-bit PROM. The fuse to be programmed is selected by its address (1 of 128), the byte at that address (1 of 5), and the bit in the byte (1 of 8). Control of programming and verifying is accomplished by applying a simple sequence of voltages on two control pins (CLK and CC).

The fuse address is selected using a full decode of the T[6:0] inputs, where T[6] is the MSB and T[0] the LSB. The 1-of-5 byte addressing is done on the P[7] (MSB), and P[6] and P[5] (LSB) outputs. The bit selection is done one output at a time by applying the programming voltage (Vop) to the respective output pin P[15:8]. A graphic representation of the fuse array organization for programming, with fuse numbering compatible to the JEDEC standard programmable logic transfer format, is shown in Figure 6.

The complete program and verify cycle timing is shown in the programming waveform. A programming sequence is initiated by raising the CLK pin to V<sub>HH</sub>. This places the device in the program mode and disables the output pins so that they may be used as fuse addressing inputs. The next step is to address the fuse to be blown as previously stated. Note that bit

selection, with V<sub>OP</sub>, should follow address and byte selection. Raising the CC pin to V<sub>HH</sub> initiates programming and lowering V<sub>OP</sub> terminates programming. Lowering the CLK pin to a TTL LOW level places the device in the fuse verification mode by enabling the programming outputs, P[15:8]. Following a clock pulse the fuse may be verified on the same output as bit selection was performed. Using this scheme, fuses can be verified in parallel as a byte if desired. The verification mode is terminated by lowering the CC pin back to a normal TTL level.

#### **Programming Yield**

AMD programmable logic devices have been designed to ensure extremely high programming yields ( > 98%). To help ensure that a part was correctly programmed (once the programming sequence is completed) the entire fuse array should be reverified at both low and high V<sub>CC</sub> (V<sub>CCL</sub> and V<sub>CCH</sub>). Reverification can be accomplished in a verification-only mode (CC at V<sub>HH</sub>) by reading the outputs in parallel. This verification cycle checks that the array fuses have been blown correctly and can be sensed under varying conditions by the outputs.

AMD programmable logic devices contain extra fuses and circuitry so that it can be verified, before shipping, that all PROM fuses can be programmed. Additional circuitry is included for pre-shipment testing of the logic portion of the device. These added features assure high programming yields and correct logic operation.

BD007551

JEDEC Fuse Numbering: If Byte  $\leq$  3, Fuse No. = 34 x (Row\_Addr) + 8 x (3-Byte) + (7-Bit) + 2 If Byte = 4, Fuse No. = 34 x (Row\_Addr) + (1-Bit)

Note: SSR fuse is JEDEC Fuse Number 4352, EXP fuse is JEDEC Fuse Number 4353

#### **Example Computations:**

Row 0, Byte 4, Bit 1 Row 127, Byte 0, Bit 0 Fuse No. = 34 (0) + (1-1) = 0

Fuse No. = 34 (127) + 8 (3-0) + (7-0) + 2 = 4351

|      | ı    | Byte Selec | t    | Bit Select |       |       |       |       |       |      |      |

|------|------|------------|------|------------|-------|-------|-------|-------|-------|------|------|

| Byte | P[7] | P[6]       | P[5] | P[15]      | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] |

| 0    | 1    | 1          | 0    | C7         | C6    | C5    | C4    | C3    | C2    | C1   | C0   |

| 1.   | 1    | 1          | 1    | C15        | C14   | C13   | C12   | C11   | C10   | C9   | C8   |

| 2    | 1    | 0          | 0    | C23        | C22   | C21   | C20   | C19   | C18   | C17  | C16  |

| ,3   | 1    | 0          | 1    | C31        | C30   | C29   | C28   | C27   | C26   | C25  | C24  |

| 4    | 0    | 1          | 0    | _          | _     | -     | -     | -     | _     | C33  | C32  |

| 5    | 0    | 1          | 1    | -          | _     | -     | _     | -     | _     | -    | -    |

| 6    | 0    | 0          | 1    | -          | -     | -     | -     | _     | -     | -    | _    |

| 7    | 0    | 0          | 0    | SSR        | EXP   |       | -     | -     | -     | -    | _    |

Notes: 1. Locations with hyphens (-) are reserved. Contents of those locations are unknown and should not be overwritten.

2. T[6:0] gives the row address for programming.

3. C33 is MSB of the Word, C0 is the LSB.

4. Unblown fuses are interpreted as HIGH (1), blown fuses are LOW (0).

Figure 6. Programming Configuration

| Parameter<br>Symbol  | Parame<br>Descrip                                    |                                   | Min.             | Тур.                   | Max  | Unit |  |

|----------------------|------------------------------------------------------|-----------------------------------|------------------|------------------------|------|------|--|

| V                    | Control Pin Extra High Level                         | CC @ 5-10 mA                      | 15.5             | 16                     | 16.5 | V    |  |

| V <sub>HH</sub>      | Control Pin Extra High Level                         | CLK@ 5-10 mA                      | 15.5             | 16                     | 16.5 |      |  |

| V <sub>OP</sub>      | Program Voltage, P [15:8] @ 19                       | 5 – 200 mA                        | 19.5             | 20                     | 20.5 | ٧    |  |

| V <sub>IHP</sub>     | Input High Level During Program                      | nming and Verify                  | 2.4              | 5                      | 5.5  | ٧    |  |

| V <sub>ILP</sub>     | Input Low Level During Program                       | nming and Verify                  | 0.0              | 0.3                    | 0.5  | ٧    |  |

| V <sub>CCP</sub>     | V <sub>CC</sub> During Programming @ I <sub>CC</sub> | c = 500 mA                        | 5                | 5.2                    | 5.5  | ٧    |  |

| V <sub>CCL</sub>     | V <sub>CC</sub> During First Pass Verification       | 4.5                               | 4.7              | 5                      | ٧    |      |  |

| Vcch                 | V <sub>CC</sub> During Second Pass Verifica          | 5.4                               | 5.7              | 6.0                    | ٧    |      |  |

| V <sub>Blown</sub>   | Successful Blown Fuse Sense L                        |                                   | 0.3              | 0.5                    | ٧    |      |  |

| dV <sub>OP</sub> /dt | Rate of Output Voltage Change                        | 20                                |                  | 250                    | V/μs |      |  |

| dV <sub>FE</sub> /dt | Rate of Fusing Enable Voltage C                      | 100                               |                  | 1000                   | V/µs |      |  |

| tp                   | Fusing Time First Attempt                            |                                   | 40               | 50                     | 100  | μs   |  |

|                      | Subsequent Attempts                                  | -                                 | 4                | 5                      | 10   | ms   |  |

| t <sub>D</sub>       | Delays Between Various Level 0                       | Changes                           | 100              | 200                    |      | ns   |  |

| tv                   | Period During which Output is Se                     | nsed for V <sub>Blown</sub> Level | 500              |                        |      | ns   |  |

| V <sub>ONP</sub>     | Pull-Up Voltage on Outputs Not                       | V <sub>CCP</sub> - 0.3            | V <sub>CCP</sub> | V <sub>CCP</sub> + 0.3 | ٧    |      |  |

| R                    | Pull- Up Resistor on Outputs No                      | ot Being Programmed               | 1.9              | 2                      | 2.1  | kΩ   |  |

| dV <sub>CLK/dt</sub> | Rate of CLK Voltage Change (F                        | Programming)                      | 40               | 50                     | 250  | V/μs |  |

250

300

1000

V/μs

Rate of CLK Voltage Change (Verify)

## **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Pin 28 to Pin 14) Continuous0.5 V to +7.0 V                                                                                                                                                                                                   |

| DC Voltage Applied to Outputs                                                                                                                                                                                                                  |

| (Except During Programming)0.5 V to +V <sub>CC</sub> Max.                                                                                                                                                                                      |

| DC Voltage Applied to Outputs                                                                                                                                                                                                                  |

| During Programming                                                                                                                                                                                                                             |

| DC Output Current, Into Outputs During Programming (Max Duration of 1 s)                                                                                                                                                                       |

| Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability. |

#### **OPERATING RANGES**

| Commercial (C) Devices  Ambient Temperature ( $T_A$ )                                             |

|---------------------------------------------------------------------------------------------------|

| Military* (M) Devices  Case Temperature (T <sub>C</sub> )                                         |

| Operating ranges define those limits between which the functionality of the device is guaranteed. |

| *Military Product 100% tested at $T_C$ = +25°C, +125°C and -55°C.                                 |

| Typical $	heta_{ m JA}$                                                                           |

DC CHARACTERISTICS over operating range unless otherwise specified (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol         | Parameter<br>Description     | Test Conditions                                                                          |                                                     |        |                                 | Min.                                       | Max.                       | Unit |      |       |

|-----------------------------|------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------|--------|---------------------------------|--------------------------------------------|----------------------------|------|------|-------|

|                             |                              |                                                                                          | C                                                   | OM'L   | 29PL14                          | $I_{OH} = -3.0 \text{ mA}$                 |                            | 2.4  |      | V     |

| V <sub>OH</sub>             | Output HIGH Voltage          | V <sub>CC</sub> = Min.,<br>V <sub>IN</sub> = V <sub>IH</sub> or V                        | IL M                                                | IL     | 29PL14                          | 2                                          | $I_{OH} = -1.0 \text{ mA}$ | 2.4  |      | •     |

|                             |                              |                                                                                          | C                                                   | OM'L   | 29PL14                          | 2                                          | I <sub>OL</sub> = 16 mA    |      | 0.50 | ٧     |

| VOL                         | Output LOW Voltage           | V <sub>IN</sub> = V <sub>IL</sub> or V                                                   | ін М                                                | IL     | 29PL142 I <sub>OL</sub> = 12 mA |                                            | I <sub>OL</sub> = 12 mA    |      | 0.50 |       |

| V <sub>IH</sub><br>(Note 1) | Input HIGH Level             | Guaranteed In                                                                            | put Logic                                           | al HIG | H Voltage                       | e for                                      | All Inputs                 | 2.0  |      | ٧     |

| V <sub>IL</sub><br>(Note 1) | Input LOW Level              | Guaranteed In                                                                            | Guaranteed Input Logical LOW Voltage for All Inputs |        |                                 |                                            |                            | 0.8  | ٧    |       |

| Iμ                          | Input LOW Current            | V <sub>CC</sub> = Max.<br>V <sub>IN</sub> = 0.5 V All Other Inputs                       |                                                     |        |                                 |                                            | -1.5<br>-0.55<br>-0.50     | mA   |      |       |

| liн                         | Input HIGH Current           | V <sub>CC</sub> = Max.<br>V <sub>IN</sub> = 2.4 V All Other Inputs                       |                                                     |        |                                 |                                            | 150<br>100<br>25           | μΑ   |      |       |

| lı .                        | Input HIGH Current           | V <sub>CC</sub> = Max., V <sub>IN</sub> = 5.5 V                                          |                                                     |        |                                 | 1.0                                        | mA                         |      |      |       |

| Isc                         | Output Short-Circuit Current | V <sub>CC</sub> = Max + 0.5 V V <sub>OUT</sub> = 0.5 V (Note 2)                          |                                                     |        | -20                             | -80                                        | mA                         |      |      |       |

|                             |                              |                                                                                          | COM'L                                               | 1 00   | PL142                           | $T_A = 0 \text{ to } + 70^{\circ}\text{C}$ |                            |      | 500  |       |

|                             | Power Supply Current         | V <sub>CC</sub> = Max.                                                                   | COMIL                                               | 29     | -L142                           | TA                                         | = + 70°C                   |      | 450  | mA    |

| Icc                         |                              |                                                                                          |                                                     | 201    | 71.440                          | Tc                                         | =-55 to +125°C             |      | 570  | 111/2 |

|                             |                              |                                                                                          | MIL                                                 | 291    | 29PL142                         |                                            | = + 125°C                  |      | 475  |       |

| VI                          | Input Clamp Voltage          | V <sub>CC</sub> = Min, I <sub>IN</sub> = -18 mA                                          |                                                     |        |                                 |                                            | -1.2                       | V    |      |       |

| lozh                        | Output Leakage Current       | $V_{CC} = Max., V_{IL} = 0.8 \text{ V}$ $V_{IH} = 2.0 \text{ V}$ $V_{O} = 0.5 \text{ V}$ |                                                     |        |                                 |                                            | 100                        | μΑ   |      |       |

| lozL                        | (Note 3)                     |                                                                                          |                                                     |        |                                 |                                            | -550                       | ٣٨   |      |       |

Notes: 1. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

2. Not more than one output should be tested at a time. Duration of the short-circuit test should not be more than one second.

V<sub>OUT</sub> = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

3. I/O pin leakage is the worst-case of I<sub>OZX</sub> or I<sub>IX</sub> (where X = H or L).

SWITCHING CHARACTERISTICS over operating range unless otherwise specified (for APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted)

|      | Parameter        | Parameter                       | ,               | COM'L |      | MIL  |      | 1    |

|------|------------------|---------------------------------|-----------------|-------|------|------|------|------|

| No.  | Symbol           | Description                     | Test Conditions | Min.  | Max. | Min. | Max. | Unit |

| 1    |                  | CLK to P[15:0]                  |                 |       | 20   |      | 25   | ns   |

| 2    |                  | CLK to A[6:0]                   |                 |       | 50   |      | 55   | ns   |

| 3    | t <sub>PD</sub>  | DCLK to SDO                     |                 |       | 30   |      | 30   | ns   |

| 4    |                  | Mode to SDO                     |                 |       | 30   |      | 30   | ns   |

| 5    |                  | SDI to SDO                      |                 |       | 30   |      | 30   | ns   |

| 6    |                  | T[6:0] to CLK (Note 1)          |                 | 15    |      | 15   |      | ns   |

| 7    |                  | CC to CLK (Note 1)              |                 | 15    |      | 15   |      | ns   |

| 8    |                  | RESET to CLK                    |                 | 15    |      | 15   |      | ns   |

| 9    | ts               | Mode to CLK                     |                 | 30    |      | 30   |      | ns   |

| 10   |                  | Mode to DCLK                    |                 | 30    |      | 30   |      | ns   |

| 11   |                  | SDI to DCLK                     |                 | 30    |      | 30   |      | ns   |

| 12   |                  | P[15:8] to DCLK                 |                 | 30    |      | 30   |      | ns   |

| 13 ` |                  | T[6:0] to CLK                   | See Test        | 0     |      | 0    |      | ns   |

| 14   |                  | CC to CLK                       | Output Load     | 0     |      | 0    |      | ns   |

| 15   |                  | RESET to CLK                    | Conditions      | 4     |      | 0    |      | ns   |

| 16   | tH               | Mode to CLK                     |                 | 0     |      | 0    |      | ns   |

| 17   |                  | Mode to DCLK                    |                 | 0     |      | 0    |      | ns   |

| 18   |                  | SDI to DCLK                     |                 | 0     |      | 0    |      | ns   |

| 19   |                  | P[15:8] to DCLK                 |                 | 0     |      | 0    |      | ns   |

| 20   | t <sub>PZX</sub> | CLK to P[15:8] Enable           | · ·             |       | 20   |      | 25   | ns   |

| 21   | t <sub>PXZ</sub> | CLK to P[15:8] Disable          |                 |       | 30   |      | 30   | ns   |

| 22   | tрwн             | CLK Pulse Width (HIGH)          |                 | 15    |      | 15   |      | ns   |

| 23   | tpwL             | CLK Pulse Width (LOW)           |                 | 25    |      | 30   |      | ns   |

| 24   | tpW              | DCLK Pulse Width (HIGH and LOW) |                 | 30    |      | 30   |      | ns   |

| 25   | tp               | CLK Period (Notes 1 & 2)        |                 | 50    |      | 65   |      | ns   |

- Notes: 1. These parameters are measured indirectly on unprogrammed devices. They are determined as follows:

a. Measure delay from input (T[6:0], or CLK) to PROM address out in test mode. This will measure the delay through the sequence

- b. Measure setup time from T[6:0] input through PROM test columns to pipeline register in verify test column mode. This will measure the delay through the PROM and register setup.

c. Measure delay from T[6:0] input to PROM address out in verify test column mode. This will measure the delay through the logic

- and P[15:0] outputs.

To calculate the desired parameter measurement the following formula is used: Measurement (a) + Measurement (b) - Measurement (c) CLK PERIOD:

CLK (a) + (b) - (c) = CLK PERIOD

2. CLK rise time must not exceed 7 ns.

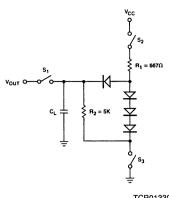

#### SWITCHING TEST CIRCUITS

Vcc TCR01340

TCR01330

#### A. Three State Outputs

## **B. Normal Outputs**

Notes: 1. CL = 50 pF includes scope probe, wiring and stray capacitances without device in test

- 2. S1, S2, and S3 are closed during function tests and all AC tests except output enable

- 3. S<sub>1</sub> and S<sub>3</sub> are closed while S<sub>2</sub> is open for tp<sub>ZH</sub> test.

- 4.  $C_1 = 5.0$  pF for output disable tests.

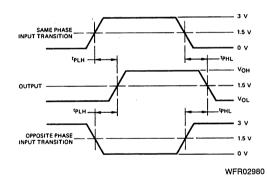

## SWITCHING TEST WAVEFORMS

#### **Propagation Delay**

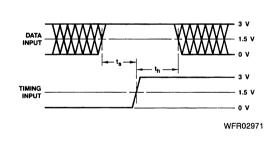

## Setup, Hold, and Release Times

Notes: 1. Diagram shown for HIGH data only. Output transition may be opposite

> 2. Cross hatched area is don't care condition.

## SWITCHING TEST WAVEFORMS (Cont'd.)

| Test                  | <b>V</b> <sub>X</sub> | Output Waveform - Measurement Level |

|-----------------------|-----------------------|-------------------------------------|

| All t <sub>PD</sub> s | 5.0V                  | V <sub>OH</sub>                     |

| t <sub>PHZ</sub>      | 0.0V                  | V <sub>OH</sub> 0.5V 0.0V           |

| <sup>t</sup> PLZ      | 5.0V                  | V <sub>OL</sub> 3v                  |

| t <sub>PZH</sub>      | 0.0V                  | 0.0VVOH                             |

| t <sub>PZL</sub>      | 5.0V                  | 3v                                  |

WFR02680

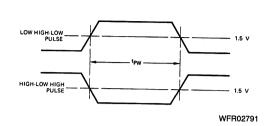

#### **Pulse Width**

## **Enable and Disable Times**

Notes: 1. Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

2. S<sub>1</sub>, S<sub>2</sub>, and S<sub>3</sub> of Load Circuit are closed except where shown.

Note: Pulse generator for all pulses: Rate  $\leq$  1.0 MHz; Z<sub>0</sub> = 50  $\Omega$ : t<sub>f</sub>  $\leq$  2.5 ns.

#### Test Philosophy and Methods

The following points give the general philosophy that we apply to tests that must be properly engineered if they are to be implemented in an automatic environment. The specifics of what philosophies applied to which test are shown.

- 1. Ensure the part is adequately decoupled at the test head. Large changes in supply current when the device switches may cause function failures due to VCC changes.

- 2. Do not leave inputs floating during any tests, as they may oscillate at high frequency.

- 3. Do not attempt to perform threshold tests at high speed. Following an input transition, ground current may change by as much as 600 mA in 5-8 ns. Inductance in the ground cable may allow the ground pin at the device to rise by hundreds of millivolts momentarily. Current level may vary from product to product.