# An Introduction to the AP400 Array Processor

## An Introduction to the AP400 Array Processor

#### PROPRIETARY NOTICE

Analogic's AP400-based Signal Processing Systems utilize designs for which patents have been issued and/or are pending.

The information contained in this publication is derived in part from proprietary and patent data of the Analogic Corporation. This information has been prepared for the express purpose of assisting operating and maintenance personnel in the efficient use of the instrument described herein. Publication of this information does not convey any rights to use or reproduce it or to use for any purpose other than in connection with the installation, operation, and maintenance of the equipment described herein.

Analogic reserves the right to modify published specifications of equipment performance without prior published notice.

Second Edition

January, 1980

Copyright 1979 ANALOGIC CORPORATION

Printed in U.S.A. All rights reserved.

#### CONTENTS

|      | CONT                                                                                                                                                                                                              | IEN 13                                                                                                                                                                                                                                                                               |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1 11 | NTRODUCTION & GENERAL DESCRIPTION                                                                                                                                                                                 | 3.2 System Software                                                                                                                                                                                                                                                                  |     |

| 1.1  | General                                                                                                                                                                                                           | 3.2.1 AP Manager<br>3.2.2 AP Driver                                                                                                                                                                                                                                                  |     |

| 1.2  | Physical Description                                                                                                                                                                                              | 3.2.3 AP Executive                                                                                                                                                                                                                                                                   |     |

| 1.3  | AP400 Card Set                                                                                                                                                                                                    | 3.2.4 AP Service Subroutines                                                                                                                                                                                                                                                         |     |

| 1.4  | AP400 Design Features 1.4.1 Operating Speeds 1.4.2 Arithmetic Pipeline 1.4.3 Memory 1.4.4 Control Processor 1.4.5 I/O Assembly 1.4.6 Software                                                                     | 3.3 Application Software 3.3.1 General 3.3.2 Requirements 3.3.3 Function Naming Conventions 3.3.3.1 Calling the Host Function 3.3.3.2 Host Function Implementation (in Ho Assembly Language) 3.3.3.4 AP Function Implementation (in AP                                               | st  |

| 1.5  | Host-Array Processor Communications 1.5.1 General                                                                                                                                                                 | Assembly Language)                                                                                                                                                                                                                                                                   |     |

|      | 1.5.1 General Sequence of Host-AP Operations 1.5.3 A View from inside the AP400                                                                                                                                   | 3.4 Utility Software 3.4.1 AP Assembler 3.4.2 AP Linker                                                                                                                                                                                                                              |     |

| 2.   | PRINCIPLES OF AP400 OPERATION                                                                                                                                                                                     | 3.4.3 Interactive Debugging Tool (IDT)                                                                                                                                                                                                                                               |     |

| 2.1  | Introduction                                                                                                                                                                                                      | 3.5 Diagnostics<br>3.5.1 General                                                                                                                                                                                                                                                     |     |

|      | System Architecture 2.2.1 Unit Functions 2.2.2 AP400 Buses                                                                                                                                                        | 3.5.2 Typical Diagnostic Program  3.6 Programming Considerations  3.6.1 Introduction                                                                                                                                                                                                 |     |

| 2.3  | AP400 Pipeline Arithmetic Unit (PA) 2.3.1 Pipeline Arithmetics 2.3.2 The AP400 Pipeline Stages 2.3.2.1 The Characterizer Stage 2.3.2.2 The Multiplier Stage 2.3.2.3 Accumulator/Logic Stage                       | <ul> <li>3.6.2 Programming Level Choice</li> <li>3.6.3 Number Formats</li> <li>3.6.4 Block Floating Point Implementation</li> <li>3.6.5 Sample Host FORTRAN Program</li> <li>3.6.6 Table-Based Functions</li> </ul>                                                                  |     |

| 2.4  | The Pipeline Arithmetic Command (PAC)                                                                                                                                                                             | 4 HOST FUNCTION CALLS                                                                                                                                                                                                                                                                |     |

|      | <ul><li>2.4.1 General</li><li>2.4.2 Elements of the PAC</li><li>2.4.3 Pipeline Timing</li><li>2.4.4 Pipeline Addressing</li><li>2.4.5 Coding Considerations</li></ul>                                             | <ul><li>4.1 Introduction</li><li>4.2 Function Control Blocks</li><li>4.2.1 FCB Structure</li><li>4.2.2 FCB Elements</li></ul>                                                                                                                                                        |     |

| 2.5  |                                                                                                                                                                                                                   | 4.3 Function Parameter List Types 4.4 Classification of Host Function Calls 4.4.1 AP Resource Management 4.4.2 AP Data Memory (Data Buffer) Managem 4.4.3 Input-Output Operations 4.4.4 Logical Data Manipulation 4.4.5 Straight Forward Computation 4.4.6 Sophisticated Computation | ent |

| 2.6  | Data Memory (DM)                                                                                                                                                                                                  | 4.5 Host Function Library                                                                                                                                                                                                                                                            |     |

| 2.7  | Input/Output (I/O) 2.7.1 I/O Block Diagram (PDP-11 Interface) 2.7.2 Host/AP Communications 2.7.3 Programmed I/O 2.7.3.1 Immediate Commands 2.7.3.2 DATA (Non Immediate) Commands 2.7.4 Direct Memory Access (DMA) | 5 AP400 ASSEMBLY LANGUAGE & MACHINE INSTRUCTIONS 5.1 Introduction 5.2 Instruction Execution Time 5.3 Program Memory                                                                                                                                                                  |     |

|      | 2.7.5 Some Programming Considerations Implicit                                                                                                                                                                    | 5.4 Assembly Language Instruction Listing                                                                                                                                                                                                                                            |     |

|      | I/O Transfer Implementation 2.7.6 AP Interrupt of Host                                                                                                                                                            | 5.5 AP Assembly Language Program Example 5.5.1 Assembler Directives                                                                                                                                                                                                                  |     |

| 2.8  | Auxiliary Port 2.8.1 Sequence of Operations 2.8.2 Input Port                                                                                                                                                      | 5.5.2 Instructions 5.5.3 Data Storage Instructions                                                                                                                                                                                                                                   |     |

|      | 2.8.3 Output Port 2.8.4 Typical Use of the Auxiliary Port                                                                                                                                                         | 6 PAC LISTINGS                                                                                                                                                                                                                                                                       |     |

| _    |                                                                                                                                                                                                                   | 6.1 Introduction                                                                                                                                                                                                                                                                     |     |

|      | SOFTWARE Introduction                                                                                                                                                                                             | <ul><li>6.2 Listing Format</li><li>6.3 User Programming</li></ul>                                                                                                                                                                                                                    |     |

| .5 1 | HILLOUGH CHOH                                                                                                                                                                                                     | 5 5                                                                                                                                                                                                                                                                                  |     |

3.1 Introduction

#### **ILLUSTRATIONS**

#### Fig.# Title

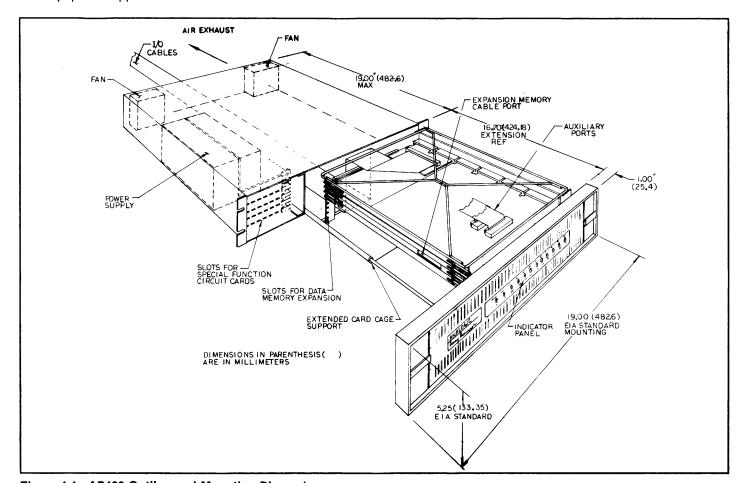

- 1-1 AP400 Outline and Mounting Dimensions

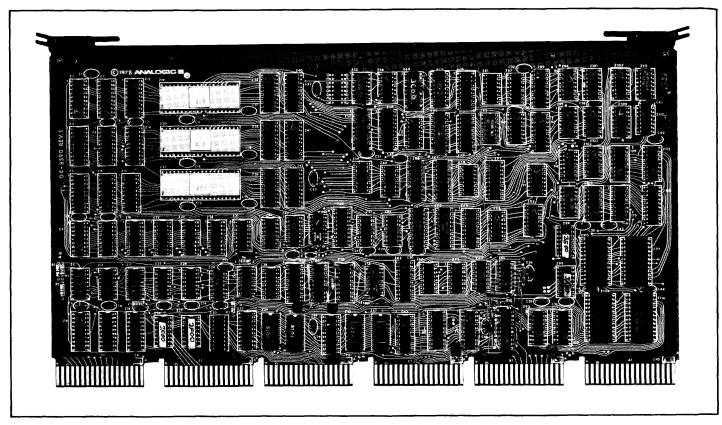

- 1-2 AP400 Arithmetic Pipeline Assembly

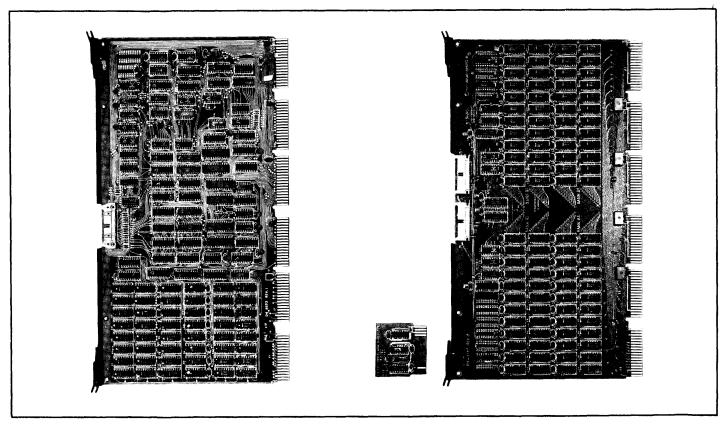

- 1-3 AP400 Data Memory and Expansion Memory Assemblies

- 1-4 AP400 Control Processor Assembly

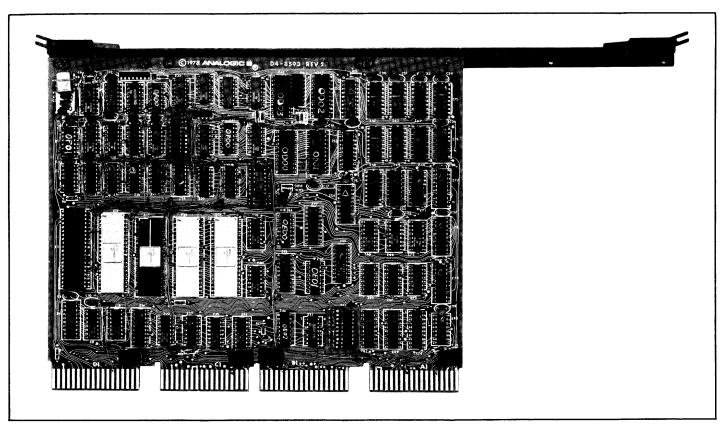

- 1-5 AP400 I/O Assembly (PDP-11)

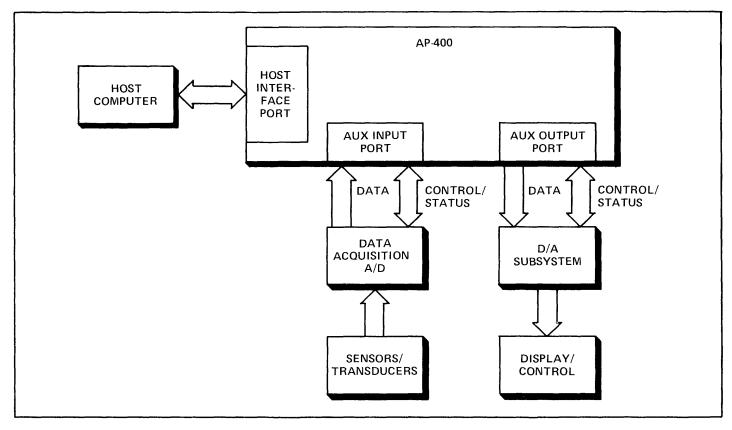

- 2-1 AP400 System Architecture

- 2-2 Pipeline Timing Efficiencies

- 2-3 Pipeline Arithmetic (PA) Block Diagram

- 2-4 PA Characterizer Stage Block Diagram

- 2-5 PA Multiplier Stage, Block Diagram

- 2-6 PA Accumulator/Logic Stage, Block Diagram

- 2-7 PAC Decoding Sequence, Hardware & Software

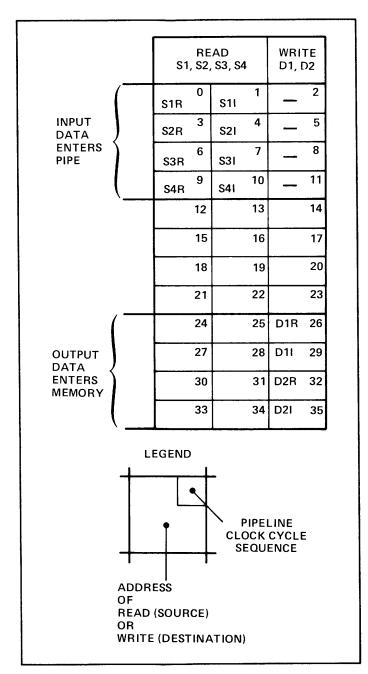

- 2-8 Read/Write Timing Sequence

- 2-9 Mapping PAD Codes into Memory Addresses

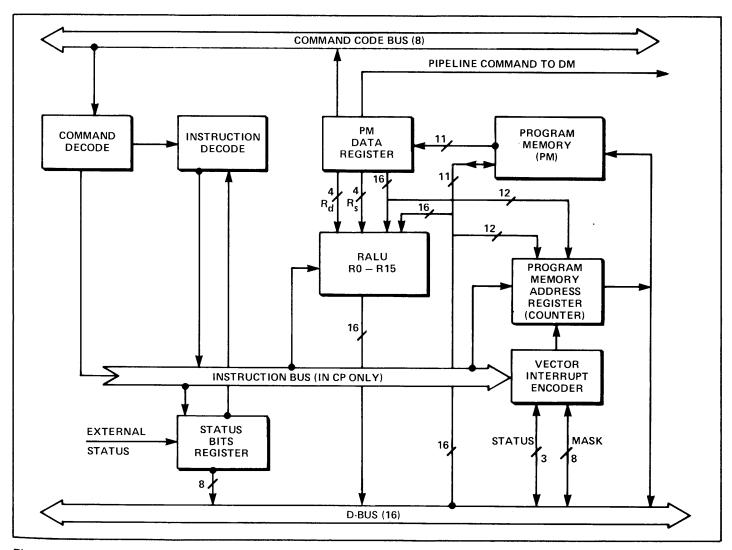

- 2-10 Control Processor Simplified Block Diagram

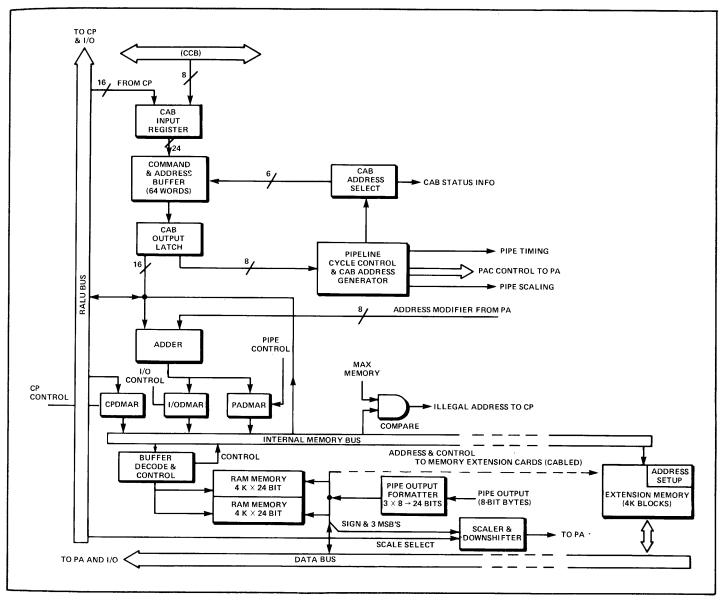

- 2-11 Data Memory Simplified Block Diagram

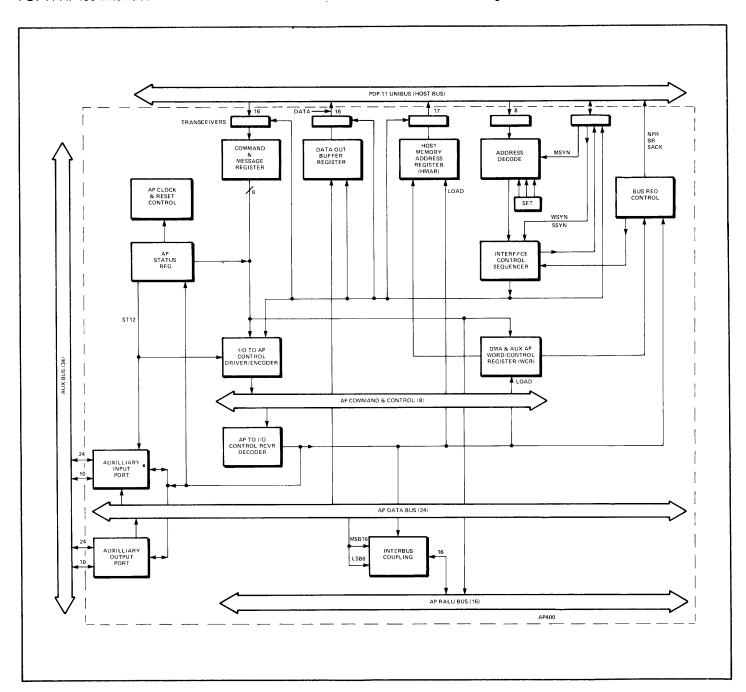

- 2-12 Interface (I/O) Simplified Block Diagram

- 2-13 AP400 Front Panel Showing Status Register Indicators

- 2-14 Command & Memory Register Word Format

- 2-15 Host Read of Message & Status Register, Host Write of Immediate or Data Commands

- 2-16 Host Read/Write of Data Memory

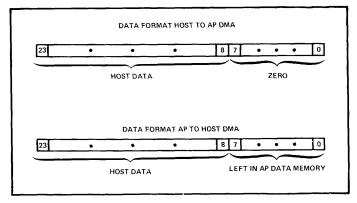

- 2-17 DMA Formats Host TO/FROM AP

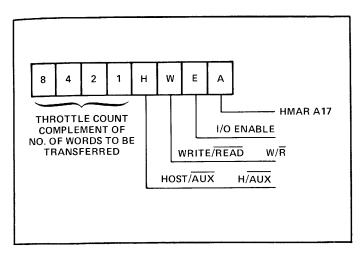

- 2-18 Word Count Register

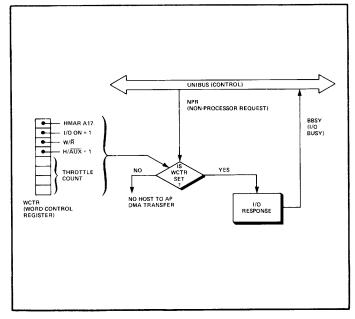

- 2-19 AP to Host in DMA Operation

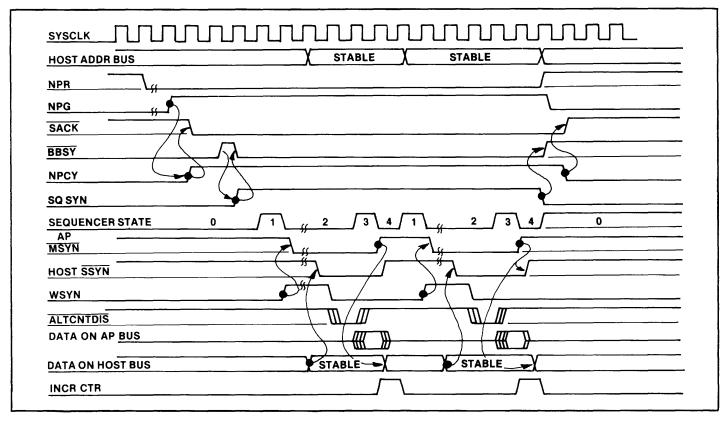

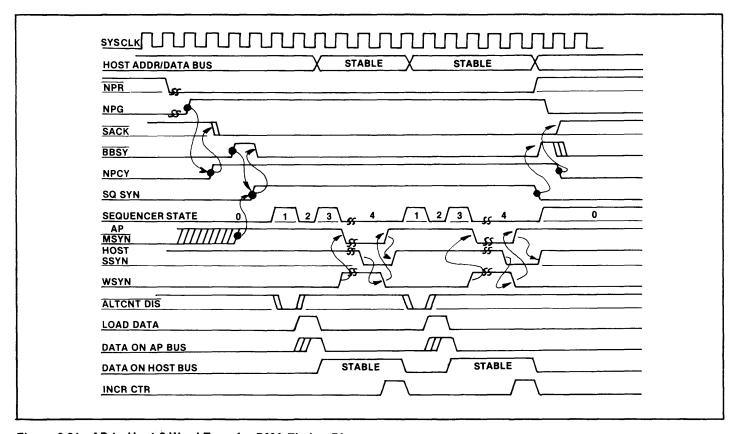

- 2-20 Host to AP DMA Timing Diagram

- 2-21 AP to Host 2-Word Transfer DMA Timing Diagram

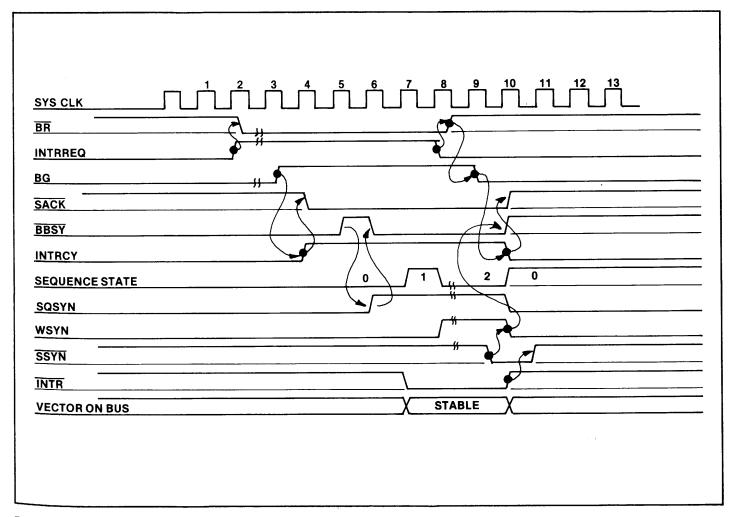

- 2-22 AP Interrupt of Host Timing Diagram

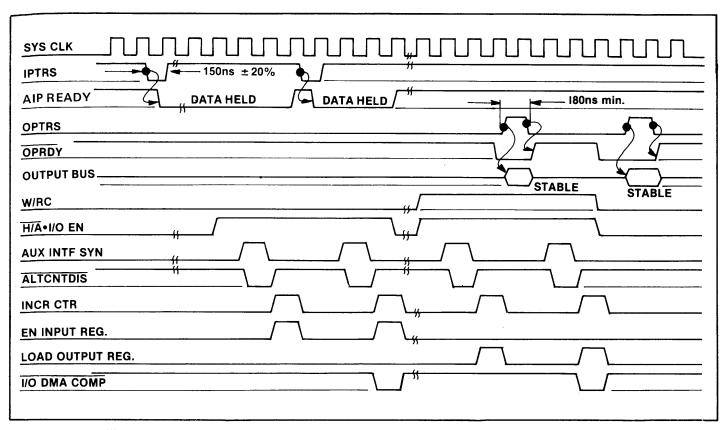

- 2-23 Auxiliary Port Timing Diagram

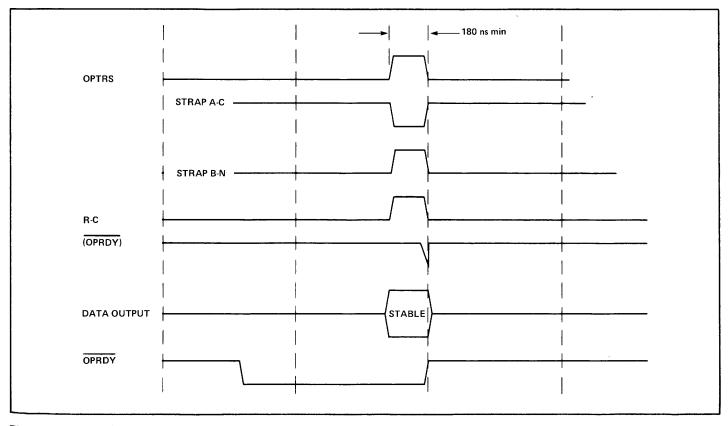

- 2-24 Auxiliary Port Output Strobe Polarity Selection

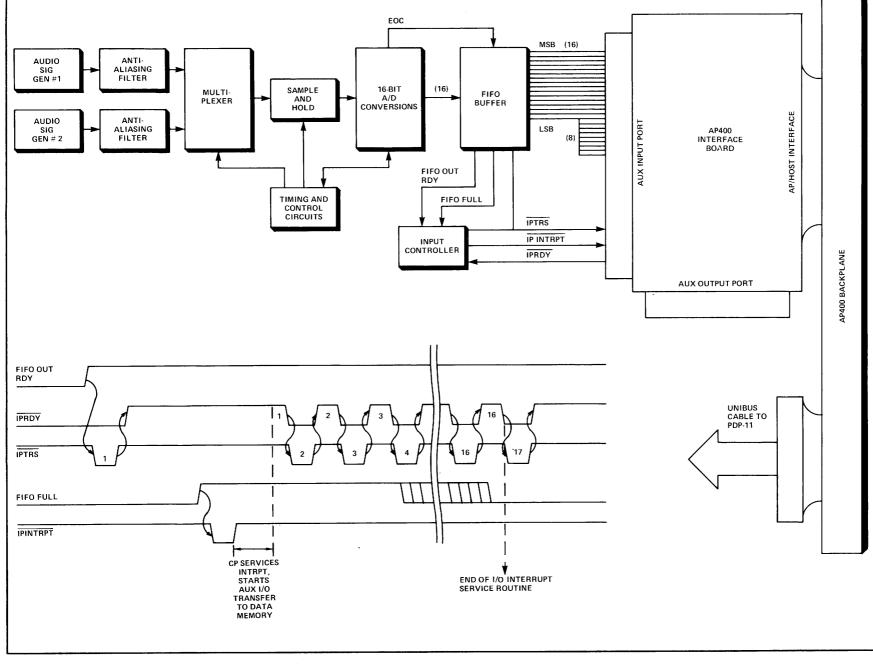

- 2-25 AP400 Auxiliary Port Application Block Diagram

- 2-26 Auxiliary Port Application Detailed Block Diagram

- 3-1 Sample Host FORTRAN Program, Real FFT on 1024 Data Points

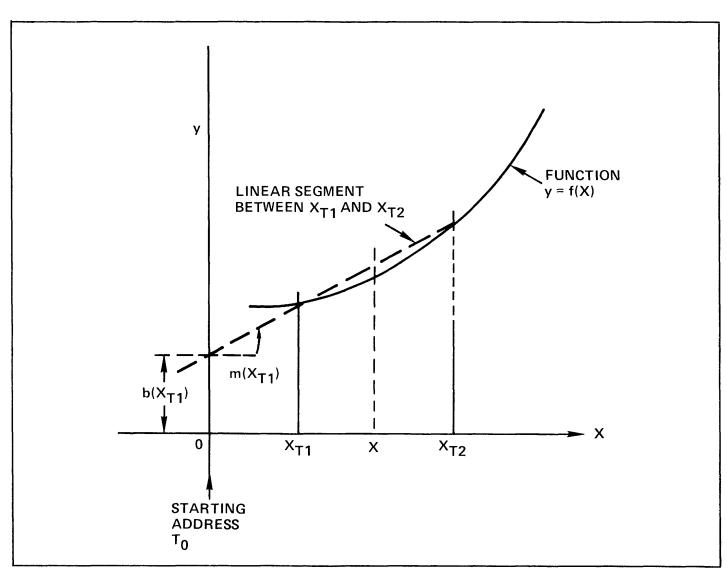

- 3-2 A Typical Linear Approximation Function

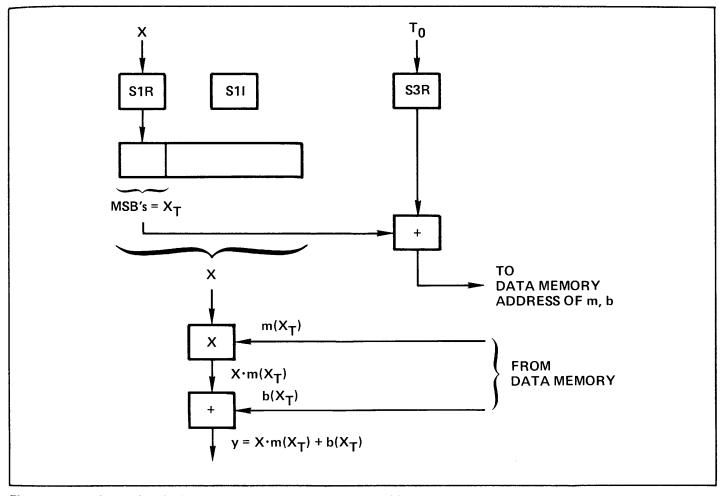

- 3-3 Implementing A Linear Approximation Function by Table Lookup

- 4-1 Function Control Block Contents

- 5-1 Sample AP Assembly Language Program Listing, Negating Data Points in a Vector

#### **TABLES**

- 1-1 Typical Performance Characteristics

- 1-2 Typical Process (From Host Point of View)

- 2-1 Address Modifier Select

- 2-2 ALU Function Select

- 2-3 HOST TO AP Command Codes In Hexadecimal

- 4-1 Function Control Block Elements—Description

# INTRODUCTION & GENERAL DESCRIPTION

#### 1.1 GENERAL

The Analogic Array Processor AP400 is a high speed arithmetic computation unit designed to be operated in conjunction with a general purpose microcomputer, minicomputer, or a computer main frame. In combination with its host computer, the AP400 peripheral adds a powerful computing capability, providing economical signal and data processing at throughput rates 10 to 100 times faster than the stand alone computer.

The AP400 delivers cost-effective performance in both dedicated and general purpose applications. It is easily programmed, for example, for signal processing in tomography, sonar, seismic exploration, speech analysis, vibration analysis, image enhancement, and automatic test equipment applications.

#### 1.2 PHYSICAL DESCRIPTION

As shown in Figure 1-1, the AP400 is configured in an EIA standard 19" (482.6mm) wide rack-mountable assembly, only 5.25"(133.35mm) high (also an EIA standard increment). The AP assembly includes the I/O board for the specified host, a Control Processor board, Arithmetic Pipeline board, and Memory board. It also includes its own power supply, real time clock assembly, and forced air cooling fans. In addition, as indicated in Figure 1-1, this assembly is designed for expansion up to the maximum data memory of 64K 24-bit words. Cabling to the host computer bus and to an auxiliary bus is ducted to the rear of the AP400 assembly. There is ample depth behind the case assembly depth of 19 inches (482.6mm) for rear cabinet interconnections.

Figure 1-1. AP400 Outline and Mounting Dimensions

The AP400 front panel includes 12 status indicator lights (including one to indicate the actuation and appearance of +5-volt power). They provide a visual indication of the relative operations of host computer and the AP400, and are useful in evaluating program efficiencies and in elementary trouble-shooting and diagnosis. Additional details are included in the functional descriptions in Chapter 2.

Figure 1-1 also illustrates the convenient access to the interior assembly. The assembly can slide forward on extensions built in to the wire card cage. During this operation a built-in "sleeve" also slides forward to maintain an efficient cooling configuration for the rearmounted fans so that the equipment may be operated without damage in its extended position. Note, in Figure 1-1, that the extended position also permits access to the spare slots in which the Memory expansion boards are inserted.

#### 1.3 AP490 CARD SET CONFIGURATION

The Array Processor may also be installed as an integral part of the host assembly. This is accomplished by installing the plug-in assembly boards and back plane within the computer main frame (or other peripheral). The card-set installation does not include the front panel, power supplies, or cage assembly.

#### 1.4 AP400 DESIGN FEATURES

#### 1.4.1 Operating Speeds.

The Analogic AP400 small-size, low-power array processor features an arithmetic pipeline design that, along with high speed memory components, buffered command and data ports, and multilevel programming, results in efficient, real time, digital signal processing previously available only in machines with many more components and that require complex programming. Typical processing times are listed in the table below.

## Table 1-1 TYPICAL PERFORMANCE CHARACTERISTICS

| Logarithm<br>Exponential             | 1.9μsec/point<br>2.4μsec/point |

|--------------------------------------|--------------------------------|

| Magnitude squared                    | 1.0µsec/point                  |

| Multiplication rate                  | up to 2.1                      |

| •                                    | million/sec                    |

| Addition, Subtraction rate           | up to 6.3                      |

|                                      | million/sec                    |

| 512-Point Real FFT                   | 1.5 msec                       |

| 1024-Point Real FFT                  | 3.6 msec                       |

| 1024-Point Complex FFT               | 7.4 msec                       |

| Real Convolution (512 Data, 1024     |                                |

| Kernel)                              | 7.3 msec                       |

| 1024-Point Real Vector * Vector      | 0.5 msec                       |

| 32 x 32 Complex Matrix Transposition | 1.9 msec                       |

#### 1.4.2 Arithmetic Pipeline. (Figure 1-2)

The Arithmetic Pipeline is the basis for the high speed processing ability of the AP400. Its operation is

described in detail in Chapter 2. In brief, the pipeline is internally programmed to receive eight 24-bit data words at the input of each pipeline pass and to produce four 24-bit data words at the output. The pipeline is structured into three stages of equal processing time. After it is once filled, data outputs occur at a rate equal to onethird of that required to fill the pipeline initially, as long as data is continuously input at the same rate. Each 24-bit data word in a group of words for a programmed pipeline operation represents the mantissa portion of a scaled data value. A common 16-bit exponent is stored for the group. The group of data words scaled for each such exponent is a "block", and the array processor operates primarily in a "block floating point mode". (The block floating point mode is further described in Chapter 3.). Some of the arithmetic pipeline design features are:

- ★ Normal Block Floating Point Data Format: 24-bit BFP 2's Complement Mantissa 16-bit BFP 2's Complement Exponent

- ★ Eight 24-bit data words in; Four 24-bit data words out

- ★ Up to 256 determinable Pipeline Arithmetic Commands

- ★ Multiplication operation: 24 x 24-bit input; full 48-bit result, truncated or rounded to 24 bits.

- \* Access to data-dependent table entries

- ★ Eight accumulators internal to pipeline, accessed as part of the pipeline operation without requiring external program cycle

- ★ Guard bits for overflow protection

- ★ Zero pipeline reconfiguration delay

#### 1.4.3 Memory (Figure 1-3)

The standard memory includes 2K words of 22-bit program memory and 4K words of 24-bit data memory. The data memory may be expanded with additional 4K words on the standard board. Up to 64K data memory words may be configured in 4K increments, using Expansion Memory boards. It should be noted that the program memory in the Array Processor may be augmented by storage in the Host or Auxiliary peripherals, since it is software configured. Some of the key features incorporated in the program and data memory, are listed below:

#### **PROGRAM MEMORY**

- ★ Standard Memory: 2048 x 22-bit, HMOS, 55 nsec RAM

- \* Address Register: 12 bits

- ★ 8 locations for vectored interrupts

- \* Contents are downloaded from the Host

#### **DATA MEMORY**

- ★ Standard Memory: 4096 words x 24-bit, HMOS, 55 nsec RAM

- ★ Add-on Memory: 4096 additional words on board; Expansion Memory boards: up to 16K words (4K increments)

- ★ Maximum Data Memory: 64K words

- ★ Program Stack: 64 words

#### **INTRODUCTION & GENERAL DESCRIPTION**

#### 1.4.4 Control Processor (Figure 1-4)

The Control Processor is the Array Processor's manager. It interprets Host-generated commands/instructions, and sets up the lists of addresses and commands for arithmetic unit processing, links programs, and passes addresses for data and parameters. In general, it functions to relieve the Host of the burden of managing the AP400. Some of the performance features designed into the AP400 Control Processor are:

- ★ 19 classes of machine language instructions

- ★ 16-bit computation word size

- ★ 16 registers, 16-bits wide

- ★ 8 levels of hardware vectored interrupts

- \* 8 special purpose hardware flags

- ★ Single-word CP instruction cycle time: 160 nsec

- ★ Maximum Host Memory and Auxiliary I/O DMA rate: 1.5 million words /sec.

#### 1.4.5 I/O Assembly (Figure 1-5)

A single Input/Output (I/O) card provides all the communications between the AP400 and the Host computer, and between the AP400 and devices connected to the AP400 via the Auxiliary Ports. A dedicated I/O card is required for each Host computer with which the AP 400 is specified to interface. Each card contains the circuitry to carry out the following I/O tasks:

- ★ Direct the AP400 status: Halt/Run, Single Step, etc.

- ★ Transfer data to and from the Host under Programmed I/O

- ★ Transfer data to and from Host via DMA

- ★ Access various nodes of the Array Processor for diagnostic testing

- ★ Transfer data in and out of Auxiliary Ports

#### 1.4.6 Software

The AP400 Array Processor is fully supported with software packages of the following types:

- ★ Applications: for problem solutions and real-time tasks

- ★ Systems: for control of Host and AP400 activity

- ★ Utilities: for software preparation and use

- ★ Diagnostics: for hardware and software fault detection and isolation

Documentation for AP400 software packages and AP400 installation are provided by:

AP400 Processor Handbook

AP400 Function Reference Manual

AP400 Host System Software Reference Manual

AP400 Interactive Debugging Tool Reference Manual

AP400 Linker Reference Manual

AP400 Diagnostic Reference Manual

AP400 PAC Reference Manual

Quick-Reference Card -- AP Assembly Language

Quick-Reference Card -- AP400 Interactive Debugging Tool

AP400 Installation Manual AP490 Installation Manual

#### 1.5 HOST-ARRAY PROCESSOR COMMUNICATION

#### 1.5.1 General

The following paragraphs describe a sequence of Host-Array Processor operations involved in executing an Array Processing function. This description illustrates the communications performed across the interfaces between the Host and the Array Processor. This section also introduces additional design features that contribute to the efficient operation of the AP400.

The scenario that follows is written from the view-point of an "observer" located in the Host computer who sees only the interface with the Array Processor and does not become aware or concerned with the operations internal to the Array Processor. Later paragraphs will consider the operation from the viewpoint of an "observer" in the Array Processor with similar constraints.

This illustration of a typical operation assumes that the AP400 is configured to interface with the designated Host computer, that the Host computer operating system FORTRAN compiler has been appended to include the AP FORTRAN calls. Also, that the Host operating system has been supplemented to include the AP Manager and AP Driver program modules. Normally, these are initializing actions and are completed at the time the AP400 is installed.

The sequence that is described includes many steps that are invisible to the system user. Almost all are invisible to the FORTRAN user of the Array Processor, and only very few are apparent to the Host Assembly Language user.

### 1.5.2 The General Sequence of Host-Array Processor Operation

The Host-Array Processor interaction occurs by both Programmed I/O (PIO) and Direct Memory Access (DMA) types of interface operation, and each of the interactions below is identified as to the type involved. In general, the DMA interface is accomplished with a single instruction for the transfer of a block of data at a transfer rate limited only by the read/write speed of the memory and buses involved. The PIO interface typically requires a separate instruction for each of the handshake protocols.

#### 1.5.3 A View from inside the AP400

The AP400 appears (from inside the interface boundary) as an independent, stored-program minicomputer. The Control Processor (CP) within the AP400 executes an assembled program of machine instructions according to the sequence called out by its program counter. In the AP400, the program counter is the Program Memory Address Register, PMAR. A program steps along at the

clock-controlled interval of 160 nanoseconds. Machine instructions may require a sequence of 2 or more such clock intervals. Most are executed in one, but a few may require up to 3 or 4, depending upon the arguments of the instruction.

When the programmed AP instruction calls for the use of the Pipeline Arithmetic unit (PA), the AP400 completes its control function by transferring four successive Command and Address words to the Command and Address Buffer (CAB). Its contents consist of the PA jobs to be done, and in the sequence to be accomplished. The CAB contents are continually changing as more pipeline commands are added, and as the existing ones are withdrawn to be processed.

The CAB has its own control pointer by which the 4-word instruction set is retrieved in the order stored. These instructions (PACs) are decoded in the pipeline in pre-programmed PROM's. The PAC's set up pipeline control signals and initial Data Memory addresses for PA processing of blocks of data beginning at that address. Addressed data is synchronously clocked through the pipeline at 1.92 microseconds per PAC and is

repeated for as many PACs as required for the complete block. For each PAC, the address of the input data is indexed until the block of data has been processed. The PA operation proceeds independently of the CP operations (once the CP has transferred the command to the CAB), retrieving data values from designated memory locations or from a modified address location, and storing the results in programmed Data Memory locations.

The Command & Address Buffer (CAB) can store up to 64 24-bit words, and, since 4 such words comprise a pipeline instruction set, the CAB has the capacity to store up to 16 PA instruction sets. When the CAB is near full, it causes the CP clock to stop to prevent possible overflow of the CAB, and consequent loss of an instruction. (The PA clock is not stopped, and processing through the PA continues.) When the CAB has been emptied below the "full" level, the CP clock is restarted, and the program continues its execution. When the CAB is empty, the PA clock is stopped to prevent any errors from timing offsets in the Pipeline and Data Memory combination. Note that the operation is asynchronous with the Host timing, but is rigorously controlled within the AP400.

Table 1-2

Typical Process (From Host Point of View)

| STEP | ACTION                                                                                                                                                                                                                        | TYPE OF I/O<br>TRANSFER |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 1.   | Host loads the address of a Function Control Block (FCB), which resides in Host Memory, into a location in the AP Data Memory.                                                                                                | PIO                     |

| 2.   | Host announces its need for the AP400 to perform a function by loading the "Perform Function" message into the AP400 Message Register, and then interrupts the AP400.                                                         | PIO                     |

| 3.   | AP400 responds to the interrupt and fetches the message from the AP400 Interface.                                                                                                                                             | (AP only)               |

| 4.   | AP400 retrieves the FCB address from the AP400 Data Memory.                                                                                                                                                                   | (AP onlÿ)               |

| 5.   | AP400 accesses the FCB in Host Memory and transfers FCB to AP400 Data Memory.                                                                                                                                                 | DMA                     |

| 6.   | The AP Function specified in the FCB is initiated, and is executed based upon control information stored in the FCB.                                                                                                          | (AP only)               |

| 7.   | Any data required by the AP Function is retrieved by the AP directly from Host Memory. Likewise, any AP Function results to be directed to the Host Memory are placed there directly by the AP.                               | DMA                     |

| 8.   | When the AP Function is completed, the AP "marks" the FCB in Host Memory and checks for another AP Function FCB chained from this last one.                                                                                   | DMA                     |

| 9.   | If another FCB is chained to the last one, the AP retrieves it and the process described above repeatswithout an interruption of the Host unless one is required for programmed synchronization of Host and AP operation.     | DMA.                    |

| 10.  | If no further FCB is chained, the AP places a "Func-<br>tion Done" message into the designated register,<br>and interrupts the Host.                                                                                          | Interrupt               |

| 11.  | When the interrupt is acknowledged, the Host may resume execution of a task that was suspended while awaiting the AP results, or may set a flag to indicate "AP Done", which a subsequent Host task may utilize as necessary. | (HOST only)             |

| 12.  | Meanwhile, the AP waits for another "Perform Function" message, and may continue to perform its ongoing operations (e.g. real-time input through the auxiliary I/O port).                                                     | (AP only)               |

Figure 1-2. AP400 Arithmetic Pipeline Assembly

Figure 1-3. AP400 Data Memory and Expansion Memory Assemblies

Figure 1-4. AP400 Control Processor Assembly

Figure 1-5. AP400 I/O Assembly (PDP-11)

**NOTES**

## PRINCIPLES OF AP400 OPERATION

#### 2.1 INTRODUCTION

This chapter describes the system architecture of the AP400 and the implementation of the major functions. The word format and block floating point implementation in the AP400 are described in Chapter 3, Programming Considerations.

#### 2.2 SYSTEM ARCHITECTURE

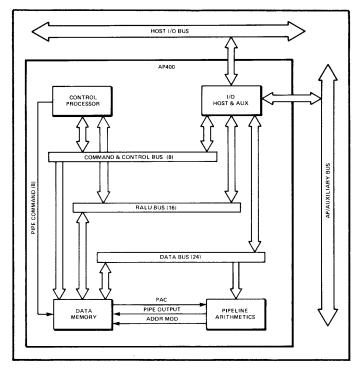

As shown in Figure 2-1, The AP400 is essentially four basic functional units interconnected by three buses (identified in the illustration) and other dedicated hardwired connections (not shown). The four functional units and their short form abbreviations are:

Interface for Host and Auxiliary (I/O) Control Processor (CP) Pipeline Arithmetics (PA) Data Memory (DM)

In some configurations, there may be one (or more) Expansion Data Memory unit(s). Functionally, however, these are only extensions of the basic Data Memory, and their incorporation does not change the system block diagram as shown in Figure 2-1. Each AP400 is supplied with a Real Time Clock assembly, that is either incorporated in an Expansion Memory assembly (if installed), or is installed as a small pc-card plugged into the back plane assembly. The primary oscillator is located in the Control Processor unit.

The three AP400 internal buses and their short form abbreviations are:

Command & Control Bus (CCB)

Register and Arithmetic Logic Unit Bus (RALU)

Data Bus (DB)

The AP400 has been designed so that related functions are, for the most part, located in the same physical assembly. Thus, the functional block subdivision shown in Figure 2-1 is used for the pc-board assemblies in the instrument, and appear on the board labels. The Interface assembly is Host dependent, and is designed for compatibility with a specific Host. By grouping the functions in separate physical units, and keeping all the interface functions on the I/O board, it is possible to adapt the AP400 to a new Host by replacing only the I/O board assembly.

Figure 2-1. AP400 System Architecture

#### 2.2.1 Unit Functions

The Interface (I/O) provides for all the communications between the AP400 and its Host or Auxilliary peripherals. It provides for the transfer of data under programmed I/O or DMA transfer modes, and for accessing specified nodes in the Array Procesor for diagnostic testing.

The **Control Processor (CP)** is the manager of the AP400. It is essentially a minicomputer, executing the programmed tasks passed to it by the Host, and using the AP400 Data Memory and Pipeline Arithmetics when programmed to do so. It contains its own microprocessor unit to perform various register-to-register, quantity-to-register, and register address modifications to support pipeline setup requirements. It also contains an Interrupt Vector structure for interrupt-driven processor coding, as well as read/write type of Program Memory.

The **Pipeline Arithmetic (PA)** is the "number crunching muscle" of the AP400. It processes 4 pairs of 24-bit input pairs (or 8 independent inputs) through three programmed stages: data characterization (allowing for input data-based modifications), multiplication, and arithmetic/logic operations and accumulations. The PA generates either 2 pairs of output values, or 4 independent outputs. This unit also contains the **PAC**s in factory programmed PROMS that provide the pipeline control signals.

The **Data Memory DM** provides a contiguous space of 24-bit RAM locations for data storage and the three registers for addressing the memory: CP-DMAR, I/O-DMAR, and PA-DMAR. The Data Memory is expandable up to 65K 24-bit words. The basic DM board is configured with 4K RAM storage, and has the capability for on-board addition of another 4K. Thereafter, additional data memory storage in 4K increments are assembled on Expansion Memory boards, with up to 16K per Expansion Memory board. This unit also contains the Command & Address Buffer **CAB** that stores up to 64 24-bit words of instruction codes for the **PA**. A group of 4 words from the CAB completely defines a pass through the pipeline. The unit also contains the means for modifying the addresses of the input data for the pipeline.

#### 2.2.2 AP400 Buses

The bus structure and operation within the AP400 are essentially invisible to the user. Their descriptions are included here to provide some reference for the unit descriptions that follow.

The Command & Control Bus (CCB) is a bidirectional bus, 8 bits wide. The commands put onto this bus determine the routing of data within the AP400 by way of the other buses. After a transfer has occurred, an address register may be incremented or a status bit set as part of the same command action. The use of the CCB minimizes the number of separate control signals needed to coordinate the actions of the four functional units of the AP400.

The CCB is also pipelined, so that the issue of one command occurs while the previous command is being executed. Every clock pulse (160 nanoseconds) a new command can be issued on the command bus. Transfers requiring more than 160 nanoseconds for execution because of propagation delays, are accomplished by the hardware issuing the identical command for two clock cycles.

When the CCB is not needed, a default command is issued that allows the CP to execute instructions not using the RALU bus, and connects the PA to the DM for pipeline operations.

The **Data Bus DB** is a bi-directional bus, 24 bits wide. It is used by the I/O when transferring data to/from the Host and from/to data memory. The data bus is actively used in the performance of the pipeline operations, transferring four pairs of data values from Data Memory locations specified by the pipe setup addresses to the pipeline. The pipeline outputs to Data Memory

travel over a separate 8-bit wide connection and are formatted in 24-bit words for Data Memory and Data Bus. Access to Data Memory via the Data Bus is shared by the I/O, CP, and PA, and the priority is in that order (PA last). When either the I/O or CP require the use of the Data Bus, the PA operation is momentarily interrupted, by stopping its clock. This is called **cycle stealing.**

The Register & Arithmetic /Logic Unit Bus (RALU) is a bi-directional bus, 16 bits wide. It is used to transfer addresses from the Control Processor and I/O to and from the Data Memory. The RALU bus is also used to transfer most of the information to the CAB from the CP.

The control bus structure used in the AP400 greatly simplifies on-line program debugging and fault detection. The CCB allows examination of the contents of most storge elements inside the AP400 while any program is either running or temporarily halted. In this mode the CP can duplicate the actions of the HOST in issuing read commands to the AP400 Host Computer's request of the Interface to do the same. Finally, the same paths and control logic are used for loading and reading back programs and data as for normal program execution.

#### 2.3 AP400 PIPELINE ARITHMETIC UNIT (PA)

#### 2.3.1 Pipeline Arithmetics

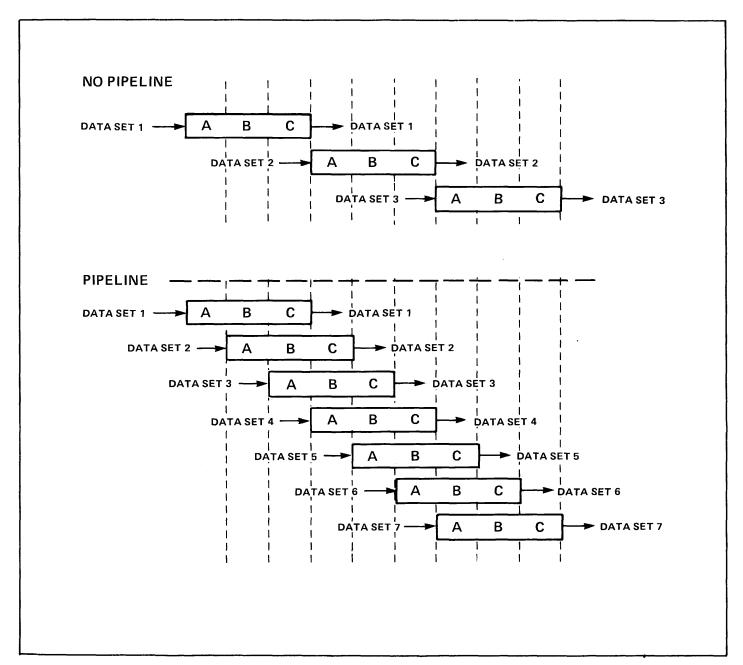

One way to increase the throughput when processing arrays of data is to parallel complete arithmetic units and to partition the data among them. This technique is costly in terms of hardware. It also causes programming complexity associated with maintaining correct synchronization among parallel units and in combining partial and final results.

Another way to increase throughput is to partition the arithmetic unit into stages and to introduce new data inputs to the first stage when the previous data moves to the second stage, etc. This is the technique used in the AP400 and three such stages are used. They are:

Stage A: Data Characterization

Stage B: Data Multiplication

Stage C: Data Accumulation and Logical Manipula-

tion

To increase the efficiency of such a partitioning, the configuration of each stage and passing of data between stages are determined by program control. This flexibility meets the requirements for a wide range of processing functions. The speed advantage of a 3-stage pipeline is illustrated in Figure 2-2. As shown in the illustration, the processing cycle time is A + B + C. When not pipelined, the processing of  $\bf n$  data sets requires  $\bf n$  processing cycle times, however fast or slow that may be.

In a 3-stage pipeline unit, the results of processing the first data set will not appear until after the full time of a processing cycle (A + B + C). But the second and succeeding data set results appear at intervals of one-third the processing cycle thereafter. Thus for  $\bf n$  data

pairs, the processing time is 1 + 1/3(n-1) cycles; and for large "n", the value approaches 1/3 the time. Note also that the last data pair to enter the pipeline must be "pushed out" in some manner if no other data pair follows.

#### 2.3.2 The AP400 Pipeline Stages

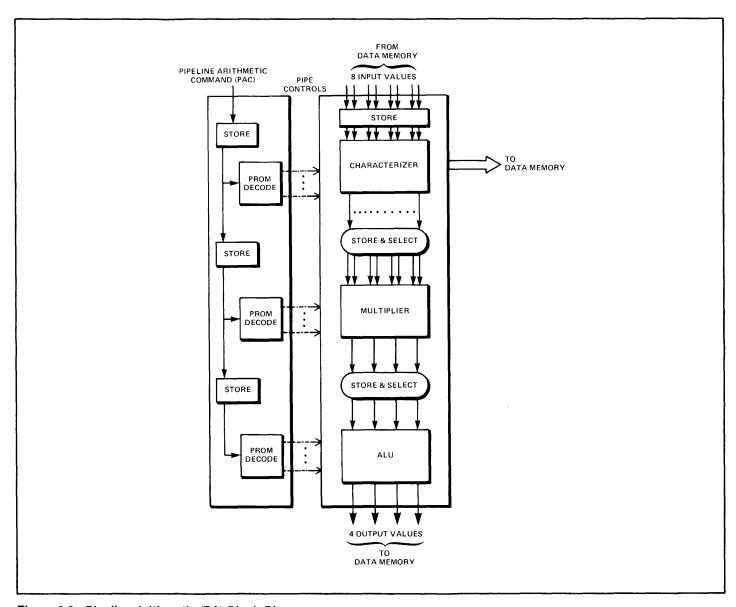

As shown in Figure 2-3, the 3-stage Pipeline Arithmetic unit receives eight 24-bit values at the input and delivers four 24-bit results at the output of the third stage.

Each stage of the PA is designed to perform several variations of that stage's function. Control

signals decoded from the PIPE instruction of the AP program configure each stage so that the appropriate inputs are selected, and the desired arithmetic combinatorial or logical operations are performed. In brief, a programmed instruction in the AP Assembly Language program is translated into a set of control signals. These signals synchronize the configuring of each of the three stages with the stepping of the numerical data through the pipeline.

Typically, the numbers that are processed through the pipeline for a given function have been "normalized" for a block floating point value. Thus, the 24-bit numbers

Figure 2-2. Pipeline Timing Efficiencies

are all mantissas of the same block exponent. The PA includes a provision to examine the results and to keep track of the change required in the block exponent to normalize the block.

The three pipeline stages and their functions are:

Characterizer Stage: a versatile type of data conditioner, that prepares multiplier and multiplicand inputs from source data or from tabular data indexed by the source data.

**Multiplier Stage:** performs multiplication of selected multipliers and multiplicands with optional accumulation of partial products.

Accumulator/Logic Stage: peforms arithmetic and logical operations on selected multiplier stage outputs. These include accumulations, additions, subtractions, logical comparisons, and block exponent normalization functions.

Figure 2-3 also indicates an inter-stage storage and selection block function. This acts as a type of controlled cross-bar switching function, setting up appropriate selection of the four pairs of multipliers and multiplicands for the Multiplier stage from any set of inputs of the previous stage.

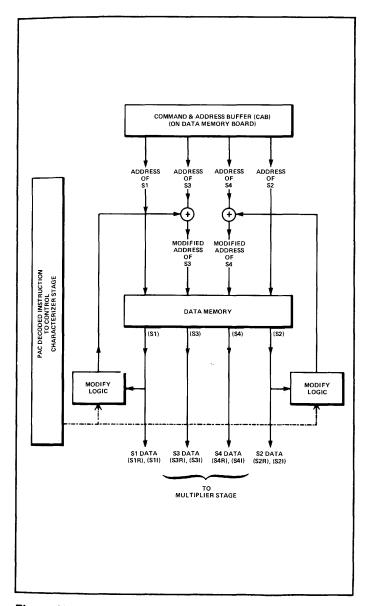

#### 2.3.2.1 The Characterizer Stage

Figure 2-4 illustrates the logical operation of the PA Characterizer Stage on the four source number pairs. As noted earlier, these may be complex pairs or independent values in adjacent addresses. As shown in the illustration, control signals determine whether these source numbers are passed through unchanged, or whether some are used in a table lookup mode. When they are passed through unchanged, then all 4 pairs become possible multiple inputs. When the characterizer is used in a lookup mode, then the data values of S1

Figure 2-3. Pipeline Arithmetic (PA) Block Diagram

Figure 2-4. PA Characterizer Stage Block Diagram

are used to modify the initial address of S3 (and the data values of S2 modify those of S4). The algorithms that generate the address modifier use either the four, six or eight MSB's of S1R (or S2R); or a combination of the 2 or 4 MSB's of S1R and S1I (or S2R and S2I); or the leading zero count with or without the sign value of S1R (or S2R).

Table 2-1 indicates the codes (1 through 7) that are used to examine the leading bits (MSBs) of S1 and S2 in performing a modification of the address for S3 and/or S4. Code 0 results in no modificiation.

Since the table data is addressable at any valid memory location, this feature of the characterizer permits the user to substitute data tables in any generic-type algorithm. For example, a linear interpolation algorithm can be used with a data table to obtain generated functions (logarithms, trigonometric values, etc), or to perform piecewise interpolation on incoming data variables.

| Table 2-1                                                                                                                                                  |                              |                                          |                                                                                     |                                      |                                                                                                                            |                                                                                                                            |                                        |                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------|

| ADDRESS MODIFIER SELECT                                                                                                                                    |                              |                                          |                                                                                     |                                      |                                                                                                                            |                                                                                                                            |                                        |                                        |

| 1<br>2<br>3<br>4<br>5<br>6<br>7                                                                                                                            | 0<br>0<br>R0<br>0<br>10<br>0 | 0<br>0<br>R <sub>1</sub><br>0<br>11<br>0 | 0<br>R <sub>0</sub><br>R <sub>2</sub><br>0<br>I <sub>2</sub><br>0<br>R <sub>0</sub> | 0<br>R1<br>R3<br>0<br>I3<br>L1<br>L1 | R <sub>0</sub><br>R <sub>2</sub><br>R <sub>4</sub><br>I <sub>0</sub><br>R <sub>0</sub><br>L <sub>2</sub><br>L <sub>2</sub> | R <sub>1</sub><br>R <sub>3</sub><br>R <sub>5</sub><br>I <sub>1</sub><br>R <sub>1</sub><br>L <sub>3</sub><br>L <sub>3</sub> | R2<br>R4<br>R6<br>R0<br>R2<br>L4<br>L4 | R3<br>R5<br>R7<br>R1<br>R3<br>L5<br>L5 |

| NOTE: R <sub>0</sub> to R <sub>7</sub> are MSBs of S1R or S2R. I <sub>0</sub> to I <sub>3</sub> are MSBs of S1I or S2I. L's define the leading zero count. |                              |                                          |                                                                                     |                                      | S2I.                                                                                                                       |                                                                                                                            |                                        |                                        |

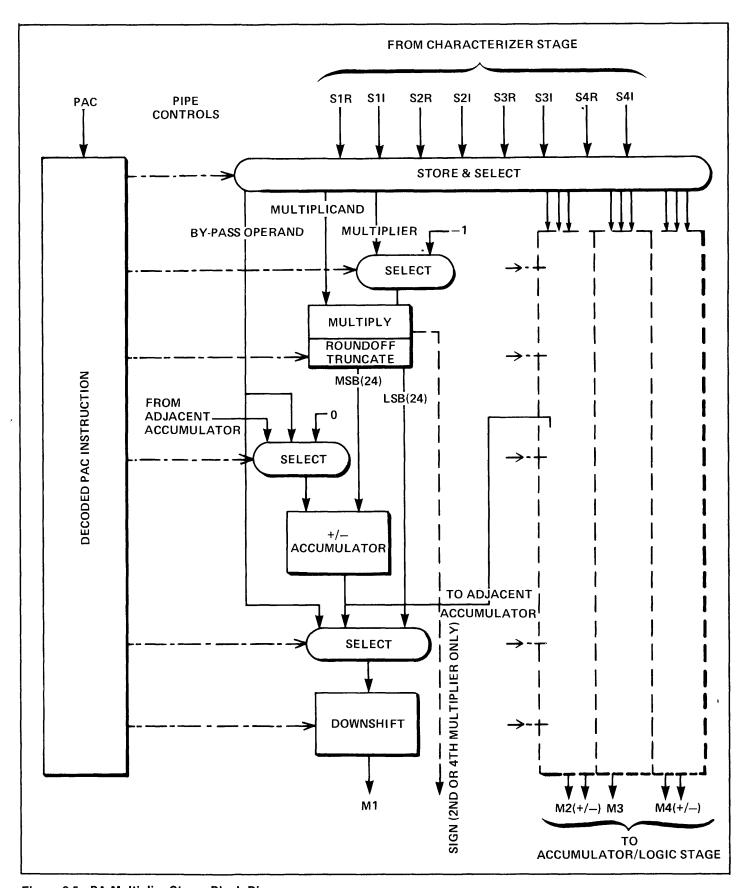

#### 2.3.2.2 The Multiplier Stage

The Multiplier Stage accepts eight (8) 24-bit input operands and delivers four (4) 24-bit output results. The result of the multiplication is a 48-bit word which is truncated or rounded to 24 bits, according to the decoded PAC instruction. When required, two 24-bit results may represent the two parts of a 48-bit double precision result. Figure 2-5 illustrates the logic flow for any one of the four adjacent multipliers in this stage. As shown in the illustration, decoded instructions develop control signals that configure the multipliers in five main groups:

- 1. To determine which input (S1R, S1I, S2R, S2I, etc.) will be a multiplier, multiplicand, or bypass operand. Recall that the S3 and/or S4 values may be table lookup data.

- To determine whether the product will be rounded or truncated.

- 3. To determine whether the MSB's or the LSB's of the output, or the bypass operand will be passed to the Storage/Select for the next stage.

- 4. To determine whether an adjacent accumulator result will be introduced into the accumulator.

- 5. To determine whether the result of the multiplication will be scaled (downshifted) before passing to the next stage. The downshift may be 0, 1, 2, or 3 places.

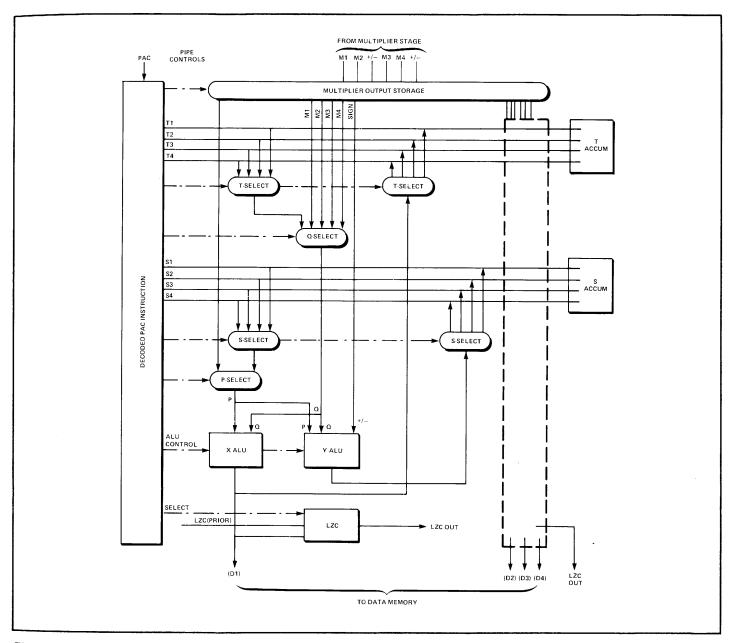

#### 2.3.2.3 Accumulator/Logic Stage

Figure 2-6 illustrates one of four processing units making up the third stage of the PA. Each unit includes two Arithmetic Logic Units (ALU's) and some data selection. The data being processed in this stage are selected from the four multiplier outputs (M1, M2, M3, and M4) and from eight accumulator registers of 24-bits each, labeled S1, S2, S3, and S4, and T1, T2, T3, and T4. These accumulators may be loaded either by a "loading" PAC prior to this PAC, or by the current PAC for use in the next pass of this PAC. Sign information from one of the multiplier outputs can also be used in the ALU operation, to provide conditional logic capabilities.

Figure 2-5. PA Multiplier Stage, Block Diagram

Figure 2-6. PA Accumulator/Logic Stage, Block Diagram

Both ALU's in each of the four processing units receive the same inputs labeled P and Q, but can form different functions of those inputs. Their arithmetic/logical combinations are determined in complementary pairs by the instruction-decoded control signals. Table 2-2 defines he 16 possible functions in each of the ALU's that are controlled by the instruction.

The outputs of each of the four units in this stage go to the PA output line and/or to replace an accumulator value in one of the eight accumulators.

A **leading zero count** function may be performed on data leaving the Accumulator/Logic stage. When this function is enabled by the decoded instruction, the leading-zero-count of the present computation is com-

pared with the previous result of such a comparison, and the lower of the two is set up as output for later comparisons. At the end of a function processing operation, the output value represents the **number of shifts to normalize**, **NSN**, and may be used to modify the block exponent for later processing. The function is programmable so that it may be inhibited when the user knowledge of the data and the operation provides assurance that such a normalization would not be necessary.

#### 2.4 THE PIPELINE ARITHMETIC COMMAND (PAC)

#### 2.4.1 General

As shown in Figures 2-3 through 2-6, the Pipeline Arithmetic unit stages are configured for each pass of

Table 2-2

ALU FUNCTION SELECT

| HEX CODE                                  | X ALU FUNCTION           | Y ALU FUNCTION          |

|-------------------------------------------|--------------------------|-------------------------|

| Q                                         | Q                        | Q MINUS P               |

| 1 1                                       | Р                        | l Q l                   |

| 2                                         | P PLUS Q                 | Q                       |

| 3                                         | P PLUS Q                 | Q MINUS P               |

| 4                                         | P MINUS Q                | Q PLUS P                |

| 5                                         | P PLUS Q PLUS CARRY      | Q MINUS P PLUS CARRY -1 |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>A | P MINUS Q PLUS CARRY - 1 | Q PLUS P PLUS CARRY     |

| 7                                         | P OR Q                   | QORP                    |

| 8                                         | P AND Q                  | Q AND P                 |

| 9                                         | P EXOR Q                 | Q EXOP P (= Q EXNOP P)  |

| Α                                         | IF MULT +                | IF MULT +               |

|                                           | THEN P                   | THEN Q                  |

|                                           | ELSE Q                   | ELSE P                  |

| В                                         | IF MULT +                |                         |

|                                           | THEN P PLUS Q            | Q OR P                  |

|                                           | ELSE P MINUS Q           |                         |

| С                                         | SPARE                    | SPARE                   |

| D                                         | IF MULT +                |                         |

|                                           | THEN P PLUS CARRY        | Q                       |

| _                                         | ELSE P PLUS CARRY - 1    |                         |

| E                                         | Q                        | IF MULT +               |

|                                           |                          | THEN Q PLUS CARRY -1    |

| _                                         | D MINUS O                | ELSE Q PLUS CARRY       |

| F                                         | P MINUS Q                | Q                       |

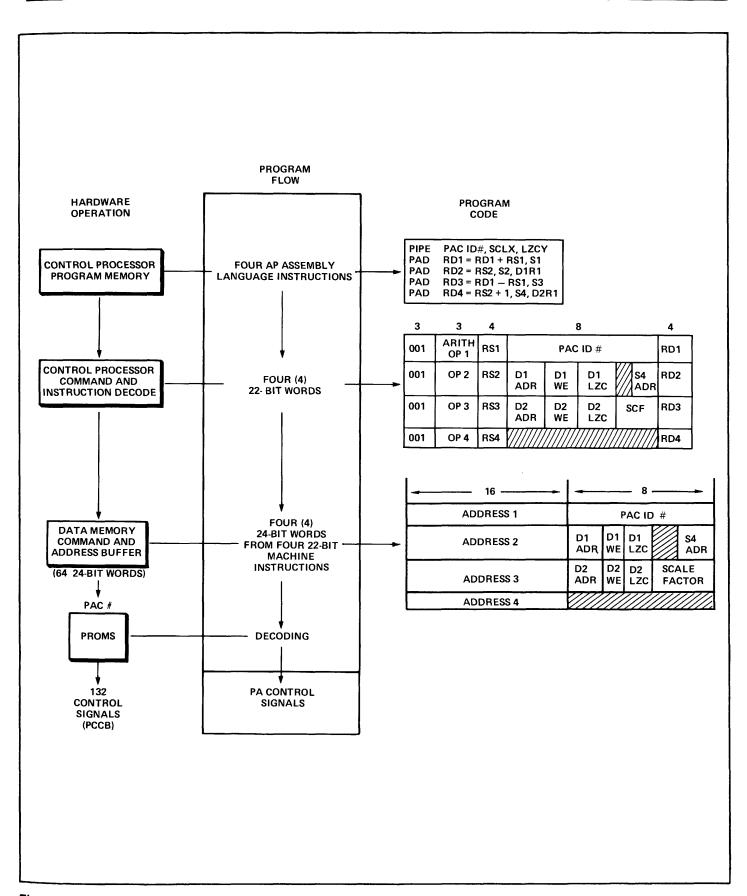

data through the "pipe" by a decoded command. The controls for each stage are derived from the command (shown in the sequence in Figure 2-7) by PROMs that are factory-programmed for the designated pipeline functions. If desired, a user may change these PROM's, and a documentation package is available to support this option. While the form of the command and its decoding are transparent to the FORTRAN and Host Assembly language programmer, brief descriptions of these items are included here to clarify the pipeline concepts described previously and to indicate the power of the AP400 Assembly Language instruction set. Although the AP400 Control Processor uses only 20 basic instructions, the Pipe instruction is expandable into 256 different PAC configurations. This macrocode expansion provides a highly flexible and efficient instruction set when writing AP400 Assembly Language code.

#### 2.4.2 Elements of the PAC

Each PAC instruction in machine language consists of **five** instructions in the form of a **PIPE**, followed by four **PAD**'s (setup instructions).

The **PIPE** may include one or more arguments identifying the PAC function, a scale factor operation, and a leading-zero count operation.

The PAD arguments include address codes for source and destination data. The actual memory addresses are computed from these codes, and are described later.

It should be noted that the PAC specifies one pass of a data set and associated commands through the three stages of the pipeline. The application-program structure determines the number of passes required as well as the amount of data to be processed. It is possible to **interleave** PAC's; one data set of 8 (or 4 pairs) of values and commands pass through the pipeline as part of function "A", followed immediately by the data set and commands for function "B", followed by function "A", etc.

Figure 2-7. PAC Decoding Sequence, Hardware & Software

#### 2.4.3 Pipeline Timing

A complete pass through the pipeline requires a number of discrete, well-defined operations: of fetching operands, operating on them, and storing the results. These are clocked through the pipeline at clock intervals of 160 nanoseconds, and a total of 36 such intervals are used for one pass. When the pipeline is kept busy, two number-pair results appear at the pipe output every 1.92 microseconds.

Figure 2-8 indicates the sequence of cycles in a pipeline pass. Twelve (12) cycles are used for read/write, and the remaining 24 cycles are used to accomplish the pipeline arithmatic operations. The 12 read/write time in-

Figure 2-8. Read/Write Timing Sequence

| PAD NUMBER | POSSIBLE MAPPINGS                       |

|------------|-----------------------------------------|

| ADDRESS 1  | S1, D1R, D1I, D1RI, D2R, D2I, D2RI      |

| ADDRESS 2  | S2, D1R, D1I, D1RI, D2R, D2I, D2RI      |

| ADDRESS 3  | \$3, \$4, D1R, D1I, D1RI, D2R, D2I, D2R |

| ADDRESS 4  | S4, D1R, D1I, D1RI, D2R, D2I, D2RI      |

Figure 2-9. Mapping PAD Codes into Memory Addresses

tervals use the Memory Data Bus , and if that bus is required for an I/O or CP operation the PA clock is temporarily stopped.

#### 2.4.4 Pipeline Addressing

As shown in Figure 2-7, the source and destination addresses are encoded in the Control Processor (CP) by PAD set-up instructions. The four 22-bit words contain codes for the arithmetic operation, the register addresses for source and destination, and codes identified as D1 ADR and D2 ADR. The latter are used to control the mapping of the source and destination addresses into 16-bit address streams A1, A2, A3, and A4 as part of the 24-bit words that are stored in the Data Memory Command and Address Buffer. (The 16 bits address up to 64K of Memory locations).

Figure 2-9 includes a table that describes the mapping. It should be noted, as shown in Figure 2-9, that the pipeline processing accomplishes a "data replacement" action. That is, the pipeline source data in memory address S1 may be replaced by the D1 output at the end of the pipeline pass. (D1R replaces S1R and D2I replaces S2I.) Note, also, that the addresses A3 and A4 may be modified by the actions of the characterizing stage in determining the location of S3 and S4.

#### 2.4.5 Coding Considerations

The pipeline works at maximum efficiency by processing PIPE instructions in a continuous sequence. The Command & Address Buffer (CAB) queues up instructions for the pipeline, not only by storing up to 13 different PAC's, or pipeline instructions, but also by causing the same PAC to sequence through all the data points in a block of data. This latter action is usually more significant as far as elapsed time is concerned. Both actions allow the programmer ample time to group together any remaining coding instead of spreading it around within the program. This makes coding, or writing in AP Assembly Language, more straightforward and allows existing code to be understood more easily. At the same time, the pipeline can operate on a more continuous basis.

#### 2.5 THE CONTROL PROCESSOR

#### 2.5.1 Functional Overview

The Control Processor (CP) is the executive controller of the AP400. It is, essentially, a minicomputer that serves as central processing unit for the Array Processor. The functions of the Control Processor are to set up the lists of addresses and commands that the Pipeline Arithmetic unit then executes, to link programs (including parameter and initial conditions passing), and to handle programmed flag conditions and interrupts. As shown in Figure 2-10, the Control Processor includes: a 16-Register File Arithmetic & Logic Unit (RALU) microprocessor element, Program Counter, Program Memory Address Register, Command and Instruction Decoder blocks, Status Bits register, and the Interrupt Vector encoder. Communication with other units of the Array Processor is accomplished by the RALU and Command Code buses, as well as interconnecting wiring of the Pipeline Command, External Status lines, and the Interrupt Signals. An internal (CP) Instruction Bus is also used.

#### 2.5.2 Program Memory

The Program Memory (PM) is 2048 words of 22 bits. It is loaded by the Host prior to run time with the AP400 Executive and the Function Library required for the applications being processed. The Program Memory is accessed by the Program Memory Address Register. which advances the 12-bit address pointer one word at a time. The PMAR receives inputs from the Vector Interrupt Encoder, the Decoded Command and Instruction bus, the RALU bus, and the Program Memory. Outputs from Program Memory are stored in a Program Memory Data Register which is used to implement overlapping normal fetch/execute instructions. (One CP instruction is being fetched from Program Memory while the previous instruction is being executed.) This overlapping is accomplished automatically within the Array Processor, and is invisible to the programmer. When a jump instruction is being executed, the fetched instruction is cycled through, but not executed.

**NOTE:** The CP cannot modify its own Program Memory. Thus, once a program is loaded by the Host computer, it

Figure 2-10. Control Processor Simplified Block Diagram

remains unchanged. However, during execution of a program, register values and Data Memory counters can change, and may have to be reinitialized before restarting program execution.

#### 2.5.3 Register and Arithmetic & Logic Unit (RALU)

The RALU contains 16 registers, (R0 through R15) that are each 16 bits long. These are used to develop addresses of sources and destinations for the pipeline arithmetic operations. Note that the RALU registers are addressable with 4-bit words (16 register addresses), but that their contents become 16-bit addresses for the Data Memory locations ( $2^{16} = 64K$ , maximum memory size). Calling out the memory locations for sources and destinations of arithmetic data is accomplished by register-to-register manipulation within the Control Processor RALU. Repetition control for pipeline operations is also executed by the Control Processor, and is accomplished by manipulation of index computations along with conditional jump and skip instructions. Refer to Chapter 5 for the machine instructions used to perform the register-to-register manipulations.

The CP can also access locations in Data Memory as part of its Instruction set on a cycle-stealing basis. This added capability enables the CP to manage its own Data Memory allocation, and relieves the Host (and the application programmer) of much of that burden. Another feature of this capability allows the CP to complete the "odds and ends" of a calculation that are scalar in nature, and thus inefficient for the vector (array) processing of the Arithmetic Pipeline (PA). For example, the CP can use the leading zero count to change the block exponent before transferring data in normalized block floating point format.

The CP accesses locations in the Host via the I/O board, with minimum Host burden. The CP tells the I/O where a block of data can be found in the AP Data Memory, where it is going in the Host memory, and how many words to transfer as a block. The execution of this data transfer to the Host is accomplished by the logic and control residing in the I/O board (refer to paragraph 2.7). Once the instructions are passed to the I/O the CP proceeds to perform its continuing tasks. The I/O returns a "transfer completed" signal when it has performed as directed.

#### 2.5.4 Stack Operation.

Register R0 within the RALU is reserved as the STACK POINTER, and stack operations are accomplished by specific instructions. There are 64 words reserved for the stack. The CP automatically checks to see that a stack instruction is valid, and within the allowable range and location. The stack allows jumping to and from subroutines, interrupts, passing subroutine parameters, etc.

#### 2.5.5 Interrupts

Host-to-AP400 interrupts are handled within the registers of the Vector Interrupt Encoder. Eight levels of interrupt priority are provided. An interrupt mask allows the inhibiting of individual or sets of interrupts. Interrupt enable/disable operations are indirectly controlled by software, using machine instructions.

Design precautions have been incorporated so that interrupt servicing cannot occur at times during the execution of a program such that recovery would not be possible. Instructions of more than one cycle must be completed. For example, four pipeline instructions (comprising the PIPE and four-PAD set) cannot be interrupted.

Interrupts from the AP400 to the Host can be held off as a consequence of the Host setting a bit in a Status Register in the Interface board assembly. The Control Processor can cause an interrupt request to the Host only after this specific status bit is enabled.

Interrupts to the AP400 by inputs to the Auxiliary Interface input port are directed by the Status Register in the Interface board assembly. Interrupts from the AP400 to the Auxiliary Port are implemented by setting status bits that can be examined by the Host.

#### 2.6 DATA MEMORY (DM)

As shown in Figure 2-11, the Data Memory assembly interfaces with the other functional units of the AP400 via three buses (CCB, DB, and RALU), and via cable with Expansion Memory assemblies, if installed. The basic DM assembly provides 4096 contiguous words of memory on a single board, and space for an additional 4096 words on the same board. Expansion beyond the 8K available on one board is obtained by adding Expansion Memory boards, which are plugged into the main assembly backplane and cabled to the existing boards, as indicated in the illustration.

The DM board performs two primary functions:

- 1. It provides a buffer (CAB) between the pipeline commands (generated by the CP) and the pipeline execution control signals which control the pipeline proper. The former are developed in a quasi-random sequence, following the program instruction listing, while the latter are developed in a rigidly controlled timing sequence that synchronizes the pipeline setups with the read/write sequence from/to the data memory. (See Fig. 2-7.)

- 2. It accesses specified data memory addresses where the read/write operations are to be executed. The memory addresses are independently controlled for the Control Processor (CP-DMAR), the Interface (I/O-DMAR), and the Pipeline (PA-DMAR). These control signals (enabling the address registers as shown in Figure 2-11) are developed on a priority basis (PA lowest priority). The PA-DMAR defines the addresses for data sources and destinations in synchronism with PA operations. Thus, when the bus is usurped for other functions, the PA clock is stopped, stealing cycles from the PA operation for other data transfers to and from Data Memory.

As shown in the illustration, the Data Memory also includes the function of determining whether any of the addressed locations exceeds the maximum data memory. The maximum data memory size is determined, by the amount of Expansion Memory installed, and that number is translated into a wire-wrap jumper setting at the back plane (detailed in the Installation Manual). The Data Memory assembly compares the addressed location and transmits an error signal if the address exceeds the maximum memory.

Figure 2-11. Data Memory Simplified Block Diagram

The Command and Address data of 24 bits for the pipeline are received from the CP via the RALU bus (16 bits), as well as directly (8 bits). The 24 bits are latched into the CAB Input Register at the end of the clock cycle. They are then transferred into the CAB Buffer, which can hold up to 64 24-bit words. A complete pipeline instruction set consists of 4 such 24-bit words, so that the Buffer can hold up to 16 instructions for pipeline "passes".

The status of the CAB buffer is monitored during the program execution. When the buffer holds only 3 pipeline instructions, it is "empty". and the PA clock is stopped, preventing any further pipeline operation. The CP clock continues. When the CAB buffer contains 15½ pipeline instructions (62 24-bit words), it is considered "full", and prevents the transfer of any more instructions from the CP until it is emptied below the "full" threshold.

#### 2.7 INPUT/OUTPUT (I/O)

The Input/Output (I/O) card provides all the communications between the AP400 and the Host computer and between the AP400 and devices connected to the Auxiliary Port. A different I/O card is required for each Host computer with which the AP400 is specified to interface. Each card contains the circuitry to carry out the following I/O tasks:

- a. Direct the AP400 status: Halt/run,single step, etc.

- b. Transfer data to and from the Host under programmed I/O;

- c. Automatic DMA transfer of data to/from Host memory;

- d. Automatic Auxiliary Port transfer;

- e. Access various nodes of the Array Processor for diagnostic testing.

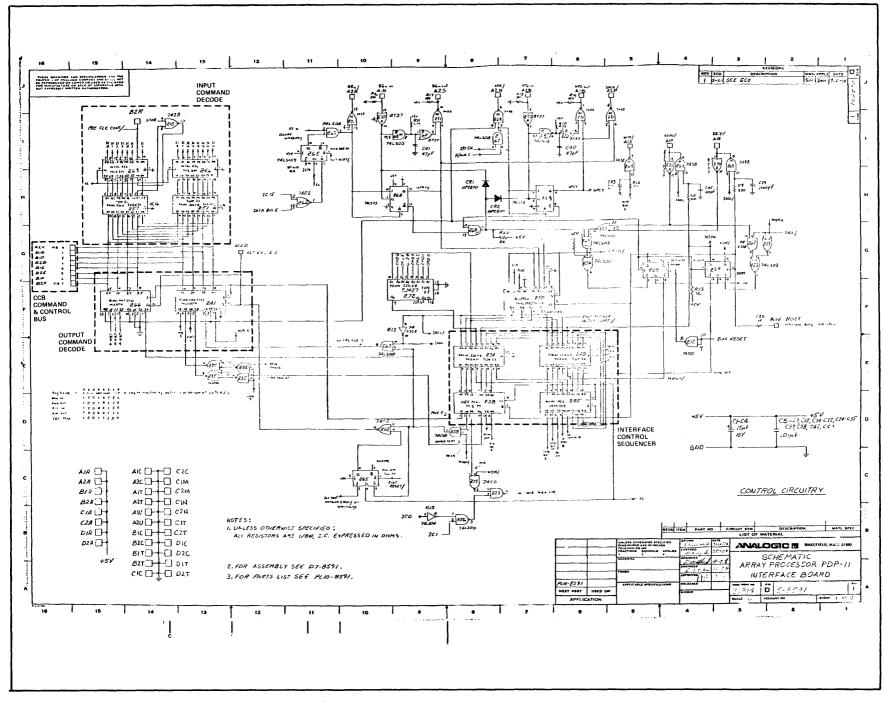

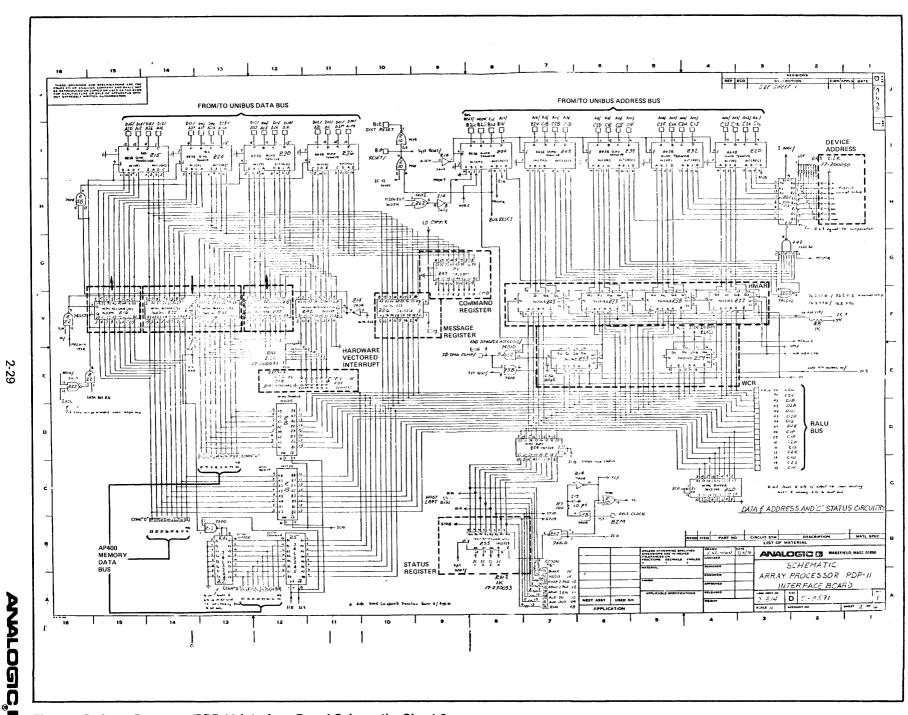

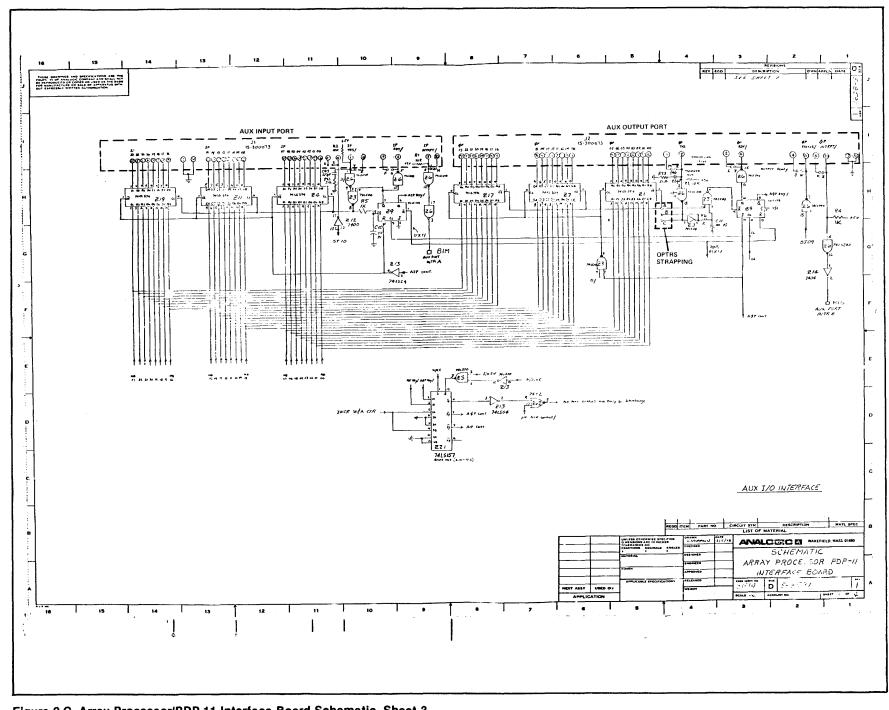

The sections that follow describe the circuitry for the I/O card used to interface the AP400 with a PDP11 computer via the Unibus, as well as the circuitry for using the Auxiliary Port. The Host dependent information will change for particular Host computers. Detailed descriptions of the I/O circuit operation, including detailed schematics, provide a complete description of the I/O capabilities of the AP400.

#### 2.7.1 I/O Block Diagram (PDP11 Interface).

Figure 2-12 is a simplified block diagram of the PDP11-AP400 interface. The titles in the blocks are fur-

ther defined in the complete schematic, reproduced at the end of this chapter as Figure 2-A, 2-B, and 2-C.

The AP400 requires two Host Memory addresses on the Unibus for data and commands, and one Host memory address for the Interrupt Vector.

The AP/Host Interface consists of bidirectional bus transceivers for the Address Bus, and the Data Bus. Incoming data is transferred to the internal memory bus via buffers. Outgoing data is latched from the internal bus in the data register.

Figure 2-12. Interface (I/O) Simplified Block Diagram

The Command Register stores the command the Host wishes the Interface to execute. The Message Register stores the message left for the Array Processor by the Host. All commands originating in the Host affect the Command and Message Registers.

A PROM-controlled Interface Control Sequencer generates all the timing controls required by the Unibus and the Array Processor interfaces.

The Auxiliary Input Port contains a holding register and interface control logic for handshaking. The Auxiliary Output Port also contains a holding register and handshaking logic. Each port has an interrupt line to the control processor.

The Host Memory Address Register (HMAR), and the Word/Control Register (WCR), are utilized in Direct Memory Access (DMA) operations. It should be noted that the Word/Control Register is also used in the operation of the Auxiliary Ports.

The internal interface between the I/O card and the Array Processor is carried out by the **Memory Bus**, **the RALU Bus**, **and the Command Bus**. The **Interface Control** uses the Command Bus to route data between the Host, the Data Memory, the Control Processor, and itself.

The status of the AP400 with respect to the communications across the interface is indicated on the AP400 front panel, as shown in Figure 2-13. The indicator lights on the panel indicate the SET/RESET conditions of eight of the 16 status bits in the STATUS/MESSAGE Register. The functions controlled by these bits are described below. (Bits 0 through 7 of the MESSAGE Register are not brought out to the front panel).

The Status Register is a "software handshake" register. Each bit is individually alterable by either the **Host or the AP400**, according to the appropriate protocol. For example, the Host may set the **Host-to-AP Interrupt** bit, but only the AP may clear it.

Both the Host and the AP may read the Status Register.

The functions controlled by th 8 status bits in the Status Register, as displayed on the AP400 front panel, are described below. The **set** condition is defined as a logic 1; the **reset** conditions as a logic 0.

#### Status Bit 8: AP RUN

When reset, this bit inhibits the clock in the Control Processor and in the Pipeline. Thus the Host can stop

Figure 2-13. AP400 Front Panel Showing Status Register Indicators

operation in the AP any time. The AP can use this bit to halt itself.

#### Status Bit 9: AUXILIARY OUT

This bit is used as a programmable output bit for the Auxiliary Output Port. It is not used internally in the Array Processor. It is also available to the Auxiliary Input Port.

#### Status Bit 10: AUXILIARY IN

This bit is used as a programmable output bit for the Auxiliary Input Port. It is not used internally in the Array Processor. It is also available to the Auxiliary Output Port.

#### Status Bit 11: INTERRUPT ENABLE

When set, this bit allows the AP to Interrupt the Host.

#### Status Bit 12: AP-TO-HOST INTERRUPT PENDING

When set, and when Status Bit 11 is set, the **INTR REQ** is set on the rise of Status Bit 12. Bit 12 is normally set by the Array Processor, and reset by the Host.

#### Status Bit 13: HOST-TO-AP INTERRUPT PENDING

This bit generates an interrupt in the Control Processor. It is normally set by the Host, and reset by the Control Processor.

#### Status Bit 14: HI/LO

When set, this bit points to the high 16 bits of Data Memory or the high 11 bits of Program Memory. When reset, it points to the low 8 eight bits of Data Memory or the low 11 bits of Program Memory.

#### Status Bit 15: (Not Assigned)

This bit may be assigned any function by the user.

#### 2.7.2 Host/AP Communications.

There are three modes of communications between the Host and the AP:

- a. **Programmed I/O:** Wherein each transfer requires the execution of an I/O instruction in the Host.

- b. **Direct Memory Access:** Wherein data is transferred to/from the Host Memory (or any other addressed device) in bursts of up to 16 words.

- c. Interrupt: Wherein the AP generates a Host processor interrupt and transfers an Interrupt Vector.

#### 2.7.3 Programmed I/O.

In PROGRAMMED I/O, the PDP Unibus protocol requires that the Host be the "bus master" and the AP be the "bus slave". The Host issues an I/O transfer to one of two sequential device addresses that are decoded by the AP. The low address is the AP Command Address, while the high address is the AP Data Address. When using the Command Address, the Host "writes" to the Command Register and to the Message Register, and "reads" from the Message Register and the Status Register. When using the Data Address, the Host transfers data to/from the AP, as part of the standard Unibus protocol.

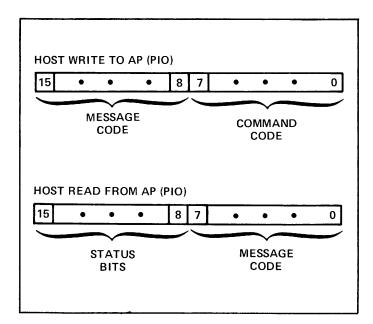

Figure 2-14 illustrates the word format and bit assignment of the Command & Message Register for the PIO transfers in the read and write operations.

There are two types of commands:

- a. Immediate: Wherein the data word that is transferred is interpreted and the command involved is executed during the actual transfer time.

- b. **Data or Non-Immediate:** Wherein the transferred command is stored and will be used to route the data that will be transferred with a Data Address.

Table 2-4 contains a listing of some of the commands that can be transferred.

Figure 2-14. Command & Memory Register Word Format

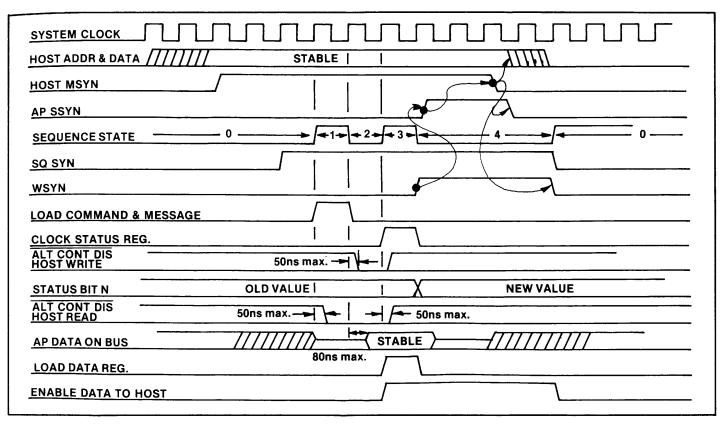

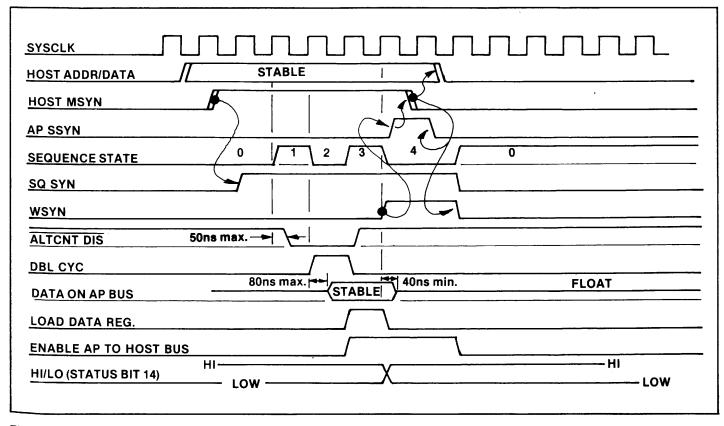

The **Transfer Sequence** begins when the Host places one of the AP addresses on the bus and asserts **MSYN**. The interface decodes this address and responds by setting **SQ SYN**. This latter action stores a set of three bits and starts the conrol sequencer. The stored bits define the following:

- a. Transfer initiated by the Host

- b. Read or write; determined by a control bit (C1) on the Unibus

- c. Upper or lower of the two AP400 addresses; determined by the LSB of the address.

The sequencer then generates control signals that accomplish the following:

- a. Assert SSYN and negate SSYN after the Host negates MSYN. Performed by setting and clearing WSYN.

- b. Enable and clock buffer gates and registers to implement the logic in the execution of the command.