# 82C605/82C606 CHIPSpak/CHIPSport MULTIFUNCTION CONTROLLERS

- 100% Compatible to IBM™ PC, XT and AT

- Fully compatible to the NS16450 Asynchronous Communications Element, and the Motorola™ 146818A Real Time Clock (82C606 only)

- Provides a parallel interface which can be configured for use with either a printer or a scanner

- Provides two UART channels which can be powered from external sources

The 82C606 CHIPSpak Multifunction Controller incorporates two UARTs, one parallel port, one game port decoder and one Real Time Clock. The UARTs are fully compatible to the NS16450 and the Real Time Clock is fully compatible with the Motorola 146818A. The 82C606 thus offers a single chip implementation of the most commonly used IBM PC, XT or AT peripherals. While offering complete compatibility with the IBM architecture, the chip offers enhanced features. These include support for power derived from three sources (main, auxiliary and standby), an additional 64 bytes of user RAM for the Real Time Clock and a software configuration scheme which

- Support for a game port

- Provides a Real Time Clock with 100 year calendar (82C606 only)

- CMOS Configuration RAM with Battery Backup support permits software selection of internal register base addresses (82C606 only)

- **■** 114 bytes of CMOS RAM

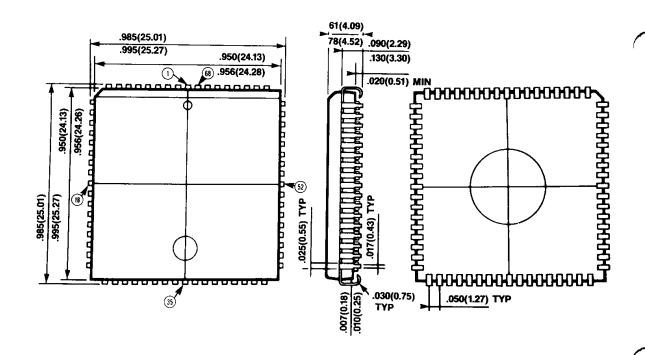

- Single chip 68-pin CMOS implementation

permits development of a system configuration program.

The CHIPSpak Multifunction Controller can be used on the system board to provide serial and parallel ports or on a multifunction card to create a low cost, high density peripheral for use with general purpose microcomputer systems.

The 82C605 CHIPSport is a functional sub-set of 82C606 CHIPSpak. The two products are identical, with the exception of the Real Time Clock. The 82C605 does not integrate the Real Time Clock. All references to 82C606

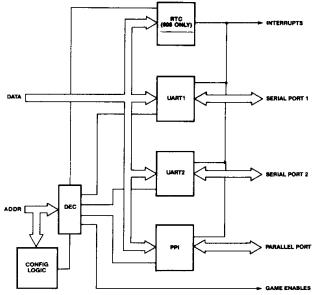

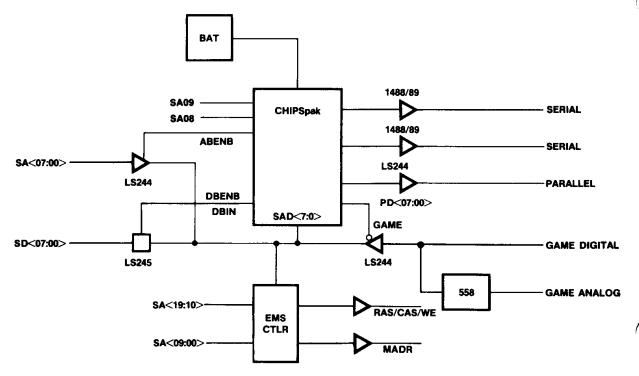

Figure 1. 82C605/606 CHIPSpak/CHIPSport Multifunction Controller Block Diagram

CHIPSpak in this data book are applicable to 82C605 CHIPSport, except where stated otherwise.

The 82C605/82C606 are implemented using advanced CMOS technology and are packaged in 68-pin PLCC packages.

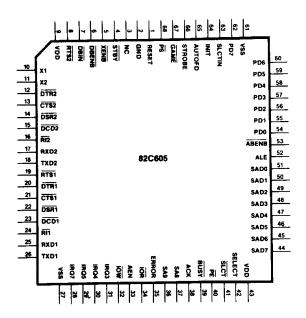

Figure 2a. 82C605 CHIPSport Multifunction Controller Pinout Diagram

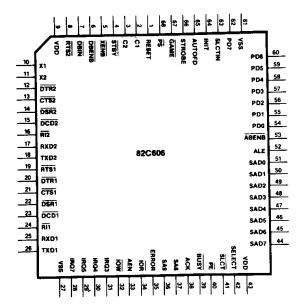

Figure 2b. 82C606 CHIPSpak Multifunction Controller Pinout Diagram

| Pin No.   | Type<br>(Note 1) | Symbol                      | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clocks an | d Control        |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

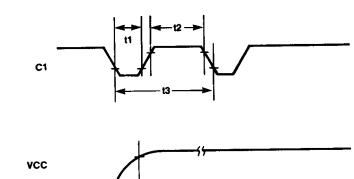

| 2         |                  | C1 (82C606)<br>GND (82C605) | 32.768KHz Real Time Clock (RTC) crystal or oscillator input. The signal level should be CMOS compatible. This pin should be connected to ground for 82C605.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3         | 0                | C2 (82C606)<br>NC (82C605)  | 32.768KHz RTC output to crystal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4         | 1                | STBY                        | ACTIVE LOW. Standby Mode. This signal should be activated when the main power supply is removed. It indicates that the bus interface is invalid and that no response should be made to any bus signals. STBY immediately terminates any bus operations in progress. If the CHIPSpak is resident on a system board, STBY should be connected to POWERGOOD. If the CHIPSpak is on an add-in card, STBY should be generated from the RESETDRV signal.                                                                                                                                                                                                 |

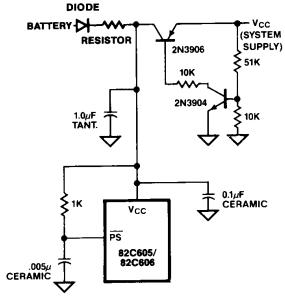

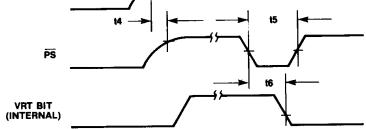

| 68        | I                | PS                          | ACTIVE LOW. Power Sense. A Schmitt trigger input that should be connected to an RC network which delays the rising edge of power (+5V supply). This signal resets the VRT bit in Register D of the RTC and the Valid Configuration bit of the Configuration Enable Register. It also disables the decode logic for the CHIPSpak which then awaits configuration by the setup software. This signal input must be provided to ensure proper operation of 82C606. When PS is asserted the configuration registers are forced to their default values When battery back-up operation is not desired, PS should be connected to inverted RESET signal. |

| 42        | l                | SELECT                      | ACTIVE HIGH. Unit Select. This pin should be connected to any one of SAD<07:04>. It is used to identify a particular CHIPSpak in a system having more than one CHIPSpak. Failure to connect it properly could result in inability to configure the chip. Unit 0 should connect to SAD<04>, unit 1 to SAD<05>, etc.                                                                                                                                                                                                                                                                                                                                 |

| PC Bus In | terface          |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

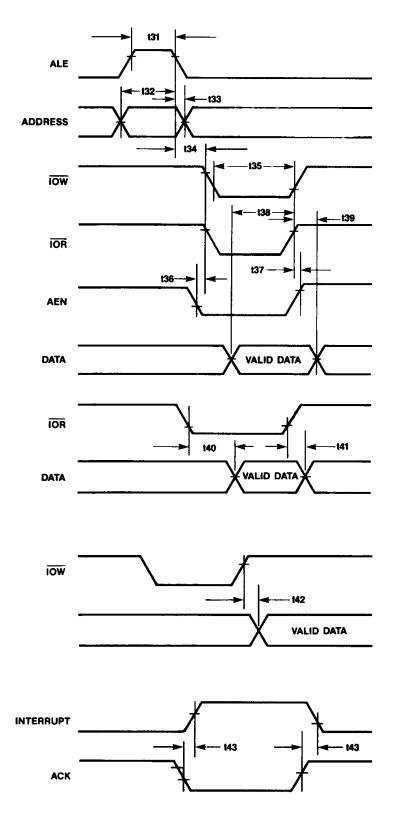

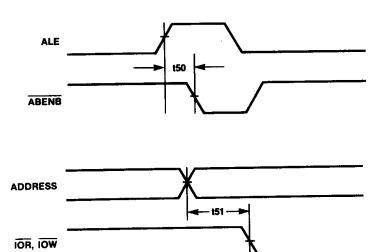

| 52        | l                | ALE                         | ACTIVE HIGH. Address Latch Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 33        | 1                | AEN                         | ACTIVE HIGH. Address ENable. Used to gate IOR and IOW. When AEN is low, IOR and IOW are enabled for the CHIPSpak                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 34        | 1                | IOR                         | ACTIVE LOW. IO Read strobe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 32        | 1                | ĪOW                         | ACTIVE LOW. IO Write strobe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |                  |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

(Continued)

| Pin No.     | Type (Note 1) | Symbol     | Pin Description                                                                                                                                                                                                                                                                                                                                                           |  |

|-------------|---------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 53          | 0             | ABENB      | ACTIVE LOW. Address Buffer/Mux ENable. Used to enable a buffer which separates the CHIPSpak SAD<07:00> pins from the system address lines in a system not using multiplexed Address/Data lines.                                                                                                                                                                           |  |

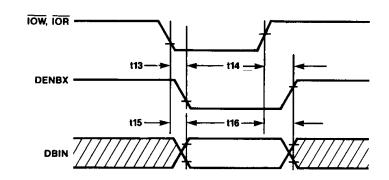

| 6           | 0             | DBENB      | ACTIVE LOW. Data Bus Driver ENable. Used to enable an LS245 type buffer which separates the system Address/Data lines (for multiplexed Address/Data) or system Data lines (non-multiplexed) from the CHIPSpak SAD<07:00>. CHIPSpak pin DBIN controls the direction of this buffer.                                                                                        |  |

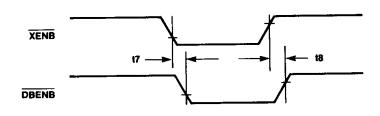

| 5           | ı             | XENB       | ACTIVE LOW. External Data Bus ENable. This input is internally ORed with the signal used to generate the DBENB output. This allows another controller sharing the board to use the same PC data bus driver without need for an external OR gate. Typically this signal would be created by an EMS or other memory controller. This pin should be tied high when not used. |  |

| 7           | Т             | DBIN       | ACTIVE LOW. Data Bus Driver Direction. Used to control the direction of an LS245 type buffer separating the SAD<07:00> lines from the system Data bus. High when IOW is asserted and low when IOR is asserted if a CHIPSpak function has been selected. In high impedance state at all other times to allow other logic to control the Data bus buffer.                   |  |

| 36,37       | <u> </u>      | SA<09:08>  | Two high order bits of the Address Bus.                                                                                                                                                                                                                                                                                                                                   |  |

| 51-44       | В             | SAD<07:00> | Multiplexed Address/Data Bus.                                                                                                                                                                                                                                                                                                                                             |  |

| 31          | T             | IRQ3       | ACTIVE HIGH. Interrupt Request 3. By IBM PC AT and IBM PC XT convention it is used for UART2 (COM2).                                                                                                                                                                                                                                                                      |  |

| 30          | Т             | IRQ4       | ACTIVE HIGH. Interrupt Request 4. By IBM PC AT and IBM PC XT convention it is used for UART1 (COM1).                                                                                                                                                                                                                                                                      |  |

| 29          | Т             | IRQ5       | ACTIVE HIGH. Interrupt Request 5. By IBM PC AT convention it is used for parallel port 2.                                                                                                                                                                                                                                                                                 |  |

| 28          | Т             | IRQ7       | ACTIVE HIGH. Interrupt Request 7. By IBM PC AT and IBM PC XT convention it is used for parallel port 1.                                                                                                                                                                                                                                                                   |  |

| 1           | 1             | RESET      | ACTIVE HIGH. Reset input.                                                                                                                                                                                                                                                                                                                                                 |  |

| Serial Inte | erface        |            |                                                                                                                                                                                                                                                                                                                                                                           |  |

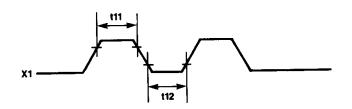

| 10          | 1             | X1         | Input pin for the clock or crystal used by the UARTs The signal level should be CMOS compatible.                                                                                                                                                                                                                                                                          |  |

| 11          | 0             | X2         | Output pin for the clock or crystal used by the UARTs.                                                                                                                                                                                                                                                                                                                    |  |

(Continued)

| Pin No. | Type<br>(Note 1) | Symbol     | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

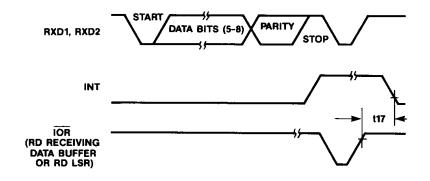

| 17      | l                | RXD2       | Input pin for serial data stream to UART2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 25      | 1                | RXD1       | Input pin for serial data stream to UART1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

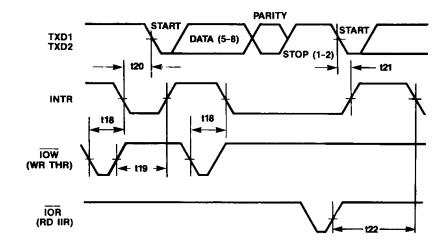

| 18      | 0                | TXD2       | Output pin for serial data stream from UART2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 26      | 0                | TXD1       | Output pin for serial data stream from UART1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

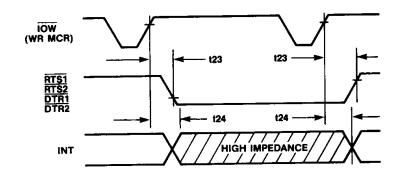

| 8,19    | 0                | RTS2, RTS1 | ACTIVE LOW. Request To Send. Handshake signals which notify a MODEM or data set that UART2 or UART1 (respectively) is ready to transmit data. This output can be changed by writing to bit 1 of the appropriate MODEM Control Register. High (inactive) after a hardware RESET is performed. Forced high (inactive) during loop mode operation.                                                                                                                                                                                                              |

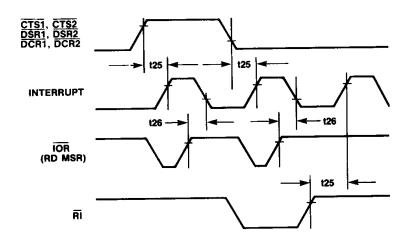

| 13,21   | 1                | CTS2, CTS1 | ACTIVE LOW. Clear To Send. Handshake signals which notify UART2 or UART1 (respectively) that a MODEM is ready to receive data. The CPU can access this signal by reading bit 4 of the MODEM Status Register (MSR) of the appropriate UART. Bit 0 of the MSR flags a change of state in the corresponding CTS signal since the last read of the MSR. This signal does not affect the UART transmitter. A change in state of bit 4 of the MSR (CTS) will will cause the CPU to be interrupted if bit 3 (MODEM Status) of the Interrupt Enable Register is set. |

| 14,22   | 1                | DSR2, DSR1 | ACTIVE LOW. Data Set Ready. Handshake signals for UART2 and UART1 respectively. Tells the CPU that the MODEM or data set is ready to transfer characters. Can be monitored by reading bit 5 of the appropriate MODEM Status Register (MSR). A change in the state of this bit since the last read of the MSR will cause bit 1 of the MSR to go high. An interrupt will be generated when bit 5 of the MSR changes state if MODEM Status interrupts are enabled (bit 3 of the Interrupt Enable Register).                                                     |

| 12,20   | 0                | DTR2, DTR1 | ACTIVE LOW. Data Terminal Ready. Notifies the MODEM or data set that UART2 or UART1 (respectively) is ready to transfer characters. Can be activated by writing a 1 to bit 0 of the MODEM Control Register. Forced high (inactive) during loop mode operation.                                                                                                                                                                                                                                                                                               |

(Continued)

| Pin No.     | Type<br>(Note 1) | Symbol     | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15,23       | 1                | DCD2, DCD1 | ACTIVE LOW. Data Carrier Detect. Notifies UART2 or UART1 (respectively) that a carrier signal has been detected by a MODEM. The CPU can monitor the value of this bit by reading bit 7 of the MODEM Status Register (MSR). A change in the state of this signal since the last read of the MSR will cause bit 3 of the MSR to go high. This signal has no affect on the UART receiver. An interrupt will be generated when bit 7 of the MSR (DCD) changes state if MODEM Status interrupts are enabled (bit 3 of the Interrupt Enable Register). |

| 16,24       | ı                | RI2, RI1   | ACTIVE LOW. Ring Indicator. Notifies UART2 or UART1 (respectively) that a telephone ringing signal has been detected by a MODEM or data set. Can be monitored by the CPU by reading bit 6 of the MODEM Status Register (MSR). When this signal goes to an inactive state (from low to high), bit 2 of the MSR will be set. If MODEM Status interrupts are enabled, activation of this signal (high to low transition) will generate an interrupt.                                                                                                |

| Parallel In | terface          |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 62,60-54    | В                | PD0-PD7    | Parallel Port Data Bus. Printer: output only. Scanner: bidirectional.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 38          | I                | ACK        | ACTIVE HIGH, Acknowledge. Printer: handshake signal indicating that data has been received. Scanner: handshake signal indicating that data has been received.                                                                                                                                                                                                                                                                                                                                                                                    |

| 39          | ı                | BUSY       | ACTIVE LOW, Busy signal.  Printer: it indicates that printer is unable to receive data.  Scanner: in print mode (PR/SC is high), it indicates that scanner is unable to receive data.                                                                                                                                                                                                                                                                                                                                                            |

| 40          | I                | PE         | ACTIVE LOW, Paper End signal. Printer: end of paper has been detected. Scanner: used as FAULT status indicator.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 41          | I                | SLCT       | ACTIVE LOW, Select. Printer: indicates printer is selected. Scanner: indicates ready for another character.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

(Continued)

| Pin No.   | Type<br>(Note 1) | Symbol | Pin Description                                                                                                                                                                                                                                                           |  |

|-----------|------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 35        | I/O              | ERROR  | ACTIVE HIGH, Error.  Printer: when HIGH indicates an error has occured.  Scanner: busy signal from host, unable to receive.                                                                                                                                               |  |

| 66        | 0                | STROBE | ACTIVE HIGH. Strobe. Printer: data strobe. Scanner: data strobe.                                                                                                                                                                                                          |  |

| 63        | 0                | SLCTIN | ACTIVE HIGH. Select In. Printer: to select printer. Scanner: to select scanner and enable data buffer.                                                                                                                                                                    |  |

| 64        | 0                | INIT   | ACTIVE HIGH. Initialize. Printer: Initialize. Scanner: reset.                                                                                                                                                                                                             |  |

| 65        | 0                | AUTOFD | ACTIVE HIGH. Auto Feed. Printer: causes printer to generate a line feed after each line is printed. Scanner: Print/Scan (PR/SC*), data buffer directional control signal.                                                                                                 |  |

| Game Por  | 1                |        |                                                                                                                                                                                                                                                                           |  |

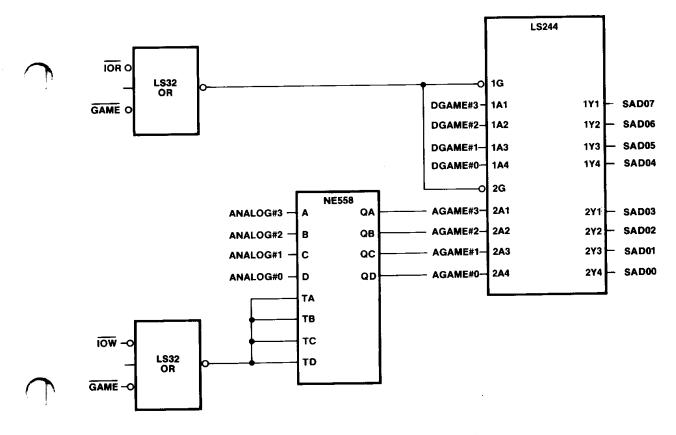

| 67        | 0                | GAME   | ACTIVE LOW. Game Port Enable. Active when the specified I/O address is valid and AEN is low. This signal must be externally gated with IOR and IOW to ensure proper access to a game peripheral. It can also be used as a programmable decoder for any peripheral device. |  |

| Power and | d Ground         |        |                                                                                                                                                                                                                                                                           |  |

| 9,43      |                  | VDD    | Power Supply                                                                                                                                                                                                                                                              |  |

| 27,61     |                  | VSS    | Ground                                                                                                                                                                                                                                                                    |  |

|           |                  |        |                                                                                                                                                                                                                                                                           |  |

**NOTE 1:** The abbreviations used in the column labeled 'Type' are as follows:  $\underline{I} = Input$

T = 3-state output

O = Output (always active)

D = Output (open drain)

I/O = Input and Output (depends on CHIPSpak mode)

B = Bidirectional

# CHIPSport/CHIPSpak MULTIFUNCTION CONTROLLERS

The 82C606 is an LSI implementation of the most commonly used peripheral devices found in an IBM PC, XT or AT. The device contains the equivalent of two NS16450 UARTs, one Motorola 146818A Real Time Clock and one parallel port. Decoding logic and one output suitable for use with a game port, support for main, auxiliary and standby power supplies and software configurable base addresses for these devices, operational modes and interrupts are also included. Figure 1 depicts the subsystems present in the 82C606. The CHIPSport 82C605 contains all functions except the Real Time Clock.

Each of the two UARTs implements a fully functioned serial link. Programmable character length, parity generation and detection, stop-bit generation and baud rate generation are provided. Double buffering is used so that precise synchronization is unnecessary. Status information is accessible to the CPU by reading internal registers. MODEM control lines are provided, as are internal diagnostic functionality and interrupt prioritization. Support for an auxiliary power system (such as that derived from a telephone line or RS232 link) permits a CHIPSpak in a battery-powered device to consume no battery power until an incoming character is detected.

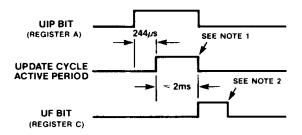

# A Real Time Clock (RTC) is included in the 82C606 only for maintaining the time and date.

This subsystem contains 114 bytes of RAM in addition to the Clock/Calendar. The date/time data and the additional RAM contents can be maintained without system power by using an external circuit to connect the device to a battery when system power is removed.

The parallel port can be configured for output only (printer application) or input and output (scanner application). The necessary control signals are provided for use as a Centronics-compatible (output only) parallel port. For scanner applications, a Centronics-like interface is used. Such an interface is utilized by the RICOH IS30 scanner.

The game port circuitry provides a decoded output for use by any peripheral. The base address of this peripheral is software programmable.

The configuration RAM and circuitry support programmable base addresses for all registers internal to the CHIPSpak. This permits creation of a menu-driven program for system configuration. It also permits integration of multiple CHIPSpaks in a single system, or one or more CHIPSpaks with other devices which provide overlapping functionality (for instance serial and parallel ports). Selection of sources for interrupts, enabling and configuring of on-chip subsystems (UARTs, parallel port, etc.) and control of the configuration process itself are also handled with this RAM and its associated circuitry.

The remainder of this data sheet will consider each of the aforesaid subsystems individually. Sections containing more general design data for the chip as a whole are at the end along with electrical and physical characteristics.

### **UARTS**

The equivalent of two NS16450 UARTs is implemented on the 82C606. Since the two UARTs are identical, only one is described below. An on-chip baud rate generator divides the input clock or crystal frequency by a number from 1 to 65535. This frequency is used for both receiving and transmitting serial data. An external clock or a crystal can be used.

Serial-to-parallel conversion is performed on received data and parallel-to-serial conversion is performed on transmitted data. Status of either or both the UARTs is available at any time. To access it, the CPU reads the appropriate status register in the CHIPSpak. The current state and type of a transfer are contained in this status information as are details regarding any errors encountered. The conditions under which the processor will be interrupted and the interrupt line to be used are programmable.

Control lines are provided to permit interfacing to a MODEM. Internal diagnostics are supported. These permit simulation of break, parity, overun and framing error conditions as well as operation in loopback mode.

### Using Standby or Auxiliary Power Sources

Support for use of a Standby (battery) or Auxiliary (derived from a telephone line or RS232 link) power supply is provided by the 82C606. An external circuit must be used to alter the source of current to the VDD pins.

The UART can be made to wake up the CPU upon receipt of a character. This is useful in certain applications (such as battery powered transportable computers) where power consumption must be minimized. To implement this, an Auxiliary or Standby power source must be provided. In addition, an interrupt must be generated upon receipt of a character. This interrupt initiates a power up sequence which culminates in the servicing of the interrupt. In order for this to work properly, the CHIPSpak RESET function must be pro-

grammed so that it will not alter the values of the UART control registers (see below).

Note that since the baud rate generator dissipates more power than many of the other CHIPSpak circuits, use of a battery for Standby power may prove to be infeasible. If this is the case, reducing another power source to the +5V needed by the CHIPSpak may be the solution. The 55 to 110 volts from a telephone line or the +9 to +12 volts from an RS232 link are two possible sources for input voltages.

### **Accessible Registers**

Addressing of the accessible UART registers is shown in the table below. The base address of all registers is software programmable during the configuration sequence (see the section entitled "Configuration Sequence".) UART registers are located at sequentially increasing addresses above this base address. A CHIPSpak contains two UARTs, each of which contains one set of the registers described below.

Table 1 Addressing of UART Registers

| DRAB | SAD2 | SAD1 | SADO | Register Name           |  |

|------|------|------|------|-------------------------|--|

| 0    | 0    | 0    | 0    | Receive Buffer (read)   |  |

| Ö    | Ō    | Ö    | 0    | Transmit Buffer (write) |  |

| ō    | Ō    | 0    | 1    | Interrupt Enable        |  |

| x    | 0    | 1    | 0    | Interrupt Flag (read)   |  |

| X    | Ō    | 1    | 1    | Byte Format             |  |

| x    | 1    | 0    | 0    | MODEM Control           |  |

| x    | 1    | 0    | 1    | Line Status             |  |

| x    | 1    | 1    | 0    | MODEM Status            |  |

| x    | 1    | 1    | 1    | Scratchpad              |  |

| 1    | 0    | 0    | 0    | Divisor LSB             |  |

| 1    | Ō    | 0    | 1    | Divisor MSB             |  |

Where:

X = Don't Care

MSB = Most Significant byte

LSB = Least Significant byte

DRAB = Divisor Register Address Bit

# BIT DEFINITIONS OF ACCESSIBLE REGISTERS

### Receive Buffer (RB)

This register holds the incoming data byte. Bit 0 is the least significant bit, which is transmitted and received first. Double buffering is supported by the CHIPSpak. This scheme uses an additional shift register (the Receive Shift Register; not user accessible) to assemble the incoming byte before it is loaded into the Receive Buffer.

### Transmit Buffer (TB)

This register holds the data byte to be sent. Bit 0 is the least significant bit, which is transmitted and received first. Double buffering is supported by the CHIPSpak. This scheme uses a shift register (the Transmit Shift Register; not user accessible) which is loaded from the Transmit Buffer. The transmitted byte is then shifted out of the Transmit Shift Register to the TXD pin.

#### Interrupt Enable Register (IER)

The low order 4 bits of this register control the enabling of each of the four possible types of interrupts. Setting a bit to a logic 1 enables the corresponding interrupt. It is possible to enable all, none or some of the interrupt sources. Disabling all interrupts means that the Interrupt Flag register content is not valid and that none of the interrupt signals output by CHIPSpak can be triggered by a UART. All other portions of the UART are unaffected by the disabling of interrupts. The individual bit definitions are as follows:

Bit 0: A logic 1 here causes an interrupt when the Receive Buffer contains valid data.

Bit 1: A logic 1 here causes an interrupt when the Transmit Buffer is empty.

Bit 2: A logic 1 here causes an interrupt when an error (Overun, Parity, Framing or Break) has been encountered. The Line Status register must be read to determine the type of error.

Bit 3: A logic 1 here causes an interrupt when one of the bits in the MODEM Status register changes state.

Bits 4-7: These four bits are set to 0.

### Interrupt Flag Register (IFR)

When accessed, this register reports the highest pending interrupt. By reading it, the CPU can determine the source of the interrupt and can act accordingly. The Interrupt Flag register (IFR) records the highest pending interrupt in bits 0 through 2. Other interrupts are temporarily disregarded (they are internally saved by the CHIPSpak) until the highest priority one is serviced.

Four levels of prioritized interrupts exist. In descending order of priority they are:

- 1. Line Status (highest priority)

- 2. Receive Buffer full

- 3. Transmit Buffer empty

- 4. MODEM Status (lowest priority)

Bit definitions for the IFR are as follows:

Bit 0: If this bit is a zero, an interrupt is pending and bits 1 and 2 can be read to determine the source of the interrupt. When this bit is a logic 1, no interrupts are pending. Note that this bit can be used in a polled environment to determine if an interrupt is pending. It can also be used for the same purpose with a hardwired interrupt priority scheme. In the latter case, bits 1 and 2 of this register act as a pointer to an interrupt service routine.

Bits 1 and 2: As indicated in the table below, these two bits specify the type and source of the interrupt.

Bits 3-7: These five bits are set to 0.

Table 2 UART Interrupt Specifications

| Bit 2 | Bit 1 | Bit 0 | Priority | Туре                     | Source                                                                          | The<br>Interrupt                     |

|-------|-------|-------|----------|--------------------------|---------------------------------------------------------------------------------|--------------------------------------|

| 0     | 0     | 1     | _        | None                     | None                                                                            | _                                    |

| 1     | 1     | 0     | Highest  | Line Status              | Overun Error or<br>Parity Error or<br>Framing Error<br>or Break<br>Interrupt    | Read Line<br>Status<br>Register      |

| 1     | 0     | 0     | Second   | Receive<br>Buffer Full   | Received Data                                                                   | Rd Receive<br>Buffer                 |

| 0     | 1     | 0     | Third    | Transmit<br>Buffer empty | Transmit Buffer                                                                 | Read IFR or<br>Wr Transmit<br>Buffer |

| 0     | 0     | 0     | Fourth   | MODEM<br>Status          | Clear to Send<br>or Data Set<br>Ready or Ring<br>Indicator or<br>Carrier Detect | Read<br>MODEM<br>Status<br>Register  |

# Byte Format Register (BFR)

This read/write register contains format information for the serial line. Since it can be read, a separate copy of its content need not be kept in system memory. Bit definitions are as follows:

Bits 0 and 1: These specify the word length for received and transmitted characters. Start, stop and parity bits are not included in the word length value. The word lengths are:

| Bit 0 | Bit 1 | Word Length |

|-------|-------|-------------|

| 0     | 0     | 5 Bits      |

| 0     | 1     | 6 Bits      |

| 1     | 0     | 7 Bits      |

| 1     | 1     | 8 Bits      |

Bit 2: The combination of this bit and Bits 0 and 1 of this register determine the number of stop bits used with each transmitted character. The table below summarizes this information. Note that the receiver will ignore additional stop bits beyond the first regardless

of the number of stop bits used when transmitting.

| Bit 2 | Word Length  | # of<br>Stop Bits |

|-------|--------------|-------------------|

| 0     | <del>_</del> | 1                 |

| 1     | 5 Bits       | 11/2              |

| 1     | 6 Bits       | 2                 |

| 1     | 7 Bits       | 2                 |

| 1     | 8 Bits       | 2                 |

Bit 3: A logic 1 in this bit enables parity generation (during transmission) and checking (during receipt). The parity bit is always after the last data bit but before the first stop bit. If enabled, a parity bit of the proper state (0 or 1) is generated such that the sum (carry ignored) of all data bits plus the parity bit produces either an even (even parity) or odd (odd parity) value.

Bit 4: This Even Parity bit controls parity sense. It is ignored unless Bit 3 is a logic 1. If

Bits 3 and 4 are logic 1's (even parity), an even number of logic 1's will be transmitted and a parity error will be generated each time an odd number is received. If Bit 3 is a 1 and Bit 4 is a 0 (odd parity), an odd number of logic 1's will be transmitted and a parity error will be generated each time an even number is received.

Bit 5: This is the Force Parity bit. It ensures that the parity bit and sense (even or odd) match regardless of the sum normally used to determine parity. Thus if Bits 3, 4 and 5 are all logic 1's (even parity), the parity bit transmitted will always be a 0 and a parity error will be generated if a logic 1 parity bit is received. If Bits 3 and 5 are 1 and Bit 4 is 0, the parity bit transmitted will always be a 1 and a parity error will be generated if a 0 parity bit is received.

Bit 6: This BREAK bit, when set to a logic 1, forces the transmitted data output pin (TXD2 or TXD1) to a Spacing or logic 0 condition. This BREAK condition is terminated when Bit 6 is set to a 0. The operation of the transmitter logic is unaffected by the value of this bit; only the value of the corresponding TXD pin is affected. A BREAK condition is typically used to signal a terminal or communications system. To prevent the transmission of erroneous data, follow the steps below:

- Load a NULL character (all zeroes) into the Transmit Buffer.

- 2. Load Bit 6 (BREAK bit) after the next Transmit Buffer Empty (TBE) occurs.

- Time the length of the BREAK condition by continuing to load NULL characters into the Transmit Buffer and counting the number loaded.

- Clear the BREAK condition only after a Transmitter Empty (TEMT) condition occurs.

Bit 7: This Divisor Register Address Bit (DRAB) must be a logic 1 to permit access to the Divisor Registers. Access to all other internal UART registers requires that this bit be 0.

### **Modem Control Register (MCR)**

This byte-wide register is used to manage the connection to an external MODEM or data set. Bit definitions are as follows:

Bit 0: This DTR bit determines the state of the corresponding DTR output pin (DTR2 or DTR1). Setting Bit 0 to a logic 1 forces DTR to its active state (logic 0). If Bit 0 is a logic 0, DTR will be inactive (logic 1). An external inverting buffer is typically used (to insure the proper polarity of DTR) when connecting a CHIPSpak DTR output to a MODEM or data set.

Bit 1: This RTS bit determines the state of the corresponding RTS CHIPSpak output pin in a fashion identical to Bit 0 (see above).

Bit 2: This bit is internally connected to bit 6 (RI) of the MODEM Status Register (MSR) in diagnostic loopback mode (MCR bit 4 is a logic 1). A 1 in this bit will force the RI bit (bit 6 of the MSR) to be active (logic 0) when the CHIPSpak UART is in diagnostic loopback mode. A 0 will force the RI bit to be inactive.

Bit 3: This bit is internally connected to bit 7 (DCD) of the MODEM Status Register (MSR) in diagnostic loopback mode (MCR bit 4 is a logic 1). A 1 in this bit will force the DCD bit (bit 7 of the MSR) to be active (logic 0) when the CHIPSpak UART is in diagnostic loopback mode. A 0 will force the DCD bit to be inactive, and a 1 enables UART interrupts.

In the normal mode (no loopback), this bit is OUT2. When OUT2 = 0 (default), the corresponding interrupt is forced into a high impedance. When OUT2 = 1, the interrupt output is enabled.

Bit 4: This Loopback bit is used for self-diagnostic purposes. If it is a logic 1:

The corresponding TXD CHIPSpak output pin (TXD2 or TXD1) is set to a logic 1 (Marking state) and is disconnected from the output of the Transmit Shift Register;

# CHIP5

- The corresponding RXD CHIPSpak input pin (RXD2 or RXD1) is disconnected from the Receive Shift Register;

- The input to the Receiver Shift Register is internally connected to the output of the Transmit Shift Register;

- All MODEM control input pins (CTS, DSR, DCD, and RI) are disconnected from the internal circuitry;

- MODEM control output pins DTR and RTS are forced to their inactive state (logic 1);

- MODEM control output DTR is connected internally to MODEM control input DSR MODEM control output RTS is internally connected to input CTS. MODEM Control Register (MCR) bit 2 determines the state of bit 6 of the MODEM Status Register (MSR). Bit 3 of the MCR controls bit 7 of the MSR.

- 7. Data which is transmitted will immediately be received, permitting the CPU to verify the data paths internal to the CHIPSpak and its connection to the CPU.

While operating in diagnostic loopback mode, interrupts are disabled. Interrupts are controlled by the Interrupt Enable register. Interrupts which are due to MODEM signals operate as documented, although the source is now the lower 4 bits of the MODEM Control Register rather than the MODEM input pin signals.

Bits 5, 6 and 7: These bits are set to 0.

# Line Status Register (LSR)

This byte-wide register supplies serial link status information to the CPU. A Receive Line Status interrupt is caused by one of the conditions flagged by Bits 1 through 4 of this register. It is read-only. Writes to it are used at the factory for testing purposes and are not recommended. Bit definitions are as follows:

Bit 0: This Receive Buffer Full (RBF) bit is set

to a logic 1 when an incoming character has been transferred from the Receive Shift Register to the Receive Buffer. Reading the Receive Buffer resets it to a logic 0.

Bit 1: This Overun Error bit is set to a logic 1 when a new character is transferred into the Receive Buffer before the previously received character was read by the CPU. The previously received character is lost. When the CPU reads the LSR, the Overun Error bit is reset to a 0.

Bit 2: This Parity Error bit is set to a logic 1 whenever a parity error is detected (received character has a parity other than that selected). Reading the LSR resets this bit to a 0.

Bit 3: This Framing Error bit is set to a logic 1 when an incoming character has no stop bit after the last data bit or (if parity is enabled) after the parity bit. A valid stop bit is the presence of a Mark condition (logic 1) in the proper time slot after the last data bit or the parity bit. Reading the LSR resets this bit to a 0.

Bit 4: This Break Interrupt bit will be a logic 1 if a Space condition (logic 0) is present on the corresponding RXD (RXD2 or RXD1) line for an entire character time (start bit time, plus data bit times, plus parity bit time, plus stop bit time). Reading the LSR resets this bit to a 0.

Bit 5: This Transmit Buffer Empty (TBE) bit is set to a logic 1 when an outgoing character is loaded from the Transmit Buffer (TB) into the Transmit Shift Register. If the TBE interrupt is enabled, an interrupt will be generated when this bit is set. Writing a character to the TB resets this bit to a 0.

Bit 6: This Transmitter Empty (TEMT) bit will be set to a logic 1 when both the Transmit Buffer and the Transmit Shift Register are empty. When either of these two registers contains a character, this bit will be reset to a 0.

Bit 7: This bit is set to 0.

# **MODEM Status Register (MSR)**

This byte-wide register holds the current value of the MODEM control lines. It also sets a bit (to a logic 1) each time one of these control lines changes state. Reading the MSR resets all of the Change bits to 0. A MODEM Status

Interrupt is generated (if it is enabled) when Bit 0, 1, 2 or 3 is set to a 1. Bit definitions are:

Bit 0: This is the Clear To Send Changed bit. It is set to a 1 if the corresponding CTS line (CTS2 or CTS1) has changed state since the last time the MSR was read.

Table 3 Summary of Accessible Register Bit Definitions

Part 1 of 2

| Bit # | Receive<br>Buffer<br>RB | Transmit<br>Buffer<br>TB | Interrupt<br>Enable<br>Register<br>IER             | Interrupt<br>Flag<br>Register<br>IFR  | Byte<br>Format<br>Register<br>BFR            | MODEM<br>Control<br>Register<br>MCR                               |

|-------|-------------------------|--------------------------|----------------------------------------------------|---------------------------------------|----------------------------------------------|-------------------------------------------------------------------|

| 0     | Data<br>Bit 0           | Data<br>Bit 0            | Enable<br>Receive<br>Buffer Full<br>Interrupt      | Logic 0<br>if<br>Interrupt<br>Pending | Word<br>Length<br>Bit 0                      | Data<br>Terminal<br>Ready<br>(DTR)                                |

| 1     | Data<br>Bit 1           | Data<br>Bit 1            | Enable<br>Transmit<br>Buffer<br>Empty<br>Interrupt | Interrupt<br>ID Bit 0                 | Word<br>Length<br>Bit 1                      | Request<br>To Send<br>(RTS)                                       |

| 2     | Data<br>Bit 2           | Data<br>Bit 2            | Enable<br>Receive<br>Line<br>Status<br>Interrupt   | Interrupt<br>ID Bit 1                 | Number<br>of Stop<br>Bits                    | Drives RI<br>internally<br>in loopback<br>mode                    |

| 3     | Data<br>Bit 3           | Data<br>Bit 3            | Enable<br>MODEM<br>Status<br>Interrupt             | 0                                     | Parity<br>Enable                             | Drives DCD Internally in loopback mode OUT2 in non- loopback mode |

| 4     | Data<br>Bit 4           | Data<br>Bit 4            | 0                                                  | 0                                     | Even<br>Parity<br>Select                     | Loop                                                              |

| 5     | Data<br>Bit 5           | Data<br>Bit 5            | 0                                                  | 0                                     | Force<br>Parity                              | 0                                                                 |

| 6     | Data<br>Bit 6           | Data<br>Bit 6            | 0                                                  | 0                                     | Set<br>BREAK                                 | 0                                                                 |

| 7     | Data<br>Bit 7           | Data<br>Bit 7            | 0                                                  | 0                                     | Divisor<br>Register<br>Address Bit<br>(DRAB) | 0                                                                 |

Bit 1: This is the Data Set Ready Changed bit. It is set to a 1 if the corresponding DSR line (DSR2 or DSR1) has changed state since the last time the MSR was read.

Bit 2: This is the Rising Edge of Ring Indicator bit. It is set to a 1 if the corresponding RI line (RI2 or RI1) has changed from a logic 0 to a logic 1 since the last time the MSR was read.

Bit 3: This is the Data Carrier Detect Changed bit. It is set to a 1 if the corresponding DCD line (DCD2 or DCD1) has changed state since the last time the MSR was read.

Bit 4: This is the Clear To Send bit. It is the complement of the corresponding CTS (CTS2

or CTS1) pin. When in diagnostic loopback mode, this bit is identical to the RTS bit in the MODEM Control Register (MCR).

Bit 5: This is the Data Set Ready bit. It is the complement of the corresponding DSR (DSR2 or DSR1) pin. When in diagnostic loopback mode, this bit is identical to the DTR bit in the MCR.

Bit 6: This is the Ring Indicator bit. It is the complement of the corresponding RI (RI2 or RI1) pin. In diagnostic loopback mode, it is controlled by Bit 2 of the MCR.

Bit 7: This is the Data Carrier Detect bit. It is the complement of the corresponding DCD

# Summary of Accessible Register Bit Definitions Part 2 of 2

| Bit # | Line<br>Status<br>Register<br>LSR | MODEM<br>Status<br>Register<br>MSR  | Scratch-<br>pad<br>Register<br>SR | Divisor<br>Register<br>LSB<br>DRL | Divisor<br>Register<br>MSB<br>DRM |

|-------|-----------------------------------|-------------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|

| 0     | Receive<br>Buffer<br>Full (RBF)   | Clear To<br>Send Changed            | Bit 0                             | Bit 0                             | Bit 8                             |

| 1     | Overrun<br>Error                  | Data Set<br>Ready<br>Changed        | Bit 1                             | Bit 1                             | Bit 9                             |

| 2     | Parity<br>Error                   | Rising Edge<br>of Ring<br>Indicator | Bit 2                             | Bit 2                             | Bit 10                            |

| 3     | Framing<br>Error                  | Data Carrier<br>Detect<br>Changed   | Bit 3                             | Bit 3                             | Bit 11                            |

| 4     | BREAK<br>Interrupt                | Clear To<br>Send                    | Bit 4                             | Bit 4                             | Bit 12                            |

| 5     | Transmit<br>Buffer<br>Empty       | Data Set<br>Ready                   | Bit 5                             | Bit 5                             | Bit 13                            |

| 6     | Transmitter<br>Empty              | Ring<br>Indicator                   | Bit 6                             | Bit 6                             | Bit 14                            |

| 7     | 0                                 | Data Carrier<br>Detect              | Bit 7                             | Bit 7                             | Bit 15                            |

# CHIPS.

(DCD2 or DCD1) pin. In diagnostic loopback mode, it is controlled by Bit 3 of the MCR.

### Scratchpad Register

This byte-wide register has no effect on the UART within which it is located. It can be used for any purpose by the programmer.

# Summary Table of Accessible Register Bit Definitions

Table 3 summarizes the bit definitions in all of the UART accessible registers.

### Effects of a Hardware Reset

The table below details the effect of a hardware RESET on each of the UARTs located in a CHIPSpak. Note that the CHIPSpak has a configuration option which permits only a part of each UART to be reset when a hardware RESET is applied. This option is useful when the CHIPSpak will monitor a serial link and wake up the CPU upon receipt of an incoming character. Bit 7 in CHIPSpak Configuration Register 1 controls this option. When Bit 7 is a 0, all registers in each UART except the Receive Buffer, Transmit Buffer

Table 4 Action of a Hardware Reset on the CHIPSpak UARTs

| Register or Signal                 | Cause of Reset             | Reset State                                   |

|------------------------------------|----------------------------|-----------------------------------------------|

| Interrupt Enable Register          | Hardware RESET             | All bits = logic 0                            |

| Interrupt Flag Register            | Hardware RESET             | Bit 0 = logic 1<br>Other bits = logic 0       |

| Byte Format Register               | Hardware RESET             | All bits = logic 0                            |

| MODEM Control Register             | Hardware RESET             | All bits = logic 0                            |

| Line Status Register               | Hardware RESET             | Bits 5, 6 = logic 1<br>Other bits = logic 0   |

| MODEM Status Register              | Hardware RESET             | Bits 0-3 = logic 0<br>Bits 4-7 = Input Signal |

| TXD2 and TXD1                      | Hardware RESET             | logic 1 (high)                                |

| Receive Line Status<br>Interrupt   | Hardware RESET or Read LSR | logic 0 (low)                                 |

| Receive Buffer Full<br>Interrupt   | Hardware RESET or Read RB  | logic 0 (low)                                 |

| Transmit Buffer Empty<br>Interrupt | Hardware RESET or Read TB  | logic 0 (low)                                 |

| MODEM Status Interrupt             | Hardware RESET or Read MSR | logic 0 (low)                                 |

| RTS2 and RTS1                      | Hardware RESET             | logic 1 (high)                                |

| DTR2 and DTR1                      | Hardware RESET             | logic 1 (high)                                |

and the Divisor Registers (LSB and MSB) will be reset when a hardware RESET occurs. If Bit 7 is a 1, none of the registers in the UARTS will be reset. See the section of this data sheet which covers Configuration for more details. The table below assumes that Bit 7 of the CHIPSpak Configuration register is a zero.

#### **Baud Rate Generation**

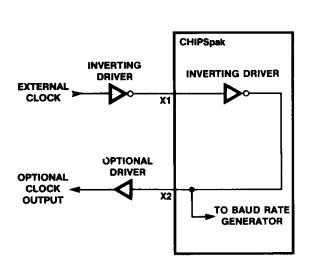

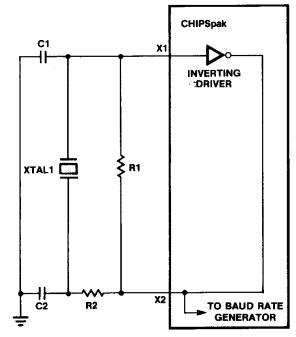

The table below details the content of the Divisor Registers for various baud rates when using either a 1.8432 MHz or a 3.072 MHz crystal. All table values are decimal. Following the table, Figure 3 depicts the use of an external oscillator for baud rate clock control and Figure 4 shows the connection of a crystal to the CHIPSpak.

### **PARALLEL PORT**

The parallel port can be configured for either of two different modes of operation: printer (output only) and scanner (bidirectional). While there is a high degree of compatibility between these modes, there are a few differences in operation and in definition of the control registers and I/O pins. The external

buffer and buffer control signals used must be changed to reconfigure the port from printer to scanner mode. This can be done either with external jumpers (requires opening of the PC case and manual intervention) or with two gates controlled by the game port decode pin (requires execution of setup software) or another decoder output. Note that this external hardware (jumpers or gates) is only required in the case where the configuration (printer or scanner) is to be software selectable.

The printer interface utilizes Centronics-compatible pin definitions. The scanner interface uses Centronics-like pin definitions which can be used to drive a RICOH IS30 scanner or equivalent.

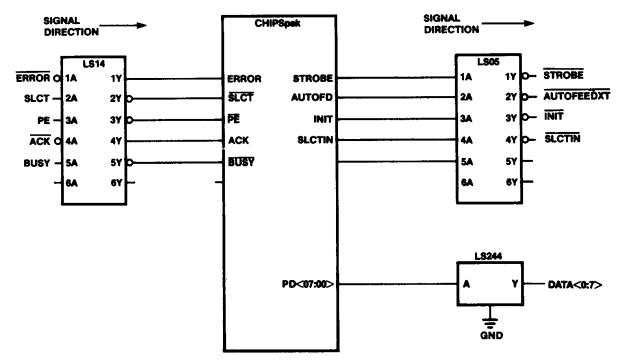

### Printer Interface

To permit the parallel port to properly drive a Centronics-compatible interface, LS05 open-collector buffers should be used with CHIPSpak control output pins to ensure sufficient drive capacity and to minimize the likelihood of electrostatic discharge (ESD) problems. The LS05 output lines should be

Table 5 Divisor Register Values for Various Baud Rates

|           | 1.8432 MHz                   | : Crystal                        | 3.072 MHz Crystal            |                                  |  |  |

|-----------|------------------------------|----------------------------------|------------------------------|----------------------------------|--|--|

| Baud Rate | Divisor<br>Register<br>Value | % Error<br>Desired vs.<br>Actual | Divisor<br>Register<br>Value | % Error<br>Desired vs.<br>Actual |  |  |

| 50        | 2304                         | none                             | 3840                         | none                             |  |  |

| 75        | 1536                         | none                             | 2560                         | none                             |  |  |

| 110       | 1047                         | 0.026                            | 1745                         | 0.026                            |  |  |

| 134.5     | 857                          | 0.058                            | 1428                         | 0.034                            |  |  |

| 150       | 768                          | none                             | 1280                         | none                             |  |  |

| 300       | 384                          | none                             | 640                          | none                             |  |  |

| 600       | 192                          | none                             | 320                          | none                             |  |  |

| 1200      | 96                           | none                             | 160                          | none                             |  |  |

| 1800      | 64                           | none                             | 107                          | 0.312                            |  |  |

| 2000      | 58                           | 0.69                             | 96                           | none                             |  |  |

| 2400      | 48                           | none                             | 80                           | none                             |  |  |

| 3600      | 32                           | none                             | 53                           | 0.628                            |  |  |

| 4800      | 24                           | none                             | 40                           | none                             |  |  |

| 7200      | 16                           | none                             | 27                           | 1.23                             |  |  |

| 9600      | 12                           | none                             | 20                           | none                             |  |  |

| 19200     | 6                            | none                             | 10                           | none                             |  |  |

| 38400     | 3                            | none                             | 5                            | none                             |  |  |

| 56000     | 2                            | 2.86                             | <del></del>                  |                                  |  |  |

Figure 3. UART Clock Provided by an External Clock

Figure 4. UART Clock Provided by a Crystal

Table 6 Resistor and Capacitor Values for Oscillator Network

| Crystal Frequency | R1     | R2       | C1       | C2       |

|-------------------|--------|----------|----------|----------|

| 1.8 MHz           | 1M Ohm | 1.5K Ohm | 10-30 pF | 40-60 pF |

| 3.1 MHz           | 1M Ohm | 1.5K Ohm | 10-30 pF | 40-60 pF |

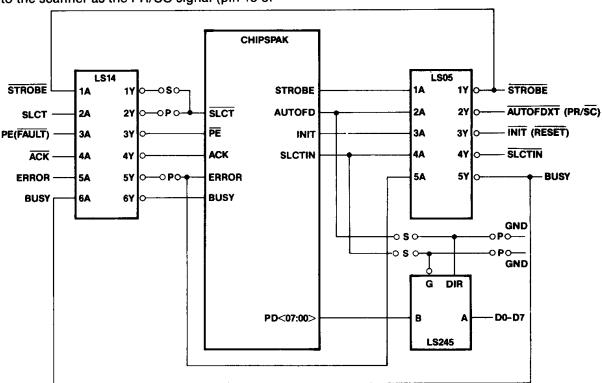

pulled up to +5V through 4.7K resistors. CHIPSpak Data outputs should be isolated with a non-inverting buffer (LS244). CHIPSpak Control inputs pins are assumed to be isolated with an inverting buffer (LS04, LS240 or Schmitt trigger LS14). A typical interface is shown in Figure 5.

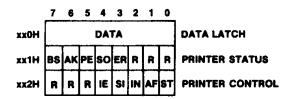

# Printer Interface Accessible Registers

Figure 6 depicts the registers and I/O ports which are accessible for the parallel printer port. These are compatible with the the IBM PC parallel port. Bit definitions for each of these registers are given after the diagram. All addresses are offsets from the base address for the parallel port specified during the CHIPSpak configuration process. Additional instructions regarding setup times and pulse widths are meant for use with Centronics-compatible interfaces. Bit definitions in Figure 6 labeled R are reserved.

### **Data Latch**

This read/write register is located at an offset of 0H from the base address of the parallel port. Data written to this register is transmitted to the printer. Data read from this port is identical to that which was last written.

### **Printer Status Register**

This read-only register is located at an offset of 1H from the base address of the parallel port. Bit definitions are as follows:

Bit 7: BS—Busy. This bit reflect the state of the CHIPSpak BUSY input pin. A 0 means that the printer is busy and cannot accept data. A 1 indicates that the printer is ready to accept data.

Bit 6: AK—Acknowledge. This bit reflects the state of the ACK input pin. A 0 means that the printer has received a character and is

Figure 5: Printer Only Configuration.

Figure 6: Parallel Port Accessible Registers

ready to accept another. A 1 means that it is still reading the last character sent.

Bit 5: PE—Paper Empty. This bit reflects the state of the CHIPSpak PE input pin. A 1 indicates a paper end condition. A 0 indicates the presence of paper.

Bit 4: SO—SLCT. This bit reflects the state of the CHIPSpak SLCT input pin. A 1 means the printer is online. A 0 means it is deselected.

Bit 3: ER—ERROR. This bit reflects the inverted state of the CHIPSpak ERROR input pin. A 0 means that an error condition has been detected. A 1 indicates no errors.

Bits 2-0: Reserved.

### **Printer Controls Register**

This read/write register is located at an offset of 2H from the base address of the parallel port. Bit definitions are:

Bits 7-5: Reserved. Reset to 0.

Bit 4: IE—IRQ Enable. This bit is used to enable or disable interrupts resulting from the printer ACK signal. A 1 enables interrupts so that when ACK is not asserted by the printer, the CPU will be interrupted on the IRQ line specified in the CHIPSpak configuration RAM. Reset to 0.

**Bit 3:** SI—SLCTIN. Used to drive the CHIPSpak SLCTIN output pin. A 1 selects the printer. Reset to 0.

Bit 2: IN—Init. Used to control the CHIPSpak INIT output pin. A 0 (active low) starts the printer (50  $\mu$ S pulse minimum). Reset to 0. Note that the INIT output pin is an inversion of this bit.

Bit 1: AF—Auto Feed. Used to control the CHIPSpak AUTOFD output pin. A 1 causes the printer to line feed after each line is printed. Reset to 0.

CHIP5

**Bit 0:** ST—Strobe. Used to control the CHIPSpak STROBE output pin. A 1 in this bit generates the active high pulse (0.5  $\mu$ S pulse minimum) which is required to clock data into the printer. There is a 0.5  $\mu$ S data setup time requirement before STROBE can be asserted. Reset to 0.

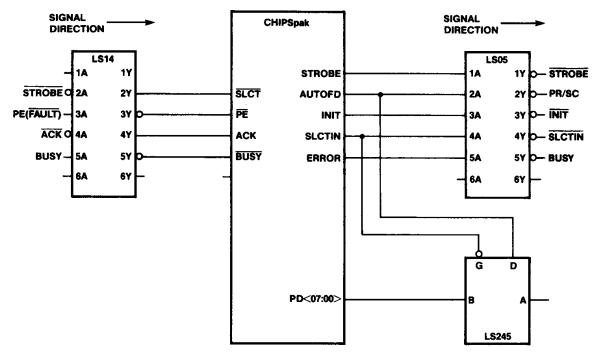

#### Scanner Interface

The CHIPSpak can drive the Centronics-like parallel interface used by the RICOH IS30 scanner. The parallel port is configured as a scanner interface by setting bit 6 in the CHIPSpak Configuration Register. This interface is similar to the standard Centronics interface commonly used for parallel printers. CHIPSpak control output pins should be buffered from the connector with LS05 opencollector drivers to ensure sufficient drive capacity and to minimize the likelihood of ESD problems. The LS05 output lines must be pulled up to +5V with 4.7K resistors. Bidirectional data pins should be isolated by a non-inverting buffer (LS245). Status and control inputs from the scanner are assumed to be isolated by an inverting buffer (LS04, LS240 or Schmitt trigger LS14).

The external buffers required for a typical scanner interface are shown in Figure 7.

A comparison of the signals used in a Centronics-compatible printer interface and in the Ricoh IS30 scanner interface is given in the table below. Pin numbers refer to those of the 36 pin connector normally used with a Centronics-compatible interface. The polarity of signals is that to be found at the connector (after buffering and possibly inverting the CHIPSpak input or output pins).

#### Scanner Interface Accessible Registers

The following registers and I/O ports are accessible when the CHIPSpak parallel port is configured for use with a scanner (see the section entitled "Configuration Sequence" for details). These are a subset of those used in the IBM PC parallel port definition. The function of the SLCTIN and AUTOFD signals has been redefined to control the operation of an external bidirectional buffer. A summary of the registers accessible when the parallel port is defined for scanner use is depicted in Figure 8. Descriptions of the use of each of the bits in these registers follows Figure 8.

Figure 7: Scanner Only Configuration.

CHIP5

Table 7 Centronics-compatible Connector Pinout vs RICOH IS30 Pinout

| Pin(s) | Dir Printer |           | Printer Dir Scanner |           | Comments            |

|--------|-------------|-----------|---------------------|-----------|---------------------|

| 1      | 0           | STROBE    | 1/0                 | STROBE    |                     |

| 2-9    | 1/0         | DATA<0:7> | 1/0                 | DATA<0:7> |                     |

| 10     | I           | ACK       | 1                   | ACK       |                     |

| 11     | 1           | BUSY      | 1/0                 | BUSY      |                     |

| 12     | ı           | PE        | 1                   | unused    |                     |

| 13     | ŀ           | SLCT      | _                   | FAULT     |                     |

| 14     | 0           | AUTOFD    | _                   | unused    | generate PR/SC      |

| 15     | ı           | unused    | 1                   | PR/SC     | generated by AUTOFD |

| 31     | 0           | INIT      | 1                   | RESET     |                     |

| 32     | 1           | ERROR     | _                   | unused    |                     |

| 36     | 0           | SLCTIN    |                     | unused    | Buffer Enable       |

|      | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |                  |

|------|----|----|----|----|----|----|----|----|------------------|

| хх0Н |    |    |    | DA | TA |    |    |    | DATA LATCH       |

| хх1Н | BS | AK | PE | so | R  | R  | R  | ST | SCANNER STATUS   |

| xx2H | BS | R  | R  | ΙE | EN | IN | PS | ST | SCANNER CONTROLS |

Figure 8: Parallel Scanner Accessible Registers.

### **Data Latch**

This read/write register is located at an offset of 0H from the base address of the parallel port. Data written to this register is transmitted to the scanner. Data read from this register is received from the scanner. CHIPSpak pins PD<07:00> are controlled by accessing this register.

### **Scanner Status Register**

This read-only register is located at an offset of 1H from the base address of the parallel port. Bit definitions are:

Bit 7: BS—Busy. A 0 in this bit when the scanner is in print mode means the scanner is busy and cannot accept data.

Bit 6: AK—acknowledge. A 0 in this bit means that the scanner has received a character and is ready to accept another. A 1 indicates that the scanner is still reading the last character sent.

Bit 5: PE—FAULT. A 0 indicates that an error exists. This bit reflects the state of the CHIPSpak PE input pin.

Bit 4: SO—SLCT. A 1 in this bit means the scanner is selected. A 0 means it is deselected.

Bits 3-1: Reserved.

Bit 0: ST—Strobe. This bit is used to read the value of the scanner's STROBE signal which is connected to the CHIPSpak SLCT pin. It has the same polarity as the CHIPSpak SLCT pin (i.e. if the SLCT pin is a 0 this bit will be a 0). The scanner asserts STROBE (forcing this bit to a 1 state) to indicate that valid data is available.

### Scanner Controls Register