Product Bulletin

#### **FEATURES**

- Fully hardware- and software-compatible with PC XT/AT computers

- Reed-Solomon error correction code (ECC) with automatic, 'on-the-fly' hardware correction

- Low-power or 'sleep' mode

- Proprietary split-data-field support for zoned recording formats

- Multisector data transfer reduces real-time processing demand

- Programmable buffer segments for user-defined caching, read look-ahead, microcode storage, etc.

- Provides direct bus interface logic with on-chip 24-mA drivers

- Contains the logic for daisy chaining two embedded disk controller drives on a PC XT, as well as PC AT

- Support for multiplexed and non-multiplexed address and data bus microcontroller interface

- Provides logic to speed up PC AT command response

- Provides on-chip registers to emulate the IBM® Task File for PC AT, IBM Command Descriptor Block for PC XT

- 100-pin QFP and VQFP packages

- Low-power CMOS technology

#### Supports:

- Host data transfer under DMA or programmed I/O for both PC XT and PC AT modes

- Direct buffer memory addressing up to 64K bytes of static RAM

- 8- and 16-bit data transfer on the host bus

- Any XT/AT interface speed with programmable and auto-inserted wait states

# High-performance PC XT/AT™ Disk Controller

## **OVERVIEW**

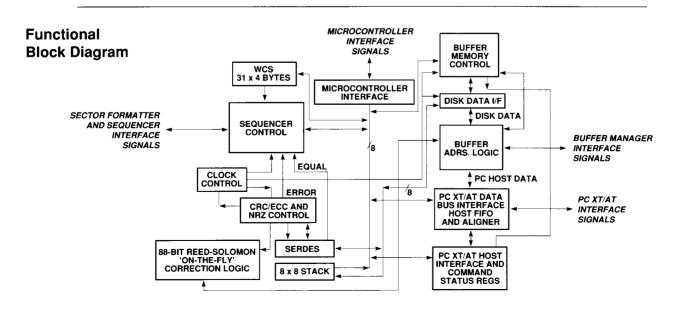

The highly integrated CL-SH360 provides a large portion of the hardware necessary to build a Winchester disk controller for the PC XT/AT or other compatible interface. The CL-SH360 includes an advanced Winchester Disk Formatter, a dual-port Buffer Manager, and a host bus interface. The CL-SH360 provides the enabling feature set and technology for smaller, faster, higher-capacity and lower-cost drives.

To ensure data integrity, the CL-SH360 performs 'on-the-fly' Reed-Solomon error correction, while transferring data at a continuous 32-Mbit/second rate. It automatically performs correction of data errors during disk-read operations (without local microprocessor intervention), making it ideal for high-performance applications. The CL-SH360 is the first intelligent PC AT-compatible disk drive controller to implement this error-tolerance capability. (cont. next page)

# **OVERVIEW** (cont.)

The enhanced CL-SH360 supports disk data rates up to 32 Mbits/second. A proprietary split-data-field technique optimizes disk capacity, enables faster access times, and increases data rates. A power-down mode reduces power consumption by up to 75 percent, making the CL-SH360 ideal for laptop and power-sensitive applications. Because the controller is architecturally compatible, it provides an easy upgrade for both existing designs and higher-performance systems.

The CL-SH360 Disk Formatter consists of a serial-izer/deserializer, a flexible RAM-based Sequencer, and CRC/ECC generation circuitry. The industry-standard 16-bit CCITT-CRC and proprietary 88-bit Reed-Solomon ECC polynomial are supported in hardware. The CL-SH360 Buffer Manager will control up to 64K bytes of SRAM buffer memory as a dual-port circular buffer. The CL-SH360 supports

multisector data transfer, thus reducing real-time processing demand on local microcontrollers, allowing creation of lower-cost, single-processor disk drive designs. It also segments a programmable buffer, for user-defined caching algorithims or protected-memory area in buffer memory.

The CL-SH360 works with a local microcontroller and supports both multiplexed address and data bus architecture, similar to Intel® 8051 family and Motorola® 68HC11 microcontrollers, as well as the newer non-multiplexed bus processor architectures. Also provided is a READY Signal interface for high-speed microcontrollers. It supports both interruptand polled-processor interfaces. The maskable interrupts include many disk and host interface events. The CL-SH360 also has hardware to speed microcontroller access of the buffer memory.

## **ADVANTAGES**

## **Unique Features**

- Reed-Solomon error correction

- Multisector data transfer

- Proprietary split-data-field support

- Low-power or sleep mode

- Provides automatic wait states or pre-programmed wait states for extended cycle transfers

- Provides logic for daisy chaining two embedded controller drives on the PC Bus in a Master/Slave Configuration

- Supports 10 Mbytes/second buffer memory throughput

- Data rate up to 32 Mbits/second

- Maskable microcontroller interrupt capability

#### **Benefits**

Supports true 'on-the-fly' error correction during full-speed data reads. Probability of miscorrection is as low as 10<sup>-20</sup> per bit corrected.

Reduces real-time processing demand on the local disk drive microcontroller, allowing creation of lower-cost, single-processor disk drive designs.

Optimizes disk capacity, enables faster access times and data rates.

Reduces power consumption by up to 75 percent.

Can be compatible with any host CPU speeds. Prevents host overrun or underrun conditions.

Allows the use of two embedded disk controllers in a system.

Compatible with high-performance applications.

Compatible with high-performance applications.

Relieves the microcontroller from polling to perform other tasks. Provides status information to the microprocessor when interrupts are disabled.

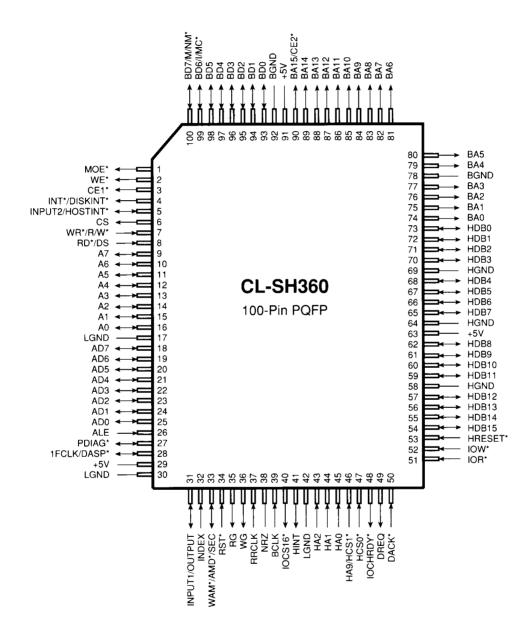

100-Pin Quad Flat Pack (QFP) Diagram

3

## PIN DESCRIPTION

| Symbol                         | Pin Number<br>(QFP)           | Туре   | Description                                   |

|--------------------------------|-------------------------------|--------|-----------------------------------------------|

| Buffer Memory Interface Pins   |                               |        |                                               |

| BA[0:15]                       | 74-77, 79-90                  | 0      | Buffer Address Lines                          |

| BD[0:7]                        | 93-100                        | I/O, Z | Buffer Data Bus                               |

| MOE*                           | 1                             | 0      | Memory Output Enable                          |

| WE*                            | 2                             | 0      | Write Enable                                  |

| CE*                            | 3                             | 0      | Buffer Chip Enable                            |

| Microcontroller Interface Pins |                               |        |                                               |

| INT*                           | 4                             | 0      | Interrupt                                     |

| I/MC*                          | 5                             | l .    | Intel/Motorola                                |

| CS                             | 6                             |        | Chip Select                                   |

| WR*/R/W*                       | 7                             | 1      | Write Strobe/Read/Write                       |

| RD*/DS                         | 8                             |        | Read Strobe/Data Strobe                       |

| A[7:0]                         | 9-16                          | I/O, Z | Local Microcontroller Address/Data Bus        |

| AD[7:0]                        | 18-25                         | I/O, Z | Microcontroller Address/Data                  |

| ALE/M/NM*                      | 26                            |        | Address Latch Enable/Multiplexed/Non-         |

| 1.55)/#                        | .=                            | •      | multiplexed Address Configuration             |

| LRDY*                          | 27                            | 0      | Local Microcontroller Ready                   |

| 1FCLK                          | 28                            | I      | ECC Corrector Circuit Clock                   |

| Disk Interface Pins            |                               |        |                                               |

| INPUT/OUTPUT                   | 31                            | I/O, Z | Input/Output                                  |

| INDEX                          | 32                            | 1      | Index                                         |

| WAM*/AMD*/SECTOR               | 33                            | I/O, Z | Write Address Mark/Address Mark Detect/Sector |

| RST*                           | 34                            | 1      | Reset                                         |

| RG                             | 35                            | 0      | Read Gate                                     |

| WG                             | 36                            | 0      | Write Gate                                    |

| RRCLK                          | 37                            | 1      | Read Reference Clock                          |

| NRZ                            | 38                            | I/O, Z | Non Return to Zero                            |

| Host Bus Interface Pins        |                               |        |                                               |

| BCLK                           | 39                            | 1      | Buffer Clock                                  |

| IOCS16*                        | 40                            | OD     | 16-bit Data Transter                          |

| HINT                           | 41                            | O, Z   | Host Interrupt                                |

| A[2:0]                         | 43-45                         | 1      | PC Bus Address Lines                          |

| A9/HCS1*                       | 46                            | 1      | PC Address Line 9 or Chip Select 1            |

| HCS0*                          | 47                            | 1      | Chip Select 0                                 |

| IOCHRDY*                       | 48                            | O, Z   | Input/Out Channel Ready                       |

| DREQ                           | 49                            | O, Z   | DMA Request                                   |

| DACK*                          | 50                            | l      | DMA Acknowledge                               |

| IOR*                           | 51                            | l      | Input Read Select                             |

| IOW*                           | 52                            | l      | Input Write Select                            |

| HRESET                         | 53                            |        | Host Reset                                    |

| HDB[15:0]                      | 54-57, 59-62,<br>65-68, 70-73 | I/O, Z | Host Data Bus                                 |

| Power and Ground Pins          |                               |        |                                               |

| HGND                           | 58, 64, 69                    | N/A    | Host Ground                                   |

| BGND                           | 78, 92                        | N/A    | Buffer Bus Ground                             |

| LGND                           | 17, 30, 42                    | N/A    | Logic Ground                                  |

| +5V                            | 29, 63, 91                    | N/A    | Power Supply (+5)                             |

**NOTE:** (\*) denotes negative true signal. I indicates input pin; O indicates output pin; I/O indicates input/output pin; OD indicates open drain output pin; Z indicates tri-state output or input/output pin.

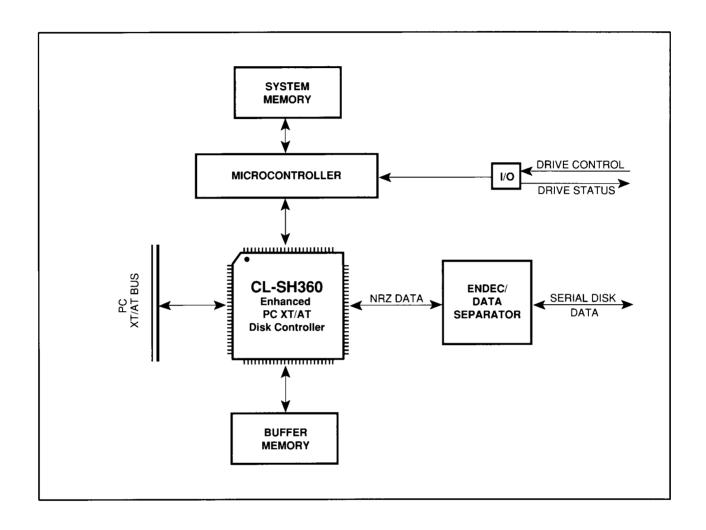

TYPICAL CL-SH360 APPLICATION

#### **Direct Sales Offices**

#### **Domestic**

N. CALIFORNIA San Jose

TEL: 408/436-7110 FAX: 408/437-8960

S. CALIFORNIA

Tustin

TEL: 714/258-8303 FAX: 714/258-8307

Thousand Oaks TEL: 805/371-5381 FAX: 805/371-5382

**ROCKY MOUNTAIN** AREA

Boulder, CO

TEL: 303/939-9739 FAX: 303/440-5712 **SOUTH CENTRAL** AREA

Austin, TX

TEL: 512/794-8490 FAX: 512/794-8069

Plano, TX

TEL: 214/985-2334 FAX: 214/964-3119

**NORTHEASTERN** AREA

Andover, MA TEL: 508/474-9300 FAX: 508/474-9149

New Brunswick, NJ TEL: 908/603-7757 FAX: 908/603-7756 **SOUTH EASTERN AREA**

Boca Raton, FL TEL: 407/362-5225 FAX: 407/394-0618

International

**GERMANY**

Herrsching TEL: 49/08152-2030

FAX: 49/08152-6211

**JAPAN** Tokvo

TEL: 81/3-5389-5300 FAX: 81/3-5389-5540 \*\*\* \*\*/ \*\***j** SINGAPORE

TEL: 65/3532122 FAX: 65/3532166

**TAIWAN**

Taipei

<sup>Rosen</sup> S. R. A. Const.

TEL: 886/2-718-4533 FAX: 886/2-718-4526

UNITED KINGDOM

Hertfordshire, England TEL: 44/0727-872424 FAX: 44/0727-875919

# The Company

Cirrus Logic, Inc., produces high-integration peripheral controller circuits for mass storage, graphics, and data communications. Our products are used in leading-edge personal computers, engineering workstations, and office automation equipment.

The Cirrus Logic formula combines proprietary S/LA<sup>TM +</sup> IC design automation with system design expertise. The S/LA design system is a proven tool for developing high-performance logic circuits in half the time of most semiconductor companies. The results are better VLSI products, on-time, that help you win in the marketplace.

Cirrus Logic's fabless manufacturing strategy, unique in the semiconductor industry, employs a full manufacturing infrastructure to ensure maximum product quality, availability and value for our customers.

Talk to our systems and applications specialists; see how you can benefit from a new kind of semiconductor company.

† U.S. Patent No. 4,293,783

© Copyright, Cirrus Logic, Inc., 1992

Cirrus Logic, Inc., believes the information contained in this document is accurate and reliable. However, it is subject to change without notice. No responsibility is assumed by Cirrus Logic, Inc., for its use, nor for infringements of patents or other rights of third parties. This document implies no license under patents or copyrights. Trademarks in this document belong to their respective companies. Cirrus Logic, Inc., products are covered under one or more of the following U.S. patents: 4,293,783; Re. 31,287; 4,763,332; 4,777,635; 4,839,896; 4,931,946; 4,979,173; 5,032,981; 5,122,783; 5,131,015; 5,140,595.

3100 West Warren Ave. Fremont, CA 94538 CIRRUS LOGIC, Inc.,

TEL: 510/623-8300 FAX: 510/226-2180

NOV O 4 1992

031328 🗸

215360-002