### Warp3<sup>TM</sup>

#### VHDL Development System

#### User's Manual

Cypress Semiconductor 3901 North First Street San Jose, CA 95134 (408)943-2600 JANUARY 1995

#### **Cypress Software License Agreement**

- 1. LICENSE. Cypress Semiconductor Corporation ("Cypress") hereby grants you, as a Customer and Licensee, a single-user, non-exclusive license to use the enclosed Cypress software program ("Program") on a single CPU at any given point in time. Cypress authorizes you to make archival copies of the software for the sole purpose of backing up your software and protecting your investment from loss.

- 2. TERM AND TERMINATION. This agreement is effective from the date the diskettes are received until this agreement is terminated. The unauthorized reproduction or use of the Program and/or documentation will immediately terminate this Agreement without notice. Upon termination you are to destroy both the Program and the documentation.

- 3. COPYRIGHT AND PROPRIETARY RIGHTS. The Program and documentation are protected by both United States Copyright Law and International Treaty provisions. This means that you must treat the documentation and Program just like a book, with the exception of making archival copies for the sole purpose of protecting your investment from loss. The Program may be used by any number of people, and may be moved from one computer to another, so long as there is **No Possibility** of its being used by two people at the same time.

- 4. DISCLAIMER. THIS PROGRAM AND DOCUMENTA-TION ARE LICENSED "AS-IS," WITHOUT WARRANTY AS TO PERFORMANCE. CYPRESS EXPRESSLY DIS-CLAIMS ALL WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTY OF MERCHANTABILITY OR

FITNESS OF THIS PROGRAM FOR A PARTICULAR PURPOSE.

- 5. LIMITED WARRANTY. The diskette on which this Program is recorded is guaranteed for 90 days from date of purchase. If a defect occurs within 90 days, contact the representative at the place of purchase to arrange for a replacement.

- 6. LIMITATION OF REMEDIES AND LIABILITY. IN NO EVENT SHALL CYPRESS BE LIABLE FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES RESULTING FROM PROGRAM USE, EVEN IF CYPRESS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. CYPRESS'S EXCLUSIVE LIABILITY AND YOUR EXCLUSIVE REMEDY WILL BE IN THE REPLACEMENT OF ANY DEFECTIVE DISKETTE AS PROVIDED ABOVE. IN NO EVENT SHALL CYPRESS'S LIABILITY HEREUNDER EXCEED THE PURCHASE PRICE OF THE SOFTWARE.

- 7. ENTIRE AGREEMENT. This agreement constitutes the sole and complete Agreement between Cypress and the Customer for use of the Program and documentation. Changes to this Agreement may be made only by written mutual consent.

- 8. GOVERNING LAW. This Agreement shall be goverend by the laws of the State of California. Should you have any question concerning this agreement, please contact:

Cypress Semiconductor Corporation Attn: Legal Counsel 3901 N. First Street San Jose, CA 95134-1599

408-943-2600

### Table of Contents

| Chapt  | ter 1 - Warp3 Process Overview                                |        |

|--------|---------------------------------------------------------------|--------|

| 1.1.   | What do you do with Warp3?                                    | 1-2    |

| 1.2.   | What kinds of devices can I target using Warp3?               | 1-4    |

| 1.3.   | What's the design process in Warp3?                           | 1-6    |

| 1.4.   | What are "parts libraries," and why should I know about them? | 1-11   |

| 1.5.   | Where can I call if I have problems?                          | 1-13   |

|        |                                                               |        |

| Chapt  | ter 2 - Warp3 Tools                                           |        |

| 2.1.   | Starting Warp3                                                | 2-2    |

| 2.2.   | The Cockpit                                                   | 2-3    |

| 2.2.1. | The Current Project                                           | 2-6    |

| 2.2.2. | The Search Order                                              | 2-8    |

| 2.2.3. | The Warp Design and Circuit Design Drawers                    | 2-11   |

| 2.3.   | ViewDraw                                                      | 2-12   |

| 2.4.   | expt1076                                                      | 2-13   |

| 2.5.   | Galaxy                                                        | . 2-15 |

| 2.6.   | Warp                                                          | 2-16   |

| 2.7.   | Place & Rte                                                   | 2-17   |

| 2.8.   | pASIC-VSim                                                    | 2-19   |

| 2.9.   | vsm                                                           | 2-21   |

| 2.10.  | ViewSim                                                       |        |

| 2.11.  | ViewTrace                                                     | 2-28   |

| 2.12.  | CypBack                                                       | 2-30   |

| 2.13.  | ViewGen                                                       |        |

| 2.14.  | ViewText                                                      |        |

| 2.15.  | vhdl->sym                                                     | 2-38   |

|        |                                                               |        |

#### **Table of Contents**

| 2.16. | Errors      | 2-40 |

|-------|-------------|------|

| 2.17. | analyzer    | 2-42 |

|       | ViewNav     |      |

| 2.19. | check       | 2-49 |

| 2.20. | netlist in  | 2-52 |

| 2.21. | netlist out | 2-55 |

| 2.22. | sym->vhdl   | 2-59 |

| 2.23. | Nova        | 2-62 |

# Chapter

## **Warp3** Process Overview

#### **About This Chapter**

#### **Overview**

This chapter provides an overview of the design process using  $Warp3^1$  tools.

<sup>1.</sup> Warp3 is a trademark of Cypress Semiconductor.

#### 1.1. What do you do with Warp3?

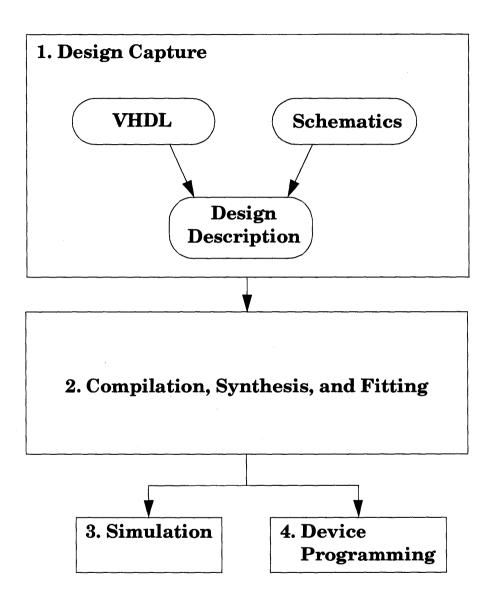

Warp3 is a collection of tools for designing, synthesizing, and simulating circuits to be transferred to programmable logic devices.

#### With Warp3, you can:

- use VHDL descriptions, schematics, or both to describe a design;

- compile and synthesize the resulting design description.

("Compile" means check the design description to make sure it's syntactically correct and contains no obvious logical errors, such as unconnected inputs, etc.

"Synthesize" means realize the design description into logic circuits to be implemented in a PLD or FPGA);

- fit the resulting logic circuits in a particular PLD, or place and route the design in an FPGA. The resulting files may be used for programming the device;

- · verify the design with a timing simulator.

There are other tasks you can perform, but at the highest conceptual level, that's it in a nutshell.

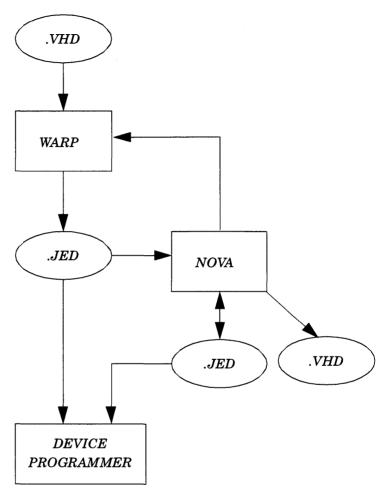

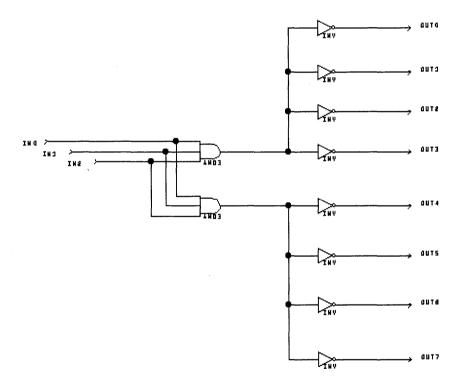

Figure 1-1. Warp3 Conceptual Process Flow.

#### 1.2. What kinds of devices can I target using Warp3?

Warp3 supports a wide variety of Cypress programmable devices. Warp3 features a common user interface so that the process of targeting one device is much like that of targeting any other.

Table 1-1 lists the parts for which you can target designs when using Warp3. These parts can be divided into five families:

- PLDs: the bulk of the Cypress programmable logic device family.

- MAX: the Cypress CY7C34X multiple-array matrix, highdensity EPLD family.

- 37X: the Cypress FLASH370 high-density flash complex PLD family. Note that in Release 1.1, C372 and C373 are supported at the alpha level.

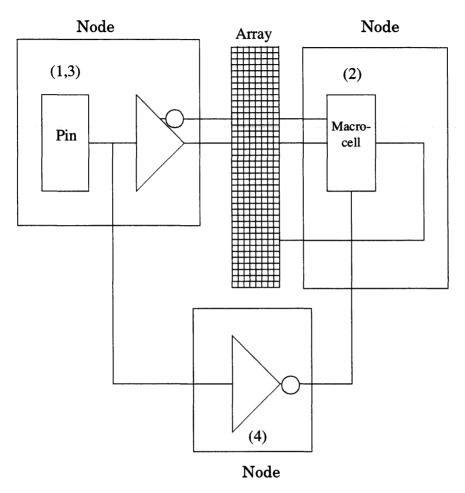

- 38X Programmable ASICs (pASICs<sup>1</sup>): the Cypress pASIC380 very-high-speed CMOS FPGA family.

<sup>1.</sup> pASIC is a trademark of QuickLogic Corporation.

Table 1-1. Warp3-Supported Parts

| Family             | Part #'s                 |                            |                          |                          |

|--------------------|--------------------------|----------------------------|--------------------------|--------------------------|

| PLD's              | C16L8<br>C16V8<br>C22V10 | C16R4<br>C20G10<br>C22VP10 | C16R6<br>C20G10C<br>C331 | C16R8<br>C20RA10<br>C335 |

| MAX<br>CPLD's      | C341<br>C346             | C342<br>C346H              | C343                     | C344                     |

| FLASH370<br>CPLD's | C371<br>C375             | C372                       | C373                     | C374                     |

| pASIC380<br>FPGA's | C381A<br>C385A           | C382A<br>C386A             | C383A                    | C384A                    |

#### 1.3. What's the design process in Warp3?

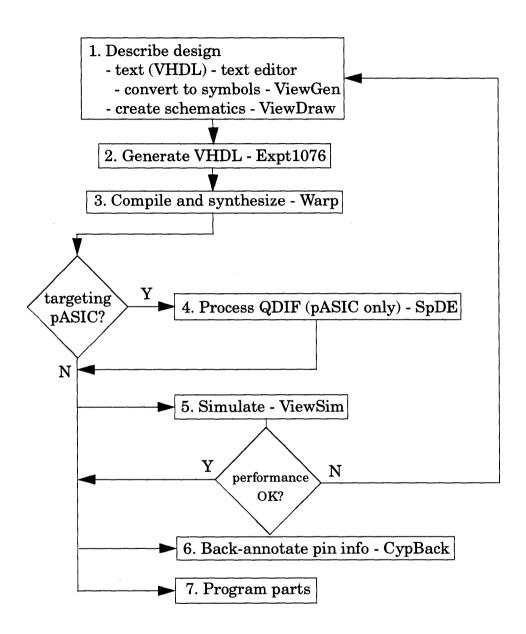

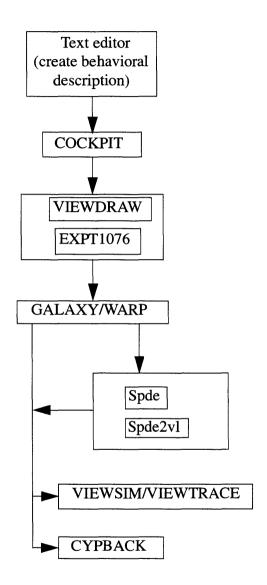

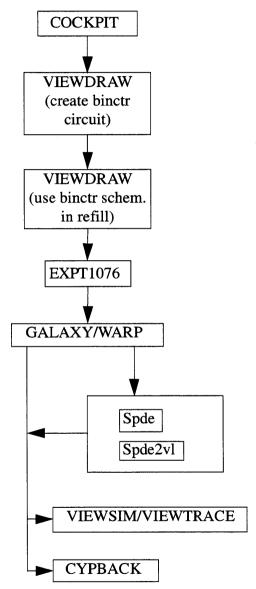

The usual order of design in Warp3 is as follows: (1) invoke the cockpit (project manager), (2) enter the design, (3) generate an IEEE1076 netlist (if necessary), (4) compile, synthesize, and fit the design, (5) place and route the design (FPGA's only), (6) create a timing model for the circuit, (7) simulate the design, (8) back-annotate pin assignment information, and (9) use the output files from the Warp3 design flow to program the target device.

#### **Project Management (Cockpit)**

The cockpit provides an easy point-and-click interface for starting the design tools within the *Warp3* design flow. The Cockpit provides a means to manage your designs by specifying a current project. When you run tools from within the Cockpit, the current design name and project directory can be passed from one tool to the next.

The following paragraphs describe each of the steps in the usual order of design. Figure 1-2 diagrams the *Warp3* design process.

#### Design Entry (ViewDraw, VHDL)

In Warp3, you can describe your designs in VHDL, schematic, or a combination of both.

VHDL designs can be written behaviorally or structurally. Behavioral design descriptions make use of VHDL constructs which permit designs to be described in terms of algorithms or equations. Structural designs are netlists which instantiate components and connect them together, much like a textual description of a schematic. Viewdraw also allows VHDL descriptions to be converted to symbols (using Viewtext, started from Viewdraw) and included as component instantiations within the hierarchy.

Schematics can be entered in Viewdraw. VHDL designs as well as schematic designs can be hierarchical.

#### **Generating a VHDL Netlist (EXPT1076)**

This tool does not need to be run for designs that are described entirely as VHDL. The Warp synthesis engine is a VHDL compiler. Because Warp takes IEEE1076 VHDL as input, all schematics must be converted to VHDL by using the EXPT1076 tool. This tool converts schematics to a VHDL netlist (a structural VHDL description) and flattens the hierarchy.

#### Compiling, Synthesizing, and Fitting the Design (Galaxy)

Galaxy is the GUI (graphical user interface) for Warp. Warp takes VHDL as input, checks the design for proper VHDL syntax, and synthesizes the design to logic equations. (Synthesis is the realization of design descriptions into logic circuits).

For CPLDs, the logic equations produced by synthesis are used by the fitter which attempts to "fit" the logic into a particular device, using algorithms to determine how to optimally use the available resources and macrocell and I/O configurations. The output of the fitter is a JEDEC map used for programming the device after simulation.

For FPGA's, the logic equations produced by synthesis are translated into a netlist specific to the FPGA. This netlist describes the interconnection of logic elements that can map directly to logic cells of the FPGA.

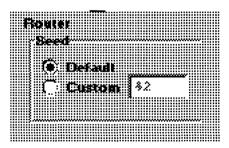

#### Placing and Routing an FPGA (Place & Rte)

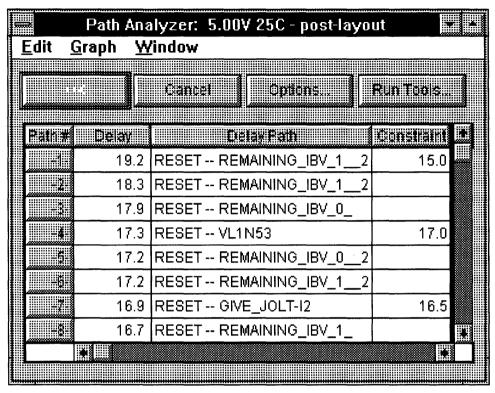

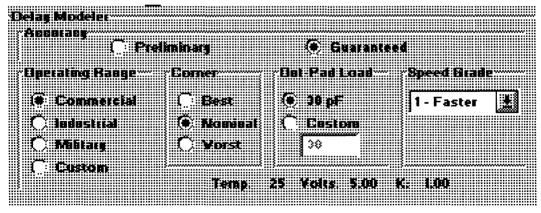

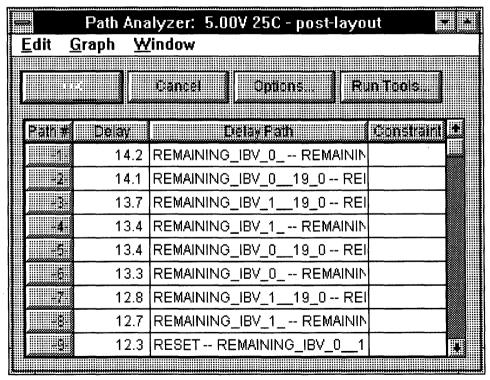

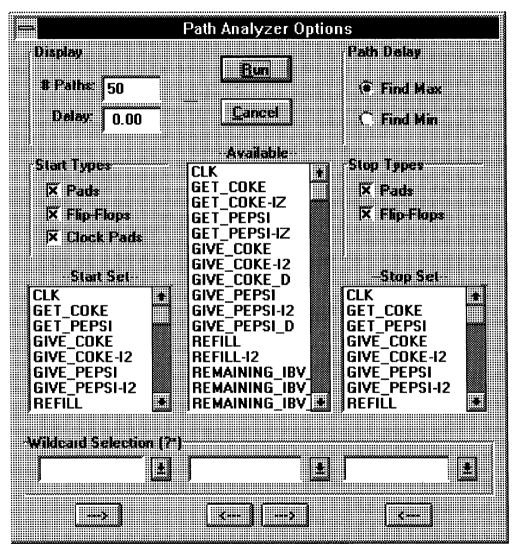

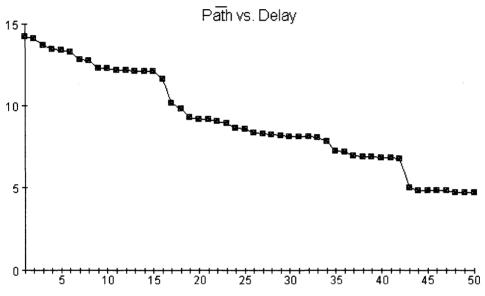

The Place and Route tool is used only for FPGA designs. As its name suggests, this tool uses the FPGA netlist from synthesis to place logic within logic cells, place the logic cells in the device, and route the necessary signals between logic cells and I/O. This tool uses algorithms for optimizing logic implementation within logic cells and for minimizing signal delays and resource utilization. A static timing analyzer is provided to evaluate worst-case delays for all paths and to specify constraints for a timing-driven place and route. The LOF file necessary for programming FPGA's can be exported from this tool

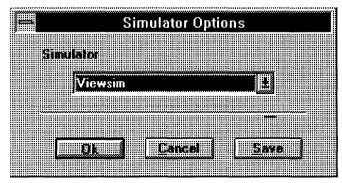

#### **Creating a Viewsim Timing Model (pASIC->VSM)**

pASIC->VSM is used only for FPGA designs. This tool converts a delay table and design description produced by the place and route tool to a Viewsim Timing model. Timing models for CPLDs can be produced from within Galaxy by selecting the appropriate option.

#### Simulating the Design (ViewSim)

Viewsim is used to simulate the design with full timing information. With Viewsim, you can verify the functionality of your design and determine if the design meets timing requirements. Viewsim provides an interface to Viewtrace, which displays waveforms and allows direct interaction with the simulator. Simulation values can also be annotated onto Viewdraw to assist in debugging designs. A sophisticated command language is available for running simulations.

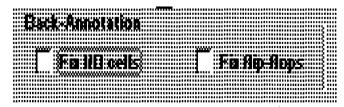

#### **Back annotating pin assignment (Cypback)**

Cypback is used to annotate pin assignments onto your schematic after place and route. It is primarily used to establish pin assignments so that subsequent place and routes will use the same pin assignments.

Figure 1-2. Warp3 Process Overview (Detailed).

#### 1.4. What are library components?

Summary: Library components are directories in which descriptions and symbols of components are stored. A comprehensive set of parts libraries comes with Warp3.

Warp3 provides libraries containing the following types of components:

- adders

- multipliers

- counters

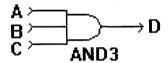

- common logic gates

- input/output components

- memory elements

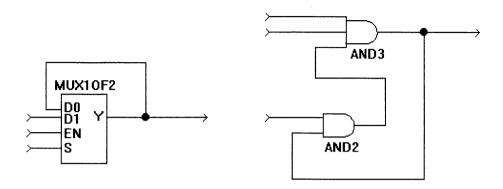

- multiplexers

- registers

- shifters

- TTL components.

You can open the VHDL description of any library component for viewing with any text editor. The default location of the VHDL descriptions of library components is:

\WARP\LIB\COMMON\FAMILY.VHD

where family is the generic name of a particular component group (e.g., COUNTER.VHD, GATES.VHD).

To instantiate a component in a VHDL description, use a VHDL component instantiation statement. See the description of components in Chapter 5 of the Warp Synthesis Compiler Manual.

For more information about the libraries, refer to the Warp System Library Reference Manual.

#### 1.5. Where can I call if I have problems?

Cypress Semiconductor has offices around the world. If you need information about (or if you experience any difficulties using) any Cypress product, call one of the numbers listed below.

| Country    | Toll- Free Number | Country     | Toll-Free Number   |

|------------|-------------------|-------------|--------------------|

| N. America | 1-800-419-1481    | Japan       | 0031-11-1731       |

| Australia  | 0014-800-125-203  | Korea       | 008-1-800-942-8203 |

| Belgium    | 11-8729           | Netherlands | 06-022-5303        |

| Denmark    | 8001-0413         | Norway      | 050-12068          |

| Finland    | 9800-10065        | Singapore   | 800-1758           |

| France     | 05-90-1251        | Spain       | 900-99-1163        |

| Germany    | 0130-81-1902      | Sweden      | 020-795-637        |

| Hong Kong  | 800-7214          | Switzerland | 045-05-8808        |

| Israel     | 00-17-942-1803    | UK          | 0800-89-7339       |

| Italy      | 1678-97-034       |             |                    |

## Chapter 2

#### Warp3 Tools

#### **About This Chapter**

#### Overview

Warp3 comprises a set of tools for creating and synthesizing designs for programmable logic devices. This chapter describes each tool in the set. The tools are discussed in their typical order of use.

#### 2.1. Starting Warp3

To start Warp3 from an IBM PC or compatible, double-click on the Warp3 icon from the Windows program manager.

To start Warp3 from a Unix workstation, type "powerview &<CR>" from the command line of a shell window.

Figure 2-1 shows the *Warp3* icon in the Windows Program Manager. Double-clicking on this icon brings up the *Warp3* program group. Double-clicking on the Cockpit icon within this group brings up the Workview PLUS Cockpit.

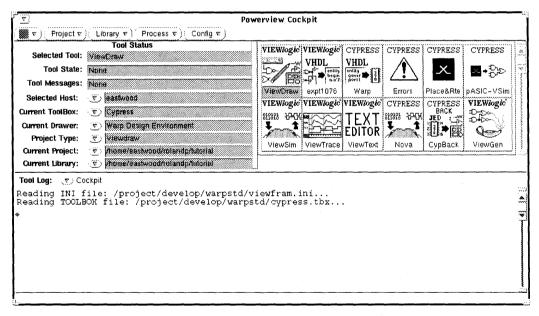

Typing the powerview command on a Unix workstation brings up the Powerview Cockpit.

Figure 2-1. Warp3 icon (IBM PCs and compatibles)

#### 2.2. The Cockpit

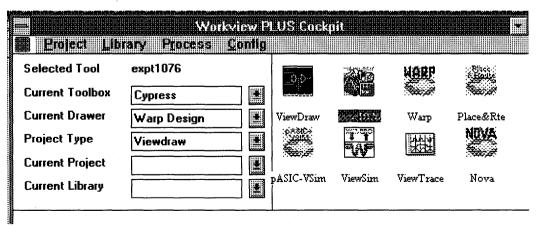

The Cockpit is the central access point for all Warp3 tools.

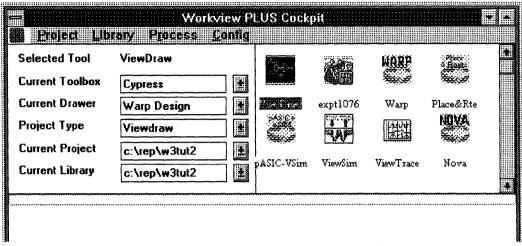

Figure 2-2 shows the Workview PLUS cockpit, which appears when you invoke *Warp3* on IBM PCs and compatibles. Figure 2-3 shows the Powerview Cockpit, which appears when you invoke *Warp3* on Unix workstations.

The main feature of the Cockpit is a collection of icons in the area to the upper right. This area contains one icon for each *Warp3* tool. To start a tool, double-click on its icon.

Other features of the Cockpit include:

- the Red Square menu in the upper left corner, which contains items that provide access to operations common to all ViewLogic tools;

- 2. four pull-down menus (Project, Library, Process, and Config), which contain items that provide access to project and library management commands;

- 3. the Tool Status area (left-half of the Cockpit, below the Red Square and pull-down menus), which provide a convenient way to set the current toolbox, drawer, project type, project, and library; and

- 4. the message area (bottom portion of the Cockpit), where messages from the various tools appear.

Figure 2-2. Workview PLUS cockpit (IBM PCs and compatibles)

Figure 2-3. Powerview cockpit (Unix workstations)

The following pages discuss several topics related to the Cockpit that you should know about in order to use *Warp3*:

- 1. the Current Project;

- 2. the Search Order; and

- 3. the Warp Design and Circuit Design drawers. (These are named the Warp Design Environment and Digital Circuit Design drawers, respectively, when using *Warp3* on Unix workstations.)

For additional information about the Cockpit, refer to *Using Workview Plus on Windows* or *Using Powerview*, from the Viewlogic documentation set.

#### 2.2. The Cockpit

#### 2.2.1. The Current Project

The Current Project is the directory where Warp3 expects to read input from and write output to.

Warp3 is easiest to use when each project is contained in its own directory. Therefore, whenever you start a new design, you should create a new project directory for it.

The current project has no relationship to the directory that you started *Warp3* from. It must be specified separately.

#### To create a new project:

- 1. Choose the **Create** menu item under the **Project** menu.

- 2. Enter a project pathname.

- 3. Click on **OK**. The software reports "Project < name > created successfully."

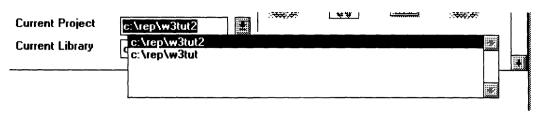

#### To change the current project:

- 1. Click on the arrow next to **Current Project**.

- 2. Select a project from the list (Figure 2-4).

Figure 2-4. Setting the Current Project (IBM PCs and compatibles)

For more information about the Current Project, see *Using Workview Plus on Windows* or *Using Powerview*, from the Viewlogic documentation set.

#### 2.2. The Cockpit

#### 2.2.2. The Search Order

The Search Order is the sequence of directories that *Warp3* searches to find symbols for components instantiated in Viewdraw schematics.

From time to time, you may want to change the search order for a project. For example, you may develop your own library of components that you want to make available for use in a particular schematic.

#### On IBM PCs or Compatibles:

To change the search order for the current project:

- 1. Select Search Order from the Project menu in the Cockpit. The Search Order dialog box appears.

- 2. To edit a search order entry, click on a line in the Search Order dialog box, then click on the Edit... button. When a new dialog box appears, set the directory's type and modify the path or the library name as needed, then click on OK.

- 3. To insert a new search order entry, click on a line in the Search Order dialog box, then click on the Insert Before... button. When a new dialog box appears, set the new directory's type, enter the path, then enter the name of the new library, then click on OK. The new library will be inserted before the highlighted line.

- 4. To add an entry to the end of the search order list, click on the Append... button. When the dialog box appears, set the new directory's type, enter the path, then enter the name of the new library, then click on OK. The new library will be added at the end of the search order.

5. To delete an entry from the search order, click on a line in the Search Order dialog box, then click on the Delete... button.

Click on OK in the Search Order dialog box to accept the changes. Click on Cancel to return to the Cockpit without changing the Search Order.

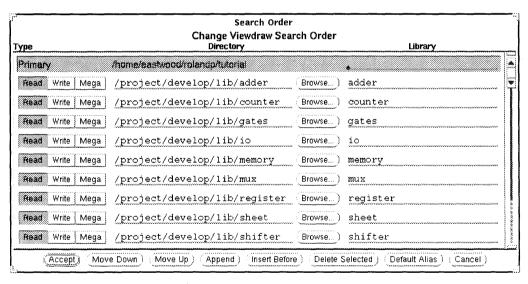

#### On Unix Workstations:

To change the search order for the current project:

- 1. Select Search Order from the Project menu in the Cockpit. The Search Order dialog box appears.

- 2. To edit a search order entry, click on a line in the Search Order dialog box, then click on the field you want to edit.

Figure 2-5. Search Order dialog box (Unix workstations).

- 3. To insert a new search order entry, click on a line in the Search Order dialog box, then click on the Insert Before button. A new blank line appears in the Search Order dialog box. Set the new directory's type, enter its path, and enter the name of the new library on this line.

- 4. To add an entry to the end of the search order list, click on the Append button. A new blank line appears at the end of the Search Order dialog box. Set the new directory's type, enter its path, and enter the name of the new library on this line.

- 5. To delete an entry from the search order, click on a line in the Search Order dialog box, then click on the Delete Selected button.

- 6. To move an entry higher in the search order, click on the entry, then click on the Move Up button.

- 7. To move an entry lower in the search order, click on the entry, then click on the Move down button.

Click on Accept in the Search Order dialog box to accept the changes. Click on Cancel to return to the Cockpit without changing the Search Order.

For more information about the Search Order, see *Using Workview Plus on Windows* or *Using Powerview*, from the Viewlogic documentation set. See also *Schematic Design User's Guide* from the Viewlogic documentation set.

#### 2.2. The Cockpit

#### 2.2.3. The Warp Design and Circuit Design Drawers

The Cockpit contains two "drawers," or collections of tools. The Warp Design drawer contains the tools most commonly used with *Warp3*. The Circuit Design drawer contains all the tools in the *Warp3* tool set.

Most often, you will be able to get by using only tools from the Warp Design drawer. The complete suite of tools in the Circuit Design drawer is provided for specialized uses.

#### 2.3. ViewDraw

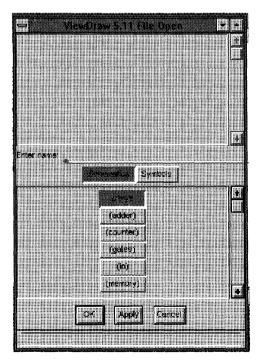

ViewDraw is a hierarchical design entry editor for easy input of schematics or symbols.

ViewDraw is a Viewlogic tool found in both the Warp Design and Circuit Design drawers. ViewDraw is used to create schematics, as well as symbols that can be instantiated in other schematics.

ViewDraw takes as input either the name of a schematic or the name of a symbol. On IBM PCs and compatibles, you specify whether the input is a schematic or symbol by means of the -sym or -sch option on the command line. On Unix workstations, you specify the same thing in the ViewDraw dialog box. The output from a "File=>Write" command is the data for the schematic or symbol window stored in a database, and for schematics a wirelist description file (.wir).

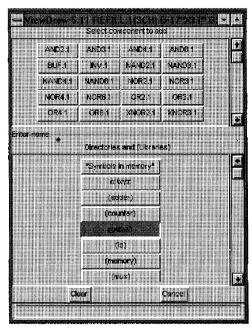

To run ViewDraw, double-click on the ViewDraw icon in the Cockpit. The ViewDraw File Open window will be displayed. Select whether you would like to edit a "Schematic", or "Symbol", and which library the schematic or symbol resides in. Now select the file to open from the list of files displayed, or enter a name on the "Enter name:" line. Double-clicking on the "Accept" button will bring up the ViewDraw Window. Make the desired modifications to the schematic, or symbol. Use the "File=>Write" command to write out the modifications to the database, check the schematic, and create a wirelist file. Selecting "Quit viewdraw..." from the Red Square menu will exit you from ViewDraw.

For additional information on ViewDraw, refer to the "ViewDraw Reference Manual" of the ViewLogic documentation set.

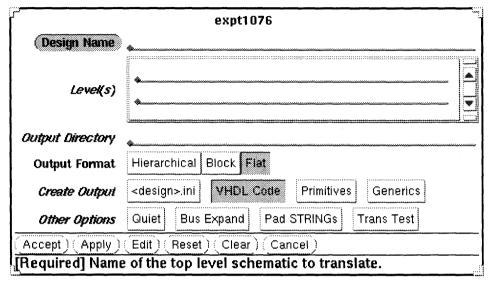

#### 2.4. expt1076

Expt1076 translates the ViewDraw schematic design into one or more VHDL models.

Expt1076 is found in both the Warp Design and Circuit Design drawers. This program translates ViewDraw designs into one or more VHDL models. Expt1076 can produce VHDL output in a hierarchical, flattened, or block structure format. The only output format currently supported by *Warp* is the flattened output format. This is the default setting for expt1076.

Expt1076 takes as input the name of the design to translate and produces a file with the name matching the VHDL entity name and the extension ".vhd".

To run expt1076, select the expt1076 icon from the Cockpit. Enter the name of the ViewDraw design to be translated.

Double-clicking on the "expt1076" icon does not run the ViewLogic tool of that name, but instead runs a sequence of Cypress-created tools that perform the same function.

For additional information about expt1076 consult the VHDL Reference Manual, Chapter 7, of the Viewlogic documentation set.

Figure 2-6. Dialog box for Expt1076 tool (Unix workstations).

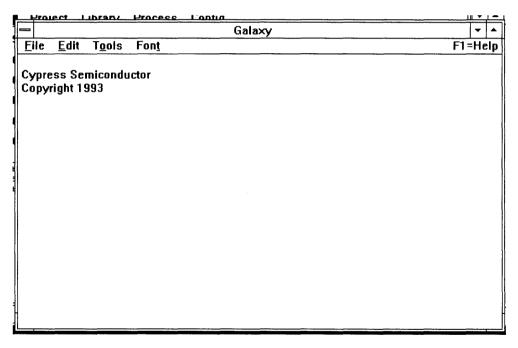

#### 2.5. Galaxy

Galaxy is the graphical user interface for Warp, Warp3's VHDL compilation and synthesis tool.

Galaxy comes up when you double-click on the *Warp* icon from within the Workview PLUS Cockpit (on IBM PCs and compatibles) or the Powerview Cockpit (on Sun workstations).

For complete information on Warp and Galaxy, see the Warp Synthesis Compiler Manual.

## 2.6. Warp

Warp is Warp3's VHDL compilation and synthesis tool.

Warp takes a VHDL description of a circuit as input. Warp produces JEDEC file (used for programming PLDs), HEX files (used for programming PROMs), or QDIF file (used by the SpDE tools when targeting pASICs).

For complete documentation of Warp, see the Warp Synthesis Compiler Reference Manual.

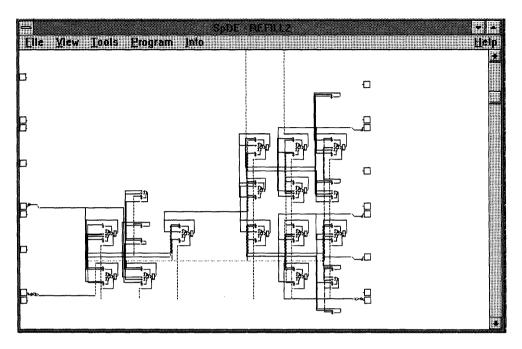

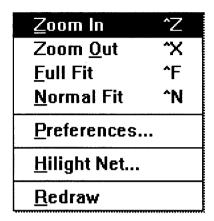

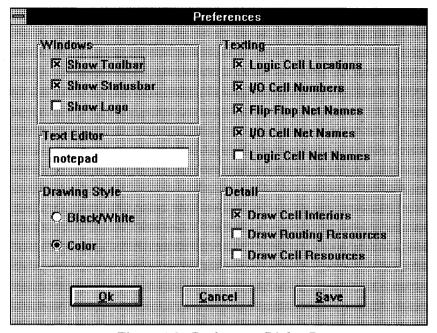

#### 2.7. Place & Rte

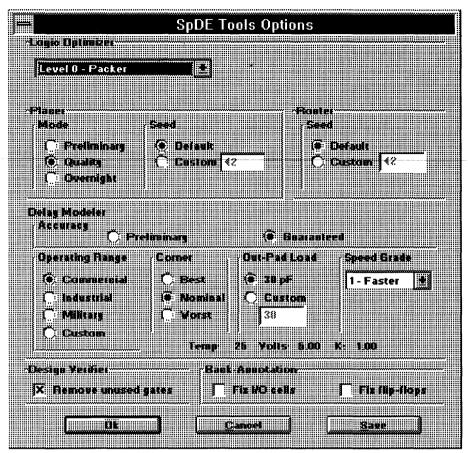

The "Place&Rte" tool is used to process a QDIF file in order to target programmable ASICs (pASICs). This tool is used to perform automatic place and route, delay modeling, critical-path timing analysis, automatic test vector generation, and device programming and test.

The "Place&Rte" tool is a tool provided by QuickLogic found in both the Warp Design and Circuit Design drawers. This tool is used to perform automatic place and route, delay modeling, critical-path timing analysis, automatic test vector generation, and device programming and test.

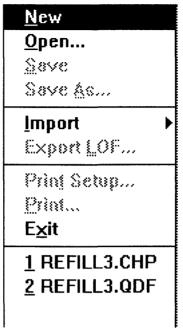

"Place&Rte" takes as input a QDIF file generated by Warp, and produces .atr (design attribute file), .dtb (delay information), .var (delay information), and .vl (x-platform ASCII) files. If a save is done on the SpDE run a .chp file will also be produced.

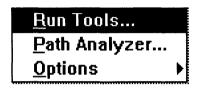

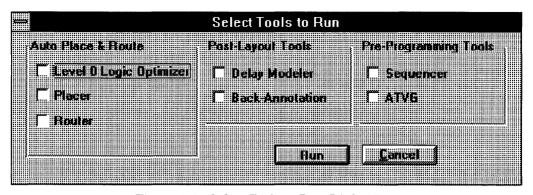

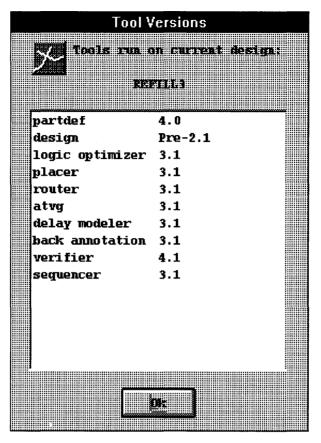

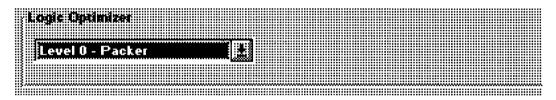

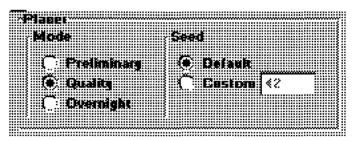

To run SpDE, double-click on the "Place&Rte" icon. The SpDE window fills the screen. Load the QDIF file into SpDE by clicking on SpDE's **File** menu and selecting **Import QDIF**. Select the QDIF file you wish to run SpDE on and click on "OK". Click the **Tools** menu and select **Run All Tools**.

To create a .LOF file to program a part after all SpDE tools have been run, select File/Export/LOF, supply a file name in the dialog box, then click on "OK".

WARNING

Do NOT use the Program menu in the SpDE window to attempt to program parts! The correct procedure in *Warp3* is to create a .LOF file and transfer it to your device programmer, as described in this section.

Figure 2-7. SpDE window.

SpDE creates the .LOF file, then asks if you would like to create a compressed version of it. (.LOF files can be rather large.) If you reply "Yes", a compressed version is created if you have a copy of the PKZIP program installed on your computer; otherwise you simply return to the main SpDE window.

(Data I/O's Unisite device programmer, as well as other popular third-party programmers, can read the ZIPped version of the .LOF file. Some device programmers cannot. Check the documentation that comes with your device programmer to be sure.)

For more information about the SpDE tools, see the SpDE/Warp System User's Manual, included in this documentation set.

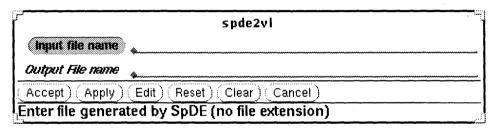

## 2.8. pASIC-VSim

The "pASIC-VSim" tool reads the output information from a SpDE Place&Rte operation and generates a Viewsim simulation file.

The pASIC-VSim tool is a QuickLogic tool found in both the Warp Design and Circuit Design drawers. This tool is used for generating WIR files that can be used in Viewlogic.

The pASIC-VSim tool takes as input a file generated by SpDE and produces a new WIR file, that can be used by Viewsim.

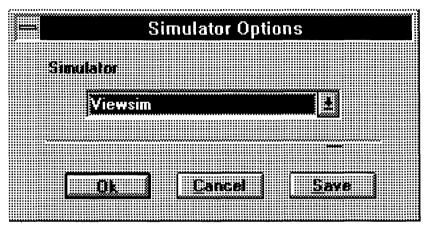

To run pASIC-VSim, double-click on the "pASIC-Vsim" icon in the Cockpit and enter a file name. Selecting "OK" runs the tool.

# On IBM PCs and Compatibles

When you invoke pASIC-VSim on an IBM PC or compatible computer, it brings up a dialog box that prompts you to enter a command line. The command line options you can use are as follows:

**input file name** The name of the file generated by SpDE,

without any extension.

output file name Optionally enter a file name for the new

WIR file, without any extension.

When you invoke pASIC-VSim on a Unix workstation, it brings up a dialog box (Figure 2-8) that lets you set options for spde2vl's execution. Options you can set are as follows:

**Input file name** Enter the name of the file generated by

SpDE, without the file extension.

Output File name Optionally enter a file name for the new

WIR file, without the file extension.

Figure 2-8. Dialog box for pASIC-VSim tool (Unix workstations).

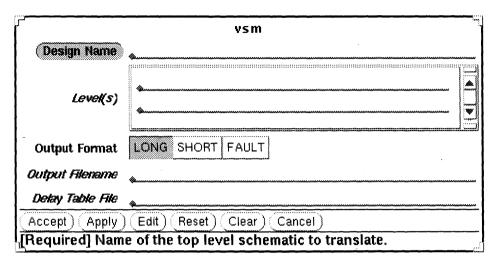

#### 2.9. vsm

Vsm creates a flattened netlist description of a structural design for logic simulation with Viewsim.

Vsm is a Viewlogic tool for taking a WIR file and translating it into a ViewSim netlist. This tool is found in both the Warp Design and Circuit Design drawers.

Vsm takes as input the name of the top level schematic to translate and produces a flattened netlist file (.vsm) for logic simulation with Viewsim.

To run **vsm**, double-click on the **vsm** icon in the cockpit. Enter the name of the schematic to translate and select **OK**. When vsm has completed running the window header will change to (Inactive vsm). To exit the window, select **Close** from the system window menu.

For additional information on vsm, refer to the "ViewSim Wirelisting" chapter of the "ViewSim Reference Manual" in the Viewlogic documentation set.

# On IBM PCs and Compatibles

When you invoke **vsm** on an IBM PC or compatible computer, it brings up a dialog box that prompts you to enter a command line. The command line options you can use are as follows:

| design name     | Specifies the name of the top level schematic to translate.     |

|-----------------|-----------------------------------------------------------------|

| <level></level> | Optional list of levels to descend to.                          |

| -f              | Directs wirelist output into a file other than design name.vsm. |

| -h         | Generates full hierarchical net name equivalences in the wirelist, allowing you to observe simulation values of logically equivalent nets at any level in the design hierarchy. This is the default. |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -s         | Performs the function complementary to the <b>-h</b> option: all nets are referred using the netname of the top level net as it appears in the design.                                               |

| - <b>v</b> | Specifies the name of a variable definition file which contains a list of parameterized attribute definitions.                                                                                       |

| -W         | Generates a flattened connectivity (\WIR file format) description of the design.                                                                                                                     |

| -t         | Specifies that the wire list is to include additional records specifically for fault simulation.                                                                                                     |

| -d         | Specifies the name of a delay back-annotation table file with the default extension .dtb.                                                                                                            |

When you invoke **vsm** on a Unix workstation, it brings up a dialog box (Figure 2-9) that lets you set options for vsm's execution. Options you can set are as follows:

**Design Name** Specify the name of the top level schematic to translate.

Level(s)

The Level string(s) list the LEVELs to descend to. The LEVEL string(s) are matched against LEVEL attributes on symbols in your schematic design. Any symbol with a matching string will be treated as a primitive.

**Output Format**

This options tells the netlister which output format to use. LONG generates full hierarchical net name equivalences in the wirelist. SHORT generates net names that refer to the top level net name. FAULT specifies that the wire list is to include additional records specifically for fault simulation.

Output Filename

Optionally specify the name of the output file. No extension should be specified since **.vsm** will be added.

Delay Table File

Optionally specify the name of the delay back-annotation table file, with the default extension .dtb.

Figure 2-9. Dialog box for vsm tool (Unix workstations).

#### 2.10. ViewSim

ViewSim is a high-capacity, full-timing simulator and (optional) debugger.

ViewSim is Viewlogic's powerful simulator designed to maximize the development and test environment. This tool can be found in both the Warp Design and Circuit Design drawers.

ViewSim will take as input either a .vsm file produced by the wirelister vsm, or .vsm and .vli files produced by the VHDL Analyzer when simulating an isolated behavioral model. ViewSim also accepts user-generated command files or command files created by ViewTrace. After the wirelist has been simulated, ViewSim outputs a waveform data stream (.wfm) for ViewTrace, simulation log file, and screen display information.

To run ViewSim, double-click on the ViewSim icon. Enter the design name and optionally the command file name on the command line. Select "OK". After the simulation has completed running you can use "Quit WVSim...", from the Red Square Menu to exit from ViewSim.

For additional information on ViewSim, refer to the "ViewSim Reference Manual", of the Viewlogic documentation set.

# On IBM PCs and Compatibles

When you invoke ViewSim on an IBM PC or compatible computer, it brings up a dialog box that prompts you to enter a command line. The command line options you can use are as follows:

design name

Specify the name of the network file for your design.

-cmdfile Name of a command file to run on startup.

**-nographics** Disables the graphical interface to the

ViewSim simulator.

**-nofault** Disables capture of a fault simulation

license.

**-nodebug** Disables the VHDL debugging com-

mands.

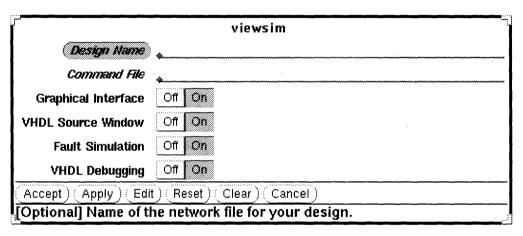

#### On Unix Workstations

When you invoke ViewSim on a Unix workstation, it brings up a dialog box (Figure 2-10) that lets you set options for ViewSim's execution. Options you can set are as follows:

**Design Name** Specify the name of the network file cor-

responding to the level at which you netlisted. If no filename extension is sup-

plied, .vsm is assumed

Command File The command file can specify any of the

simulation commands that would be issued during a simulation load/run.

Graphical Inter-

face

This option enables or disables the graphical interface to the ViewSim simulator

VHDL Source

Window

This window is used to display the VHDL source code while editing and debugging.

Fault Simulation This option instructs the simulator

whether to capture a fault simulation license at startup. If disabled, another attempt will be made when the first fault

simulation command is issued.

VHDL Debugging This option enables or disables the VHDL

debugging commands.

Figure 2-10. ViewSim Dialog Box on Unix workstations.

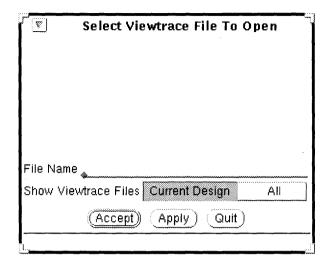

#### 2.11. ViewTrace

ViewTrace is a graphical waveform analysis tool that directly ties to ViewDraw and ViewSim.

ViewTrace is Viewlogic's waveform analyzer tool. This tool is found in both the Warp Design and Circuit Design drawers.

ViewTrace enables you to read, display and process simulation results. ViewTrace takes as input a digital waveform stream file (.wfm), produced by ViewSim, and outputs a ViewSim command file (.cmd).

You will usually start ViewTrace by executing a wave command from Viewsim. To run ViewTrace by itself, double-click on the ViewTrace icon. Enter the name of the waveform file on the command line or select a file to open from the ViewTrace file selection dialog box. Perform the analysis on the displayed waveform using the available ViewTrace commands. Exit ViewTrace by selecting "Quit VIEWTRACE..." from the Red Square menu.

For additional information on ViewTrace, refer to the "ViewTrace User's Guide" in the Viewlogic documentation set.

Figure 2-11. ViewTrace Dialog Box, Unix Workstations.

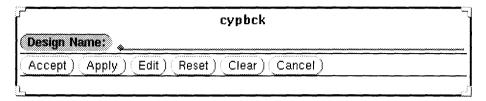

## 2.12. CypBack

CypBack back annotates pin assignment information added to the design during compilation and synthesis.

CypBack is a Cypress tool found in both the Warp Design and Circuit Design drawers. CypBack takes the pin assignment information found in either the .vhd file produced by Warp, or the .atr file produced from running Place and Route and writes the pin assignment information back to the schematic.

CypBack will modify the original schematic, adding the pin number attribute to the specified input and output ports. To view the new attributes select File/Read from the ViewDraw window and re-read the schematic.

To run CypBack, select the CypBack icon from the Cockpit and specify the design to back-annotate to.

# On IBM PCs and Compatibles

When you invoke CypBack on an IBM PC or compatible computer, it brings up a dialog box that prompts you to enter a command line. You need enter no command line options to run CypBack. Make the command line read "CYPBCK <schematicname>", then click on "OK".

# **On Unix Workstations**

When you invoke CypBack on a Unix workstation, it brings up a dialog box (Figure 2-12) that lets you set options for CypBack's execution. Options you can set are as follows:

Design Name

enter the name of the design to be back-

annotated

Figure 2-12. Dialog box for CypBack tool (Unix workstations).

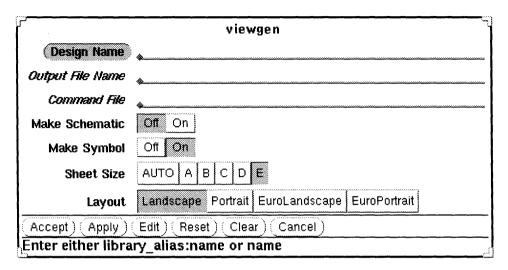

#### 2.13. ViewGen

In Warp3, ViewGen generates symbols from schematic drawing.

ViewGen is a Viewlogic tool found in both the Warp Design and Circuit Design drawers.

In Warp3, you would use ViewGen to generate a symbol for a circuit from a schematic. The resulting symbol could then be instantiated in other, higher-level schematics.

To run ViewGen in *Warp3* on IBM PCs and compatibles, double-click on the ViewGen icon, enter the name of the WIR file, followed by the arguments "-makesym" and "-noschem", then click on "OK".

To run ViewGen in *Warp3* on Unix workstations, double-click on the ViewGen icon, enter the name of the WIR file, make sure that "Make Schematic" is OFF and "Make Symbol" is ON, then click on "OK".

For additional information on ViewGen, refer to the "ViewGen Reference Manual" found in Viewlogic's online documentation set.

# On IBM PCs and Compatibles

When you invoke ViewGen on an IBM PC or compatible computer, it brings up a dialog box that prompts you to enter a command line. Command line options required in *Warp3* are:

**-makesym** Specifies that a top level symbol should be

created for the design.

**-noschem** Specifies that the generation of a sche-

matic should be inhibited.

When you invoke ViewGen on a Unix workstation, it brings up a dialog box (Figure 2-13) that lets you set options for ViewGen's execution. Options you can set are as follows:

**Design Name** En

Enter either library\_alias:name or the

name of the WIR file.

Output File Name

Optionally enter an output file name.

Command File

Optionally enter a command file name.

**Make Schematic**

Set to "OFF" to suppress schematic gener-

ation.

Make Symbol

Set to "ON" to generate a symbol for the

design.

**Sheet Size**

Does not apply in Warp3.

Layout

Does not apply in Warp3.

Figure 2-13. Dialog box for ViewGen tool (Unix workstations).

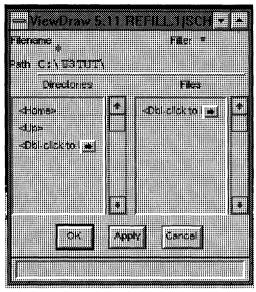

#### 2.14. ViewText

# ViewText is Viewlogic's ASCII text editor.

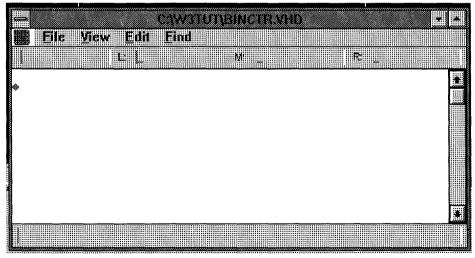

ViewText is a Viewlogic tool for editing an ASCII text file. This tool is available in both the Warp Design and Circuit Design drawers on Unix Workstations. On IBM PCs and compatibles, ViewText is available from most tool windows through the Red Square menu, except the Workview PLUS cockpit.

ViewText allows you to edit VHDL files, configuration files and initialization files. To run ViewText, double-click on the ViewText icon. Select the desired file from the ViewText file list window and click on "OK" ("ACCEPT" on Unix Workstations). This brings up the text editing window. To exit ViewText, select "Dismiss Window" from the Red Square menu.

One of the nice features of the *Warp3* text editor is the command "File=>VHDL to Symbol". This command will take the VHDL file being edited and translate it into a symbol.

For additional information on ViewText, refer to the chapter entitled, "Text Editing with ViewText", in "Using Workview PLUS," or "Using Powerview," in the Viewlogic documentation set.

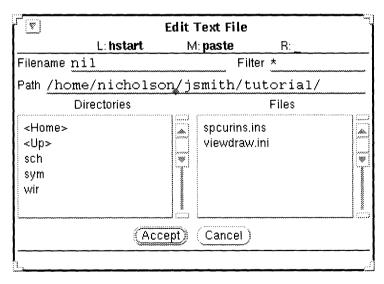

When you invoke ViewText on a Unix workstation, it brings up a dialog box (Figure 2-14) that lets you specify the file name for ViewText's execution. Options you can set are as follows:

**Filename** The name of the file to edit.

**Filter** Use the filter to specify the names to be

displayed in the Files list.

**Path** The full path of the current working direc-

tory.

**Directories** List of directories available in the current

working directory.

Files List of files available in the specified

directory.

Figure 2-14. Dialog box for ViewText tool (Unix workstations).

# On IBM PCs and Compatibles

The ViewText tool is not available from the Cockpit on the PC versions of *Warp3*. To access ViewText when working on an IBM PC or compatible, do the following:

- 1. Select and open one of the Viewlogic tools available in the cockpit.

- 2. From the Red Square menu of the selected tool, use the "Edit text file" command.

## 2.15. vhdl->sym

The vhdl->sym translator utility converts a VHDL model into a ViewDraw symbol.

Vhdl->sym is a Viewlogic tool that can be found in the Circuit Design drawer. The 'VHDL to Symbol' translator analyzes a VHDL model and automatically generates a symbol. You can confirm the correctness of the VHDL model by executing the VHDL Analyzer before executing vhdl->sym.

Vhdl->sym takes as input the name of either a VHDL source file or a library and translates each VHDL model into a ViewDraw symbol. The symbol name and the filename will have the same name as the VHDL entity name with an extension of ".1".

For additional information about vhdl->sym, refer to the VHDL Reference Manual, Chapter 8, in the Viewlogic documentation set.

# On IBM PCs and Compatibles

When you invoke vhdl->sym on an IBM PC or compatible computer, it brings up a dialog box that prompts you to enter a command line. The command line options you can use are as follows:

| VHDLfile[.ext]    | Specify the name of the VHDL source code file to be translated. If no filename extension is supplied, .vhd is used. |

|-------------------|---------------------------------------------------------------------------------------------------------------------|

| -l input_library  | The <b>-l</b> option directs vhdl2sym to translate all VHDL models in the specified library.                        |

| -d output_library | Specifies a library to write the output file (symbol) to.                                                           |

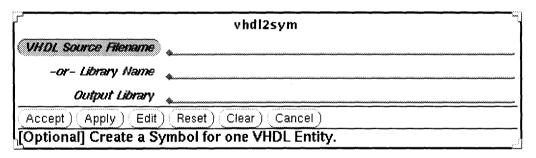

When you invoke vhdl->sym on a Unix workstation, it brings up a dialog box (Figure 2-15) that lets you set options for vhdl2sym's execution. Options you can set are as follows:

VHDL Source

Filename

Specify the name of the VHDL source code file for translation. If no filename extension is supplied, vhd is used.

-or- Library Name

Specify the name of the library of VHDL source code files.

Output Library

Use this field to specify a library to write the output file (symbol) to. If not filled in, output goes to the library used or to the primary library.

Figure 2-15. Dialog box for vhdl->sym tool (Unix workstations).

#### 2.16. Errors

The Warp Error Tracker highlights the line of text in the VHDL file that contains the error.

The Errors tool is a Cypress-created tool for highlighting errors found by *Warp* back to the VHDL file. This tool is found in both the Warp Design and Circuit Design drawers, on Unix versions of *Warp3* only.

Errors takes as input a .ver file produced by Warp. This file is used to highlight the identified errors back to the specified .vhd file.

To run the Warp Error Tracker select the Errors icon from the Cockpit. Enter the name of the error file you wish to view (file\_name.ver). From the Alert box select the error line you would like to correct. Selecting the "Visit (Next)" button will invoke the ViewText editor with the error highlighted in the .vhd file. Selecting the "Continue" button will return you to the Warp Error Tracker dialog box.

## **On Unix Workstations**

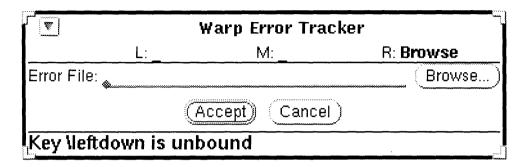

When you invoke the *Warp* Error Tracker on a Unix workstation, it brings up the dialog box shown in Figure 2-16.

Enter the name of the error file you wish to view on the line labeled "Error File", then click on Accept. Clicking on Browse allows you to search the directory structure for error files to view. Clicking on Cancel cancels the operation.

Figure 2-16. Dialog box for the Warp Error Tracker (Unix workstations).

# On IBM PCs and Compatibles

The Errors tool is not provided on PC versions of *Warp3*. To locate sources of errors when working on an IBM PC or compatible, do the following:

- 1. Bring up ViewDraw and select the Red Square Menu.

- 2. From the Red Square Menu select "Help=>Track Errors from file...". This will bring up a dialog window asking for the name of the Error File. Warp creates a .err file if there were errors found in the VHDL file.

- 3. Enter the name of the error file (*file\_name.err*). The "Browse..." button may also be used to select an error file from a list of error files. Selecting OK will bring up the Alert box with the list of errors.

- 4. Select the error to view and choose the "Visit (Next)" button. This will bring up the ViewText editor with the error line highlighted.

## 2.17. analyzer

The analyzer reads behavioral models in the form of VHDL source files, and produces an intermediate format file which ViewSim interprets to simulate behavioral models.

The **analyzer** is a Viewlogic tool that can be found in the Circuit Design drawer. This tool reads a VHDL source file, checks for errors, and creates the following files:

- 1. A listing file (source\_file.lis) which indicates the location of errors in the source file. This file is always created.

- 2. An intermediate format file (source\_file.vli). The intermediate format file is a functional description required by ViewSim. This file is only created if no errors occurred during analysis.

- 3. Optionally, the analyzer can create a netlist file (source\_file.vsm) of a single instantiation of the model, allowing simulation of the isolated model.

- 4. An error message file (source\_file.elf) which is used by the source level debugger to step through the error and warning messages that were issued by the analyzer.

The analyzer can be invoked from the Cockpit by selecting the analyzer icon. It can also be accessed from a ViewSim window, using the Analyze command button, or it can be invoked as a stand-alone program directly from the operating system.

The analyzer is not needed when targeting pASICs, because pASIC->VSim creates the .vsm file. Additionally, the analyzer is run automatically when you check the "Create Viewsim Model" box in *Warp*.

For additional information on the Analyzer, refer to the VHDL User's Guide, Chapter 3, in the Viewlogic documentation set.

# On IBM PCs and Compatibles

When you invoke the analyzer on an IBM PC or compatible computer, it brings up a dialog box that prompts you to enter a command line. The command line options you can use are as follows:

-e[rrlevel]=

3-Error reporting

2-Error, warning reporting

1- Error, warning, extension reporting

0-Error, warning, extension, note

reporting

-d[ebug]

This options adds source level debugging

code (default: debugging disabled)

-n[ocheck]

This option specifies: No array bounds

violation checking (default: checking

enabled)

**-p**[ath]=<dir>

Search <dir> for .msg, .ini

-v[sm]

Generate ViewSim wirelist (default: no

wirelist generated)

-w[ork]=<library>

Equate library WORK with < library>

(default: WORK = <default dir>)

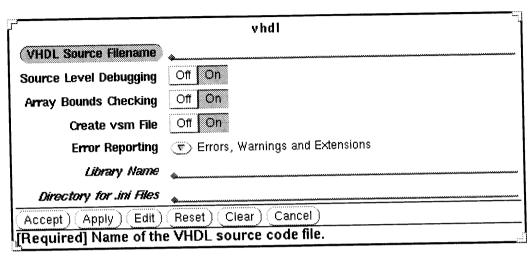

When you invoke the analyzer on a Unix workstation, it brings up a dialog box (Figure 2-17) that lets you set options for the analyzer's execution. Options you can set are as follows:

| <b>VHDL</b> | Source |

|-------------|--------|

| Filenan     | ne     |

Specify the name of the source file.

# Source Level Debugging

Turning this value ON instructs the analyzer to record line numbers from the source file in the intermediate (.vli) file.

# Array Bounds Checking

Turning this value ON instructs the analyzer to add extra code which ensures that array references are always within the defined bounds. This option should not be turned OFF until the model has been fully tested and debugged.

#### Create vsm File

This option tells the analyzer to create a ViewSim wirelist file which has the base name of your model and the extension VSM. This netlist can be used to simulate your model in isolation without entering ViewDraw to create a symbol and enclosing schematic for your model. The network contains one instance of the analyzed behavioral model; each port of the model is connected to a net of the same name.

## **Error Reporting**

This option selects the kinds of errors to report. The choices are:

- Errors

- Errors and Warnings

- Errors, Warnings and Extensions

- Errors, Warnings, Extensions and Notes

## Library Name

This option is used to specify the name of the library where this model resides. If the analyzer can not find the source file in the local directory, it searches the specified library. (The library name must match a Viewdraw library.) If a library name is NOT specified, AND the analyzer does not find the source code file in the local directory, each of the Viewdraw project libraries are searched sequentially.

## Directory for .ini Files

This option is used to specify the path name of a directory containing the files workview.ini and viewdraw.ini. If a path is not specified, the analyzer searches (in order) the current directory and the directories specified by the WDIR environment variable. If a path is specified, the analyzer searches the current directory and then the specified path.

Figure 2-17. Dialog box for analyzer tool (Unix workstations).

#### 2.18. ViewNav

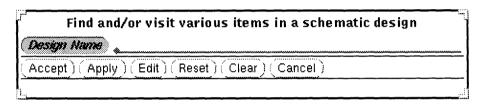

ViewNav allows the user to find and/or visit various objects in a schematic design.

ViewNav is a Viewlogic tool found in the Circuit Design drawer. ViewNav allows the user to find objects within a ViewDraw design or between ViewDraw and another tool. An "object" can be a net, component, pin, or refdes (reference designator).

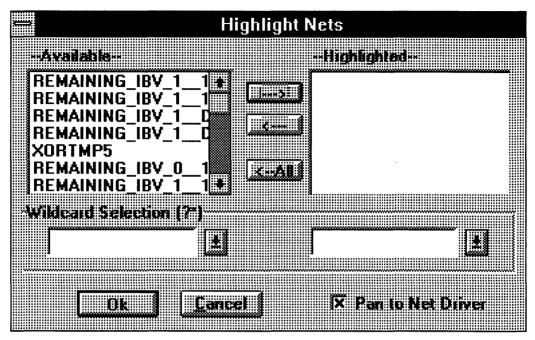

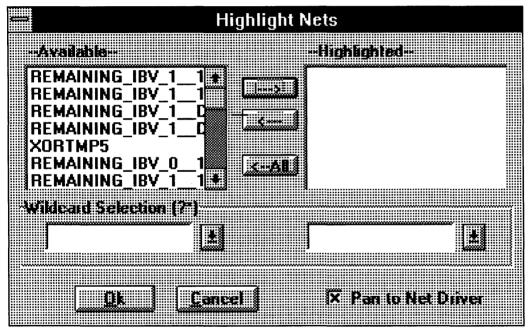

ViewNav takes as input the name of the design you wish to navigate through. It will query you as to how you want to search the design and use this information to highlight items in the schematic design.

To run ViewNav, double-click on the ViewNav icon. Enter the design name you wish to navigate and select "Accept". (Note: ViewDraw must be running, and the schematic you wish to navigate through should be loaded.)

The ViewNav top-level window will now be displayed for you to select between searching for objects, tracking errors from an error file, or editing parameters in the preferences window.

To exit the navigator, select "Quit vnav..." from the Red Square menu, and "Accept" from the Quit dialog box.

For additional information on ViewNay, refer to the online documentation section entitled, "Navigator and Cross Prober".

When you invoke ViewNav on a Unix workstation, it brings up a dialog box (Figure 2-18) that lets you set options for ViewNav's execution. Options you can set are as follows:

**Design Name** The name of the design you want to navi-

gate through.

**-co** configfile Optionally, enter the name of a configura-

tion file on the Design Name line.

Figure 2-18. Dialog box for ViewNav tool (Unix workstations).

# On IBM PCs and Compatibles

The ViewNav tool is not provided on PC versions of Warp3.

#### 2.19. check

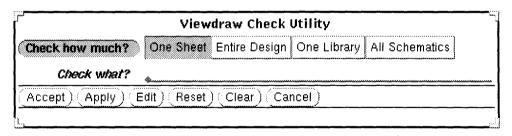

The check utility checks the current sheet or project for minor connectivity violations and creates a wirelist description file.

The check utility is a Viewlogic tool that is found in the Circuit Drawer. It takes either one sheet, the entire design, one library, or all schematics and performs a connectivity check on them.

Running the check utility creates a .wir file and places it in the wir subdirectory. This file contains information such as component type, component label, attributes, and connectivity, as well as any error messages that were reported during the check.

The check utility is automatically run when you write out a schematic in Viewdraw. You may also use the Utils => Check command from the Viewdraw menu, or select the Viewlogic check icon from the Cockpit.

For additional information on the check Utility, see the *ViewDraw Reference Manual*, Appendix B, in the Viewlogic documentation set.

# On IBM PCs and Compatibles

When you invoke the check utility on an IBM PC or compatible computer, it brings up a dialog box that prompts you to enter a command line. The command line options you can use are as follows:

-all

The **-all** option checks all writable schematics in all writable directories in the viewdraw.ini file.

| -f | The <b>-f</b> option (include with only the -l or -p options) retains symbols in memory between checking schematics.           |

|----|--------------------------------------------------------------------------------------------------------------------------------|

| -1 | The -l option checks all projects in the specified library (-l library_alias).                                                 |

| -р | The <b>-p</b> option checks the specified project and underlying hierarchy.(-p project_name)                                   |

| -S | The -s option checks only the specified schematic sheet. If no sheet number is specified, sheet one is checked. (-s project.n) |

| -v | The -v option (include with any option) reports additional check status.                                                       |

When you invoke the check utility on a Unix workstation, it brings up a dialog box (Figure 2-19) that lets you set options for check's execution. Options you can set are as follows:

| One Sheet     | The <b>One Sheet (-s)</b> options checks only the specified schematic sheet. If no sheet number is specified, sheet one is checked. |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Entire Design | The <b>Entire Design (-p)</b> option checks the specified project and underlying hierarchy.                                         |

| One Library   | The <b>One Library</b> (-1) option checks all projects in the specified library.                                                    |

| All Schematics | The All Schematics (-all) option checks all writable schematics in all writable directories in the viewdraw.ini file.                                                                                     |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Check What?    | Specify the <i>project.n</i> for the <b>One Sheet</b> option, specify the <i>project_name</i> for the <b>Entire Design</b> option, or specify the <i>library_alias</i> for the <b>One Library</b> option. |

| -f             | The <b>-f</b> option (include with only <b>-l</b> or <b>-p</b> options) retains symbols in memory between checking schematics.                                                                            |

| -v             | The <b>-v</b> option (include with any option) reports additional check status.                                                                                                                           |

If you click on a check option and then click on **Edit**, you can modify the command line to include the **-f** and **-v** options.

Figure 2-19. Dialog box for check tool (Unix workstations).

#### 2.20. netlist in

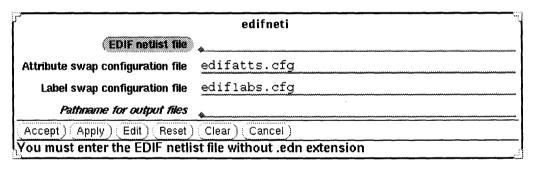

The EDIF Netlist Reader is based on the industry standard EDIF (Electronic Design Interchange Format) to transfer netlist information from other vendor's EDIF translators.

The EDIF Netlist Reader (edifneti) is a Viewlogic tool that is available in the Circuit Design Drawer.

The EDIF Netlist Reader (edifneti) takes as input an EDIF 2 0 0 netlist and produces Powerview WIR files. Its purpose is to provide for connectivity linkage between "foreign" schematic capture systems and Powerview-supported physical design and verification tools.

To run the EDIF Netlist Reader select the "netlist in" icon in the Cockpit and enter the EDIF netlist file name. Clicking on "Accept" invokes the tool.

A word of caution about EDIF file transfers: importing or exporting EDIF files may not pass the entire design description. Libraries used to create the design may be needed in the environment to which the design is transferred.

For additional information, refer to Viewlogic's online documentation under the section entitled "EDIF 2 0 0 Netlister".

### On IBM PCs and Compatibles

When you invoke the EDIF Netlist Reader on an IBM PC or compatible computer, it brings up a dialog box that prompts you to enter a command line. The command line options you can use are as follows:

| <infile></infile>        | Refers to the input EDIF netlist filename.<br>You must specify the filename extension.                                                                                                                               |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -a <filename></filename> | Specifies that the filename is the attribute name/value swap pairs configuration file. The default filename is <b>edifatts.cfg</b> .                                                                                 |

| -l <labmapfn></labmapfn> | Specifies that the labmapfn is the label swap configuration file. The default Label Swap Config File is <b>ediflabs.cfg.</b>                                                                                         |

| -o <outpath></outpath>   | Specifies the output directory where the WIR files are to be written. The default is the WIR subdirectory of DIR 0 as specified in the <b>viewdraw.ini</b> file. Output filename(s) will be generated automatically. |

### **On Unix Workstations**

When you invoke the EDIF Netlist Reader on a Unix workstation, it brings up a dialog box (Figure 2-20) that lets you set options for **edifneti**'s execution. Options you can set are as follows:

| EDIF netlist file                 | Enter the input EDIF netlist filename without the .edn extension                                                            |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Attribute swap configuration file | Enter the name of the attribute name/value swap configuration file if the default, <b>edifatts.cfg</b> , is not being used. |

Label swap con-Enter the name of the label swap configuration file if the default, ediflabs.cfg, is figuration file not being used. Enter the path where the WIR files are to Pathname for output files be written. If the pathname is not speci-

fied, the WIR files will be written to the

primary project directory.

If specified on a Unix platform, the output -u

file names will be written in lowercase.

If you enter the EDIF netlist filename and then click on Edit, you can modify the command line to include the **-u** option.

Figure 2-20. Dialog box for netlist in tool (Unix workstations).

#### 2.21. netlist out

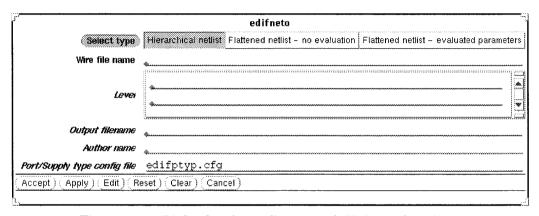

The EDIF Netlist Writer (edifneto) is based on the industry standard EDIF (Electronic Design Interchange Format) to transfer netlist information to other vendor's EDIF translators.

The EDIF Netlist Writer is a Viewlogic tool found in the Circuit Design Drawer.

The EDIF Netlist Writer (**edifneto**) takes as input an up-to-date WIR file and produces a file (the "netlist") that describes the connectivity of a schematic in EDIF 2 0 0 format. This file may then be used as input to a foreign system's EDIF netlist reader.

To run the EDIF Netlist Writer select the **netlist out** icon and either provide the command-line options followed by a selection of the "**OK**" button, or on a Unix Workstation, respond to the dialog box options and click on the "**Accept**" button.

A word of caution about EDIF file transfers: importing or exporting EDIF files may not pass the entire design description. Libraries used to create the design may be needed in the environment to which the design is transferred.

For additional information on the EDIF Netlist Writer, refer to Viewlogic's online documentation under the section entitled "EDIF 2 0 0 Netlister".

### On IBM PCs and Compatibles

When you invoke the EDIF Netlist Writer on an IBM PC or compatible computer, it brings up a dialog box that prompts you to enter a command line. The command line options you can use are as follows:

| -f | Flatten the netlist without evaluating |

|----|----------------------------------------|

|----|----------------------------------------|

attributes.

**-e** Flatten the netlist and evaluate attributes

**project>** The top-level project name.

-l < level> The -l option specifies that the level string

indicates what level the netlist is to stop. Multiple -l command-line options may be used. In that case, the flattener will flatten an instance down to the highest level listed among the provided etripgs.

listed among the provided strings.

**<outfile>** This specifies the output EDIF filename.

The default name is *project*.edn

-a <author> The -a option specifies the author string.

When specifying the *author* string on the command line it must be one string with

no spaces.

-c < filename > The -c option specifies the filename of the

port/supply type of the configuration file.

The default is **edifptyp.cfg**

-n <nameswfp> The -n option specifies the filename of the

name swap configuration file. There is no

default.

-p

The **-p** option specifies that the use of library aliasing, in the naming of cells, within the EDIF file, be inhibited.

### On Unix Workstations

When you invoke **netlist out** on a Unix workstation, it brings up a dialog box (Figure 2-21) that lets you set options for **edifneto**'s execution. Options you can set are as follows:

| Select typ | e |

|------------|---|

|------------|---|

Select between the three ways of extracting the EDIF Netlist. Selecting Hierarchical netlist will produce a hierarchical netlist. Selecting Flattened netlist - no evaluation will produce a flattened netlist without parameterized attribute evaluation. Selecting Flattened netlist - evaluated parameters, will produce a flattened netlist with the evaluation of parameterized attributes.

### Wire file name

Enter the name of the netlist (WIR file) to be translated into the EDIF format.

#### Level

If you do not want the EDIF netlister to flatten down to the lowest level, enter a string representing the level to netlist

down to.

### Output filename

Specify the name of the output file for the EDIF Writer. The default is the Wire file name followed by the **.edn** extension.

**Author name** Optionally enter the author name as one

string to be stored as author string in the

EDIF output file.

Port/Supply type config file

Optionally specify a configurable file other than the default, **edifptyp.cfg**.

Figure 2-21. Dialog box for netlist out tool (Unix workstations).

### 2.22. sym->vhdl

The sym->vhdl translator utility converts a Viewdraw symbol into a VHDL model.

Sym->vhdl is a Viewlogic tool that can be found in the Circuit Design drawer. The 'Symbol to VHDL' translator analyzes a ViewDraw symbol and automatically generates a VHDL model skeleton. The tool can be directed to convert a single symbol or an entire library of symbols into VHDL models.

Sym->vhdl takes as input the name of a symbol, or a library, and translates each ViewDraw symbol into a VHDL file. The VHDL file has the same name as the symbol, except when modification is needed to create a legal VHDL name. The VHDL entity name is the same as the filename (minus the .vhd file extension).

For additional information about sym->vhdl, refer to the VHDL Reference Manual, Chapter 9, in the Viewlogic documentation set.

### On IBM PCs and Compatibles

When you invoke sym->vhdl on an IBM PC or compatible computer, it brings up a dialog box that prompts you to enter a command line. The command line options you can use are as follows:

-i

Write the default initialization file into the working directory. When processing a single symbol, this option creates a *symbol\_name.* ini file. When processing a library, this option creates a *library\_name.* ini file.

-I *library* Writes the VHDL model for all symbols

that exist in the specified library.

-d dir\_name Writes the VHDL model file into the spec-

ified directory. If the directory does not

exist, sym2vhdl will create it.

symbol[.ext] Writes the VHDL model for the symbol,

symbol.ext. If the extension is not speci-

fied, .1 is assumed.

### **On Unix Workstations**

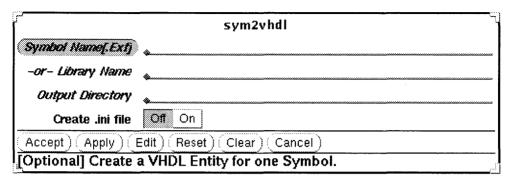

When you invoke sym->vhdl on a Unix workstation, it brings up a dialog box (Figure 2-22) that lets you set options for sym2vhdl's execution. Options you can set are as follows:

Symbol Creates a VHDL entity for one symbol. If

Name[.Ext] the symbol name is not followed by an

extension, .1 is assumed

-or- Library Name Creates VHDL entities for all symbols in

the named library.

Output Directory Use this field to specify a directory to

write the output files to. If not filled in, output goes to the specified library or to

the local directory.

Create .ini file Turning this option "On" instructs the

translator to create a template initialization file which can be edited to control numerous aspects of the translation pro-

cess.

$Figure\ 2\hbox{-}22.\ Dialog\ box\ for\ sym->vhdl\ tool\ (Unix\ workstations).$

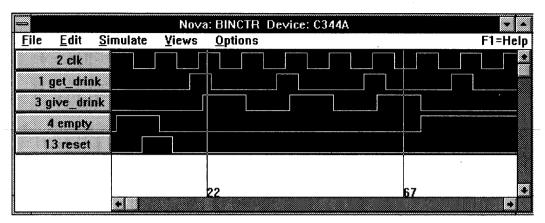

### 2.23. Nova

### Nova is Warp2's functional simulator.

Nova is the functional simulator that comes with Warp2, Cypress Semiconductor's original VHDL compilation and synthesis product. It is included with Warp3 for the sake of compatibility and completeness only. For simulating designs created in Warp3, we recommend use of Viewsim.

## Index

```

Α

analyzer 2-42 thru 2-46

C

check 2-49 thru 2-51

Circuit Design drawer 2-11

Cockpit 2-3 thru 2-11

current project 2-6 thru 2-7

search order 2-8 thru 2-10

Current Project 2-6 thru 2-7

CypBack 2-30 thru 2-31

Cypress Semiconductor

toll-free help numbers 1-13

Devices supported 1-4 thru 1-5

E

Errors 2-40 thru 2-41

expt1076 2-13 thru 2-14

N

netlist in 2-52 thru 2-54

netlist out 2-55 thru 2-58

Nova 2-62

P

Parts libraries 1-11

pASIC-VSim 2-19 thru 2-20

Place & Rte 2-17 thru 2-18

```

```

S

Search Order 2-8 thru 2-10

Starting Warp3 2-2

Sym->vhdl 2-59 thru 2-61

Т

Toll-free help numbers 1-13

V

Vhdl->sym 2-38 thru 2-39

ViewDraw 2-12

ViewGen 2-32 thru 2-34

ViewNav 2-47 thru 2-48

ViewSim 2-25 thru 2-27

ViewText 2-35 thru 2-37

ViewTrace 2-28 thru 2-29

Vsm 2-21 thru 2-24

W

Warp 2-16

Warp Design drawer 2-11

Warp3

design process 1-6 thru 1-9

devices supported 1-4 thru 1-5

starting 2-2

Warp3 process overview 1-1 thru 1-13

Warp3 tools 2-1 thru 2-16

```

## **Warp3**™ VHDL Development System

Tutoria

Cypress Semiconductor 3901 North First Street San Jose, CA 95134

(408)943-2600 JANUARY 1995

### **Cypress Software License Agreement**

- 1. LICENSE. Cypress Semiconductor Corporation ("Cypress") hereby grants you, as a Customer and Licensee, a single-user, non-exclusive license to use the enclosed Cypress software program ("Program") on a single CPU at any given point in time. Cypress authorizes you to make archival copies of the software for the sole purpose of backing up your software and protecting your investment from loss.

- 2. TERM AND TERMINATION. This agreement is effective from the date the diskettes are received until this agreement is terminated. The unauthorized reproduction or use of the Program and/or documentation will immediately terminate this Agreement without notice. Upon termination you are to destroy both the Program and the documentation.

- 3. COPYRIGHT AND PROPRIETARY RIGHTS. The Program and documentation are protected by both United States Copyright Law and International Treaty provisions. This means that you must treat the documentation and Program just like a book, with the exception of making archival copies for the sole purpose of protecting your investment from loss. The Program may be used by any number of people, and may be moved from one computer to another, so long as there is **No Possibility** of its being used by two people at the same time.

- 4. DISCLAIMER. THIS PROGRAM AND DOCUMENTA-TION ARE LICENSED "AS-IS," WITHOUT WARRANTY AS TO PERFORMANCE. CYPRESS EXPRESSLY DIS-CLAIMS ALL WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTY OF MERCHANTABILITY OR

FITNESS OF THIS PROGRAM FOR A PARTICULAR PURPOSE.

- 5. LIMITED WARRANTY. The diskette on which this Program is recorded is guaranteed for 90 days from date of purchase. If a defect occurs within 90 days, contact the representative at the place of purchase to arrange for a replacement.

- 6. LIMITATION OF REMEDIES AND LIABILITY. IN NO EVENT SHALL CYPRESS BE LIABLE FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES RESULTING FROM PROGRAM USE, EVEN IF CYPRESS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. CYPRESS'S EXCLUSIVE LIABILITY AND YOUR EXCLUSIVE REMEDY WILL BE IN THE REPLACEMENT OF ANY DEFECTIVE DISKETTE AS PROVIDED ABOVE. IN NO EVENT SHALL CYPRESS'S LIABILITY HEREUNDER EXCEED THE PURCHASE PRICE OF THE SOFTWARE.

- 7. ENTIRE AGREEMENT. This agreement constitutes the sole and complete Agreement between Cypress and the Customer for use of the Program and documentation. Changes to this Agreement may be made only by written mutual consent.

- 8. GOVERNING LAW. This Agreement shall be governed by the laws of the State of California. Should you have any question concerning this agreement, please contact:

Cypress Semiconductor Corporation Attn: Legal Counsel 3901 N. First Street San Jose, CA 95134-1599

408-943-2600

# Table of Contents

### **Chapter 1 - Introduction**

| 1.1.    | Introduction to Warp3                               | 1-3  |

|---------|-----------------------------------------------------|------|

| 1.2.    | Assumptions                                         |      |

| 1.3.    | Conventions                                         |      |

| 1.4.    | Installation and Licensing                          | 1-9  |

| 1.5.    | Objectives                                          |      |

| 1.6.    | About the Tutorial                                  |      |

| 1.6.1.  | File/Directory Management                           | 1-16 |

| 1.6.2.  | Differences in Operating Systems                    |      |

| Chapter | 2 - Exercise 1 : Behavioral Description             |      |

| 2.1.    | Start Warp3                                         | 2-2  |

| 2.2.    | Create a Project                                    |      |

| 2.3.    | Start Viewdraw                                      |      |

| 2.4.    | Start Viewtext (Viewdraw's Text Editor)             | 2-5  |

| 2.5.    | Write the "binctr" VHDL description                 | 2-7  |

| 2.5.1.  | Write the Entity Declaration                        | 2-8  |

| 2.5.2.  | Write the Architecture                              | 2-9  |

| 2.5.3.  | Write the Package Declaration                       | 2-12 |

| 2.6.    | Run Warp                                            | 2-14 |

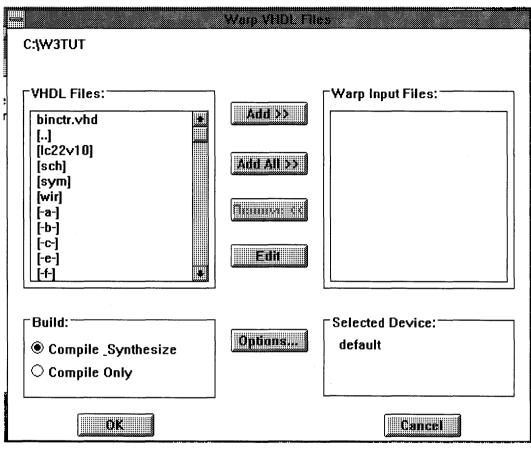

| 2.6.1.  | Start Galaxy                                        | 2-15 |

| 2.6.2.  | Compile binctr.vhd                                  | 2-16 |

| 2.7.    | Generate a symbol for the "binctr" VHDL description | 2-18 |

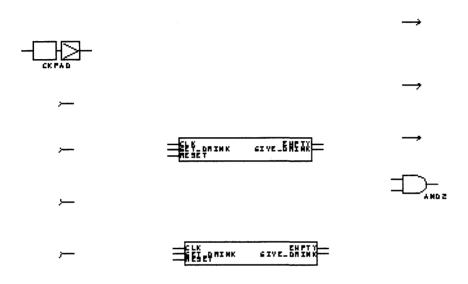

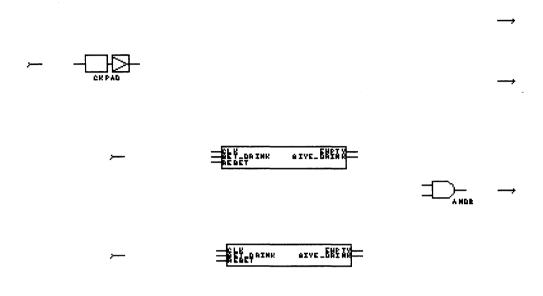

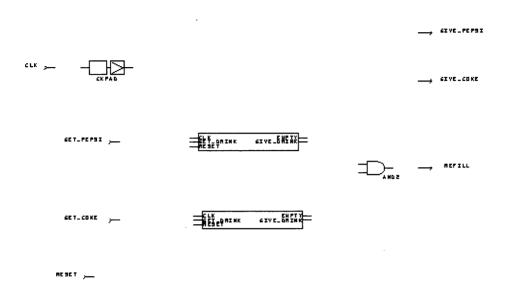

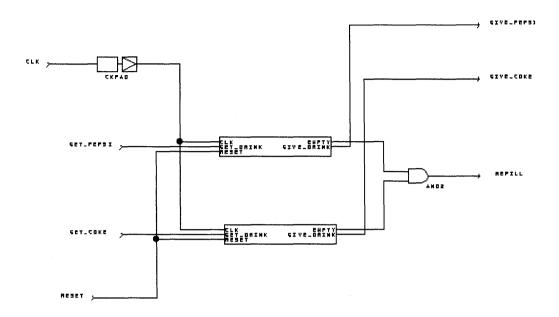

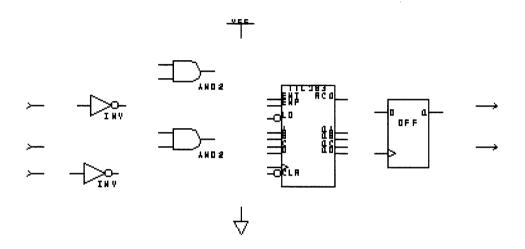

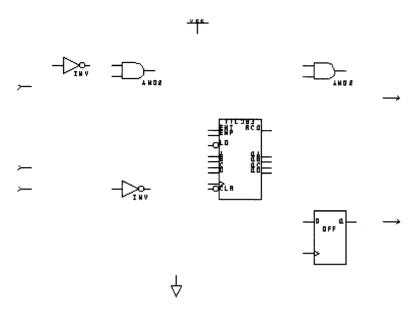

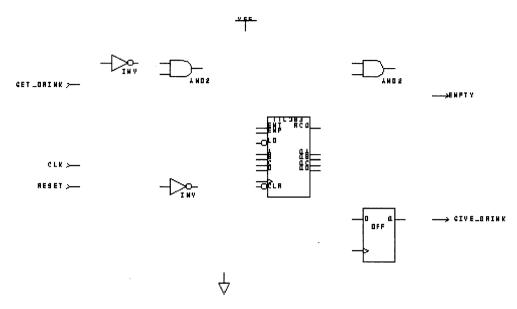

| 2.8.    | Create the schematic for the "refill" circuit       | 2-19 |

| 2.8.1.  | Instantiate components                              | 2-20 |

|         |                                                     |      |

### **Table of Contents**

|              | 2.8.2.   | Position Components                                     | 2-23   |

|--------------|----------|---------------------------------------------------------|--------|

|              | 2.8.3.   | Label Ports                                             | 2-25   |

|              | 2.8.4.   | Wire Components Together                                | 2-27   |

|              | 2.8.5.   | Save the Schematic                                      | 2-29   |

|              | 2.9.     | Generate a VHDL Description of the Schematic            | 2-30   |

|              | 2.10.    | Run Warp                                                | 2-31   |

|              | 2.10.1.  | Start Galaxy                                            | . 2-32 |

|              | 2.10.2.  | Start Warp                                              | 2-33   |

|              | 2.10.3.  | Synthesize a VHDL Description                           | 2-35   |

|              | 2.11.    | Run SpDE tools to process the QDIF file                 | . 2-38 |

|              | 2.11.1.  | Run pASIC->VSim to Generate a Viewsim Model             | . 2-40 |

|              | 2.12.    | Run CypBack to back-annotate pin assignment information | . 2-41 |

|              | 2.13.    | Run ViewSim to simulate the behavior of the design      | . 2-42 |

|              | 2.14.    | Conclusion                                              | . 2-45 |

|              |          |                                                         |        |

| C            | hapter 3 | 3 - Exercise 2: Structural Description                  |        |

|              | 3.1.     | Make the "binctr" symbol point to a schematic           | 3-3    |

|              | 3.2.     | Create the schematic for the "binctr" circuit.          | 3-4    |

|              | 3.2.1.   | Instantiate components                                  | 3-5    |

|              | 3.2.2.   | Position Components                                     | 3-8    |

|              | 3.2.3.   | Label Ports                                             | . 3-10 |

|              | 3.2.4.   | Wire Components Together                                | . 3-12 |

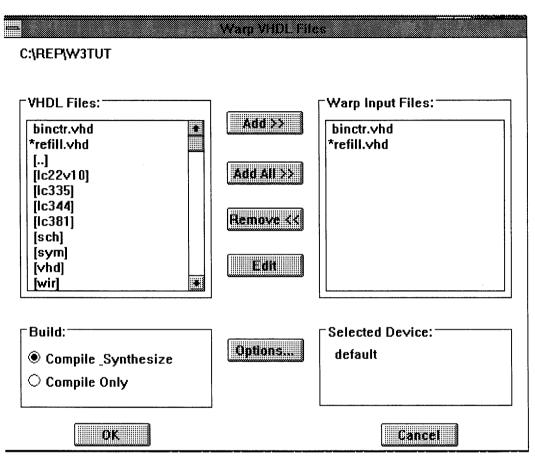

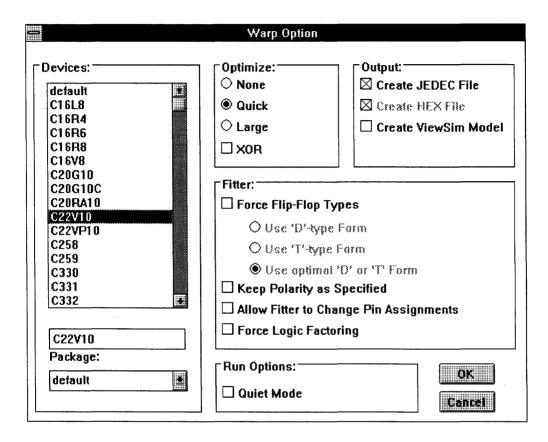

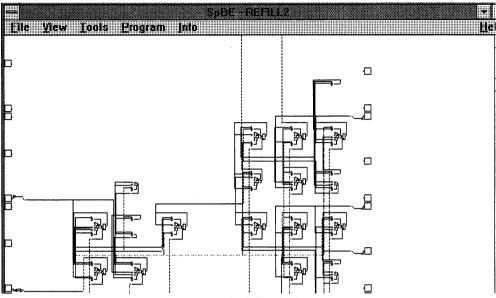

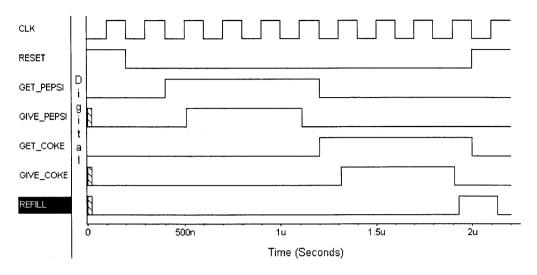

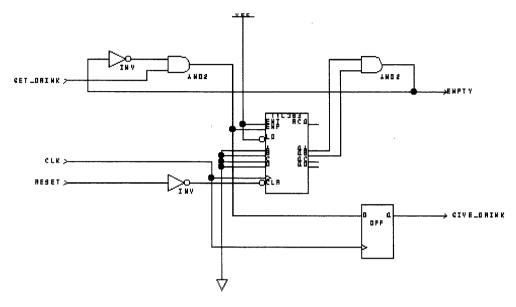

|              | 3.2.5.   | Save the binctr Schematic                               | . 3-14 |