# FAIRCHILD SEMICONDUCTOR

LOW POWER SCHOTTKY AND MACROLOGIC™TTL

## LOW POWER SCHOTTKY AND MACROLOGIC™TTL

464 Ellis Street, Mountain View, California 94042

## **TABLE OF CONTENTS**

| Page                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTRODUCTION 1-1 General Description 1-3 Circuit Characteristics 1-4 Input Configuration 1-4 Output Configuration 1-4 Output Characteristics 1-5 AC Switching Characteristics 1-6 Definition of Terms and Symbols 1-7                                                         |

| DESIGN CONSIDERATIONS       2-1         Supply Voltage and Temperature Range       2-3         Noise Immunity       2-3         Fan-in and Fan-out       2-4         Wired-OR Applications       2-5         Unused Inputs       2-5         Interconnection Delays       2-6 |

| DEVICE INDEX AND SELECTOR INFORMATION 3-1 Numerical Index of Devices 3-2 SSI Selector and Replacement Guide 3-6 MSI Selector Guide by Function 3-12                                                                                                                           |

| SSI DATA SHEETS                                                                                                                                                                                                                                                               |

| MSI DATA SHEETS 5-1                                                                                                                                                                                                                                                           |

| MACROLOGIC™ TTL DATA SHEETS                                                                                                                                                                                                                                                   |

| ORDERING INFORMATION AND PACKAGE OUTLINES                                                                                                                                                                                                                                     |

| FAIRCHILD FIELD SALES OFFICES, SALES REPRESENTATIVES AND DISTRIBUTOR LOCATIONS                                                                                                                                                                                                |

# LOW POWER SCHOTTKY AND MACROLOGIC TILL

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| DESIGN CONSIDERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2 |

| DEVICE INDEX AND<br>SELECTOR INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3 |

| SSI DATA SHEETS description of the state of | 4 |

| MSI DATA SHEETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5 |

| MACROLOGIC™ TTL DATA SHEETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6 |

| ORDERING INFORMATION AND PACKAGE OUTLINES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7 |

| FAIRCHILD FIELD SALES OFFICES,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

SALES REPRESENTATIVES AND DISTRIBUTOR LOCATIONS

### INTRODUCTION

General Description — For many years TTL has been the most popular digital integrated circuit technology, offering a good compromise between cost, speed, power consumption and ease of use. As the price of TTL circuits decreased and the average IC complexity increased to MSI (medium scale integration), the cost and size of the power supply and the difficulty of removing the heat dissipated in the TTL circuits became increasingly important factors. Recent improvements in semiconductor processing have made it possible to not only reduce TTL power consumption significantly, but also to improve the speed over that of standard TTL.

Fairchild's 9LS Low Power Schottky TTL family combines a current and power reduction by a factor 5 (compared to 7400 TTL) with anti-saturation Schottky diode clamping and advanced processing, using shallower diffusions and higher sheet resistivity to achieve circuit performance better than conventional TTL. With a full complement of popular TTL functions available in 9LS and the new, more complex and powerful LSI MACRO-LOGIC™ circuits introduced in 1975, Low Power Schottky is destined to become the dominating TTL logic family.

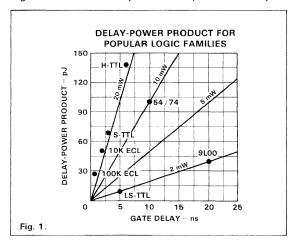

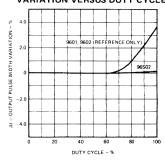

9LS represents more than just a conventional speed versus power trade-off. This is best illustrated by *Figure 1* which compares 9LS to other TTL technologies. Note that 9LS dissipates eleven times less power than 9S or 74S, suffering a delay increase of only 1.7 times. 9L (Fairchild's Low Power non-Schottky family) by comparison also dissipates eleven times less power than 74H, and 74L dissipates ten times less power than 74N, but both suffer a delay increase of 3.4 times.

The performance of 9LS is not just the result of Schottky clamping. 9LS is four times faster than 9L at the same power dissipation, while 9S and 74S are only two times faster than 74H at the same power. The new and higher level of efficiency exhibited by 9LS is made pos-

sible by advanced processing, which provides better switching transistors without any sacrifice in manfacturability.

To the system designer the advantages of this new TTL family are many:

- Less supply current allows smaller, cheaper power supplies, reducing equipment cost, size and weight.

- Lower power consumption means less heat is generated, which simplifies thermal design. Packing density can be increased or cooling requirements reduced, or perhaps both. The number of cooling fans can be reduced, or slower, quieter ones substituted.

- Reliability is enhanced, since lower dissipation causes less chip temperature rise above ambient; lower junction temperature increases MTBF. Also, lower chip current densities minimizes metal related failure mechanisms.

- Less noise is generated, since the improved transistors and lower operating currents lead to much smaller current spikes than standard TTL, which means that fewer or smaller power supply decoupling capacitors are needed. In addition, load currents are only 25% of standard TTL and 20% of HTTL, which means that when a logic transition occurs the current changes along signal lines are proportionately smaller, as are the changes in ground current. Rise and fall times, and thus wiring rules, are the same as for standard TTL and more relaxed than for HTTL or STTL.

- Simplified MOS to TTL interfacing is provided, since the input load current of LSTTL is only 25% of a standard TTL load.

- Ideally suited for CMOS to TTL interfacing. All Fairchild CMOS and most other 4000 or 74C CMOS are designed to drive one 9LS input load at 5.0 V. The 9LS can also interface directly with CMOS operating up to 15 V due to the high voltage Schottky input diodes.

- Best TTL to MOS or CMOS driver. With the modest input current of MOS or CMOS as a load, any 9LS output will rise up to within 1 V of V<sub>CC</sub>, and can be pulled up to 10 V with an external resistor.

- Interfaces directly with other TTL types, as indicated in the input and output loading tables.

- The functions and pinouts are the same as the familiar 7400/9300 series, which means that no extensive learning period is required to become adept in their use.

#### **Circuit Characteristics**

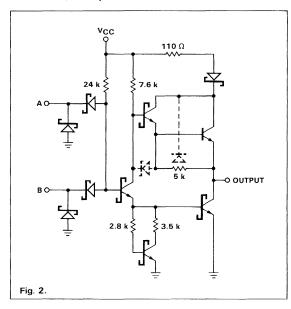

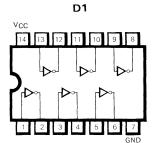

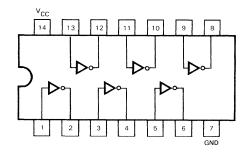

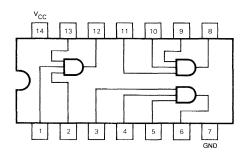

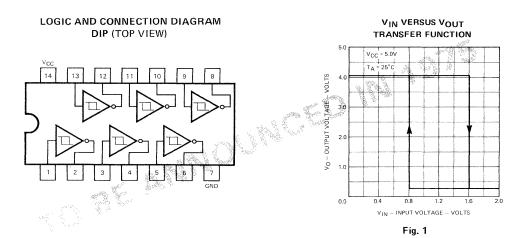

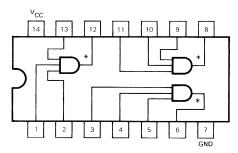

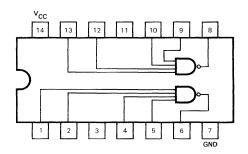

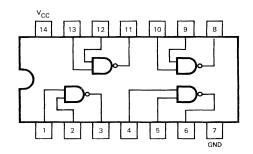

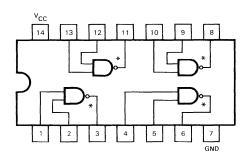

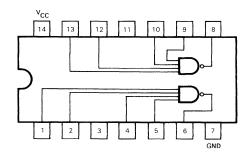

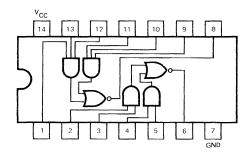

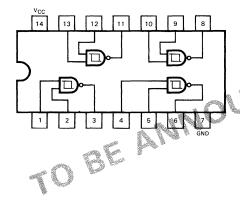

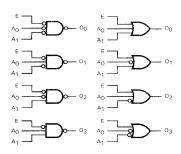

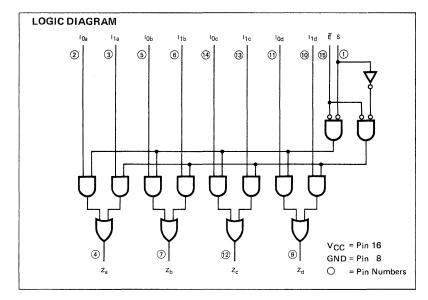

The 9LS circuit features are easiest explained by using the 9LS00 2-input NAND gate as an example. The input/output circuits of all 9LS TTL, including, SSI, MSI and MACROLOGIC are almost identical. While the logic function and the basic structure of 9LS circuits are the same as conventional TTL, there are also significant differences, as explained below:

#### Input Configuration

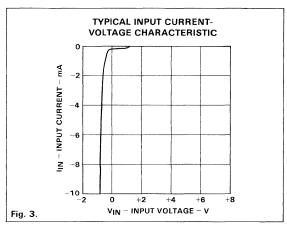

LSTTL is considered part of the TTL family, but it does not use the multi-emitter input structure that originally gave TTL its name. All 9LS TTL, with the exception of some early designs (see Note 1), employ a DTL-type input circuit which uses Schottky diodes to perform the AND function. Compared to the classical multi-emitter structure, this circuit is faster and it increases the input breakdown voltage to 15 V. Each input has a Schottky clamping diode which conducts when an input signal goes negative, as indicated by the input characteristic of Figure 3. This helps to simplify interfacing with those MOS circuits whose output signal tends to go negative. For a long TTL interconnection, which acts like a transmission line, the clamp diode acts as a termination for a negative-going signal and thus minimizes ringing. Otherwise, ringing could become significant when the finite delay along an interconnection is greater than one-fourth the fall time of the driving signal.

The effective capacitance of an LSTTL input is approximately 3.3 pF. For an input which serves more than one internal function, each additional function adds 1.5 pF.

Note 1. The 9LS03, 05, 22, 74, 109, 112, 113 and 114 use transistor inputs at present, but will be redesigned by the first part of 1976 to incorporate diode inputs.

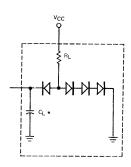

#### **Output Configuration**

The output circuits of 9LS Low Power Schottky TTL have several features not found in conventional TTL. A few of these features are discussed below.

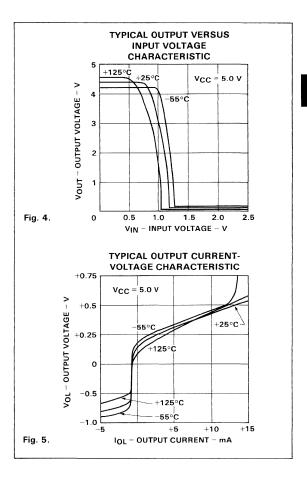

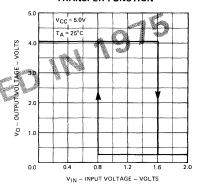

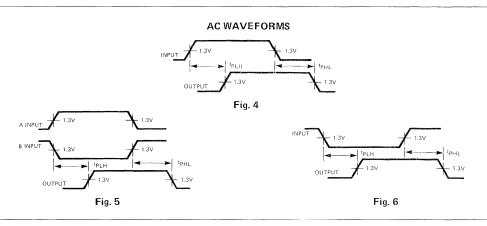

- The base of the pull-down output transistor is returned to ground through a resistor-transistor network instead of through a simple resistor. This squares up the transfer characteristics since it prevents conduction in the phase-splitter until base current is supplied to the pull-down output transistor. This also improves the propagation delay and transition time. (See Figure 4)

- The output pull-up circuit is a 2-transistor Darlington circuit with the base of the output transistor returned through a 5 kΩ resistor to the output terminal. (Unlike 74H and 74S where it is returned to ground, which is a more power consuming configuration). This configuration allows the output to pull-up to one V<sub>BE</sub> below V<sub>CC</sub> for low values of output current.

- As a unique feature, the 9LS outputs use a Schottky diode in series with the Darlington collector resistor. This diode allows the output to be pulled substantially higher than  $V_{CC}$  (e.g., to  $\pm 10$  V, convenient for interfacing with CMOS). For the same reason the parasistic diode of the base return resistor is connected to the Darlington common collector, not to V<sub>CC</sub>. Some early 9LS designs - the 9LS00, 02, 04, 10, 11, 20, 32, 74, 109, 112, 113 and 114 - do not have the diode in series with the Darlington collector resistor. These outputs are, therefore, clamped one diode drop above the positive supply voltage (V<sub>CC</sub>). These older circuits also contain a "speed-up" diode that supplies additional phase splitter current while the output goes from HIGH to LOW and also limits the maximum output voltage to one diode drop above V<sub>CC</sub>. Since this is the fastest transition even without additional speed-up, this diode is omitted in all new designs.

#### **Output Characteristics**

Figure 5 shows the LOW state output characteristics. For low I<sub>OL</sub> values, the pull-down transistor is clamped out of deep saturation which contributes to speed. The curves also show the clamping effect when I<sub>OL</sub> tends to go negative, as it often does due to reflections on a long interconnection after a negative-going transition. This clamping effect helps to minimize ringing.

The waveform of a rising output signal resembles an exponential, except that the signal is slightly rounded at the beginning of the rise. Once past this initial rounded portion, the starting edge rate is approximately 0.5 V/ns with a 15 pF load and 0.25 V/ns with a 50 pF load. For analytical purposes, the rising waveform can be approximated by the following expression.

$$v(t) = V_{OL} + 3.7 [1 - exp (-t/T)]$$

where

T = 8 ns for

$$C_L$$

= 15 pF

= 16 ns for  $C_I$  = 50 pF

The waveform of a falling output signal resembles that part of a cosine wave between angles of 0° and 180°. Fall times from 90% to 10% are approximately 4.5 ns with a 15 pF load and 8.5 ns with a 50 pF load. Equivalent edge rates are approximately 0.8 V/ns and 0.4 V/ns, respectively. For analytical purposes, the falling waveform can be approximated by the following expression.

$$v(t) = V_{OL} + 1.9 \mu(t) [1 + \cos \omega t] - 1.9 \mu(t-a) [1 + \cos \omega (t-a)]$$

where

$$\mu(t) = 0 \text{ for } t < 0$$

= 1 for t > 0

and

$$\mu(t-a) = 0 \text{ for } t < a$$

= 1 for t > a

For t in nanoseconds and

$$C_L$$

= 15 pF,

$$a = 7.5 \text{ ns. } \omega = 0.42$$

For

$$C_L = 50 pF$$

,

$$a = 14 \text{ ns}, \ \omega = 0.23$$

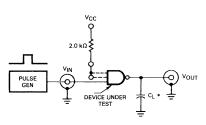

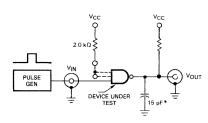

#### **AC Switching Characteristics**

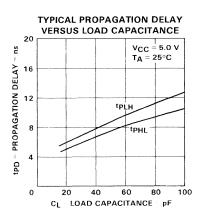

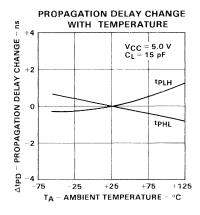

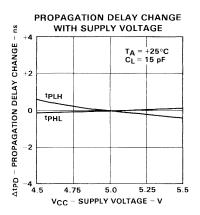

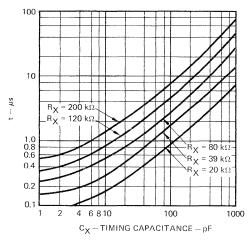

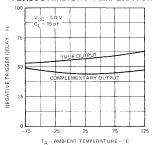

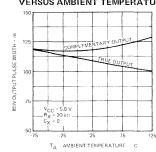

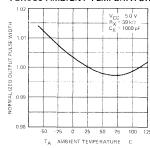

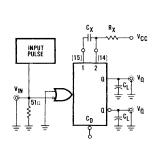

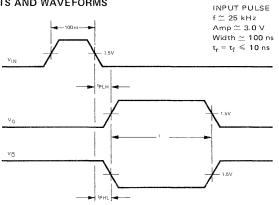

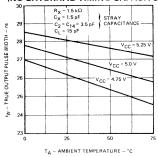

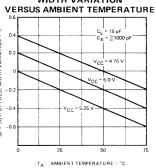

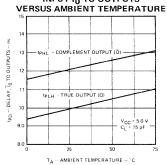

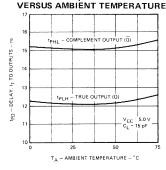

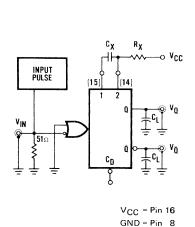

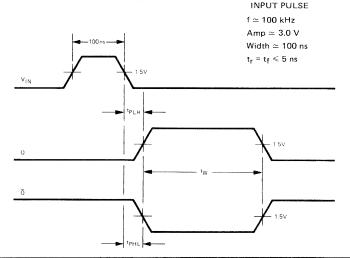

The average propagation delay of a Low Power Schottky gate is 5 ns at a load of 15 pF as shown in *Figure 6*. The delay times increase at an average of 0.08 ns/pF for larger values of capacitance load. These delay times are relatively insensitive to variations in power supply and temperature. The average propagation delay time changes less than 1.0 ns over temperature and less than

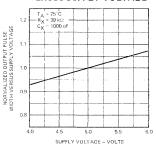

0.5 ns with  $V_{CC}$  for the military temperature and voltage ranges. (See *Figures 8* and 9).

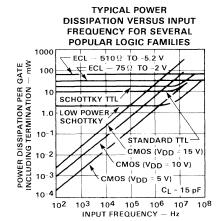

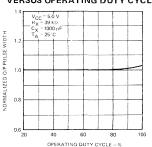

The power versus frequency characteristics of the 9LS family, as shown in *Figure 7*, indicate that at operating frequencies above 1 MHz the Low Power Schottky devices are more efficient than CMOS for most applications.

Fig. 6.

Fig. 8.

Fig. 7.

Fig. 9.

#### **DEFINITION OF SYMBOLS AND TERMS USED IN THIS DATA SHEET**

**CURRENTS** — Positive current is defined as conventional current flow into a device. Negative current is defined as conventional current flow out of a device. All current limits are specified as absolute values.

$\label{eq:CC} \textbf{Supply current} - \text{The current flowing into the V}_{\text{CC}} \text{ supply terminal of a circuit with the specified input conditions and the outputs open. When not specified, input conditions are chosen to guarantee worst case operation.}$

Input HIGH current — The current flowing into an input when a specified HIGH voltage is applied.

I<sub>IL</sub> Input LOW current – The current flowing out of an input when a specified LOW voltage is applied.

Output HIGH current — The leakage current flowing into a turned off open collector output with a specified HIGH output voltage applied. For devices with a pull-up circuit, the I<sub>OH</sub> is the current flowing out of an output which is in the HIGH state.

I<sub>OL</sub> Output LOW current – The current flowing into an output which is in the LOW state.

I<sub>OS</sub>

Output short circuit current — The current flowing out of an output which is in the HIGH state when that output is short circuited to ground (or other specified potential).

I<sub>OZH</sub>

Output off current HIGH — The current flowing into a disabled 3-state output with a specified HIGH output voltage applied.

Output off current LOW – The current flowing out of a disabled 3-state output with a specified LOW output voltage applied.

**VOLTAGES** – All voltages are referenced to ground. Negative voltage limits are specified as absolute values (*i.e.*, –10 V is greater than –1.0 V).

V<sub>CC</sub> Supply voltage – The range of power supply voltage over which the device is guaranteed to operate within the specified limits.

V<sub>CD(MAX)</sub>

Input clamp diode voltage — The most negative voltage at an input when 18 mA is forced out of that input terminal. This parameter guarantees the integrity of the input diode which is intended to clamp negative ringing at the input terminal.

V<sub>IH</sub> Input HIGH voltage — The range of input voltages that represents a logic HIGH in the system.

V<sub>IH(MIN)</sub> Minimum input HIGH voltage — The minimum allowed input HIGH in a logic system. This value represents the guaranteed input HIGH threshold for the device.

V<sub>IL</sub> Input LOW voltage — The range of input voltages that represents a logic LOW in the system.

V<sub>IL(MAX)</sub> Maximum input LOW voltage — The maximum allowed input LOW in a system. This value represents the guaranteed input LOW threshold for the device.

V<sub>OH(MIN)</sub> Output HIGH voltage — The minimum voltage at an output terminal for the specified output current I<sub>OH</sub> and at the minimum value of V<sub>CC</sub>.

V<sub>OL(MAX)</sub> Output LOW voltage — The maximum voltage at an output terminal sinking the maximum specified load current I<sub>OL</sub>.

### DEFINITION OF SYMBOLS AND TERMS USED IN THIS DATA SHEET (Cont'd)

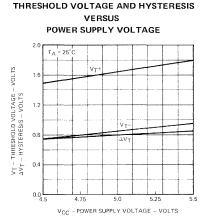

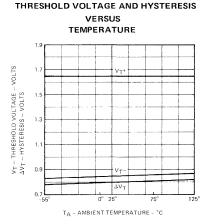

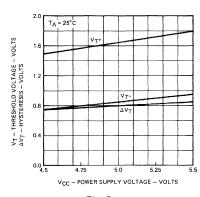

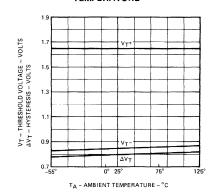

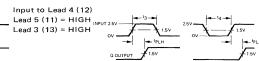

- V<sub>T+</sub> Positive-going threshold voltage The input voltage of a variable threshold device (*i.e.*, Schmitt Trigger) that is interpreted as a V<sub>IH</sub> as the input transition rises from below V<sub>T</sub>-(MIN).

- $V_{T-}$  Negative-going threshold voltage The input voltage of a variable threshold device (i.e., Schmitt Trigger) that is interpreted as a  $V_{IL}$  as the input transition falls from above  $V_{T+(MAX)}$ .

#### **AC SWITCHING PARAMETERS**

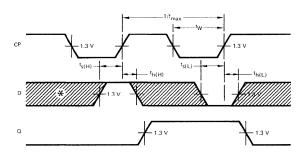

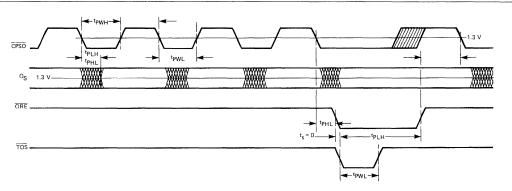

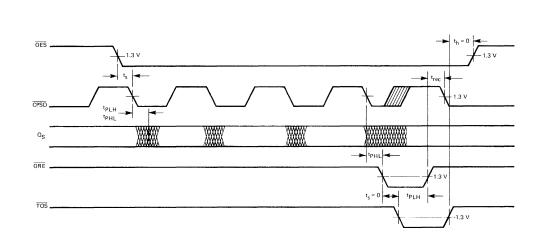

- f<sub>MAX</sub>

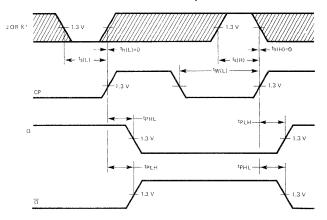

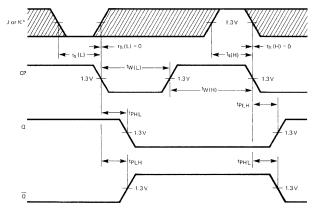

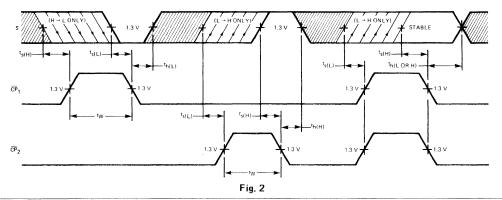

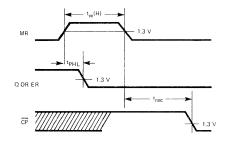

Toggle frequency/operating frequency The maximum rate at which clock pulses may be applied to a sequential circuit. Above this frequency the device may cease to function.

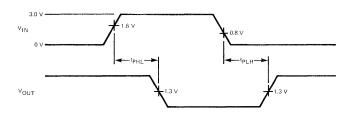

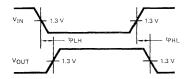

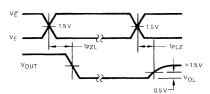

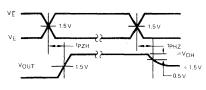

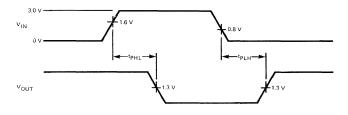

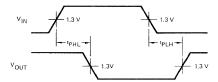

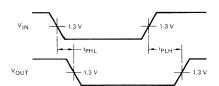

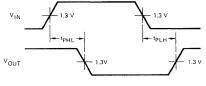

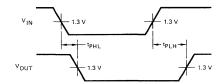

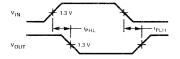

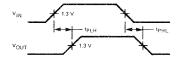

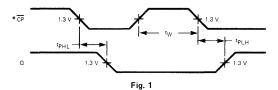

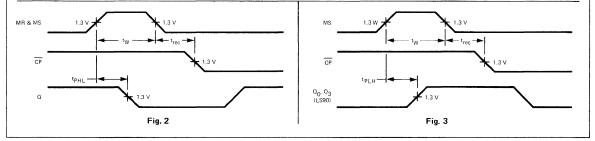

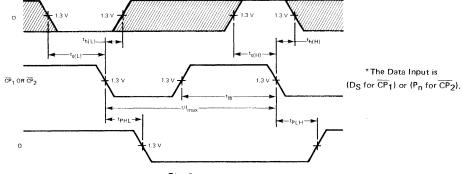

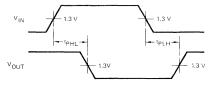

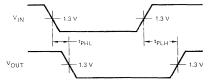

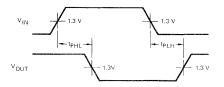

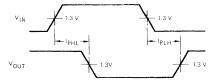

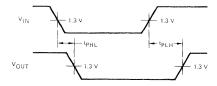

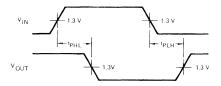

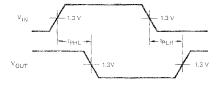

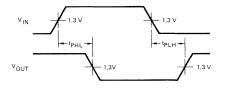

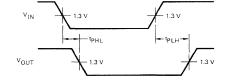

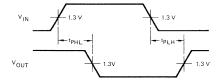

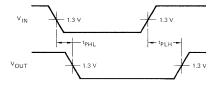

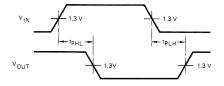

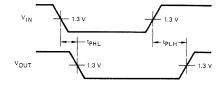

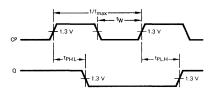

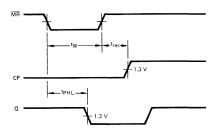

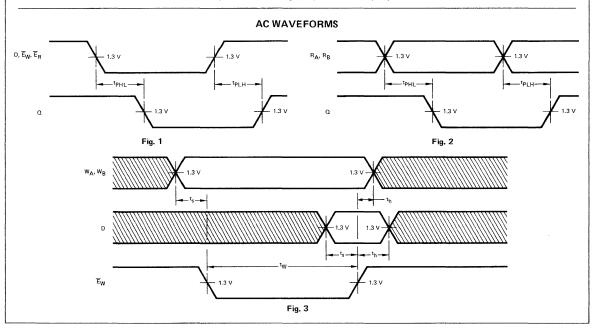

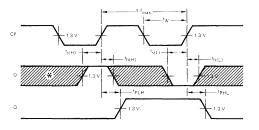

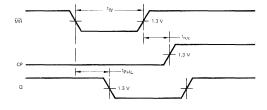

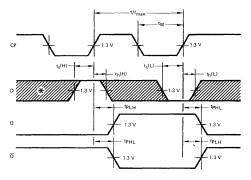

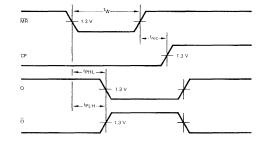

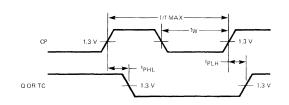

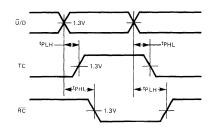

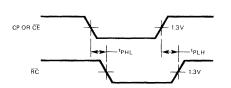

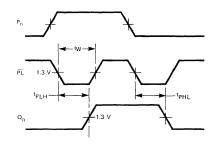

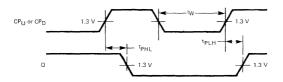

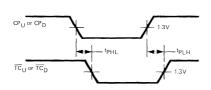

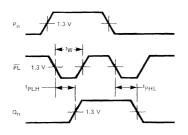

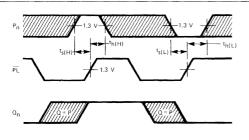

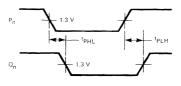

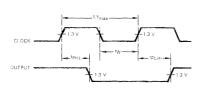

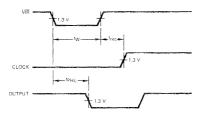

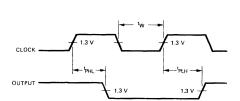

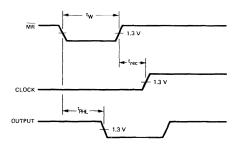

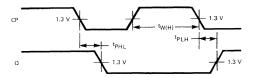

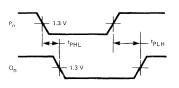

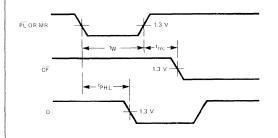

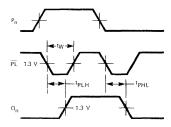

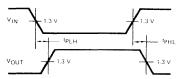

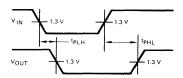

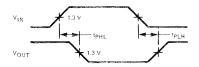

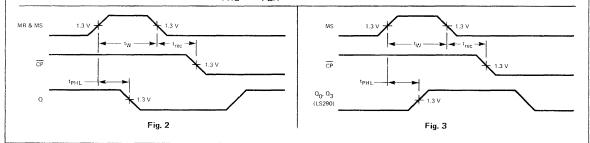

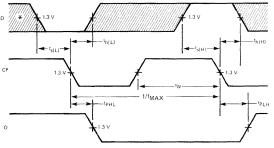

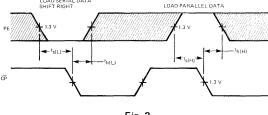

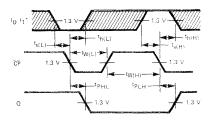

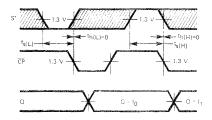

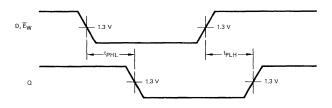

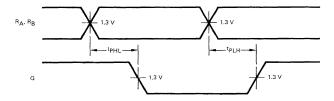

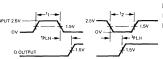

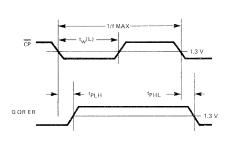

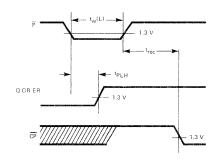

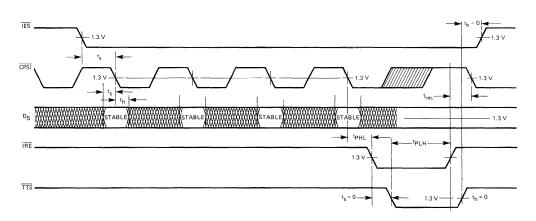

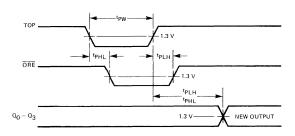

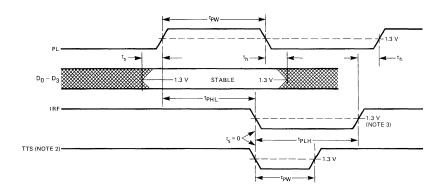

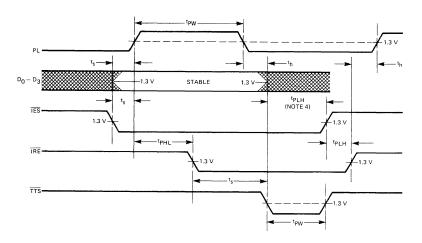

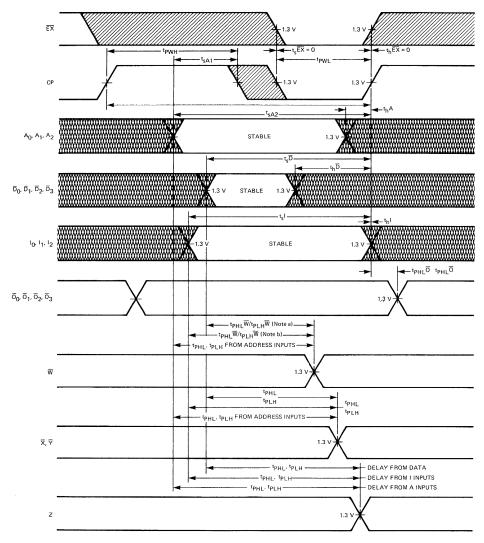

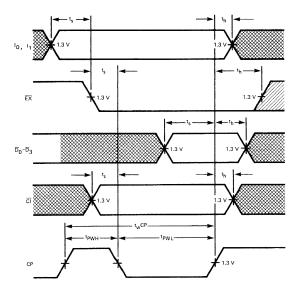

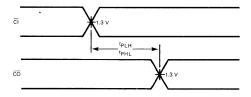

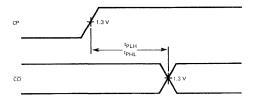

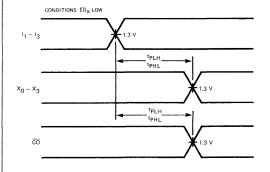

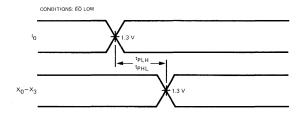

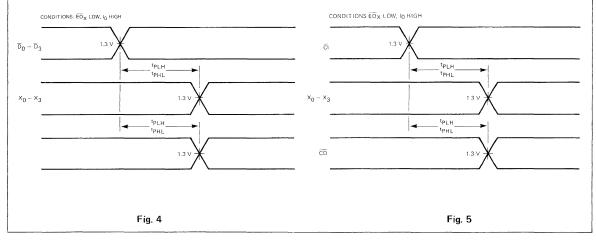

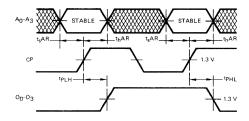

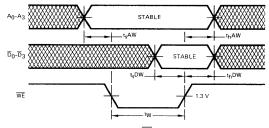

- tpLH Propagation delay time The time between the specified reference points, normally 1.3 V on the input and output voltage waveforms, with the output changing from the defined LOW level to the defined HIGH level.

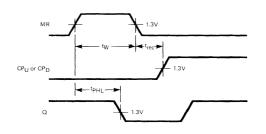

- tpHL Propagation delay time The time between the specified reference points, normally 1.3 V on the input and output voltage waveforms, with the output changing from the defined HIGH level to the defined LOW level.

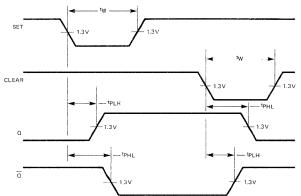

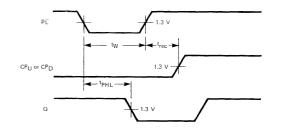

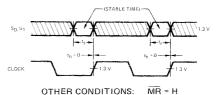

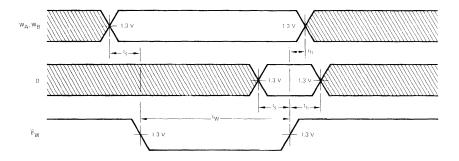

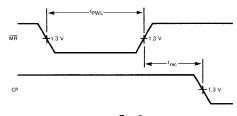

- t<sub>W</sub> Pulse width The time between 1.3 V amplitude points on the leading and trailing edges of a pulse.

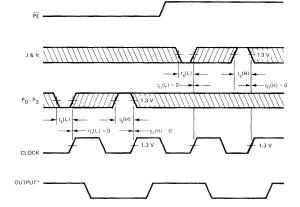

- th

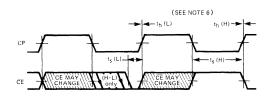

Hold time The interval immediately following the active transition of the timing pulse (usually the clock pulse) or following the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure its continued recognition. A negative hold time indicates that the correct logic level may be released prior to the active transition of the timing pulse and still be recognized.

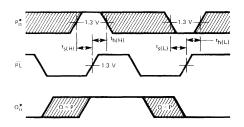

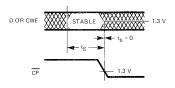

- ts

Set-up time The interval immediately preceding the active transition of the timing pulse (usually the clock pulse) or preceding the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure its recognition. A negative set-up time indicates that the correct logic level may be initiated sometime after the active transition of the timing pulse and still be recognized.

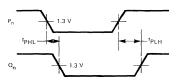

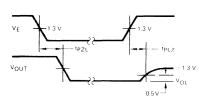

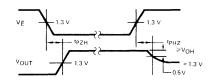

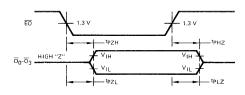

- tpHZ

Output disable time (of a 3-state output) from HIGH level The time between the 1.3 V level on the input and a voltage 0.5 V below the steady state output HIGH level with the 3-state output changing from the defined HIGH level to a high-impedance (off) state.

- t<sub>PLZ</sub>

Output disable time (of a 3-state output) from LOW level The time between the 1.3 V level on the input and a voltage 0.5 V above the steady state output LOW level with the 3-state output changing from the defined LOW level to a high-impedance (off) state.

- tpZH

Output enable time (of a 3-state output) to a HIGH level The time between the 1.3 V levels of the input and output voltage waveforms with the 3-state output changing from a high-impedance (off) state to a HIGH level.

- tpZL Output enable time (of a 3-state output) to a LOW level The time between the 1.3 V levels of the input and output voltage waveforms with the 3-state output changing from a high-impedance (off) state to a LOW level.

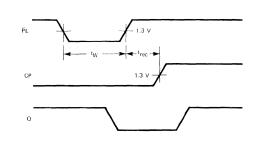

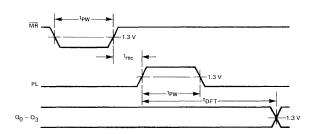

- t<sub>rec</sub>

Recovery time The time between the 1.3 V level on the trailing edge of an asynchronous input control pulse and the 1.3 V level on a synchronous input (clock) pulse such that the device will respond to the synchronous input.

# LOW POWER SCHOTTKY AND MACROLOGIC THE TTL

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| DESIGN CONSIDERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2 |

| DEVICE INDEX AND<br>SELECTOR INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3 |

| SSI DATA SHEETS Control of the contr | 4 |

| MSI DATA SHEETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 |

| MACROLOGIC™ TTL DATA SHEETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6 |

| ORDERING INFORMATION AND PACKAGE OUTLINES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7 |

FAIRCHILD FIELD SALES OFFICES, SALES REPRESENTATIVES AND DISTRIBUTOR LOCATIONS

## **DESIGN CONSIDERATIONS**

#### Supply Voltage and Temperature Range

The nominal supply voltage ( $V_{CC}$ ) for all TTL circuits is  $\pm 5.0$  V. Commercial grade parts are guaranteed to perform with a  $\pm 5\%$  supply tolerance ( $\pm 250$  mV) over an ambient temperature range of 0°C to 75°C. MIL-grade parts are guaranteed to perform with a  $\pm 10\%$  supply

tolerance ( $\pm 500\,$  mV) over an ambient temperature range of  $-55\,^{\circ}\text{C}$  to  $+125\,^{\circ}\text{C}$ .

TTL families may be mixed for optimum system design. The following tables specify the worst case noise immunity in mixed systems.

### Worst Case TTL DC Noise Immunity / Noise Margins

#### **Electrical Characteristics**

|      |        |                                        | Military (-55 to +125°C) Commercial (0 to 75°C) |     |     |     |          |     |     |     |       |

|------|--------|----------------------------------------|-------------------------------------------------|-----|-----|-----|----------|-----|-----|-----|-------|

| Item | Symbol | Fairchild TTL Families                 | VIL                                             | VIH | VOL | VOH | $v_{IL}$ | VIH | VOL | VOH | Units |

| 6    | TTL    | Standard TTL 9000, 9N (54/74)          | 0.8                                             | 2.0 | 0.4 | 2.4 | 0.8      | 2.0 | 0.4 | 2.4 | V     |

| 7    | HTTL   | High Speed TTL 9H (54H/74H)            | 0.8                                             | 2.0 | 0.4 | 2.4 | 8.0      | 2.0 | 0.4 | 2.4 | V     |

| 8    | LPTTL  | Low Power TTL, 93L00 (MSI)             | 0.7                                             | 2.0 | 0.3 | 2.4 | 8.0      | 2.0 | 0.3 | 2.4 | V     |

| 9    | STTL   | Schottky TTL 9S (54S/74S), 93S00       | 0.8                                             | 2.0 | 0.5 | 2.5 | 0.8      | 2.0 | 0.5 | 2.7 | V     |

| 10   | LSTTL  | Low Power Schottky TTL 9LS (54LS/74LS) | 0.7                                             | 2.0 | 0.4 | 2.5 | 8.0      | 2.0 | 0.5 | 2.7 | V     |

$V_{OL}$  and  $V_{OH}$  are the voltages generated at the output.  $V_{IL}$  and  $V_{IH}$  are the voltage required at the input to generate the appropriate output levels. The numbers given above are guaranteed worst-case values.

#### LOW Level Noise Margins (Military)

#### Τo From TTL HTTL LPTTL STTL **LSTTL** Units TTI 400 400 300 400 300 mV 400 400 300 400 300 mV HTTL **LPTTL** 500 500 400 500 400 mV STTL 300 300 200 300 200 mV 400 **LSTTL** 400 300 400 300 mV

From "VOL" to "VIL"

HIGH Level Noise Margins (Military)

| s | From To | TTL | HTTL | LPTTL | STTL | LSTTL | Units |

|---|---------|-----|------|-------|------|-------|-------|

|   | TTL     | 400 | 400  | 400   | 400  | 400   | mV    |

| 1 | HTTL    | 400 | 400  | 400   | 400  | 400   | mV    |

|   | LPTTL   | 400 | 400  | 400   | 400  | 400   | mV    |

|   | STTL    | 500 | 500  | 500   | 500  | 500   | mV    |

|   | LSTTL   | 500 | 500  | 500   | 500  | 500   | mV    |

From "VOH" to "VIH"

### LOW Level Noise Margins (Commercial)

| From To             | TTL | HTTL | LPTTL | STTL | LSTTL | Units |  |

|---------------------|-----|------|-------|------|-------|-------|--|

| TTL                 | 400 | 400  | 400   | 400  | 400   | mV    |  |

| HTTL                | 400 | 400  | 400   | 400  | 400   | mV    |  |

| LPTTL               | 500 | 500  | 500   | 500  | 500   | mV    |  |

| STTL                | 300 | 300  | 300   | 300  | 300   | mV    |  |

| LSTTL               | 300 | 300  | 300   | 300  | 300   | mV    |  |

| From "VOL" to "VIL" |     |      |       |      |       |       |  |

From "VOH" to "VIH"

| <b>HIGH Level</b> | Noise | Margins | (Commercial) |

|-------------------|-------|---------|--------------|

|                   |       |         |              |

| S | From To | TTL | HTTL | LPTTL | STTL | LSTTL | Units |

|---|---------|-----|------|-------|------|-------|-------|

|   | TTL     | 400 | 400  | 400   | 400  | 400   | mV    |

| 1 | HTTL    | 400 | 400  | 400   | 400  | 400   | mV    |

|   | LPTTL   | 400 | 400  | 400   | 400  | 400   | mV    |

|   | STTL    | 700 | 700  | 700   | 700  | 700   | mV    |

|   | LSTTL   | 700 | 700  | 700   | 700  | 700   | mV    |

#### Fan-in and Fan-out

In order to simplify designing with Fairchild TTL devices, the input and output loading parameters of all families are normalized to the following values:

1 TTL Unit Load (U.L.) = 40  $\mu$ A in the HIGH state (logic "1")

1 TTL Unit Load (U.L.) = 1.6 mA in the LOW state (logic "O")

Input loading and output drive factors of all products described in this handbook are related to these definitions.

#### **EXAMPLES - INPUT LOAD**

- A 9N00/7400 gate, which has a maximum I<sub>|L</sub> of 1.6 mA and I<sub>|H</sub> of 40 µA is specified as having an input load factor of 1 U.L. (Also called a fan-in of 1 load.)

- 2. The 9LS95 which has a value of  $I_{\parallel L}=0.8$  mA and  $I_{\parallel H}$  of 40  $\mu$ A on the CP terminal, is specified as having an input LOW load factor of

$$\frac{0.8 \text{ mA}}{1.6 \text{ mA}}$$

or 0.5 U.L.

and an input HIGH load factor of

$$\frac{40 \mu A}{40 \mu A}$$

or 1 U.L.

3. The 9LS00 gate which has an I $_{IL}$  of 0.36 mA and an I $_{IH}$  of 20  $\mu$ A, has an input LOW load factor of

$$\frac{0.36 \text{ mA}}{1.6 \text{ mA}}$$

or 0.225 U.L.

(normally rounded to 0.25 U.L.) and an input HIGH load factor of

$$\frac{20 \ \mu A}{40 \ \mu A}$$

or 0.5 U.L.

#### EXAMPLES - OUTPUT DRIVE

The output of the 9N00/7400 will sink 16 mA in the LOW (logic "0") state and source 800 μA in the HIGH (logic "1") state. The normalized output LOW drive factor is therefore

$$\frac{16 \text{ mA}}{1.6 \text{ mA}} = 10 \text{ U.L.}$$

and the output HIGH drive factor is

$$\frac{800 \mu A}{40 \mu A}$$

or 20 U.L.

2. The output of the 9LS00XC (Commercial Grade) will sink 8.0 mA in the LOW state and source 400  $\mu$ A in the HIGH state. The normalized output LOW drive factor is

$$\frac{8.0 \text{ mA}}{1.6 \text{ mA}}$$

or 5 U.L.

and the output HIGH drive factor is

$$\frac{400 \,\mu\text{A}}{40 \,\mu\text{A}}$$

or 10 U.L.

Relative load and drive factors for the basic TTL families are given in *Table I*.

TABLE I

| FAMILY     | INPUT     | LOAD      | OUTPUT DRIVE |           |  |

|------------|-----------|-----------|--------------|-----------|--|

| PAIVILT    | HIGH      | LOW       | HIGH         | LOW       |  |

| 9LS00      | 0.5 U.L.  | 0.25 U.L. | 10 U.L.      | 5 U.L.    |  |

| 9N00/7400  | 1 U.L.    | 1 U.L.    | 20 U.L.      | 10 U.L.   |  |

| 9000       | 1 U.L.    | 1 U.L.    | 20 U.L.      | 10 U.L.   |  |

| 9H00/74H00 | 1.25 U.L. | 1.25 U.L. | 25 U.L.      | 12.5 U.L. |  |

| 9S00/74S00 | 1.25 U.L. | 1.25 U.L. | 25 U.L.      | 12.5 U.L. |  |

Values for MSI devices vary significantly from one element to another. Consult the appropriate data sheet for actual characteristics.

### Wired-OR Applications

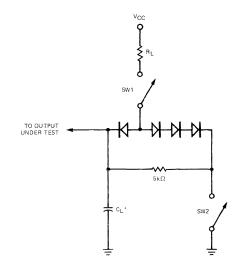

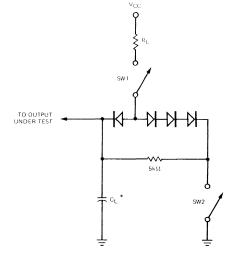

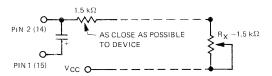

Certain TTL devices are provided with an "open" collector output to permit the Wired-OR (actually Wired-AND) function. This is achieved by connecting open collector outputs together and adding an external pullup resistor.

The value of the pull-up resistor is determined by considering the fan-out of the OR tie and the number of devices in the OR tie. The pull-up resistor value is chosen from a range between a maximum value (established to maintain the required  $V_{OH}$  with all the OR tied outputs HIGH) and a minimum value (established so that the OR tie fan-out is not exceeded when only one output is LOW).

# MINIMUM AND MAXIMUM PULL-UP RESISTOR VALUES

$$R_{X(MIN)} = \frac{V_{CC(MAX)} - V_{OL}}{I_{OL} - N_2(LOW) \cdot 1.6 \text{ mA}}$$

$$R_{X(MAX)} = \frac{V_{CC(MIN)} - V_{OH}}{N_1 \cdot I_{OH} + N_2(HIGH) \cdot 40 \mu A}$$

where:

R<sub>X</sub> = External Pull-up Resistor

N<sub>1</sub> = Number of Wired-OR Outputs

N<sub>2</sub> = Number of Input Unit Loads being Driven

I<sub>OH</sub> = I<sub>CEX</sub> = Output HIGH Leakage Current

I<sub>OL</sub> = LOW Level Fan-out Current of Driving Element

V<sub>OL</sub> = Output LOW Voltage Level (0.5 V) V<sub>OH</sub> = Output HIGH Voltage Level (2.4 V)

V<sub>CC</sub> = Power Supply Voltage

Example: Four 9LS03 gate outputs driving four other 9LS gates or MSI inputs.

$$R_{X \text{ (MIN)}} = \frac{5.25 \text{ V} - 0.5 \text{ V}}{8 \text{ mA} - 1.6 \text{ mA}} = \frac{4.75 \text{ V}}{6.4 \text{ mA}} = 742 \Omega$$

$$R_{X(MAX)} = \frac{4.75 \text{ V} - 2.4 \text{ V}}{4 \cdot 100 \, \mu\text{A} + 2 \cdot 40 \, \mu\text{A}} = \frac{2.35 \text{ V}}{0.48 \text{ mA}} = 4.9 \text{ k}\Omega$$

where:

$N_1 = 4$

$N_2(HIGH) = 4 \cdot 0.5 \text{ U.L.} = 2 \text{ U.L.}$

$N_2(LOW) = 4 \cdot 0.25 \text{ U.L.} = 1 \text{ U.L.}$

$I_{OH} = 100 \,\mu A$

$I_{OL} = 8 \text{ mA}$

$V_{OL} = 0.5 V$

$V_{OH} = 2.4 V$

Any value of pull-up resistor between 742  $\Omega$  and 4.9 k $\Omega$  can be used. The lower values yield the fastest speeds while the higher values yield the lowest power dissipation.

#### **Unused Inputs**

For best noise immunity and switching speed, unused TTL inputs should not be left floating, but should be held between 2.4 V and the absolute maximum input voltage.

Two possible ways of handling unused inputs are:

- 1. Connect unused input to V<sub>CC</sub>. Most 9LS inputs have a breakdown voltage  $\geq$  15 V and require, therefore, no series resistor. For all multi-emitter conventional TTL inputs, a 1 to 10 k $\Omega$  current limiting series resistor is recommended, to protect against V<sub>CC</sub> transients that exceed 5.5 V.

- 2. Connect the unused input to the output of un unused gate that is forced HIGH.

CAUTION: Do not connect an unused LSTTL input to another input of the same NAND or AND function. This method, recommended for normal TTL, increases the input coupling capacitance and thus reduces the ac noise immunity.

#### Interconnection Delays

For those parts of a system in which timing is critical, designers should take into account the finite delay along the interconnections. These range from about 0.12 to 0.15 ns/inch for the type of interconnections normally used in TTL systems. Exceptions occur in systems using ground planes with STTL to reduce ground noise during a logic transition; ground planes give higher distributed capacitance and delays of about 0.15 to 0.22 ns/inch.

Most interconnections on a logic board are short enough that the wiring and load capacitance can be treated as a lumped capacitance for purposes of estimating their effect on the propagation delay of the driving circuit. When an interconnection is long enough that its delay is one-fourth to one-half of the signal transition time, the driver output waveform exhibits noticeable slope changes during a transition. This is evidence that during the initial portion of the output voltage transition the driver sees the characteristic impedance of the interconnection (normally 150  $\Omega$  to 200  $\Omega$ ), which for transient conditions appears as a resistor returned to the quiescent voltage existing just before the beginning of the transition. This characteristic impedance forms a voltage divider with the driver output impedance, tending to produce a signal transition having the same rise or fall time as in the no-load condition but with a reduced amplitude. This attenuated signal travels to the far end of the interconnection, which is essentially an unterminated transmission line, whereupon the signal starts doubling. Simultaneously, a reflection voltage is generated which has the same amplitude and polarity as the original signal, e.g., if the driver output signal is positive-going the reflection will be positive-going, and as it travels back toward the driver it adds to the line voltage. At the instant the reflection arrives at the driver it adds algebraically to the still-rising driver output, accelerating the transition rate and producing the noticeable change in slope.

If an interconnection is of such length that its delay is longer than half the signal transition time, the attenuated output of the driver has time to reach substantial completion before the reflection arrives. In the limit, the waveform observed at the driver output is a 2-step signal with a pedestal. In this circumstance the first load circuit to receive a full signal is the one at the far end, because of the doubling effect, while the last one to receive a full signal is the one nearest the driver since it must wait for the reflection to complete the transi-

tion. Thus, in a worst-cast situation, the net contribution to the overall delay is twice the delay of the interconnection because the initial part of the signal must travel to the far end of the line and the reflection must return.

When load circuits are distributed along an interconnection, the input capacitance of each will cause a small reflection having a polarity opposite that of the signal transition, and each capacitance also slows the transition rate of the signal as it passes by. The series of small reflections, arriving back at the driver, is subtractive and has the effect of reducing the apparent amplitude of the signal. The successive slowing of the transition rate of the transmitted signal means that it takes longer for the signal to rise or fall to the threshold level of any particular load circuit. A rough but workable approach is to treat the load capacitances as an increase in the intrinsic distributed capacitance of the interconnection. Increasing the distributed capacitance of a transmission line reduces its impedance and increases its delay. A good approximation for ordinary TTL interconnections is that distributed load capacitance decreases the characteristic impedance by about one-third and increases the delay by one-half.

Another advantage of LSTTL has to do with its output impedance during a positive-going transition. Whereas the low output impedance of STTL and HTTL allows these circuits to force a larger initial swing into a low impedance interconnection, the low output impedance also has a disadvantage. It makes the reflection coefficient negative at the driven end of the interconnection, a circumstance that exists any time a transmission line is terminated by an impedance lower than its characteristic impedance. This means that when the reflection from the (essentially) open end of the interconnection arrives back at the driver it will be re-reflected with the opposite polarity. The result is a sequence of reflected signals which alternate in sign and decrease in magnitude, commonly known as ringing. The lower the driver output impedance, the greater the amplitude of the ringing and the longer it takes to damp out.

The output impedance of LSTTL, on the other hand, is closer to the characteristic impedance of the interconnections commonly used with TTL, and ringing is practically non-existent. Thus no special packaging is required. This advantage, combined with excellent speed, modest edge rates and very low transient currents, are some of the reasons that designers have found LSTTL extremely easy to work with and very cost effective.

| INTRODUCTION                                                                         | 1 |

|--------------------------------------------------------------------------------------|---|

| DESIGN CONSIDERATIONS                                                                | 2 |

| DEVICE INDEX AND<br>SELECTOR INFORMATION                                             | 3 |

| SSI DATA SHEETS                                                                      | 4 |

| MSI DATA SHEETS                                                                      | 5 |

| MACROLOGIC™ TTL DATA SHEETS                                                          | 6 |

| ORDERING INFORMATION AND PACKAGE OUTLINES                                            | 7 |

| FAIRCHILD FIELD SALES OFFICES,<br>SALES REPRESENTATIVES AND<br>DISTRIBUTOR LOCATIONS | 8 |

## **NUMERICAL INDEX OF DEVICES**

| DEVICE       | DESCRIPTION                               | PAGE |

|--------------|-------------------------------------------|------|

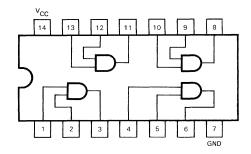

| 54LS/74LS00  | Quad 2-Input NAND Gate                    | 4-3  |

| 54LS/74LS02  | Quad 2-Input NOR Gate                     | 4-4  |

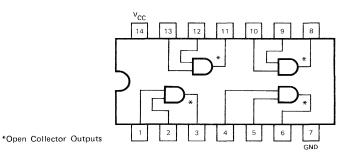

| 54LS/74LS03  | Quad 2-Input NAND Gate (Open Collector)   | 4-5  |

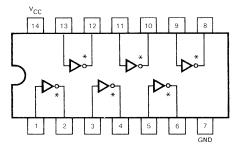

| 54LS/74LS04  | Hex Inverter                              | 4-6  |

| 54LS/74LS05  | Hex Inverter (Open Collector)             | 4-7  |

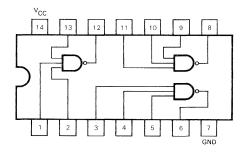

| 54LS/74LS08  | Quad 2-Input AND Gate                     | 4-8  |

| 54LS/74LS09  | Quad 2-Input AND Gate (Open Collector)    | 4-9  |

| 54LS/74LS10  | Triple 3-Input NAND Gate                  | 4-10 |

| 54LS/74LS11  | Triple 3-Input AND Gate                   | 4-11 |

| 54LS/74LS14  | Hex Schmitt Trigger                       | 4-12 |

| 54LS/74LS15  | Triple 3-Input AND Gate (Open Collector)  | 4-14 |

| 54LS/74LS20  | Dual 4-Input NAND Gate                    | 4-15 |

| 54LS/74LS21  | Dual 4-Input AND Gate                     | 4-16 |

| 54LS/74LS22  | Dual 4-Input NAND Gate (Open Collector)   | 4-17 |

| 54LS/74LS27  | Triple 3-Input NOR Gate                   | 4-18 |

| 54LS/74LS30  | 8-Input NAND Gate                         | 4-19 |

| 54LS/74LS32  | Quad 2-Input OR Gate                      | 4-20 |

| 54LS/74LS37  | Quad 2-Input NAND Buffer                  | 4-21 |

| 54LS/74LS38  | Quad 2-Input NAND Buffer (Open Collector) | 4-22 |

| 54LS/74LS40  | Dual 4-Input NAND Buffer                  | 4-23 |

| 54LS/74LS42  | 1-of-10 Decoder                           | 5-3  |

| 54LS/74LS51  | Dual AND-OR-Invert Gate                   | 4-24 |

| 54LS/74LS54  | 2-3-3-2-Input                             | 4-25 |

| 54LS/74LS55  | 2-Wide 4-Input                            | 4-26 |

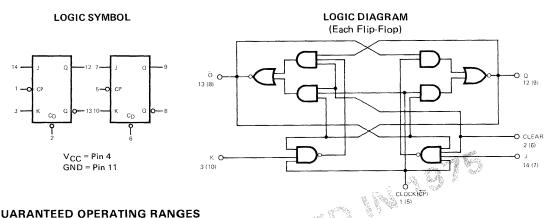

| 54LS/74LS73  | Dual JK Flip-Flop                         | 4-27 |

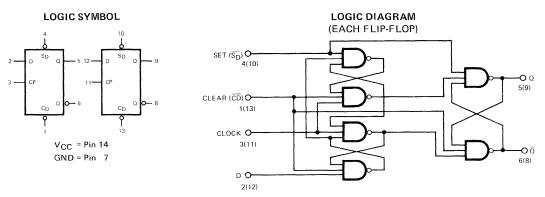

| 54LS/74LS74  | Dual D Flip-Flop                          | 4-29 |

| 54LS/74LS83  | 4-Bit Full Adder                          | 5-6  |

| 54LS/74LS86  | Quad Exclusive OR Gate                    | 4-31 |

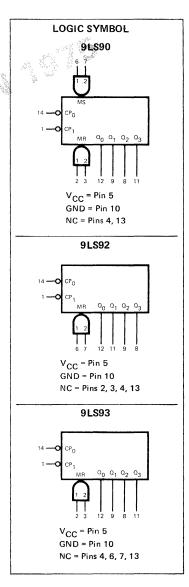

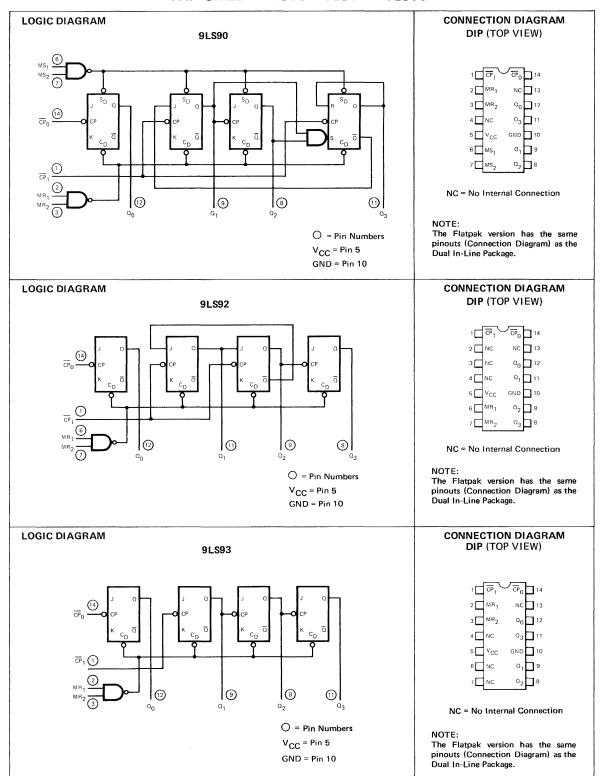

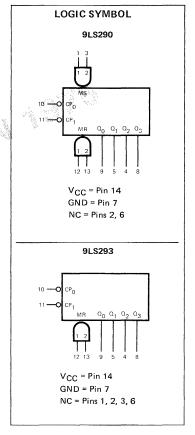

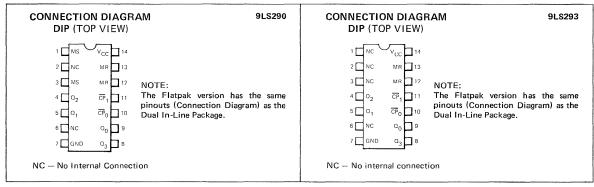

| 54LS/74LS90  | Decade Counter                            | 5-9  |

| 54LS/74LS92  | Divide-by-12 Counter                      | 5-9  |

| 54LS/74LS93  | 4-Bit Binary Counter                      | 5-9  |

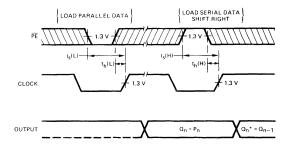

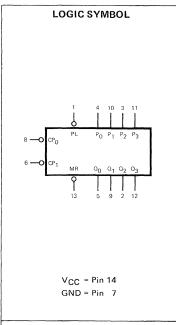

| 54LS/74LS95  | 4-Bit Shift Register                      | 5-15 |

| 54LS/74LS109 | Dual JK Edge-Triggered Flip-Flop          | 4-32 |

| 54LS/74LS112 | Dual JK Edge-Triggered Flip-Flop          | 4-34 |

| 54LS/74LS113 | Dual JK Edge-Triggered Flip-Flop          | 4-36 |

| 54LS/74LS114 | Dual JK Edge-Triggered Flip-Flop          | 4-38 |

| 54LS/74LS125 | Quad 3-State Buffer (LOW Enable)          | 4-40 |

| 54LS/74LS126 | Quad 3-State Buffer (HIGH Enable)         | 4-40 |

| 54LS/74LS132 | Quad 2-Input Schmitt Trigger              | 4-42 |

| 54LS/74LS133 | 13-Input NAND Gate                        | 4-44 |

| 54LS/74LS136 | Quad Exclusive OR (Open Collector)        | 4-45 |

| 54LS/74LS138 | 1-of-8 Decoder/Demultiplexer              |      |

| 54LS/74LS139 | Dual 1-of-4 Decoder/Demultiplexer         | 5-22 |

| 54LS/74LS151 | 8-Input Multiplexer                       |      |

| 54LS/74LS152 | 8-Input Multiplexer                       |      |

| 54LS/74LS153 | Dual 4-Input Multiplexer                  |      |

| 54LS/74LS155 | Dual 1-of-4 Decoder                       |      |

| 54LS/74LS156 | Dual 1-of-4 Decoder (Open Collector)      |      |

| 54LS/74LS157 | Quad 2-Input Multiplexer (Non-inverting)  |      |

## NUMERICAL INDEX OF DEVICES (Cont'd)

| DEVICE       | DESCRIPTION                                          | PAGE  |

|--------------|------------------------------------------------------|-------|

| 54LS/74LS158 | Quad 2-Input Multiplexer (Inverting)                 | 5-41  |

| 54LS/74LS160 | BCD Decade Counter, Asynchronous Reset (9310 Type)   | 5-44  |

| 54LS/74LS161 | 4-Bit Binary Counter, Asynchronous Reset (9316 Type) |       |

| 54LS/74LS162 | BCD Decade Counter, Synchronous Reset                |       |

| 54LS/74LS163 | 4-Bit Binary Counter, Synchronous Reset              | 5-44  |

| 54LS/74LS164 | 8-Bit Shift Register (Serial In-Parallel Out)        | 5-49  |

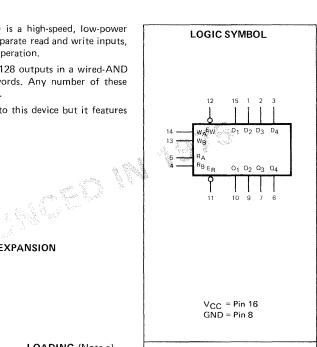

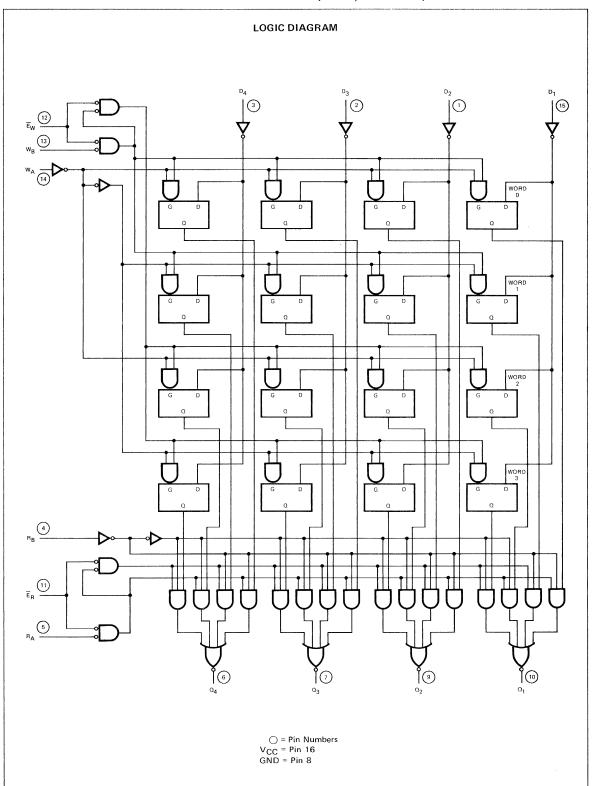

| 54LS/74LS170 | 4 x 4 Register File (Open Collector)                 |       |

| 54LS/74LS174 | Hex D Flip-Flop w/Clear                              | 5-57  |

| 54LS/74LS175 | Quad D Flip-Flop w/Clear                             |       |

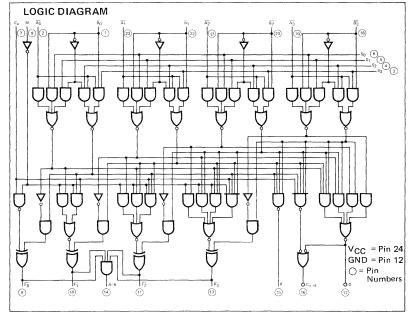

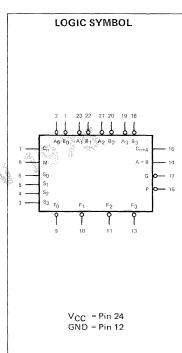

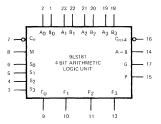

| 54LS/74LS181 | 4-Bit ALU                                            | 5-63  |

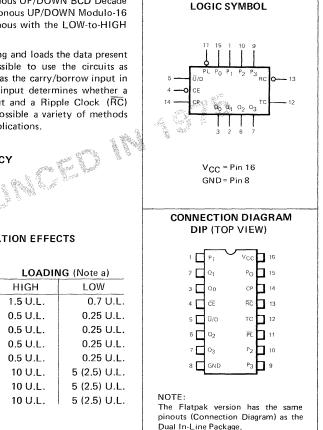

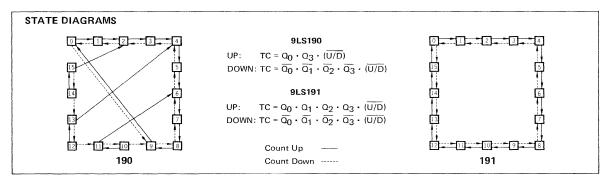

| 54LS/74LS190 | Up/Down Decade Counter                               | 5-68  |

| 54LS/74LS191 | Up/Down Binary Counter                               | 5-68  |

| 54LS/74LS192 | Up/Down Decade Counter                               | 5-75  |

| 54LS/74LS193 | Up/Down Binary Counter                               | 5-75  |

| 54LS/74LS194 | 4-Bit Right/Left Shift Register                      | 5-81  |

| 54LS/74LS195 | 4-Bit Shift Register (9300 Type)                     | 5-85  |

| 54LS/74LS196 | Decade Counter                                       |       |

| 54LS/74LS197 | 4-Bit Binary Counter                                 |       |

| 54LS/74LS251 | 8-Input Multiplexer (3-State)                        | 5-95  |

| 54LS/74LS253 | Dual 4-Input Multiplexer (3-State)                   | 5-99  |

| 54LS/74LS257 | Quad 2-Input Multiplexer (3-State)                   | 5-102 |

| 54LS/74LS258 | Quad 2-Input Multiplexer (3-State)                   | 5-105 |

| 54LS/74LS259 | 8-Bit Addressable Latch (9334)                       |       |

| 54LS/74LS266 | Quad Exclusive NOR (Open Collector)                  | 4-46  |

| 54LS/74LS279 | Quad Set-Reset Latch                                 |       |

| 54LS/74LS283 | 4-Bit Full Adder (Rotated LS83)                      |       |

| 54LS/74LS290 | Decade Counter                                       |       |

| 54LS/74LS293 | 4-Bit Binary Counter                                 |       |

| 54LS/74LS295 | 4-Bit Shift Register (3-State)                       |       |

| 54LS/74LS298 | Quad 2-Input Multiplexer w/Output Latches            |       |

| 54LS/74LS365 | Hex Buffer w/Common Enable (3-State)                 |       |

| 54LS/74LS366 | Hex Inverter w/Common Enable (3-State)               |       |

| 54LS/74LS367 | Hex Buffer, 4-Bit & 2-Bit (3-State)                  |       |

| 54LS/74LS368 | Hex Inverter, 4-Bit & 2-Bit (3-State)                |       |

| 54LS/74LS670 | 4 x 4 Register File (3-State)                        | 5-124 |

## NUMERICAL INDEX OF DEVICES (Cont'd)

| DEVICE | DESCRIPTION                               | PAGE |

|--------|-------------------------------------------|------|

| 9LS00  | Quad 2-Input NAND Gate                    | 4-3  |

| 9LS02  | Quad 2-Input NOR Gate                     | 4-4  |

| 9LS03  | Quad 2-Input NAND Gate (Open Collector)   |      |

| 9LS04  | Hex Inverter                              |      |

| 9LS05  | Hex Inverter (Open Collector)             |      |

| 9LS08  | Quad 2-Input AND Gate                     |      |

| 9LS09  | Quad 2-Input AND Gate (Open Collector)    | 4-9  |

| 9LS10  | Triple 3-Input NAND Gate                  | 4-10 |

| 9LS11  | Triple 3-Input AND Gate                   | 4-11 |

| 9LS14  | Hex Schmitt Trigger                       | 4-12 |

| 9LS15  | Triple 3-Input AND Gate (Open Collector)  | 4-14 |

| 9LS20  | Dual 4-Input NAND Gate                    | 4-15 |

| 9LS21  | Dual 4-Input AND Gate                     | 4-16 |

| 9LS22  | Dual 4-Input NAND Gate (Open Collector)   | 4-17 |

| 9LS27  | Triple 3-Input NOR Gate                   | 4-18 |

| 9LS30  | 8-Input NAND Gate                         | 4-19 |

| 9LS32  | Quad 2-Input OR Gate                      | 4-20 |

| 9LS37  | Quad 2-Input NAND Buffer                  | 4-21 |

| 9LS38  | Quad 2-Input NAND Buffer (Open Collector) | 4-22 |

| 9LS40  | Dual 4-Input NAND Buffer                  | 4-23 |

| 9LS42  | 1-of-10 Decoder                           | 5-3  |

| 9LS51  | Dual AND-OR-Invert Gate                   | 4-24 |

| 9LS54  | 2-3-3-2-Input                             | 4-25 |

| 9LS55  | 2-Wide 4-Input                            | 4-26 |

| 9LS73  | Dual JK Flip-Flop                         | 4-27 |

| 9LS74  | Dual D Flip-Flop                          |      |

| 9LS83  | 4-Bit Full Adder                          |      |

| 9LS86  | Quad Exclusive OR Gate                    | 4-31 |

| 9LS90  | Decade Counter                            |      |

| 9LS92  | Divide-by-12 Counter                      | 5-9  |

| 9LS93  | 4-Bit Binary Counter                      | 5-9  |

| 9LS95  | 4-Bit Shift Register                      |      |

| 9LS109 | Dual JK Edge-Triggered Flip-Flop          | 4-32 |

| 9LS112 | Dual JK Edge-Triggered Flip-Flop          |      |

| 9LS113 | Dual JK Edge-Triggered Flip-Flop          |      |

| 9LS114 | Dual JK Edge-Triggered Flip-Flop          |      |

| 9LS125 | Quad 3-State Buffer (LOW Enable)          | 4-40 |

| 9LS126 | Quad 3-State Buffer (HIGH Enable)         |      |

| 9LS132 | Quad 2-Input Schmitt Trigger              | 4-42 |

| 9LS133 | 13-Input NAND Gate                        | 4-44 |

| 9LS136 | Quad Exclusive OR (Open Collector)        |      |

| 9LS138 | 1-of-8 Decoder/Demultiplexer              | 5-19 |

| 9LS139 | Dual 1-of-4 Decoder/Demultiplexer         |      |

| 9LS151 | 8-Input Multiplexer                       | 5-25 |

| 9LS152 | 8-Input Multiplexer                       |      |

| 9LS153 | Dual 4-Input Multiplexer                  |      |

| 9LS155 | Dual 1-of-4 Decoder                       | 5-34 |

| 9LS156 | Dual 1-of-4 Decoder (Open Collector)      | 5-34 |

| 9LS157 | Quad 2-Input Multiplexer (Non-inverting)  | 5-38 |

## NUMERICAL INDEX OF DEVICES (Cont'd)

| DEVICE | DESCRIPTION                                          | PAGE  |

|--------|------------------------------------------------------|-------|

| 9LS158 | Quad 2-Input Multiplexer (Inverting)                 | 5-41  |

| 9LS160 | BCD Decade Counter, Asynchronous Reset (9310 Type)   | 5-44  |

| 9LS161 | 4-Bit Binary Counter, Asynchronous Reset (9316 Type) | 5-44  |

| 9LS162 | BCD Decade Counter, Synchronous Reset                | 5-44  |

| 9LS163 | 4-Bit Binary Counter, Synchronous Reset              | 5-44  |

| 9LS164 | 8-Bit Shift Register (Serial In-Parallel Out)        | 5-49  |

| 9LS170 | 4 x 4 Register File (Open Collector)                 | 5-53  |

| 9LS174 | Hex D Flip-Flop w/Clear                              | 5-57  |

| 9LS175 | Quad D Flip-Flop w/Clear                             | 5-60  |

| 9LS181 | 4-Bit ALU                                            | 5-63  |

| 9LS190 | Up/Down Decade Counter                               | 5-68  |

| 9LS191 | Up/Down Binary Counter                               | 5-68  |

| 9LS192 | Up/Down Decade Counter                               | 5-75  |

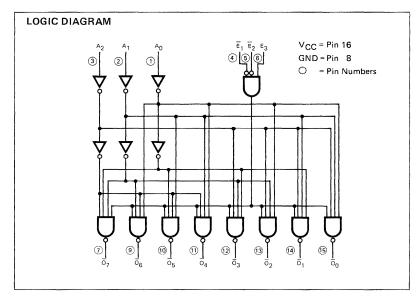

| 9LS193 | Up/Down Binary Counter                               | 5-75  |