# 8/16 BIT MULTI-CHIP MICROCOMPUTER DATA BOOK

### **TABLE OF CONTENTS**

| Quality and Reliability Commitment                                   | 3 |

|----------------------------------------------------------------------|---|

| Hitachi Microprocessor/Peripheral Cross Reference                    | 4 |

| New Hitachi Microprocessor Numbering System                          | 5 |

| HD6800, HD68A00, HD68B00 MPU (Micro Processing Unit)                 | 6 |

| HD6802 MPU (Microprocessor with Clock and RAM)                       | 7 |

| HD6809, HD68A09, HD68B09  MPU (Micro Processing Unit)4               | 8 |

| HD6821, HD68A21, HD68B21 PIA (Peripheral Interface Adapter)          | 7 |

| HD6840, HD68A40, HD68B40 PTM (Programmable Timer Module)             | 7 |

| HD6843S, HD68A43S  FDC (Floppy Disk Controller)                      | 0 |

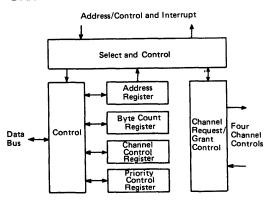

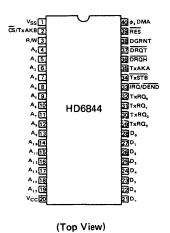

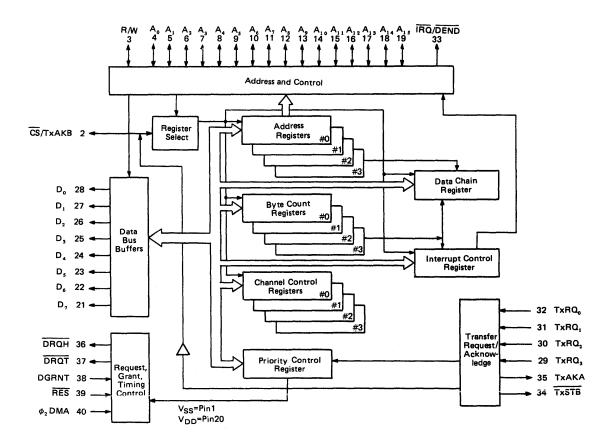

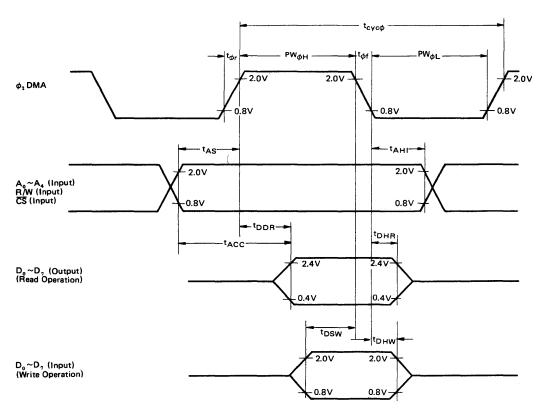

| HD6844, HD68A44  DMAC (Direct Memory Access Controller)              | 3 |

| HD6845S, HD68A45S, HD68B45S  CRTC (CRT Controller)                   | 0 |

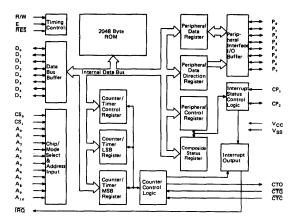

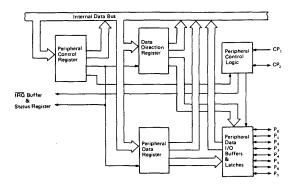

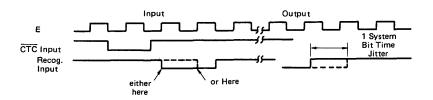

| HD6846 COMBO (Combination ROM I/O Timer)19                           | 0 |

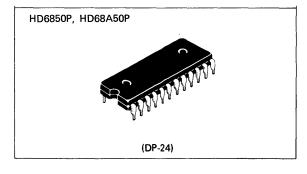

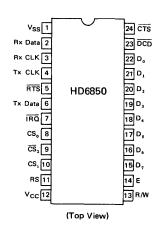

| HD6850, HD68A50 ACIA (Asynchronous Communication Interface Adapter)  | 1 |

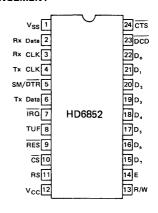

| HD6852, HD68A52<br>SSDA (Synchronous Serial Data Adapter)21          | 1 |

| HD46508, HD46508-1 ADU (Analog Data Acquisition Unit)—Preliminary23- | 4 |

| HD68000 MPU (Micro Processing Unit)—Preliminary25                    | 3 |

| APPENDIX                                                             |   |

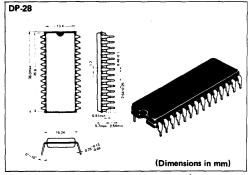

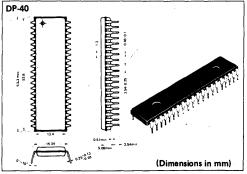

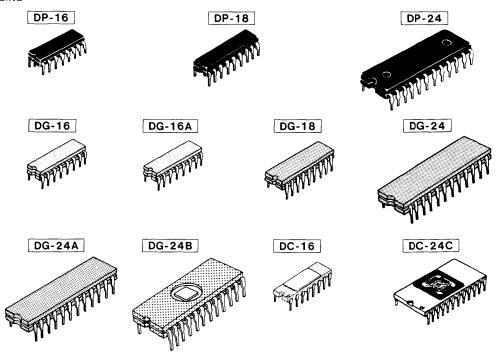

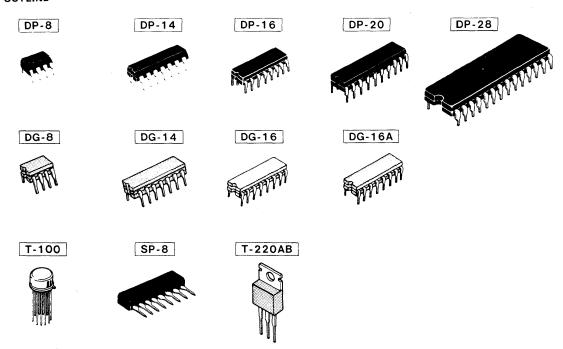

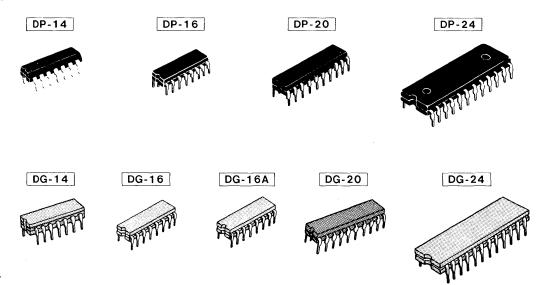

| Package Information                                                  | 6 |

| HMCS6800 Family Instructions                                         | В |

| Memories                                                             | 3 |

| Linear IC & Interface Circuits                                       | 6 |

| TTL HD74/HD74S/HD74LS Series                                         | 8 |

# An Unprecedented Commitment to Quality and Reliability . . .

As quality and reliability become increasingly important concerns, Hitachi continues to improve its efforts to provide the best possible product. The experience gained in shipping millions of microprocessors and peripheral LSIs for critical and demanding automotive and industrial applications is reflected in every product we sell. Each unit shipped receives 100% dynamic high-temperature burn-in, a quality assurance effort unparalleled in the semiconductor industry, and another reason why Hitachi is the Symbol of Semiconductor Quality, Worldwide.

## QUALITY ASSURANCE FLOW FOR ASSEMBLY AND TEST (all microprocessor and microcomputer products):

|    | PROCESS                                                                                                                                                                                                                      | INSPECTION LEVEL  | QC CRITERIA        | REMARKS                            |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|------------------------------------|

| 1  | Dicing                                                                                                                                                                                                                       | _                 | _                  | _                                  |

| 2  | Chip Visual                                                                                                                                                                                                                  | 100%              | Visual             | 100x                               |

| 3  | Lot Acceptance                                                                                                                                                                                                               | AQL = 0.25% *     | Visual             | 100x                               |

| 4  | Die Attachment                                                                                                                                                                                                               | _                 | _                  | Au-Si                              |

| 5  | Patrol Inspection                                                                                                                                                                                                            | Once/Day/Machine  | Visual             |                                    |

| 6  | Wire Bonding                                                                                                                                                                                                                 | _                 | _                  | Al Ultrasonic                      |

| 7  | Patrol Inspection                                                                                                                                                                                                            | Once/Day/Machine  | Visual             |                                    |

|    |                                                                                                                                                                                                                              | Once/Week/Machine | Bond Dimension     |                                    |

|    |                                                                                                                                                                                                                              |                   | Bond Strength      |                                    |

| 8  | Chip Visual Lot Acceptance Die Attachment Patrol Inspection Wire Bonding Patrol Inspection  Visual Inspection Lot Acceptance Seal Temperature Cycle  Hermeticity  Plating Lead Trim Visual Inspection Lot Acceptance Burn-in | 100%              | Visual             | 20x                                |

| 9  | Lot Acceptance                                                                                                                                                                                                               | AQL = 0.25% *     | Visual             | 20x                                |

| 10 | Seal                                                                                                                                                                                                                         | · –               | _                  | A-Sn Alloy                         |

| 11 | Temperature Cycle                                                                                                                                                                                                            | 100 %             | _                  | -55 °C -25 °C -150 °C<br>10 Cycles |

| 12 | Hermeticity                                                                                                                                                                                                                  | 100 %             | Fine and Gross     | Hermetic Packages<br>Only          |

| 13 | Plating                                                                                                                                                                                                                      | _                 | _                  | Tin (Sn)                           |

| 14 | Lead Trim                                                                                                                                                                                                                    | _                 | _                  | _                                  |

| 15 | Visual Inspection                                                                                                                                                                                                            | 100%              | Visual             |                                    |

| 16 | Lot Acceptance                                                                                                                                                                                                               | AQL = 0.25%       | Visual             |                                    |

| 17 | Burn-in                                                                                                                                                                                                                      | 100%              | _                  | Dynamic Ta = 125 °C                |

| 18 | Electrical Test                                                                                                                                                                                                              | 100%              | DC, AC, Functional | Ta = 70 °C                         |

| 19 | Marking                                                                                                                                                                                                                      |                   | _                  |                                    |

| 20 | Electrical                                                                                                                                                                                                                   | 100%              | DC                 |                                    |

| 21 | Visual Inspection                                                                                                                                                                                                            | 100%              | External Visual    |                                    |

| 22 | Lot Acceptance                                                                                                                                                                                                               | AQL = 0.25% *     | Electrical         |                                    |

|    |                                                                                                                                                                                                                              | AQL = 0.65%       | External Visual    |                                    |

<sup>\*</sup>Combined DC, AC and functional.

#### HITACHI MICROPROCESSOR/PERIPHERAL CROSS REFERENCE

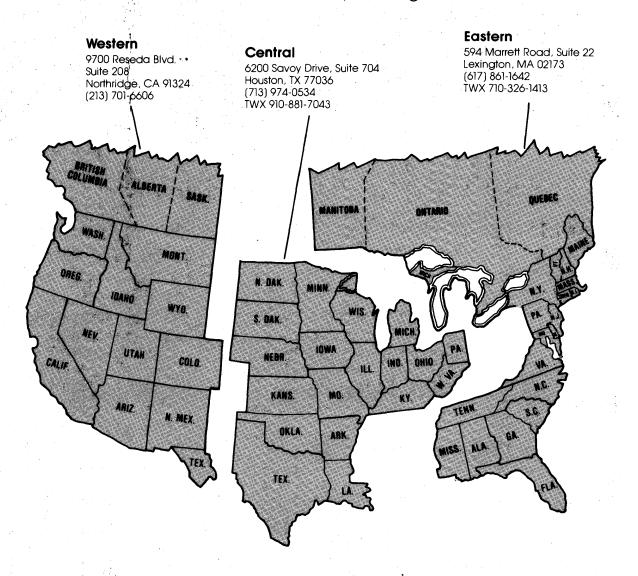

Hitachi is in the process of converting many microprocessor part numbers to "industry standard" generic part numbers. A complete list showing both the "old" and "new" part numbers is shown in figure 1. The use of industry standard part numbers will greatly simplify the interface between Hitachi and our customers.

Beginning JULY 1, 1981, all orders should be entered using the "new" part numbers only.

Note that during the conversion process, product shipped by Hitachi will be marked 1 of 2 ways (see figure 2). 1) marked with the "old" Hitachi part number...

or

2) marked with a dual number ("old" and "new")

At the completion of the conversion (approximately JANUARY 1, 1982) all product will be shipped with the dual marking (2 above).

If this conversion plan poses problems, or you have any questions, please contact Hitachi Microprocessor Marketing.

| Description                                                   | "old"<br>HITACHI<br>number | "new"<br>HITACHI<br>number | MOTOROLA number |

|---------------------------------------------------------------|----------------------------|----------------------------|-----------------|

| 16/32 bit microprocessing unit, 8 mhz                         |                            | HD68000-8                  | MC68000L        |

| 16/32 bit microprocessing unit, 6 mhz                         |                            | HD68000-6                  | MC68000L6       |

| 16/32 bit microprocessing unit, 4 mhz                         |                            | HD68000-4                  | MC68000L4       |

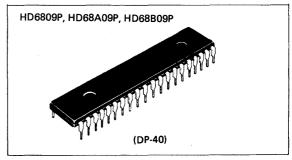

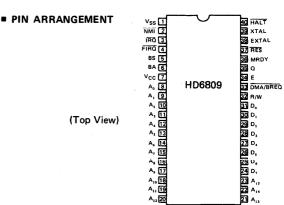

| 8/16 bit microprocessing unit, 1mhz                           | HD6809P                    | HD6809P                    | MC6809P         |

| 8/16 bit microprocessing unit, 1.5mhz                         | HD68A09P                   | HD68A09P                   | MC68A09P        |

| 8/16 bit microprocessing unit, 2mhz                           | HD68B09P                   | HD68B09P                   | MC68B09P        |

| 8 bit microprocessing unit, 1mhz                              | HD46800DP                  | HD6800P                    | MC6800P         |

| 8 bit microprocessing unit, 1.5mhz                            | HD468A00P                  | HD68A00P                   | MC68A00P        |

| 8 bit microprocessing unit, 2mhz                              | HD468B00P                  | HD68B00P                   | MC68B00P        |

| 8 bit microprocessing unit, 1mhz                              | HD46802SP                  | HD6802SP                   | MC6802P         |

| with clock and 128 bytes RAM                                  |                            |                            |                 |

| 8 bit microprocessing unit, 1mhz with clock and 256 bytes RAM |                            | HD6802WP                   |                 |

| 128 x 8 static RAM, 450ns access time                         | HM46810P                   | HD6810P                    | MC6810P         |

| 128 x 8 static RAM, 360ns access time                         | HM468A10P                  | HD68A10P                   | MC68A10P        |

| Peripheral interface adapter, 1mhz                            | HD46821P                   | HD6821P                    | MC6821P         |

| Peripheral interface adapter, 1.5mhz                          | HD468A21P                  | HD68A21P                   | MC68A21P        |

| Peripheral interface adapter, 2mhz                            | HD468B21P                  | HD68B21P                   | MC68B21P        |

| Programmable timer module, 1mhz                               |                            | HD6840P                    | MC6840P         |

| Programmable timer module, 1.5mhz                             |                            | HD68A40P                   | MC68A40P        |

| Programmable timer module, 2mhz                               |                            | HD68B40P                   | MC68B40P        |

| Floppy disk controller, 1mhz                                  | HD46503SP                  | HD6843SP                   | MC6843P         |

| Floppy disk controller, 1.5mhz                                | HD46503SP-1                | HD68A43SP                  | MC68A43P        |

| 8 bit DMA controller, 1mhz                                    | HD46504RP                  | HD6844P                    | MC6844P         |

| 8 bit DMA controller, 1.5mhz                                  | HD46504RP-1                | HD68A44P                   | MC68A44P        |

| 8 bit DMA controller, 2mhz                                    | HD46504RP-2                | HD68B44P                   | MC68B44P        |

| CRT controller, 1mhz                                          | HD46505RP                  | HD6845RP                   | MC6845P         |

| CRT controller, 1.5mhz                                        | HD46505RP-1                | HD68A45RP                  | MC68A45P        |

| CRT controller, 2mhz                                          | HD46505RP-2                | HD68B45RP                  | MC68B45P        |

| CRT controller (enhanced), 1 mhz                              | HD46505SP                  | HD6845SP                   |                 |

| CRT controller (enhanced), 1.5mhz                             | HD46505SP-1                | HD68A45SP                  |                 |

| CRT controller (enhanced), 2mhz                               | HD46505SP-2                | HD68B45SP                  |                 |

| ROM, I/O, Timer combo, 1mhz                                   | <del></del>                | HD6846P                    | MC6846P         |

| Asynchronous comm interface, 1mhz                             | HD46850P                   | HD6850P                    | MC6850P         |

| Asynchronous comm interface, 1.5mhz                           | HD468A50P                  | HD68A50P                   | MC68A50P        |

| Synchronous comm interface, 1mhz                              | HD46852P                   | HD6852P                    | MC6852P         |

| Synchronous comm interface, 1.5mhz                            | HD468A52P                  | HD68A52P                   | MC68A52P        |

| Analog data acquisition unit, 1mhz                            | HD46508P                   | HD46508P                   |                 |

| Analog data acquisition unit, 1.5mhz                          | HD46508P-1                 | HD46508P-1                 |                 |

| Analog data acquisition unit, 1mhz (enhanced)                 | HD46508PA                  | HD46508PA                  |                 |

| Analog data acquisition unit, 1.5mhz (enhanced)               | HD46508PA-1                | HD46508PA-1                |                 |

Figure 1. Hitachi Microprocessor/Peripheral Cross Reference

#### NEW HITACHI MICROPROCESSOR NUMBERING SYSTEM

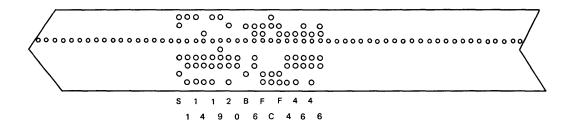

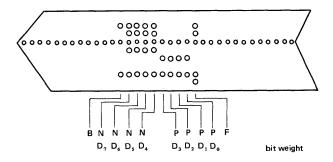

(a) Present marking

(b) New marking

Figure 2.

### **HD6800, HD68A00, HD68B00**

#### **MPU (Micro Processing Unit)**

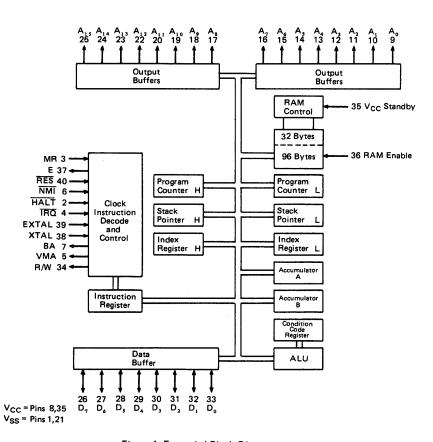

The HD6800 is a monolithic 8-bit microprocessor forming the central control function for Hitachi's HMCS6800 family. Compatible with TTL, the HD6800 as with all HMCS6800 system parts, requires only one 5V power supply, and no external TTL devices for bus interface. The HD68A00 and HD68B00 are high speed versions.

The HD6800 is capable of addressing 65K bytes of memory with its 16-bit address lines. The 8-bit data bus is bi-directional as well as 3-state, making direct memory addressing and multiprocessing applications realizable.

#### ■ FÉATURES

- Versatile 72 Instruction Variable Length (1~3 Byte)

- Seven Addressing Modes Direct, Relative, Immediate, Indexed, Extended, Implied and Accumulator

- Variable Length Stack

- Vectored Restart

- Maskable Interrupt

- Separate Non-Maskable Interrupt Internal Registers Saved in Stack

- Six Internal Registers Two Accumulators, Index Register, Program Counter, Stack Pointer and Condition Code Register

- Direct Memory Accessing (DMA) and Multiple Processor Capability

- Clock Rates as High as 2.0 MHz (HD6800 ... 1 MHz, HD68A00 ... 1.5 MHz, HD68B00 ... 2.0 MHz)

- Halt and Single Instruction Execution Capability

- Compatible with MC6800, MC68A00 and MC68B00

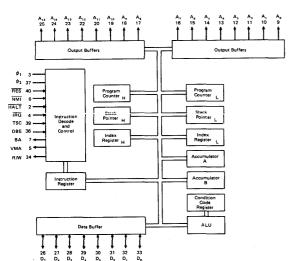

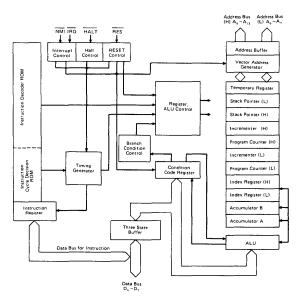

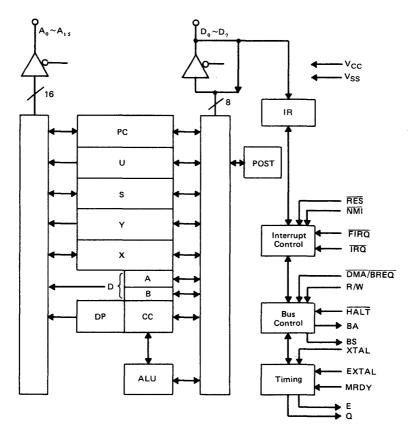

#### **■ BLOCK DIAGRAM**

#### PIN ARRANGEMENT

#### ■ ABSOLUTE MAXIMUM RATINGS

| Item                  | Symbol            | Value                     | Unit |

|-----------------------|-------------------|---------------------------|------|

| Supply Voltage        | V <sub>cc</sub> * | <b>-0.3</b> ∼ <b>+7.0</b> | V    |

| Input Voltage         | V <sub>in</sub> * | -0.3 ∼ +7.0               | V    |

| Operating Temperature | Topr              | - 20 ~ + 75               | °C   |

| Storage Temperature   | T <sub>stg</sub>  | - 55 ∼ +150               | °C   |

<sup>\*</sup> With respect to V<sub>SS</sub> (SYSTEM GND)

#### **■ RECOMMENDED OPERATING CONDITION**

| Item                  | Symbol            | min  | typ | max             | Unit |

|-----------------------|-------------------|------|-----|-----------------|------|

| Supply Voltage        | V <sub>cc</sub> * | 4.75 | 5   | 5.25            | V    |

| Inmus Valsana         | V <sub>IL</sub> * | -0.3 | _   | 0.8             | V    |

| Input Voltage         | V <sub>1H</sub> * | 2.0  | _   | V <sub>cc</sub> | V    |

| Operating Temperature | T <sub>opr</sub>  | -20  | 25  | 75              | °c   |

<sup>\*</sup> With respect to  $V_{SS}$  (SYSTEM GND)

#### ■ ELECTRICAL CHARACTERISTICS

#### • DC CHARACTERISTICS (V<sub>CC</sub> = 5V $\pm$ 5%, V<sub>SS</sub> = 0V, Ta = -20 $^{\sim}$ +75 $^{\circ}$ C, unless otherwise noted.)

| Item                       |                                                  | Symbol           | Test Condition                                     | min                   | typ* | max                   | Unit |

|----------------------------|--------------------------------------------------|------------------|----------------------------------------------------|-----------------------|------|-----------------------|------|

| Input "High" Voltage       | Logic**                                          | V <sub>IH</sub>  |                                                    | V <sub>SS</sub> + 2.0 | _    | V <sub>cc</sub>       | ٧    |

| Input "Low" Voltage        | Logic**                                          | VIL              |                                                    | V <sub>SS</sub> - 0.3 |      | V <sub>SS</sub> + 0.8 | ٧    |

| Clock Input "High" Voltage | $\phi_1$ , $\phi_2$                              | V <sub>IHC</sub> |                                                    | V <sub>CC</sub> - 0.6 |      | V <sub>CC</sub> + 0.3 | ٧    |

| Clock Input "Low" Voltage  | $\phi_1$ , $\phi_2$                              | VILC             |                                                    | V <sub>SS</sub> - 0.3 | _    | V <sub>SS</sub> + 0.4 | ٧    |

|                            | D <sub>0</sub> ~D <sub>7</sub>                   |                  | I <sub>OH</sub> = -205μA                           | V <sub>SS</sub> + 2.4 |      | _                     | ٧    |

| Output "High" Voltage      | A <sub>0</sub> ~A <sub>15</sub> , R/W<br>VMA     | V <sub>OH</sub>  | I <sub>OH</sub> = -145μA                           | V <sub>SS</sub> + 2.4 | _    | -                     | V    |

|                            | ВА                                               |                  | I <sub>OH</sub> = -100μA                           | V <sub>SS</sub> + 2.4 | _    | -                     | ٧    |

| Output"Low" Voltage        |                                                  | VoL              | I <sub>OL</sub> = 1.6mA                            | _                     | _    | V <sub>SS</sub> + 0.4 | V    |

|                            | Logic***                                         | lin              | V <sub>in</sub> = 0~5.25V,                         | _                     | 1.0  | 2.5                   | μΑ   |

| Input Leakage Current      | $\phi_1$ , $\phi_2$                              | 'in              | All other pins are connected to GND                | _                     | _    | 100                   | μΑ   |

| Three-State (Off-state)    | D <sub>0</sub> ~D <sub>7</sub>                   | I <sub>TSI</sub> | V <sub>in</sub> = 0.4 ~ 2.4V                       | - 1                   | 2.0  | 10                    | μΑ   |

| Input Current              | A <sub>0</sub> ~A <sub>15</sub> , R/W            | 'ISI             | V <sub>in</sub> - 0.4 - 2.4 V                      | _                     |      | 100                   | μΑ   |

| Power Dissipation          |                                                  | Po               |                                                    | _                     | 0.5  | 1.0                   | W    |

|                            | Logic***                                         |                  |                                                    |                       | 6.5  | 10                    | pF   |

| Input Capacitance          | D <sub>0</sub> ~D <sub>7</sub>                   | C <sub>in</sub>  | $V_{in} = 0V$ , $Ta = 25^{\circ}C$ ,               | -                     | 10   | 12.5                  | pF   |

| impar Suparitance          | $\phi_1$                                         | ] Sin            | f = 1 MHz                                          | _                     | 25   | 35                    | рF   |

|                            | $\phi_2$                                         | 1                |                                                    | -                     | 45   | 70                    | pF   |

| Output Capacitance         | A <sub>0</sub> ~A <sub>15</sub> , R/W<br>VMA, BA | Cout             | $V_{in} = 0V$ , $Ta = 25^{\circ}C$ ,<br>f = 1  MHz | _                     | _    | 12                    | pF   |

<sup>(</sup>NOTE) Permanent LSI damage may occur if maximum rating are exceeded. Normal operation should be under recommended operating conditions. If these conditions are exceeded, it could affect reliability of LSI.

<sup>\*</sup> Ta = 25°C,  $V_{CC}$  = 5V \*\* All inputs except  $\phi_1$  and  $\phi_2$ \*\*\* All inputs except  $\phi_1$ ,  $\phi_2$  and  $D_0 \sim D_7$

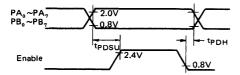

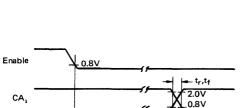

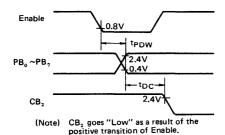

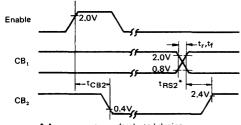

#### • AC CHARACTERISTICS

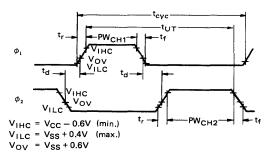

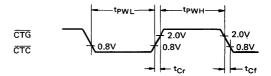

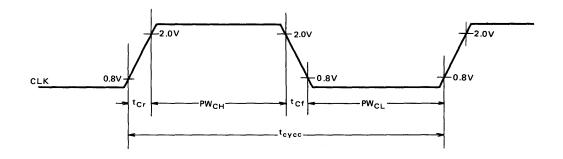

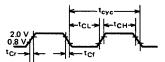

#### 1. TIMING CHARACTERISTICS OF CLOCK PULSE $\phi_1$ and $\phi_2$

| Item                |                       | Symbol                                | Test      | Н     | D6800 |       | Н     | D68A0 | 00    | Н     | Unit |       |      |

|---------------------|-----------------------|---------------------------------------|-----------|-------|-------|-------|-------|-------|-------|-------|------|-------|------|

| rtem                |                       | Symbol                                | Condition | min   | typ   | max   | min   | typ   | max   | min   | typ  | max   | Onit |

| Frequency of Operat | tion                  | f                                     |           | 0.1   | -     | 1.0   | 0.1   | _     | 1.5   | 0.1   |      | 2.0   | MHz  |

| Cycle Time          |                       | t <sub>cyc</sub>                      | Fig. 10   | 1.000 | _     | 10    | 0.666 | _     | 10    | 0.500 | _    | 10    | μs   |

| Clock Pulse Width   | $\phi_1$ , $\phi_2$   | PW <sub>CH1</sub> , PW <sub>CH2</sub> | Fig. 10   | 400   | _     | 4,500 | 230   | _     | 4,500 | 180   |      | 4,500 | ns   |

| Rise and Fall Times | $\phi_1,\phi_2$       | t <sub>r</sub> , t <sub>f</sub>       | Fig. 10   | _     | _     | 100   | _     | _     | 100   | _     | -    | 100   | ns   |

| Delay Time (Clock I | nternal)              | t <sub>d</sub>                        | Fig. 10   | _     | _     | 4,500 | _     |       | 4,500 | ,     | _    | 4,500 | ns   |

| Clock "High" Level  | ock "High" Level Time |                                       | Fig. 10   | 900   |       | _     | 600   | _     | _     | 440   | _    |       | ns   |

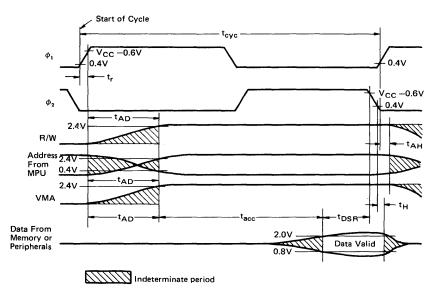

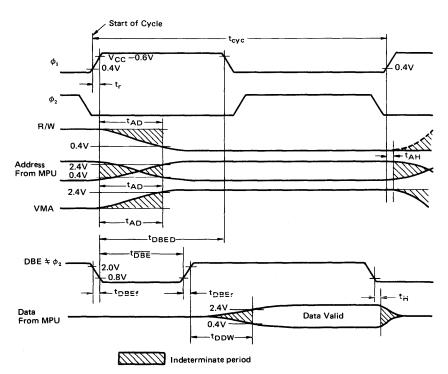

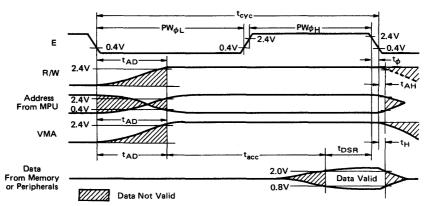

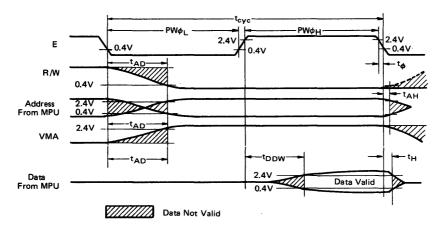

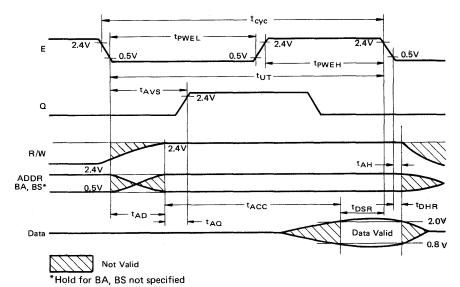

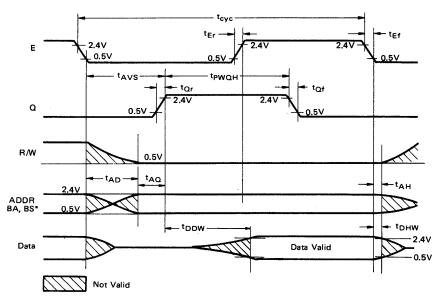

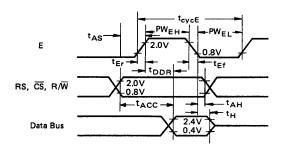

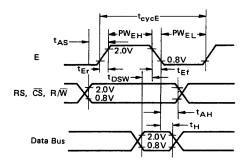

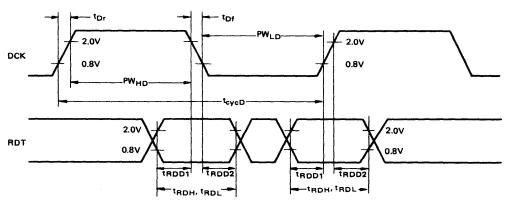

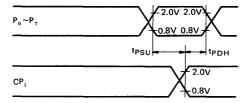

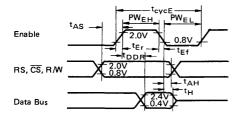

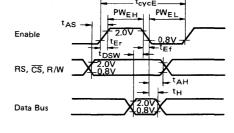

#### 2. READ/WRITE CHARACTERISTICS

| Item                                                                              |                        | Symbol                               | Test                | 1   | 1D6800 | )   | Н   | D68A0 | 0   | Н   | D68B0 | 00  | Unit |

|-----------------------------------------------------------------------------------|------------------------|--------------------------------------|---------------------|-----|--------|-----|-----|-------|-----|-----|-------|-----|------|

| Item                                                                              |                        | Зуппоот                              | Condition           | min | typ    | max | min | typ   | max | min | typ   | max | Onit |

| Address Delay                                                                     | C=90pF                 | t <sub>AD1</sub>                     | Fig. 11,<br>Fig. 12 | _   | _      | 270 | _   | _     | 180 | _   | _     | 150 | ns   |

| Time                                                                              | C=30pF                 | t <sub>AD2</sub>                     | Fig. 11,<br>Fig. 12 | _   | _      | 250 | _   | -     | 165 | -   | _     | 135 | ns   |

| Data Setup Time (Re                                                               | ad)                    | t <sub>DSR</sub>                     | Fig. 11             | 100 | _      | _   | 60  | _     | _   | 40  |       |     | ns   |

| Peripheral Read Acce<br>t <sub>acc</sub> = t <sub>UT</sub> - (t <sub>AD</sub> + t |                        | t <sub>acc</sub>                     | Fig. 11             | _   | _      | 530 | _   | _     | 360 | -   | _     | 250 | ns   |

| Input Data Hold Time                                                              |                        | t <sub>H</sub>                       | Fig. 11             | 10  | _      | _   | 10  | _     | _   | 10  | _     | _   | ns   |

| Output Data Hold Time                                                             |                        | t <sub>H</sub>                       | Fig. 12             | 20  |        | _   | 20  | _     | _   | 20  | _     | _   | ns   |

| Address Hold Time<br>(Address, R/W, VMA)                                          |                        | t <sub>AH</sub>                      | Fig. 11,<br>Fig. 12 | 10  | _      | _   | 10  | _     | -   | 10  | _     | _   | ns   |

| Enable "High" Time Input                                                          | for DBE                | t <sub>EH</sub>                      | Fig. 12             | 450 | _      | -   | 280 | _     | _   | 220 | -     | -   | ns   |

| Data Delay Time (Wr                                                               | rite) t <sub>DDW</sub> |                                      | Fig. 12             | _   | _      | 225 | _   | _     | 200 | -   | _     | 160 | ns   |

| Data Bus Enable Dov<br>(During $\phi_1$ Up Time)                                  |                        | tobe                                 | Fig. 12             | 150 | _      | _   | 120 | _     | -   | 75  | _     | -   | ns   |

| Data Bus Enable Dela                                                              | ay Time                | t <sub>DBED</sub>                    | Fig. 12             | 300 | _      | _   | 250 | _     | _   | 180 | _     | _   | ns   |

| Data Bus Enable<br>Rise and Fall Times                                            |                        | t <sub>DBEr</sub>                    | Fig. 12             | _   | _      | 25  | -   | _     | 25  | -   | _     | 25  | ns   |

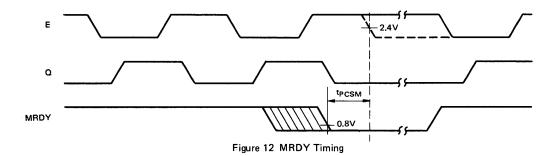

| Processor Control Se                                                              | tup Time               | t <sub>PCS</sub>                     |                     | 200 | -      | _   | 140 | _     | _   | 110 | _     | _   | ns   |

| Processor Control<br>Rise and Fall Times                                          |                        | t <sub>PCr</sub><br>t <sub>PCf</sub> |                     | _   | -      | 100 | _   | _     | 100 | -   | -     | 100 | ns   |

| Bus Available Delay                                                               | Time (BA)              | t <sub>BA</sub>                      |                     | -   | -      | 250 |     | -     | 165 | -   |       | 135 | ns   |

| Three-State Delay Ti                                                              | me                     | t <sub>TSD</sub>                     |                     |     | _      | 270 | _   | -     | 270 | -   | _     | 220 | ns   |

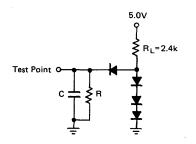

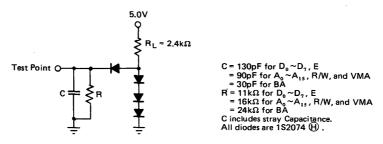

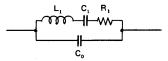

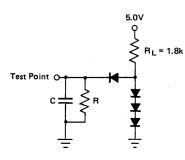

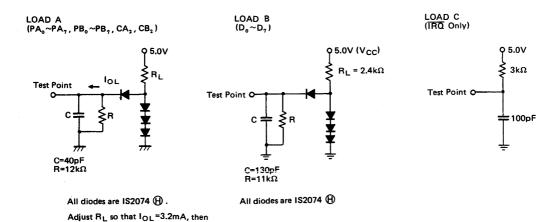

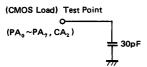

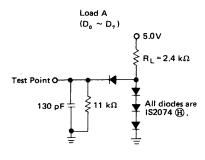

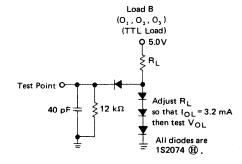

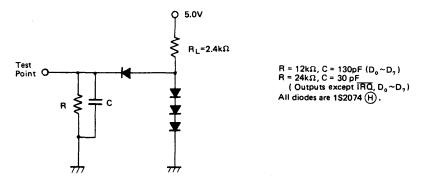

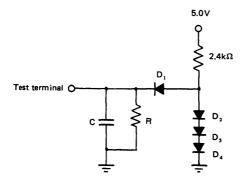

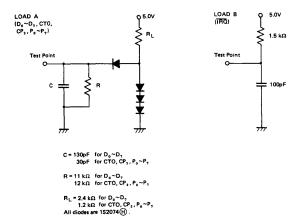

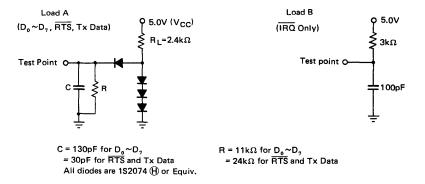

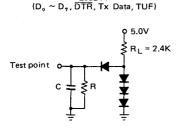

Figure 1 Bus Timing Test Load

C = 130pF for  $D_0 \sim D_7$ = 90pF for  $A_0 \sim A_{15}$ , R/W, and VMA

<sup>= 30</sup>pF for BA

R = 11k $\Omega$  for D<sub>0</sub> ~D<sub>7</sub>

<sup>= 16</sup>k $\Omega$  for  $A_0 \sim A_{15}$ , R/W and VMA

<sup>= 24</sup>kΩ for BA

C includes Stray Capacitance. All diodes are 1S2074().

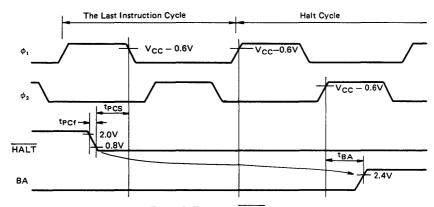

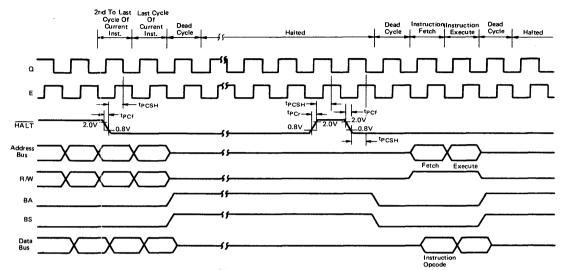

Figure 2 Timing of HALT and BA

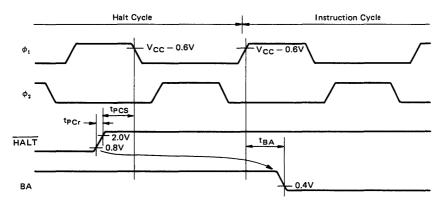

Figure 3 Timing of HALT and BA

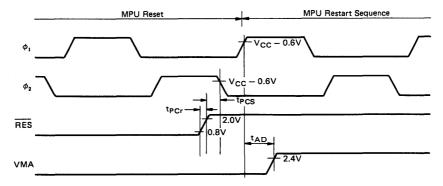

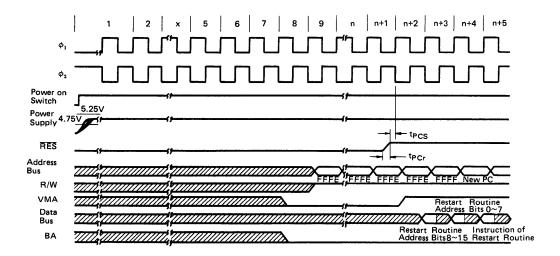

Figure 4 RES and MPU Restart Sequence

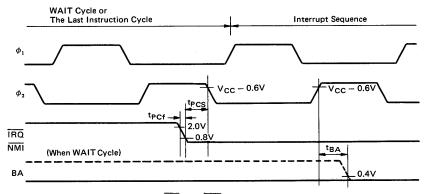

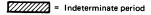

Figure 5 IRQ and NMI Interrupt Timing

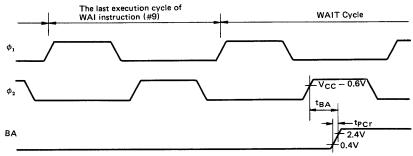

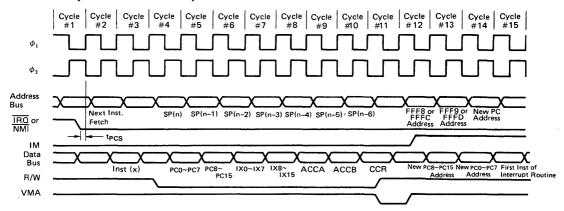

Figure 6 WAI Instruction and BA Timing

Figure 7 TSC Input and MPU Output

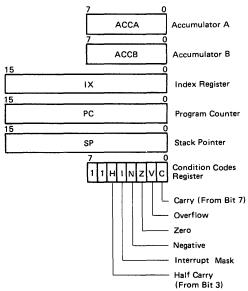

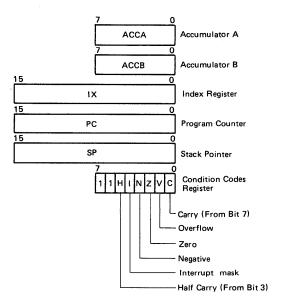

#### ■ MPU REGISTERS

The MPU provides several registers in Fig. 8, which is available for use by the programmer.

Each register is described below.

#### Program Counter (PC)

The program counter is a two byte (16-bit) register that points to the current program address.

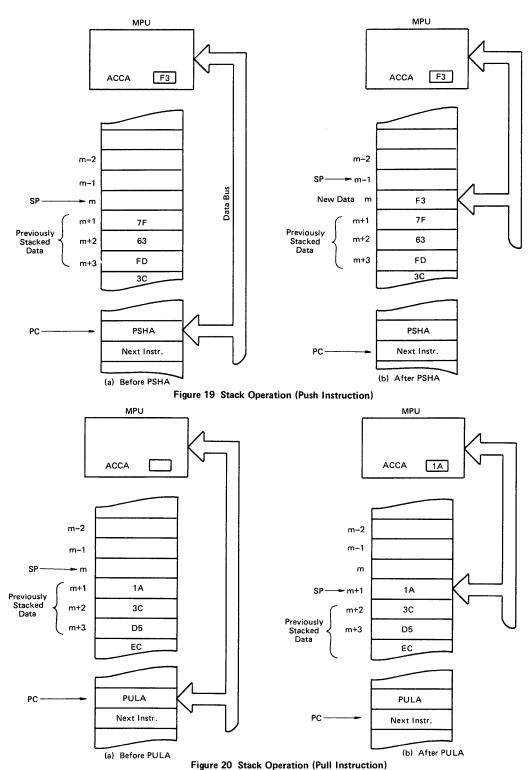

#### Stack Pointer (SP)

The stack pointer is a two byte register that contains the address of the next available location in an external push-down/pop-up stack. This stack is normally a random access Read/Write memory that may have any location (address) that is convenient. In those applications that require storage of information in the stack when power is lost, the stack must be non-volatile.

#### Index Register (IX)

The index register is a two byte register that is used to store data or a sixteen bit memory address for the Indexed mode of memory addressing.

#### Accumulators (ACCA, ACCB)

The MPU contains two 8-bit accumulators that are used to hold operands and results from an arithmetic logic unit (ALU).

Figure 8 Programming Model of the Microprocessing Unit

#### Condition Code Register (CCR)

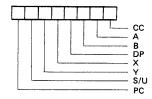

The condition code register indicates the results of an Arithmetic Logic Unit operation: Negative (N), Zero (Z), Overflow (V), Carry from bit 7 (C), and half carry from bit 3(H). These bits of the Condition Code Register are used as testable conditions for the conditional branch instructions. Bit 4 is the interrupt mask bit (I). The unused bits of the Condition Code Register (b6 and b7) are "1". The detail block diagram of the microprossing unit is shown in Fig. 9.

Figure 9 Internal Block Diagram of MPU

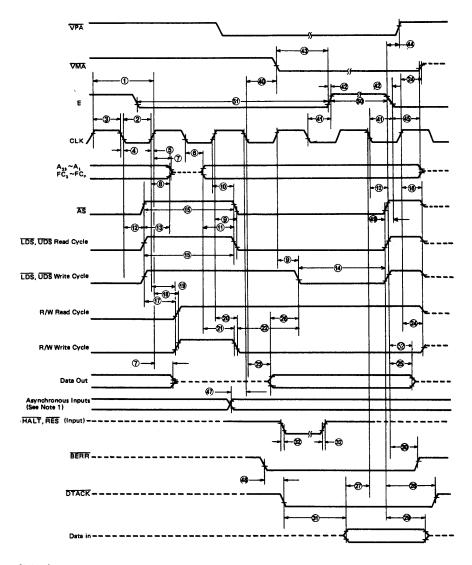

#### MPU SIGNAL DESCRIPTION

Proper operations of the MPU requires that certain control and timing signals (Fig. 9) be provided to accomplish specific functions. The functions of pins are explained in this section.

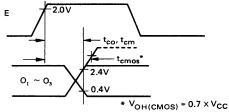

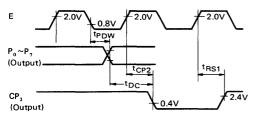

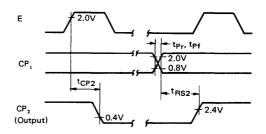

#### • Clock $(\phi_2, \phi_2)$

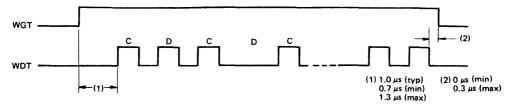

Two pins are used to provide the clock signals. A two-phase non-overlapping clock is provided as shown in Fig. 10.

Figure 10 Clock Timing Waveform

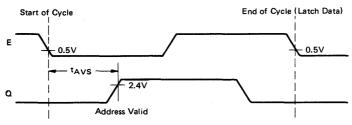

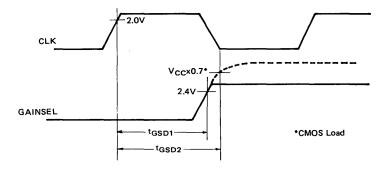

#### Address Bus (A<sub>0</sub>~A<sub>15</sub>)

Sixteen pins are used for the address bus. The outputs are three-state bus drivers capable of driving one standard TTL load and 90pF. When the output is turned off, it is essentially an open circuit. This permits the MPU to be used in DMA applications. Putting TSC in its high state forces the Address bus to go into the three-state mode.

#### Data Bus (D<sub>0</sub>∼D<sub>7</sub>)

Eight pins are used for the data bus. It is bidirectional, transferring data to and from the memory and peripheral devices. It also has three-state output buffers capable of driving one standard TTL load and 130pF. Data Bus is placed in the three-state mode when DBE is "Low."

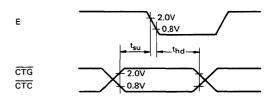

Figure 11 Read from Memory or Peripherals

Figure 12 Write to Memory of Peripherals

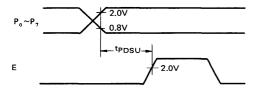

#### Data Bus Enable (DBE)

This input is the three-state control signal for the MPU data bus and will enable the bus drivers when in the "High" state; will make the bus driver off when in the "Low" state. This input is TTL compatible; however in normal operation, it would be driven by  $\phi_2$  clock. During an MPU read cycle, the data bus drivers will be disabled internally. When it is desired that another device control the data bus such as in Direct Memory Access (DMA) applications, DBE should be held "Low."

If additional data setup or hold time is required on an MPU write, the DBE down time can be decreased as shown in Fig. 13 (DBE  $\neq \phi_2$ ). The minimum down time for DBE is  $t_{\overline{DBE}}$  as shown and must occur within  $\phi_1$  up time. As for the characteristical values in Fig. 12, refer to the table of electrical characteristics.

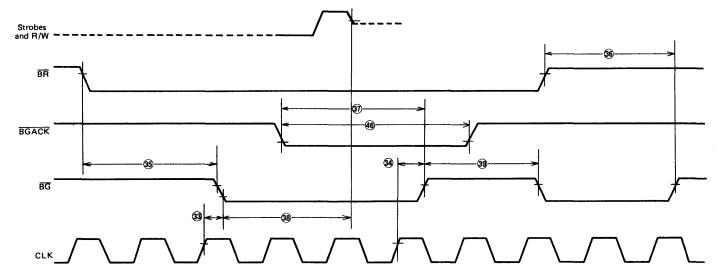

#### Bus Available (BA)

The BA signal will normally be in the "Low" state. When activated, it will go to the "High" state indicating that the microprocessor has stopped and that the address bus is available. This will occur if the  $\overline{HALT}$  line is in the "Low" state or the processor is in the WAIT state as a result of the execution of a WAIT instruction. At such time, all three-state output drivers will go to their off state and other outputs to their normally inactive level. The processor is removed from the WAIT state by the occurrence of a maskable (mask bit I = 0) or nonmaskable interrupt. This output is capable of driving one standard TTL load and 30pF. If TSC is in the "High" state, Bus Available will be "Low".

#### Read/Write (R/W)

This TTL compatible output signals the peripherals and memory devices whether the MPU is in a Read ("High") or

Write ("Low") state. The normal standby state of this signal is Read ("High"). Three-State Control going "High" will turn R/W to the off (high impedance) state. Also, when the processor is halted, it will be in the off state. This output is capable of driving one standard TTL load and 90pF.

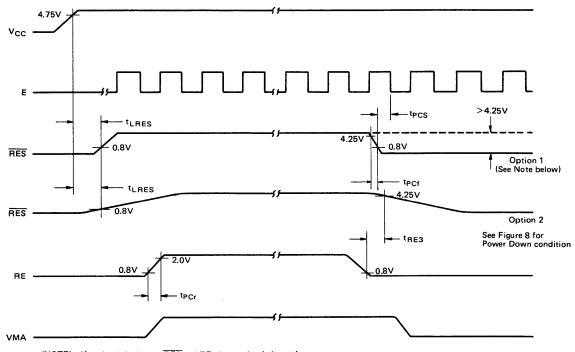

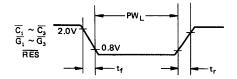

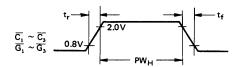

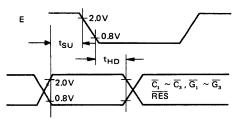

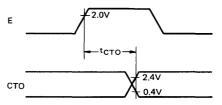

#### Reset (RES)

The RES input is used to reset and start the MPU from a power down condition resulting from a power failure or initial start-up of the processor. This input can also be used to reinitialize the machine at any time after start-up.

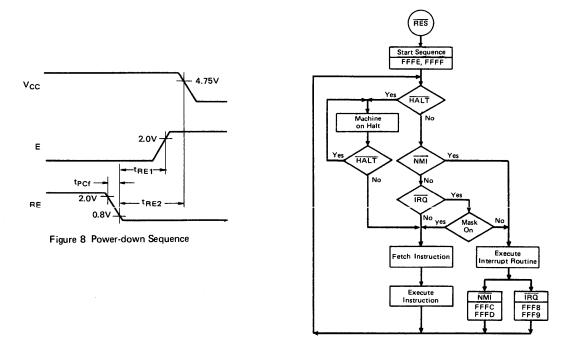

If a "High" level is detected in this input, this will signal the MPU to begin the reset sequence. During the reset sequence, the contents of the last two locations (FFFE, FFFF) in memory will be loaded into the Program Counter to point to the beginning of the reset routine. During the reset routine, the interrupt mask bit is set and must be cleared under program control before the MPU can be interrupted by IRQ. While RES is "Low" (assuming a minimum of 8 clock cycles have occured) the MPU output signals will be in the following states: VMA = "Low", BA = "Low", Data Bus = high impedance, R/W = "High" (read state), and the Address Bus will contain the reset address FFFE. Fig. 13 illustrates a power up sequence using the Reset control line. After the power supply reaches 4.75V, a minimum of eight clock cycles are required for the processor to stabilize in preparation for restarting. During these eight cycles, VMA will be in an indeterminate state so any devices that are enabled by VMA which could accept a false write during this time (such as a battery-backed RAM) must be disabled until VMA is forced "Low" after eight cycles. RES can go "High" asynchronously with the system clock any time after the eighth cycle.

Figure 13 RES Timing

The Reset control line may also be used to reinitialize the MPU system at any time during its operation. This is accomplished by pulsing RES "Low" for the duration of a minimum of three complete  $\phi_2$  cycles. The RES pulse can be completely asynchronous with the MPU system clock and will be recognized during  $\phi_2$  if setup time  $t_{PCS}$  is met.

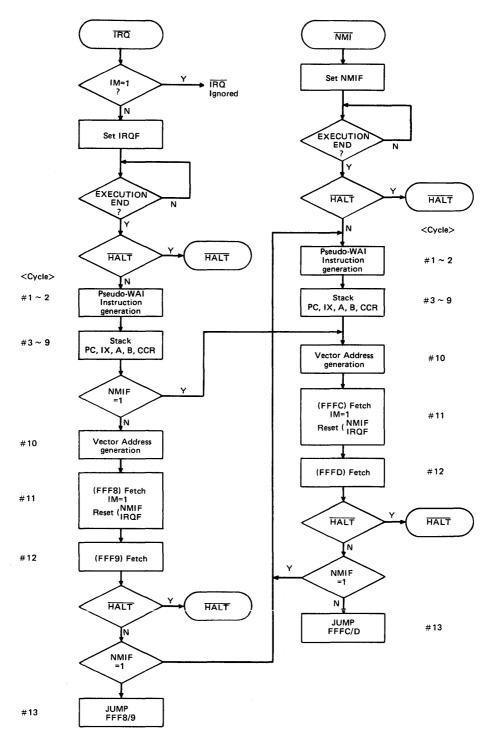

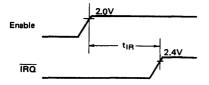

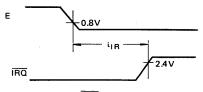

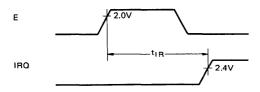

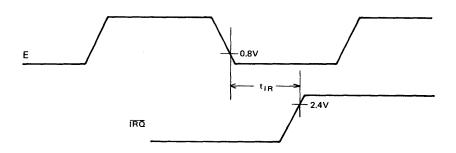

#### Interrupt Request (IRQ)

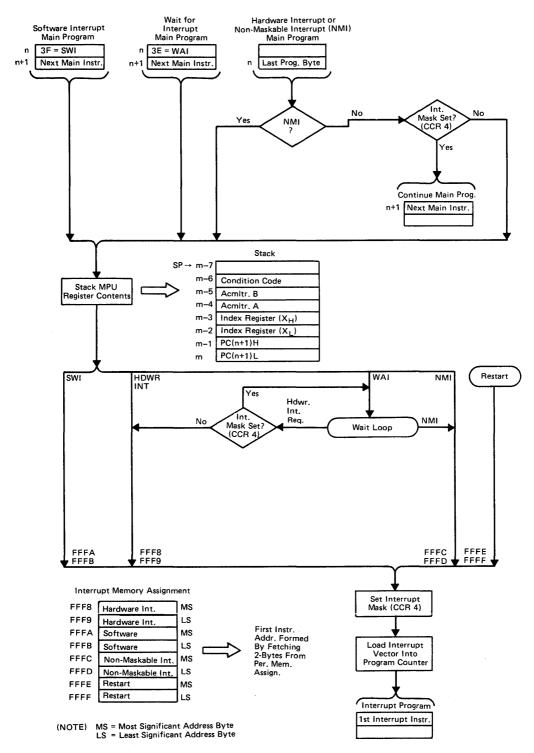

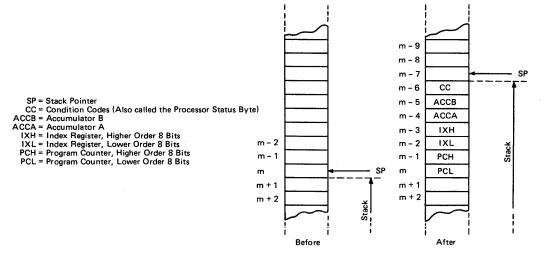

This level sensitive input requests that an interrupt sequence be generated within the machine. The processor will wait until it completes the current instruction that is being executed before it recognizes the request. If the interrupt mask bit in the Condition Code Register is not set, the machine will begin an interrupt sequence. The Index Register, Program Counter, Accumulators, and Condition Code Register are stored away on the stack.

Next the MPU will respond to the interrupt request by setting the interrupt mask bit "1" so that no further interrupts may occur. At the end of the cycle, a 16-bit address will be loaded that points to a vectoring address which is located in memory locations FFF8 and FFF9. An address loaded at these locations causes the MPU to branch to an interrupt routine in memory. Interrupt timing is shown in Fig. 14.

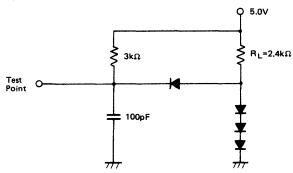

The  $\overline{HALT}$  line must be in the "High" state for interrupts to be serviced. Interrupts will be latched internally while  $\overline{HALT}$  is "Low". The  $\overline{IRQ}$  has a high impedance pullup device internal to the chip; however a  $3k\Omega$  external resistor to  $V_{CC}$  should be used for wire-OR and optimum control of interrupts.

#### Non-Maskable Interrupt (NMI) and Wait for Interrupt (WAI)

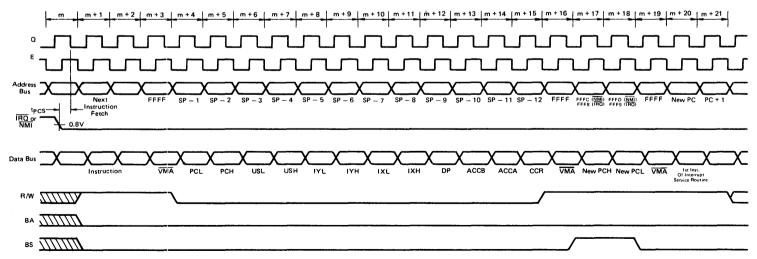

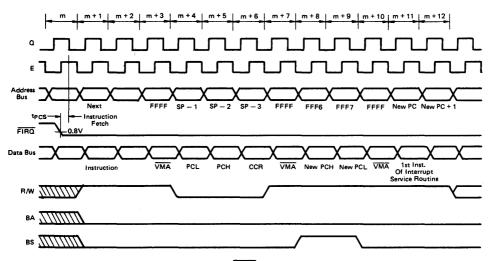

The MPU is capable of handling two types of interrupts: maskable ( $\overline{IRQ}$ ) as described earlier, and non-maskable ( $\overline{NMI}$ ).  $\overline{IRQ}$  is maskable by the interrupt mask in the Condition Code Register while  $\overline{NMI}$  is not maskable. The handling of these interrupts by the MPU is the same except that each has its own vector address. The behavior of the MPU when interrupted is shown in Fig. 14 which details the MPU response to an interrupt while the MPU is executing the control program. The interrupt shown could be either  $\overline{IRQ}$  or  $\overline{NMI}$  and can be asynchronous with respect to  $\phi_2$ . The interrupt is shown going "Low" at time  $t_{PCS}$  in cycle #1 which precedes the first cycle of an instruction ( $\overline{OP}$  code fetch). This instruction is not executed but instead the Program Counter ( $\overline{PC}$ ), Index Register ( $\overline{IX}$ ), accumulators ( $\overline{ACCX}$ ), and the Condition Code Register ( $\overline{CCR}$ ) are pushed onto the stack.

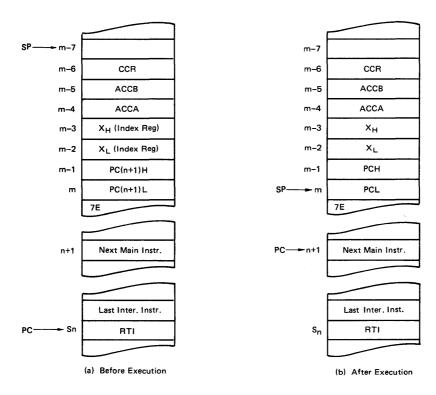

The Interrupt Mask bit is set to prevent further interrupts. The address of the interrupt service routine is then fetched from FFFC, FFFD for an NMI interrupt and from FFF8, FFF9 for an IRQ interrupt. Upon completion of the interrupt service routine, the execution of RTI will pull the PC, IX, ACCX, and CCR off of the stack; the Interrupt Mask bit is restored to its condition prior to interrupts. Fig. 15 is a similar interrupt sequence, except in this case, a WAIT instruction has been executed in preparation for the interrupt. This technique speeds up the MPU's response to the interrupt because the stacking of

Figure 14 Interrupt Timing

(NOTE) Midrange waveform indicates high impedance state

Figure 15 WAI Instruction Timing

the PC, IX, ACCX, and the CCR is already done.

While the MPU is waiting for the interrupt, Bus Available will go "High" indicating the following states of the control lines: VMA is "Low", and the Address Bus, R/W and Data Bus are all in the high impedance state. After the interrupt occurs, it is serviced as previously described.

Table 1 Memory Map for Interrupt Vectors

| Ve   | ctor | D                      |

|------|------|------------------------|

| MS   | LS   | Description            |

| FFFE | FFFF | Restart                |

| FFFC | FFFD | Non-maskable Interrupt |

| FFFA | FFFB | Software Interrupt     |

| FFF8 | FFF9 | Interrupt Request      |

Refer to Figure 18 for program flow for Interrupts.

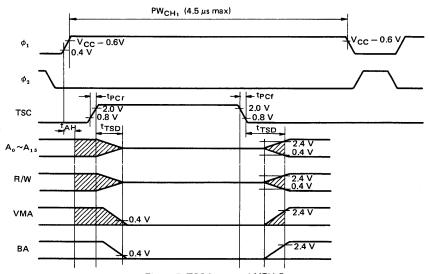

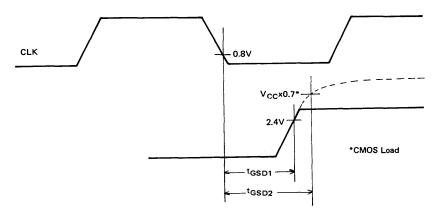

#### Three State Control (TSC)

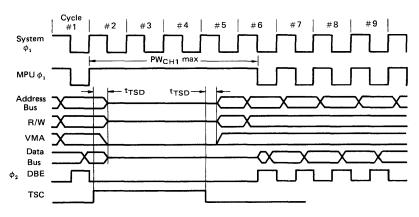

When the Three State Control (TSC) line is "High" level, the Address Bus and the R/W line are placed in a high impedance State. VMA and BA are forced "Low" when TSC = "High" to prevent false reads or writes on any device enabled by VMA. It is necessary to delay program execution while TSC is held "High". This is done by insuring that no transitions of  $\phi_1$  (or  $\phi_2$ ) occur during this period. (Logic levels of the clocks are irrelevant so long as they do not change.)

Since the MPU is a dynamic device, the  $\phi_1$  clock can be stopped for a maximum time PW<sub>CH1</sub> without destroying data within the MPU. TSC then can be used in a short Direct Memory Access (DMA) application.

Fig. 16 shows the effect of TSC on the MPU. The Address Bus and R/W line will reach the high impedance state at  $t_{TSD}$  (three-state delay), with VMA being forced "Low". In this example, the Data Bus is also in the high impedance state while  $\phi_2$  is being held "Low" since DBE= $\phi_2$ . At this point in time, a DMA transfer could occur on cycles #3 and #4. When TSC is returned "Low," the MPU address and R/W lines return to the bus. Because it is too late in cycle #5 to access memory, this cycle is dead and used for synchronization. Program execution resumes in cycle #6.

#### Valid Memory Address (VMA)

This output indicates to peripheral devices that there is a valid address on the address bus. In normal operation, this signal should be utilized for enabling peripheral interfaces such as the PIA and ACIA. This signal is not three-state. One standard TTL load and 90pF may be directly driven by this active "High" signal.

#### Halt (HALT)

When this input is in the "Low" state, all activity in the machine will be halted. This input is level sensitive.

The HALT line provides an input to the MPU to allow control or program execution by an outside source. If HALT is "High", the MPU will execute the instructions; if it is "Low", the MPU will go to a halted or idle mode. A response signal, Bus Available (BA) provides an indication of the current MPU status. When BA is "Low", the MPU is in the process of executing the control program; if BA is "High", the MPU has halted and all internal activity has stopped.

When BA is "High", the Address Bus, Data Bus, and R/W line will be in a high impedance state, effectively removing the MPU from the system bus. VMA is forced "Low" so that the floating system bus will not activate any device on the bus that is enabled by VMA.

While the MPU is halted, all program activity is stopped, and if either an  $\overline{NMI}$  or  $\overline{IRQ}$  interrupt occurs, it will be latched into the MPU and acted on as soon as the MPU is taken out of the halted mode. If a  $\overline{RES}$  command occurs while the MPU is halted, the following states occur: VMA = "Low", BA = "Low", Data Bus = high impedance, R/W = "High" (read state), and the Address Bus will contain address FFFE as long as  $\overline{RES}$  is "Low". As soon as the  $\overline{HALT}$  line goes "High", the MPU will go to locations FFFE and FFFF for the address of the reset routine.

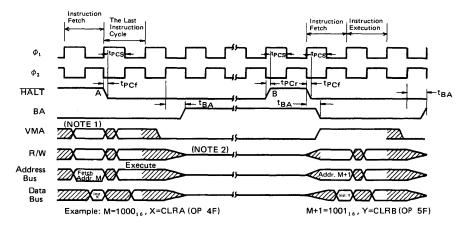

Fig. 18 shows the timing relationships involved when halting the MPU. The instruction illustrated is a one byte, 2 cycle instruction such as CLRA. When  $\overline{HALT}$  goes "Low", the MPU will halt after completing execution of the current instruction. The transition of  $\overline{HALT}$  must occur  $t_{PCS}$  before the trailing edge of  $\phi_1$  of the last cycle of an instruction (point A of Fig. 18).  $\overline{HALT}$  must not go "Low" any time later than the minimum  $t_{PCS}$  specified.

Figure 16 TSC Control Timing

Figure 17 MPU Interrupt Flow Chart

(NOTE) 1. Oblique lines indicate indeterminate range of data.

Midrange waveform indicates high impedance state.

Figure 18 HALT and Single Instruction Execution for System Dubug

Table 2 Operation States of MPU and Signal Outputs (Except the Execution of Instruction)

| Signals                          | Halt state | Reset state          | Halt and<br>Reset state | WAI state | TSC state |

|----------------------------------|------------|----------------------|-------------------------|-----------|-----------|

| ВА                               | "H"        | "L"                  | "L"                     | "H"       | "L"       |

| VMA                              | "L"        | "L"                  | "L"                     | "L"       | "L"       |

| R/W                              | "T"        | "H"                  | "H"                     | "Τ"       | "T"       |

| A <sub>0</sub> ~ A <sub>15</sub> | "T"        | (FFFE) <sub>16</sub> | (FFFE) <sub>16</sub>    | "T"       | "T"       |

| $D_0 \sim D_7$                   | "T"        | "T"                  | "T"                     | "T"       | -         |

<sup>&</sup>quot;T" indicates high impedance state.

The fetch of the OP code by the MPU is the first cycle of the instruction. If HALT had not been "Low" at Point A but went "Low" during  $\phi_2$  of the cycle, the MPU would have halted after completion of the following instruction. BA will go "High" by time  $t_{BA}$  (bus available delay time) after the last instruction cycle. At this point in time, VMA is "Low" and R/W, Address Bus, and the Data Bus are in the high impedance state.

To debug programs it is advantageous to step through programs instruction by instruction. To do this,  $\overline{\text{HALT}}$  must be brought "High" for one MPU cycle and then returned "Low" as shown at point B of Fig. 18. Again, the transitions of  $\overline{\text{HALT}}$  must occur  $\text{tp}_{CS}$  before the trailing edge of  $\phi_1$ . BA will go "Low" at  $t_{BA}$  after the leading edge of the next  $\phi_1$ , indicating that the Address Bus, Data Bus, VMA and R/W lines are back on the bus. A single byte, 2 cycle instruction such as LSR is used for this example also. During the first cycle, the instruction Y is fetched from address M+1. BA returns "High" at  $t_{BA}$  on the last cycle of the instruction indicating the MPU is off the bus, if instruction Y had been three cycles, the width of the BA "Low" time would have been increased by one cycle.

Table 2 shows the relation between the state of MPU and signal outputs.

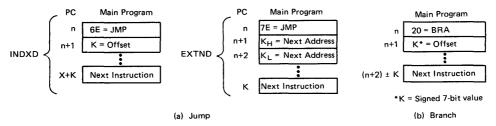

#### ■ MPU INSTRUCTION SET

This Section will provide a brief introduction and discuss their use in developing HD6800 MPU control programs. The HD6800 MPU has a set of 72 different executable source instructions. Included are binary and decimal arithmetic, logical, shift, rotate, load, store, conditional or unconditional branch, interrupt and stack manipulation instructions.

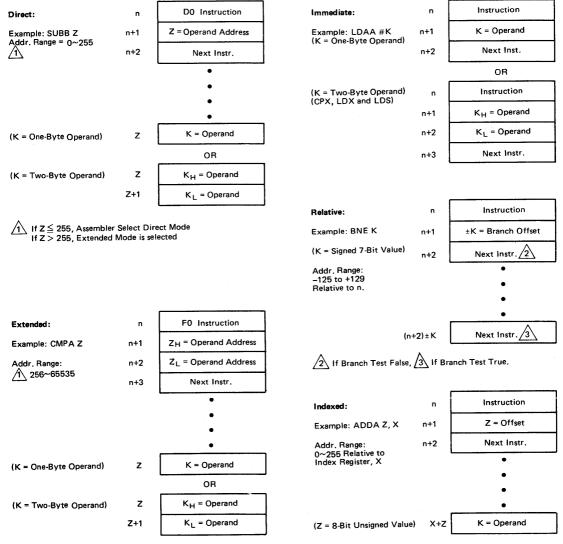

Each of the 72 executable instructions of the source language assembles into 1 to 3 bytes of machine code. The number of bytes depends on the particular instruction and on the addressing mode. (The addressing modes which are available for use with the various executive instructions are discussed later.)

The coding of the first (or only) byte corresponding to an executable instruction is sufficient to identify the instruction and the addressing mode. The hexadecimal equivalents of the binary codes, which result from the translation of the 72 instructions in all valid modes of addressing, are shown in Table 3. There are 197 valid machine codes, 59 of the 256 possible codes being unassigned.

When an instruction translates into two or three bytes of code, the second byte, or second and third bytes contain(s) an operand, an address, or information from which an address is obtained during execution.

Microprocessor instructions are often devided into three general classifications; (1) memory reference, so called because they operate on specific memory locations; (2) operating instructions that function without needing a memory reference; (3) I/O instructions for transferring data between the microprocessor and peripheral devices.

In many instances, the HD6800 MPU performs the same operation on both its internal accumulators and the external

memory locations. In addition, the HD6800 MPU allow the MPU to treat peripheral devices exactly like other memory locations, hence, no I/O instructions as such are required. Because of these features, other classifications are more suitable for introducing the HD6800's instruction set: (1) Accumulator and memory operations; (2) Program control operations; (3) Condition Code Register operations.

For Accumulator and Memory Operations, refer to Table 4.

Table 3 Hexadecimal Values of Machine Codes

| LSB<br>MSB | 0               | 1                           | 2                           | 3            | 4             | 5            | 6            | 7                           | 8            | 9               | A               | В            | С               | D            | E            | F            |

|------------|-----------------|-----------------------------|-----------------------------|--------------|---------------|--------------|--------------|-----------------------------|--------------|-----------------|-----------------|--------------|-----------------|--------------|--------------|--------------|

| 0          | •               | NOP<br>(IMP)                | •                           | •            | •             | •            | TAP<br>(IMP) | TPA<br>(IMP)                | INX<br>(IMP) | DEX<br>(IMP)    | CLV<br>(IMP)    | SEV<br>(IMP) | CLC<br>(IMP)    | SEC<br>(IMP) | CLI<br>(IMP) | SEI<br>(IMP) |

| 1          | SBA<br>(A, B)   | CBA<br>(A, B)               |                             |              | •             | •            | TAB<br>(IMP) | TBA<br>(IMP)                | •            | DAA<br>(IMP)    | *               | ABA<br>(IMP) | •               |              | •            | •            |

| 2          | BRA<br>(REL)    | •                           | BHI<br>(REL)                | BLS<br>(REL) | BCC<br>(REL)  | BCS<br>(REL) | BNE<br>(REL) | BEO<br>(REL)                | BVC<br>(REL) | BVS<br>(REL)    | BPL<br>(REL)    | BMI<br>(REL) | BGE<br>(REL)    | BLT<br>(REL) | BGT<br>(REL) | BLE<br>(REL) |

| 3          | TSX<br>(IMP)    | INS<br>(IMP)                | PUL<br>(A)                  | PUL<br>(B)   | DE\$<br>(IMP) | TXS<br>(IMP) | PSH<br>(A)   | PSH<br>(B)                  | *            | RTS<br>(IMP)    | •               | RTI<br>(IMP) | *               |              | WAI<br>(IMP) | SWI<br>(IMP) |

| 4          | NEG<br>(A)      | •                           | •                           | COM<br>(A)   | LSR<br>(A)    | •            | ROR<br>(A)   | ASR<br>(A)                  | ASL<br>(A)   | ROL<br>(A)      | DEC<br>(A)      | *            | INC<br>(A)      | TST<br>(A)   |              | CLR<br>(A)   |

| 5          | NEG<br>(B)      | •                           | •                           | COM<br>(B)   | LSR<br>(B)    | •            | ROR<br>(B)   | ASR<br>(B)                  | ASL<br>(B)   | ROL<br>(B)      | DEC<br>(B)      | •            | INC<br>(B)      | TST<br>(B)   | •            | CLR<br>(B)   |

| 6          | NEG<br>(IND)    | •                           |                             | COM<br>(IND) | LSR<br>(IND)  | •            | ROR<br>(IND) | ASR<br>(IND)                | ASL<br>(IND) | ROL<br>(IND)    | DEC<br>(IND)    | •            | INC<br>(IND)    | TST<br>(IND) | JMP          | CLR<br>(IND) |

| 7          | NEG<br>(EXT)    | •                           | •                           | COM<br>(EXT) | LSR<br>(EXT)  | •            | ROR<br>(EXT) | ASR<br>(EXT)                | ASL<br>(EXT) | ROL<br>(EXT)    | DEC<br>(EXT) *  |              | INC<br>(EXT)    | TST<br>(EXT) | JMP<br>(EXT) | CLR<br>(EXT) |

| 8          | SUB<br>(IMM)(A) | CMP<br>(IMM) <sup>(A)</sup> | SBC<br>(IMM) <sup>(A)</sup> | •            | AND<br>(IMM)  | BIT<br>(IMM) | LDA<br>(IMM) | •                           | EOR<br>(IMM) | ADC<br>(IMM)(A) | ORA<br>(IMM)    | ADD (A)      | CPX<br>(IMM)    | BSR<br>(REL) | LDS<br>(IMM) | •            |

| 9          | SUB<br>(DIR)    | CMP<br>(DIR)                | SBC (A)                     | •            | AND (A)       | BIT<br>(DIR) | LDA<br>(DIR) | STA<br>(DIR)                | EOR (A)      | ADC (A)         | ORA<br>(DIR)    | ADD (A)      | CPX<br>(DIR)    | •            | LDS<br>(DIR) | STS<br>(DIR) |

| A          | SUB<br>(IND)    | CMP (A)                     | SBC<br>(IND)                | *            | AND (A)       | BIT (A)      | LDA<br>(IND) | STA<br>(IND)                | EOR (A)      | ADC (A)         | ORA<br>(IND)    | ADD (A)      | CPX<br>(IND)    | JSR<br>(IND) | LDS<br>(IND) | STS<br>(IND) |

| В          | SUB (A)         | CMP<br>(EXT)                | SBC<br>(EXT)                | •            | AND<br>(EXT)  | BIT<br>(EXT) | LDA<br>(EXT) | STA<br>(EXT)                | EOR (A)      | ADC (A)         | ORA (A)         | ADD (A)      | CPX<br>(EXT)(A) | JSR<br>(EXT) | LDS<br>(EXT) | STS<br>(EXT) |

| С          | SUB (B)         | CMP (B)                     | SBC (B)                     | •            | AND<br>(IMM)  | BIT<br>(IMM) | LDA<br>(IMM) | *                           | EOR (B)      | ADC (B)         | ORA<br>(IMM)(B) | ADD (B)      | •               | *            | LDX<br>(IMM) | •            |

| D          | SUB (B)         | CMP<br>(DIR)                | SBC<br>(DIR)                |              | AND (B)       | BIT<br>(DIR) | LDA<br>(DIR) | STA (B)                     | EOR (B)      | ADC (B)         | ORA (B)         | ADD (B)      | •               | *            | LDX<br>(DIR) | STX<br>(DIR) |

| E          | SUB (B)         | CMP (B)                     | SBC (B)                     |              | AND (B)       | BIT<br>(IND) | LDA<br>(IND) | STA<br>(IND)                | EOR (B)      | ADC (B)         | ORA<br>(IND)    | ADD (B)      | •               |              | LDX<br>(IND) | STX<br>(IND) |

| F          | SUB (B)         | CMP (B)                     | SBC<br>(EXT)(B)             |              | AND (B)       | BIT<br>(EXT) | LDA<br>(EXT) | STA<br>(EXT) <sup>(B)</sup> | EOR (B)      | ADC (B)         | ORA (B)         | ADD (B)      |                 |              | LDX<br>(EXT) | STX<br>(EXT) |

DIR = Direct Addressing Mode

EXT = Extended Addressing Mode IMM = Immediate Addressing Mode

IND = Index Addressing Mode IMP = Implied Addressing Mode

REL = Relative Addressing Mode

A = Accumulator A B = Accumulator B

Table 4 Accumulator and Memory Operations

|                         |              |          |     | _ |          | _   |    | dress    |     |      |          |     |    |          |    |     | Boolean/                                                                                 | _      | _ | I. C     | _        |            | _        |

|-------------------------|--------------|----------|-----|---|----------|-----|----|----------|-----|------|----------|-----|----|----------|----|-----|------------------------------------------------------------------------------------------|--------|---|----------|----------|------------|----------|

| Operation               | Mnemonic     |          | ME  |   | <u> </u> | REC |    |          | DE) |      |          | TN  |    | IME      |    |     | Arithmetic Operation                                                                     | 5      | 4 | 3        | 2        | 1          | 0        |

|                         |              | OF       | · ~ | # | _        | `~  |    | _        | ~   | -    | _        | P ~ | -  | OF       | ~  | #   |                                                                                          | н      | 1 | N        | z        | V          | C        |

| Add                     | ADDA         | 8B       | 2   | 2 | 9B       | 3   | 2  | AB       | 5   | 2    | ВВ       |     | 3  |          |    |     | A + M → A                                                                                | ‡      | • | \$       | ‡        | ‡          | \$       |

|                         | ADDB         | СВ       | 2   | 2 | DB       | 3   | 2  | EB       | 5   | 2    | FB       | 4   | 3  |          | _  | ١.  | B + M → B                                                                                | \$     | • | \$       | ‡        | ‡          | ‡        |

| Add Acmitrs             | ABA          |          | ١.  |   |          | _   | _  | ١.,      |     |      |          | ١.  |    | 1B       | 2  | 1   | A + B → A                                                                                | \$     | : | \$       | ‡        | ‡          | #        |

| Add with Carry          | ADCA         | 89       | 2   | 2 | 99       | 3   | 2  | A9       | 5   | 2    | B9       | 4   | 3  |          |    |     | A + M + C → A                                                                            | ‡      | : | ‡        | \$       | ‡          | <b>‡</b> |

|                         | ADCB         | C9       | 2   | 2 | D9       | 3   | 2  | E9       | 5   | 2    | F9       | 4   | 3  |          |    |     | B + M + C → B<br>  A • M → A                                                             | ‡<br>• | : | ‡<br>‡   | ‡        | Ř          | \$       |

| And                     | ANDA         | 84<br>C4 | 2   | 2 | 94<br>D4 | 3   | 2  | A4<br>E4 | 5   | 2    | B4<br>F4 | 4   | 3  |          |    |     | B·M→B                                                                                    |        | • | Ť        | \$       | R          |          |

| Bit Test                | BITA         | 85       | 2   | 2 | 95       | 3   | 2  | A5       | 5   | 2    | B5       | 4   | 3  |          |    |     | A·M                                                                                      |        | • | 1        | ‡        | R          |          |

| Dit rest                | BITB         | C5       | 2   | 2 | D5       | 3   | 2  | E5       | 5   | 2    | F5       | 4   | 3  |          |    |     | B • M                                                                                    |        | • | 1        | ‡        | R          |          |

| Clear                   | CLR          | 03       | *   | - | 55       | 1   | 1  | 6F       | 7   | 2    | 7F       | 6   | 3  |          |    |     | 00 → M                                                                                   | •      | • | Ř        | š        | R          | R        |

| 0.55.                   | CLRA         |          | l   |   |          | ]   |    |          | 1   | -    |          | -   | ľ  | 4F       | 2  | 1   | 00 → A                                                                                   | •      | • | R        | s        | R          | R        |

|                         | CLRB         |          |     | l |          |     |    |          |     |      |          |     |    | 5F       | 2  | 1   | 00 → B                                                                                   | •      | • | R        | s        | R          | R        |

| Compare                 | CMPA         | 81       | 2   | 2 | 91       | 3   | 2  | A1       | 5   | 2    | В1       | 4   | 3  | 1        |    |     | A – M                                                                                    | •      | • | ‡        | \$       | \$         | 1        |

| • • • •                 | СМРВ         | C1       | 2   | 2 | D1       | 3   | 2  | E1       | 5   | 2    | F1       | 4   | 3  | l        |    |     | B M                                                                                      | •      | • | ‡        | t        | 1          | 1        |

| Compare Acmitrs         | CBA          |          |     | 1 |          |     |    |          |     |      |          |     |    | 11       | 2  | 1   | A – B                                                                                    | •      | • | 1        | 1        | ‡          | 1        |

| Complement, 1's         | сом          |          |     |   |          |     |    | 63       | 7   | 2    | 73       | 6   | 3  | i        |    |     | M→M                                                                                      | •      | • | 1        | ‡        | R          | S        |

|                         | COMA         |          |     |   |          |     |    |          |     |      |          | 1   |    | 43       | 2  | 1   | A→A                                                                                      | • i    | • | 1        | ‡        | R          | S        |

|                         | COMB         |          | ĺ   |   | 1        |     |    |          |     |      |          |     | 1  | 53       | 2  | 1   | B → B                                                                                    | •      | • | <b>‡</b> | \$       | R          | S        |

| Complement, 2's         | NEG          |          |     | 1 |          |     |    | 60       | 7   | 2    | 70       | 6   | 3  |          |    |     | 00 − M → M                                                                               | •      | • | \$       | ‡        | 1          |          |

| (Negate)                | NEGA         |          |     |   |          |     |    |          |     | ١.   |          |     |    | 40       | 2  | 1   | 00 - A → A                                                                               | •      | • | <b>‡</b> | ‡        | 0          |          |

|                         | NEGB         |          |     | İ | İ        |     |    |          |     |      | i        |     |    | 50       | 2  | 1   | 00 — B → B                                                                               | •      | • | 1        | \$       | 1          | 2        |

| Decimal Adjust, A       | DAA          |          |     |   |          | l   |    |          |     |      |          |     |    | 19       | 2  | 1   | Converts Binary Add of BCD                                                               | •      | • | ‡        | \$       | ‡          | 3        |

|                         |              |          |     | ļ |          |     |    |          |     | ١. ا |          |     | ١. |          |    |     | Characters into BCD Format                                                               |        |   | ١.       |          | _          | ١.       |

| Decrement               | DEC          |          |     |   |          |     |    | 6A       | 7   | 2    | 7A       | 6   | 3  |          | _  |     | $M-1 \rightarrow M$                                                                      | •      | • | 1        | \$       | <b>(4)</b> | •        |

|                         | DECA         |          |     | l |          |     |    |          |     |      |          |     |    | 4A       | 2  | 1   | $A-1 \rightarrow A$                                                                      | •      | • | <b>‡</b> | \$       | 0          |          |

|                         | DECB         |          | _   | _ |          | _   | _  |          | _   | _    |          | ١.  | L  | 5A       | 2  | 1   | B — 1 → B                                                                                | •      | • | ‡        | ‡        | 4          |          |

| Exclusive OR            | EORA         | 88       | 2   | 2 | 98       | 3   | 2  | A8       | 5   | 2    | B8       | 4   | 3  |          |    | l   | $A \oplus M \rightarrow A$                                                               | •      | • | ‡        | \$       | R          | •        |

|                         | EORB         | C8       | 2   | 2 | D8       | 3   | 2  | E8       | 5   | 2    | F8       | 4   | 3  |          |    |     | $B \oplus M \rightarrow B$                                                               | :      | : | ‡        | ‡        | R          | :        |

| Increment               | INC          |          |     |   |          |     |    | 6C       | 7   | 2    | 7C       | 6   | 3  |          |    |     | M + 1 → M                                                                                | •      |   | ‡        | \$       | (5)        |          |

|                         | INCA         |          | 1   |   |          |     | l  |          |     |      |          |     |    | 4C       | 2  | 1   | A + 1 → A                                                                                | •      |   | ‡<br>±   | \$       | (5)<br>(5) |          |

| Land Armin              | INCB         |          | _   | _ | 00       | ١,  | ١, |          | -   | _    | B.C.     | ١.  | 1  | 5C       | 2  | 1   | B + 1 → B                                                                                | 1.     |   |          | ‡        | R          |          |

| Load Acmitr             | LDAA         | 86       | 2   | 2 | 96       | 3   | 2  | A6       | 5   | 2    | B6       | 4   | 3  |          |    |     | M → A                                                                                    |        |   | \$       | ‡        |            |          |

| On the decision         | LDAB         | C6       | 2   | 2 | D6<br>9A | 3   | 2  | E6       | 5   | 2    | F6<br>BA | 4   | 3  |          |    |     | M → B                                                                                    |        |   | \$       | ‡        | R          |          |

| Or, Inclusive           | ORAA         | 8A       |     | 2 | DA       | 3   | 2  | AA<br>EA | 5   | 2    | FA       |     | 3  |          |    |     | A + M → A<br>  B + M → B                                                                 |        |   | \$       | ‡        | R          |          |

| Buck Date               | ORAB         | CA       | 2   | 2 | DA       | 3   | 2  | EA       | 5   | 2    | FA       | 4   | 3  | 26       | ١, | ١.  |                                                                                          |        |   |          | *        | 🚡          |          |

| Push Data               | PSHA<br>PSHB |          |     |   |          |     |    |          |     | l.   |          |     |    | 36<br>37 | 4  | 1   | $A \rightarrow Msp, SP - 1 \rightarrow SP$<br>$B \rightarrow Msp, SP - 1 \rightarrow SP$ |        |   |          |          |            |          |

| Pull Data               | PULA         |          |     |   |          |     |    |          |     |      |          |     |    | 32       | 4  | 1   | $SP + 1 \rightarrow SP, Msp \rightarrow A$                                               |        |   |          |          |            |          |

| ruii Data               | PULB         |          |     |   |          |     |    |          |     |      |          | -   |    | 33       | 4  | i   | $SP + 1 \rightarrow SP, Msp \rightarrow B$                                               |        |   |          |          |            |          |

| Rotate Left             | ROL          |          |     |   | ĺ        |     |    | 69       | 7   | 2    | 79       | 6   | 3  | 33       | 7  | i ' | M)                                                                                       |        |   | 1        | 1        | 6          | 1        |

| Hotate Leit             | ROLA         |          |     |   |          |     |    | 09       | l ′ | -    | /9       | ١٠  | ١, | 49       | 2  | 1   | A                                                                                        |        |   | t        | i        | 6          | 1        |

|                         | ROLB         |          |     |   |          |     |    |          |     |      |          |     |    | 59       | 2  | i   | B) C b7 ← b0                                                                             |        |   | 1        | ‡        | 6          | \$       |

| Rotate Right            | ROR          |          |     | l |          |     |    | 66       | 7   | 2    | 76       | 6   | 3  | 1        | -  | ١.  | M )                                                                                      |        |   | 1        | 1        | 6          | 1        |

| Tiotato Trigint         | RORA         |          |     |   |          |     |    | "        |     | -    |          | _   |    | 46       | 2  | 1   | A +0 + 0111110                                                                           |        |   | ŧ        | <b>†</b> | 6          | 1        |

|                         | RORB         |          | 1   |   |          |     |    | 1        | 1   |      |          | 1   | }  | 56       | 2  | 1   | B C b7 → b0                                                                              | •      | • | 1        | 1        | 6          | 1        |

| Shift Left, Arithmetic  | ASL          |          |     |   |          |     |    | 68       | 7   | 2    | 78       | 6   | 3  |          |    |     | M )                                                                                      |        | • | \$       | ‡        | 6          | 1        |

|                         | ASLA         |          |     |   |          |     |    |          | l   |      |          |     |    | 48       | 2  | 1   | A D+ IIIIIIII + 0                                                                        | •      | • | \$       | 1        | 6          | 1        |

|                         | ASLB         |          |     |   |          |     | l  |          |     |      | 1        |     |    | 58       | 2  | 1   | B) C b7 b0                                                                               | •      | • | \$       | ‡        | 6          | \$       |

| Shift Right, Arithmetic | ASR          |          |     |   |          |     |    | 67       | 7   | 2    | 77       | 6   | 3  |          |    |     | M)                                                                                       | •      | • | \$       | ‡        | 6          | ‡        |

|                         | ASRA         |          |     |   |          |     |    |          |     |      |          |     |    | 47       | 2  | 1   | A                                                                                        | •      | • | \$       | ‡        | 6          | \$       |

|                         | ASRB         |          |     |   |          |     |    |          |     |      |          |     |    | 57       | 2  | 1   | в) 67 60 С                                                                               | •      | • | \$       | 1        | 6          | \$       |

| Shift Right, Logic      | LSR          |          |     |   |          |     |    | 64       | 7   | 2    | 74       | 6   | 3  |          |    |     | M) _                                                                                     | •      | • | R        | \$       | 6          | \$       |

|                         | LSRA         |          |     |   |          |     |    | İ        |     |      |          | ł   |    | 44       | 2  | 1   | A                                                                                        | •      | • | R        | \$       | 6          | 1        |

|                         | LSRB         |          |     |   |          |     |    |          |     |      |          | ĺ   |    | 54       | 2  | 1   | в) 67 60 С                                                                               | •      | • | R        | \$       | 6          | \$       |

| Store Acmitr            | STAA         |          |     |   | 97       | 4   | 2  | A7       | 6   | 2    | B7       | 5   | 3  |          |    |     | A → M                                                                                    | •      | • | ‡        | \$       | R          | •        |

|                         | STAB         |          |     |   | D7       | 4   | 2  | E7       | 6   | 2    | F7       | 5   | 3  | ĺ        |    |     | B → M                                                                                    | •      | • | \$       | \$       | R          |          |

| Subtract                | SUBA         | 80       | 2   | 2 | 90       | 3   | 2  | A0       | 5   | 2    | В0       | 4   | 3  | i        | 1  |     | $A - M \rightarrow A$                                                                    | •      | • | \$       | \$       | 1          | 1        |

|                         | SUBB         | CO       | 2   | 2 | D0       | 3   | 2  | EO       | 5   | 2    | F0       | 4   | 3  |          |    |     | $B - M \rightarrow B$                                                                    | •      | • | ‡        | ‡        | 1          | 1        |

| Subtract Acmitrs        | SBA          |          |     |   |          | 1   |    |          |     |      |          |     | 1  | 10       | 2  | 1   | $A - B \rightarrow A$                                                                    | •      | • | \$       | ‡        | 1          | \$       |

| Subtr with Carry        | SBCA         | 82       | 2   | 2 | 92       | 3   | 2  | A2       | 5   | 2    | B2       | 4   | 3  | i        |    | 1   | $A - M - C \rightarrow A$                                                                | •      | • | \$       | \$       | 1          | \$       |

|                         | SBCB         | C2       | 2   | 2 | D2       | 3   | 2  | E2       | 5   | 2    | F2       | 4   | 3  | 1        |    |     | $B - M - C \rightarrow B$                                                                | •      | • | 1        | ‡        | 1          | 1        |

| Transfer Acmitrs        | TAB          |          | 1   |   |          | ł   | }  |          |     |      |          |     |    | 16       | 2  | 1   | A → B                                                                                    | •      | • | 1        | ‡        | R          | •        |

|                         | TBA          |          |     |   |          |     |    |          |     |      |          |     |    | 17       | 2  | 1   | B → A                                                                                    | •      | • | \$       | \$       | R          | •        |

| Test Zero or Minus      | TST          |          |     |   |          |     |    | 6D       | 7   | 2    | 7D       | 6   | 3  |          |    | Į   | M - 00                                                                                   | •      | • | 1        | \$       | R          | R        |

|                         | TSTA         |          |     | l | ĺ        |     |    |          |     |      |          | 1   |    | 4D       | 2  | 1   | A - 00                                                                                   | •      | • | ‡        | \$       | R          | R        |

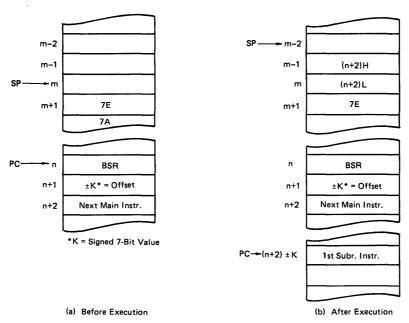

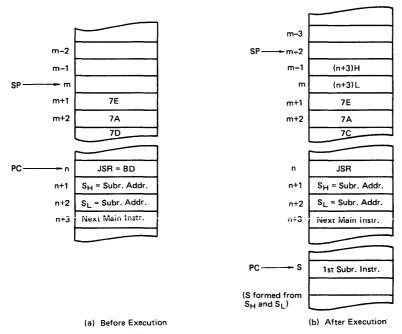

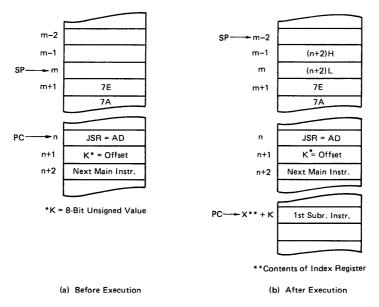

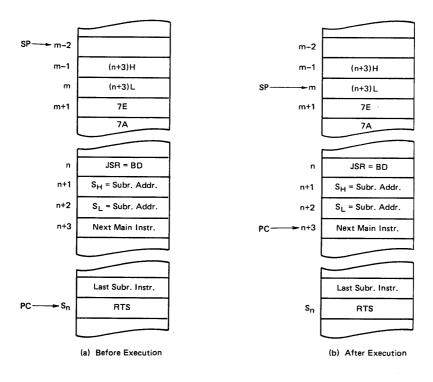

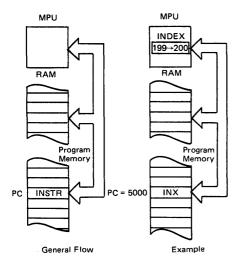

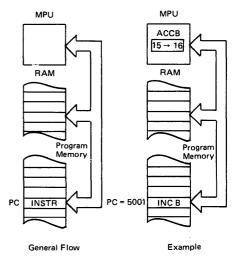

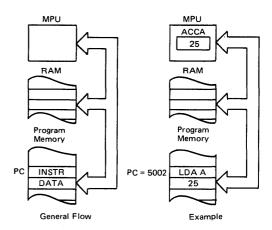

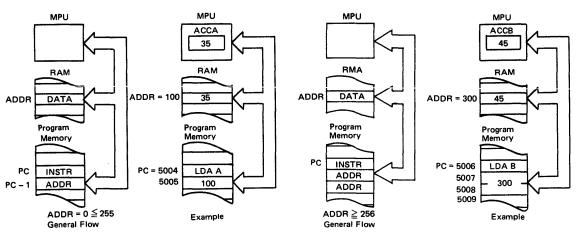

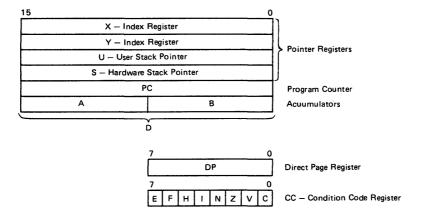

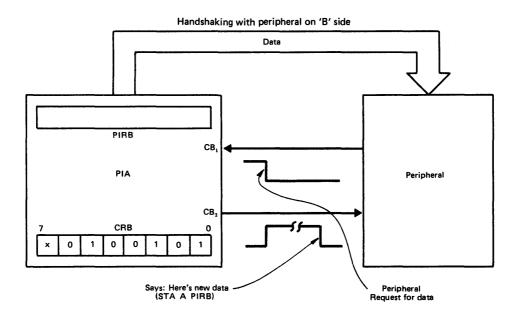

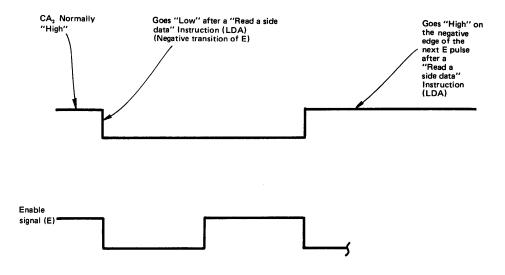

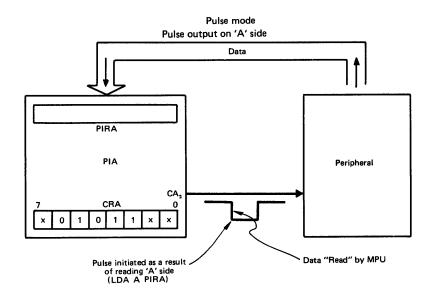

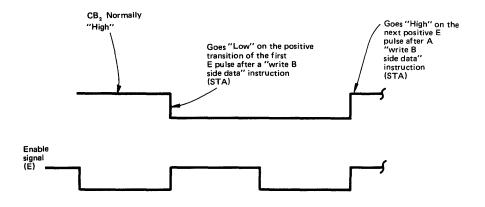

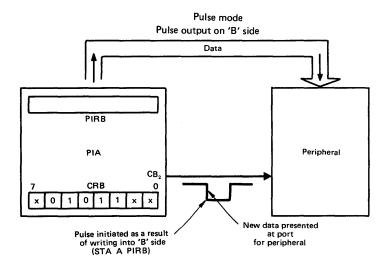

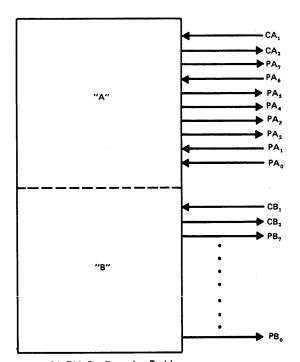

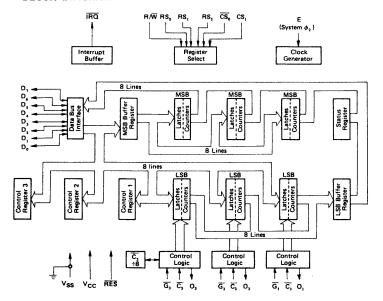

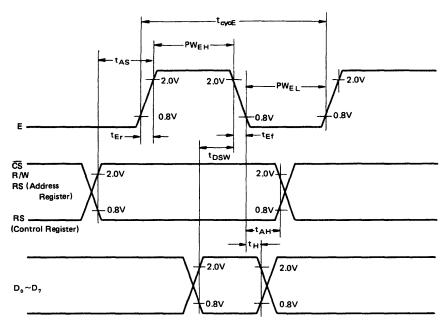

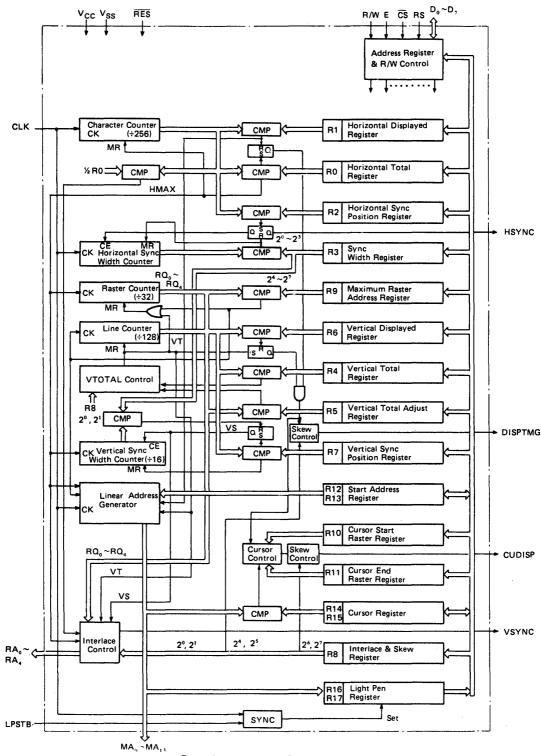

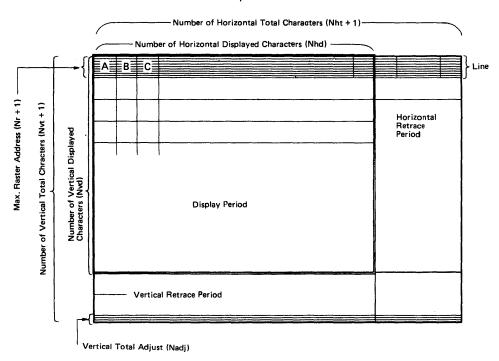

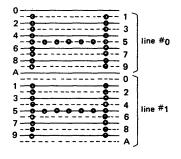

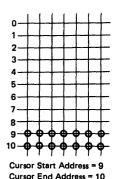

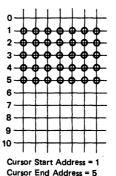

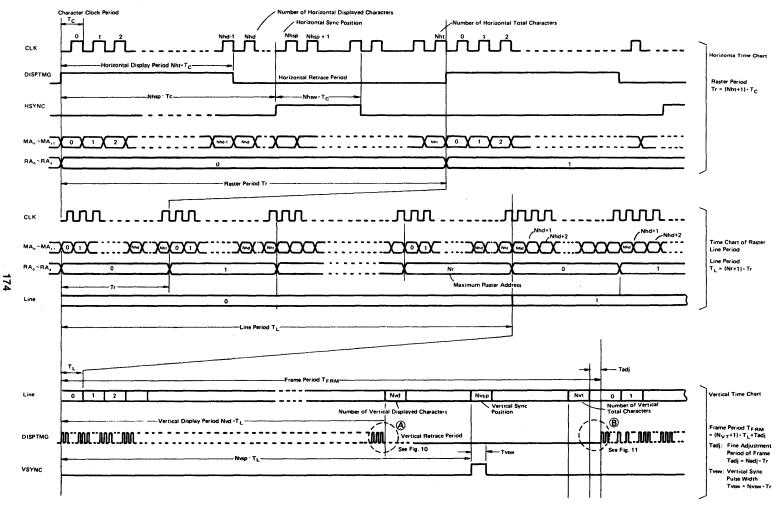

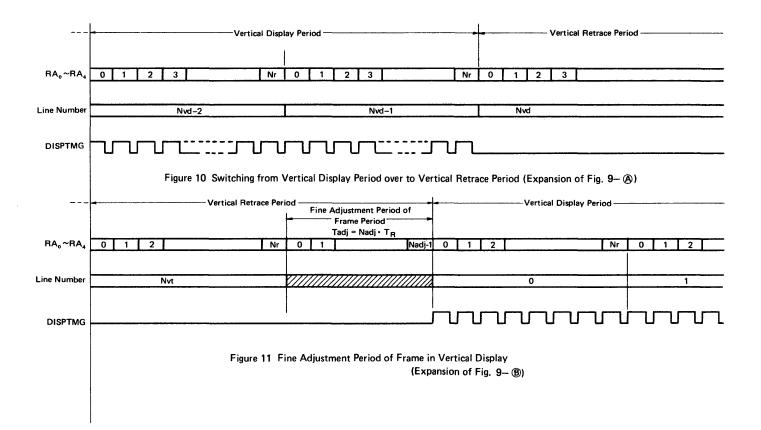

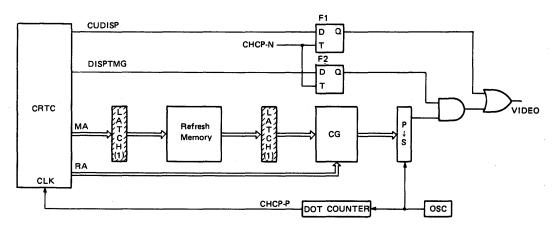

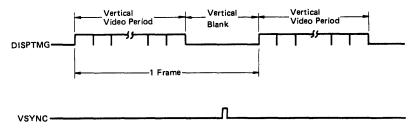

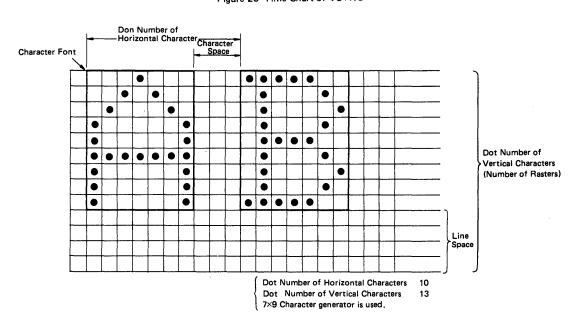

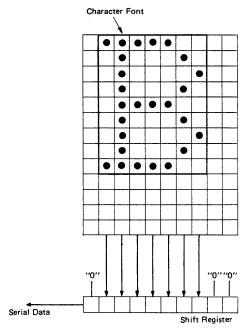

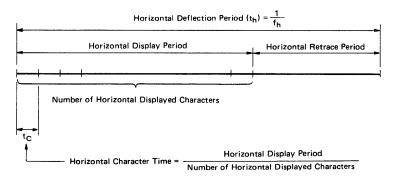

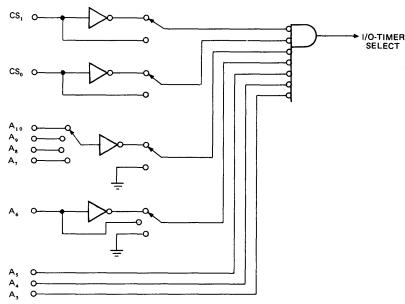

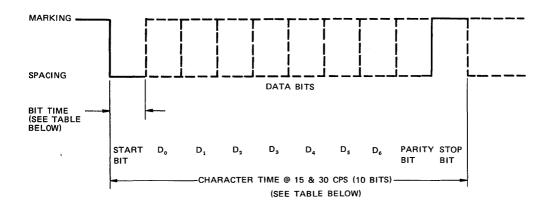

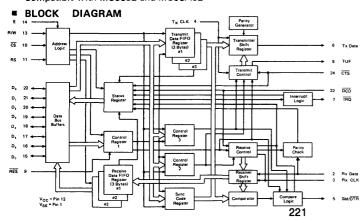

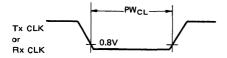

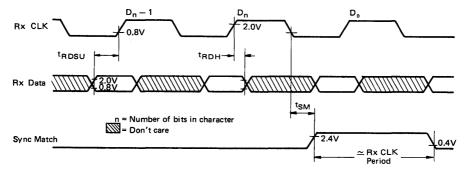

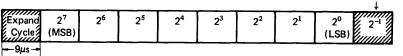

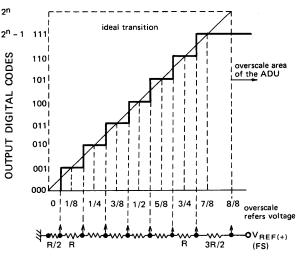

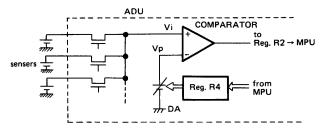

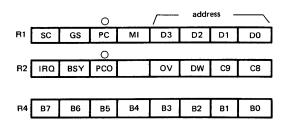

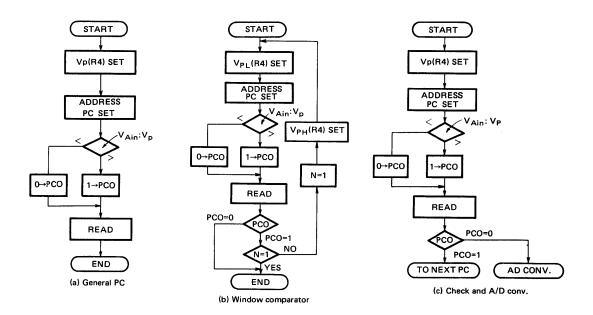

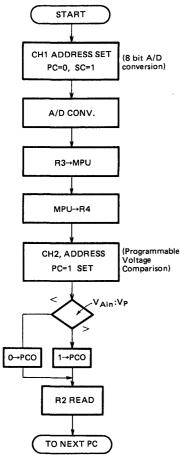

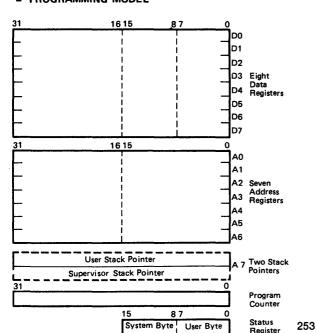

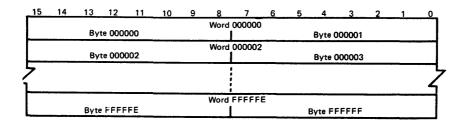

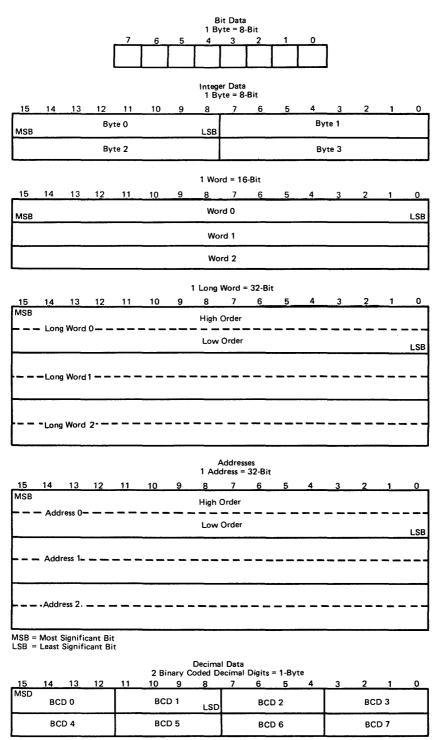

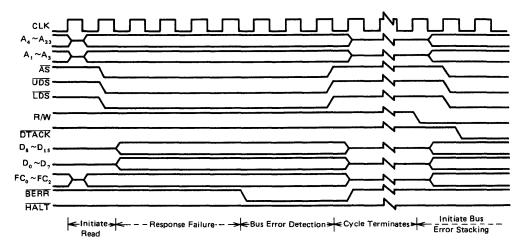

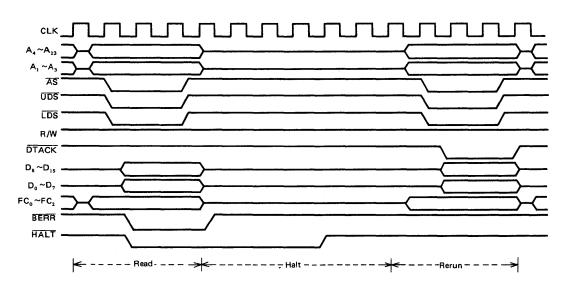

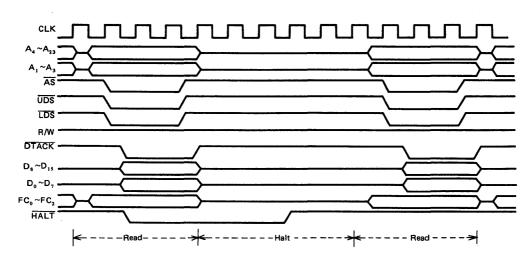

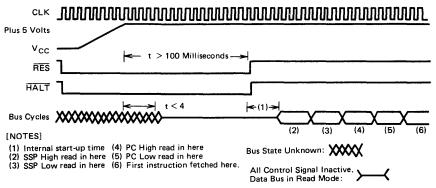

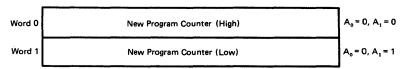

|                         | TSTB         |          | 1   |   | 1        | 1   | 1  | 1        | 1   | 1    | 1        | 1   | i  | 5D       | 2  | 1   | B - 00                                                                                   |        |   | 1        | \$       | R          | R        |