# **@HITACHI®** SRAM DATA BOOK

#M18

# SRAM DATA BOOK

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

## **SRAM DATA BOOK INDEX**

Introduction

Section

**MOS Static RAM**

Cache Static RAM and Fast SRAM Modules

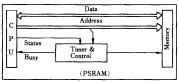

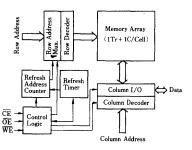

MOS Pseudo Static RAM

**ECL RAM**

HITACHI SALES OFFICES SECTION 5, PAGE 434

#### SRAM DATA BOOK TABLE OF CONTENTS

|  |  | 0 |  |

|--|--|---|--|

|  |  |   |  |

| Introduction                                                                                                                                                                                                                                                                                                                                                 |                                                          | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|

| QUICK REFERENCE GUIDE                                                                                                                                                                                                                                                                                                                                        |                                                          | vi   |

|                                                                                                                                                                                                                                                                                                                                                              |                                                          | 1    |

|                                                                                                                                                                                                                                                                                                                                                              | S                                                        | 13   |

|                                                                                                                                                                                                                                                                                                                                                              | Y                                                        | 28   |

|                                                                                                                                                                                                                                                                                                                                                              |                                                          | 34   |

| APPLICATION                                                                                                                                                                                                                                                                                                                                                  |                                                          | 35   |

| Section 2<br>MOS Static Ram                                                                                                                                                                                                                                                                                                                                  |                                                          |      |

| <ul> <li>HM6116 SERIES         HM6116P-2/3/4         HM6116LP-2/3/4         HM6116FP-2/3/4         HM6116LFP-2/3/4     </li> </ul>                                                                                                                                                                                                                           | 2,048-word × 8-bit High Speed CMOS Static RAM            | 64   |

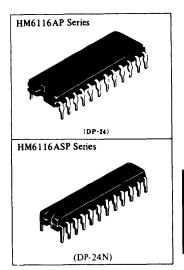

| <ul> <li>HM6116A SERIES         HM6116AP-12/15/20         HM6116ALP-12/15/20         HM6116ASP-12/15/20         HM6116ALSP-12/15/20     </li> </ul>                                                                                                                                                                                                          | 2,048-word × 8-bit High Speed Static CMOS RAM            | 69   |

| <ul> <li>HM6716 SERIES<br/>HM6716P-25/30</li> </ul>                                                                                                                                                                                                                                                                                                          | 2,048-word × 8-bit High Speed Hi-BiCMOS Static RAM       | 74   |

| • HM6719 SERIES<br>HM6719P-25/30                                                                                                                                                                                                                                                                                                                             | 2,048-word × 9-bit High Speed Hi-BiCMOS Static RAM       | 74   |

| <ul> <li>HM6268 SERIES<br/>HM6268P-25/35/45<br/>HM6268LP-25/35/45</li> </ul>                                                                                                                                                                                                                                                                                 | 4,096-word x 4-bit High Speed CMOS Static RAM            | 80   |

| <ul> <li>HM6267 SERIES<br/>HM6267P-35/45/55<br/>HM6267LP-35/45/55</li> </ul>                                                                                                                                                                                                                                                                                 | 16,384-word × 1-bit High Speed CMOS Static RAM           | 87   |

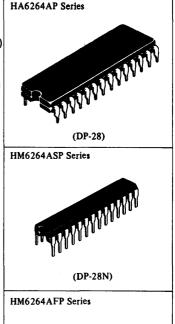

| <ul> <li>HM6264A SERIES         HM6264AP-10/12/15         HM6264ALP-10/12/15         HM6264ALP-10/12/15L         HM6264ASP-10/12/15         HM6264ALSP-10/12/15         HM6264ALSP-10/12/15L         HM6264ALSP-10/12/15L         HM6264ALFP-10/12/15         HM6264ALFP-10/12/15         HM6264ALFP-10/12/15         HM6264ALFP-10L/12L/15L     </li> </ul> | 8,192-word × 8-bit High Speed CMOS Static RAM            | 94   |

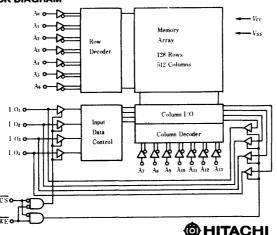

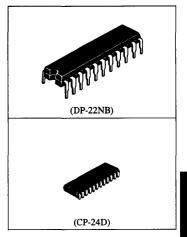

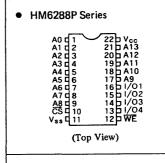

| <ul> <li>HM6288 SERIES         HM6288P-25/35         HM6288LP-25/35         HM6288LJP-25/35     </li> <li>HM6288LJP-25/35</li> </ul>                                                                                                                                                                                                                         | 16,384-word × 4-bit High Speed CMOS Static RAM           | 103  |

| • HM6788 SERIES<br>HM6788P-25/30                                                                                                                                                                                                                                                                                                                             | 16,384-word × 4-bit High Speed Hi-BiCMOS Static RAM      | 111  |

| • HM6788H SERIES<br>HM6788HP-15/20                                                                                                                                                                                                                                                                                                                           | 16,384-word × 4-bit High Speed Hi-BiCMOS Static RAM      | 115  |

| • HM6788HA SERIES<br>HM6788HAP-12/15/20                                                                                                                                                                                                                                                                                                                      | 16,384-word × 4-bit High Speed Static RAM                | 119  |

| <ul> <li>HM6289 SERIES<br/>HM6289JP-25/35<br/>HM6289LJP-25/35</li> </ul>                                                                                                                                                                                                                                                                                     | 16,384-word × 4-bit High Speed CMOS Static RAM (with OE) | 124  |

#### **TABLE OF CONTENTS -**

| Section 2—MOS Static Ram (contin                                                                                                                                                     | ued)                                                                                      | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|

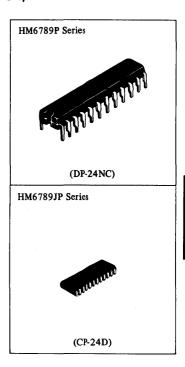

| <ul> <li>HM6789 SERIES<br/>HM6789P-25/30<br/>HM6789JP-25/30</li> </ul>                                                                                                               | 16,384-word $\times$ 4-bit High Speed Hi-BiCMOS Static RAM (with $\overline{\text{OE}}$ ) | 135  |

| <ul> <li>HM6789H SERIES<br/>HM6789HP-15/20<br/>HM6789HJP-15/20</li> </ul>                                                                                                            | 16,384-word $\times$ 4-bit High Speed Hi-BiCMOS Static RAM (with $\overline{\text{OE}}$ ) | 142  |

| <ul> <li>HM6789HA SERIES<br/>HM6789HAP-12/15/20<br/>HM6789HAJP-12/15/20</li> </ul>                                                                                                   | 16,384-word × 4-bit High Speed Static RAM (with $\overline{\text{OE}}$ )                  | 149  |

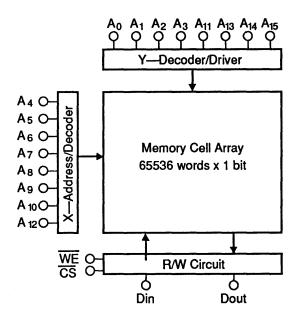

| <ul> <li>HM6287 SERIES<br/>HM6287P-45/55/70<br/>HM6287LP-45/55/70</li> </ul>                                                                                                         | 65,536-word × 1-bit High Speed CMOS Static RAM                                            | 157  |

| <ul> <li>HM6287H SERIES         HM6287HP-25/35     </li> <li>HM6287HLP-25/35</li> <li>HM6287HJP-25/35</li> <li>HM6287HJP-25/35</li> </ul>                                            | 65,536-word × 1-bit High Speed CMOS Static RAM                                            | 164  |

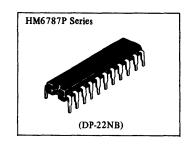

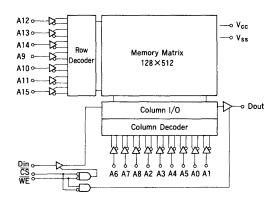

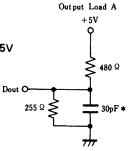

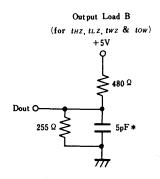

| <ul> <li>HM6787 SERIES<br/>HM6787P-25/30</li> </ul>                                                                                                                                  | 65,536-word × 1-bit High Speed Hi-BiCMOS Static RAM                                       | 173  |

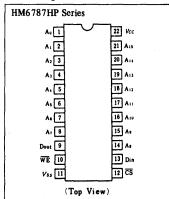

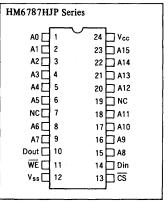

| <ul> <li>HM6787H SERIES<br/>HM6787HP-15/20<br/>HM6787HJP-15/20</li> </ul>                                                                                                            | 65,536-word × 1-bit High Speed Hi-BiCMOS Static RAM                                       | 178  |

| <ul> <li>HM6787HA SERIES<br/>HM6787HAP-12/15/20<br/>HM6787HAJP-12/15/20</li> </ul>                                                                                                   | 65,536-word × 1-bit High Speed Static RAM                                                 | 183  |

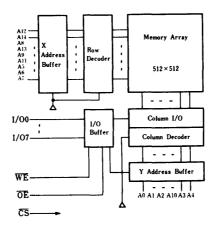

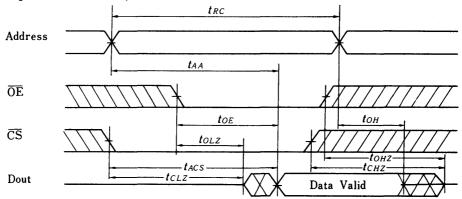

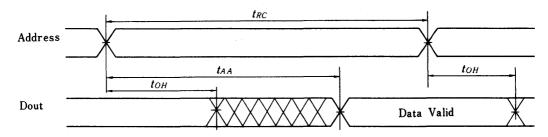

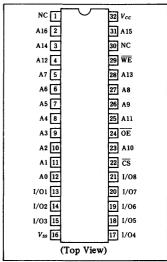

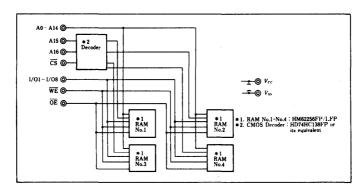

| HM62256 SERIES     HM62256P-8/10/12/15     HM62256LP-8/10/12/15     HM62256LP-10/12/15     HM62256P-8T/107/12T/15T     HM62256FP-8T/10T/12T/15T     HM62256LFP-8SLT/10SLT/12SLT/15SL | 32,768-word × 8-bit High Speed CMOS Static RAM                                            | 189  |

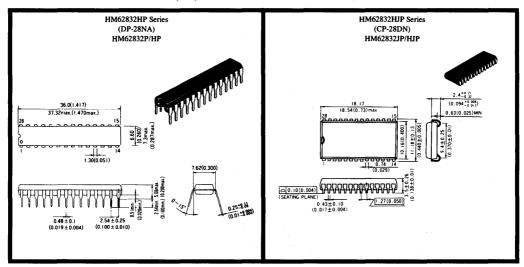

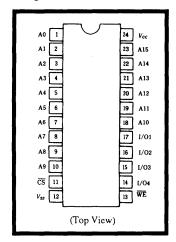

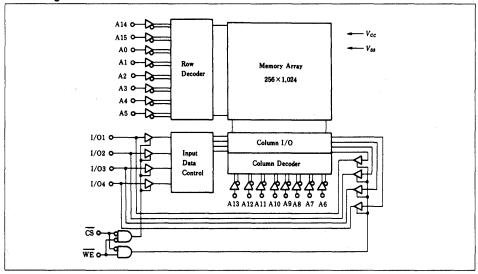

| HM62832/HM62832H SERIES     HM62832P-35/45     HM62832LP-35/45     HM62832JP-35/45     HM62832JP-35/45     HM62832HP-35/45     HM62832HJP-35/45                                      | 32,768-word × 8-bit High Speed CMOS Static RAM                                            | 197  |

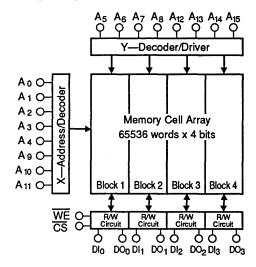

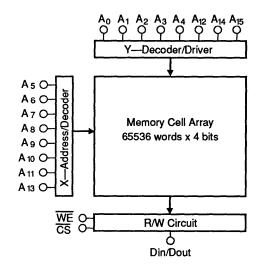

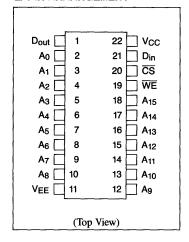

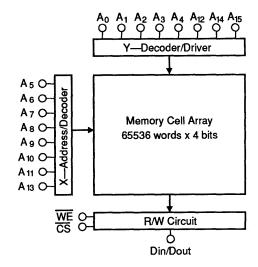

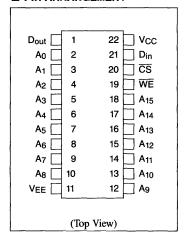

| <ul> <li>HM6208/HM6208H SERIES         HM6208P-35/45     </li> <li>HM6208HP-25/35</li> <li>HM6208HLP-25/35</li> <li>HM6208HJP-25/35</li> <li>HM6208HLJP-25/35</li> </ul>             | 65,536-word × 4-bit High Speed CMOS Static RAM                                            | 203  |

| <ul> <li>HM6708 SERIES<br/>HM6708P-20/25<br/>HM6708JP-20/25</li> </ul>                                                                                                               | 65,536-word × 4-bit High Speed Hi-BiCMOS Static RAM                                       | 211  |

| <ul> <li>HM6708A SERIES<br/>HM6708AP-15/20/25<br/>HM6708AJP-15/20/25</li> </ul>                                                                                                      | 65,536-word × 4-bit High Speed Static RAM                                                 | 217  |

| <ul> <li>HM6709 SERIES<br/>HM6709JP-20/25</li> </ul>                                                                                                                                 | 65,536-word × 4-bit High Speed Static RAM (with $\overline{\text{OE}}$ )                  | 222  |

| • HM6709A SERIES<br>HM6709AP-15/20/25<br>HM6709AJP-15/20/25                                                                                                                          | 65,536-word × 4-bit High Speed Static RAM (with $\overline{\text{OE}}$ )                  | 229  |

| Section 2—MOS Static Ram (continu                                                                                                                                                            | ued)                                                     | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|

| • HM6207 SERIES<br>HM6207P-35/45<br>HM6207LP-35/45                                                                                                                                           | 262,144-word × 1-bit High Speed CMOS Static RAM          | 236  |

| <ul> <li>HM6207/HM6207H SERIES         HM6207P-35/45         HM6207HP-25/35         HM6207HLP-25/35         HM6207HJP-25/35         HM6207HJP-25/35         HM6207HLJP-25/35     </li> </ul> | 262,144-word x 1-bit High Speed CMOS Static RAM          | 243  |

| • HM6707 SERIES<br>HM6707P-20/25<br>HM6707JP-20/25                                                                                                                                           | 262,144-word x 1-bit High Speed Hi-BiCMOS Static RAM     | 250  |

| • HM6707A SERIES<br>HM6707AP-15/20/25<br>HM6707AJP-15/20/25                                                                                                                                  | 262,144-word × 1-bit High Speed Static RAM               | 255  |

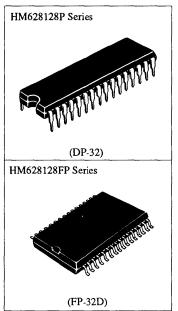

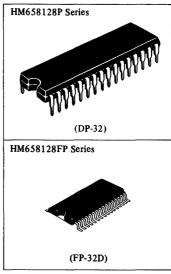

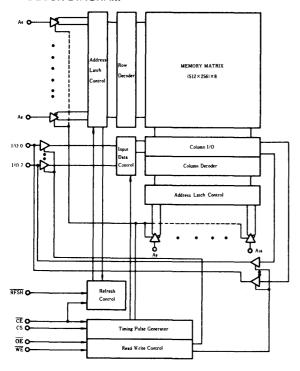

| <ul> <li>HM628128 SERIES         HM628128P-7/8/10/12         HM628128LP-7/8/10/12         HM628128FP-7/8/10/12         HM628128LFP-7/8/10/12     </li> </ul>                                 | 131,072-word x 8-bit High Speed CMOS Static RAM          | 261  |

| <ul> <li>HM624256 SERIES         HM624256P-35/45         HM624256LP-35/45         HM624256JP-35/45         HM624256LJP-35/45     </li> </ul>                                                 | 262,144-word × 4-bit High Speed CMOS Static RAM          | 269  |

| • HM624257 SERIES<br>HM624257JP-35/45<br>HM624257LJP-35/45                                                                                                                                   | 262,144-word × 4-bit High Speed CMOS Static RAM          | 275  |

| • HM66204 SERIES<br>HM66204-12/15<br>HM66204L-12/15                                                                                                                                          | 131,072-word × 8-bit High Density CMOS Static RAM Module | 283  |

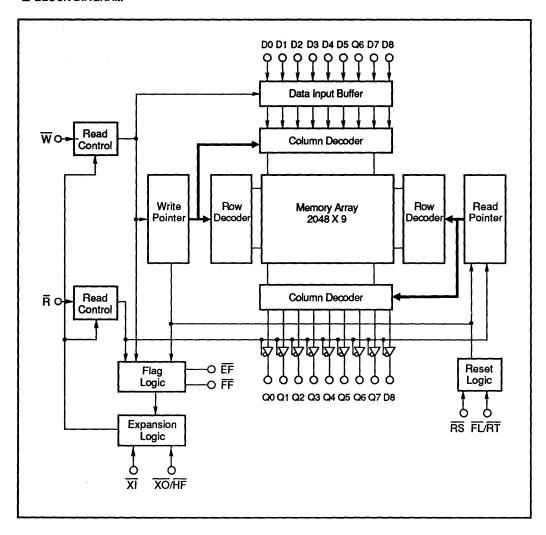

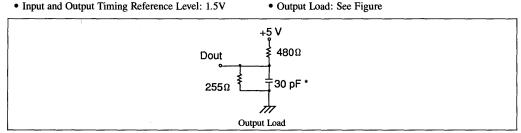

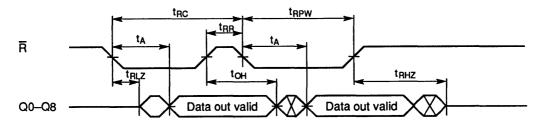

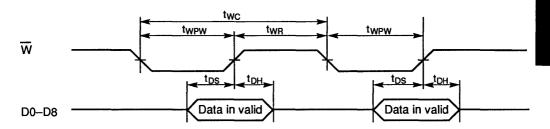

| • HM63921-20/25/35<br>HM63921P-20/25/35                                                                                                                                                      | 2K × 9-bit CMOS Parallel In-Out FIFO Memory              | 289  |

| • HM63941-25/35/45<br>HM63941P-25/35/45                                                                                                                                                      | 4K × 9-bit CMOS Parallel In-Out FIFO Memory              | 301  |

| Section 3 Cache Static RAM and Fast SRAM I                                                                                                                                                   | Modules                                                  |      |

| • HM62A168/HM62A188 SERIES<br>HM62168CP-25/35/45<br>HM62188CP-25/35/45                                                                                                                       | Direct Mapped 8,192-word × 16/18-bit 2-way               | 311  |

| • HM67C932 SERIES<br>HM67C932CP-20/25                                                                                                                                                        | 8,192-word × 9-bit × 4-row Static Cache RAM              | 319  |

| • HB66B1616A-25/35<br>HB66B1616A-25/35                                                                                                                                                       | 16,384-word × 16-bit High Speed Static RAM Module        | 333  |

| • HB66A2568A-25/35<br>HB66A2568A-25/35                                                                                                                                                       | 262,144-word × 8-bit High Speed Static RAM Module        | 343  |

| • HM644332<br>HM644332G-25/30                                                                                                                                                                |                                                          | 351  |

#### **TABLE OF CONTENTS -**

| Section 4<br>MOS Pseudo Static RAM                                                                                                                                                          |                                                                      | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------|

| HM65256B SERIES     HM65256BP-10/12/15/20     HM65256BLP-10/12/15/20     HM65256BSP-10/12/15/20     HM65256BLSP-10/12/15/20     HM65256BLSP-10T/12T/15T/20T     HM65256BLFP-10T/12T/15T/20T | 32,768-word × 8-bit High Speed Pseudo Static RAM                     | 369  |

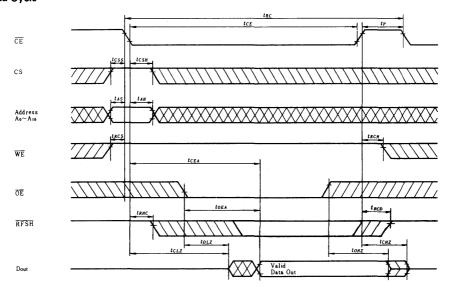

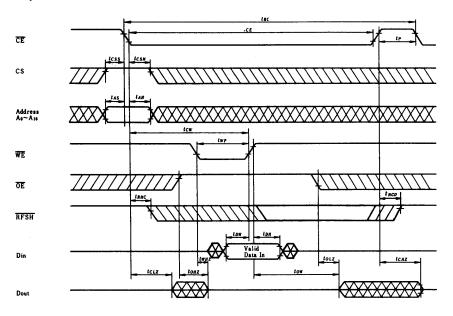

| HM658128 SERIES     HM658128DP-10/12/15     HM658128LP-10/12/15     HM658128DFP-10/12/15     HM658128LFP-10/12/15                                                                           | 131,072-word × 8-bit High Speed CMOS Pseudo Static RAM               | 376  |

| Section 5<br>ECL RAM                                                                                                                                                                        |                                                                      |      |

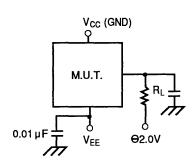

| <ul> <li>HM10494 SERIES<br/>HM10494-10/12<br/>HM10494F-10/12</li> </ul>                                                                                                                     | 16,384-word × 4-bit Fully Decoded Random Access Memory               | 388  |

| <ul> <li>HM10490 SERIES<br/>HM10490-10/12</li> </ul>                                                                                                                                        | 65,536-word × 1-bit Fully Decoded Random Access Memory               | 393  |

| • HM10504-10/12 SERIES                                                                                                                                                                      | 65,536-word × 4-bit Fully Decoded Random Access Memory               | 397  |

| • HM10500-15                                                                                                                                                                                | 262,144-word × 1-bit Fully Decoded Random Access Memory              | 399  |

| <ul> <li>HM100494 SERIES         HM100500-18         HM100500CG-18         HM100500F-18     </li> </ul>                                                                                     | 16,384-word $	imes$ 4-bit Fully Decoded Random Access Memory $\dots$ | 403  |

| <ul> <li>HM100490 SERIES<br/>HM100490-10/12</li> </ul>                                                                                                                                      | 65,536-word × 1-bit Fully Decoded Random Access Memory               | 407  |

| • HM100504F-10/12                                                                                                                                                                           | 65,536-word × 4-bit Fully Decoded Random Access Memory               | 411  |

| <ul> <li>HM100500CG-18         HM100500-18         HM100500CG-18         HM100500F-18     </li> </ul>                                                                                       | 262,144-word × 1-bit Fully Decoded Random Access Memory              | 412  |

| HM101494 SERIES     HM101494-10/12     HM101494F-10/12                                                                                                                                      | 16,384-word $	imes$ 4-bit Fully Decoded Random Access Memory $\dots$ | 415  |

| • HM101490 SERIES<br>HM101490-10/12                                                                                                                                                         | 65,536-word × 1-bit Fully Decoded Random Access Memory               | 419  |

| • HM101504F-10/12                                                                                                                                                                           | 65,536-word × 4-bit Fully Decoded Random Access Memory               | 423  |

| • HM101500F-15                                                                                                                                                                              | 262,144-word × 1-bit Fully Decoded Random Access Memory              | 424  |

| HITACHI SAI ES OFFICES                                                                                                                                                                      |                                                                      | 434  |

# Section 1 Introduction

- Quick Reference to Hitachi I.C. Memories

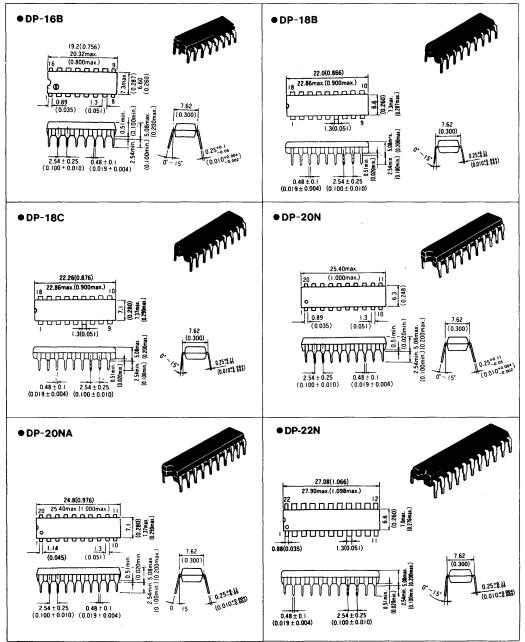

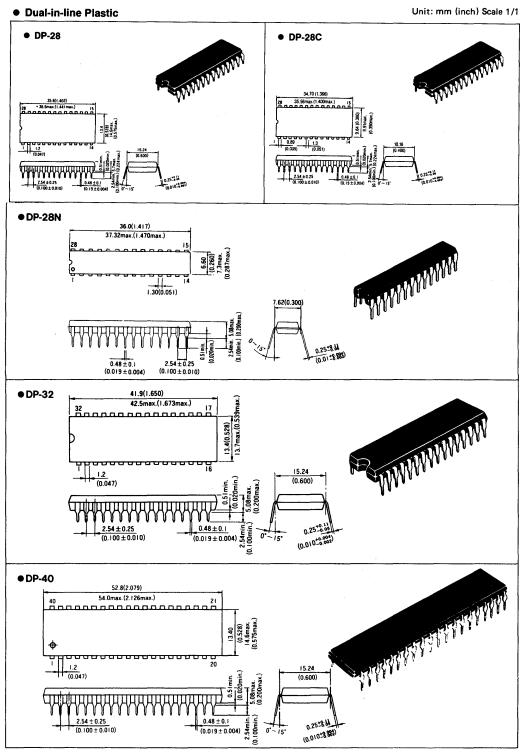

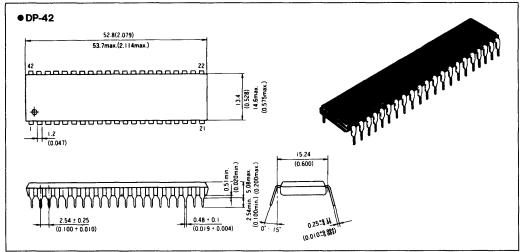

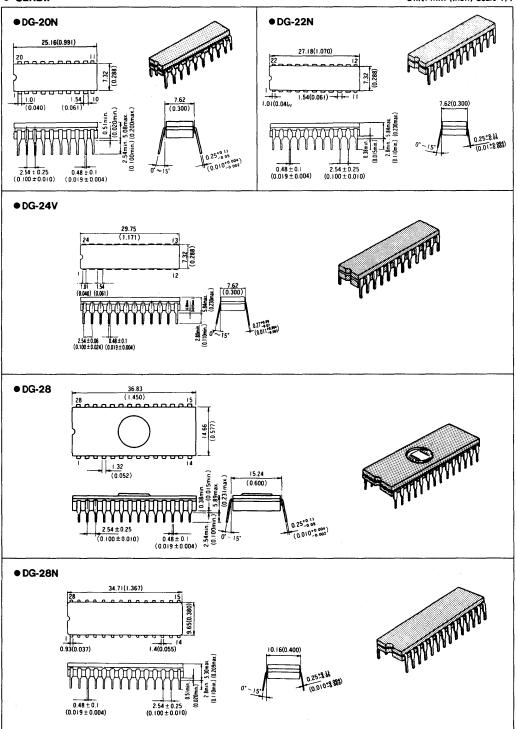

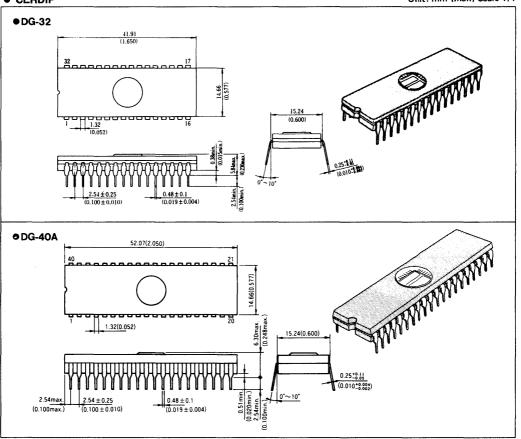

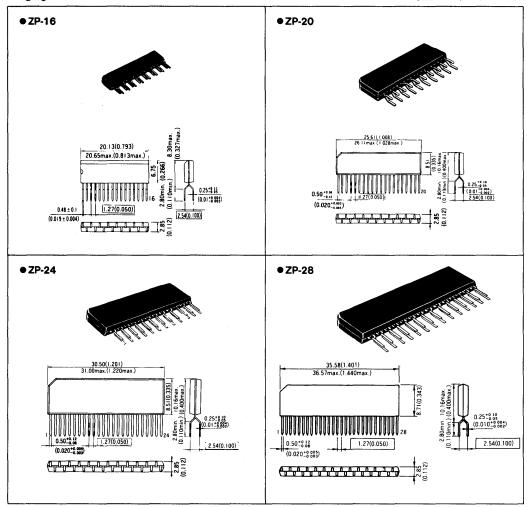

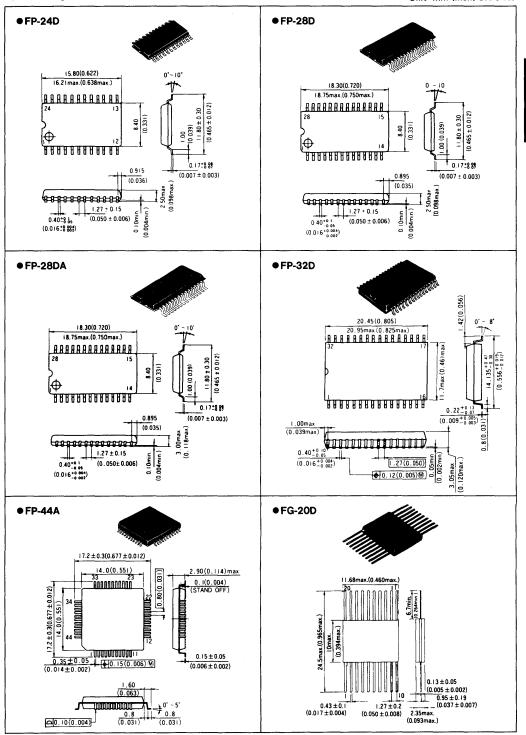

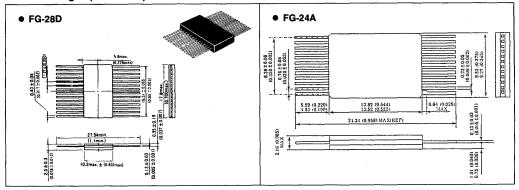

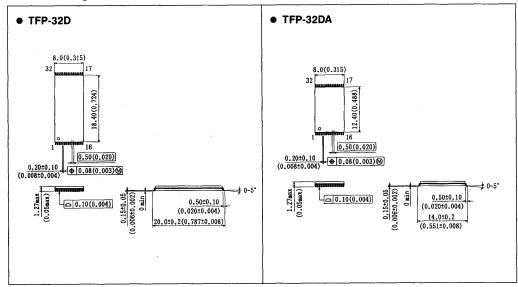

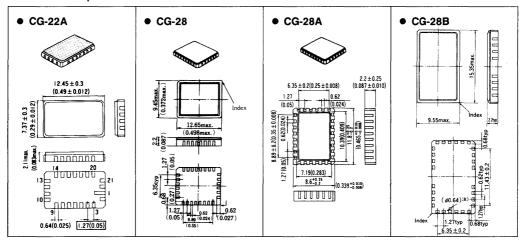

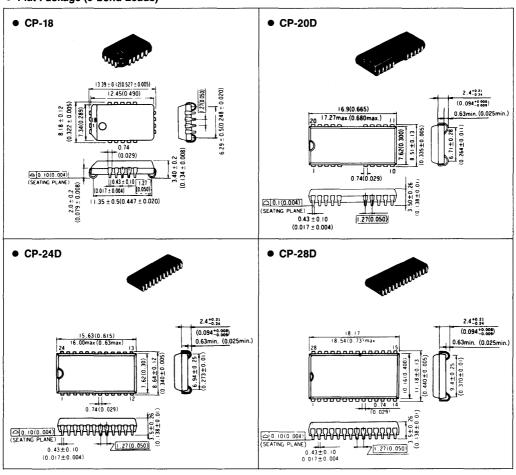

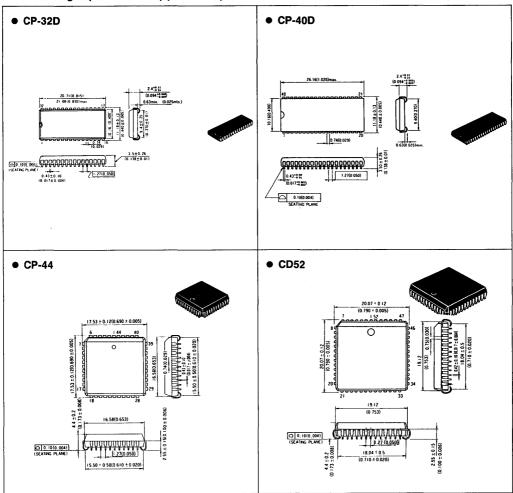

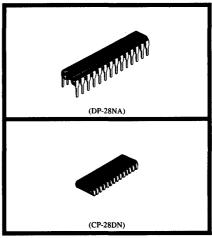

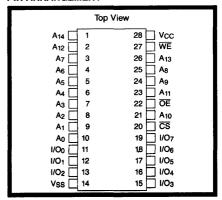

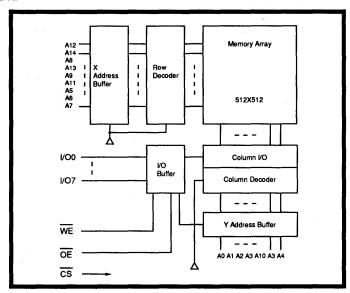

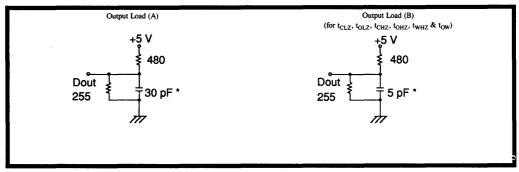

- Package Information

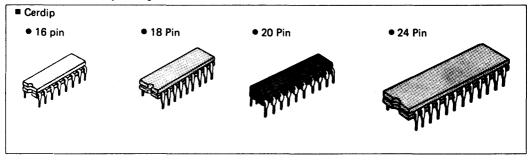

- Reliability of Hitachi I.C. Memories

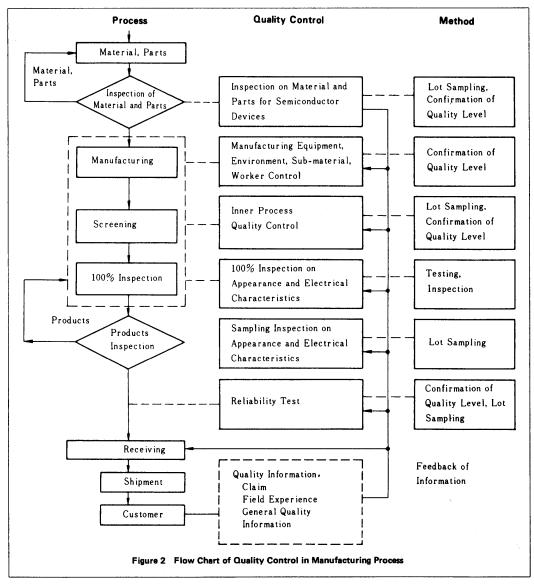

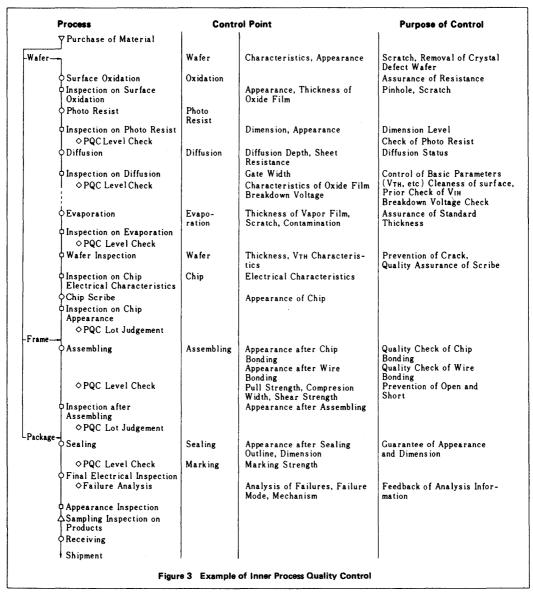

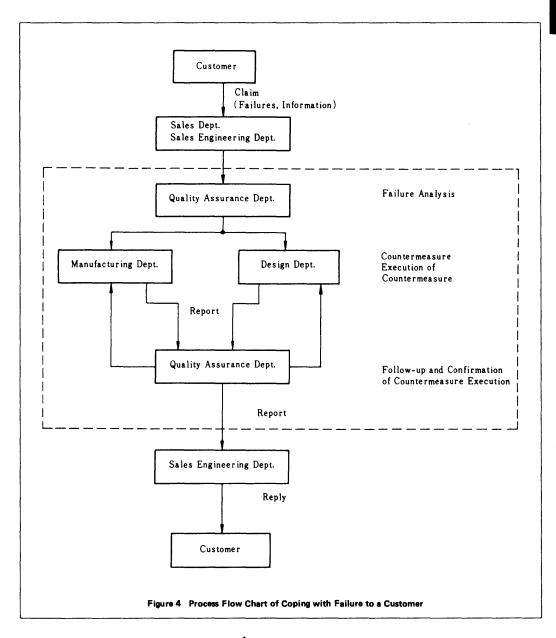

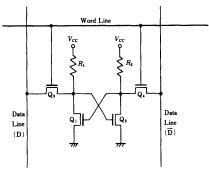

- Quality Assurance of I.C. Memory

- Outline of Testing Method

- Application

## **QUICK REFERENCE GUIDE TO HITACHI MEMORIES**

#### **MOS RAM**

| /lode | Total      | Type No.                     | Process      | Organization<br>(word × bit) | Access<br>Time<br>(ns) | Cycle<br>Time<br>(ns) | Supply<br>Voltage<br>(V) | Power<br>Dissipation |                                                  |               |         | Pa | ackag    | je *1                                            |                                                  |                                                  |                                                  |          | Pag      |          |    |   |  |  |

|-------|------------|------------------------------|--------------|------------------------------|------------------------|-----------------------|--------------------------|----------------------|--------------------------------------------------|---------------|---------|----|----------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------|----------|----------|----|---|--|--|

|       |            |                              |              | (word x bit)                 | Max                    | Max                   | (V)                      | (W)                  | Pin No.                                          | G             | Р       | FP | SP       | ZP                                               | CG                                               | СP                                               | JP                                               | М        |          |          |    |   |  |  |

|       |            | HM6116-2*2                   |              |                              | 120                    | 120                   |                          | 0.1m/0.2             |                                                  |               | •       | •  |          | 1                                                |                                                  |                                                  |                                                  |          | 6        |          |    |   |  |  |

|       |            | HM6116-3 <sup>2</sup>        |              |                              | 150                    | 150                   |                          | 0.1m/0.175           | 1                                                |               | •       | •  |          |                                                  |                                                  |                                                  |                                                  |          | 6        |          |    |   |  |  |

|       |            | HM6116-4*2                   |              |                              | 200                    | 200                   |                          |                      | 1                                                |               | •       | •  |          |                                                  |                                                  |                                                  |                                                  |          | 6        |          |    |   |  |  |

|       |            | HM6116L-2*2                  |              |                              | 120                    | 120                   |                          | 10μ/0.175            | 1                                                | L_            | •       | •  | _        |                                                  | L                                                |                                                  | <u> </u>                                         |          | 6        |          |    |   |  |  |

|       |            | HM6116L-3 <sup>2</sup>       |              |                              | 150                    | 150                   |                          | 10μ/0.15             |                                                  |               | •       | •  | _        | L                                                | <u> </u>                                         | ļ                                                | <u> </u>                                         |          | - 6      |          |    |   |  |  |

|       |            | HM6116L-4*2                  | CMOS         | 2048 × 8                     | 200                    | 200                   | 1                        |                      | 4                                                | <u> </u>      | •       | •  | L_       |                                                  | <b> </b>                                         | <u> </u>                                         | _                                                |          | _6       |          |    |   |  |  |

|       |            | HM6116A-12*2                 |              |                              |                        |                       | 20.070                   | 120                  | 120                                              |               | 0.1 /15 | ŀ  | <u> </u> | •                                                |                                                  | •                                                | ļ                                                | <u> </u> | -        | <u> </u> |    | _ |  |  |

|       | ł          | HM6116L-15*2<br>HM6116A-20*2 | 1            | }                            | 150<br>200             | 150<br>200            |                          | 0.1m/15m             | 24                                               | L             | •       |    | •        |                                                  | -                                                | -                                                | _                                                | <u> </u> | L_(      |          |    |   |  |  |

|       |            | HM6116AL-12*2                |              |                              | 120                    | 120                   |                          |                      | 1                                                |               | •       |    | •        | ┢                                                | ┢                                                |                                                  | ├                                                | $\vdash$ | - 6      |          |    |   |  |  |

|       | ł          | HM6116AL-15*2                | -            |                              | 150                    | 150                   | 1                        | 5μ/10m               |                                                  |               | ÷       |    | •        | ┢                                                | ⊢                                                |                                                  | ├                                                |          | -        |          |    |   |  |  |

|       |            | HM6116AL-20*2                | -            |                              | 200                    | 200                   |                          | <i>3μι</i> 10111     |                                                  |               | •       |    | •        |                                                  | ╁                                                |                                                  | ├                                                |          | -        |          |    |   |  |  |

|       |            | HM6716-25                    |              |                              | 25                     | 25                    | 1                        |                      | 1                                                |               | •       |    | •        | $\vdash$                                         | ├                                                |                                                  |                                                  | $\vdash$ | <b>—</b> |          |    |   |  |  |

|       |            | HM6716-30                    | 1            | 2048×8                       | 30                     | 30                    |                          |                      |                                                  |               |         |    | •        | ┢                                                | +                                                |                                                  |                                                  |          |          |          |    |   |  |  |

|       | 16k-b      | HM6719-25                    | Bi-CMOS      | (with OE)                    | 25                     | 25                    |                          | 0.28                 | 1                                                | Н             |         | -  | •        | t                                                | t                                                |                                                  |                                                  |          |          |          |    |   |  |  |

|       |            | HM6719-30                    | 1            | ` ′                          | 30                     | 30                    |                          |                      |                                                  |               |         |    | •        | <del> </del>                                     | 1                                                |                                                  |                                                  |          |          |          |    |   |  |  |

|       |            | HM6268-25                    | <del> </del> | <u> </u>                     | 25                     | 25                    | 1                        |                      | <del>                                     </del> | $\vdash$      | •       |    | _        | <del>                                     </del> | $t^-$                                            |                                                  |                                                  |          | -        |          |    |   |  |  |

|       |            | HM6268-35                    | 1            |                              | 35                     | 35                    | 1                        | $0.1\mu/0.25$        |                                                  |               | •       |    |          |                                                  | 1                                                |                                                  |                                                  | Н        |          |          |    |   |  |  |

|       |            | HM6268-45                    |              | 4000 4                       | 45                     | 45                    | 1                        |                      | İ                                                |               | •       |    |          |                                                  | <b></b>                                          |                                                  |                                                  |          | -        |          |    |   |  |  |

|       | ļ          | HM6268L-25                   |              | 4096 × 4                     | 25                     | 25                    | 1 .                      |                      | 1                                                |               | •       |    |          |                                                  | t                                                |                                                  |                                                  |          | 1        |          |    |   |  |  |

|       |            | HM6268L-35                   | 1            |                              | 35                     | 35                    |                          | $5\mu/0.25$          |                                                  |               | •       |    |          |                                                  |                                                  |                                                  |                                                  |          | - {      |          |    |   |  |  |

|       |            | HM6268L-45                   | CMOC         | 1                            | 45                     | 45                    |                          | ·                    | 00                                               |               | •       |    |          |                                                  | T                                                |                                                  |                                                  |          | _        |          |    |   |  |  |

|       |            | HM6267-35                    | CMOS         |                              | 35                     | 35                    | i '                      |                      | 20                                               |               | •       |    |          |                                                  |                                                  |                                                  |                                                  |          |          |          |    |   |  |  |

|       |            | HM6267-45                    | 1            |                              | 45                     | 45                    | 0.1m/0.2                 | 0.1m/0.2             |                                                  |               | •       |    |          |                                                  |                                                  |                                                  |                                                  |          |          |          |    |   |  |  |

|       |            | HM6267-55                    |              | 16384×1                      | 55 5                   | 55                    |                          |                      |                                                  |               | •       |    |          |                                                  |                                                  |                                                  |                                                  |          | 8        |          |    |   |  |  |

|       | ł          | HM6267L-35                   | ]            |                              | 10384 X I              | 10384 X I             | 10384 × 1                | 10384 × 1            | , 10304 X I                                      | 10304 X I     | 35      | 35 | }        |                                                  | 7                                                |                                                  | •                                                |          |          |          |    |   |  |  |

|       |            | HM6267L-45                   |              |                              | 45                     | 45                    | +5                       | $5\mu/0.2$           |                                                  |               | •       |    |          |                                                  |                                                  |                                                  |                                                  |          |          |          |    |   |  |  |

| atic  |            | HM6267L-55                   |              |                              | 55                     | 55                    |                          |                      |                                                  |               | •       |    |          |                                                  |                                                  |                                                  |                                                  |          |          |          |    |   |  |  |

|       | 18k-b      | HM6719-25                    | Bi-CMOS      | 2048×9                       | 25                     | 25                    |                          | 0.28                 | 24                                               |               |         |    | •        |                                                  |                                                  |                                                  |                                                  |          |          |          |    |   |  |  |

|       | LOK B      | HM6719-30                    | DI 011100    | 2010 / 0                     | 30                     | 30                    |                          | 0.20                 |                                                  |               |         |    | •        |                                                  |                                                  |                                                  |                                                  |          |          |          |    |   |  |  |

|       |            | HM6264-10*2                  | ]            |                              | 100                    | 100                   |                          | 0.1m/0.2             |                                                  |               | •       | •  | <u> </u> | _                                                | _                                                |                                                  |                                                  | Ш        |          |          |    |   |  |  |

|       | 1          | HM6264-12*2                  | 1            | ĺ                            | 120                    | 120                   |                          | 0.1111/0.2           | 1                                                |               | •       | •  | L        |                                                  | _                                                |                                                  | Ш                                                |          | 9        |          |    |   |  |  |

|       |            | HM6264A-10                   | 1            |                              | 100                    | 100                   |                          |                      |                                                  |               | •       | •  | •        |                                                  | <b>├</b> _                                       |                                                  |                                                  |          | 9        |          |    |   |  |  |

|       |            | HM6264A-12                   | 4            |                              | 120                    | 120                   |                          | 0.1m/15m             |                                                  | $\vdash$      | •       | •  | •        | _                                                | _                                                |                                                  | <u> </u>                                         |          | 9        |          |    |   |  |  |

|       |            | HM6264A-15                   | 1            | 1                            | 150                    | 150                   |                          |                      | -                                                |               | •       | •  | •        | _                                                | <u> </u>                                         | ļ                                                |                                                  |          | _ 9      |          |    |   |  |  |

|       | ļ          | HM6264AL-10                  | -            | 0400 0                       | 100                    | 100                   |                          | 40 /45               | 28                                               |               | •       | •  | •        | -                                                |                                                  | <u> </u>                                         | _                                                | $\vdash$ |          |          |    |   |  |  |

|       |            | HM6264AL-12                  | CMOC         | 8192×8                       | 120                    | 120                   |                          | 10μ/15m              |                                                  | <del> </del>  | •       | •  | •        | ├-                                               | ├                                                | -                                                | -                                                | Н        | _ 9      |          |    |   |  |  |

|       |            | HM6264AL-15<br>HM6264AL-10L  | CMOS         |                              | 150                    | 150<br>100            |                          |                      | 1                                                | -             | •       | •  | •        | ├                                                | $\vdash$                                         |                                                  |                                                  | $\vdash$ | 9        |          |    |   |  |  |

|       | 1          | HM6264AL-12L                 | 1            |                              | 120                    | 120                   |                          | 10μ/15m              |                                                  | H             | •       | •  | •        | -                                                | $\vdash$                                         |                                                  |                                                  | $\vdash$ |          |          |    |   |  |  |

|       | 1          | HM6264AL-15L                 | 1            |                              | 150                    | 150                   |                          | ιομι ιστι            | 1                                                | $\vdash$      | -       | :  | •        | $\vdash$                                         | $\vdash$                                         |                                                  | -                                                | Н        | - 5      |          |    |   |  |  |

|       | 16k-b      | HM6288-25                    | 1            |                              | 25                     | 25                    |                          |                      | <del> </del>                                     |               | _       | _  | •        | $\vdash$                                         | $\vdash$                                         | -                                                | •                                                | Н        | 10       |          |    |   |  |  |

|       | 10, 2      | HM6288-35                    | †            |                              | 35                     | 35                    |                          |                      | 22                                               | -             |         |    | •        | ├                                                | +                                                | $\vdash$                                         | •                                                | Н        | 10       |          |    |   |  |  |

|       | Ì          | HM6288L-25                   | †            | }                            | 25                     | 25                    |                          | 0.1m/0.3             | 24                                               | <del>  </del> |         |    | •        | <del>                                     </del> |                                                  |                                                  | •                                                | $\vdash$ | 10       |          |    |   |  |  |

|       |            | HM6288L-35                   | 1            |                              |                        |                       | 35                       | 35                   |                                                  |               | (SOJ)   | -  |          |                                                  | •                                                | <del>                                     </del> | 1                                                | $\vdash$ | •        | $\vdash$ | 10 |   |  |  |

|       |            | HM6788-25                    | <u> </u>     |                              | 25                     | 25                    |                          |                      | <del>                                     </del> | H             |         |    | •        | $\vdash$                                         | t                                                |                                                  | <del>-</del> -                                   | -        | 1        |          |    |   |  |  |

|       | ·          | HM6788-35                    | 1            | Bi-CMOS 20                   | 35                     | 35                    |                          | 10m/0.23             | 1                                                | $\vdash$      | -       |    | •        |                                                  | <del>                                     </del> | _                                                | <del>                                     </del> | Н        | 1        |          |    |   |  |  |

|       | 1          | HM6788H-20                   | D: 01400     |                              | 20                     | 20                    |                          | 0.28                 | 1 00                                             | Н             |         |    | •        | _                                                | <del>                                     </del> |                                                  | 1                                                | Н        | 1        |          |    |   |  |  |

|       |            | HM6788HA-12                  | - RI-CMOS    |                              | 12                     | 12                    | 1                        |                      | 22                                               |               |         |    | •        | _                                                | †                                                |                                                  | $\vdash$                                         | Н        | 1        |          |    |   |  |  |

|       |            | HM6788HA-15                  | 1            |                              | 15                     | 15                    | [                        | .3                   | 1                                                | $\vdash$      |         | _  | •        | t                                                |                                                  |                                                  |                                                  |          | 1        |          |    |   |  |  |

|       | <b>l</b> . | HM6788HA-20                  | 1            |                              | 20                     | 20                    |                          | _                    |                                                  |               |         |    | •        |                                                  | T                                                |                                                  |                                                  |          | 1        |          |    |   |  |  |

|       | ·          | HM6289-25                    | <u> </u>     |                              | 25                     | 25                    |                          |                      | T                                                |               |         |    | <u> </u> |                                                  | T                                                |                                                  | •                                                | $\vdash$ | 12       |          |    |   |  |  |

|       |            | HM6289-35                    | 01400        | 16384 × 4                    | 35                     | 35                    |                          | 0.4                  |                                                  |               |         |    |          |                                                  | 1                                                |                                                  | •                                                | П        | 12       |          |    |   |  |  |

|       | 64k-b      | HM6289L-25                   | CMOS         | (with OE)                    | 25                     | 25                    |                          | 0.1m/0.3             | 24                                               |               |         |    |          |                                                  | t                                                |                                                  | •                                                |          | 12       |          |    |   |  |  |

|       |            |                              |              |                              |                        |                       |                          |                      |                                                  |               |         |    |          |                                                  |                                                  |                                                  |                                                  |          |          |          |    |   |  |  |

(continued)

#### **MOS RAM**

| Mode   | Total  | Type No.                       | Process   | Organization<br>(word × bit) | Access<br>Time<br>(ns) | Cycle<br>Time<br>(ns) | Supply<br>Voltage<br>(V) | Power<br>Dissipation<br>(W) |             |           |           | Pa         | ckag    | je *1    |          |         |          | _         | Page       |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|--------|--------|--------------------------------|-----------|------------------------------|------------------------|-----------------------|--------------------------|-----------------------------|-------------|-----------|-----------|------------|---------|----------|----------|---------|----------|-----------|------------|------------|----------|-----------|------|------------|----------|-----|---|---|----------|--|------------|----------|-----|----|---|-----|---|---|--|-----|--|---|---|--|---|-----|-----|

|        | 1      |                                | }         | ,                            | Max                    | Max                   | ""                       | (VV)                        | Pin No.     | G         | Р         | FP         | SP      | ZP       | CG       | CP      | JP       | М         |            |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6789-25                      |           |                              | 25                     | 25                    |                          | 10μ/0.23                    |             |           |           |            | •       |          |          |         | •        |           | 135        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6789-30                      |           |                              | 30                     | 30                    |                          | 10,010.20                   |             |           |           | _          | •       | L_       |          |         | •        |           | 135        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6789H-15<br>HM6789H-20       | Bi-CMOS   | 1638 <u>4 × 4</u>            | 15                     | 15                    | -                        |                             | 24          | -         | $\vdash$  | $\dashv$   | •       | <u> </u> |          |         | •        | -         | 142        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6789HA-12                    | DI-CIVIOS | (with OE                     | 12                     | 20<br>12              |                          | 0.28                        | 24          | <u> </u>  | $\vdash$  | -          | •       | -        |          |         | •        | Н         | 142        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6789HA-15                    | 1         |                              | 15                     | 15                    |                          | 0.20                        |             |           | $\vdash$  |            | •       | -        |          |         | •        | H         | 149        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6789HA-20                    |           |                              | 20                     | 20                    | 1 .                      |                             |             |           |           |            | •       |          |          |         | •        |           | 149        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6287-45                      |           |                              | 45                     | 45                    |                          |                             |             |           |           |            | •       |          |          |         |          |           | 157        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6287-55<br>HM6287-70         |           |                              | 55<br>70               | 55                    |                          | 0.1m/0.3                    |             |           | $\vdash$  | _          | •       | _        | <u> </u> |         |          | $\sqcup$  | 157        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6287L-45                     |           |                              | 45                     | 70<br>45              |                          |                             | 22          | -         | -         | $\dashv$   | •       |          | -        |         | $\vdash$ | $\vdash$  | 157<br>157 |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6287L-55                     | CNACC     |                              | 55                     | 55                    | İ '                      | $10\mu/0.3$                 | Ì           | H         |           | -          | •       | -        |          |         |          |           | 157        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6287L-70                     | CMOS      |                              | 70                     | 70                    |                          |                             |             |           |           |            | •       |          |          |         |          |           | 157        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6287H-25                     |           | 65536 × 1                    | 65536 × 1              | 65526 v. 1            | eeene1                   | 25                          | 25          |           | 0.1m/0.3  |            |         |          |          | •       |          |           |            | •          |          | 164       |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6287H-35                     |           |                              |                        |                       |                          | eccoc1                      | 35          | 35        |           | 0.1118/0.0 | ļ       | <u></u>  | _        |         | •        |           | <u> </u>   |            | •        | $\square$ | 164  |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6287HL-25<br>HM6287HL-35     | 1         |                              |                        | 25<br>35              | 25<br>35                 |                             | $10\mu/0.3$ |           | -         | $\vdash$   | -       | •        | -        | _       |          | •         | $\vdash$   | 164<br>164 |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6787-25                      |           |                              |                        |                       | 25                       | 25                          |             | 00 10 10  | 22        | H          |         |          | •        | -       | -        |           | •          | $\vdash$   | 173      |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6787-35                      | 1         |                              | 35                     | 35                    | ĺ                        | 38m/0.18                    | 24          |           |           |            | •       | -        | _        |         |          | H         | 173        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6787H-15                     | ]         |                              |                        | 15                    | 15                       |                             | 0.21        | (SOJ)     |           |            |         | •        |          |         |          | •         |            | 178        |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6787H-20                     | Bi-CMOS   |                              | 20                     | 20                    |                          |                             | 1           | ╙         |           |            | •       |          |          |         | •        |           | 178        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6787HAJP-12<br>HM6787HAJP-15 |           |                              | 12                     | 12                    |                          | .3                          |             | <u> </u>  |           | _          | •       |          |          |         | •        | Н         | 178        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6787HAJP-13                  | '         |                              | 20                     | 15<br>20              |                          | .ئ                          | Ì           | <u> </u>  | Н         | $\dashv$   | •       | ├        |          | -       | •        | $\vdash$  | 183<br>183 |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM62256-8                      |           |                              | 85                     | 85                    |                          |                             | ļ           | -         | •         | •          | •       |          | $\vdash$ |         |          | $\vdash$  | 189        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM62256-10                     | j         | 32768 × 8                    | 100                    | 100                   |                          | 0.2m/40m                    |             |           | •         | •          |         | _        |          |         |          |           | 189        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        | l .    | HM62256-12                     | ]         |                              | 120                    |                       |                          | 0.2111/40111                |             |           | •         | •          |         |          |          |         |          |           | 189        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM62256-15                     |           |                              | 150                    | 150                   |                          |                             |             |           | •         | •          |         |          |          |         |          |           | 189        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM62256L-8<br>HM62256L-10      |           |                              | 32768×8                | 32768×8               | 32768×8                  | 32768×8                     | 32768×8     |           |           |            |         |          |          |         | 100      | 85<br>100 |            |            |          |           | •    | •          |          |     |   |   | _        |  | 189<br>189 |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM62256L-12                    | 1         |                              |                        |                       |                          |                             |             |           |           | 120        | 120     |          | 10μ/40m  |         | $\vdash$ | •         | •          |            |          | -         |      | -          | $\vdash$ | 189 |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

| Static | 256k-b | HM62256L-15                    | 1         |                              |                        |                       |                          |                             |             |           |           | 00700      | 00700   | 00700    | 150      | 150     | +5       |           |            |            | •        | •         |      |            |          |     |   |   | 189      |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM62256L-10SL                  |           |                              |                        |                       |                          |                             |             |           |           |            |         |          | 00700 0  | 00700 0 | 100      | 100       |            |            |          |           | •    | •          |          |     |   |   |          |  | 189        |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM62256L-12SL                  |           |                              |                        |                       |                          |                             |             | 120       | 120       |            | 10μ/40m | 28       |          | •       | •        |           |            |            |          |           | Щ    | 189        |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        | İ      | HM62256L-15SL<br>HM62832-35    | }         |                              |                        |                       |                          |                             |             | 150<br>35 | 150<br>35 | 1          |         | -        | $\vdash$ | •       | •        | •         |            | H          |          | •         | -    | 189<br>197 |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM62832-45                     | 1         |                              |                        |                       |                          |                             |             |           | 45        | 45         |         | 75m/.3   | l        |         | $\vdash$ |           | •          | -          | $\vdash$ |           | •    | $\vdash$   | 197      |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM62832L-35                    | 1         |                              |                        |                       |                          |                             |             |           |           | 35         | 35      |          | 10m/ 2   |         |          |           |            | •          | _        |           |      | •          |          | 197 |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM62832L-45                    | CMOS      |                              |                        |                       |                          |                             |             |           |           | 45         | 45      | ]        | 10m/.3   | ļ       |          |           |            | •          |          |           |      | •          |          | 197 |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        | l i    | HM62832H-25                    |           |                              |                        | 25                    | 25                       |                             |             |           |           |            |         | •        |          |         |          | •         |            | 197        |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM62832H-35<br>HM62832H-45     |           |                              |                        |                       |                          |                             |             |           |           |            |         |          |          |         | -        |           | 35<br>45   | 35         |          | .1m/.3    |      |            |          |     | • |   |          |  | •          |          | 197 |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM62832HL-25                   | 1         |                              | 25                     | 45<br>25              |                          |                             | 1           | $\vdash$  | $\dashv$  |            | •       |          |          |         | •        |           | 197<br>197 |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM62832HL-35                   |           |                              |                        |                       |                          | 35                          | 35          |           | 30m/.3    |            | Н       |          |          | •       |          |           |            | •          |          | 197       |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM62832HL-45                   |           |                              | 45                     | 45                    |                          |                             |             |           |           |            | •       |          |          |         | •        |           | 197        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        | ļ      | HM6208-35                      | Į I       |                              | 35                     | 35                    |                          | 0.1m/0.3                    | ļ           | ┕         | •         | _          |         |          |          |         |          |           | 203        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

|        |        | HM6208-45                      |           |                              | 45                     | 45                    |                          |                             | 4           | <u> </u>  | •         |            |         |          | _        |         | <u> </u> | $\vdash$  | 203        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |

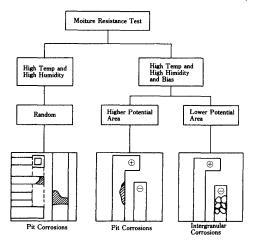

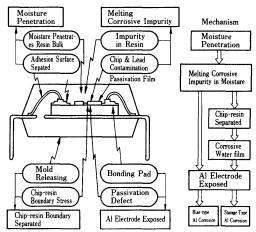

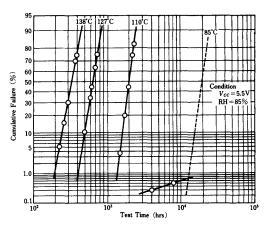

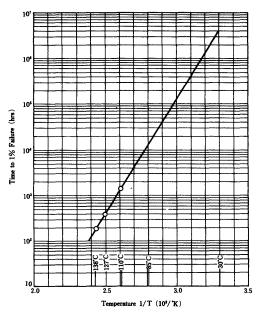

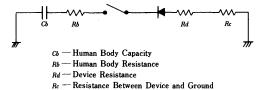

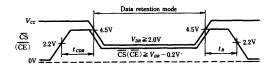

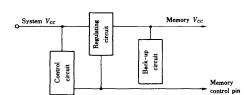

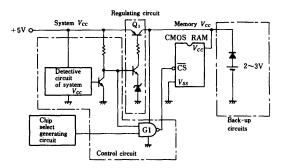

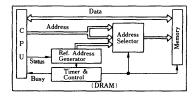

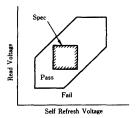

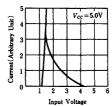

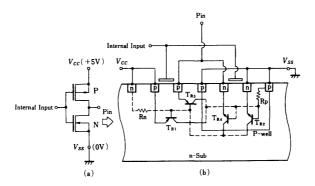

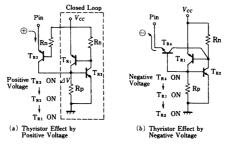

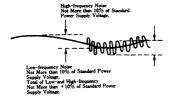

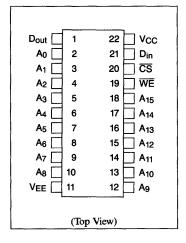

|        |        | HM6208L-35<br>HM6208L-45       | ł         |                              | 35<br>45               | 35<br>45              |                          | $10\mu/0.3$                 | ĺ           | ┝         | •         | -          |         | -        | -        |         |          | $\vdash$  | 203        |            |          |           |      |            |          |     |   |   |          |  |            |          |     |    |   |     |   |   |  |     |  |   |   |  |   |     |     |