## **CHITACHI** HD63484 ACRTC ADVANCED CRT CONTROLLER USER'S MANUAL

### HD63484 ACRTC ADVANCED CRT CONTROLLER USER'S MANUAL

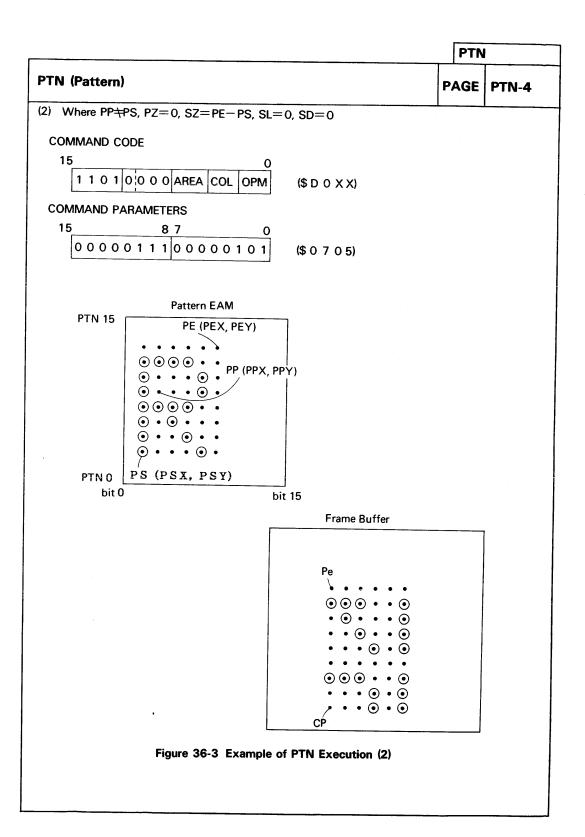

November 1984 Printed in USA

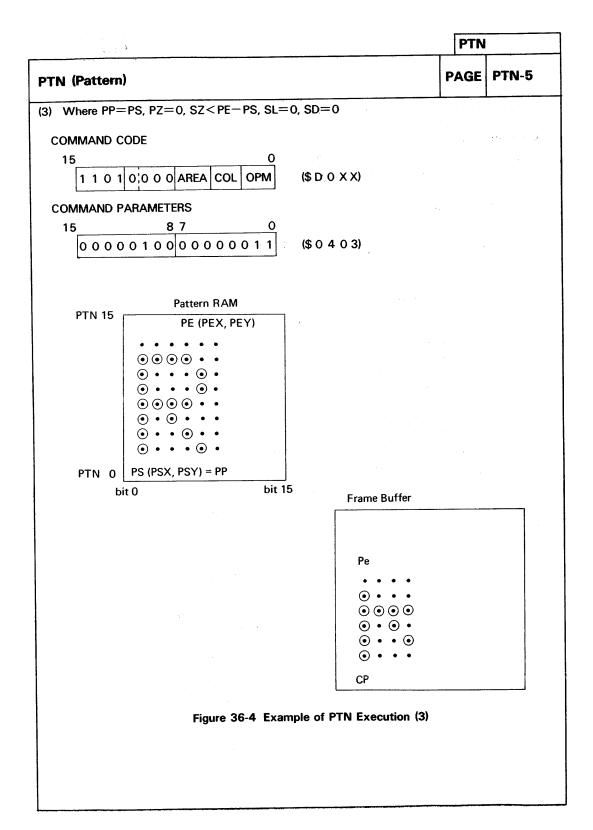

When using this manual, the reader should keep the following in mind:

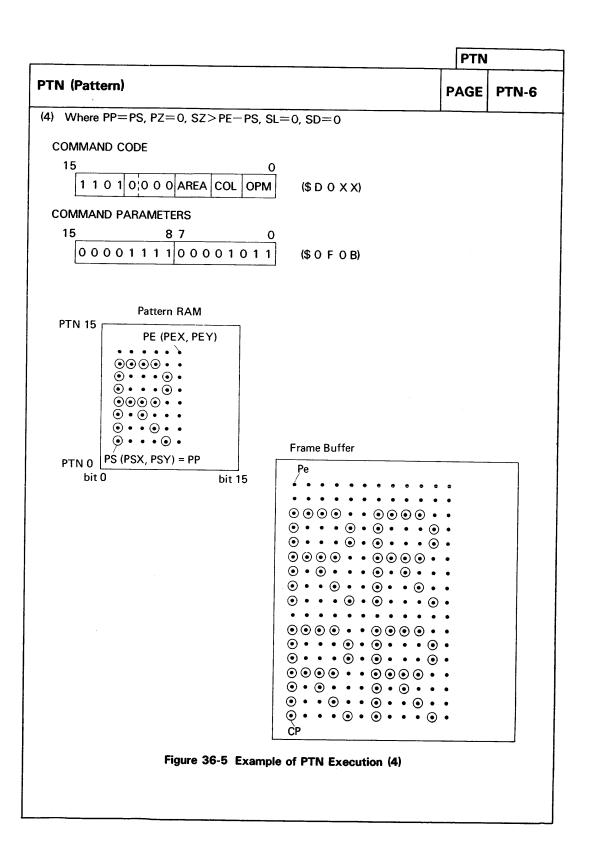

- 1. This manual may, wholly or partially, be subject to change without notice.

- 2. All rights reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this manual without Hitachi's permission.

- Hitachi will not be responsible for any damage to the user that may result from accidents or any other reasons during operation of his unit according to this manual.

- 4. This manual neither ensures the enforcement of any industrial properties or other rights, nor sanctions the enforcement right thereof.

#### **TABLE OF CONTENTS**

| 1. | ACR  | TC INTRODUCTION           |       |

|----|------|---------------------------|-------|

|    | 1.1  | Applications              | 3     |

|    | 1.2  | System Configuration      |       |

|    | 1.3  | Block Diagram             | 6     |

|    | 1.4  | Signal Description        | 8     |

|    | 1.5  | Address Space             | 10    |

|    | 1.6  | Registers                 | 12    |

|    | 1.7  | Commands                  |       |

|    | 1.8  | Graphic Drawing.          | 16    |

| 2. | SYS. | TEM INTERFACE             |       |

|    | 2.1  | Basic Clock               | 17    |

|    | 2.2  | CRT Interface             |       |

|    | 2.3  | MPU Interface.            |       |

|    |      |                           |       |

| 3. | DISP | PLAY FUNCTION             |       |

|    | 3.1  | Logical Display Screens   |       |

|    | 3.2  | Cursor Control            |       |

|    | 3.3  | Scrolling                 |       |

|    | 3.4  | Raster Scan Modes         |       |

|    | 3.5  | Zooming                   |       |

|    | 3.6  | Light Pen                 | 46    |

| 4. | SIGN | IAL DESCRIPTION           |       |

|    | 4.1  | Pin Arrangement           | 47    |

|    | 4.2  | Signal Functions          | 48    |

| 5. | REGI | STER DESCRIPTION          |       |

|    | 5.1  | Internal Register Access  | 57    |

|    | 5.2  | Address Register          |       |

|    | 5.3  | Status Register           |       |

|    | 5.4  | FIFO Entry                |       |

|    | 5.5  | Command Control Register  |       |

|    | 5.6  | Operation Mode Register   |       |

|    | 5.7  | Display Control Register  |       |

|    | 5.8  | Timing Control RAM        |       |

|    | 5.9  | Display Control RAM       |       |

|    |      | Drawing Control Registers | . 113 |

| 6.  | COMMANDS          |                             |     |  |  |  |

|-----|-------------------|-----------------------------|-----|--|--|--|

|     | 6.1               | Command Overview            | 125 |  |  |  |

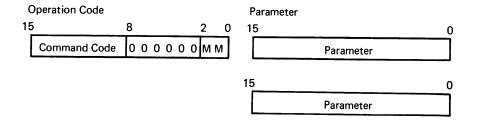

|     | 6.2               | Command Format              | 125 |  |  |  |

|     | 6.3               | Command Transfer Modes      | 126 |  |  |  |

|     | 6.4<br>6.5<br>6.6 | Register Access Commands    | 127 |  |  |  |

|     |                   | Data Transfer Commands      | 128 |  |  |  |

|     |                   | Graphic Drawing Commands    | 135 |  |  |  |

|     | 6.7               | Graphic Drawing Processor   |     |  |  |  |

|     | 6.8               | Graphic Drawing Operation   |     |  |  |  |

| FU  | NCTIC             | ON OF COMMANDS              | 171 |  |  |  |

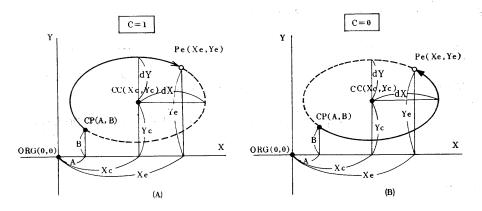

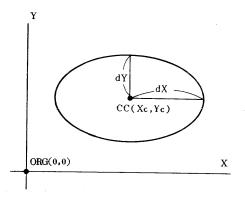

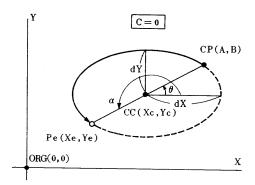

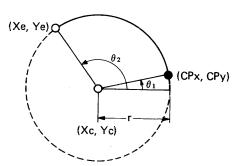

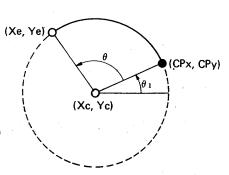

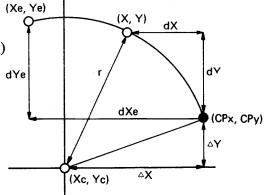

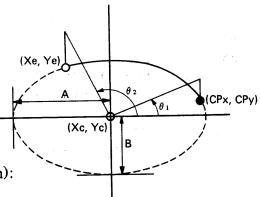

| US  | E OF              | ARC AND ELLIPSE ARC COMMAND | 301 |  |  |  |

| ELE | CTRIC             | CAL SPECIFICATION           | 300 |  |  |  |

Name Description

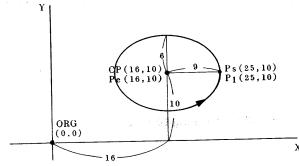

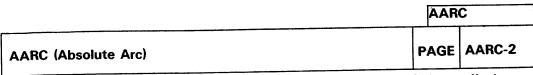

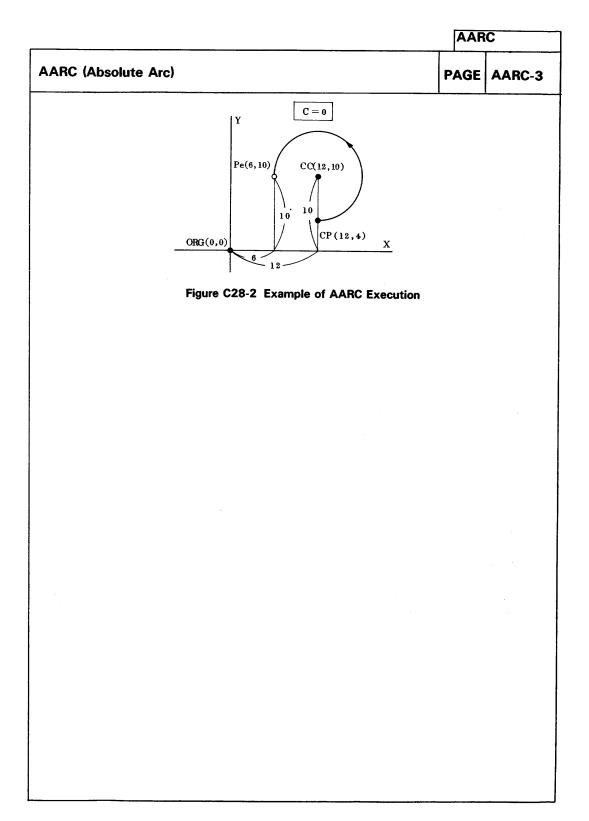

AARC Absolute Arc

ABT Abort

ACM Access Mode ACP Access Priority

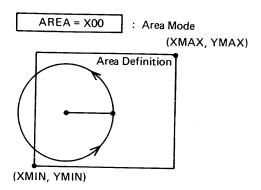

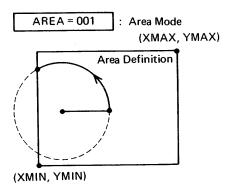

ADR Area Definition Register

AEARC Absolute Ellipse Arc

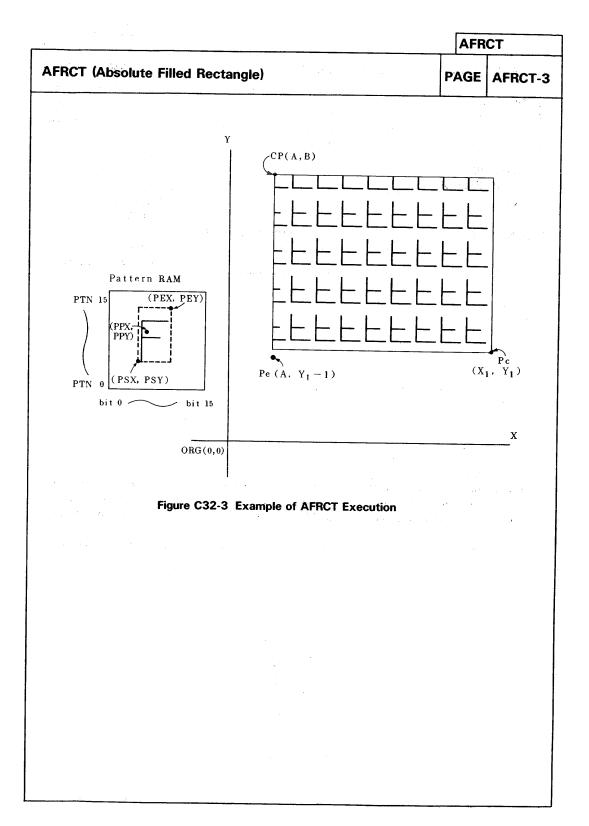

AFRCT Absolute Filled Rectangle

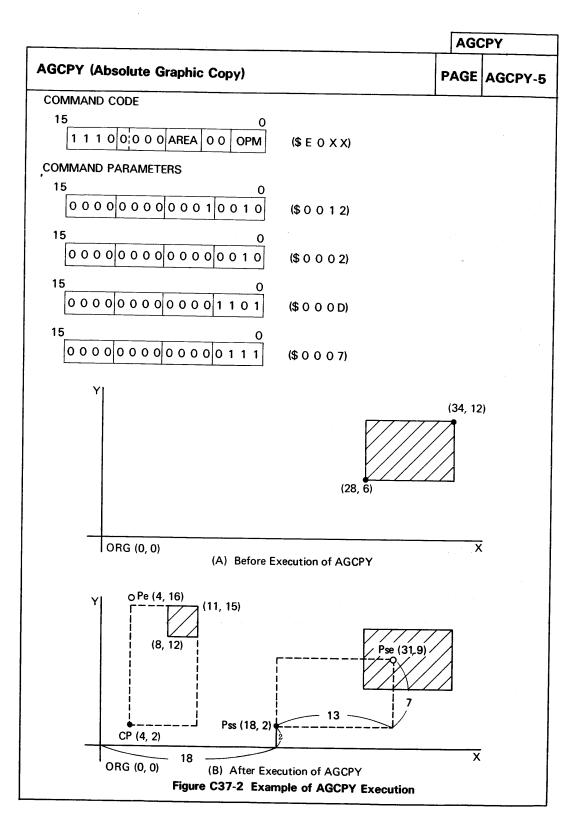

AGCPY Absolute Graphic Copy

ALINE Absolute Line

AMOVE Absolute Move

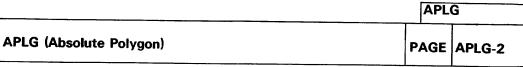

APLG Absolute Polygon

APLL Absolute Poly Line

AR Address Register

ARCT Absolute Rectangle

ARD Area Detect

ARE Area Detect Interrupt Enable

**AREA** Area Detect Mode **ATC** Attribute Code **ATR** Attribute Control **BCA Block Cursor Address** BCA1 Block Cursor Address 1 BCA2 Block Cursor Address 2 BCER1 Block Cursor End Raster 1 BCER2 Block Cursor End Raster 2 **BCR** Blink Control Register BCSR1 Block Cursor Start Raster 1 BCSR2 Block Cursor Start Raster 2 BCUR1 Block Cursor Register 1 BCUR2 Block Cursor Register 2 BCW1 Block Cursor Width 1 BCW2 Block Cursor Width 2

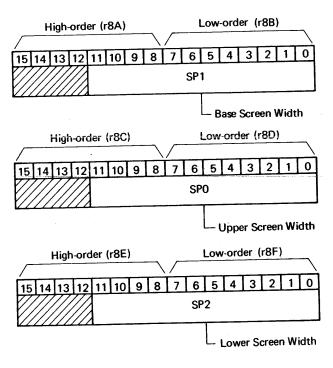

BLINK1 Blink 1

BLINK2 Blink 2

BOFF1 Blink Off 1

BOFF2 Blink Off 2

BON1 Blink On 1

BON2 Blink On 2

Name Description

CCR Command Control Register

CDM Command DMA Mode

CDR Cursor Definition Register

CED Command End

CEE Command End Interrupt Enable

CER Command Error

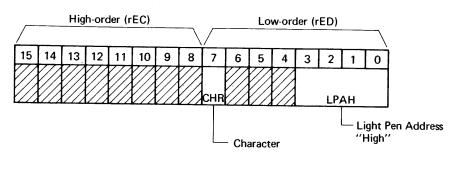

CHR Character CLR Clear

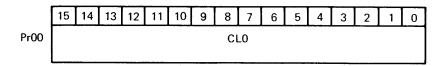

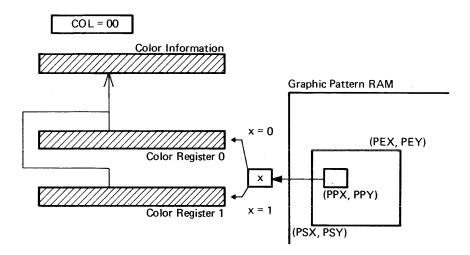

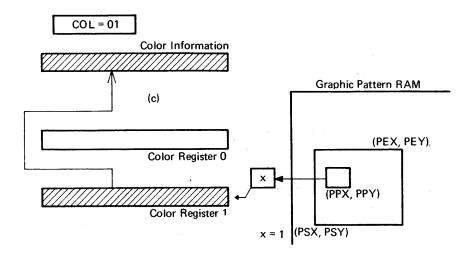

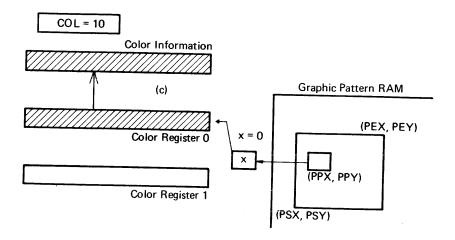

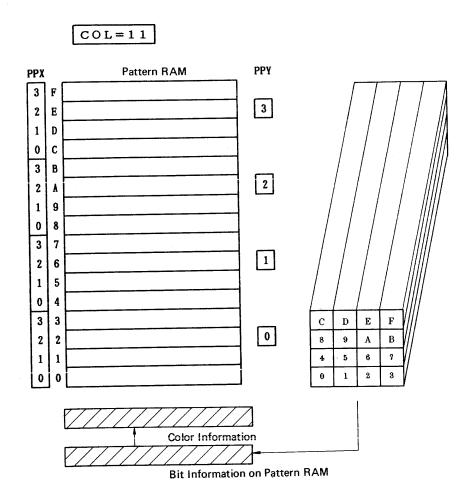

CL0 Color 0 Register

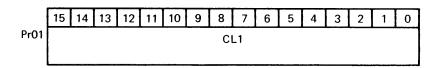

CL1 Color 1 Register

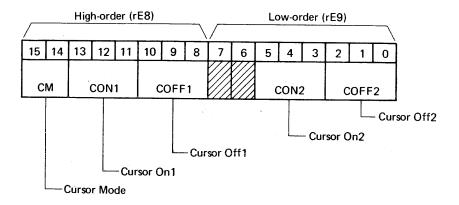

CM Cursor Mode

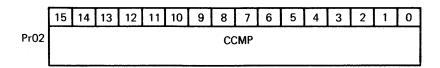

CCMP Color Comparison Register

COFF1 Cursor Off 1

COFF2 Cursor Off 2

CON1 Cursor On 1

CON2 Cursor On 2

CP Current Pointer

CPY Copy CRCL Circle

CRE Command Error Interrupt Enable

CSK Cursor Display Skew

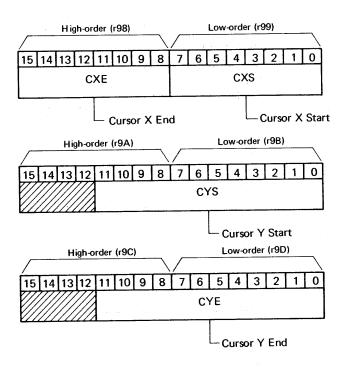

CXE Cursor X End

CXS Cursor X Start

CYE Cursor Y End

CYS Cursor Y Start

DCR Display Control Register

DDM Data DMA Mode

DMOD DMA Modify

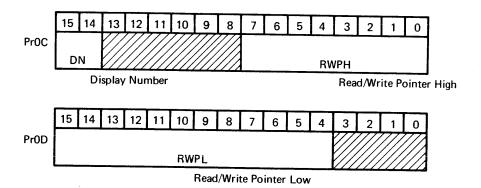

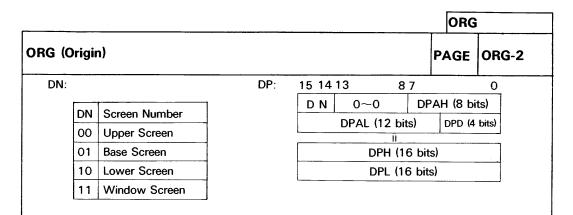

DN Display Number

DOT Dot

DP Drawing Pointer

DPAH Drawing Pointer Address High DPAL Drawing Pointer Address Low

DPD Drawing Pointer Dot DRC DMA Request Control

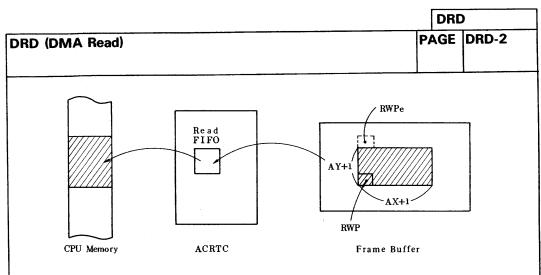

DRD DMA Read

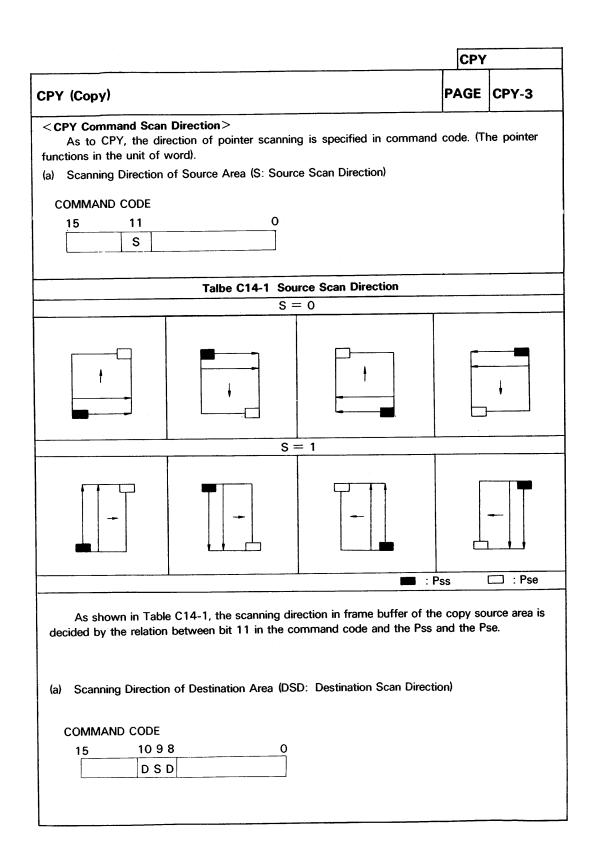

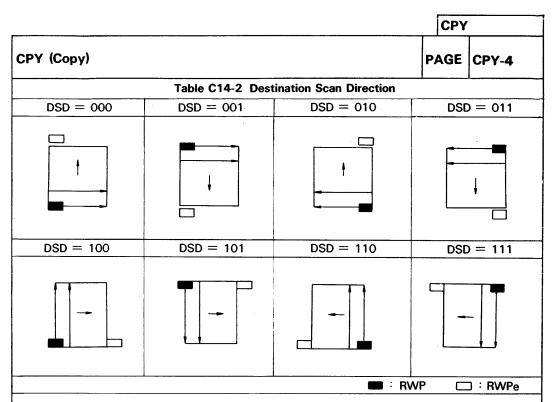

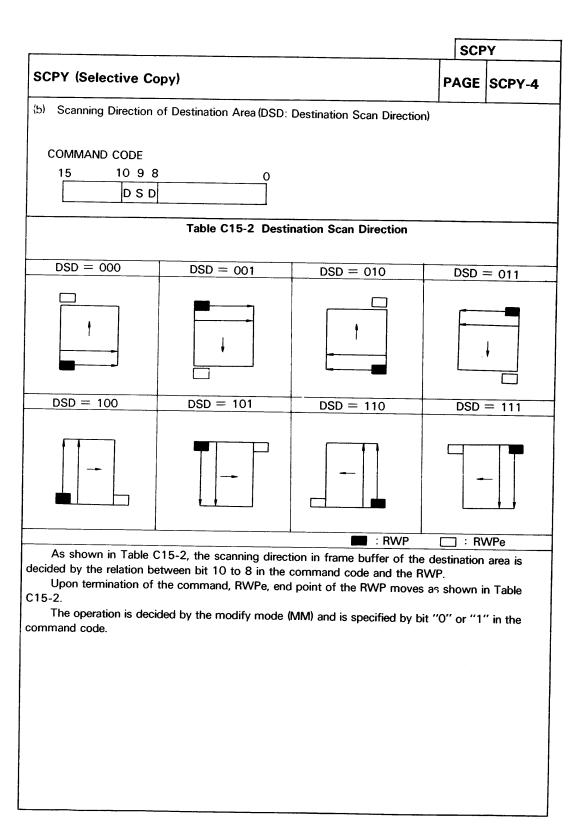

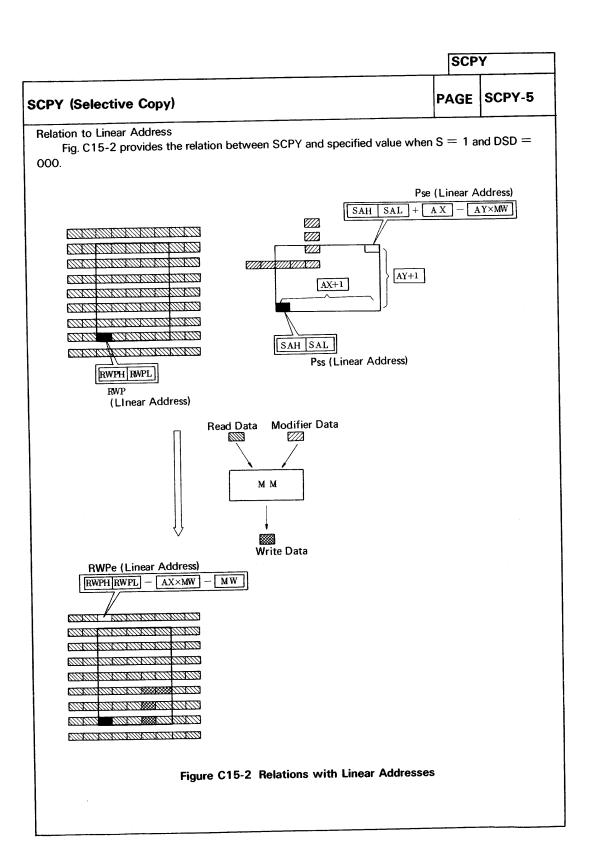

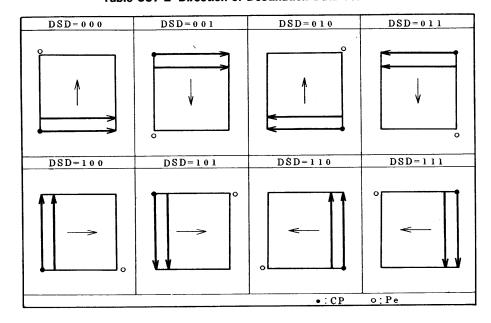

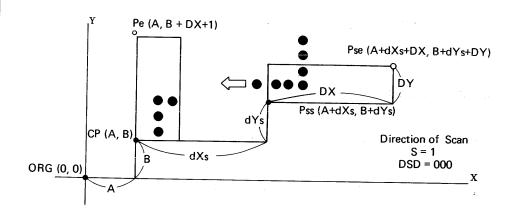

DSD Destination Scan Direction

| Name | Description                        |

|------|------------------------------------|

| DSK  | DISP Skew                          |

| DSP  | DISP Signal Control                |

| DWT  | DMA Write                          |

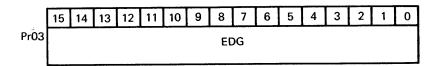

| EDG  | Edge Color Register                |

| ELPS | Ellipse                            |

| FE   | FIFO Entry                         |

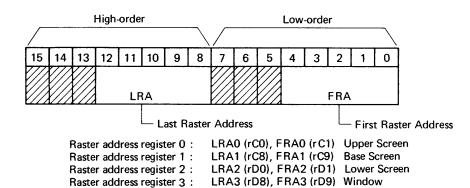

| FRA  | First Raster Address               |

| FRA0 | First Raster Address 0             |

| FRA1 | First Raster Address 1             |

| FRA2 | First Raster Address 2             |

| FRA3 | First Raster Address 3             |

| GAI  | Graphic Address Increment Mode     |

| GBM  | Graphic Bit Mode                   |

| GCR  | Graphic Cursor Register            |

| HC   | Horizontal Cycle                   |

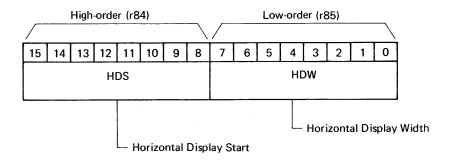

| HDR  | Horizontal Display Register        |

| HDS  | Horizontal Display Start           |

| HDW  | Horizontal Display Width           |

| HSD  | Horizontal Scroll Dot              |

| HSR  | Horizontal Sync Register           |

| HSW  | Horizontal Sync Width              |

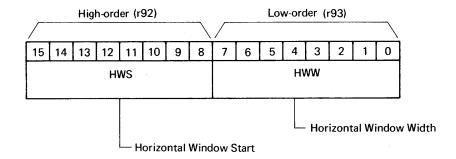

| HWR  | Horizontal Window Display Register |

| HWS  | Horizontal Window Start            |

| HWW  | Horizontal Window Width            |

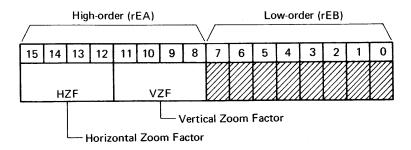

| HZ   | Horizontal Zoom                    |

| HZF  | Horizontal Zoom Factor             |

| IE   | Interrupt Enable                   |

| LPAH | Light Pen Address High             |

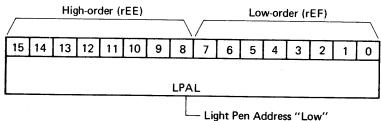

| LPAL | Light Pen Address Low              |

| LPAR | Light Pen Address Register         |

| LPD  | Light Pen Strobe Detect            |

| LPE  | Light Pen Strobe Interrupt Enable  |

| LRA  | Last Raster Address                |

| LRA0 | Last Raster Address 0              |

| LRA1 | Last Raster Address 1              |

| LRA2 | Last Raster Address 2              |

| LRA3 | Last Raster Address 3              |

Name Description

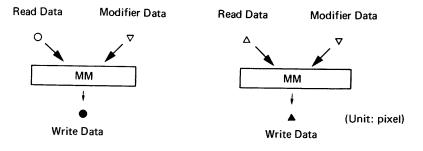

M/S Master/Slave MM Modify Mode

MOD Modify

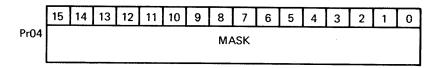

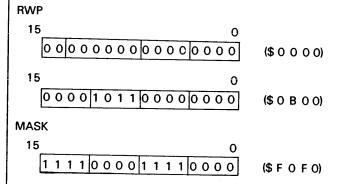

MASK Mask Register

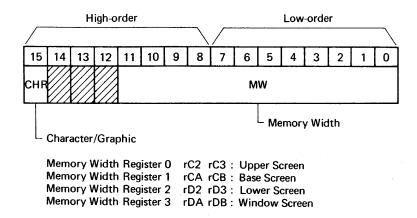

MW Memory Width

MW0 Memory Width 0

MW1 Memory Width 1

MW2 Memory Width 2

MW3 Memory Width 3

MWR Memory Width Register

MWR0 Memory Width Register 0

MWR1 Memory Width Register 1

MWR2 Memory Width Register 2

MWR3 Memory Width Register 3

OMR Operation Mode Register

OPM Operation Mode

ORG Origin PAINT Paint

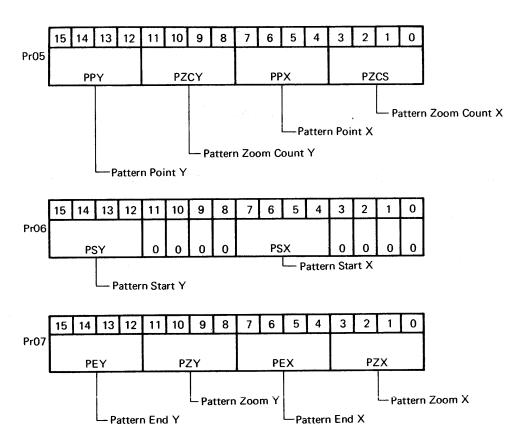

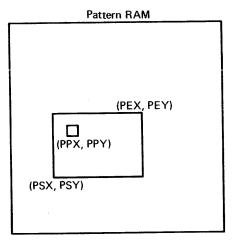

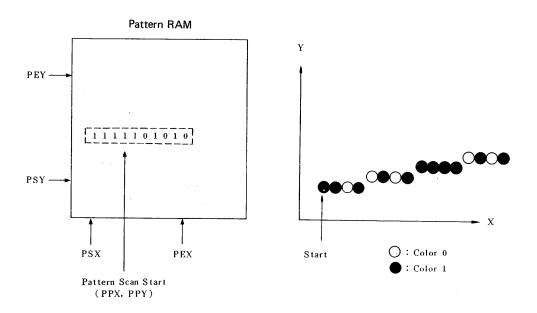

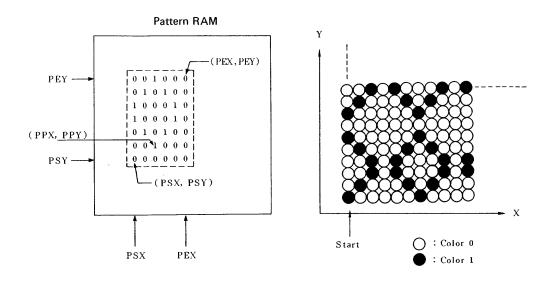

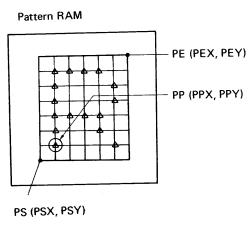

PE Pattern End

PEX Pattern End X

PEY Pattern End Y

PP Pattern Pointer

PPX Pattern Pointer X

PPY Pattern Pointer Y

PRA Pattern RAM Address

PRC Pattern RAM Control Register

PS Pattern Start

PSE Pause

PSX Pattern Start X PSY Pattern Start Y

PTN Pattern

PZCX Pattern Zoom Count X PZCY Pattern Zoom Count Y

PZX Pattern Zoom X

PZY Pattern Zoom Y

RAM RAM Mode

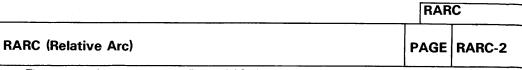

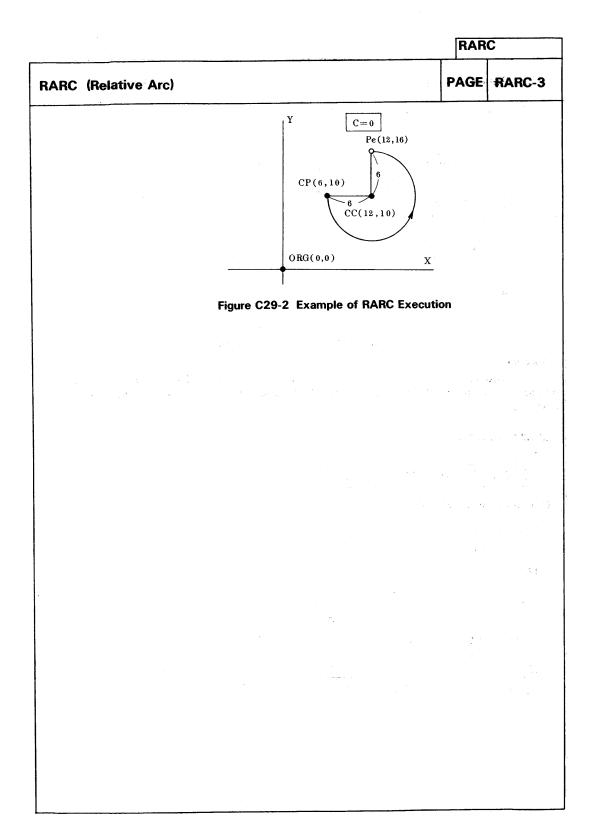

RARC Relative Arc

Name Description

RAR Raster Address Register

RAR0 Raster Address Register 0

RAR1 Raster Address Register 1

RAR2 Raster Address Register 2

RAR3 Raster Address Register 3

RC Raster Count

RCR Raster Count Register

RD Read

REARC Relative Ellipse Arc

RFE Read FIFO Full Interrupt Enable

RFF Read FIFO Full

RFR Read FIFO Ready

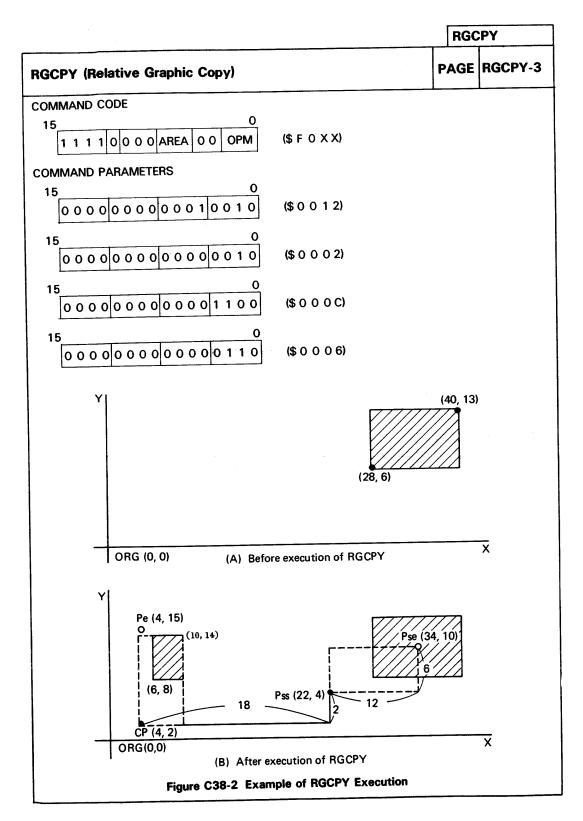

RFRCT Relative Filled Rectangle RGCPY Relative Graphic Copy

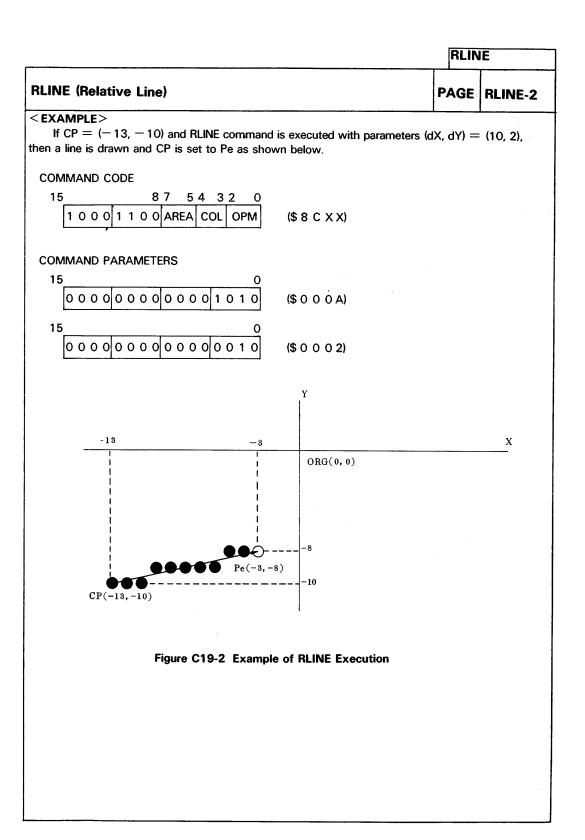

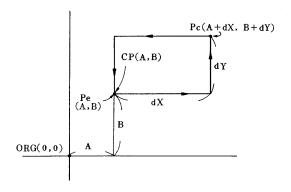

RLINE Relative Line

RMOVE Relative Move

RN Register Number

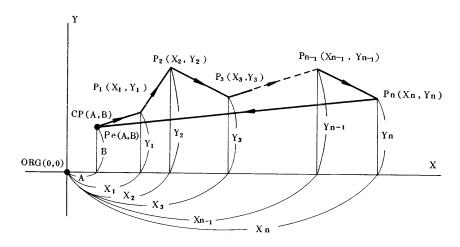

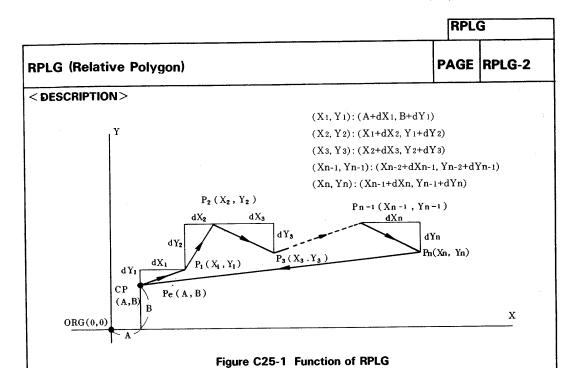

RPLG Relative Polygon

RPLL Relative Poly Line

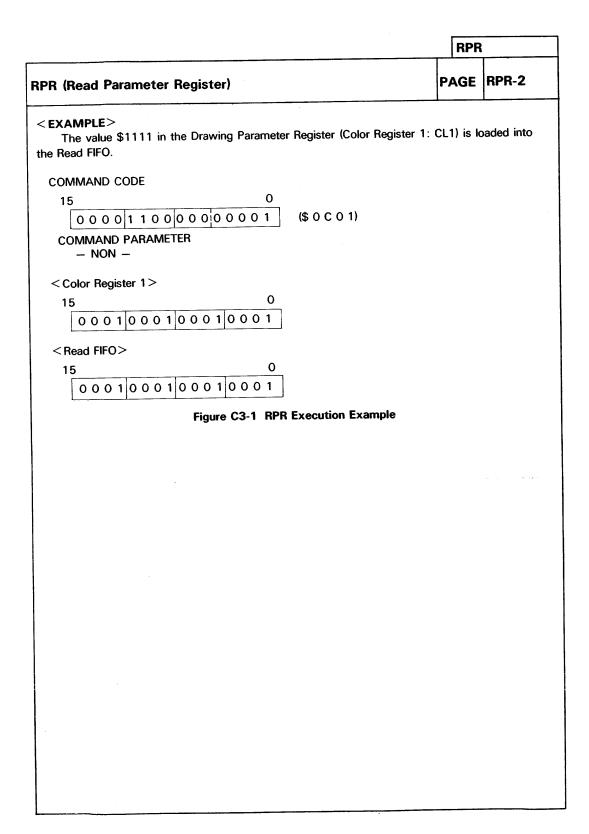

RPR Read Parameter Register

RPTN Read Pattern RAM

RRCT Relative Rectangle

RRE Read FIFO Ready Interrupt Enable

Start Address Register 3

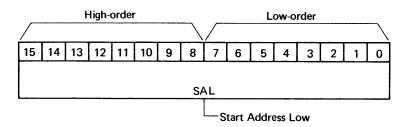

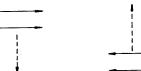

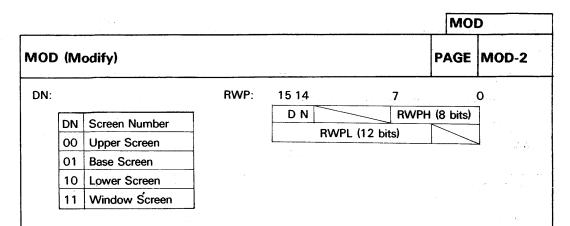

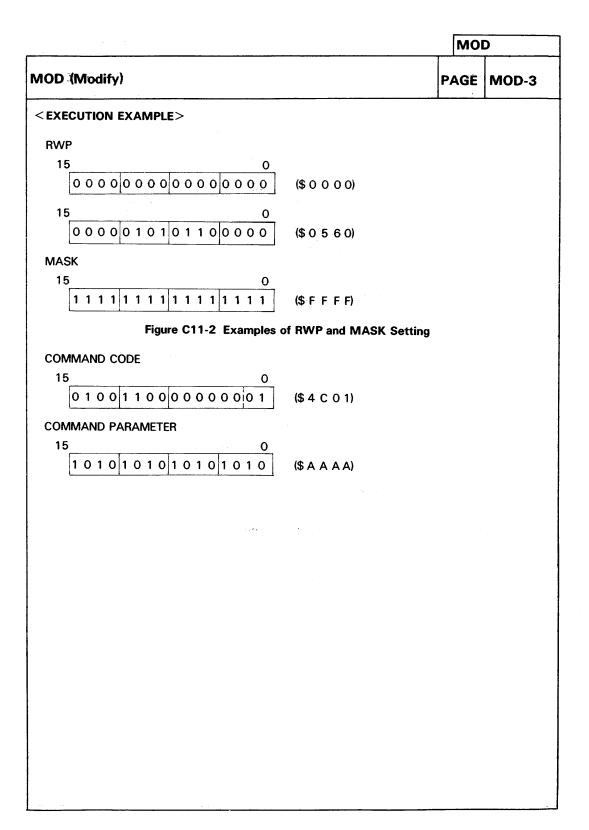

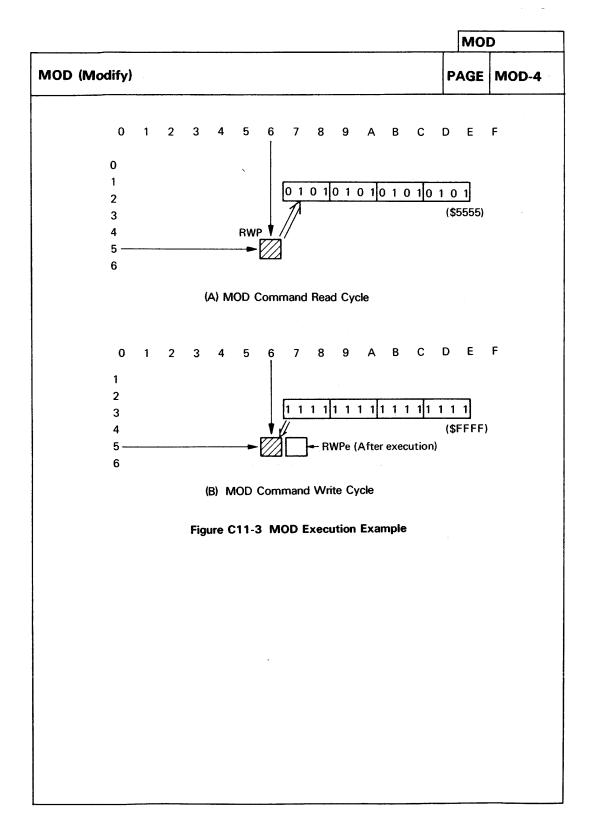

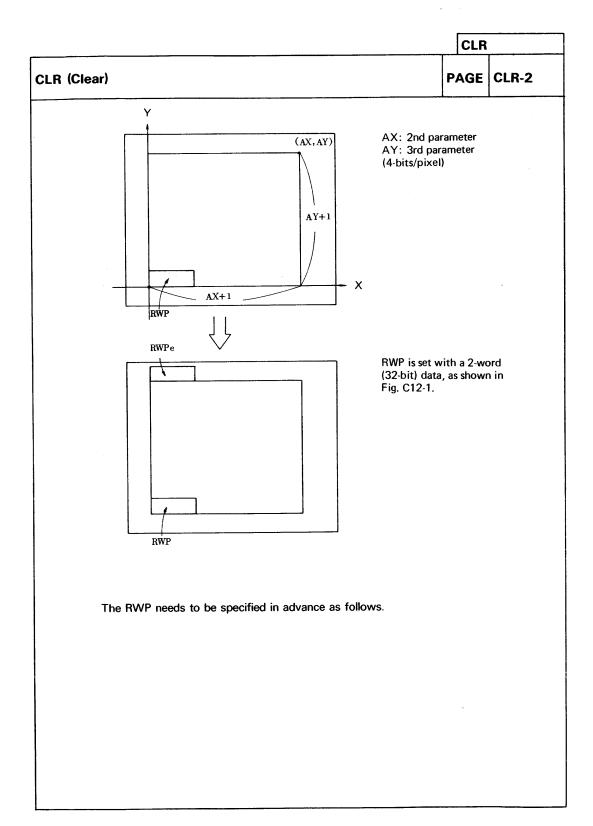

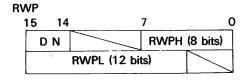

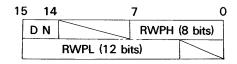

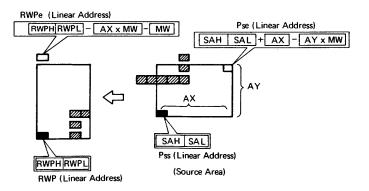

Raster Scan Mode **RSM** Read/Write Pointer **RWP** Read/Write Pointer High **RWPH** Read/Write Pointer Low **RWPL** Source Scan Direction S Start Address High SAH Start Address Low SAL Start Address Register SAR Start Address Register 0 SAR<sub>0</sub> Start Address Register 1 SAR1 Start Address Register 2 SAR2

SCLR Selective Clear SCPY Selective Copy

SAR3

| Name | Description                       |

|------|-----------------------------------|

| SD   | Scan Direction                    |

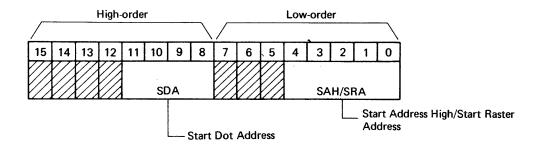

| SDA  | Start Dot Address                 |

| SE   | Split Screen Enable               |

| SE0  | Split Screen 0 Enable             |

| SE1  | Split Screen 1 Enable             |

| SE2  | Split Screen 2 Enable             |

| SE3  | Split Screen 3 Enable             |

| SL   | Slant                             |

| SPL  | Split                             |

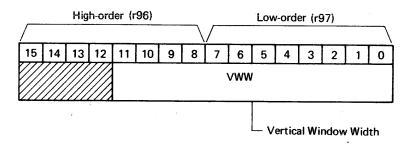

| SP0  | Split Screen 0 Width              |

| SP1  | Split Screen 1 Width              |

| SP2  | Split Screen 2 Width              |

| SR   | Status Register                   |

| SRA  | Start Raster Address              |

| SSW  | Split Screen Width                |

| STR  | Start                             |

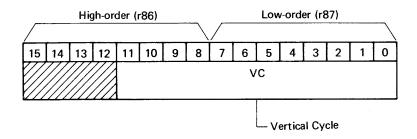

| VC   | Vertical Cycle                    |

| VDR  | Vertical Display Register         |

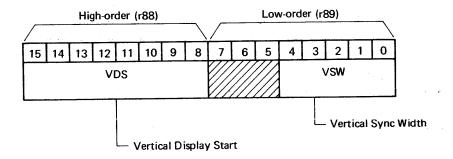

| VDS  | Vertical Display Start            |

| VSR  | Vertical Sync Register            |

| VSW  | Vertical Sync Width               |

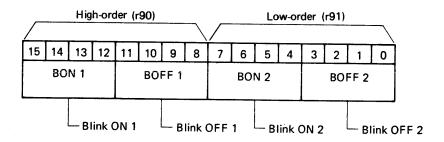

| VWR  | Vertical Window Register          |

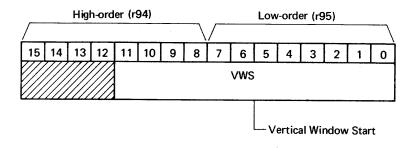

| VWS  | Vertical Window Start             |

| VWW  | Vertical Window Width             |

| VZF  | Vertical Zoom Factor              |

| WEE  | Write FIFO Empty Interrupt Enable |

| WFE  | Write FIFO Empty                  |

| WFR  | Write FIFO Ready                  |

| WPR  | Write Parameter Register          |

| WPTN | Write Pattern RAM                 |

| WRE  | Write FIFO Ready Interrupt Enable |

| WSS  | Window Smooth Scroll              |

| WT   | Write                             |

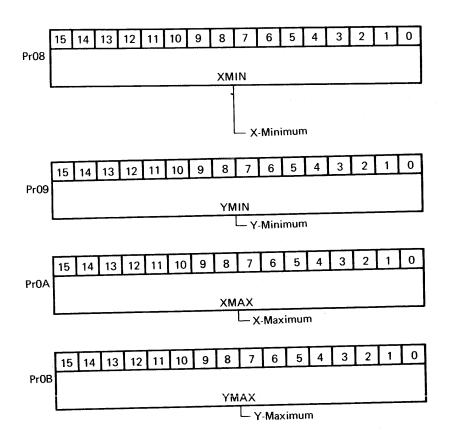

| XMAX | X Maximum                         |

| XMIN | X Minimum                         |

| YMAX | Y Maximum                         |

| YMIN | Y Minimum                         |

| ZFR  | Zoom Factor Register              |

#### HD63484 ACRTC

#### (Advanced CRT Controller)

Powerful visual interfaces are a key component of advanced system architectures. A proven technique uses raster scanned CRT technology for the display of graphics and text information.

Systems which use first generation CRT Controllers (CRTCs) are constrained by hardware/software design time, manufacturing cost, and limited MPU bandwidth.

To meet the functional requirements for powerful visual interfaces, and to support their use in high volume, cost sensitive applications, advanced circuit design and VLSI CMOS manufacturing technologies have been used to create a next generation CRTC, the HD63484 ACRTC (Advanced CRT Controller).

The ACRTC concept is to incorporate major functionality, formerly requiring external hardware and software, on-chip. In this way, both higher performance and reduced system cost benefits are achieved.

- \* High Level Command Language Increases Performance and Reduces Software Development Cost.

- ACRTC Converts Logical X-Y Coordinates to Physical Frame Buffer Addresses.

- 38 Commands including 23 Graphic Drawing Commands LINE, REC-TANGLE, POLYLINE, POLYGON, CIRCLE, ELLIPSE, ARC, ELLIPSE ARC, FILLED RECTANGLE, PAINT, PATTERN and COPY.

- On-chip 32 Byte Pattern RAM.

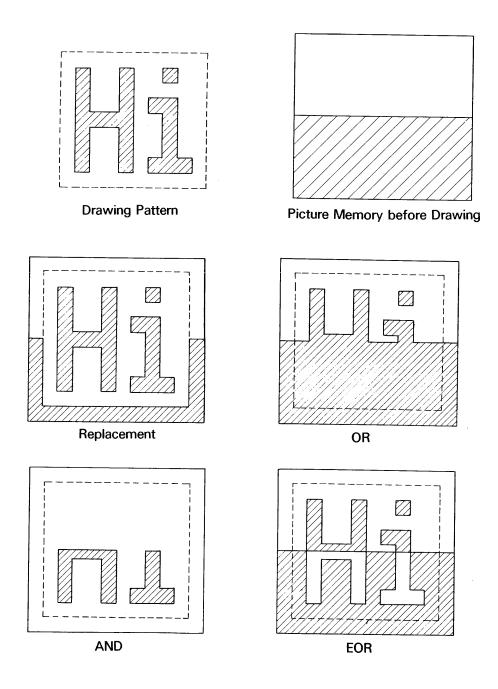

- Conditional Drawing function (8 conditions) for Drawing Patterns, Color Mixing and Software Windowing.

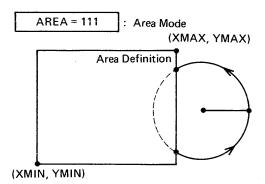

- Drawing Area Control with Hardware Clipping and Hitting.

- Maximum Drawing Speed of 2 Million Logical Pixels per Second is the same for Monochrome and Color applications.

- \* High Resolution Display with Advanced Screen Control

- Up to 4096 by 4096 Bit Map GRAPHIC Display and/or 256 Line by 256 Character by 32 Raster CHARACTER Display.

- Separate Bit Map GRAPHIC (2M byte) and CHARACTER (128K byte) Address Spaces with Combined GRAPHIC/CHARACTER Display.

- Three Horizontal Split Screens and One Window Screen.

Size and Postition Fully Programmable.

- Independent Horizontal and Vertical Smooth Scroll for each Screen.

- 1 to 16 Zoom Magnitude Independent X and Y Zoom Factors.

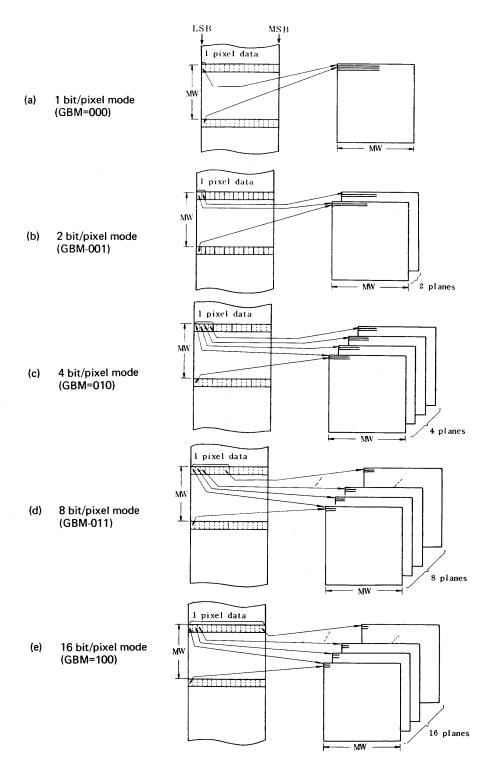

- Logical Pixel Specification as 1, 2, 4, 8 or 16 Bits for Monochrome, Gray Scale and Color Displays.

- Programmable Address Increment Supports Frame Buffer Memory Widths to 128 Bits for Video Bit Rates > 500 MHz.

- Unique Interleaved Access Mode for Screen Superimposition or 'Flashless' Displays.

- ACRTC provides Dynamic RAM Refresh Address.

- \* High Performance MPU Interface

- Optimized Interface with the HD68000 MPU and HD68450 DMAC.

- 8 or 16 Bit Bus Compatible With Other MPUs.

- Separate on-chip 16 Byte READ and WRITE FIFOs.

- Maskable Interrupts Including FIFO status.

- \* Versatile CRT Interface

- Full Programmability of CRT Timing Signals.

- Three Raster Scanning Modes.

- Master or Slave Synchronization to Multiple ACRTCs or Other Video Generating Devices.

- Two Hardware Cursors. Three Cursor Modes.

- Progreammable Cursor and Display Timing Skew.

- Eight User Defineable Video Attributes.

- Light Pen Detection.

- \* VLSI CMOS Process

#### 1. ACRTC INTRODUCTION

#### 1.1 Applications

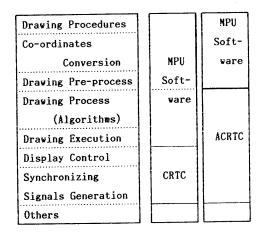

The overall function of a visual interface is logically partitioned into layers. At the lowest layer are CRT timing and control signal generation. At the top layer are general purpose drawing procedures which provide a high-level interface to the users OS or application software. At this layer, a number of popular standards have emerged including GKS, Core, NAPLP, GSX and others.

Figure 1.1 shows how the ACRTC performs the key functions or logical drawing algorithm and physical drawing execution. Formerly, these function were performed by external hardware and/or MPU software.

Figure 1.1 ACRTC vs. CRTC

As shown, the ACRTC reduces the 'gap' between device functionality and high level graphics procedures. Since the ACRTC device itself provides capabilities closely related to those of high level graphics packages, the effort (hardware and software design time and cost) required to develop a visual interface is significantly reduced.

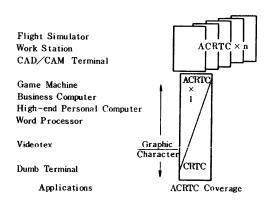

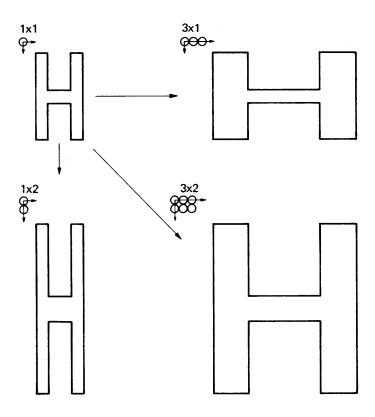

Noting the traditional and emerging applications for visual interfaces, figure 1.2 shows that a single ACRTC is suitable for a broad range of products in both alphanumeric and graphics areas.

Multiple ACRTCs can achieve performance beyond that of any first generation CRTC configuration.

Figure 1.2 Application Spectrum

#### 1.2 System Configuration

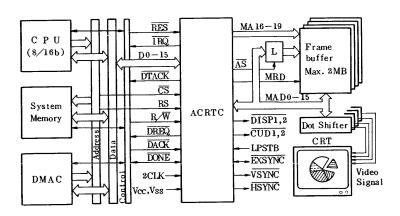

Figure 1.3 System Configuration

Existing CRTCs provide a single bus interface to the frame buffer which must be shared with the host MPU. However, the refresh of large frame buffers and the requirement to access the frame buffer for drawing operations can quickly saturate this shared bus bandwidth.

As shown, the ACRTC uses separate host MPU and frame buffer bus interfaces. This allows the ACRTC full access to the frame buffer for display refresh, DRAM refresh and drawing operations while minimizing the ACRTCs usage of the MPU system bus. Thus, overall system performance is maximized. A related benefit is that a large frame buffer (2M byte for each ACRTC) is useable even if the host MPU has a smaller address space or segment size restriction.

The ACRTC can utilize an external DMA Controller. This increases system throughput when large amounts of command, parameter and data information must be transferred to the ACRTC. Also, advanced DMAC features, such as the HD68450 DMACs 'chaining' modes, can be used to develop powerful graphics system architectures.

However, more cost sensitive or less performance sensitive applications do not require a DMAC. The interface to the ACRTC can be handled completely under MPU software control.

While both ACRTC bus interfaces (Host MPU and Frame Buffer) exploit 16 bit data paths for maximum performance, the ACRTC also offers an 8 bit MPU mode for easy connection to popular 8 bit bus structures.

#### 1.3 Block Diagram

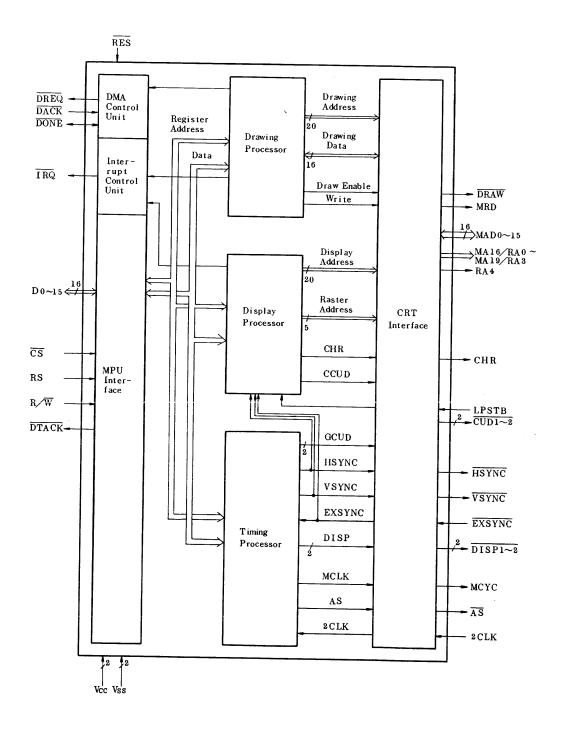

Figure 1.4 Block Diagram

#### 6 HITACHI

The ACRTC consists of five major functional blocks. These functional blocks operate in parallel to achieve maximum performance. Two of the blocks perform the external bus interface for the host MPU and CRT respectively.

#### O MPU Interface

Manages the asynchronous host MPU interface including the programmable interrupt control unit and DMA handshaking control unit.

#### O CRT Interface

Manages the frame buffer bus and CRT timing input and output control signals. Also, the selection of either display refresh address or drawing address outputs is performed.

The other three blocks are separately microprogrammed processors which operate in parallel to perform the major functions of drawing, display control and timing.

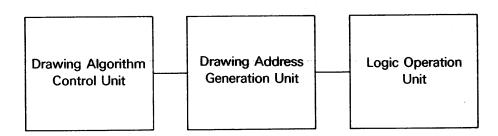

#### O Drawing Processor

Interprets commands and command parameters issued by the host bus (MPU and/or DMAC) and performs the drawing operations on the frame buffer memory. This processor is responsible for the execution of ACRTC drawing algorithms and conversion of logical pixel X-Y addresses to physical frame buffer addresses.

Communication with the host bus is via separate 16 byte read and write FIFOs.

#### O Display Processor

Manages frame buffer refresh addressing based on the user programmed specification of display screen organization. Combines and displays as many as 4 independent screen segments (3 horizontal splits and 1 window) using an internal high speed address calculation unit. Controls display refresh address outputs based on GRAPHIC (physical frame buffer address) or CHARACTER (physical frame buffer address + row address) display modes.

#### O Timing Processor

Generates the CRT synchronization signals and other timing signals used internally by the ACRTC.

The ACRTCs software visible registers are similarly partitioned and reside in the appropriate internal processor depending on function. The registers in the Display and Timing processors are loaded with basic display parameters during system initialization. During operation, the host primarily communicates with the ACRTCs Drawing processor via the on-chip FIFOs.

#### 1.4 Signal Description

Following is a brief description of the ACRTC pin functions organized as MPU Interface, DMAC Interface, CRT Interface and Power Supply. The detailed signal description is provided in section 4.

#### **MPU Interface**

RES - Input

Hardware reset input to the ACRTC.

D0 - D15 - Input/Output

The bidirectional data bus for communication with the host MPU or DMAC. In 8 bit data bus mode, DO-D7 are used.

$R/\overline{W}$  – Input

Controls the direction of host ←→ ACRTC transfers.

$\overline{\text{CS}}$  – Input

Enables data transfers between the host and the ACRTC.

RS - Input

Selects the ACRTC register to be accessed and is normally connected to the least significant bit of the host address bus.

DTACK - Output

Provides asynchronous bus cycle timing and is compatible with the HD68000 MPU  $\overline{DTACK}$  input.

IRQ - Output

Generates interrupt service requests to the host MPU.

#### **DMAC Interface**

DREO - Output

Generates DMA service requests to the host DMAC.

DACK - Input

Receives DMA acknowledge timing from the host DMAC.

DONE - Input/Output

Terminates DMA transfer and is compatible with the HD68450 DMAC  $\overline{\text{DONE}}$  signal.

#### **CRT Interface**

2CLK - Input

Basic ACRTC operating clock derived from the dot clock.

MAD0-15 - Input/Output

Multiplexed frame buffer address/data bus.

$\overline{AS}$  – Output

Address strobe for demultiplexing the frame buffer address/data bus (MAD0-15).

MA16/RA0-MA19/RA3 — Output

The high order address bits for graphic screens and the raster address outputs for character screens.

RA4 - Output

Provides the high order raster address bit (up to 32 rasters) for character screens.

CHR - Output

Indicates whether a graphic or character screen is being accessed.

MCYC - Output

Frame buffer memory access timing - one half the frequency of 2CLK.

MRD - Output

Frame Buffer data bus direction control.

DRAW - Output

Differentiates between drawing cycles and CRT display refresh cycles.

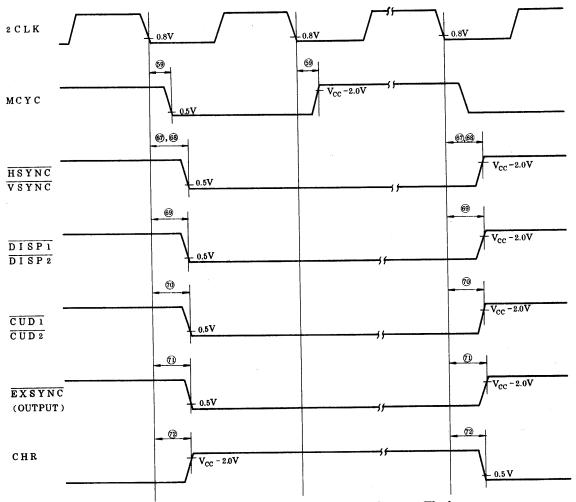

DISP1, DISP2 - Output

Programmable display enable timing used to selectively enable, disable and blank logical screens.

$\overline{\text{CUD1}}$ ,  $\overline{\text{CUD2}}$  — Output

Provides cursor timing determined by ACRTC programmed parameters such as cursor definition, cursor mode, cursor address, etc.

VSYNC - Output

CRT device vertical synchronization pulse.

HSYNC - Output

CRT device horizontal synchronization pulse.

EXSYNC - Input/Output

For synchronization between multiple ACRTCs and other video signal generating devices.

LPSTB - Input

Connection to an external light pen.

#### 1.5 Address Space

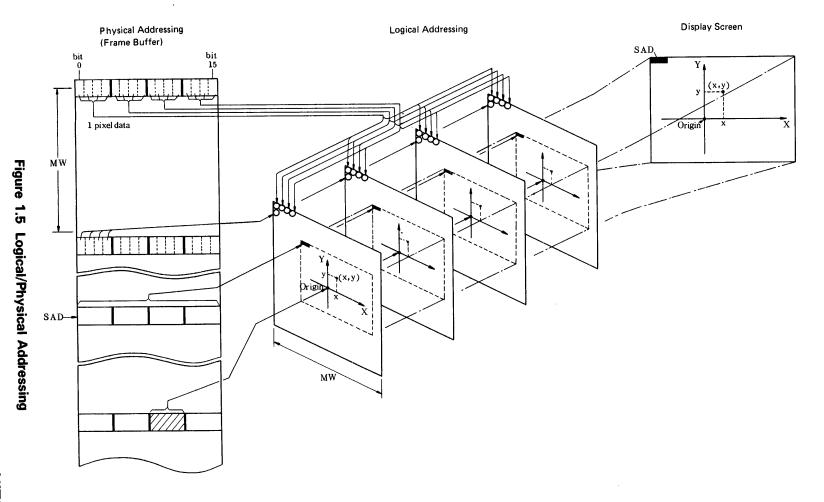

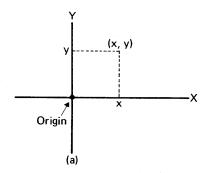

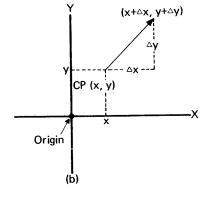

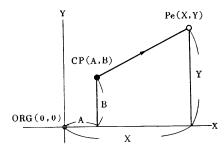

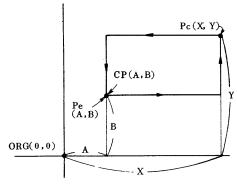

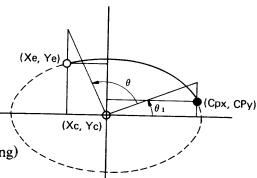

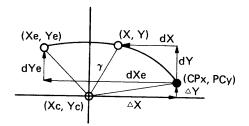

The ACRTC allows the host to issue commands using logical X-Y coordinate addressing. The ACRTC converts these to physical linear word addresses with bit field offsets in the frame buffer.

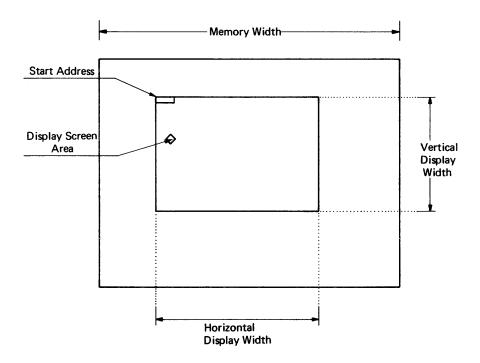

Figure 1.5 shows the relationship between a logical X-Y screen address and the frame buffer memory, organized as sequential 16 bit words. The host may specify that a logical pixel consists of 1, 2, 4, 8 or 16 physical bits in the frame buffer. In the example, 4 bits per logical pixel is used allowing 16 colors or tones to be selected.

Up to four logical screens (Upper, Base, Lower and Window) are mapped into the ACRTC physical address space. The host specifies a logical screen physical start address, logical screen physical memory width (number of memory words per raster), logical pixel physical memory width (number of bits per pixel) and the logical origin physical address. Then, logical pixel X-Y addresses issued by the host or by the ACRTC Drawing processor are converted to physical frame buffer addresses. The ACRTC also performs bit extraction and masking to map logical pixel operations (in the example, 4 bits) to 16 bit word frame buffer accesses.

#### 1.6 Registers

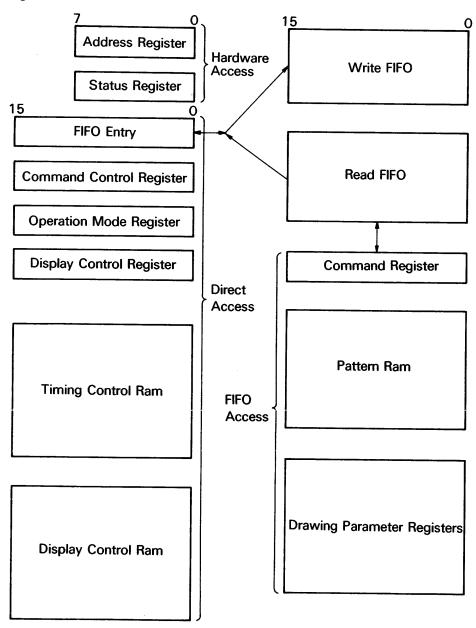

Figure 1.6 Accessible Registers

The ACRTC has over two hundred bytes of accessible registers. These are organized as Hardware, Directly and FIFO accessible.

#### O Hardware Accessible

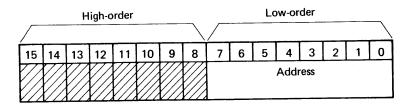

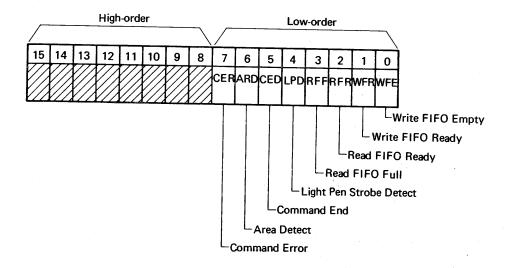

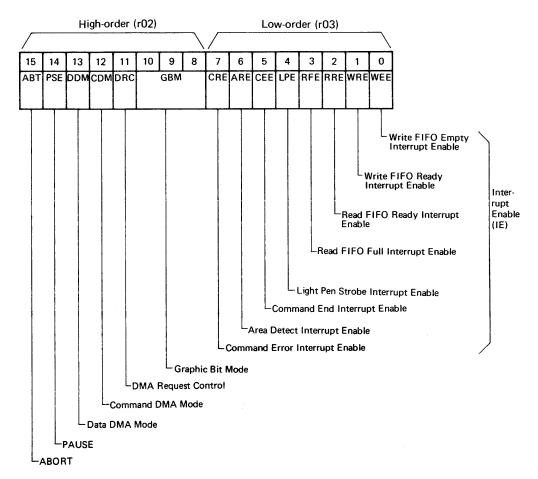

The ACRTC is connected to the host MPU as a standard peripheral which occupies two word locations of the host address space. The RS (Register Select) pin selects one of these two locations. When RS is low, reads access the Status Register and writes access the Address Register.

The Status Register summarizes the ACRTC state and is used by the MPU to monitor the overall operation of the ACRTC. The Address Register is used to program the ACRTC with the address of the specific directly accessible register which the MPU wishes to access.

#### O Directly Accessible

These registers are accessed by prior loading of the Address Register with the chosen register address. Then, when the MPU accesses the ACRTC with RS=1, the chosen register is accessed.

The FIFO entry enables access to FIFO accessible registers using the ACRTC read and write FIFOs.

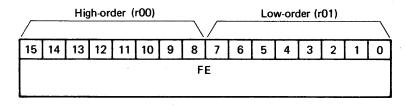

The Command Control Register is used to control overall ACRTC operation such as aborting or pausing commands, defining DMA protocols, enabling/disabling interrupt sources, etc.

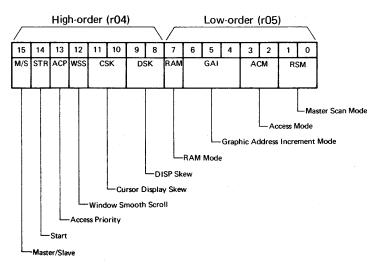

The Operation Mode Register defines basic parameters of ACRTC operation such as frame buffer access mode, display or drawing priority, cursor and display timing skew factors, raster scan mode, etc.

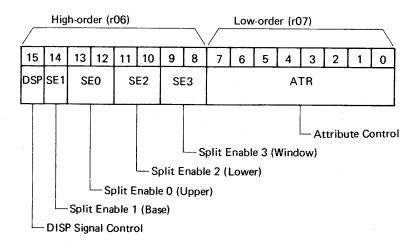

The Display Control Register allows the independent enabling and disabling of each of the four ACRTC logical display screens (Base, Upper, Lower and Window). Also, this register contains the 8 bits of user defineable video attributes.

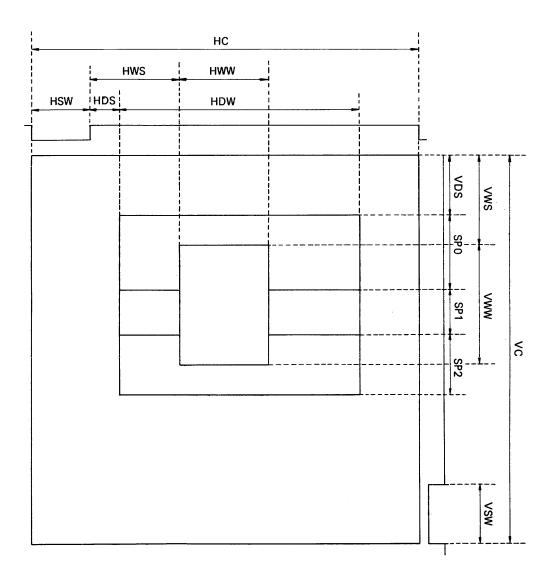

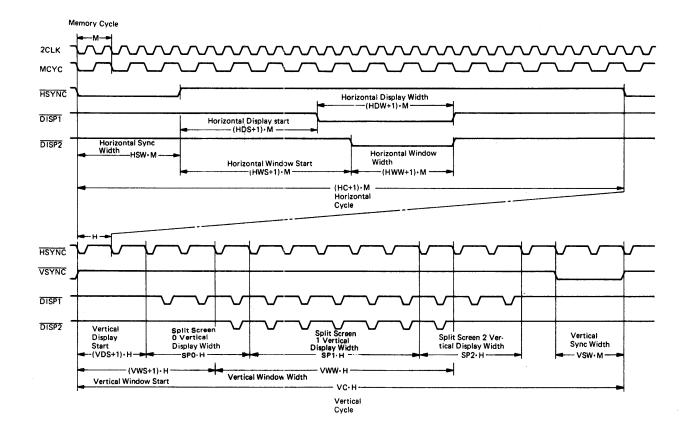

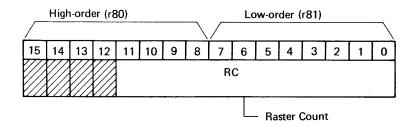

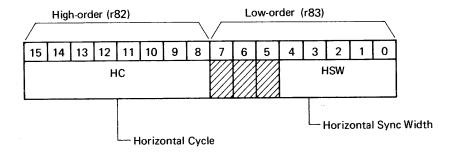

The Timing Control RAM contains registers which define ACRTC timing. This includes timing specification for CRT control signals (e.g. HSYNC, VSYNC), logical display screen size and display period, blink timing, etc.

The Display Control RAM contains registers which define logical screen display parameters such as start addresses, raster addresses and memory width. Also included are the cursor(s) definition, zoom factor and light pen registers.

#### O FIFO Accessible

For high performance drawing, key Drawing Processor registers are coupled to the host via the ACRTCs separate 16 byte read and write FIFOs.

ACRTC commands are sent from the MPU via the write FIFO to the Command register. As the ACRTC completes command execution, the next command is automatically fetched from the FIFO into the Command register.

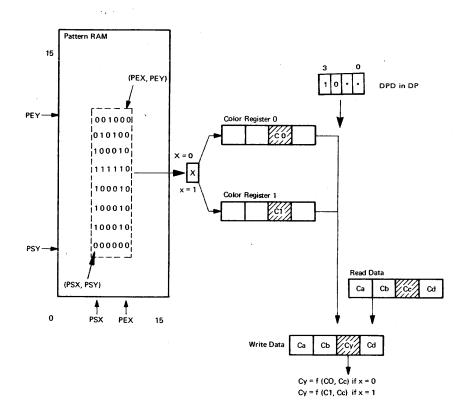

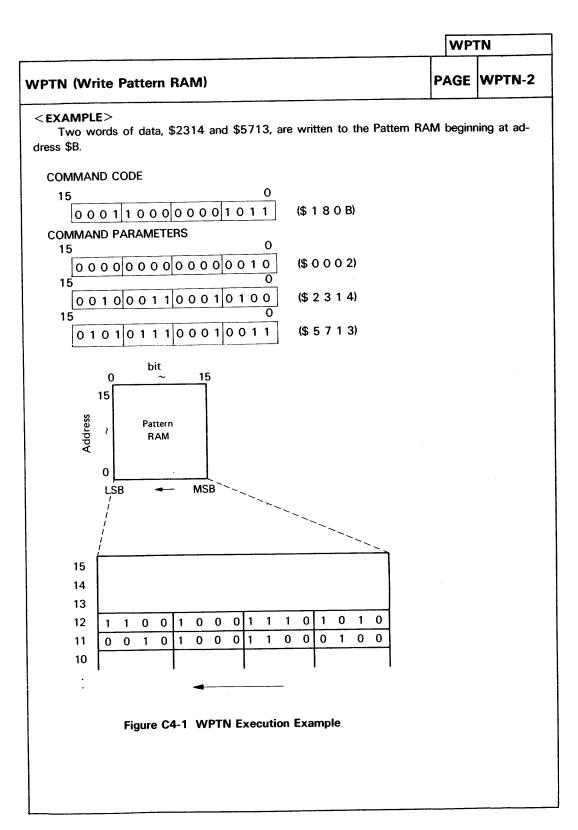

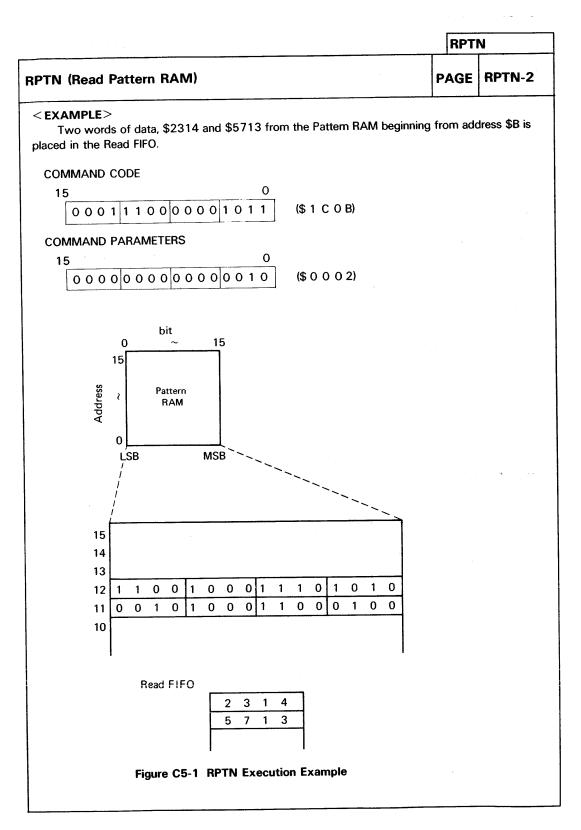

The Pattern RAM is used to define drawing and painting 'patterns'. The Pattern RAM is accessed using the ACRTCs Read Pattern RAM (RPTN) and Write Pattern RAM (WPTN) register access commands.

The Drawing Parameter Registers define detailed parameters of the drawing process, such as color control, area control (hitting/clipping) and Pattern RAM pointers. The Drawing Parameter Registers are accessed using the ACRTCs Read Parameter Register (RPR) and Write Parameter Register (WPR) register access commands.

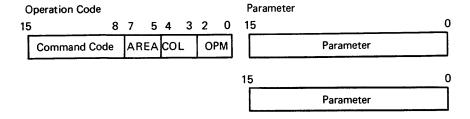

#### 1.7 Commands

| Туре                                                                                                                                     | Mnemonic                    | Function                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------|

| Register<br>Access<br>Commands                                                                                                           | ORG<br>RPR,WPR<br>RPTN,WPTN | Set Origin Point<br>Read/Write Parameter Registers<br>Read/Write Pattern RAM                                        |

| Data DRD,DWT,DMOD Transfer RD,WT,MOD CLR CPY,SCPY                                                                                        |                             | DMA Read/Write/Modify<br>Read/Write/Modify<br>Clear<br>Copy                                                         |

| AMOVE,RMOVE ALINE,RLINE ARCT,RRCT APLL,RPLL APLG,RPLG CRCL Drawing Commands  AARC,RARC AEARC,REARC AFRCT,RFRCT PAINT DOT PTN AGCPY,RGCPY |                             | Move Line Rectangle Polyline Polygon Circle Ellipse Arc Ellipse Arc Filled Rectangle Paint Dot Pattern Graphic Copy |

Figure 1.7 Commands

The ACRTC has 38 commands classified into three groups — REGISTER ACCESS, DATA TRANSFER and GRAPHIC DRAWING.

Five REGISTER ACCESS commands allow access to Drawing processor Drawing Parameter Registers and the Pattern RAM.

Ten DATA TRANSFER commands are used to move data between the host system memory and the frame buffer, or within the frame buffer.

Twenty three GRAPHIC DRAWING commands cause the ACRTC to perform drawing operations. Parameters for these commands are specified using logical X-Y addressing.

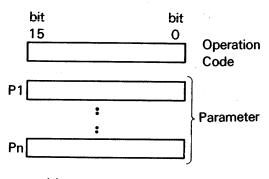

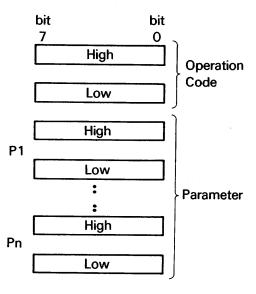

All the above commands, parameters and data are transferred via the ACRTC read and write FIFOs.

#### 1.8 Graphic Drawing

Assuming the ACRTC has been properly initialized, the MPU must perform two steps to cause graphic drawing.

First, the MPU must specify certain drawing parameters which define a number of details associated with the drawing process. For excample, to draw a figure or paint an area, the MPU must specify the drawing or painting 'pattern' by initializing the ACRTC Pattern RAM and related pointers. Also, if clipping and hitting control are desired, the MPU specifies the 'arera' to be monitored during drawing by initializing area definition registers. Other drawing parameters include color, edge definition, etc.

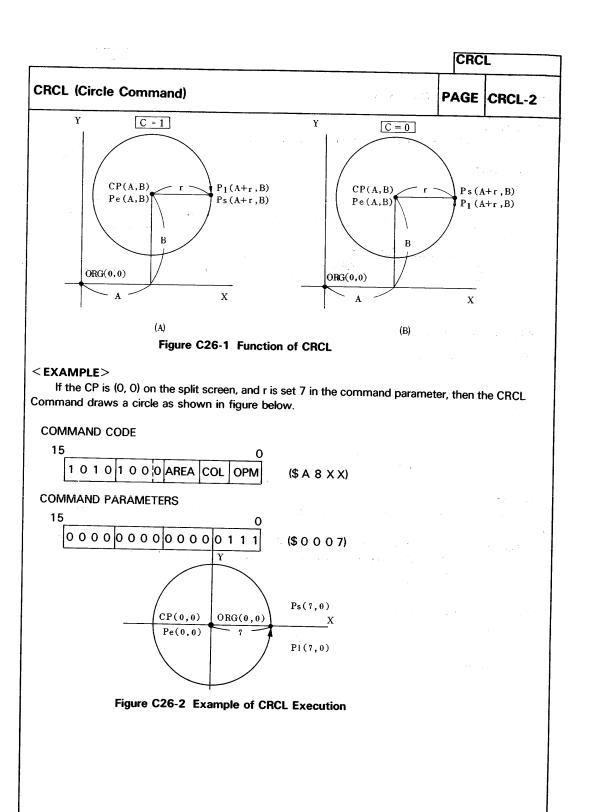

After the drawing parameters have been specified, the MPU issues a graphic drawing command and any required command parameters, such as the CRCL (Circle) command with a radius parameter. The ACRTC then performs the specified drawing operation by reading, modifying and rewriting the contents of the frame buffer.

#### 2. SYSTEM INTERFACE

#### 2.1 Basic Clock

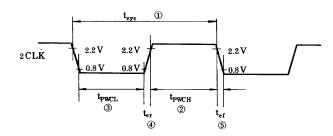

The ACRTC basic clock is 2CLK. 2CLK controls all primary ACRTC display and logic timing parameters.

2CLK, along with the specification of number of bits per logical pixel, the Graphic Address Increment mode and the Display Access mode, also determines the video data rate.

#### 2.2 CRT Interface

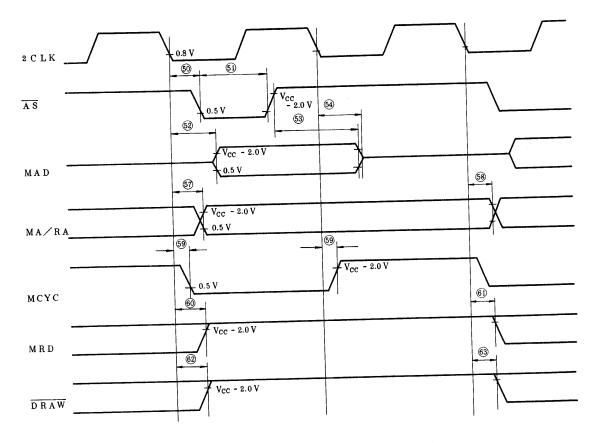

#### 2.2.1 Frame Buffer Access

#### 2.2.1.1 Access Modes

The three ACRTC display memory access modes are Single, Interleaved and Superimposed.

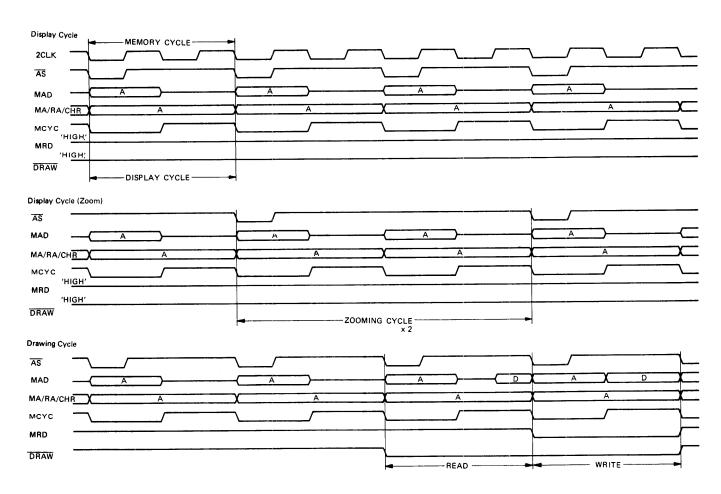

#### (a) Single Access Mode

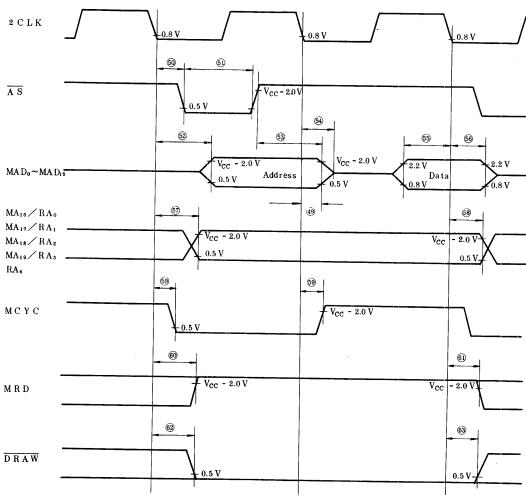

A display (or drawing) cycle is defined as two cycles of 2CLK. During the first 2CLK cycle, the frame buffer display or drawing address is output. During the second 2CLK cycle, the frame buffer data is read (display cycles and/or drawing cycles) or written (drawing cycles).

In this mode, display and drawing cycles contend for access to the frame buffer. The ACRTC allows the priority to be defined as display priority or drawing priority. If display priority, drawing cycles are only allowed to occur during vertical retrace. So, a 'flashless' display is obtained at the expense of slower drawing. If drawing priority, drawing may occur during display so high speed drawing is obtained, however the display may flash.

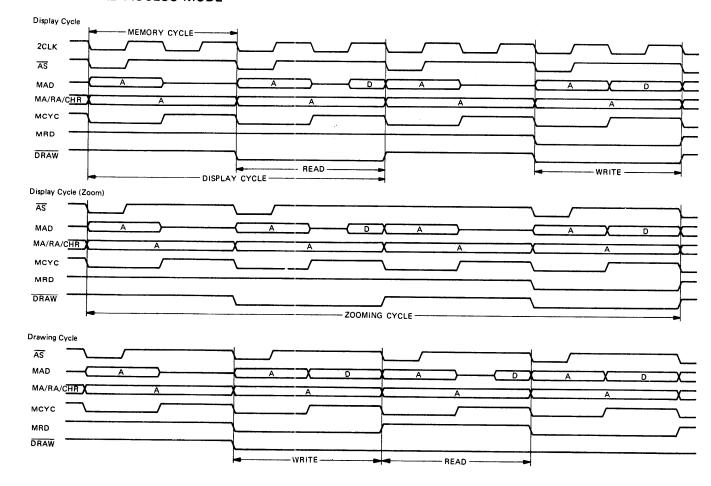

#### (b) Interleaved Access Mode (Dual Access Mode 0)

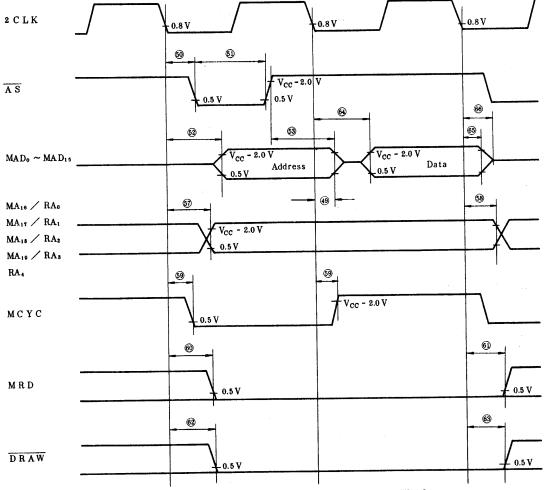

In this mode, display cycles and drawing cycles are interleaved. A display/drawing cycle is defined as four cycles of 2CLK. During the first 2CLK cycle, the frame buffer display address is output. During the second 2CLK cycle, the display data is read from the frame buffer. During the third 2CLK cycle, the frame buffer drawing address is output. During the fourth 2CLK cycle, the drawing data is read or written.

Since there is no contention between display and drawing cycles, a 'flashless' display is obtained while maintaining full drawing speed. However, for a given configuration, frame buffer memory access time must be twice as fast as an equivalent Single Access Mode configuration.

(c) Superimposed Access Mode (Dual Access Mode 1)

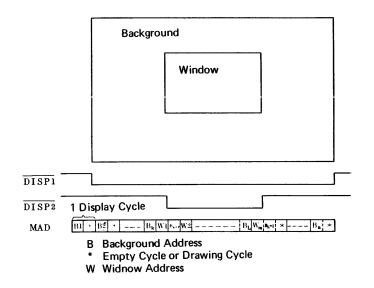

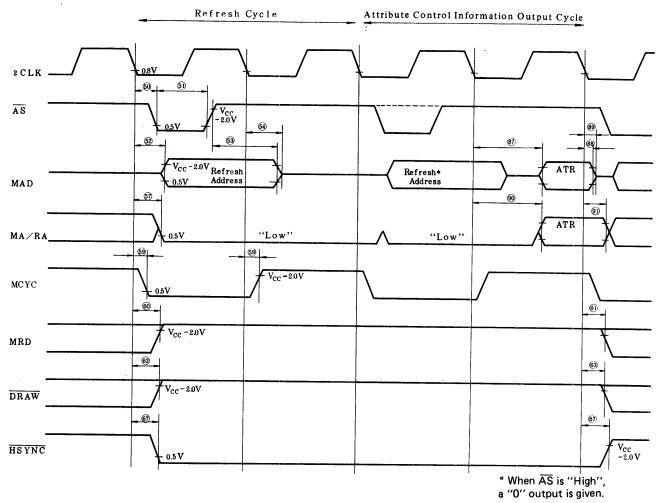

In this mode, two separate logical screens are accessed during each display cycle. The display cycle is defined as four 2CLK cycles. During the first 2CLK cycle, the Background (Upper, Base or Lower) screen frame buffer address is output. During the second 2CLK cycle, the Background screen display or drawing data is read (display or drawing) or written (drawing). During the third 2CLK cycle, the window screen frame buffer address is output. During the fourth 2CLK cycle, the window screen display or drawing data is read (display or drawing) or written (drawing). Note that the third and fourth cycles can be used for Background screen drawing (similar to Interleaved mode) when these cycles are not used for Window display.

#### SA (SINGLE ACCESS MODE)

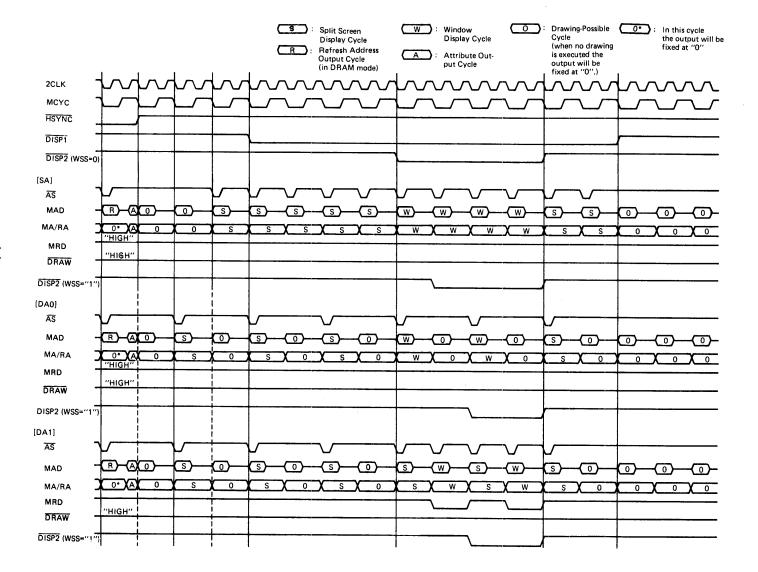

Figure 2.1(b) Access Mode Timing

#### INTERLEAVED ACCESS MODE

Figure 2.1(d) Access Mode Timing

# Figure 2.1(c) Access Mode Timing

SUPERIMPOSED ACCESS MODE

#### Display Cycle MEMORY CYCLE-2CLK ĀS MAD MA/RA/CHR MCYC MRD 'HIGH' DRAW WINDOW BACK GROUND - DISPLAY CYCLE Display Cycle (Zoom) AS MAD MA/RA/CHR MCYC MRD DRAW ZOOMING CYCLE x 2 **Drawing Cycle** ĀŜ MAD MA/RA/CHR MCYC MRD DRAW WRITE -READ

#### 2.2.1.2 Graphic Address Increment Mode

During display operation, the ACRTC can be programmed to control the graphic display address in six ways including increment by 1, 2, 4 and 8 words, 1 word every two display cycles and no increment.

Setting GAI to increment by 2, 4 or 8 words per display cycle achieves linear increases in the video data rate i.e. for a given configuration setting GAI to 2, 4 or 8 words will achieve 2, 4 or 8 times the video data rate corresponding to GAI=1. This allows increasing the number of bits/logical pixel and logical pixel resolution while meeting the 2CLK maximum frequency constraint.

Figure 2.2 shows the summary relationship between 2CLK, Display Access Mode, Graphic Address Increment, # bits/logical pixel, memory access time and video data rate. The frame buffer cycle frequency (Fc) is shown by the following equation where:

Fv = Dot Clock

N = # bits/logical pixel

D = Display Access Mode

1 for Single Access Mode

2 for interleaved and Superimposed Access Modes

A = Graphic Address Increment (1/2, 1, 2, 4, 8)

$Fc = (Fv \times N \times D)/(A \times 16)$

| Dot Rate                 |              | 16    | ИHz   | 32MHz |    | 64MHz |    | 128MHz |    |

|--------------------------|--------------|-------|-------|-------|----|-------|----|--------|----|

| Acces                    | ss Mode      |       |       |       |    |       |    |        |    |

| Color No.<br>(bit/pixel) | Memory Cycle | S     | D     | s     | D  | S     | D  | s      | D  |

| 1                        | 250ns        | -     | + 1/2 | +1/2  | +1 | +1    | +2 | +2     | +4 |

| •                        | 500ns        | + 1/2 | +1    | +1    | +2 | +2    | +4 | +4     | +8 |

| 2                        | 250ns        | +1/2  | +1    | +1    | +2 | +2    | +4 | +4     | +8 |

|                          | 500ns        | +1    | +2    | +2    | +4 | +4    | +8 | +8     | _  |

| 4                        | 250ns        | +1    | +2    | +2    | +4 | +4    | +8 | +8     | _  |

| <del>-</del>             | 500ns        | +2    | +4    | +4    | +8 | +8    | _  | _      | _  |

| 8                        | 250ns        | +2    | +4    | +4    | +8 | +8    | _  | _      |    |

| <u> </u>                 | 500ns        | +4    | +8    | +8    | _  | _     | _  | _      | _  |

| 16                       | 250ns        | +4    | +8    | +8    | _  | _     | _  |        | _  |

|                          | 500ns        | +8    | _     | _     | _  | -     | _  | _      | _  |

Figure 2.2 Graphic Address Increment Modes

#### 2.2.2 Dynamic RAM Refresh

When dynamic RAMs (DRAMs) are used for the frame buffer memory, the ACRTC can automatically provide DRAM refresh addressing.

The ACRTC maintains an 8 bit  $\overline{DRAM}$  refresh counter which is decremented on each frame buffer access. During  $\overline{HSYNC}$  low, the ACRTC will output the sequential refresh addresses on MAD. The refresh address assignment depends on Graphic Address Increment (GAI) mode as shown in figure 2.3(a).

| Address Increment Mode | Refresh Address Output Terminal |

|------------------------|---------------------------------|

| +1 (GAI=000)           | MAD0-7                          |

| +2 (GAI=001)           | MAD1-8                          |

| +4 (GAI=010)           | MAD2-9                          |

| +8 (GAI=011)           | MAD3-10                         |

| + 1/2 (GAI= 111)       | MAD0 – 7                        |

Figure 2.3(a) GAI and DRAM Refresh Addressing

The ACRTC provides "0" output on the remaining address line of MAD and MA/RA.

DRAM refresh cycle timing must be factored into the determination of  $\overline{\text{HSYNC}}$  low pulse width (HSW – specified in units of frame buffer memory cycles).

If the horizontal scan rate is Fh (kHz), number of DRAM refresh cycles is N and the DRAM refresh cycle time is Tr (msec) then horizontal sync width (HSW) is specified by the following equation:

$$HSW \ge N / (Tr \times Fh)$$

For example, if the scan rate is 15.75 kHz and the DRAMS have 128 refresh cycles of 2 msec, HSW must be greater than or equal to 5.

$$HSW \ge 128 / (2 \times 15.75) = 4.06$$

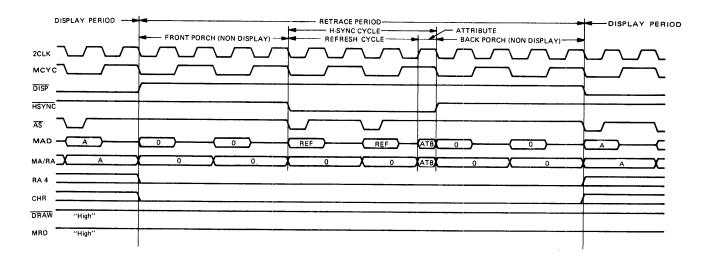

Figure 2.3(b) DRAM Refresh Timing

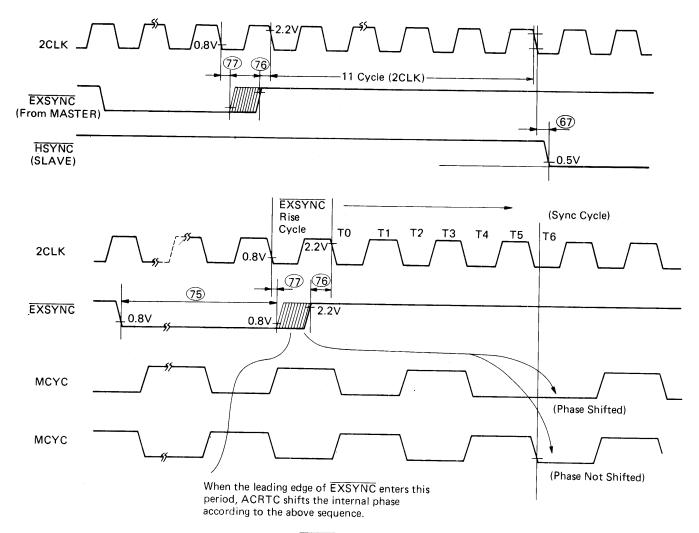

# 2.2.3 External Synchronization

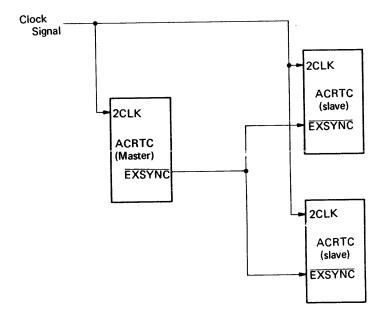

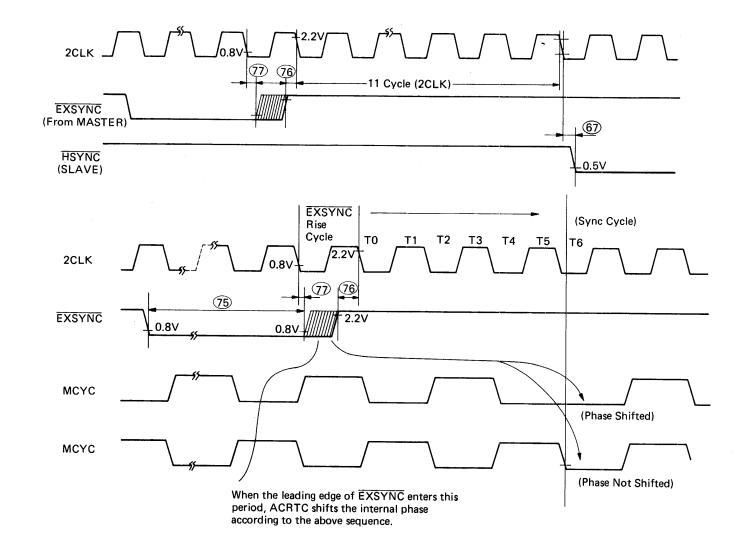

The ACRTC EXSYNC pin allows synchronization of multiple ACRTCs or other video signal generators. The ACRTC may be programmed as a single Master device, or as one of a number of Slave devices.

To synchronize multiple ACRTCs, simply connect all the  $\overline{\text{EXSYNC}}$  pins together.

For synchronizing to other video signals, the connection scheme depends on the raster scan mode. In Non-Interlace mode,  $\overline{EXSYNC}$  corresponds to  $\overline{VSYNC}$ . In Interlace modes,  $\overline{EXSYNC}$  corresponds to  $\overline{VSYNC}$  of the odd field.

Figure 2.4(a) External Synchronization

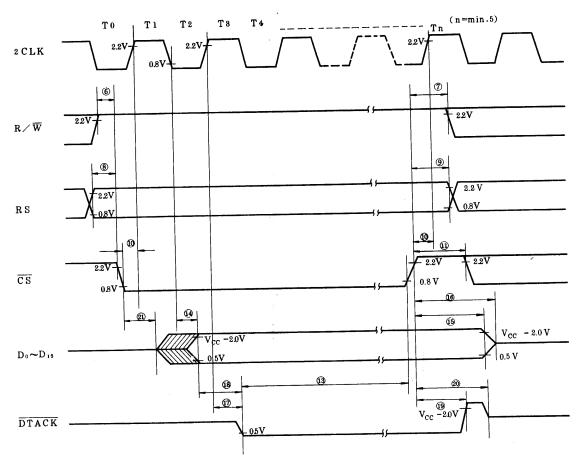

# 2.3 MPU Interface

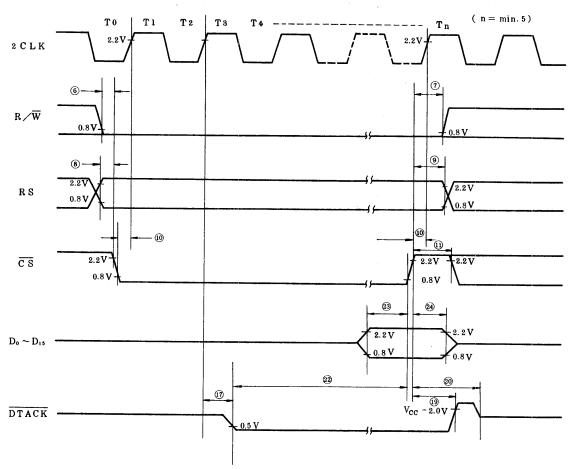

# 2.3.1 MPU Bus Cycle

The ACRTC interfaces to the MPU as a peripheral occupying two addresses in the MPU address space. The ACRTC can operate as an 8 or 16 bit peripheral as configured during RES.

An MPU bus cycle is initiated when  $\overline{CS}$  is asserted (following the assertion of RS and R/ $\overline{W}$ ). The ACRTC responds to  $\overline{CS}$  low by asserting  $\overline{DTACK}$  low to complete the data transfer. DTACK will be returned to the MPU in between 1 and 1.5 2CLK cycles.

MPU WAIT states will be added in the following two cases.

- (a) If the ACRTC 2CLK input is much slower than the MPU clock, continuous ACRTC accesses may be delayed due to internal processing of the previous bus cvcle.

- (b) If an ACRTC read cycle immediately follows an ACRTC write cycle, a WAIT state may occur due to ACRTC preparation for bus 'turn-around'. However, MPUs normally have no instructions which immediately follow a write cycle with a read cycle.

For connection to synchronous bus interface MPUs, DTACK can simply be left open assuming the system design guarantees that WAIT states cannot occur as described above. If WAIT states may occur, DTACK can be used with external logic to synthesize a READY signal.

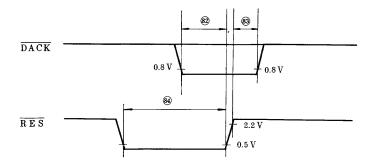

# 2.3.2 DMA Transfer

The ACRTC can interface with an external DMA controller using three handshake signals, DMA Request (DREQ), DMA Acknowledge (DACK) and DMA Done (DONE).

The ACRTC uses the external DMAC for two types of transfers, Command/ Parameter DMA and Data DMA. For both types, DMA transfers use the ACRTC read and write FIFOs.

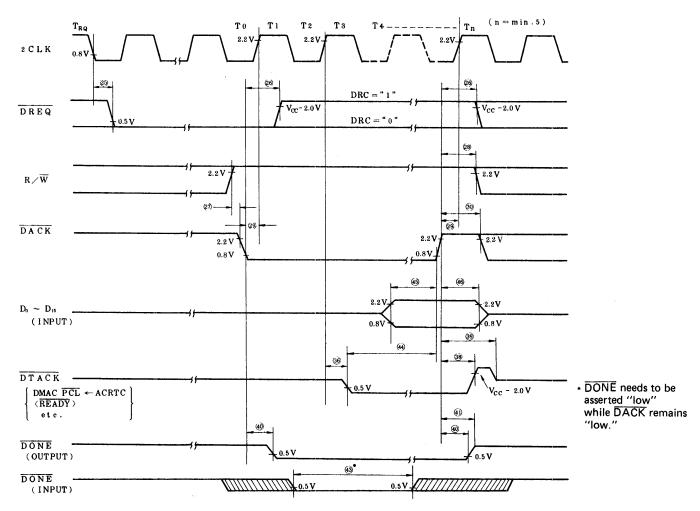

# 2.3.2.1 Command/Parameter DMA

The MPU initiates this mode by setting bit 12 (CDM) in the ACRTC Command Control Register to 1. Then, the ACRTC will automatically request DMA transfer for commands and their associated parameters as long the write FIFO has space. Only cycle steal request mode (DREQ pulses low for each data transfer) can be used. Command/Parameter DMA is terminated when the MPU resets bit 12 in CCR to 0 or the external  $\overline{DONE}$  input is asserted.

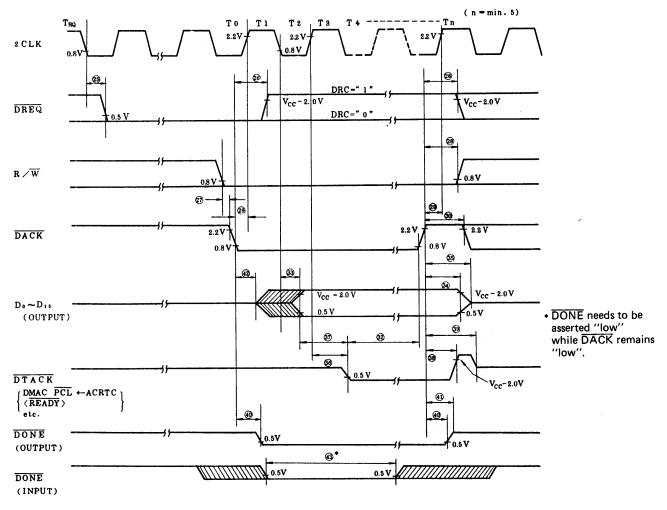

#### 2.3.2.2 Data DMA

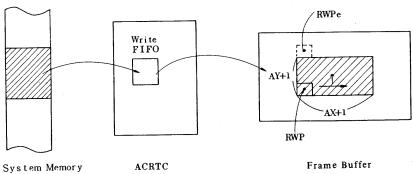

Data DMA is used to move data between the MPU system memory and the ACRTC frame buffer.

The MPU sets-up the transfer by specifying the frame buffer transfer address (and other parameters of the transfer, such as 'on-the fly' logical operations) to the ACRTC. Next, when the MPU issues a Data Transfer Command to the ACRTC, the ACRTC will request DMA transfer to and from system memory. The ACRTC will request DMA, automatically monitoring FIFO status, until the DMA Transfer Command is completed.

Data DMA request mode can be cycle steal (as in Command/Parameter DMA) or burst mode in which  $\overline{DREQ}$  is a low level control output to the DMAC which allows multiple data transfers during each acquisition of the MPU bus.

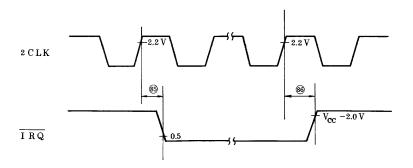

#### 2.3.3 Interrupts

The ACRTC recognizes eight separate conditions which can generate an interrupt including command error detection, command end, drawing edge detection, light pen strobe and four FIFO status conditions. Each condition has an associated mask bit for enabling/disabling the associated interrupt. The ACRTC removes the interrupt request when the MPU performs appropriate interrupt service by reading or writing to the ACRTC.

#### 3. DISPLAY FUNCTION

#### 3.1 Logical Display Screens

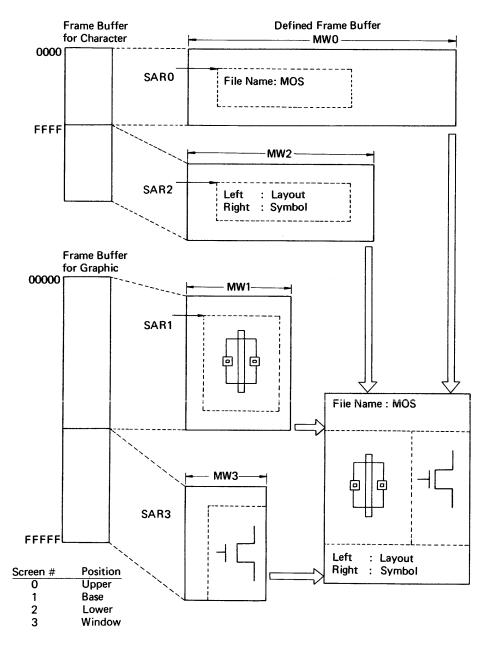

The ACRTC allows division of the frame buffer into four separate logical screens.

| Screen Number | Screen Name   | Screen Group Name    |

|---------------|---------------|----------------------|

| 0             | Upper Screen  |                      |

| 1             | Base Screen   | —Background Screens  |

| 2             | Lower Screen_ | - background screens |

| 3             | Window Screen |                      |

In the simplest case, only the Base screen parameters must be defined. Other screens may be selectively enabled, disabled and blanked under software control.

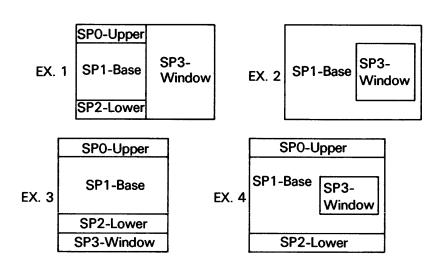

The Background (Upper, Base and Lower) screens partition the display into three horizontal splits whose position is fully programmable. A typical application might use the Base screen for the bulk of user interaction, using the Lower screen for a 'status line(s)' and the Upper screen for 'pull-down menu(s)'.

The Window screen is unique, since the ACRTC gives the Window screen higher priority than Background screens. thus, when the Window, whose size and position is fully programmable, overlaps a Background screen, the Window screen is displayed. One exception is the ACRTC Superimposed Access Mode, in which the Window has the same display priority as Background screens. In this case, the Window and Background screen are 'superimposed' on the display.

The ACRTC logical screen organization can be programmed to best suit a number of display applications.

Figure 3.1 Display Screen/Frame Buffer Relationship

Figure 3.2 Display Screen Combination

Figure 3.3 Display Screen Specification

Figure 3.4 Display Screen Timing

Figure 3.5 Example Screen Combinations

# 3.1.1 Graphic/Character Address Spaces

The ACRTC controls two separate logical address spaces. The CHR pin allows external decoding if physically separate frame buffers are desired.

Each of the four logical screens (Upper, Base, Lower and Window) is programmed as residing in the Graphics address space or the Character address space.

ACRTC accesses to Graphics screens are treated as bit mapped using a 20 bit frame buffer address, with an address space of one megaword (1M by 16 bit).

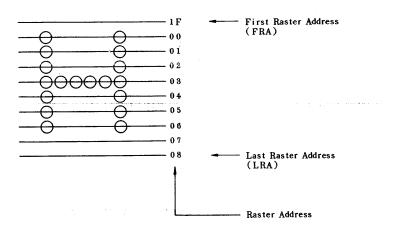

ACRTC accesses to Character screens are treated as character generator mapped. In this case, a 64K word address space is used and 5 bits of raster address are output to an external character generator.

Multiple logical screens defined as Character can be externally decoded to use separate character generators or different addresses within a combined character generator. Also, each Character screen may be defined with separate line spacing, separate cursors, etc.

Figure 3.6 Character Screen Raster Addressing

#### 3.2 Cursor Control

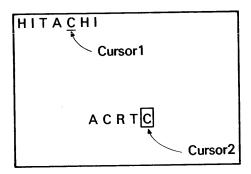

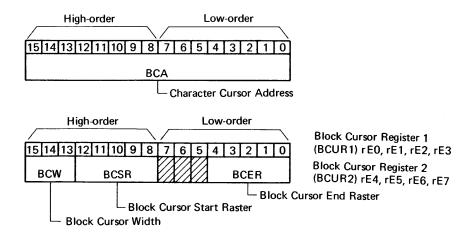

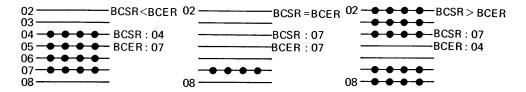

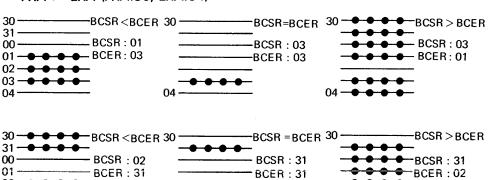

The ACRTC has two Block Cursor Registers and a Graphics Cursor Register.

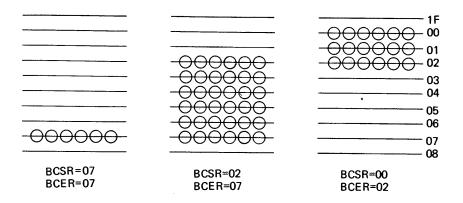

A Block cursor is used with Character screens. The cursor start and ending raster addresses are fully programmable. Also, the cursor width can be defined as one to eight memory cycles.

A Graphics cursor is defined by specifying the start and end addresses in both the X and Y dimensions.

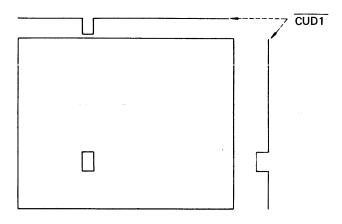

Figure 3.7(a) Two Separate Block Cursors

Figure 3.7(b) Block Cursor Examples

Figure 3.8 Graphic Cursor

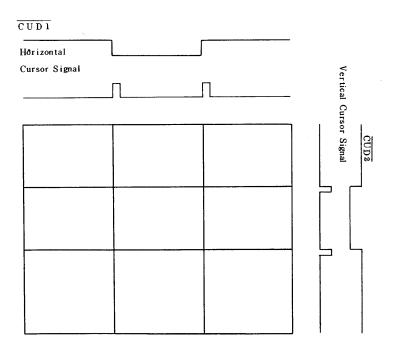

The ACRTC provides two separate cursor outputs,  $\overline{\text{CUD1}}$  and  $\overline{\text{CUD2}}$ . These are combined with two character cursor registers and a graphics cursor register to provide three cursor modes.

# 3.2.1 Block Mode

Two Block cursors are output on  $\overline{\text{CUD1}}$  and  $\overline{\text{CUD2}}$  respectively.

#### 3.2.2 Graphic Mode

The Graphic cursor is output on  $\overline{CUD1}$ . Using an external cursor pattern memory allows a graphic cursor of various shapes. Two Block cursors are multiplexed on  $\overline{CUD2}$ .

#### 3.2.3 Crosshair Mode

The horizontal and vertical components of the Graphic cursor are output on  $\overline{\text{CUD1}}$  and  $\overline{\text{CUD2}}$  respectively. This allows simple generation of a crosshair cursor control signal.

Figure 3.9 Crosshair Cursor

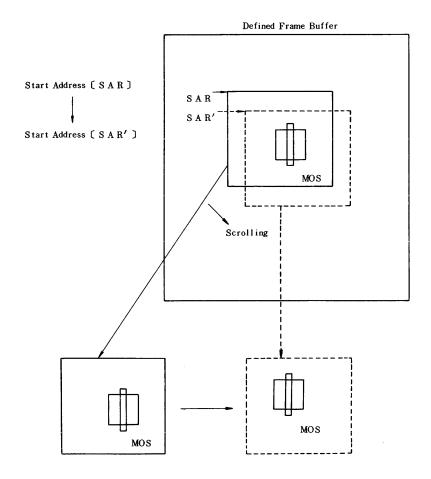

#### 3.3 Scrolling

#### 3.3.1 Vertical Scroll

Each logical screen performs independent vertical scroll. On Character Screens, vertical smooth scroll is accomplished using the programmable Start Raster Address (SRA). Line by line scroll is accomplished by increasing or decreasing the screen start address by one unit of horizontal memory width.

On Graphics screens, vertical smooth scroll is accomplished by increasing or decreasing the screen start address by one unit of horizontal memory width.

#### 3.3.2 Horizontal Scroll

Horizontal scroll can be performed in units of characters for Character screens and units of words (multi logical pixels) for Graphic screens by increasing or decreasing the screen start address by 1.

For smooth horizontal scroll, the ACRTC has dot shift video attributes which can be used with an external circuit which conditions shift register load/clocking.

Since this dot shift information is output each raster, horizontal smooth scroll is limited to either the Background screens or the Window screen at any given time. However, horizontal smooth scroll is independent for each of the Background screens (Upper, Base, Lower).

Figure 3.10 Scrolling By SAR (Start Address Register) Rewrite

Figure 3.11 Horizontal Smooth Scroll - Base Screen

Figure 3.12 Horizontal Smooth Scroll — Window Screen

#### 3.4 Raster Scan Modes

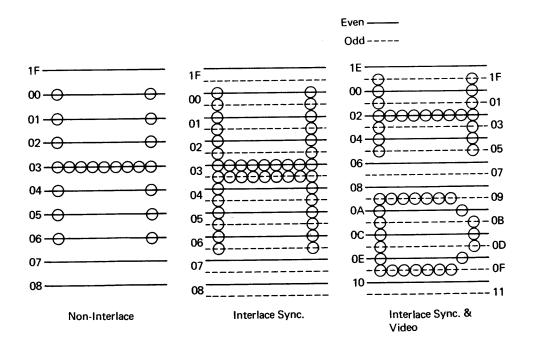

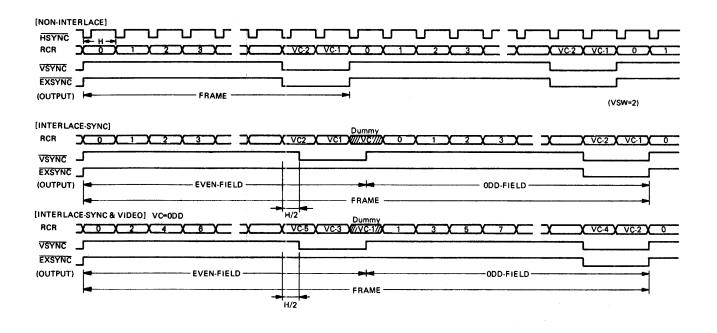

The ACRTC has three software selectable raster scan modes — Non-Interlace, Interlace Sync and Interlace Sync & Video. In Non-Interlace mode a frame consists of one field. In the Interlace modes, a frame consists of two fields, the even and odd fields.

The Interlace modes allow increasing screen resolution while avoiding limits imposed by the CRT display device, such as maximum horizontal scan frequency or maximum video dot rate.

Interlace Sync mode simply repeats each raster address for both the even and odd fields. This is useful for increasing the quality of a displayed figure when using an interlaced CRT device such as a Television Set with RF modulator.

Interlace Sync & Video mode displays alternate even and odd rasters on alternate even and odd fields. For a given number of rasters/character, this mode allows twice as many characters to be displayed in the vertical direction as Non-Interlace mode.

Note that for Interlace modes, the refresh frequency for a given dot on the screen is one-half that of the Non-Interlace mode. Interlace modes normally require the use of a CRT with a more persistent phosphor to avoid a flickering display.

Figure 3.13 Raster Scan Modes

#### 3.5 Zooming

The Base screen (Screen 1) is supported by the ACRTC zooming function. Note that ACRTC zooming is performed by controlling the CRT timing signals. The contents of the frame buffer area being zoomed are not changed.

The ACRTC allows specification of a zoom factor (1 to 16) independently in the X and Y directions.

For horizontal zoom, the programmed zoom factor is output as video attributes. An external circuit uses this factor to condition the external shift register clock to accomplish horizontal zooming.

For vertical zoom, no external circuit is required. The ACRTC will scan a single raster multiple times to accomplish vertical zooming.

Figure 3.15 Zooming

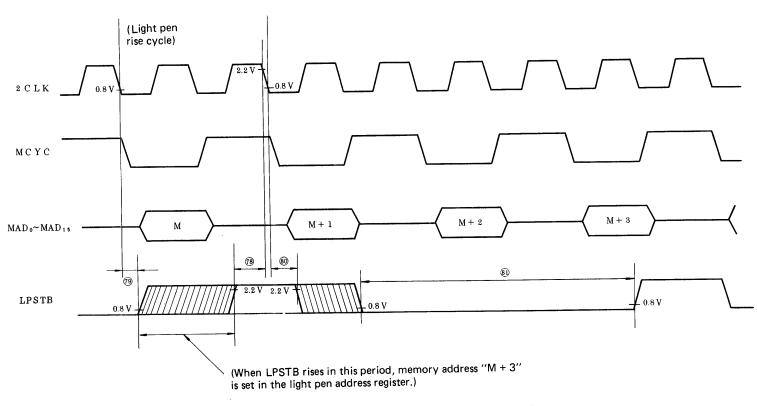

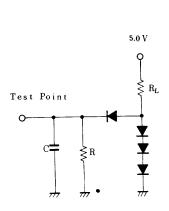

#### 3.6 Light Pen

The ACRTC provides a 20 bit Light Pen Address Register and a Light Pen Strobe (LPSTB) input pin for connection with a light pen.

A light pen strobe pulse will occur when the CRT electron beam passes under the light pen during display refresh. When this pulse occurs, the contents of the ACRTC display refresh address counter will be latched into the Light Pen Address Register along with a logical screen (Character or Graphic screen) designator. Also, an ACRTC status flag indicating light pen activity is set, generating an optional (maskable) MPU interrupt. Note that for Superimposed access mode, when the light pen strobe occurs in an area in which the Window overlaps a Background (Upper, Base or Lower) screen, the Background screen address will be latched.

Various system and ACRTC delays will cause the latched address to differ slightly from the actual light pen position. the light pen address can be corrected using software, based upon system specific delays. Or, if the application does not require the highest light pen pointing resolution, software can 'bound' the light pen address by specifying a range of values associated with a given area of the screen.

# 4. SIGNAL DESCRIPTION

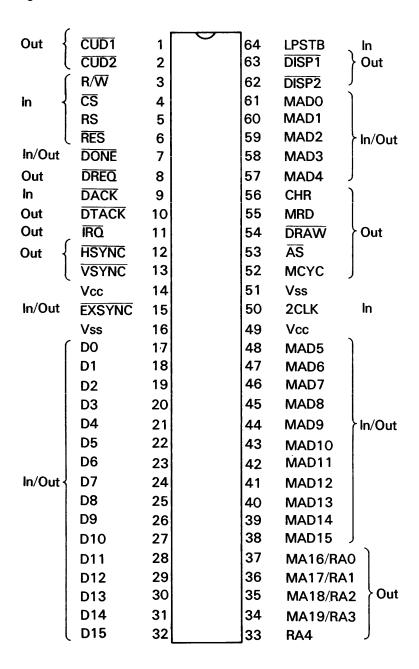

# 4.1 Pin Arrangement

Figure 4.1 Pin Arrangement

#### 4.2 Signal Functions

The ACRTC signal functions are grouped into 4 functional categories, MPU Interface, DMAC Interface, CRT Interface and Power Supply. All signals are TTL compatible.

#### 4.2.1 MPU Interface

# 4.2.1.1 Reset (RES:INPUT)

A low level on the  $\overline{RES}$  input forces the ACRTC into the following state.

- (a) Drawing and Display operation is stopped.

- (b) ACRTC registers are initialized as follows.

Status register (SR) - CED, WFR and WFE bits are set to 1, all other bits reset to 0.

Command Control Register (CCR) - The ABT bit is set to 1. All other bits are reset to 0.

Operation Mode Register (OMR) - The M/S and STR bits are reset to 0. All other bits are unaffected.

All other ACRTC registers are unaffected by RES.

(c) The DRAM refresh address is placed on the MAD lines determined by the graphic address increment (GAI) mode. This remains the case until the start bit (STR) in the Operation Mode Register (OMR) is set to 1. HSYNC is also held low during the period from RES until the start bit in OMR is set to 1 by the host.

# 4.2.1.2 Bi-directional Host System Data Bus (DO-D15:INPUT/OUTPUT:3-STATE)

These lines are used for data transfer between the ACRTC and the host system data bus (MPU and/or DMAC). D0-D15 outputs are three state buffers and remain in the high impedance state except during host reads of ACRTC registers.

During reset, depending on the state of the DACK input, the ACRTC can be configured for an 8 bit data bus using D0-D7. In this case, D8-D15 should be left open.

#### 4.2.1.3 Read/Write (R/W:INPUT)

R/W controls the direction of transfer between the host system bus and the ACRTC. During non-DMA transfers, when  $R/\overline{W}$  is high, data is transferred from the ACRTC to the host, and when low, data is transferred from the host to the ACRTC.

When the ACRTC executes a DMA transfer using an external DMAC, the polarity of  $R/\overline{W}$  is reversed. In this case, when  $R/\overline{W}$  is high, data is transferred from the host to the ACRTC, and when low, data is transferred from the ACRTC to the host.

# 4.2.1.4 Chip Select (CS:INPUT)

The Chip Select, when low, enables access of the ACRTC by the host MPU. Note that Chip Select must not be low during DMA transfers ( $\overline{DACK} = low$ ). RS and  $R/\overline{W}$  must be valid when  $\overline{CS}$  is asserted and write data must be valid prior to the trailing (rising) edge of  $\overline{CS}$ .

When the ACRTC host data bus mode is 16 bit data bus, 8 bit data transfers are not allowed.

#### 4.2.1.5 Register Select (RS: INPUT)

RS is used to select ACRTC hardware accessed registers. When RS is low, reads  $(R/\overline{W} = \text{high})$  access the Status register and writes  $(R/\overline{W} = \text{low})$  access the Address register. When RS is high, reads and writes access the particular ACRTC Control register with address defined in the previous write to the Address register. If the accessed register is in the range of r80 - rFF, the address register will automatically be incremented to allow access to the next sequential register address. This allows high speed initialization of registers in the address range of r80 - rFF without requiring the MPU to reload the address register for each sequential access. Note that the address increment is 1 for 8 bit host interface mode and 2 for 16 bit host interface mode.

Normally, RS is connected to the least significant bit of the MPU address bus.

# 4.2.1.6 Data Transfer Acknowledge (DTACK:OUTPUT:OPEN DRAIN)

The ACRTC will drive  $\overline{DTACK}$  low to indicate completion of a data transfer cycle.  $\overline{DTACK}$  is compatible with asynchronous bus interface hosts including the HD68000 MPU and HD68450 DMAC.

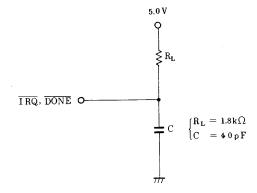

# 4.2.1.7 Interrupt Request (IRQ:OUTPUT:OPEN DRAIN)

This open drain output is driven low when the ACRTC requires interrupt service. In order to generate an  $\overline{IRQ}$ , the interrupting condition must be enabled in the Command Control Register (CCR).

The action required to clear the interrupting condition is specified in the Status Register description (section 5.3).

#### 4.2.2 DMAC Interface

Three DMA handshaking lines allow the ACRTC to use an external DMA controller. The DMA protocol is directly compatible with HD68450 DMAC single address mode transfers.

#### 4.2.2.1 DMA Request (DREQ:OUTPUT)

During DMA transfer mode,  $\overline{DREQ}$  is used to request data transfer service from the host bus DMAC.  $\overline{DREQ}$  is asserted to active low level by ACRTC execution of a Data DMA transfer command (when the Data DMA Mode bit (DDM) in CCR is set to 1) or by setting the Command/Parameter DMA transfer mode bit (CDM) in the CCR to 1. Data DMA can be programmed as burst or cycle steal, while Command/Parameter DMA can only be burst mode.

# 4.2.2.2 DMA Acknowledge (DACK:INPUT)

$\overline{DACK}$  is an answer back signal from the DMAC to which  $\overline{DREQ}$  has been issued and indicates that the host bus has been acquired, and data transfer can occur. Note that when  $\overline{DACK}$  is asserted low,  $\overline{CS}$  must not be low and the R/ $\overline{W}$  signal polarity is reversed.

RS and R/ $\overline{W}$  must be valid prior to  $\overline{DACK}$  assertion and data written to the ACRTC must be valid prior to the trailing (rising) edge of  $\overline{DACK}$ .

$\overline{DACK}$  is also used to define whether an 8 or 16 bit host data bus is used. During reset, if  $\overline{DACK}$  is low, 8 bit mode is used and if  $\overline{DACK}$  is high, 16 bit mode is used. In the case of 8 bit mode, host-ACRTC communication occurs on the D0-D7 portion of the data bus, white D8-D15 are disabled and driven high. When 8 bit bus mode is selected the automatic increment mode for the Address Register is set to '+1' (alternating even and odd register addresses), while 16 bit bus mode sets it to '+2' (even addresses only).

When 16 bit host data bus mode is used, 8 bit transfers are not allowed. When DMA is not used, DACK should be pulled up to a high level.

#### 4.2.2.3 Done (DONE:INPUT/OUTPUT:OPEN DRAIN)

DONE is used to terminate DMA transfers. During Data DMA transfers, DONE is an output and when asserted low indicates DMA termination to the external DMAC. During Command/Parameter DMA transfers, DONE is an input asserted low by the external DMAC to terminate DMA. Note that Data DMA cannot be terminated by externally forcing DONE low.

DONE is open drain when in the output state, and should be pulled up to high level when not used.

#### 4.2.3 CRT Interface

#### 4.2.3.1 Clock (2CLK:INPUT)

This is the basic operating clock for the ACRTC which is derived from the external dot clock. The ACRTC internally divides 2CLK by 2 to generate the MCYC Memory Cycle Clock. Thus, 2CLK is twice the frequency of the frame buffer memory access timing. 2CLK must be a continuous clock input.

#### 4.2.3.2 Vertical Synchronization (VSYNC:OUTPUT)

VSYNC is used to output the active low Vertical Synchronization timing signal required by the CRT display device.

# 4.2.3.3 Horizontal Synchronization (HSYNC:OUTPUT)

HSYNC is used to output the active low Horizontal Synchronization timing signal required by the CRT display device.

HSYNC is also used when the ACRTC performs DRAM refresh addressing of the frame buffer. In the case that the STR start bit or the RAM bit in the Operation Mode Register (OMR) are set to 0, HSYNC asserted low indicates that the DRAM refresh addresses are present on MAD frame buffer address/data bus.

# 4.2.3.4 External Synchronization (EXSYNC:INPUT/OUTPUT)

EXSYNC is an active low input and output signal used for synchronizing multiple ACRTCs or synchronizing the ACRTC with other video generating devices. The ACRTC is programmed as a master or slave by the state of the M/S bit in the Operation Mode Register (OMR). When the ACRTC is master, EXSYNC is an output which may be used to drive a slave video generating devices VSYNC input or a slave ACRTCs EXSYNC input. When the ACRTC is slave, EXSYNC is an input which receives the masters EXSYNC (master is another ACRTC) or VSYNC (master is another video generating device).

In both master and slave configurations, the timing of  $\overline{EXSYNC}$  depends on the interlace mode. For example, in interlaced modes,  $\overline{EXSYNC}$  timing corresponds to  $\overline{VSYNC}$  of the odd field.

#### 4.2.3.5 Light Pen Strobe (LPSTB:INPUT)

LPSTB input accepts a positive strobe pulse generated by an external light pen. When asserted high, the current frame buffer display refresh address is latched into the Light Pen Address Register and the LPD (Light Pen Detect) bit in the Status Register is set to 1, generating an interrupt if enabled to do so by the MPU. The stored address will be different from the actual address due to the following delays.

- (a) ACRTC address output delay

- (b) Address output to video signal output delay

- (c) Light pen detection to LPSTB delay

- (d) LPSTB to internal recognition delay

The actual address should be calculated by adjusting the stored address considering the above delays. Also note that, for Superimposed access mode, when the light pen strobe occurs in the Window screen, the overlapped Background (Upper, Base, Lower) screen address is latched.

#### 4.2.3.6 Memory Cycle (MCYC:OUTPUT)

MCYC frequency is one-half that of thr ACRTC 2CLK input and is output continuously. MCYC determines frame buffer memory access timing. MCYC low indicates the address portion of the memory access while MCYC high indicates the data portion of the memory access.

#### 4.2.3.7 Address Strobe (AS:OUTPUT)

$\overline{AS}$  output is used to latch the frame buffer address. When  $\overline{AS}$  is low, the MAD outputs contain the frame buffer address.  $\overline{AS}$  is also used to load the external parallel to serial (shift register) converter with the data from frame buffer during the display cycle.

#### 4.2.3.8 Memory Read (MRD:OUTPUT)

During a frame buffer access, MRD indicates the direction of data transfer between the ACRTC and the frame buffer. When MRD is high, a frame buffer read cycle occurs, and when MRD is low, a frame buffer write cycle occurs. In superimposed mode, MRD low indicates the read cycle of window screen data (second phase).

#### 4.2.3.9 Draw (DRAW:OUTPUT)

The  $\overline{DRAW}$  signal differentiates between ACRTC drawing and CRT display refresh cycles. When  $\overline{DRAW}$  is low, the MAD outputs contain multiplexed drawing address and data information. When  $\overline{DRAW}$  is high, the MAD outputs contain a display refresh address during the address portion of the cycle, and are high impedance during the data portion of the cycle.

# 4.2.3.10 Frame Buffer Memory Address/Data (MAD0-MAD15:INPUT/OUTPUT:3-STATE)

MAD0-MAD15 are the time multiplexed, bi-directional frame buffer memory address and data bus. When  $\overline{AS}$  is low, MAD contains the lower 16 bits of the drawing or display address. When  $\overline{AS}$  is high and  $\overline{DRAW}$  is low, MAD transfers the drawing data to and from the frame buffer.

When no frame buffer access is occurring, the MAD bus is 3-stated.

When the RAM bit in the Operation Mode Register (OMR) is set to 0, the 8 bit DRAM refresh address is output on MAD during HSYNC low. The particular bits of MAD used for this 8 bit refresh address depend on the programmed Graphic Address Increment (GAI) mode.

#### 4.2.3.11 Memory Address/Raster Address (MA16/RA0-MA19/RA3:OUTPUT)

These lines output either the 4 most significant bits of the frame buffer address (MA16-MA19) or the 4 least significant bits of the raster address (RA0-RA3). In Character mode (CHR = high), these lines are used as a raster address for connection to an external character generator. In Graphic mode (CHR = low) these lines are used with MAD0-MAD15 to provide a 20 bit linear frame buffer address.

#### 4.2.3.12 Raster Address 4 (RA4:OUTPUT)

In Character mode (CHR = high), RA4 output the most significant bit of the raster address. Thus, 5 bits (RA0-RA4) provide up to 32 rasters per character.

In Graphic mode (CHR = low), the state of this output is undefined.

#### 4.2.3.13 Character (CHR:OUTPUT)

CHR is an output indicating whether the current frame buffer address on MAD has been defined as corresponding to character (CHR = high) or graphic (CHR = low). When high, MAD0-MAD15 contains a 16 bit frame buffer address, while other MAD lines contain raster address information. When low, MAD0-MAD15, MA16-MA19 contains a 20 bit linear frame buffer address. CHR can be used to enable an external character generator. Also, CHR can be used to enable the appropriate memory bank in the case that character and graphic memory are separated.

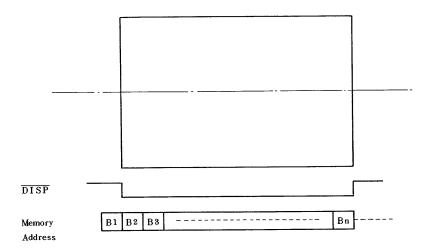

#### 4.2.3.14 Display Timing (DISP1, DISP2: OUTPUT)

These active low outputs indicate the active display period of the screen. They can be used in one of two ways.

- (a) Background screen/window screen display timing signal

- (b) Vertical/horizontal display timing signal

#### 4.2.3.15 Cursor Display (CUD1, CUD2: OUTPUT)

These outputs are externally logically combined with the video signal to produce the cursor display on the screen. Three modes of cursor display are selectable by setting the cursor mode (CM) bits in the Cursor Definition Register (CDR).

| Cursor Mode | Description                                                       | CUD1              | CUD2                |

|-------------|-------------------------------------------------------------------|-------------------|---------------------|

| BLOCK       | The separate display of two BLOCK cursors                         | Block<br>cursor 1 | Block<br>cursor 2   |

| GRAPHIC     | The display of a GRAPHIC cursor and two multiplexed BLOCK cursors | Graphic<br>cursor | Block<br>cursor 1&2 |

| CROSSHAIR   | The X and Y portions of a CROSSHAIR cursor                        | X portion         | Y portion           |

#### 4.2.4 Power Supply

#### 4.2.4.1 Vcc, Vss

These pins supply power to the ACRTC.  $V_{CC}$  is specified as  $5V \pm 10\%$  (4.5 $V\sim5.5V$ ).

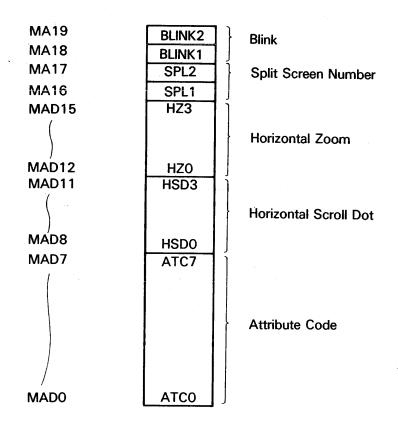

# 4.2.5 Video Attributes

The ACRTC outputs 20 bits of video attributes on MAD0-MAD15 and MA16/RA0-MA19/RA3. These attributes are output at the last cycle prior to the rising edge of HSYNC and should be latched externally. Thus, video attributes can be set on a raster by raster basis.

Figure 4.2 Video Attributes

# 4.2.5.1 Attribute Code (ATCO-ATC7:MADO-MAD7)

These are user defined attributes. The programmed contents of the Attribute Control bits (ATR) of the Display Control Register (DCR) are output on these lines.

# 4.2.5.2 Horizontal Scroll Dot (HSD0-HSD3:MAD8-MAD11)

These are used in conjunction with external circuitry to implement smooth horizontal scroll. These lines contain the encoded start dot address which is used to control the external shift register load timing and data. HSD usually corresponds to the start dot address of the background screens. However, if the window smooth scroll (SWS) bit of OMR (Operation Mode Register) is set to 1, HSD outputs the start dot address of the window screen segment.

# 4.2.5.3 Horizontal Zoom Factor (HZO-HZ3:MAD12-MAD15)

These lines output the encoded (1-16) horizontal zoom factor as stored in the Zoom Factor Register (ZFR). Horizontal zoom is accomplished by the ACRTC repeating a single display address and using the HZ outputs to control the external shift register clock. Horizontal zoom can only be applied to the Base screen.

# 4.2.5.4 Split Position (SPL1-SPL2:MA16-MA17)

These lines present the encoded information showing the enabled background screen currently being displayed by the ACRTC.

| SPL2 | SPL1 |                                            |

|------|------|--------------------------------------------|

| 0    | 0    | Background Screen not enabled or displayed |

| 0    | 1    | Base Screen                                |

| 1    | 0    | Upper Screen                               |

| 1    | 1    | Lower Screen                               |

# 4.2.5.5 Blink (BLINK1-BLINK2:MA18-MA19)

The lines alternate from high to low periodically as defined in the Blink Control Register (BCR). the blink frequency is specified in units of 4 field times. A field is defined as the period between successive  $\overline{VSYNC}$  pulses. These lines are used to implement character and screen blink.

# 5. REGISTER DESCRIPTION

#### 5.1 Internal Register Access

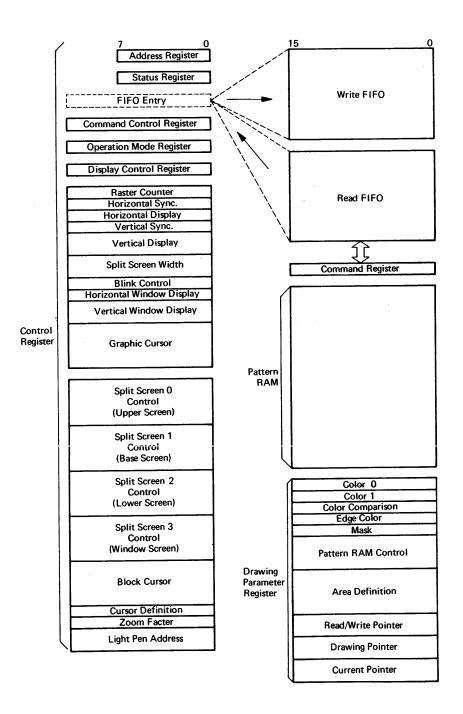

The ACRTC incorporates more than 200 bytes of internal Control registers and Control RAM which are accessible by the host MPU. The programming model is shown in figure 5.1.

For the detailed register descriptions in this section, the following terminology is used.

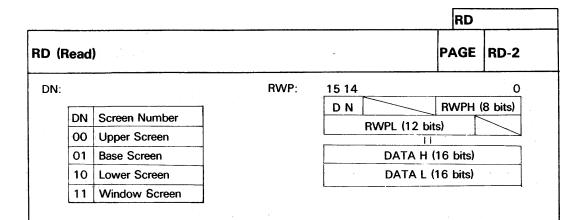

Hexadecimal numbers are denoted by a leading \$ i.e. \$1234, \$FF, etc.

For directly accessible registers, the register address is shown as 'rNN' where NN is interpreted as an 8 bit hexadecimal value. For example, the Zoom Factor Register address is OEA hexadecimal, so ZFRs register address is shown as 'rEA'.

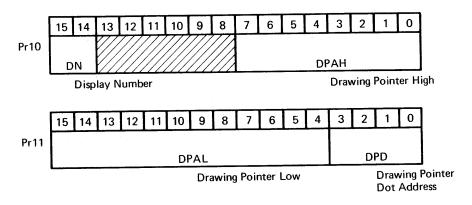

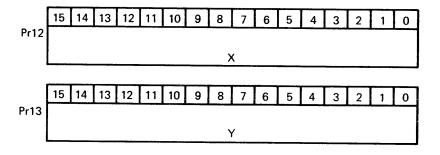

For FIFO accessible Drawing Parameter Registers, the register address is shown as 'PrNN'. For example, the Color Comparison Register is addressed as parameter register 2 hex, so the CMP register address is shown as 'Pr02'.

Bit subfields within the register are denoted using decimal bit numbers in which bit 0 is the least significant bit and bit 15 the most significant bit.

When the register diagram is shown, unused bits will be shaded. Unless stated otherwise, unused bits may be freely written with any value, and that value will be returned on subsequent reads of the register.

Figure 5.1 Programming Model

| 1                                       | ]                                                                  | T                                                                                                                       | Т                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                      |                                                                                                        | Т                                       |      |           |      |                                          |                                                      |                  |                        |                                                  |        |               |             |                                      |                                       |      |     |

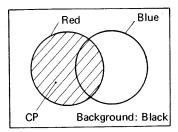

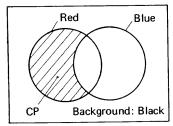

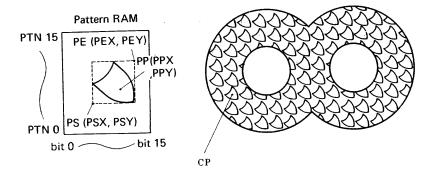

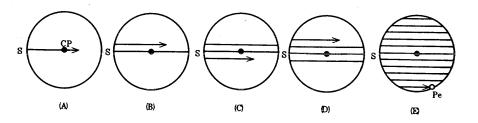

|-----------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------|------|-----------|------|------------------------------------------|------------------------------------------------------|------------------|------------------------|--------------------------------------------------|--------|---------------|-------------|--------------------------------------|---------------------------------------|------|-----|