# Enhanced Super I/O with IrDA Transmission

#### **Features**

- On board Enhanced Super I/O Controller

- · Provide Configurable area for each device on

- Address mapping

- IRQ channel routing

- DMA channel routing

- Support the floppy disk upto 2.88MB

- FDD re-route to Parallel port

- Support 3-mode FDD

- Two high speed serial ports with the IrDA and ASKIr Supporting

- MIDI bit rate supporting on serial port

- Multi-mode parallel port supporting on ECP/EPP/SPP

- IDE/Game port interface decoder output

- Power Management supporting

- 100 PQFP

### **General Description**

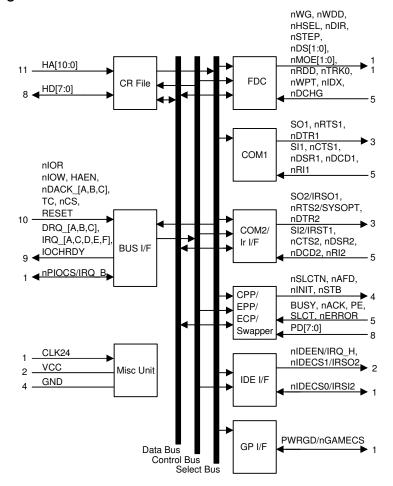

HT8669IR is a high integrated I/O device. It supports a floppy disk controller, a multi-mode printer port, two high speed serial communcation ports, one of which is enriched to support IrDA SIR and ASKIR transmission. By setting the different configuration, HT8669IR can also support IDE and game port interfaces.

There are some configuration register sets to reconfigure the ISA address, IRQ access channel, and DRQ channel for each device in order to support compatible function. The floppy disk controller supports the disk capacity upto 2.88MB with 3-mode floppy disk hardware in-

terface. The disk interface can be re-routed to printer port for some specific applications. In the print port interface, it supports standard mode, PC/AT or PS/2 mode, Enhanced Parallel Port (EPP) 1.7/1.9, or Enhanced Capabilities Port (ECP). For the serial communication interface, there are two high speed ports for serial communication with the MIDI rate supports. One of which is expanded to support IrDA SIR or ASKIR transmission. By using the infrared interface, this device can support wireless communication easily.

# **Block Diagram**

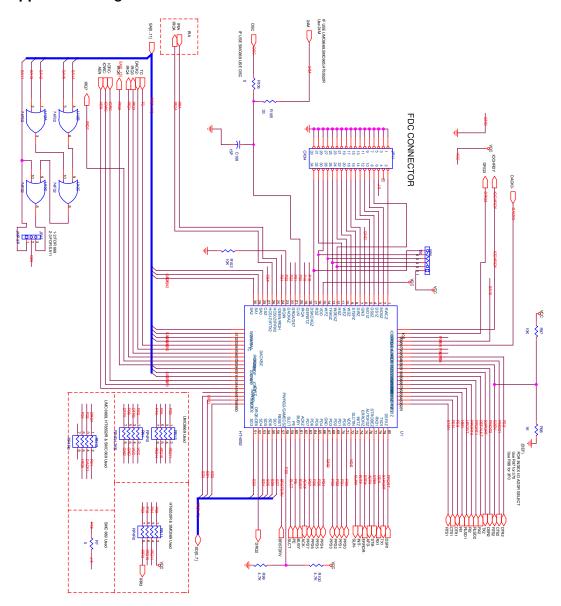

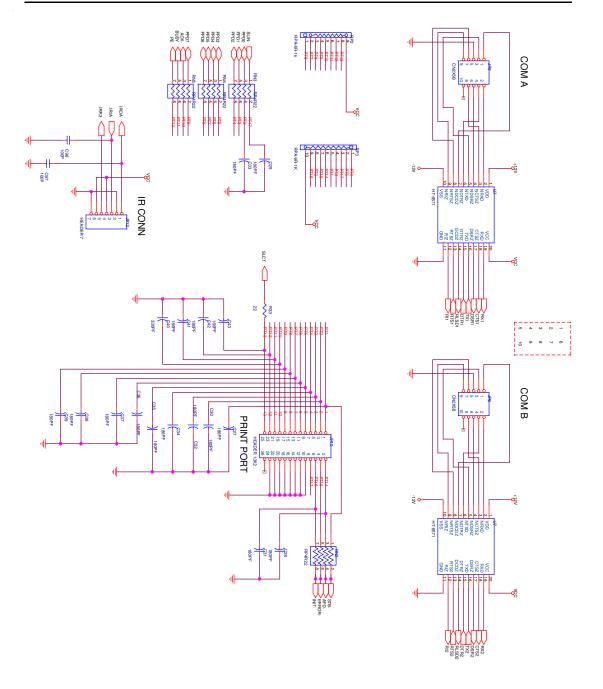

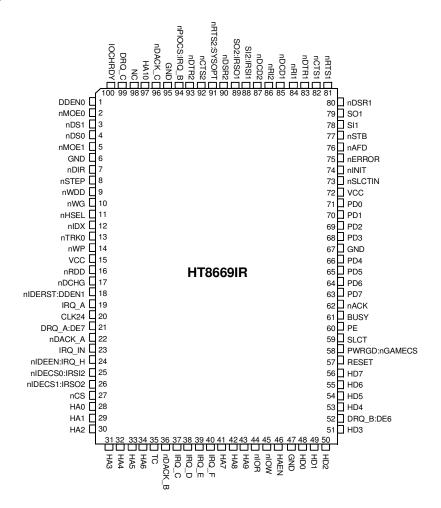

# **Pin Assignment**

# **Pin Description**

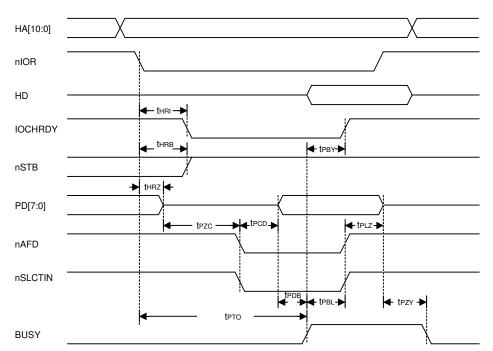

# **Host Interface**

| Pin No.                                | Pin Name                                  | Type                                          | Description                                                                                                                                                                                                                              |  |  |  |

|----------------------------------------|-------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

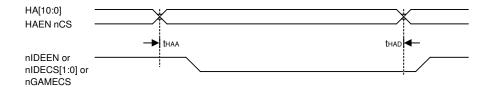

| 97,[43:41],<br>[34:28]                 | HA[10:0]                                  | I                                             | Host I/O Address: For internal decoder use. The contents are latched internally by the leading edge of nIOR or nIOW.                                                                                                                     |  |  |  |

| [56:53],<br>[51:48]                    | HD[7:0]                                   | I/O24                                         | Host I/O Data: For data accesses. These pins are Hi-Z when no output.                                                                                                                                                                    |  |  |  |

| 46                                     | HAEN                                      | I                                             | Host Address Enable: For indicating DMA operation and internal address decode qualification.                                                                                                                                             |  |  |  |

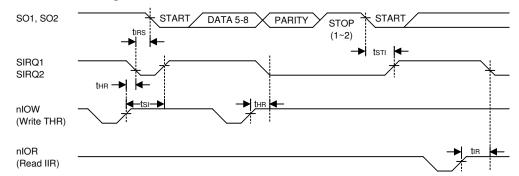

| 44                                     | nIOR                                      | I                                             | I/O Read: For host read operation.                                                                                                                                                                                                       |  |  |  |

| 45                                     | nIOW                                      | I                                             | I/O Write: For host write operation.                                                                                                                                                                                                     |  |  |  |

| 100                                    | IOCHRDY                                   | OD8U                                          | I/O Channel Ready: It is used to extend the host command EPP mode. It is internal pull-up.                                                                                                                                               |  |  |  |

| 22<br>36<br>96                         | nDACK_A<br>nDACK_B<br>nDACK_C             | I<br>I<br>I                                   | DMA Acknowledgement: Host acknowledge the DMA requestor transferring.                                                                                                                                                                    |  |  |  |

| 21<br>52<br>99                         | DRQ_A/<br>DRQ_B/<br>DRQ_C                 | O24ID<br>O24ID<br>O24                         | DMA Request: This pin is used to request host a DMA transferring. It will be cleared on the last data transfer by the nDACK/nIOR being low.                                                                                              |  |  |  |

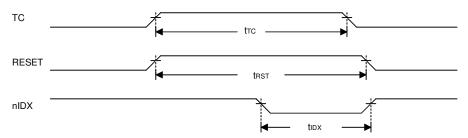

| 35                                     | TC                                        | I                                             | Terminal Count: It indicates the DMA transfer is complete.                                                                                                                                                                               |  |  |  |

| 23                                     | IRQ_IN                                    | I                                             | IRQ Input: An external IRQ input to the chip for IRQ router.                                                                                                                                                                             |  |  |  |

| 19<br>94<br>37<br>38<br>39<br>40<br>24 | IRQ_A IRQ_B IRQ_C IRQ_D IRQ_E IRQ_F IRQ_H | O24<br>O24<br>O24<br>O24<br>O24<br>O24<br>O24 | Interrupt Requests: The IRQ router outputs. Internal subsystems and IRQ_IN are connected to the router for reconfigurable IRQ channels. When EPP or ECP mode is enable, the related IRQ output issues a low pulse for interrupt request. |  |  |  |

| 27                                     | nCS                                       | I                                             | Chip Select: External decoder input for selecting this device.                                                                                                                                                                           |  |  |  |

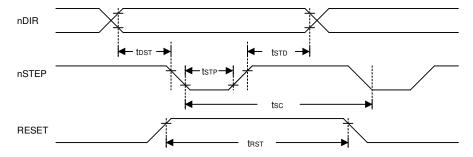

| 57                                     | RESET                                     | IS                                            | System Reset: It is a reset input with a 500ns minimum active pulse for internal egisters reset. The configuration registers are unaffected.                                                                                             |  |  |  |

# FDD

| Pin No. | Pin Name       | Туре         | Description                                                                                                               |

|---------|----------------|--------------|---------------------------------------------------------------------------------------------------------------------------|

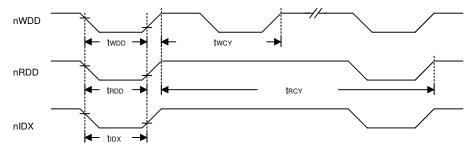

| 16      | nRDD           | IS           | Read Disk Data: Raw serial disk data coming from disk presents a flux transition on each falling edge.                    |

| 9       | nWDD           | OD48         | Write Disk Data: Encoded disk data stream for disk write.                                                                 |

| 10      | nWG            | OD48         | Write Gate: For disk write head operation.                                                                                |

| 17      | nDCHG          | IS           | Disk Changed: Indicate drive door is open.                                                                                |

| 14      | nWP            | IS           | Write Protect: For disk status indication on write protection.                                                            |

| 13      | nTRK0          | IS           | Track 00: For disk status indication on track 0 being sensed.                                                             |

| 12      | nIDX           | IS           | Index Hole: For disk status indication on index hole being sensed.                                                        |

| 11      | nHSEL          | OD48         | Head Select: For disk head selection. A logic "1" means side 0 and a logic "0" means side 1.                              |

| 7       | nDIR           | OD48         | Direction Control: For disk head direction control. A logic "1" means inward motion and a logic "0" means outward motion. |

| 8       | nSTEP          | OD48         | Step Pulse: A pulse sequence output for track-to-track operation.                                                         |

| 3,4     | nDS[1:0]       | OD48         | Drive Selects: For disk driver selection.                                                                                 |

| 5,2     | nMOE[1:0]      | OD48         | Motor On: For disk motor control.                                                                                         |

| 18<br>1 | DDEN1<br>DDEN0 | OD48<br>OD48 | Driver Density(Reduce Write Current): Select drive and media. Refer to CR03, CR0B, and CR1F.                              |

# Serial port

| Pin No.  | Pin Name       | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|----------|----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 78<br>88 | SI1<br>SI2     | I         | Serial Data In: Received serial data input.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 79<br>89 | SO1<br>SO2     | 04        | Serial Data Out: Transmit serial data output.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 81<br>91 | nRTS1<br>nRTS2 | O4<br>OT4 | Request To Send: Handshake output signals notify modem to<br>the UARTn is ready to transmit data. It can be programmed<br>writing to rts.CMn_MCR. It will be reset to inactive mode dur<br>hardware reset or forced to inactive during loop mode operation                                                                                                                                                    |  |  |  |  |  |

| 83<br>93 | nDTR1<br>nDTR2 | 04        | Data Terminal Ready: Handshake output signals no tify modem that the UARTn is ready to setup data communication link. It can be programmed by writing to dtr.CMn_MCR. It will be reset to inactive mode during hardware reset or forced to inactive during loop mode operation.                                                                                                                               |  |  |  |  |  |

| 82<br>92 | nCTS1<br>nCTS2 | I         | Clear To Send: Han dshake input signals notify UARTn that the modem is ready to receive data. An nCTSn signal state change from low to high after the last CMn_MSR read will set dcts.CMn_MSR to "1". If emsi.CMn_IER is set, it will generate an interrupt when nCTSn changes state. The CPU can monitor the status of nCTSn by reading cts. CMn_MSR. The bit is the complement of nCTSn.                    |  |  |  |  |  |

| 80<br>90 | nDSR1<br>nDSR2 | I         | Data Send Ready: Handshake input signals notify UARTn that the modem is ready to setup the data communication link. An nDSRn signal stat change from low to high after the last CMn_MSR read will set ddsr. CMn_MSR to "1". If emsi.CMn_IER is set, it will generate an interrupt when nDSRn changes state. The CPU can monitor the status of nDSRn by reading dsr.CMn_MSR. The bit is the complement onDSRn. |  |  |  |  |  |

| 85<br>87 | nDCD1<br>nDCD2 | I         | Data Carrier Detect: Handshake input signals notify UARTn that carrier signal is detected by the modem. An nDCDn signal state change from low to high after the last CMn_MSR read will set ddcd.CMn_MSR to "1". If emsi.CMn_IER is set, i t will generate an interrupt when nDCDn changes state. The CPU can monitor the status of nDCDn by reading dcd.CMn_MSR. The bit is the complement of nDCDn.          |  |  |  |  |  |

| 84<br>86 | nRI1<br>nRI2   | I         | Ring Indicator: Handshake input signals notify UARTn that the telephone ring signal is d etected by the modem. An nRIn signal state change from low to high after the last CMn_MSR read will set teri.CMn_MSR to "1". If emsi.CMn_IER is set, it will generate an interrupt when nRIn changes state. The CPU can monitor the status of nRIn by reading r i.CMn_MSR. The bit is the complement of nRIn.        |  |  |  |  |  |

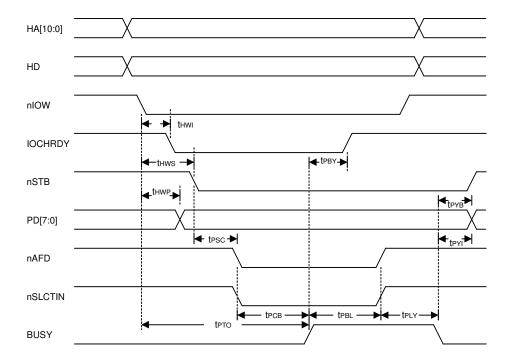

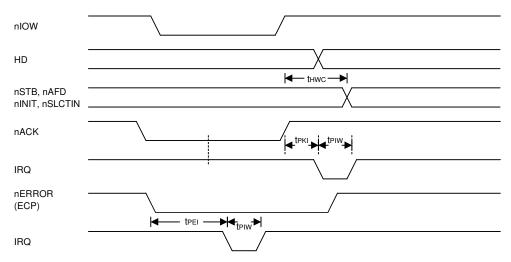

# Parallel port

| Pin No.             | Pin Name | Type  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [63:66],<br>[68:71] | PD[7:0]  | I/O24 | Parallel Port Data I/O: The bi-directional parallel port data for data transfer between HOST and peripherals. It contents either address or data in EPP or ECP mode, the data may i nclude RLE data in ECP mode.                                                                                                                                                                                                                                                                                                  |

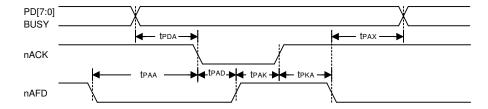

| 61                  | BUSY     | I     | Line Busy: A busy signal from printer to indicate printer is not available to receive the new data. The bit nbusy. SPP_SPR is the complement of this input.  nWAIT(Wait): In EPP mode, it is active low to indicate the device is ready for the next transfer.  BUSY/nPACK(Line Busy/Peripheral Acknowledge): In ECP mode, it is inactive low to indicate the peripheral is ready for the next transfer in the forward direction. It indicates the the data line is ECP command or data in the reverse direction. |

| 62                  | nACK     | I     | Acknowledgment: A acknowledge signal from printer to indicate printer has received data and is ready to accept a new data. The bit nack. SPP_SPR directly reflects this signal. INTR(Interrupt): In EPP mode, it is active high with the positive edge triggered for the interrupt signal. nPACK(Peripheral Acknowledgment): In ECP mode, it is active low to indicate valid data being driven by peripheral.                                                                                                     |

| 60                  | PE       | I     | Paper End: A status signal from printer to indicate the printer is out of paper. The bit pe.SPP_SPR directly reflects this signal. (Same definition as SPP in EPP mode) PERROR/nACKR(PError/nAckReverse): In ECP mode, peripheral uses it to acknowledge a transfer direction change for nRREQ. The direction is forward when asserted, host is then permitted to drive the bus.                                                                                                                                  |

| 59                  | SLCT     | I     | Printer Selected Status: A status signal from p inter to indicate the printer has powered on. The bit slct. SPP_SPR directly reflects this signal. (Same definition as SPP in EPP mode) SLCT(Printer Selected Status): In ECP mode, A status signal from printer to indicate it is on-line.                                                                                                                                                                                                                       |

| 75                  | nERROR   | I     | Printer Port Error: A status signal from printer to indicate an error status at the printer. The bit nerr.SPP_SPR directly reflects this signal. (Same definition as SPP in EPP mode) nFAULT/nPREQ(Fault/Peripheral Request): In ECP mode, peripheral uses it to indicate an error interrupt. It is valid only in forward mode. Occasionally, it can be used as a request for reverse transfer.                                                                                                                   |

| Pin No. | Pin Name | Туре        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 73      | nSLCTIN  | OD24<br>O24 | Printer Select Input: This output is the complement of the bit slctin. SPP_CPR to select the printer.  nASTB(Address Strobe): This output is used to indicate an address port access in EPP mode.nSLCTIN(Printer Select Input): In ECP mode, it is always deasserted.                                                                                                                                                                                                                                |

| 74      | nINIT    | OD24<br>O24 | Printer Initial Output: This output reflects the bit ninit.SPP_CPR to initiate the printer. (Same definition as SPP in EPP mode) nINIT/nRREQ(Initial Output/Reverse Request): In ECP mode, it sets the transfer direct ion. The transfer direction is reversed when it is asserted.                                                                                                                                                                                                                  |

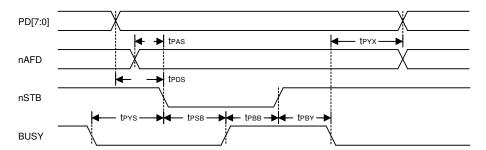

| 76      | nAFD     | OD24<br>O24 | Printer Autofeed Output: This output is the complement of the bit autofd.SPP_CPR to control the printer for the auto line feed after each line is printed.  nDSTB(Data Strobe): This output is used to indicate a data port access in EPP mode.  nAFD/HACK(Autofeed Output/Host Acknowledge): In ECP mode, it is asserted to request a byte from the peripheral by the handshaking with nPACK in the reverse direction. In the forward direction, it indicates the data contents is address or data. |

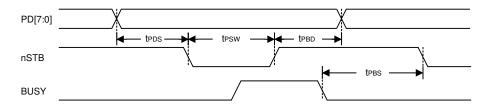

| 77      | nSTB     | OD24<br>O24 | Printer Strobe Output: This output is the complement of the bit stb.SPP_CPR to strobe the data into printer.  nWRITE(Write): In EPP mode, this output is used to indicate a write operation.  nSTB(Strobe Output): In ECP mode, it is used to strobe the address or data into the peripheral on the asserting edge during write operation.                                                                                                                                                           |

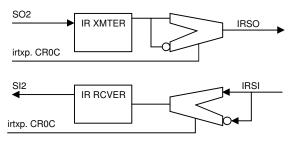

# Infra-red interface

| Pin No. | Pin Name | Туре | Description                                                     |  |  |  |  |  |

|---------|----------|------|-----------------------------------------------------------------|--|--|--|--|--|

| 88      | IRSI1    | I    | IR Receive Data In 1: IR Receive data input.                    |  |  |  |  |  |

| 89      | IRSO1    | 04   | IR Transmit Data Out 1: IR Transmit data output.                |  |  |  |  |  |

| 25      | IRSI2    | I    | IR Receive Data In 2: An alternative IR Receive data input.     |  |  |  |  |  |

| 26      | IRSO2    | O24  | IR Transmit Data Out 2: An alternative IR Transmit data output. |  |  |  |  |  |

# Game port interface

| Pin No. | Pin Name | Туре | Description                                                                                                                       |  |  |  |  |

|---------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 58      | nGAMECS  | 04   | Game Port Select: This is a select signal for game port I/O address corresponding to the setup of CR1E when game port is enabled. |  |  |  |  |

# IDE interface

| Pin No. | Pin Name | Туре | Description                                                                                                                            |  |  |  |  |

|---------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 18      | nIDERST  | OD48 | IDE Reset Output: An inverted RESET output for IDE interface.                                                                          |  |  |  |  |

| 24      | nIDEEN   | O24  | IDE Enable: This signal is active when the IDE port is enabled and the system is accessing an IDE register.                            |  |  |  |  |

| 25      | nIDECS0  | O24  | IDE Chip Select 0: This is a select signal for IDE base address corresponding to the setup of CR21 when IDE port is enabled.           |  |  |  |  |

| 26      | nIDECS1  | O24P | IDE Chip Select 1: This is a select signal for IDE alternate base address corresponding to the setup of CR22 when IDE port is enabled. |  |  |  |  |

### Misc

| Pin No. | Pin Name | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|---------|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 58      | PWRGD    | I     | Power Good: This signal indicates the power (Vcc) is valid. When it is inactive, all inputs are disconnected, all outputs are tri-stated, and the contents of registers are kept if the Vcc is valid. It sets system into standby mode.                                                                                                                                                                 |  |  |  |  |  |

| 20      | CLK24    | ICLK  | Clock 24MHz: A clock input for whole chip.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 94      | nPIOCS   | OD24U | Programmable I/O Address Decode: This is a select signal for a 1, 8, or 16 byte I/O address corresponding to the setup of CR08 and CR09 when p94s[1:0].CR03 is set to decode mode.                                                                                                                                                                                                                      |  |  |  |  |  |

| 52      | DE6      | ID    | DE6: HT8669 supports an internal pull down input for ISA mode power on setup. System can use an external pull-up resistor to determine the operation mode. At the rising edge of PWRGD, the DE6 input is latched for the mode selection:  0: Normal mode, On-board with no device being active after hardware reset.  1: ISA mode, Adapter based design with default active value after hardware reset. |  |  |  |  |  |

| 21      | DE7      | ID    | DE7: HT8669 supports an internal pull down input for Ir mo power on setup. System can use an external pull-up resistor determine the operation mode. At the rising edge of PWRG the DE7 input is latched for the mode selection:  0: Normal mode, polarity of IR receive signal is normal.  1: Inverted mode, polarity of IR receive signal is inverted.                                                |  |  |  |  |  |

| 91      | SYSOPT   | I     | Index Base I/O Address Selection: HT8669 supports an for configuration access setup. System can use an ex pull-up/down resistor to determine the address. At the tredge of hardware reset, the SYSOPT input is latched faddress selection:  0: Index base I/O address is 3F0h.  1: Index base I/O address is 370h.                                                                                      |  |  |  |  |  |

#### Power

| Pin No.    | Pin Name | Туре  | Description |

|------------|----------|-------|-------------|

| 15,72      | VCC      | Power | Vcc Power:  |

| 6,47,67,95 | GND      | Power | Ground:     |

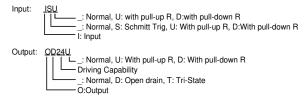

### Note: Pin type definition:

# **Register Definition**

### FDC register set

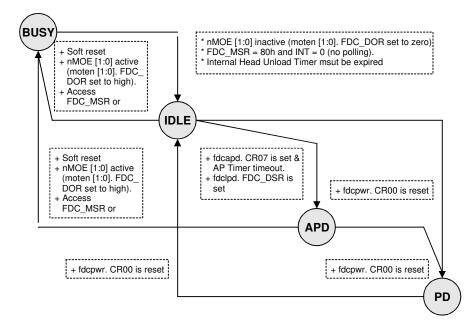

There are status registers, data register, and control registers being built in the FDC subsystem. The address map and the short form of these registers are shown below:

| Base I/O<br>Address Attribute Abbrevia |        | Abbreviation       | Description                                              |  |  |

|----------------------------------------|--------|--------------------|----------------------------------------------------------|--|--|

| fdc+00h                                |        |                    | Reserved                                                 |  |  |

| fdc+01h                                |        |                    | Reserved                                                 |  |  |

| fdc+02h                                | W/R    | FDC_DOR            | Digital output register                                  |  |  |

| fdc+03h                                |        |                    | Reserved                                                 |  |  |

| fdc+04h                                | W<br>R | FDC_DSR<br>FDC_MSR | Data rate select register<br>Main status register        |  |  |

| fdc+05h                                | W/R    | FDC_MDR            | Main data register                                       |  |  |

| fdc+06h                                |        |                    | Reserved                                                 |  |  |

| fdc+07h                                | W<br>R | FDC_CCR<br>FDC_DIR | Configuration control register<br>Digital input register |  |  |

| Default | Reg | bit7   | bit6    | bit5       | bit4   | bit3                  | bit2   | bit1       | bit0   |  |

|---------|-----|--------|---------|------------|--------|-----------------------|--------|------------|--------|--|

| 00      | DOR | 0      | 0       | moten[1:0] |        | dmaen                 | nreset | dvse       | l[1:0] |  |

| 02      | DSR | sreset | fdchpd  | 0          | ]      | pcomp[2:0] drsel[1:0] |        |            | [1:0]  |  |

| _       | MSR | rqm    | dio     | nondma     | cmdbsy | dbsy dubsy[3:0]       |        |            |        |  |

| _       | MDR |        | hd[7:0] |            |        |                       |        |            |        |  |

| 10b     | CCR | _      | _       | _          | _      | _                     | _      | drsel[1:0] |        |  |

| _       | DIR | dskchg | _       | _          | _      | _                     | _      | _          | _      |  |

This register is used to control the driver Interface. It can not be affected by a software reset. The definition of the bits are:

| FDC_DOR: Digital Output Register (fdc+02h) |                                              |   |   |        |        |       |        |        |        |

|--------------------------------------------|----------------------------------------------|---|---|--------|--------|-------|--------|--------|--------|

| Address                                    | Type bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 |   |   |        |        |       |        |        |        |

| fdc+02h                                    | WR                                           | 0 | 0 | moten1 | moten0 | dmaen | nreset | dvsel1 | dvsel0 |

| Reset Defa                                 | 0                                            | 0 | 0 | 0      | 0      | 0     | 0      | 0      |        |

| Bit | Name       | Description                                                                                                                                                                                                                                                  |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | 0          | Reserved.                                                                                                                                                                                                                                                    |

| 5:4 | moten[1:0] | Motor Enable [1:0]: These bits control the related nMOE disk interface. A logic "1" will cause the related output pin to go active.                                                                                                                          |

| 3   | dmaen      | FDC DRQ Enable: Writing "0" can disable nDACK and TC inputs, and hold DRQ and IRQ outputs to Hi-Z state. Writing "1" will enable nDACK, TC, DRQ, and IRQ for DMA function.                                                                                   |

| 2   | nreset     | FDC DOR Reset: A logic "0" written to this bit resets FDC. It will remain active until a logic "1" is written to this bit. The minimum reset duration for the software reset is 100ns. It does not affect FDC_DSR, FDC_CCR, and other bits of this register. |

| 1:0 | dvsel[1:0] | Drive Select: These bits are encoded selection bits to select DS0 - DS3. Therefore, only one drive can be accessed at one time.                                                                                                                              |

The access of disk drive can be configured by programming FDC\_DOR with the value as below:

| Drive | DOR_FDC Value | Drive | DOR_FDC Value |  |  |

|-------|---------------|-------|---------------|--|--|

| 0     | 1Ch           | 2     | 4Eh           |  |  |

| 1     | 2Dh           | 3     | 8Fh           |  |  |

• Data rate select register (FDC\_DSR)

This register is a write-only register. It is used to program the write precompensation, low power mode, software reset, and data rate selection. In PC-AT system, data rate is programmed by using FDC\_CCR instead of this register. But, the data rate is set by the recent programming of the FDC\_CCR or FDC\_DSR. This register is not affected by a software reset. The definition of the bits are:

|                               | FDC_DSR: Data Rate Select Register (fdc+04h.w) |                                              |        |   |        |        |        |        |        |

|-------------------------------|------------------------------------------------|----------------------------------------------|--------|---|--------|--------|--------|--------|--------|

| Address                       | Type                                           | Type bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 |        |   |        |        |        |        |        |

| fdc+04h                       | W                                              | sreset                                       | fdclpd | 0 | pcomp2 | pcomp1 | pcomp0 | drsel1 | drsel0 |

| Reset Default 0 0 0 0 0 0 0 0 |                                                |                                              |        |   |        |        | 0      |        |        |

| Bit | Name       | Description                                                                                                                                                                                                                                               |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | sreset     | FDC Software Reset: This bit has the same function as nreset.FDC_DOR except the polarity. By the way, this bit is self clearing.                                                                                                                          |

| 6   | fdclpd     | FDC Low Power Mode: Writing "1" can put FDC into Manual Low Power mode. In this mode, the FDC clock and data separator circuit will be turned off. FDC will leave this mode after software reset or access of the FDC_DR or FEC_MSR (and clear this bit). |

| 5   | 0          | Reserved and read only.                                                                                                                                                                                                                                   |

| 4:2 | pcomp[2:0] | FDC Write Precompensation Select: These bits select the value of write precompensation for WDATA. Track 0 is the default starting track for precompensation and can be changed by the configuration command.                                              |

| 1:0 | drsel[1:0] | Data Rate Select: These bits control the data rate of the FDC.                                                                                                                                                                                            |

ullet Main status register (FDC\_MSR)

This register is a read-only register. It reports the FDC status for the handshaking with system for FDC access. The definition of the bits are:

|               | FDC_MSR: Main Status Register (fdc+04h.r) |      |      |        |        |        |        |        |        |

|---------------|-------------------------------------------|------|------|--------|--------|--------|--------|--------|--------|

| Address       | Type                                      | bit7 | bit6 | bit5   | bit4   | bit3   | bit2   | bit1   | bit0   |

| fdc+04h       | R                                         | rqm  | dio  | nondma | cmdbsy | dvbsy3 | dvbsy2 | dvbsy1 | dvbsy0 |

| Reset Default |                                           |      |      | _      | _      | _      |        |        |        |

| Bit | Name       | Description                                                                                                                                                                                                                                                         |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | rqm        | FDC Ready for Access: FDC can be accessed if this bit is "1", otherwise the access is not allowed.                                                                                                                                                                  |

| 6   | dio        | FDC Data Transfer Direction: It indicates the data transfer direction when rqm is set. Reading "1" indicates a read operation. "0" is a write.                                                                                                                      |

| 5   | nondma     | FDC Non-DMA Operation: It reflects the DMA setup in SPECIFY command and will be set "1" during execution phase of a command. It is for polled transfer and helps to distinguish between the data transfer phase and the reading of result bytes.                    |

| 4   | cmdbsy     | FDC Command Progress: This bit indicates the command being processed. It is set after the command bytes being transfer and goes inactive at the end of result phase. If there is no result phase, it will return "0" after the last command byte being transferred. |

| 3:0 | dvbsy[3:0] | Drive x Busy: These bits are set to 1s when a driver is in the seek operation, including implied and overlapped seeks and recalibration.                                                                                                                            |

### • Main data register (FDC\_MDR)

This register is a data I/O register for FDC. All commands, data, and result status are accessed from this register.

|               | FDC_MDR: MainData Register (fdc+05h) |         |                                         |   |   |   |   |  |   |

|---------------|--------------------------------------|---------|-----------------------------------------|---|---|---|---|--|---|

| Address       | Type                                 | bit7    | bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 |   |   |   |   |  |   |

| fdc+05h       | WR                                   | hd[7:0] |                                         |   |   |   |   |  |   |

| Reset Default |                                      | _       | _                                       | _ | _ | _ | _ |  | _ |

$\bullet \ Configuration \ control \ register \ (FDC\_CCR) \\$

This register is a write-only register. It is programmed for data rate selection as the function as drsel[1:0].FDC\_DOR. The definition of the bits are:

|               | FDC_CCR: Configuration Control Register (fdc+07h.w) |      |      |      |      |      |      |        |        |

|---------------|-----------------------------------------------------|------|------|------|------|------|------|--------|--------|

| Address       | Type                                                | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1   | bit0   |

| fdc+07h       | W                                                   | _    |      | _    | _    | _    | _    | drsel1 | drsel0 |

| Reset Default |                                                     | _    |      | _    | _    | _    | _    | _      | _      |

| Bit | Name                                                                        | Description |  |  |  |  |

|-----|-----------------------------------------------------------------------------|-------------|--|--|--|--|

| 7:2 | Reserved and could not be accessed.                                         |             |  |  |  |  |

| 1:0 | 0 drsel[1:0] Data Rate Select: These bits control the data rate of the FDC. |             |  |  |  |  |

• Digital input register (FDC\_DIR)

This register is a read-only register. It reports the FDC status for the disk changes. The definition of the bits are:

| FDC_DIR: Digital Input Register (fdc+07h.r) |      |        |      |      |      |      |      |      |      |

|---------------------------------------------|------|--------|------|------|------|------|------|------|------|

| Address                                     | Type | bit7   | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

| fdc+07h                                     | R    | dskchg | _    | _    | _    |      | _    | _    | _    |

| Reset Default                               |      | _      | Hi-Z |

| Bit | Name   | Description                                                                |

|-----|--------|----------------------------------------------------------------------------|

| 7   | dskchg | FDD Disk Changed: This bit reflects the opposite value of the nDCHG input. |

| 6:0 | _      | Reserved and tri-state during read access.                                 |

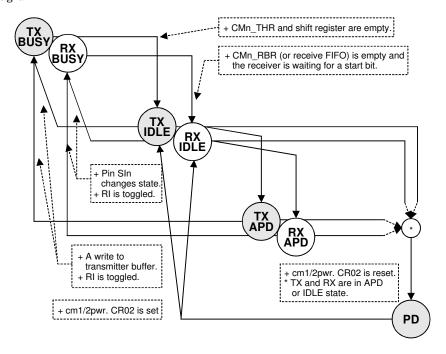

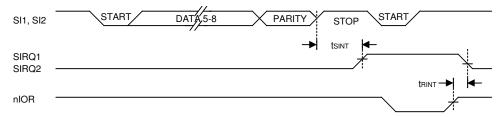

# Serial port (UART) register set

There are status registers, data buffer registers, and control registers being built in the UART subsystem. The address map of these registers and the short form is shown below:

| Base I/O<br>Address | dlab | Attribute | Abbreviation       | Description                                                |

|---------------------|------|-----------|--------------------|------------------------------------------------------------|

| cmn+0h              | 0    | W<br>R    | CMn_THR<br>CMn_RBR | Transmit Buffer Register<br>Receive Buffer Register        |

| cmn+0h              | 1    | W/R       | CMn_DLL            | Divisor LSB (Baud Rate Generator)                          |

| cmn+1h              | 0    | W/R       | CMn_IER            | Interrupt Enable Register                                  |

| cmn+1h              | 1    | W/R       | CMn_DLH            | Divisor MSB (Baud Rate Generator)                          |

| cmn+2h              | X    | W<br>R    | CMn_FCR<br>CMn_IIR | FIFO Control Register<br>Interrupt Identification Register |

| cmn+3h              | X    | W/R       | CMn_LCR            | Line Control Register                                      |

| cmn+4h              | X    | W/R       | CMn_MCR            | Modem Control Register                                     |

| cmn+5h              | X    | W/R       | CMn_LSR            | Line Status Register                                       |

| cmn+6h              | X    | W/R       | CMn_MSR            | Modem Status Register                                      |

| cmn+7h              | X    | W/R       | CMn_SCR            | Scratchpad Register                                        |

Note: dlab is the 7th bit of CMn\_LCR.

| Default | Reg | bit7   | bit6         | bit5 | bit4                  | bit3   | bit2   | bit1   | bit0   |  |

|---------|-----|--------|--------------|------|-----------------------|--------|--------|--------|--------|--|

| 00      | THR |        | Binary       |      |                       |        |        |        |        |  |

| 00      | RBR |        | Binary       |      |                       |        |        |        |        |  |

| 00      | IER | 0      | 0            | 0    | 0                     | emsi   | elsi   | ethrei | erdai  |  |

| 00      | DLL |        | Binary (LSB) |      |                       |        |        |        |        |  |

| 00      | DLH |        | Binary (MSB) |      |                       |        |        |        |        |  |

| 02      | DLL | sreset | fdclpd       | 0    | pcomp[2:0] drsel[1:0] |        |        |        | [[1:0] |  |

| 00      | FCR | thr[   | [1:0]        | 0    | 0                     | 0      | xmtrst | rcvrst | fifoen |  |

| 01      | IIR | fi     | fo           | 0    | 0                     | fifoto | intid1 | intid0 | noint  |  |

| 00      | LCR | dlab   | sbc          | spb  | eps                   | pen    | stb    | wls1   | wls0   |  |

| 00      | MCR | 0      | 0            | 0    | loop                  | out2   | out1   | rts    | dtr    |  |

| 60      | LSR | erfifo | temt         | thre | bi                    | fe     | pe     | oe     | dr     |  |

| -0      | MSR | dcd    | ri           | dsr  | cts                   | ddcd   | teri   | ddsr   | dcts   |  |

| 00      | SCR |        |              |      | Bin                   | ary    |        |        |        |  |

$\bullet \ Transmit/Receive \ Buffer \ Register \ (CMn\_THR/CMn\_RBR)$

These registers are used to buffer the transmitting or received data. Bit 0 is transmitted and received first. The definition of the bits are:

| CMn_THR: Transmit Buffer Register (com+0h.w/dlab=0) |      |        |      |      |      |      |      |      |      |

|-----------------------------------------------------|------|--------|------|------|------|------|------|------|------|

| Address                                             | Type | bit7   | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

| cmn+0h                                              | W    | Binary |      |      |      | •    |      |      |      |

| Reset Default                                       |      | 0      | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| CMn_RBR: Receive Buffer Register (com+0h.r/dlab=0) |      |      |        |      |      |      |      |      |      |

|----------------------------------------------------|------|------|--------|------|------|------|------|------|------|

| Address                                            | Type | bit7 | bit6   | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

| cmn+0h                                             | R    |      | Binary |      |      |      |      |      |      |

| Reset Defa                                         | ıult | 0 0  |        | 0    | 0    | 0    | 0    | 0    | 0    |

• Interrupt enable register (CMn\_IER)

This register is used to control the attribute of interrupt. The definition of the bits are:

|               | CMn_IER: Interrupt Enable Register (com+1h/dlab=0) |      |      |      |      |      |      |        |       |

|---------------|----------------------------------------------------|------|------|------|------|------|------|--------|-------|

| Address       | Type                                               | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1   | bit0  |

| cmn+1h        | WR                                                 | 0    | 0    | 0    | 0    | emsi | elsi | ethrei | erdai |

| Reset Default |                                                    | 0    | 0    | 0    | 0    | 0    | 0    | 0      | 0     |

| Bit | Name   | Description                                                                                                                                                                                               |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | 0      | None.                                                                                                                                                                                                     |

| 3   | emsi   | Enable MODEM Status Interrupt: Writing "1" can enable the function. This is caused when one of CMn_MSR bits changes state.                                                                                |

| 2   | elsi   | Enable Receiver Line Status Interrupt: Writing "1" can enable the function. The error sources for the interrupt are overrun, parity, framing and break. The CMn_LSR must be read to determine the source. |

| 1   | ethrei | Enable Transmit Buffer Register Empty Interrupt: Writing "1" can enable the function.                                                                                                                     |

| 0   | erdai  | Enable Received Dtat Available Interrupt: Writing "1" can enable the function and timeout interrupts in the FIFO mode.                                                                                    |

• Divisor MSB/LSB register (CMn\_DLH/CMn\_DLL)

These registers program the 16-bit divisor for baud rate generator. The definition are:

|            | CMn_DLH/DLL: Divisor MSB/LSB Register (com+1/0h/dlab=1) |      |                                         |   |   |   |   |   |   |

|------------|---------------------------------------------------------|------|-----------------------------------------|---|---|---|---|---|---|

| Address    | Type                                                    | bit7 | bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 |   |   |   |   |   |   |

| cmn+1h     | WR                                                      |      | Binary (MSB)                            |   |   |   |   |   |   |

| cmn+0h     | WR                                                      |      | Binary (LSB)                            |   |   |   |   |   |   |

| Reset Defa | ıult                                                    | 0    | 0                                       | 0 | 0 | 0 | 0 | 0 | 0 |

Below shown is the programming reference table for some specific baud rates, the input clock is 1.8462MHz which is output from 24MHz with a divisor circuit of 13:

| Desired Baud Rate | Divisor used to generate<br>16 x Clock | Percent Error Difference between<br>Desired and Actual |

|-------------------|----------------------------------------|--------------------------------------------------------|

| 50                | 2307                                   | 0.03                                                   |

| 75                | 1538                                   | 0.03                                                   |

| 110               | 1049                                   | 0.005                                                  |

| 134.5             | 858                                    | 0.01                                                   |

| 150               | 769                                    | 0.03                                                   |

| 300               | 384                                    | 0.16                                                   |

| 600               | 192                                    | 0.16                                                   |

| 1200              | 96                                     | 0.16                                                   |

| 1800              | 64                                     | 0.16                                                   |

| 2000              | 58                                     | 0.5                                                    |

| 2400              | 48                                     | 0.16                                                   |

| 3600              | 32                                     | 0.16                                                   |

| 4800              | 24                                     | 0.16                                                   |

| 7200              | 16                                     | 0.16                                                   |

| 9600              | 12                                     | 0.16                                                   |

| 19200             | 6                                      | 0.16                                                   |

| 38400             | 3                                      | 0.16                                                   |

| 57600             | 2                                      | 1.6                                                    |

| 115200            | 1                                      | 0.16                                                   |

• FIFO control register (CMn\_FCR)

This register is a write-only register and is used to control the FIFO operation. It is not supporting during the DMA operation. The definition of the bits are:

| CMn_FCR: FIFO Control Register (com+2h.w) |      |      |      |      |      |      |        |        |        |

|-------------------------------------------|------|------|------|------|------|------|--------|--------|--------|

| Address                                   | Type | bit7 | bit6 | bit5 | bit4 | bit3 | bit2   | bit1   | bit0   |

| cmn+2h                                    | W    | thr1 | thr0 | 0    | 0    | 0    | xmtrst | rcvrst | fifoen |

| Reset Default                             |      | 0    | 0    | 0    | 0    | 0    | 0      | 0      | 0      |

| Bit | Name     | Description                                                                                                                                                                                                               |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | thr[1:0] | FIFO Threshold Level: These bits are used to set the trigger level for the RCVR FIFO interrupt. Programming with "00" set 1 byte threshold, "01" for 4 bytes, "10" for 8 bytes, and "11" for 14 bytes.                    |

| 5:3 | 0        | Reserved and read only.                                                                                                                                                                                                   |

| 2   | xmtrst   | Transmit FIFO Reset: Writing "1" can clear all bytes in the XMIT FIFO and can reset its counter logic to 0. By the way, The shift register is not cleared. It is a self-cleared bit.                                      |

| 1   | rcvrst   | Receive FIFO Reset: Writing "1" can clear all bytes in the RCVR FIFO and can reset its counter logic to 0. It is a self-cleared bit.                                                                                      |

| 0   | fifoen   | FIFO Enable: Writing "1" can enable both XMIT and RCVR FIFOs. When write "0" to this bit, it will disable the FIFOs and clear the contents automatically. It should be set to "1" if other bits in this register are set. |

$\bullet \ Interrupt \ identification \ register \ (CMn\_IIR)$

This register is a read-only register and is used to determine the interrupt source and its priority. During CPU accessing the CMn\_IIR, UART will freeze all interrupts and keep current status and pending new interrupts until CPU complete the access. The definition of the bits are:

| CMn_IIR: Interrupt Identification Register (com+2h.r) |      |      |      |      |      |        |        |        |       |

|-------------------------------------------------------|------|------|------|------|------|--------|--------|--------|-------|

| Address                                               | Type | bit7 | bit6 | bit5 | bit4 | bit3   | bit2   | bit1   | bit0  |

| cmn+2h                                                | R    | fifo | fifo | 0    | 0    | fifoto | intid1 | intid0 | noint |

| Reset Default                                         |      | 0    | 0    | 0    | 0    | 0      | 0      | 0      | 1     |

| Bit | Name       | Description                                                                                                                                                                                             |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | fifo       | FIFO is Enabled: These bits are set when fifoen.CMn_FCR is set.                                                                                                                                         |

| 5:4 | 0          | None.                                                                                                                                                                                                   |

| 3   | fifoto     | FIFO Time-Out: When in non-FIFO mode, this bit is always "0", In FIFO mode (fifoen.CMn_FCR is set), this bit is set along with bit 2 when a timeout interrupt is pending.                               |

| 2:1 | intid[1:0] | Interrupt Identification: These bits are used to identify the highest priority interrupt indicated below.                                                                                               |

| 0   | noint      | No Interrupt Pending: There is no interrupt pending when this bit is "1". Otherwise, an interrupt is pending if the bit is "0". It can be used in either a hardwired prioritized or pulled environment. |

Below shown is the Interrupt control table for the explanation of fifoto, intid[1:0], noint:

|        | IIR    | [3:0]  |       |          | Interrup                           | ot set and reset fun                                                                                                                                                               | ctions                                                               |

|--------|--------|--------|-------|----------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| fifoto | intid1 | intid0 | noint | Priority | Interrupt<br>type                  | Interrupt source                                                                                                                                                                   | Interrupt Reset<br>Control                                           |

| 0      | 0      | 0      | 1     | _        | None                               | None                                                                                                                                                                               | _                                                                    |

| 0      | 1      | 1      | 0     | Highest  | Receiver line status               | Overrun Error,<br>Parity Error,<br>Framing Error,<br>or Break Interrupt.                                                                                                           | Reading the CMn_LSR.                                                 |

| 0      | 1      | 0      | 0     | Second   | Received<br>Data<br>Available      | Received Data<br>Available.                                                                                                                                                        | Read CMn_RBR or<br>the FIFO drops<br>below the trigger<br>level.     |

| 1      | 1      | 0      | 0     | Second   | Character<br>Timeout<br>Indication | No Character have<br>been removed from<br>or input to the<br>RCVR FIFO during<br>the last 4<br>characters times<br>and there is at least<br>1 character in it<br>during this time. | Reading the CMn_RBR.                                                 |

| 0      | 0      | 1      | 0     | Third    | CMn_THR<br>Empty                   | CMn_THR empty.                                                                                                                                                                     | Reading the CMn_IIR (if source of interrupt) or Writing the CMn_THR. |

| 0      | 0      | 0      | 0     | Lowest   | MODEM<br>Status                    | Clear to Send,<br>or Data Set Ready,<br>or Ring Indicator,<br>or Data Carrier<br>Detect                                                                                            | Reading the CMn_MSR.                                                 |

ullet Line control register (CMn\_LCR)

This register is used to determine the format of serial line. The definition of the bits are:

|                             | CMn_LCR: Line Control Register (com+3h) |      |                      |      |      |      |      |      |      |

|-----------------------------|-----------------------------------------|------|----------------------|------|------|------|------|------|------|

| Address                     | Type                                    | bit7 | bit6                 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

| cmn+3h                      | WR                                      | dlab | $\operatorname{sbc}$ | spb  | eps  | pen  | stb  | wls1 | wls0 |

| Reset Default 0 0 0 0 0 0 0 |                                         |      |                      |      |      |      | 0    |      |      |

| Bit | Name     | Description                                                                                                                                                                                                                        |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | dlab     | Divisor Latch Access Bit: It must be set to "1" to access the CMn_DLH/DLL and set to "0" for the access of CMn_RBR/THR/IER.                                                                                                        |

| 6   | sbc      | Set Break Control Bit: When this bit is set "1", the SO output is forced to the spacing or logic "0" state and remains there until the bit is reset. This feature enables the UART to alert a terminal in a communications system. |

| 5   | spb      | Stick Parity Bit: When this bit is set "1" and pen is enabled, the parity bit is transmitted and then detected by the receiver in the opposite state indicated by eps.                                                             |

| 4   | eps      | Even Parity Select Bit: When pen is set "1", it will generate or check the serial data with odd number of logic "1" if this bit is set to "0", or even parity check rule will be followed for the bit is set to "1".               |

| 3   | pen      | Parity Enable Bit: When it is set, a parity bit is generated for transmit or checked during receiving between the last data word bit and the first stop bit of the serial data.                                                    |

| 2   | stb      | Number of Stop Bit: This bit defines the number of stop bits for transmitting or receiving data. The number of stop bits is depended to wls[1:0] too.                                                                              |

| 1:0 | wls[1:0] | Word Length Select Bits: These bits defines the number of bits in each transmitted or received serial character. Below shown is the different types of character format.                                                           |

| stb | wls1 | wls0 | Word Length | Number of Stop Bits |

|-----|------|------|-------------|---------------------|

| 0   | 0    | 0    | 5 Bits      | 1                   |

| 0   | 0    | 1    | 6 Bits      | 1                   |

| 0   | 1    | 0    | 7 Bits      | 1                   |

| 0   | 1    | 1    | 8 Bits      | 1                   |

| 1   | 0    | 0    | 5 Bits      | 1.5                 |

| 1   | 0    | 1    | 6 Bits      | 2                   |

| 1   | 1    | 0    | 7 Bits      | 2                   |

| 1   | 1    | 1    | 8 Bits      | 2                   |

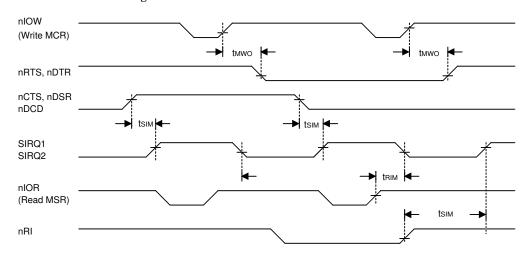

### • MODEM control register (CMn\_MCR)

This register is used to control the interfaces of MODEM or data set or the emulated MODEM mode. The definition of the bits are:

|                               | CMn_MCR: MODEM Control Register (com+4h) |      |      |      |      |      |      |      |      |

|-------------------------------|------------------------------------------|------|------|------|------|------|------|------|------|

| Address                       | Type                                     | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

| cmn+4h                        | WR                                       | 0    | 0    | 0    | loop | out2 | out1 | rts  | dtr  |

| Reset Default 0 0 0 0 0 0 0 0 |                                          |      |      |      |      |      | 0    |      |      |

| Bit | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | 0    | None.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4   | loop | Loopback Control Bit: When this bit is set "1", the UART will go into diagnostic test. First, SO is set to marking state (Logic "1") and SI is disconnected. Then, the output of Transmitter Shift Register is looped back into the Receiver Shift Register input. In this mode, all MODEM inputs (nCTS, nDSR, nRI, and nDCD) are disconnected, and the four MODEM Control output (nDTR, nRTS, OUT1, and OUT2) are internally connected to the four MODEM Control inputs (nCTS, nDSR, nRI, and nDCD) respectively. In addition, the MODEM control output pins are forced Hi-Z and the transmitted data is received immediately. |

| 3   | out2 | Output 2: This bit sets to "1" to enable the serial port interrupt. When this bit is "0", the interrupt is disabled with a Hi-Z state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2   | out1 | Output 1: For read/write access only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1   | rts  | Request To Send: This bit controls the nRTS output. When it is set to "1", the nRTS output is forced to a logic "0", and nRTS will be "1" if the bit is "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0   | dtr  | Data Terminal Ready: This bit controls the nDTR output. If it is set to "1", the nDTR output is forced to a logic "0", and nDTR will be "1" if the bit is "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

### • Line status register (CMn\_LSR):

This register reports the status of serial port interface. Bits 7 through 4 are the error conditions that produce a Receiver Line Status Interrupt when any of the corresponding conditions are detected and the interrupt is enabled. The definition of the bits are:

|                               | CMn_LSR: Line Status Register (com+5h) |        |      |      |      |      |      |      |      |

|-------------------------------|----------------------------------------|--------|------|------|------|------|------|------|------|

| Address                       | Type                                   | bit7   | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

| cmn+5h                        | WR                                     | erfifo | temt | thre | bi   | fe   | pe   | oe   | dr   |

| Reset Default 0 1 1 0 0 0 0 0 |                                        |        |      |      |      |      | 0    |      |      |

| Bit | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | erfifo | Error in RCVR FIFO: When in non-FIFO mode, this bit is permanently set to "0". In FIFO mode, this bit is set "1", when there is at least one parity error, frame error or break indication in the FIFO. This bit is cleared when this register is read if there are no subsequent errors in the FIFO.                                                                                                                                                                                                                                                                                                           |

| 6   | temt   | Transmitter Empty: This bit is set whenever CMn_THR and CMn_TSR are both empty, and will be reset whenever either CMn_THR or CMn_TSR contains a data character. In the FIFO mode, this bit is set when the CMn_THR and CMn_TSR are both empty. This is a read-only bit.                                                                                                                                                                                                                                                                                                                                         |

| 5   | thre   | Transmitter Holding Register Empty: This bit indicates the UART is ready to accept a new character for transmission. It is set when a character is transferred from CMn_THR into the CMn_TSR (Transmitter Shift Register), and will be reset whenever Host loads the CMn_THR. In addition, this bit causes the UART to issue an interrupt when ethrei.CMn_IER is set. In the FIFO mode, this bit is set when the XMIT FIFO is empty. It is cleared when at least 1 byte is written to the XMIT FIFO. This is a read-only bit.                                                                                   |

| 4   | bi     | Break Interrupt: This bit is set whenever the received data is held in the Spacing state ("0") for longer than a full word transmission time (total time of the start bit + data bits + parity bit + stop bits). It is reset when this register is read. In FIFO mode, this error is associated with the particular character in the FIFO it applies to. This error is indicated when the associated character is at the top of the FIFO. When break occurs only one zero character is loaded into the FIFO. Restarting after a break is received requires the serial data to be "1" for at least 1/2 bit time. |

| 3   | fe     | Frame Error: This bit is set whenever the received character did not have a valid stop bit, i.e. a spacing level. It is reset when this register is read. In FIFO mode, this error is associated with the particular character in the FIFO it applies to. This error is indicated when the associated character is at the top of the FIFO. The UART will try to re-synchronize after a frame error. To do this, it assumes that the framing error was due to the next start bit, so it samples this "start" bit twice and then takes in the "data" field.                                                       |

| 2   | pe     | Parity Error: This bit is set when the parity of the receive data is detected error, and is reset when this register is read. In FIFO mode, this error is associated with the particular character in the FIFO it applies to. This error is indicated when the associated character is at the top of the FIFO.                                                                                                                                                                                                                                                                                                  |