THE

**TRANSPUTER**

**APPLICATIONS**

**NOTEBOOK**

Architecture and Software

INMOS is a member of the SGS-THOMSON Microelectronics group

## Worldwide Headquarters

INMOS Limited 1000 Aztec West Almondsbury Bristol BS12 4SQ UNITED KINGDOM Telephone (0454) 616616 Fax (0454) 617910 Telex 4444723

## **Worldwide Business Centres**

### USA

INMOS Business Centre

Headquarters (USA)

SGS-THOMSON Microelectronics Inc

2225 Executive Circle

PO Box 16000

Colorado Springs

Colorado 80935-6000

Telephone (719) 630 4000

Fax (719) 630 4325

Telex Easylink 62944936

SGS-THOMSON Microelectronics Inc Sales and Marketing Headquarters (USA) 1000 East Bell Road Phoenix Arizona 85022 Telephone (602) 867 6100 Fax (602) 867 6102 Telex 249976 SGSPH UR

INMOS Business Centre

SGS-THOMSON Microelectronics Inc

Five Burlington Woods Drive

Suite 201

Burlington

Massachusetts 01803

Telephone (617) 229 2550

Fax (617) 229 6010

INMOS Business Centre

SGS-THOMSON Microelectronics Inc

9861 Broken Land Parkway

Suite 320

Columbia

Maryland 21045

Telephone (301) 995 6952

Fax (301) 290 7047

Telex Easylink 62034521

INMOS Business Centre SGS-THOMSON Microelectronics Inc 200 East Sandpointe Suite 650 Santa Ana California 92707 Telephone (714) 957 6018 Fax (714) 957 3281 Telex Easylink 62034531

INMOS Business Centre

SGS-THOMSON Microelectronics Inc

2620 Augustine Drive

Suite 100

Santa Clara

California 95054

Telephone (408) 727 7771

Fax (408) 727 1458

Telex Easylink 62203010

INMOS Business Centre SGS-THOMSON Microelectronics Inc 1310 Electronics Drive Carrollton Texas 75006 Telephone (214) 466 8844 Fax (214) 466 7352

## EUROPE

## United Kingdom

Telex Easylink 62934544

INMOS Business Centre

SGS-THOMSON Microelectronics Ltd

Planar House

Parkway Globe Park

Marlow

Bucks SL7 1YL

Telephone (0628) 890 800

Fax (0628) 890 391

Telex 847458

## France

INMOS Business Centre SGS-THOMSON Microelectronics SA 7 Avenue Gallieni BP 93 94253 Gentilly Cedex Telephone (1) 47 40 75 75 FAX (1) 47 40 79 10 Telex 632570 STMHQ

## West Germany

INMOS Business Centre SGS-THOMSON Microelectronics GmbH Bretonischer Ring 4 8011 Grasbrunn Telephone (089) 46 00 60 Fax (089) 460 54 54 Telex 528211

## ASIA PACIFIC

## Japan

INMOS Business Centre SGS-THOMSON Microelectronics K K Nisseki Takanawa Building, 4th Floor 18–10 Takanawa 2-chome Minato-ku Tokyo 108 Telephone (03) 280 4125 Fax (03) 280 4131

## Singapore

INMOS Business Centre SGS-THOMSON Microelectronics Pte Ltd 28 Ang Mo Kio Industrial Park 2 Singapore 2056 Telephone (65) 482 14 11 Fax (65) 482 02 40 Telex RS 55201 ESGIES

# TRANSPUTER APPLICATIONS NOTEBOOK

**Architecture and Software**

## **INMOS Databook Series**

Transputer Databook

Transputer Support Databook: Development and Sub-systems

Memory Databook Graphics Databook Digital Signal Processing Databook Military Micro-Products Databook

Transputer Applications Notebook: Architecture and Software Transputer Applications Notebook: Systems and Performance

Copyright @INMOS Limited 1989

INMOS reserves the right to make changes in specifications at any time and without notice. The information furnished by INMOS in this publication is believed to be accurate; however, no responsibility is assumed for its use, nor for any infringement of patents or other rights of third parties resulting from its use. No licence is granted under any patents, trademarks or other rights of INMOS.

•, Inmos, IMS and occam are trademarks of the INMOS Group of Companies.

INMOS is a member of the SGS-THOMSON Microelectronics Group of Companies.

INMOS document number: 72-TRN-206-00

## **Contents overview**

|      | 1 | INMOS | An overview. |

|------|---|-------|--------------|

| - 1. |   |       |              |

## Principles

| 2 | Communicating processes and OCCAM      | Discusses the design of OCCAM. (INMOS technical note 20)                                                       |

|---|----------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 3 | The transputer implementation of occam | Explains how the concurrent processes of OCCAM can be implemented by the transputer. (INMOS technical note 21) |

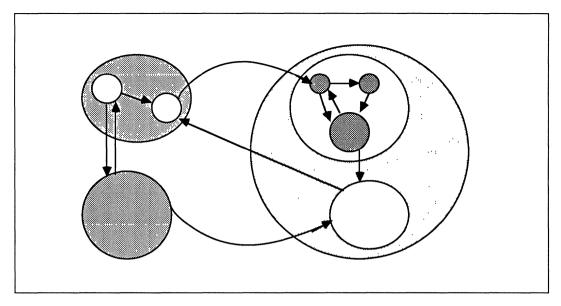

| 4 | Communicating process computers        | Discusses construction of parallel computers from collections of transputers. (INMOS technical note 22)        |

| 5 | Compiling occam into silicon           | Describes how communicating processes can be implemented directly on silicon. (INMOS technical note 23)        |

## **Practice**

| 6  | The development of occam 2                                                | Shows how occam has been extended to support numerical applications. (Originally INMOS technical note 32)                           |

|----|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

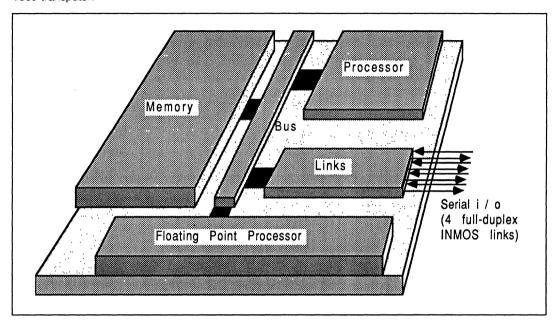

| 7  | IMS T800 architecture                                                     | Describes the design of the IMS T800 transputer. (INMOS technical note 06)                                                          |

| 8  | The role of occam in<br>the design of the IMS<br>T800                     | Shows how the floating-point unit of the IMS T800 was verified. (INMOS technical note 47)                                           |

| 9  | Simpler real-time<br>programming with the<br>transputer                   | Illustrates how occam and the transputer simplifies the design of real-time processing systems. (INMOS technical note 51)           |

| 10 | Long arithmetic on the<br>computer                                        | Shows how to perform efficient multiple length arithmetic on the transputer. (INMOS technical note 39)                              |

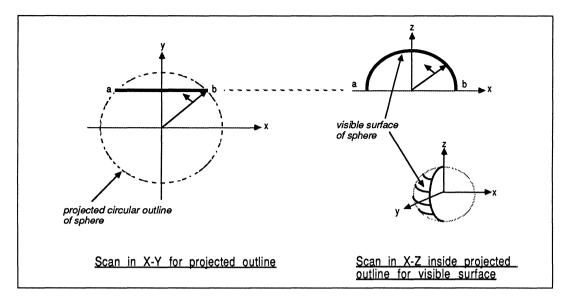

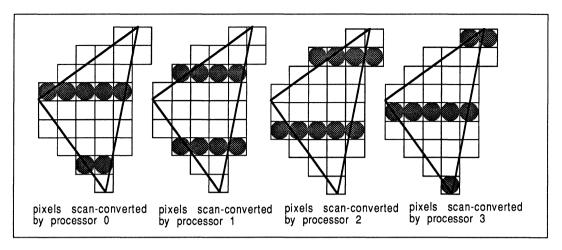

| 11 | Exploiting concurrency: a ray tracing example                             | Describes a concurrent ray tracing program. (INMOS technical note 07)                                                               |

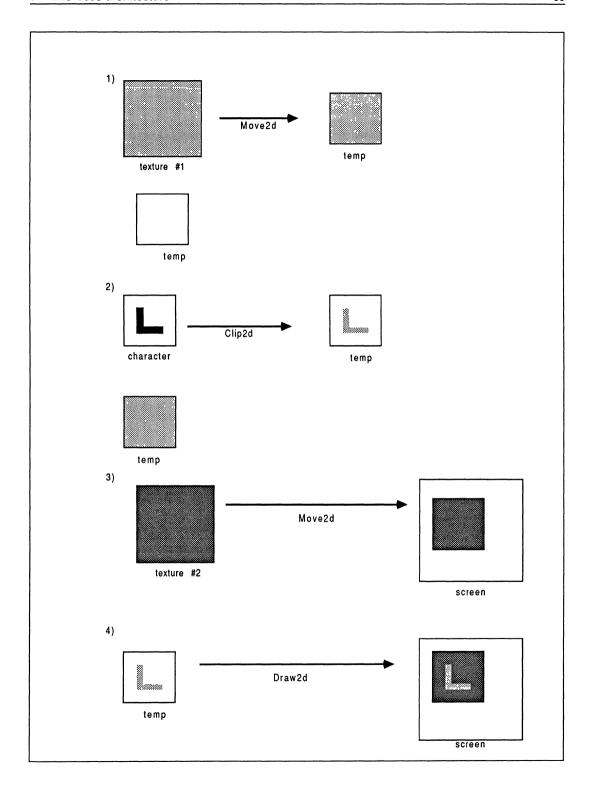

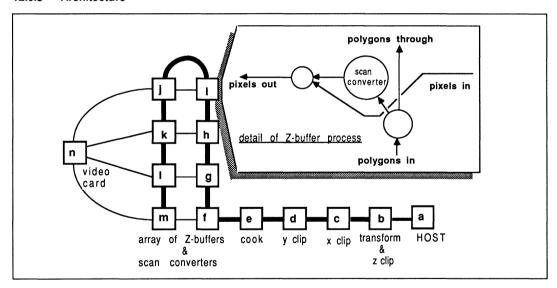

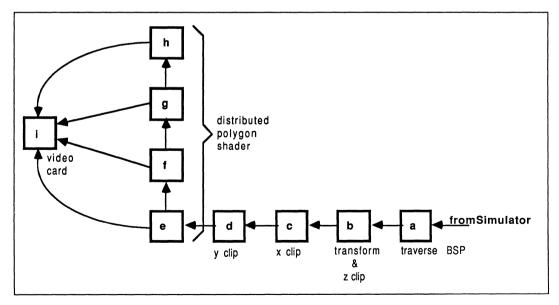

| 12 | High-performance<br>graphics with the IMS<br>T800                         | Discusses concurrency in computer graphics. (INMOS technical note 37)                                                               |

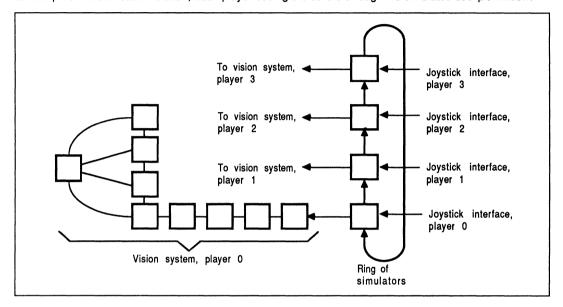

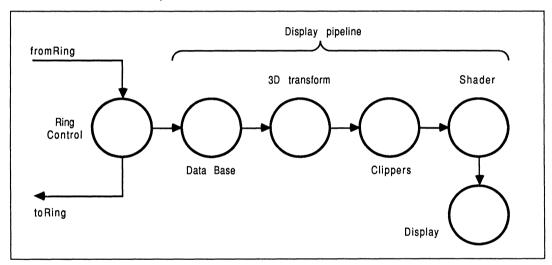

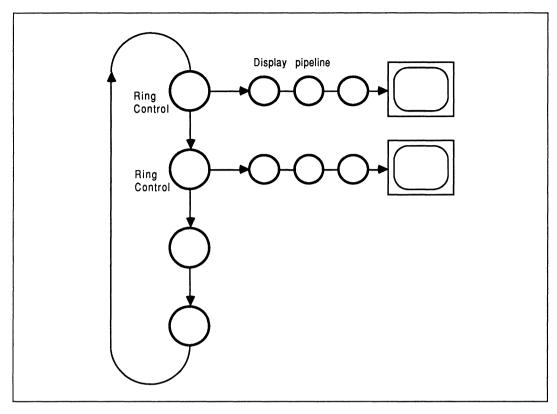

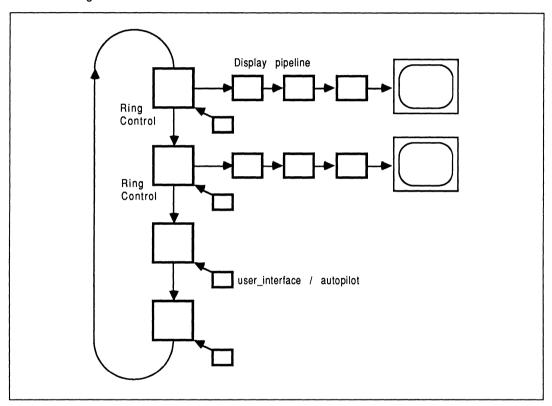

| 13 | A transputer based<br>multi-user flight<br>simulator                      | Describes the operation of a multi-pilot flight simulator. (INMOS technical note 36)                                                |

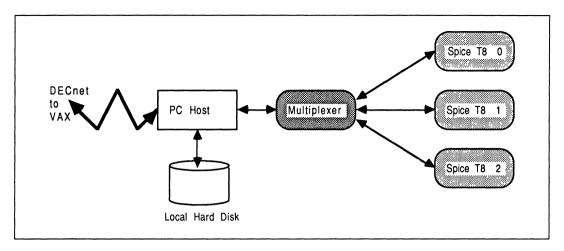

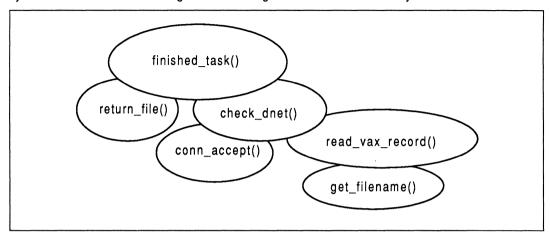

| 14 | Porting SPICE to the<br>INMOS IMS T800<br>transputer                      | Describes an example of porting existing FORTRAN applications to the transputer. (INMOS technical note 52)                          |

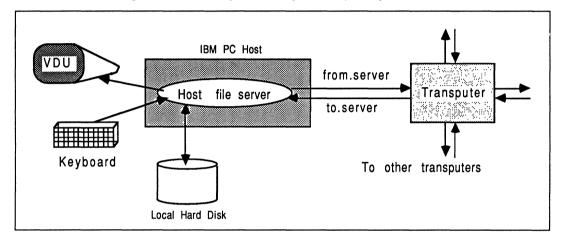

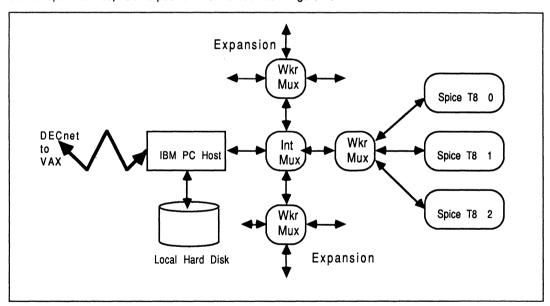

| 15 | A transputer farm<br>accelerator for<br>networked computing<br>facilities | Shows a general purpose technique for using multiple transputers to accelerate conventional applications. (INMOS technical note 54) |

## Contents

|   |      | Prefac     | e .                                                        | xiii     |

|---|------|------------|------------------------------------------------------------|----------|

|   |      |            |                                                            |          |

|   | 1    | INMOS      |                                                            |          |

|   |      | 1.1        | Introduction                                               | 2        |

|   |      | 1.2        | Manufacturing                                              | 2        |

|   |      | 1.3        | Assembly                                                   | 2        |

|   |      | 1.4        | Test                                                       | 2        |

|   |      | 1.5        | Quality and Reliability                                    |          |

|   |      | 1.6        | Military                                                   | 2        |

|   |      | 1./        | Future Developments 1.7.1 Research and Development         | 3        |

|   |      |            | 1.7.1 Research and Development 1.7.2 Process Developments  | 3        |

|   |      |            | 1.7.2 Process Developments                                 | <u></u>  |

| 1 | Prin | ciples     |                                                            | 5        |

|   |      |            | · · · · · · · · · · · · · · · · · · ·                      |          |

|   | 2    |            | unicating processes and OCCAM                              | 7        |

|   |      | 2.1        | Introduction                                               | 7        |

|   |      | 2.2        | Architecture                                               | 7        |

|   |      |            | 2.2.1 Locality                                             | 7        |

|   |      | 0.0        | 2.2.2 Simulated and real concurrency                       | 7        |

|   |      | 2.3        | The occam primitives                                       |          |

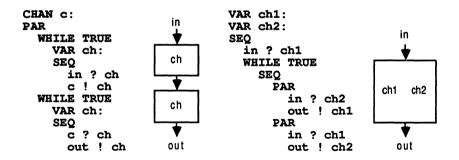

|   |      | 2.4        | The parallel construct 2.4.1 Synchronised communication    | 9        |

|   |      | 0.5        | 2.4.1 Synchronised communication The alternative construct | 9        |

|   |      | 2.5        |                                                            | 10       |

|   |      | 26         | 2.5.1 Output guards                                        | 11       |

|   |      | 2.6<br>2.7 | Channels and hierarchical decomposition                    | 12       |

|   |      | 2.8        | Arrays and replicators Time                                | 12<br>13 |

|   |      | 2.9        | Types and data structures                                  | 14       |

|   |      | 2.10       | Implementation of OCCAM                                    | 14       |

|   |      | 2.10       | 2.10.1 Compile-time allocation                             | 15       |

|   |      | 2.11       | Program development                                        | 15       |

|   |      | 2.11       | 2.11.1 Configuration                                       | 16       |

|   |      | 2.12       | OCCAM programs                                             | 17       |

|   |      | 2.12       | 2.12.1 Example: systolic arrays                            | 18       |

|   |      |            |                                                            | 18       |

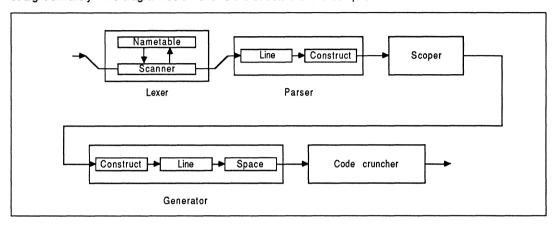

|   |      | 2.13       | 2.12.2 Example: OCCAM compiler Conclusions                 | 20       |

|   |      | 2.13       | References                                                 | 20       |

|   |      | 2.14       | neielelices                                                | 20       |

|   | 3    | The tr     | ansputer implementation of OCCAM                           | 21       |

|   |      | 3.1        | Introduction                                               | 21       |

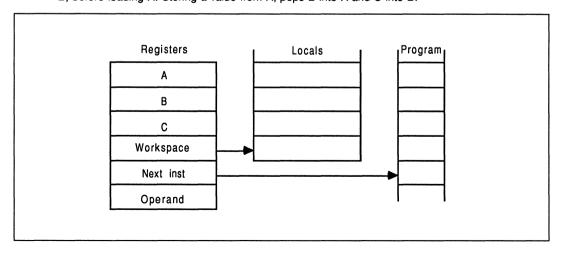

|   |      | 3.2        | Architecture                                               | 21       |

|   |      | 3.3        | occam                                                      | 21       |

|   |      | 3.4        | The transputer                                             | 22       |

|   |      |            | 3.4.1 Sequential processing                                | 22       |

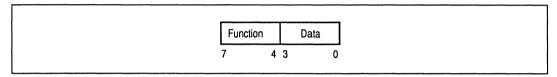

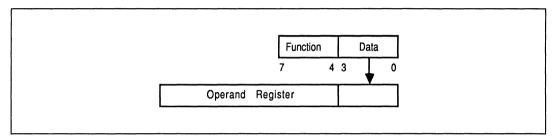

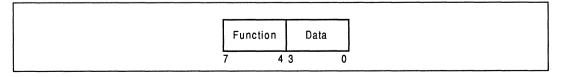

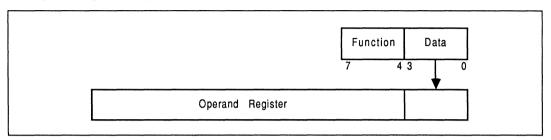

|   |      |            | 3.4.2 Instructions                                         | 23       |

|   |      |            | Direct functions                                           | 23       |

|   |      |            | Prefix functions                                           | 24       |

|   |      |            | Indirect functions                                         | 24       |

|   |      |            | 3.4.3 Expression evaluation                                | 25       |

|   |      |            | Efficiency of encoding                                     | 25       |

|   |      |            |                                                            |          |

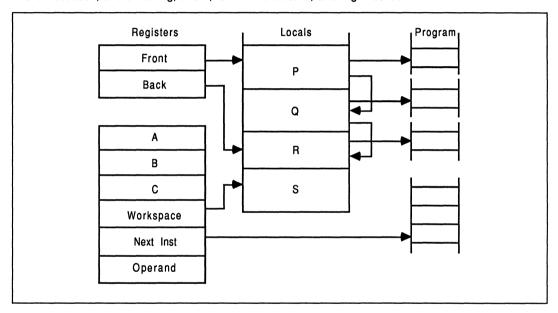

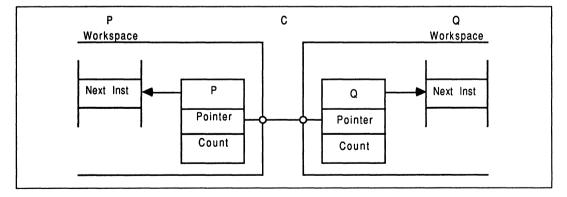

|                                         |   |       | 3.4.4       | Support for concurrency                                 | 25              |

|-----------------------------------------|---|-------|-------------|---------------------------------------------------------|-----------------|

| ***********                             |   |       |             | Communications                                          | 27              |

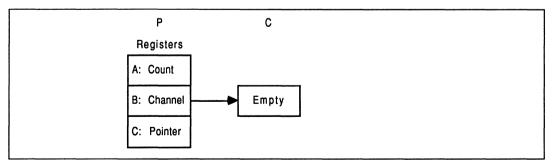

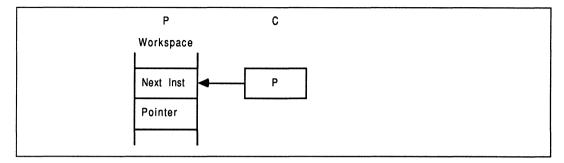

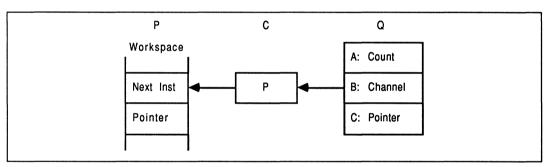

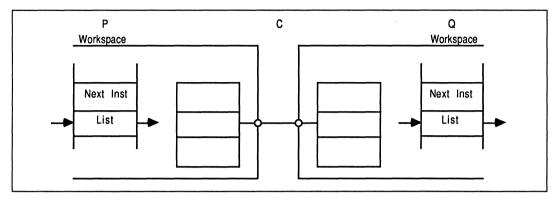

|                                         |   |       | <del></del> | Internal channel communication                          | 27              |

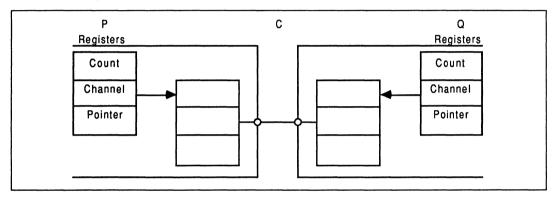

|                                         |   |       |             | External channel communication                          | 29              |

|                                         |   |       |             | Timer                                                   | 30              |

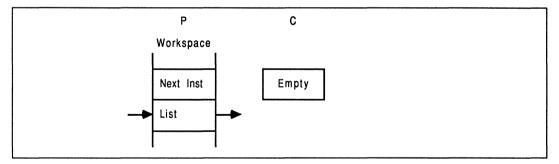

|                                         |   |       |             | Alternative                                             | 30              |

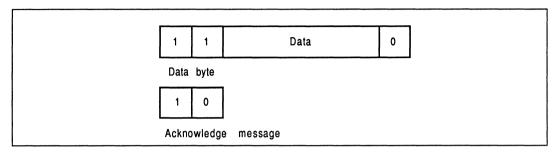

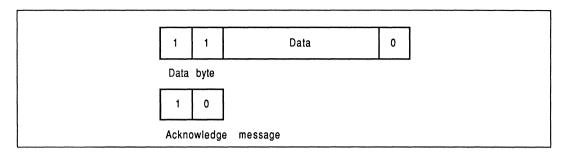

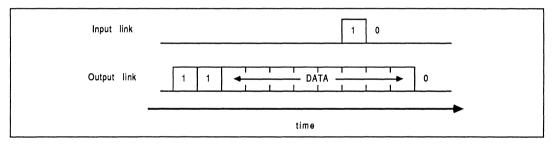

|                                         |   |       | 3.4.5       | Inter-transputer links                                  | 30              |

|                                         |   | 3.5   | Summa       | ary                                                     | 31              |

|                                         |   | 3.6   | Refere      |                                                         | 31              |

|                                         |   |       |             |                                                         |                 |

|                                         | 4 | Comm  | unicating   | g process computers                                     | 33              |

|                                         |   | 4.1   | Introdu     |                                                         | 33              |

|                                         |   | 4.2   | Applica     | ations with special configurations                      | 33              |

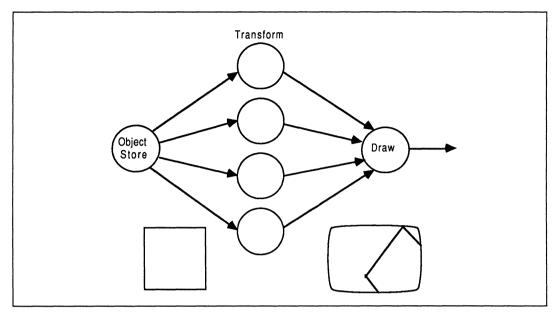

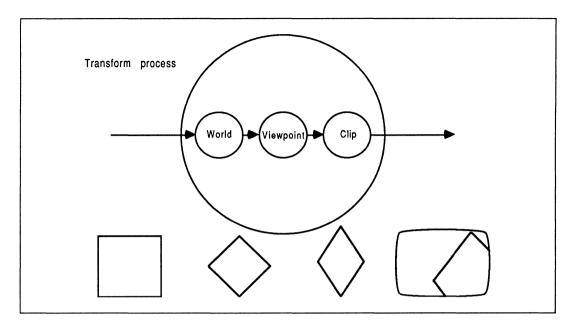

|                                         |   |       | 4.2.1       | Algorithmic parallelism or dataflow decomposition       | 34              |

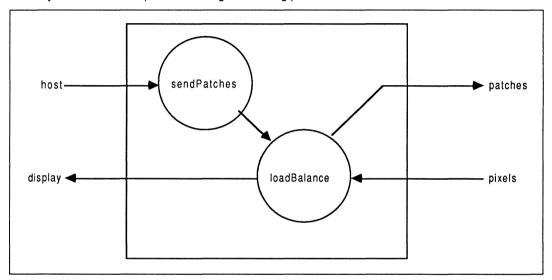

|                                         |   |       |             | Example: OCCAM compiler                                 | 34              |

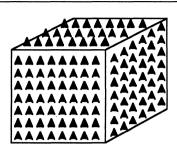

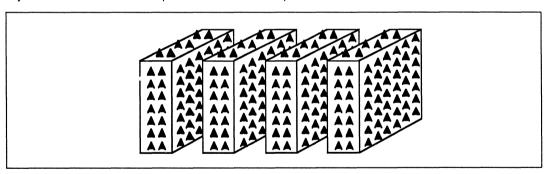

|                                         |   |       |             | Example: solid modelling                                | 35              |

|                                         |   |       | 4.2.2       | Geometric parallelism or data structure decomposition   | 37              |

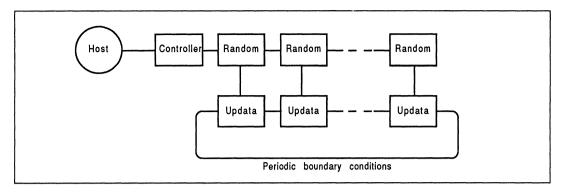

|                                         |   |       |             | Statistical mechanics                                   | 37              |

|                                         |   |       | 4.2.3       | Farming out processing                                  | 39              |

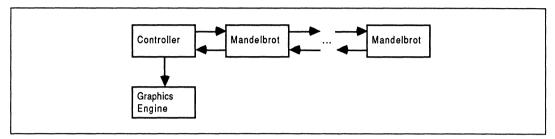

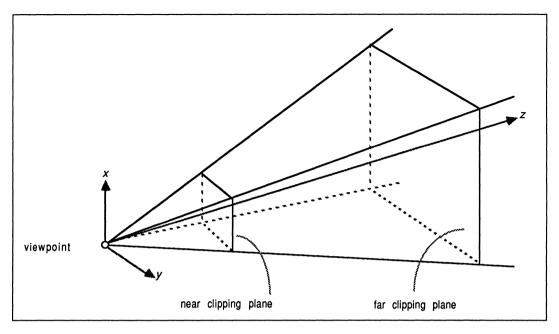

|                                         |   |       |             | Example: Graphical representation of the Mandelbrot Set | 39              |

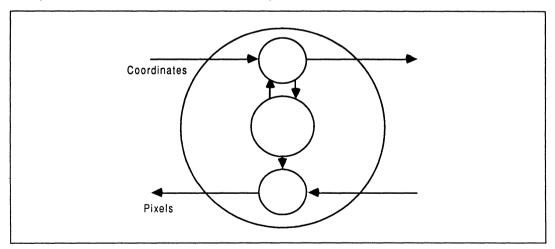

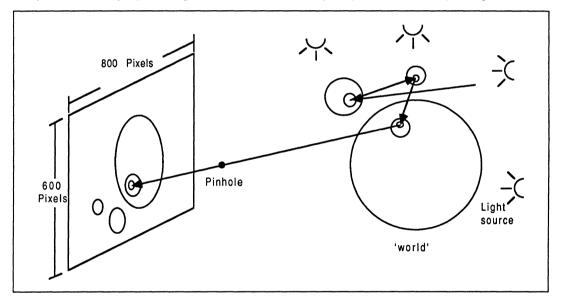

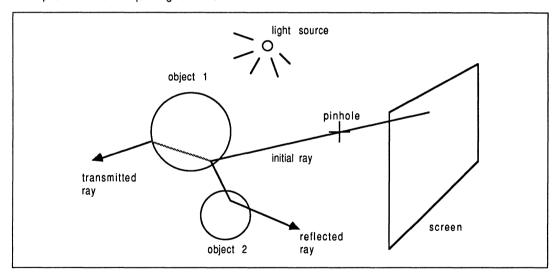

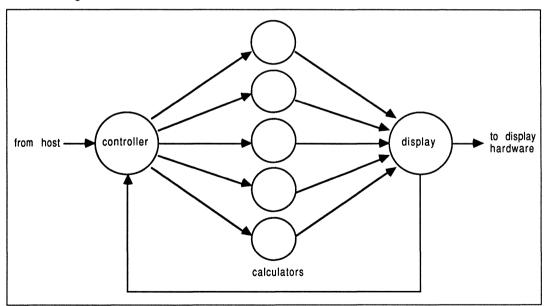

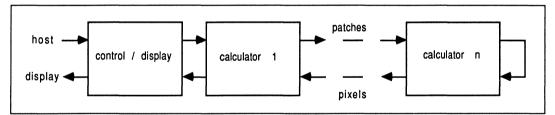

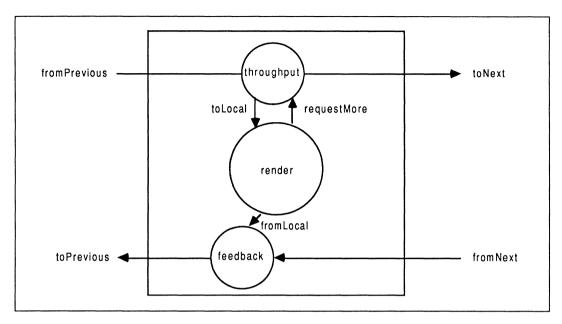

|                                         |   |       |             | Example: ray tracing                                    | 41              |

|                                         |   |       |             | Some comments about the previous two examples           | 42              |

|                                         |   | 4.3   | Genera      | al-purpose structures                                   | 42              |

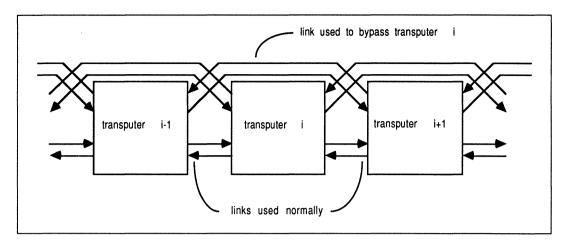

|                                         |   |       | 4.3.1       | Routing and the communication/computation trade-off     | 43              |

|                                         |   |       | 4.3.2       | Comparison of pipelines and processor farms             | 44              |

|                                         |   | 4.4   | Refere      |                                                         | 46              |

|                                         |   |       |             |                                                         |                 |

|                                         | 5 | Compi | ling OCC    | cam into silicon                                        | 47              |

|                                         |   | 5.1   | Introdu     |                                                         | 47              |

|                                         |   | 5.2   | VLSI d      | esian                                                   | 47              |

|                                         |   | 5.3   | occan       |                                                         | 47              |

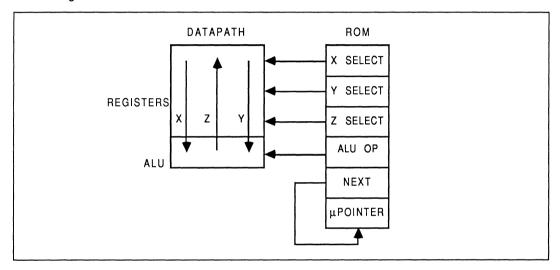

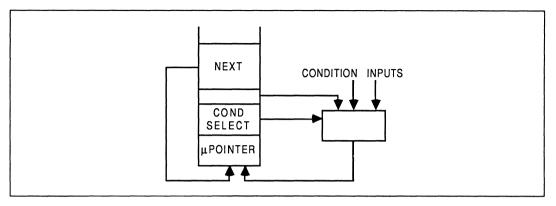

|                                         |   | 5.4   | Implem      | nentation of OCCAM                                      | 48              |

|                                         |   | 5.5   |             | stract micro-machine                                    | 49              |

|                                         |   | 5.6   |             | mpiler output                                           | 49              |

|                                         |   | 5.7   |             | les, expressions, assignment and SEQ                    | 50              |

|                                         |   | 5.8   |             | WHILE                                                   | 51              |

|                                         |   | 5.9   | Arrays      |                                                         | 52              |

|                                         |   | 5.10  | Proced      |                                                         | 53              |

|                                         |   | 5.11  | PAR         |                                                         | 53              |

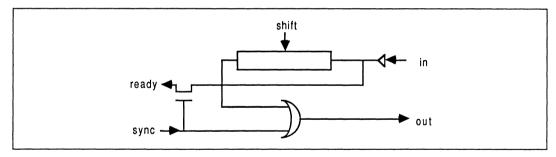

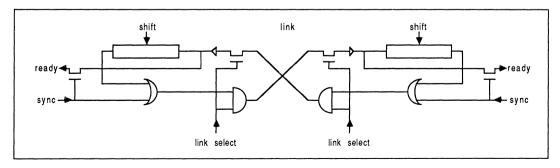

|                                         |   | 5.12  |             | els and communication                                   | 53              |

|                                         |   | 5.13  | ALT         | ers and communication                                   | <del>54</del>   |

| *************************************** |   | 5.14  |             | ele: the prime farm                                     | 55              |

|                                         |   | 5.14  |             | le: signal processing                                   | 56              |

|                                         |   | 5.16  |             | le: simple processor                                    | <u>56</u>       |

|                                         |   | 5.17  | Conclu      |                                                         | 56<br>59        |

|                                         |   |       |             |                                                         | <u>59</u><br>59 |

|                                         |   | 5.18  | Refere      | lices                                                   | 59              |

| 2 | Prac       | ctice       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 61       |

|---|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|   | 6          | The de      | evelopment of OCCAM 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 63       |

|   | <u>-</u> - | 6.1         | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 63       |

|   | ·····      | 6.2         | The data types of occam 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63       |

|   |            | 6.3         | Channel protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64       |

|   |            | 6.4         | Numerical behaviour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 66       |

|   |            | 6.5         | Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67       |

|   |            | 6.6         | Alias checking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68       |

|   |            | 6.7         | Checking the validity of parallel constructs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 70       |

|   |            | 6.8         | Run-time error handling in occam 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 71       |

|   |            | 6.9         | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 72       |

|   |            | 6.10        | References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72       |

|   |            | 1140 T      | 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 70       |

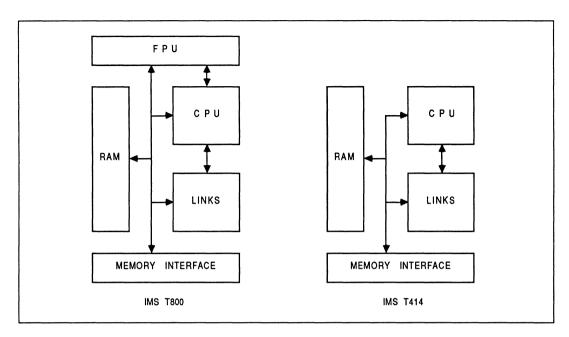

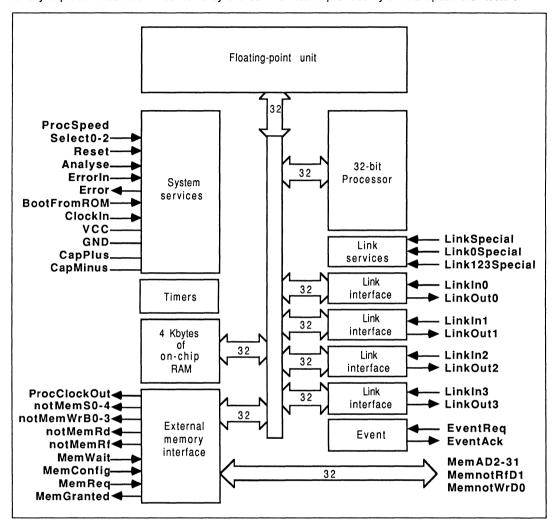

|   | 7          |             | 800 architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73       |

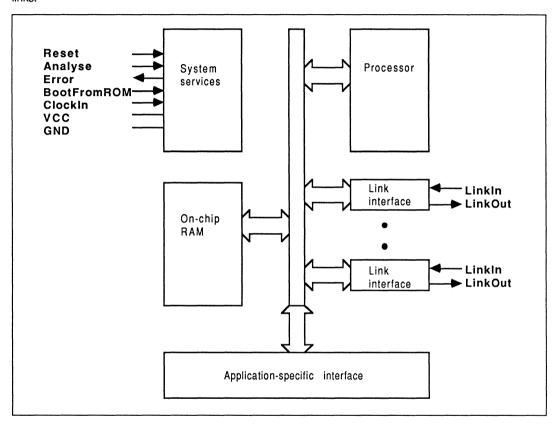

|   |            | 7.1<br>7.2  | Introduction The transport has been applied to the control of the | 73<br>73 |

|   |            | 1.2         | The transputer: basic architecture and concepts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|   |            |             | 7.2.1 A programmable device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73       |

|   |            |             | 7.2.2 Processor and memory on a single chip 7.2.3 Serial communication between transputers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 73       |

|   |            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 74       |

|   |            |             | 7.2.4 Simplified processor with microcoded scheduler 7.2.5 Transputer products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74<br>74 |

|   |            | 7.3         | 7.2.5 Transputer products IMS T800 architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|   |            | 7.3         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 74       |

|   |            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 75       |

|   |            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 76       |

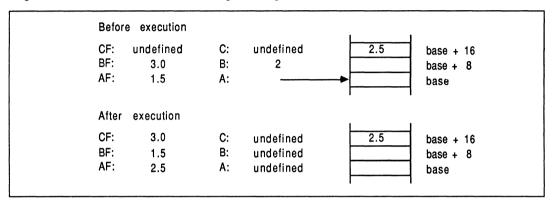

|   |            |             | 7.3.3 Optimising use of the stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 78       |

|   |            | <del></del> | 7.3.4 Concurrent operation of FPU and CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 78       |

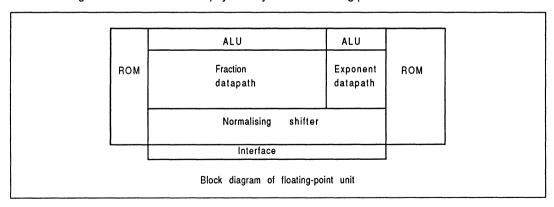

|   |            | 7.4         | Floating-point unit design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 80       |

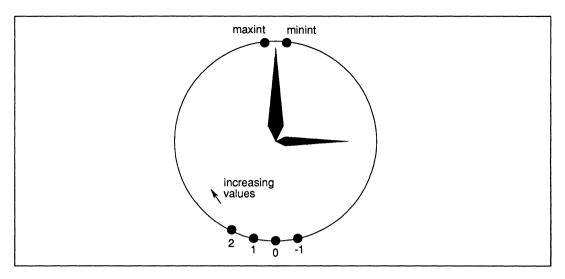

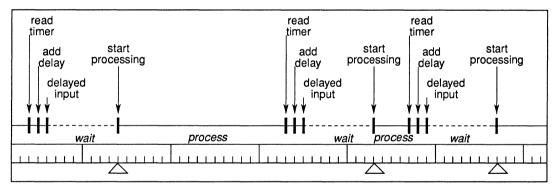

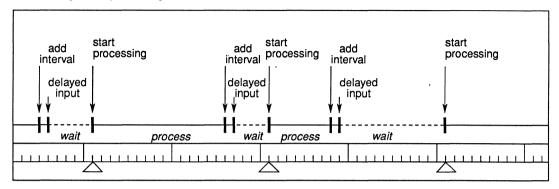

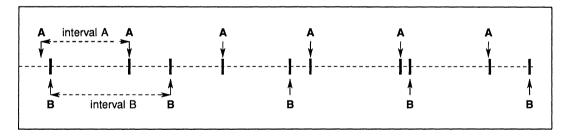

|   |            | 7.5         | Floating-point performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 82       |