# **IMS B008**

## IBM PC Motherboard

#### **FEATURES**

- IBM PC-AT format board

- Ten transputer module (TRAM) slots

- IBM PC bus interface supports DMA and interrupts

- IMS C004 programmable 32 way crossbar switch allows link configuration

- Conforms to the Module Motherboard Architecture (INMOS Technical Note 49)

- 37 way D-type connector gives access to links and system services allowing larger systems to be built

#### **DESCRIPTION**

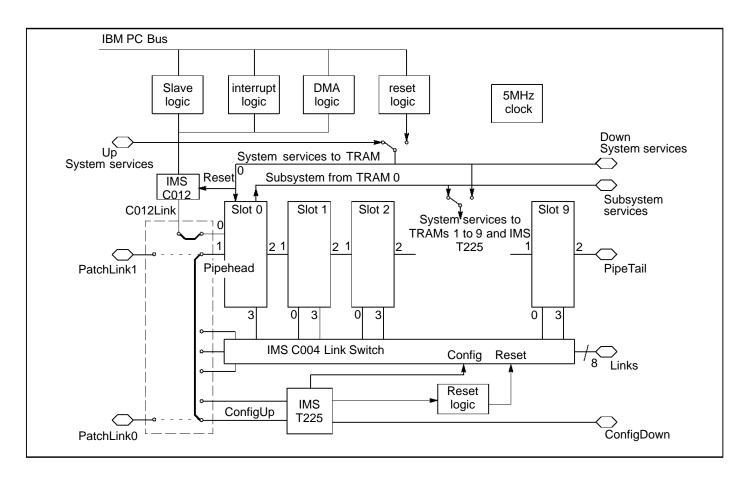

The IMS B008 is a TRAM motherboard which plugs into the IBM PC-XT or PC-AT and provides an interface between the IBM PC and transputer based systems. It has slots for up to ten TRAMs. Links 1 and 2 from each of the TRAM slots are hard wired on the IMS B008, such that the TRAMs, when plugged in, form a pipeline of processing elements. The remaining links can be "softwired" using an INMOS IMS C004 programmable link switch, incorporated on the IMS B008. This arrangement allows a large variety of networks to be created under software control.

### 1.1 Description

#### 1.1.1 Introduction

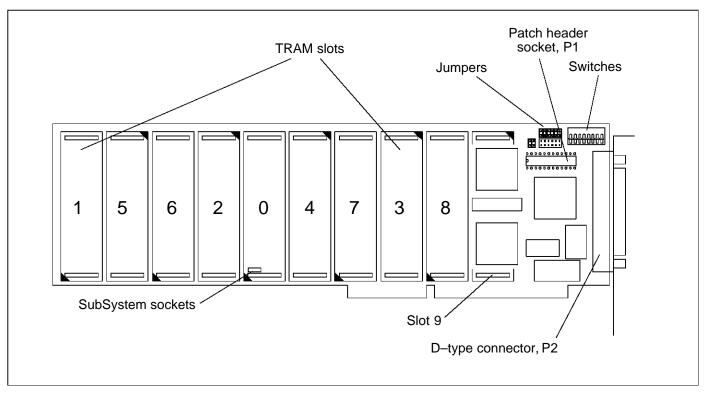

The IMS B008 is a full length PC-AT format card which which allows transputer systems to interface to the IBM PC-XT or PC-AT bus. It supports up to ten TRAMS plugged into the slots on the board which are configured into a pipeline. An IMS T225 transputer controlling an IMS C004 link switch enables networks of TRAMs to be configured under software control. A connector on the backpanel of the board gives access to links and system services allowing connections to other IMS B008 boards, or to any board compatible with the link and system service signals. The IBM PC bus interface supports DMA and interrupts. A top view of the IMS B008 is shown in figure 1.1.

Figure 1.1 Top view of IMS B008

#### 1.1.2 TRAM Slots

The IMS B008 has ten locations for TRAMs to be plugged into, called TRAM slots. Each slot can accommodate a size 1 TRAM. Larger TRAMs may be fitted, occupying more than one slot. Each of the ten slots on the IMS B008 has connections for four INMOS links. Links are numbered 0 to 3 and slots, in the case of the IMS B008, are numbered 0 to 9.

The ten slots on the IMS B008 are connected into a pipeline, using links 1 and 2 from each slot. So slot 0, link 2 is connected to slot 1, link 1; slot 1, link 2 is connected to slot 2, link 1 and so on. The two unconnected links, slot 0, link 1 and slot 9, link 2, at the ends of the slot pipeline are referred to as *pipehead* (slot 0, link 1) and *pipetail* (slot 9, link 2). *Pipetail is* taken out to the 37 way D-type connector, P2, at the back of the board.

Jumpers are provided to allow the IMS B008 to be set up as a head of a pipeline of motherboards or as a board in such a pipeline. Links 0 and 3 from each slot are connected to the IMS C004. If JP1 is fitted then C012Link is connected to slot 0, link 0, and slot 0, link 1 (Pipehead) to IMS T225, link1 (ConfigUp). If JP2 is fitted then Pipehead is connected to PatchLink1, and ConfigUp to PatchLink0. A patch header, inserted into P1, may be used instead of the jumpers, allowing other link wiring options.

In a lot of cases not all of the slots of the IMS B008 will have TRAMs fitted. Even if they are covered by a TRAM they may not be connected to it electrically. In this case to maintain the pipeline connection *pipejumpers* must be used, plugged

into each un-occupied slot, or the TRAM covering that slot. These pipejumpers connect link 1 to link 2 of the same slot. They are plugged into the pin 1 end of the TRAM slot, with the triangle marked on the corner. The pipejumpers have a mark on them which must be pointing towards the pin 1 marker triangle.

### 1.1.3 System Services

On all INMOS board products the term 'system services' refers to the collection of the reset, analyse, and error signals. On the IMS B008 the system services for the TRAM in slot 0 can be connected to either the UP system services from another board or the system services controlled by the PC bus interface. System services for the other TRAMs can be connected to the same source as TRAM 0 or to the subsystem port of TRAM 0. As shown in the block diagram the Down and Subsystem services are brought out to the 37 way D-type connector allowing this hierarchy to be extended to multi board systems.

#### 1.1.4 Link Configuration

An IMS T225 transputer and an IMS C004 link switch on the board allow the configuring of the TRAMs into different networks under software control. These networks can also extend onto multiple IMS B008s, or onto other transputer boards, by connecting the links on P2 to the links coming out to an external connector on the other boards.

The configuration information is passed to the IMS T225 either by TRAM 0 when the board is at the head of a pipe of boards or from the ConfigDown link of another board. Link 2 (ConfigDown) from the IMS T225 is taken out to the D-type connector. This allows the IMS T225 devices on all the motherboards in a system to be connected into a pipe allowing configuration information to be passed to each board. The IMS C004 can be hard reset by the IMS T225.

#### 1.1.5 IBM PC Bus Interface

The PC bus has become a de-facto standard after appearing in the IBM PC. Since then a large number of other machines have become available that incorporate the PC bus. The IMS B008 has been designed to work when plugged into either a PC/AT bus slot or a PC bus slot (but the number of options for the interrupt and Direct Memory Access (DMA) channels are reduced when plugged into a PC bus slot).

The bus interface on the IMS B008 performs four functions:

- 1 Converting the 8 bit parallel transfers on the PC bus to serial INMOS link transfers, and vice versa.

- 2 Providing a system services port.

- 3 Controlling DMA transfers.

- 4 Generating interrupts on events on the link interface, when transputer error has been asserted or on DMA transfer end.

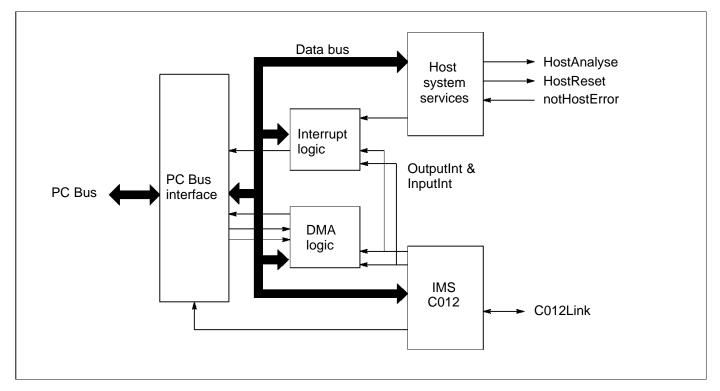

Figure 1.2 PC bus interface block diagram

A block diagram of the PC bus interface is shown in figure 1.2. To enable control of the bus interface functions from software running on the PC, the PC bus interface has a number of registers mapped into the I/O address space of the PC bus (separate from the memory address space).

#### Link interface

An IMS C012 link adaptor is used as the basis of the link interface on the IMS B008. This device performs the parallel data to serial INMOS link conversions in both directions in a similar fashion to a UART device used on an RS232 interface.

The IMS C012 has four registers which can be written to or read by the PC bus, these registers and the interface control registers occupy a 32 byte area in the address map, the base address of which can be located at 150, 200, or 300 ( HEX ). A memory map is shown in table 1.1.

| Board address            | Register                                  |

|--------------------------|-------------------------------------------|

| Board base address + #00 | IMS C012 Input data register              |

| Board base address + #01 | IMS C012 Output data register             |

| Board base address + #02 | IMS C012 Input status register            |

| Board base address + #03 | IMS C012 Output status register           |

| Board base address + #10 | Reset/Error register                      |

| Board base address + #11 | Analyse register                          |

| Board base address + #10 | Error location                            |

| Board base address + #12 | DMA request register                      |

| Board base address + #13 | Interrupt enable register                 |

| Board base address + #14 | DMA and interrupt channel select register |

Table 1.1 IMS B008 memory map

#### Host system services

A port is provided by the PC bus interface to allow software on the PC to provide 'system services' to transputers connected to the IMS B008, either as TRAMs plugged into the board or transputers on other boards. The port appears as two registers in the I/O map of the PC.

#### **DMA**

DMA logic on the IMS B008 allows data to be transferred between the PC memory and the transputer system at a faster rate than is possible using a polling scheme or interrupting on each byte transferred. DMA requests are generated when the IMS C012 is free to transmit a byte or has received a byte depending on the direction of the transfer. These DMA requests can be generated on DMA channels 0, 1, or 3 with only 1 and 3 being available on the IBM PC-XT. Control of the direction of transfer and starting of the DMA process is achieved by writing into the DMA request register.

#### Interrupts

The IMS B008 can generate an interrupt on the PC bus when one of the following events occurs:

- The end of a DMA transfer

- notHostError is asserted

- The OutputInt signal from the IMS C012 is asserted

- The InputInt signal from the IMS C012 is asserted

Generation of interrupts is enabled on a particular event when the corresponding enable bit is set in the interrupt enable register. Interrupt channels 3, 5, 11, or 15 can be driven on the PC bus selected by switches on the IMS B008.

### 1.1.6 Link Speeds

The link speeds of the TRAMs, the IMS C012, and the IMS C004 can be set to 10 or 20 Mbits/s. Link speeds for the IMS T225 link 0 can be set 5, 10, or 20 Mbits/s

### 1.2 Specifications

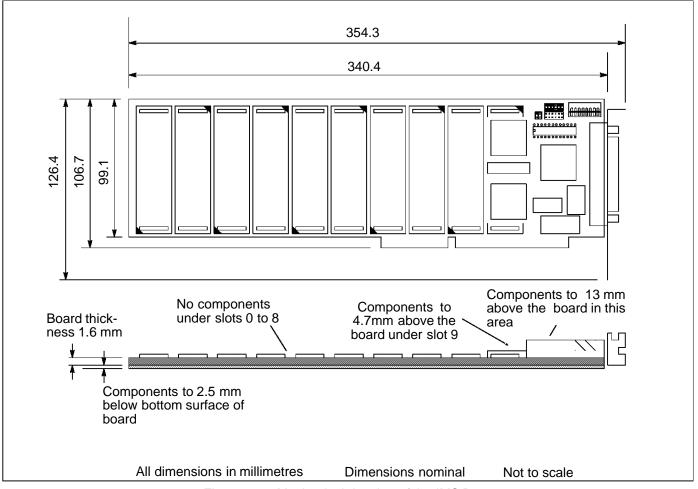

#### **Mechanical details**

The IMS B008 is a PC/AT format board and is nominally 354mm by 126mm by 22mm overall. The PCB thickness is nominally 1.6 mm. The board includes a metal PC I/O bracket through which the 37 way D-type P2 passes. This bracket serves two functions, to ensure the board is held rigidly at the edge connector end and to maintain the integrity of the shielding of the PC. To enable the bracket to perform these functions it must be securely fixed to the backpanel metalwork of the PC by a screw passing through the slot on the right hand side of the bracket, as viewed with the board towards you in the PC. A mechanical drawing of the IMS B008 is shown in figure 1.3.

The IMS B008 weighs 187g without any TRAMs or a patch header fitted.

Figure 1.3 Mechanical drawing of the IMS B008

#### **Thermal Information**

The IMS B008 with no TRAMs installed will dissipate not more than 3W.

When installing the IMS B008 in a PC consideration needs to be given to cooling airflow not only across the IMS B008 itself but also any TRAMs fitted to it. It is the responsibility of the user to ensure that the operating environment limits for the IMS B008 listed in table 1.2 are not exceeded. This will not occur as long as there are not a large number of high dissipation boards also present in the PC.

To ensure good airflow in the PC the blank backpanels should be present in any slots that are empty.

#### **Operating and Storage Environments**

The IMS B008 is designed to be operated and stored in the environments in table 1.2.

| Parameter               | Operating          | Storage            |

|-------------------------|--------------------|--------------------|

| Ambient air temperature | 0 to +50°C         | −55 to +85°C       |

| Relative Humidity       | 95% non condensing | 95% non condensing |

| Thermal Shock           | <0.08°C/s          | <0.15°C/s          |

| Altitude                | -300 to +3000m     | -300 to +16000m    |

Table 1.2 Environmental details

#### **Electrical details**

The IMS B008 only requires a +5 V dc supply which must be between 4.75V and 5.25V with less than 50mV peak-peak noise and ripple between DC and 10MHz. The IMS B008 does not incorporate protection against incorrect power

supplies. Major damage will result from connecting a supply to the board which is outside its power supply range. The IMS B008 will draw a maximum of 600mA from the +5V supply.

### 1.3 Connector Pin Assignments

### P1 pin assignments

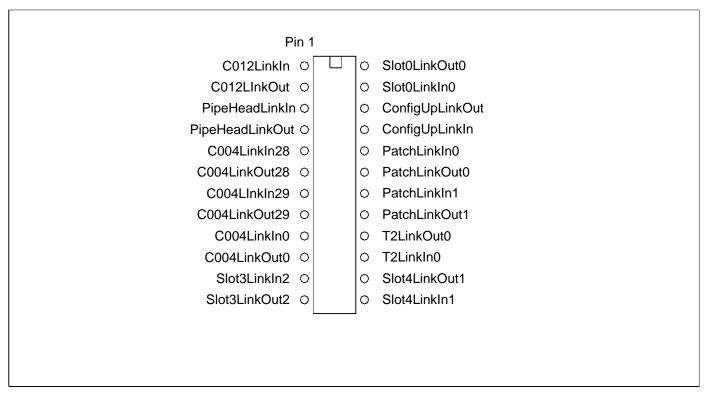

The pin numbering for this connector is same as for a standard 24 pin IC. The pin assignments are shown in figure 1.4.

Figure 1.4 P1, the patch header socket pin assignments

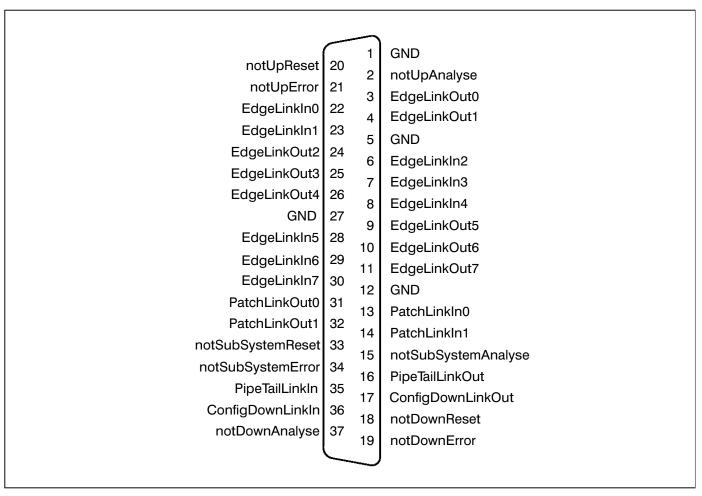

#### P2 pin assignments

Figure 1.5 Pin assignments for the 37 way D-type connector, P2

### 1.4 Jumpers

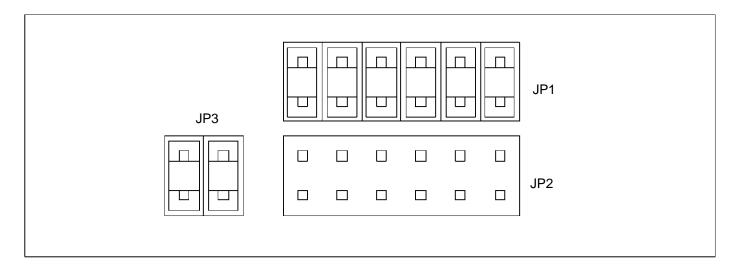

There are two 12 pin( JP1 and JP2 ) and one 4 pin ( JP3 ) jumper pin arrays on the IMS B008. Jumper sockets which connect two pins together should be installed in all positions on a pin array if a jumper is to be used. This requires six jumper sockets to be used on jumper pin arrays JP1 and JP2, and two on JP3. Fitting of jumper sockets onto the pin arrays is shown in figure 1.6. Jumpers must be fitted with their long side parallel to the backpanel of the IMS B008.

Note that the jumpers should be fitted with the small square holes in the plastic down towards the board. Use of jumpers JP1 and JP2 are mutually exclusive and the use of any of the jumpers is mutually exclusive with the use of a patch header plugged into P1. The connections made by the jumpers are shown in table 1.3.

Figure 1.6 Diagram showing the fitting of jumpers to the jumper pin arrays, jumpers shown fitted to JP1 and JP3

| Jumper pin array | Connections made when jumper sockets fitted |  |  |  |

|------------------|---------------------------------------------|--|--|--|

| JP1              | C012Link to slot 0, link 0                  |  |  |  |

|                  | slot 0, link 1 to IMS T225, link 1          |  |  |  |

|                  | IMS T225, link 0 to IMS C004, link 28       |  |  |  |

| JP2              | Pipehead to PatchLink1                      |  |  |  |

|                  | ConfigUp to PatchLink0                      |  |  |  |

|                  | slot 0, link 0 to IMS C004, link 28         |  |  |  |

| JP3              | slot 3, link 2 to slot 4, link 1            |  |  |  |

Table 1.3 Connections made by the jumper pin arrays

### 1.5 Switches

There are eight switches on the IMS B008 which select options for the PC interface, system services, and the link speeds. The functions of each of these switches is shown in tables 1.4 to 1.9.

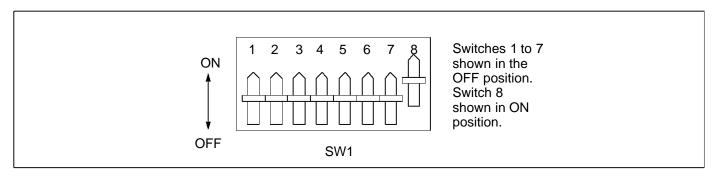

Note a switch is on when the slider is pushed towards the top of the board, away from the edge connector, as shown in figure 1.7.

Figure 1.7 Detail of switch on the IMS B008 showing the ON and OFF positions.

| Switch No. | Function                                                 |

|------------|----------------------------------------------------------|

| SW1:1      | PC bus interface enable and board base address selection |

| SW1:2      | PC bus interface enable and board base address selection |

| SW1:3      | Slot 0 and Down system services selection                |

| SW1:4      | Slots 1 to 9 system services selections                  |

| SW1:5      | Link speed selections                                    |

| SW1:6      | Link speed selections                                    |

| SW1:7      | Link speed selections                                    |

| SW1:8      | Link speed selections                                    |

Table 1.4 Switch functions when ON and OFF

| SW1:1 | SW1:2 | Board base address        |

|-------|-------|---------------------------|

| ON    | ON    | PC bus interface disabled |

| ON    | OFF   | #150                      |

| OFF   | ON    | #200                      |

| OFF   | OFF   | #300                      |

Table 1.5 Board base address and PC bus interface disable selections

| SW1:3 | TRAM slot 0 and DOWN system services |  |

|-------|--------------------------------------|--|

| ON    | From Up system services              |  |

| OFF   | From Host system services            |  |

Table 1.6 Selections for slot 0 and Down system services

| SW1:4 | TRAM slots 1 - 9 system services       |  |

|-------|----------------------------------------|--|

| ON    | From TRAM in slot 0 Subsystem services |  |

| OFF   | From Down system services              |  |

Table 1.7 System services selections for slots 1 to 9

| SW1:5 | SW1:6 | Link 0 speed | Links 1 - 3 speed | Notes |

|-------|-------|--------------|-------------------|-------|

| ON    | ON    | 10 Mbits/s   | 10 Mbits/s        |       |

| OFF   | ON    | 10 Mbits/s   | 20 Mbits/s        | 1     |

| ON    | OFF   | 20 Mbits/s   | 10 Mbits/s        | 2     |

| OFF   | OFF   | 20 Mbits/s   | 20 Mbits/s        |       |

Table 1.8 TRAM link speed selections

- 1 Note that this switch setting results in an inoperable link 3 since this link is connected to the IMS C004 which will be set to 10 Mbits/s by this setting.

- 2 This switch setting results in an inoperable link 3 since the IMS C004 will be set to a link speed of 20 Mbits/s.

| SW1:6 | SW1:7 | SW1:8 | C012 and C004<br>Link(s) | T2 Link 0  | T2 Links 1 - 3 | Notes |

|-------|-------|-------|--------------------------|------------|----------------|-------|

| ON    | ON    | ON    | 10 Mbits/s               | 10 Mbits/s | 10 Mbits/s     |       |

| ON    | ON    | OFF   | 10 Mbits/s               | 5 Mbits/s  | 10 Mbits/s     |       |

| ON    | OFF   | ON    | 10 Mbits/s               | 10 Mbits/s | 10 Mbits/s     |       |

| ON    | OFF   | OFF   | 10 Mbits/s               | 20 Mbits/s | 10 Mbits/s     |       |

| OFF   | ON    | ON    | 20 Mbits/s               | 10 Mbits/s | 5 Mbits/s      | 1     |

| OFF   | ON    | OFF   | 20 Mbits/s               | 5 Mbits/s  | 5 Mbits/s      | 1     |

| OFF   | OFF   | ON    | 20 Mbits/s               | 10 Mbits/s | 20 Mbits/s     |       |

| OFF   | OFF   | OFF   | 20 Mbits/s               | 20 Mbits/s | 20 Mbits/s     |       |

Table 1.9 IMS C012, IMS C004, and IMS T225 link speed selections

1 Note these switch settings will result in the T2 not being able to send configuration messages to the IMS C004 link switch.

#### 1.6 Reference

1 IMS B008 User Guide and Reference Manual, INMOS Limited, 1990

#### 1.7 **Ordering Information**

| Description                        | Order Number |  |  |

|------------------------------------|--------------|--|--|

| IMS B008 IBM PC Module Motherboard | IMS B008-1   |  |  |

| Associated products                |              |  |  |

| IMS S708 device driver software    | IMS S708     |  |  |

Figure 1.8 Ordering information

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1995 SGS-THOMSON Microelectronics - All Rights Reserved

), inmos, IMS, occam and DS-Link are trademarks of SGS-THOMSON Microelectronics Limited.

SGS-THOMSON Microelectronics Group.

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.