# 80386 System Software Writer's Guide

# LITERATURE SALES ORDER FORM

| NAME:                                                                                                                                      |                                                   |             |           |              |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------|-----------|--------------|

| COMPANY:                                                                                                                                   |                                                   |             |           |              |

| ADDRESS:                                                                                                                                   |                                                   |             |           |              |

| CITY:                                                                                                                                      | STATE: .                                          |             | ZIP:      |              |

| COUNTRY:                                                                                                                                   |                                                   |             |           |              |

| PHONE NO.: ()                                                                                                                              |                                                   |             |           |              |

| ORDER NO. TI                                                                                                                               | TLE                                               | QTY.        | PRICE     | TOTAL        |

|                                                                                                                                            |                                                   | ×           | =         |              |

|                                                                                                                                            |                                                   | ×           | =         |              |

|                                                                                                                                            |                                                   | ×           | =         |              |

|                                                                                                                                            |                                                   | ×           | =         |              |

|                                                                                                                                            |                                                   | ×           | =         |              |

|                                                                                                                                            |                                                   | ×           | =         |              |

|                                                                                                                                            |                                                   | ×           | =         | · .          |

|                                                                                                                                            |                                                   | ×           | =         |              |

|                                                                                                                                            |                                                   | ×           | =         |              |

|                                                                                                                                            |                                                   | ×           | =         |              |

|                                                                                                                                            |                                                   | ;           | Subtotal  |              |

|                                                                                                                                            |                                                   | Must Add    | d Your    |              |

|                                                                                                                                            |                                                   | Local Sa    | ales Tax  |              |

| Must add appropriate postage to subtotal (10% U.S. and Canada, 20% all other)                                                              |                                                   | <del></del> | Postage   |              |

|                                                                                                                                            |                                                   |             | Total     |              |

| Pay by Visa, MasterCard, American Express, to Intel Literature Sales. Allow 2-4 weeks for ☐ Visa ☐ MasterCard ☐ American Expre Account No. | delivery.                                         |             |           | rder payable |

| Signature:                                                                                                                                 |                                                   |             |           |              |

|                                                                                                                                            |                                                   |             | o the LLC | and Canada   |

| Mail To: Intel Literature Sales P.O. Box 58130                                                                                             | International Custome<br>should contact their loc |             |           |              |

listed in the back of most Intel literature.

European Literature Order Form in back of book.

Call Toll Free: (800) 548-4725 for phone orders

Santa Clara, CA

95052-8130

Mail To: Intel Literature Sales P.O. Box 58130 Santa Clara, CA 95052-8130

# **CUSTOMER SUPPORT**

#### CUSTOMER SUPPORT

Customer Support is Intel's complete support service that provides Intel customers with hardware support, software support, customer training, and consulting services. For more information contact your local sales offices.

After a customer purchases any system hardware or software product, service and support become major factors in determining whether that product will continue to meet a customer's expectations. Such support requires an international support organization and a breadth of programs to meet a variety of customer needs. As you might expect, Intel's customer support is quite extensive. It includes factory repair services and worldwide field service offices providing hardware repair services, software support services, customer training classes, and consulting services.

#### HARDWARE SUPPORT SERVICES

Intel is committed to providing an international service support package through a wide variety of service offerings available from Intel Hardware Support.

#### SOFTWARE SUPPORT SERVICES

Intel's software support consists of two levels of contracts. Standard support includes TIPS (Technical Information Phone Service), updates and subscription service (product-specific troubleshooting guides and COMMENTS Magazine). Basic support includes updates and the subscription service. Contracts are sold in environments which represent product groupings (i.e., iRMX environment).

#### CONSULTING SERVICES

Intel provides field systems engineering services for any phase of your development or support effort. You can use our systems engineers in a variety of ways ranging from assistance in using a new product, developing an application, personalizing training, and customizing or tailoring an Intel product to providing technical and management consulting. Systems Engineers are well versed in technical areas such as microcommunications, real-time applications, embedded microcontrollers, and network services. You know your application needs; we know our products. Working together we can help you get a successful product to market in the least possible time.

#### CUSTOMER TRAINING

Intel offers a wide range of instructional programs covering various aspects of system design and implementation. In just three to ten days a limited number of individuals learn more in a single workshop than in weeks of self-study. For optimum convenience, workshops are scheduled regularly at Training Centers worldwide or we can take our workshops to you for on-site instruction. Covering a wide variety of topics, Intel's major course categories include: architecture and assembly language, programming and operating systems, bitbus and LAN applications.

|  |  | • |

|--|--|---|

|  |  |   |

|  |  |   |

# 80386 SYSTEM SOFTWARE WRITER'S GUIDE

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

Above, BITBUS, COMMputer, CREDIT, Data Pipeline, FASTPATH, Genius, i,  $\stackrel{\uparrow}{\Lambda}$ , ICE, iCEL, iCS, iDBP, iDIS, I²ICE, iLBX, i $_m$ , iMDDX, iMMX, Inboard, Insite, Intel, intel, intel, intel, S, Intel Certified, Intelevision, inteligent Identifier, inteligent Programming, Intellec, Intellink, iOSP, iPDS, iPSC, iRMK, iRMX, iSBC, iSBX, iSDM, iSXM, KEPROM, Library Manager, MAPNET, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, MultiSERVER, ONCE, OpenNET, OTP, PC BUBBLE, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Quick-Pulse Programming, Ripplemode, RMX/80, RUPI, Seamless, SLD, SugarCube, SupportNET, UPI, and VLSiCEL, and the combination of ICE, iCS, iRMX, iSBC, iSBX, iSXM, MCS, or UPI and a numerical suffix, 4-SITE.

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 58130 Santa Clara, CA 95052-8130

©INTEL CORPORATION 1988 CG-1/18/88

# **PREFACE**

The 80386 System Software Writer's Guide describes the interface between the 80386 system architecture and low-level operating system mechanisms. It does not discuss operating system policy issues or operating system facilities that are independent of a processor's architecture. For example, the book shows how an operating system can use the 80386's task switch instruction to dispatch a new task (process), but it does not discuss the many policies an operating system could adopt for selecting the task to be dispatched. To cite another example, the 80386 System Software Writer's Guide covers the 80386's facilities for device input/output, but leaves the discussion of file I/O to operating system textbooks.

## **AUDIENCE**

This book has been written primarily for the systems programmer who is developing an operating system for the 80386 microprocessor. Programmers writing other systems software, such as linkers and utilities, may also benefit from reading this book. The book can also be valuable to anyone who wants to see how 80386 architectural facilities support common operating system mechanisms.

To use this book successfully, you must be thoroughly familiar with multitasking operating systems.

## **RELATED PUBLICATIONS**

The 80386 System Software Writer's Guide is one of four Intel publications that describe the 80386 microprocessor. The others are

- Introduction to the 80386, Order No. 231252

- 80386 Programmer's Reference Manual, Order No. 230985

- 80386 Hardware Reference Manual, Order No. 231298

The 80386 System Software Writer's Guide can be read independently of the 80386 Hardware Reference Manual. The Introduction to the 80386 is a prerequisite to this book and the 80386 Programmer's Reference Manual is a companion to it.

Before reading this book you should thoroughly understand the material in the *Introduction* to the 80386, especially Chapters 2 (Application Architecture) and 3 (System Architecture). If you are interested in running 8086 or 80286 programs on the 80386, you need to read Chapter 4 (Architectural Compatibility) as well. Before reading this book you should browse through the 80386 Programmer's Reference Manual and you should keep it handy while reading the 80386 System Software Writer's Guide. The 80386 System Software Writer's Guide frequently simplifies the presentation of architectural features in order to more clearly show how these features relate to operating system mechanisms. When you want the definitive description of any 80386 facility, consult the 80386 Programmer's Reference Manual.

Some examples in this guide are written in ASM386, Intel's 80386 assembly language, documented in the ASM386 Assembly Language Reference Manual, Order No. 122332.

# **HOW TO READ THIS BOOK**

The ten chapters of the 80386 System Software Writer's Guide are generally arranged so that the most specialized topics are covered at the end of the guide. The first seven chapters describe the 80386's protected 32-bit operation, the mode of operation most likely to be selected for new 80386 applications. Features that make the 80386 compatible with earlier Intel 86 family processors are described in Chapters 8 and 9, while Chapter 10 describes one way to implement the UNIX System V operating system on the 80386.

Chapters 1 and 2 describe tasking and memory management. These topics are very closely related and you will find frequent references in the first chapter to the second. Having read the *Introduction to the 80386*, however, most readers should understand enough about the 80386's memory management facilities to ignore these inevitable forward references. The third chapter covers interrupts and their close relatives, exceptions. Chapter 4 describes how operating system calls can be implemented on the 80386. Chapter 5 describes the 80386's input/output facilities. The first five chapters describe the 80386 as if it were already running in protected 32-bit mode, with all architecture-defined data structures (for example, page tables) in place. Chapter 6 tells you how to take the 80386 from a hardware RESET to protected 32-bit operation.

The last four chapters cover specialized topics and can be read selectively. Chapter 7 describes the interaction between an 80386 operating system and the 80287 and 80387 numerics coprocessors (or their software emulators). Chapters 8 and 9 describe 80386 facilities for running existing 80286 and 8086 software. The final chapter is an extended example that describes one way to implement the UNIX System V operating system on the 80386.

Note that the code examples given in this book have not been tested.

įν

| CHAPTER 1                                         | Page |

|---------------------------------------------------|------|

| TASKS                                             |      |

| 1.1 The Task Execution Environment                | 1-1  |

| 1.2 Task State Segments and Descriptors           | 1-1  |

| 1.3 Task Creation                                 | 1-4  |

| 1.4 Task Termination                              | 1-5  |

| 1.5 Task Switching                                | 1-6  |

|                                                   |      |

| CHAPTER 2                                         |      |

| MEMORY MANAGEMENT                                 |      |

| 2.1 Segmentation                                  | 2-1  |

| 2.1.1 Required Segments                           | 2-2  |

| 2.1.2 Segmentation Models                         | 2-2  |

| 2.1.3 Defining Segments                           | 2-4  |

| 2.1.3.1 Descriptors                               | 2-4  |

| 2.1.3.2 Descriptor Tables                         | 2-4  |

| 2.1.4 Aliases                                     | 2-6  |

| 2.1.5 Sharing                                     | 2-8  |

| 2.1.6 Protection                                  | 2-8  |

| 2.1.6.1 Type and Rights                           | 2-8  |

| 2.1.6.2 Limit                                     | 2-9  |

| 2.1.6.3 Expand-Down Segments                      | 2-10 |

| 2.1.6.4 Privilege                                 | 2-13 |

| 2.1.7 Other Attributes                            | 2-14 |

| 2.1.8 Building Descriptors                        | 2-14 |

| 2.2 Paging                                        | 2-15 |

| 2.2.1 Relationship of Segments and Pages          | 2-16 |

| 2.2.2 Page Table and Page Directory Entries       | 2-17 |

| 2.2.3 Aliases                                     | 2-19 |

| 2.2.4 Sharing                                     | 2-19 |

| 2.2.5 Protection Attributes                       | 2-21 |

| 2.2.5.1 Privilege                                 | 2-21 |

| 2.2.5.2 Rights                                    | 2-21 |

| 2.2.6 Other Attributes                            | 2-22 |

| 2.2.7 Translation Lookaside Buffer Considerations | 2-22 |

| 2.3 Virtual Memory                                | 2-23 |

| 2.3.1 Demand Segmentation                         | 2-23 |

| 2.3.2 Demand Paging                               | 2-25 |

| 2.3.2.1 Handling Page Faults                      | 2-25 |

| 2.3.2.2 Replacing Pages                           | 2-26 |

| 2.4 Examples                                      | 2-27 |

| 2.4.1 A Flat Memory Design                        | 2-27 |

| 2.4.2 A Paged Memory Design                       | 2-34 |

# intel

| 0.4.0. A Companied Mamony Design                    | Page |

|-----------------------------------------------------|------|

| 2.4.3 A Segmented Memory Design                     | 2-35 |

| 2.4.4 A Hybrid Memory Design                        | 2-38 |

| CHAPTER 3                                           |      |

| INTERRUPTS AND EXCEPTIONS                           |      |

| 3.1 Interrupt Descriptor Table                      | 3-1  |

| 3.2 Interrupt and Exception Handlers                | 3-2  |

| 3.2.1 Procedures versus Tasks                       | 3-2  |

| 3.2.2 Procedure-Based Handlers                      | 3-3  |

| 3.2.3 Task-Based Handlers                           | 3-5  |

| 3.2.4 Memory Residency                              | 3-7  |

| 3.3 Exception Handling Guidelines                   | 3-8  |

| 3.3.1 Invalid Opcode Fault, Number 6                | 3-9  |

| 3.3.2 Device Not Available Fault, Number 7          | 3-9  |

| 3.3.3 Double Fault, Number 8                        | 3-10 |

| 3.3.4 Processor Extension Segment Overrun, Number 9 | 3-10 |

| 3.3.5 Invalid TSS Fault, Number 10                  | 3-11 |

| 3.3.6 Segment Fault, Number 11                      | 3-11 |

| 3.3.7 Stack Fault, Number 12                        | 3-11 |

| 3.3.8 General Protection Fault, Number 13           | 3-11 |

| 3.3.9 Page Fault, Number 14                         | 3-12 |

| 3.3.10 Coprocessor Error Fault, Number 16           | 3-12 |

| C.O. TO COPIOCOCCO EITOI T dait, Hambor To          | 0 12 |

| CHAPTER 4                                           |      |

| SYSTEM CALLS                                        |      |

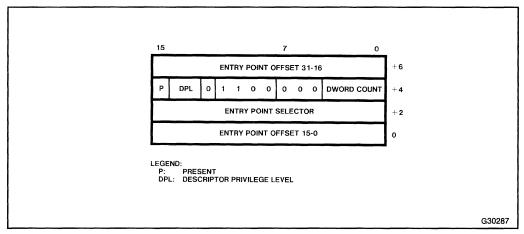

| 4.1 Call Gates                                      | 4-1  |

| 4.1.1 How Many Gates?                               | 4-2  |

| 4.1.2 Controlling Access                            | 4-2  |

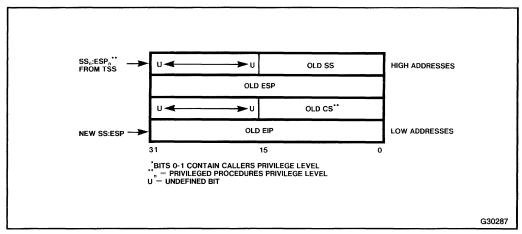

| 4.1.3 Switching Privilege Levels and Stacks         | 4-3  |

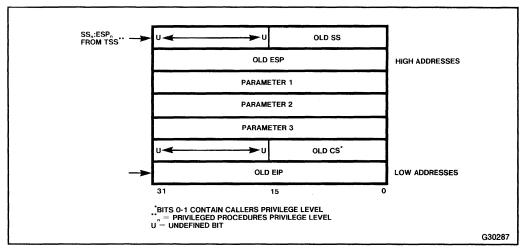

| 4.1.4 Passing Parameters                            | 4-3  |

| 4.2 Trap Gates                                      | 4-5  |

| 4.3 Segmented Pointer Validation                    | 4-6  |

| 4.4 Calling Less-Privileged Procedures              | 4-7  |

| CHAPTER 5                                           |      |

| INPUT/OUTPUT                                        |      |

| 5.1 Programmed I/O                                  | E 4  |

|                                                     | 5-1  |

| 5.1.1 I/O-Mapped I/O                                | 5-1  |

| 5.1.2 Memory-Mapped I/O                             | 5-1  |

| 5.2 IOPL and the I/O Permission Map                 | 5-2  |

| 5.2.1 Protecting I/O-Mapped Devices                 | 5-2  |

| 5.2.2 Device Driver Privilege                       | 5-4  |

| 5.3 Direct I/O                                      | 5-5  |

|                                                    | Page       |

|----------------------------------------------------|------------|

| 5.3.1 Physical Addressing                          | 5-5        |

| 5.3.2 Locking Segments and Pages                   | 5-5        |

|                                                    |            |

| CHAPTER 6                                          |            |

| INITIALIZATION                                     |            |

| 6.1 Entering Protected Mode                        | 6-1        |

| 6.2 Enabling Paging                                | 6-4        |

| 6.3 Switching to the Initial Task                  | 6-7        |

| CHAPTER 7                                          |            |

| NUMERICS                                           |            |

| 7.1 Supporting a Coprocessor                       | 7-1        |

| 7.1.1 Initialization                               | 7-1        |

| 7.1.2 Exceptions                                   | 7-8        |

| 7.1.2.1 Coprocessor Context Switching              | 7-8        |

| ·                                                  | 7-8<br>7-9 |

| 7.1.2.2 Coprocessor Error                          |            |

| 7.1.2.3 Simultaneous Exceptions                    | 7-10       |

| 7.1.3 Coprocessor Differences                      | 7-10       |

| 7.2 Supporting an Emulator                         | 7-10       |

| 7.2.1 Initialization                               | 7-11       |

| 7.2.2 Exceptions                                   | 7-11       |

| CHAPTER 0                                          |            |

| CHAPTER 8                                          |            |

| 80286 COMPATIBILITY                                | 0.4        |

| 8.1 Running an 80286 Operating System              | 8-1        |

| 8.2 Running 80286 and 80386 Programs Concurrently  | 8-2        |

| 8.2.1 Basic Operating System Support               | 8-2        |

| 8.2.2 Handling Mixed System Calls                  | 8-3        |

| 8.2.2.1 System Call Adapters                       | 8-3        |

| 8.2.2.2 Parameter Passing                          | 8-4        |

| 8.2.2.3 Parameter Conversion                       | 8-4        |

| CHAPTER 9                                          |            |

| 8086 COMPATIBILITY                                 |            |

| 9.1 Common Elements of Real and Virtual 8086 Modes | 9-1        |

| 9.1.1 Instruction Set                              | 9-1        |

| 9.1.2 Pseudodescriptors                            | 9-2        |

| 9.2 Real Mode                                      | 9-3        |

| 9.3 Virtual 8086 Mode                              | 9-5        |

| 9.3.1 Virtual Machine Monitors                     | 9-6        |

| 9.3.2 Task Management                              | 9-6        |

| 9.3.3 Memory Management                            | 9-9        |

| 9.3.4 Interrupts and Exceptions                    | 9-10       |

| 9.3.4.1 Handler Considerations                     | 9-10       |

| 0.0,7,1   Handid Otholadiono                       | 0 10       |

# intel

|                                              | Page  |

|----------------------------------------------|-------|

| 9.3.4.2 Interrupt Enable Flag Considerations | 9-10  |

| 9.3.4.3 Simulating Interrupts                | 9-11  |

| 9.3.5 System Calls                           | 9-11  |

| 9.3.6 Input/Output                           |       |

|                                              |       |

| CHAPTER 10                                   |       |

| A UNIX SYSTEM IMPLEMENTATION                 |       |

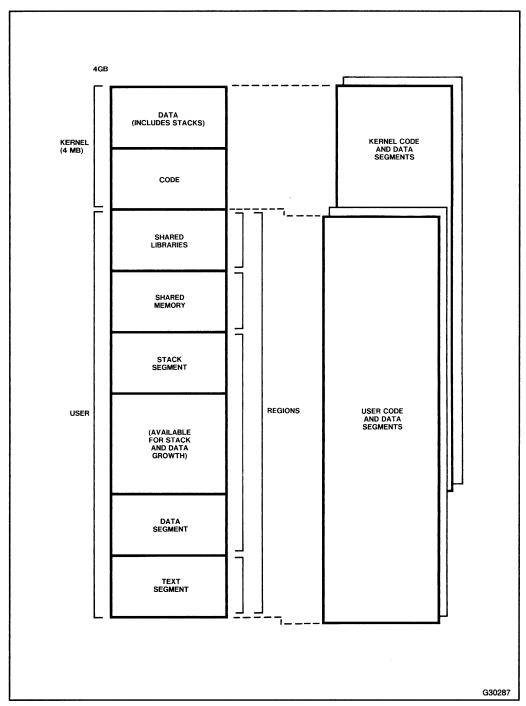

| 10.1 U/386 Implementation Philosophy         | 10-1  |

| 10.2 Process and Memory Overview             | 10-1  |

| 10.3 Processes                               |       |

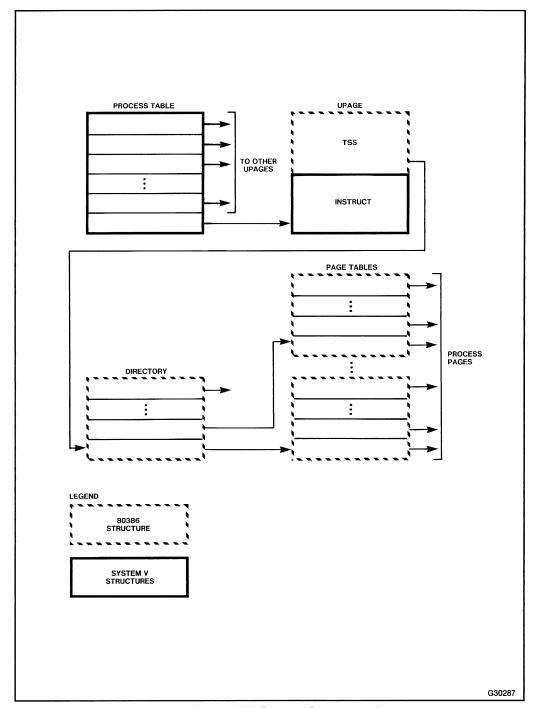

| 10.3.1 Representing a Process                | 10-5  |

| 10.3.2 Forking a Child Process               | 10-5  |

| 10.3.3 Executing a New Program               | 10-8  |

| 10.3.4 Process Switching                     | 10-8  |

| 10.3.5 Process Termination                   | 10-8  |

| 10.4 Memory Management                       | 10-9  |

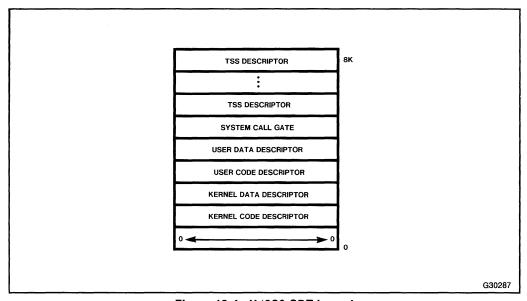

| 10.4.1 Descriptor Tables                     |       |

| 10.4.2 Directories and Page Tables           |       |

| 10.4.3 Managing the Stack and the Heap       |       |

| 10.4.4 Protection                            |       |

| 10.4.5 Sharing                               |       |

| 10.4.6 Virtual Memory                        |       |

| 10.4.7 Locking                               | 10-16 |

| 10.5 System Calls                            |       |

| 10.6 Interrupts and Exceptions               |       |

| 10.6.1 Interrupts                            |       |

| 10.6.2 Blocking Interrupts in the Kernel     |       |

| 10.6.3 Exceptions                            |       |

| 10.7 Input/Output                            |       |

| 10.8 Numerics                                |       |

| 10.9 Debug Support                           |       |

|                                              |       |

| Figures                                      |       |

| i iguico                                     |       |

| Figure Title                                 | Page  |

|                                              | _     |

| 1-1 Task Execution Environment               |       |

| 1-2 Task State Segment                       |       |

| 1-3 Task State Segment Descriptor            |       |

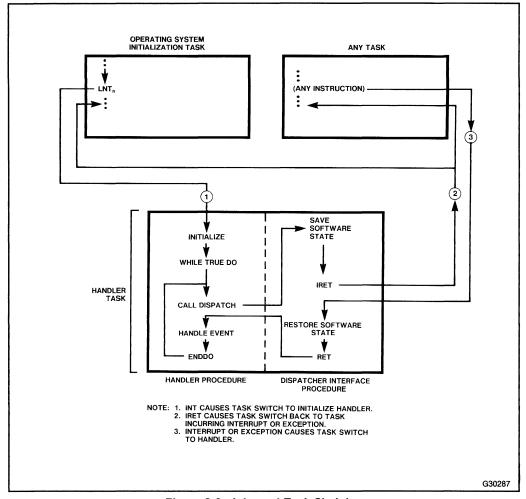

| 1-4 Example Dispatcher                       |       |

| 2-1 Code and Data Segment Descriptors        |       |

| 2-2 Alias Table                              | 2-7   |

# intel®

# TABLE OF CONTENTS

| Figure | Title                                              | Page  |

|--------|----------------------------------------------------|-------|

| 2-3    | Intrastack References                              | 2-11  |

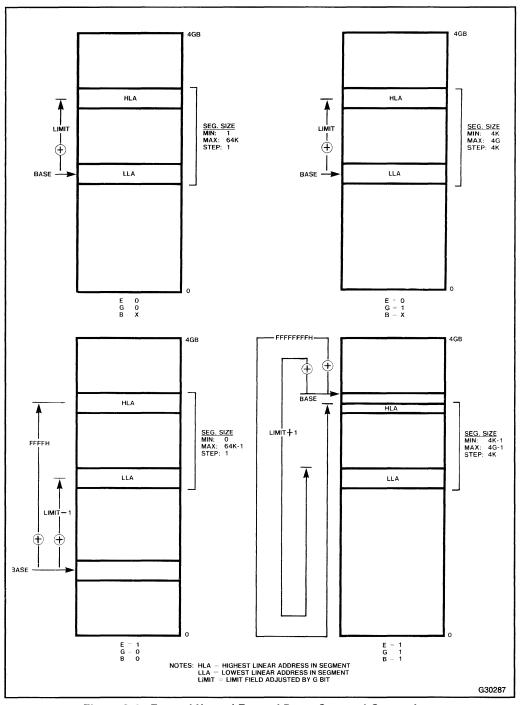

| 2-4    | Expand-Up and Expand-Down Segment Comparison       | 2-12  |

| 2-5    | Storing Descriptor Fields                          | 2-14  |

| 2-6    | Building a Descriptor                              | 2-15  |

| 2-7    | Extracting a Descriptor's Base Address             | 2-15  |

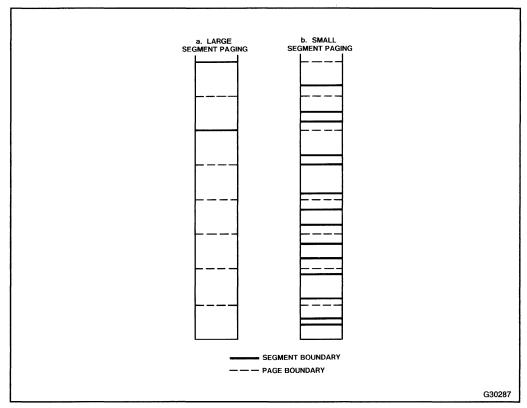

| 2-8    | Two Ways to Map Segments to Pages                  | 2-16  |

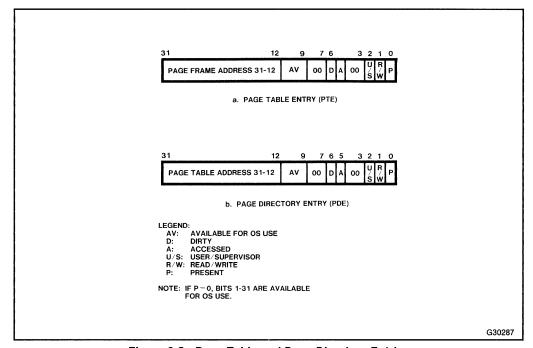

| 2-9    | Page Table and Page Directory Entries              | 2-17  |

| 2-10   | Example Page Table Addressing Convention           | 2-20  |

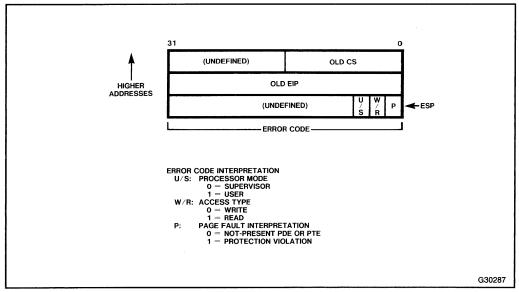

| 2-11   | Page Fault Handler Stack                           | 2-26  |

| 2-12   | F/386 Linear Space Map                             | 2-28  |

| 2-13   | Flat Mode Initialization Code                      | 2-29  |

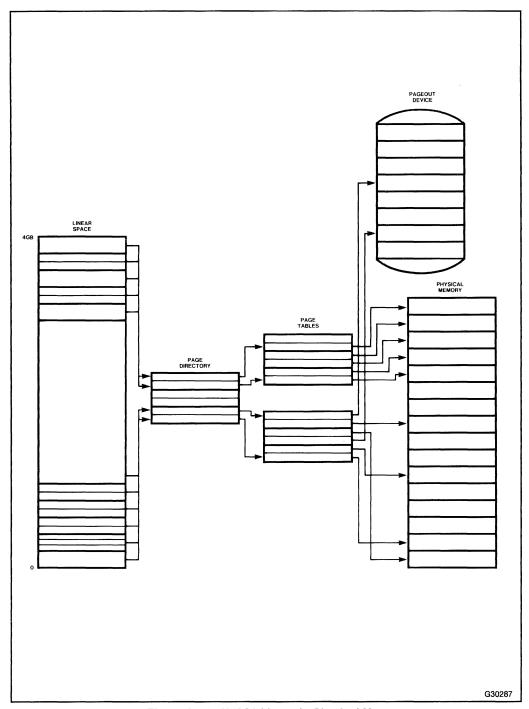

| 2-14   | P/386 Linear Space Map                             | 2-34  |

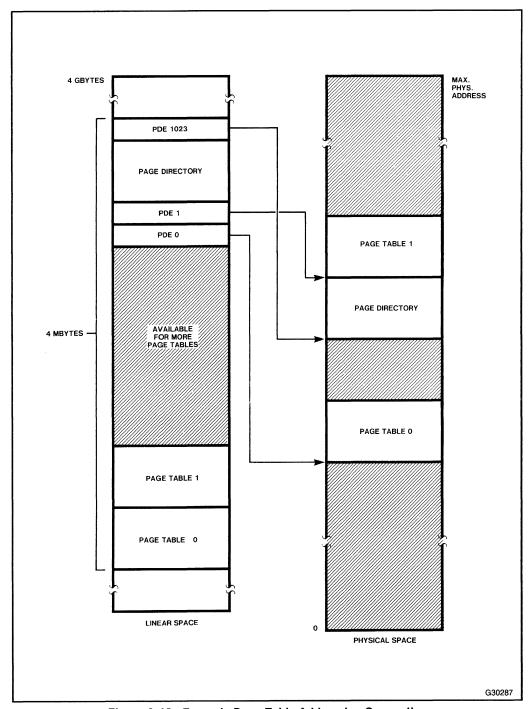

| 2-15   | P/386 Linear-to-Physical Map                       | 2-36  |

| 2-16   | S/386 Linear Space Map                             | 2-37  |

| 2-17   | H/386 Linear-to-Physical Map                       | 2-39  |

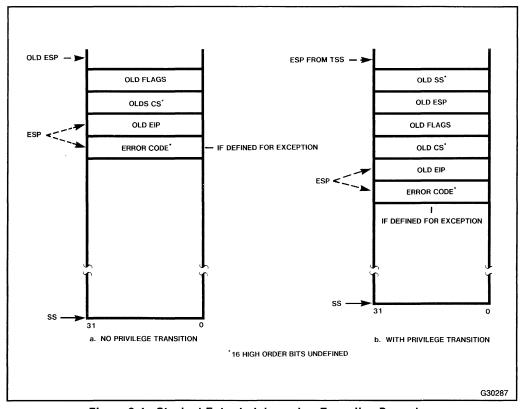

| 3-1    | Stack at Entry to Interrupt or Exception Procedure | 3-4   |

| 3-2    | Interrupt Task Skeleton                            | 3-7   |

| 3-3    | Error Code Format                                  | 3-10  |

| 4-1    | Call Gate                                          | 4-1   |

| 4-2    | Stack at Entry to Privileged Procedure             | 4-4   |

| 4-3    | Parameters Copied to Privileged Procedure          | 4-5   |

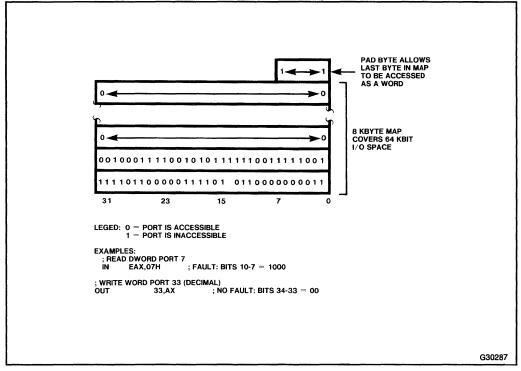

| 5-1    | I/O Permission Map Structure and Operation         | 5-3   |

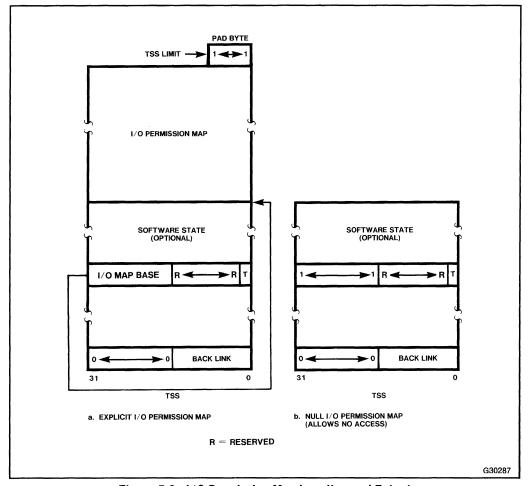

| 5-2    | I/O Permission Map Location and Extent             | 5-4   |

| 6-1    | Entering Protected Mode (Part 1)                   | 6-3   |

| 6-2    | Entering Protected Mode (Part 2)                   | 6-4   |

| 6-3    | Entering Protected Mode (Part 3)                   | 6-5   |

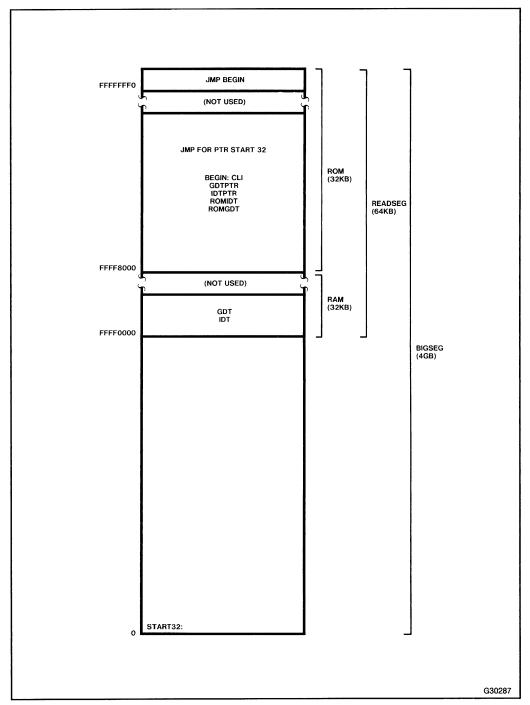

| 6-4    | Entering Protected Mode Program Layout             | 6-6   |

| 7-1    | Probing for an 80287                               | 7-2   |

| 7-2    | Switching the Coprocessor Context                  | 7-9   |

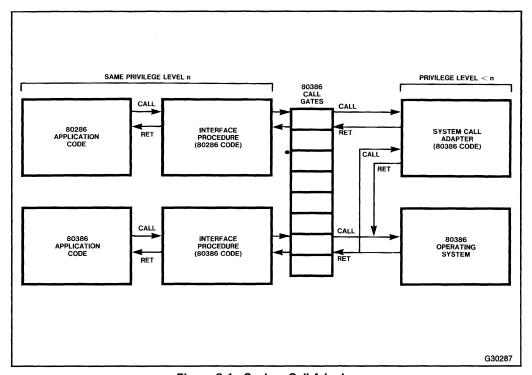

| 8-1    | System Call Adapter                                | 8-3   |

| 9-1    | Switching to Real Mode                             | 9-4   |

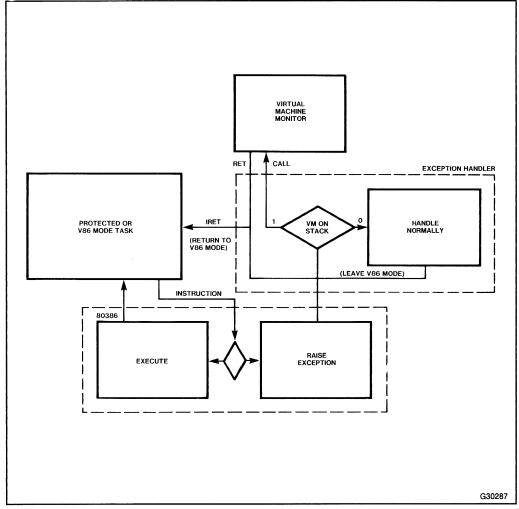

| 9-2    | Invoking a Virtual Machine Monitor                 | 9-7   |

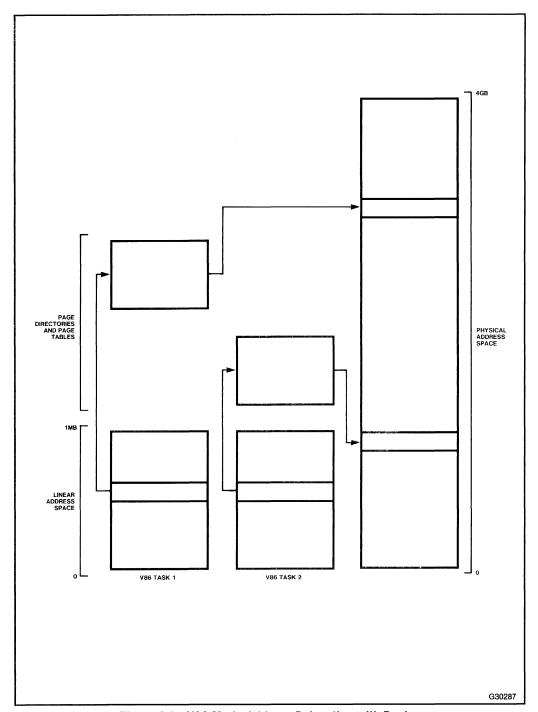

| 9-3    | V86 Mode Address Relocation with Paging            | 9-8   |

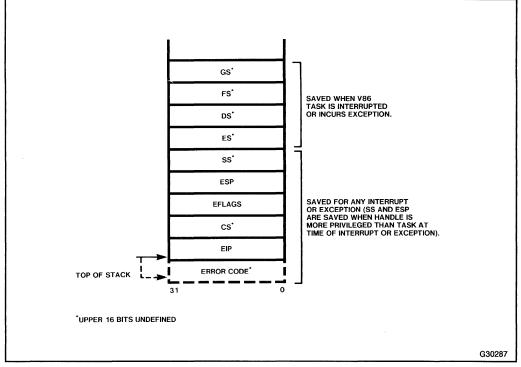

| 9-4    | Handler's Stack after V86 Interrupt or Exception   | 9-9   |

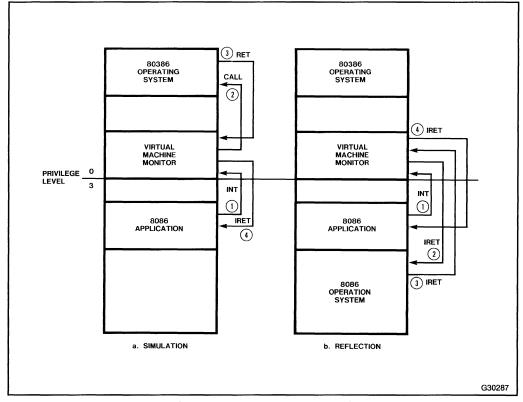

| 9-5    | Simulating and Reflecting V86 System Calls         | 9-12  |

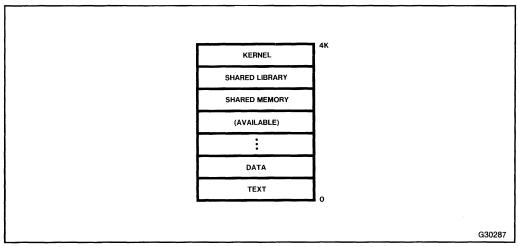

| 10-1   | U/386 Linear Address Space Snapshot                | 10-3  |

| 10-2   | U/386 Process Representation                       | 10-6  |

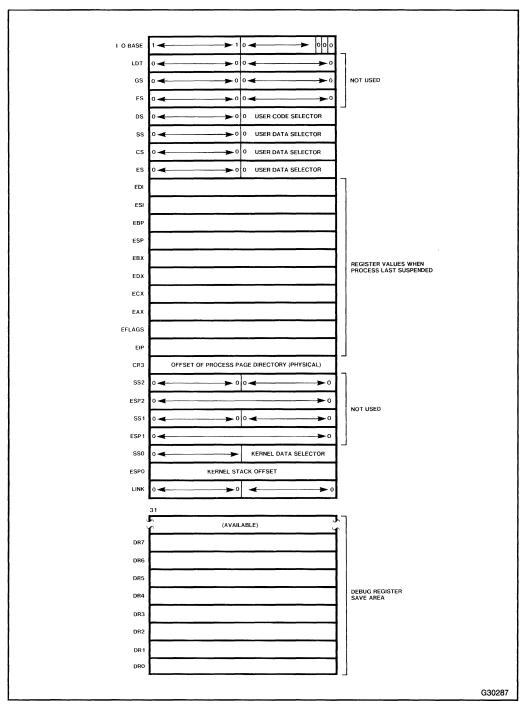

| 10-3   | U/386 Process TSS                                  | 10-7  |

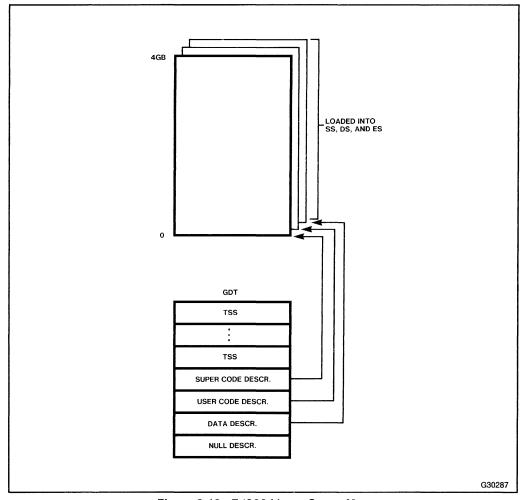

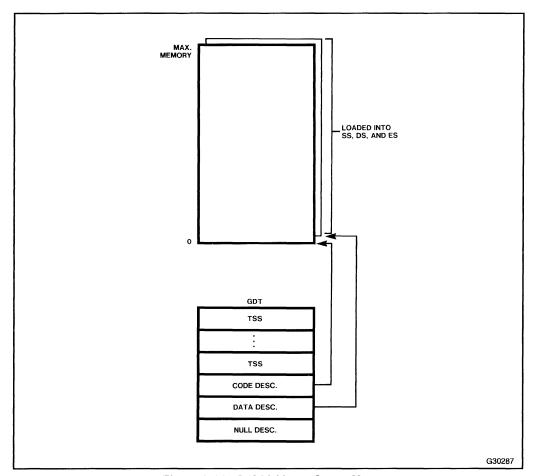

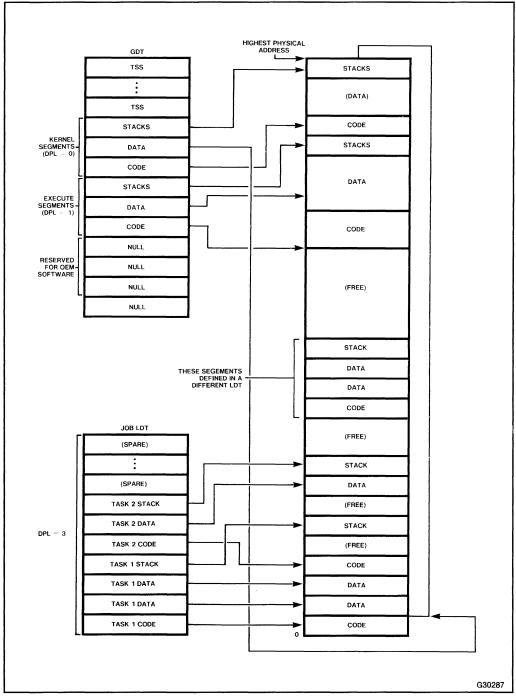

| 10-4   | U/386 GDT Layout                                   | 10-9  |

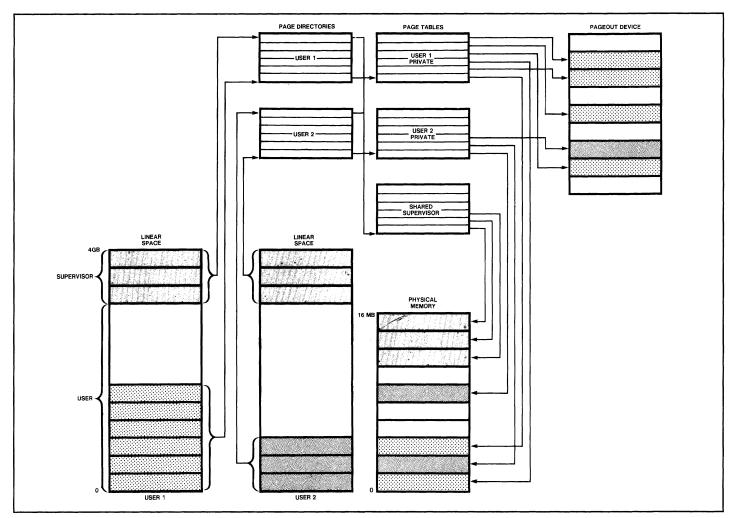

| 10-5   | U/386 Kernel Data Segment                          | 10-11 |

| 10-6   | Typical U/386 Process Page Directory               | 10-12 |

| Figure                        | Title                                                                                                                                     | Page                             |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

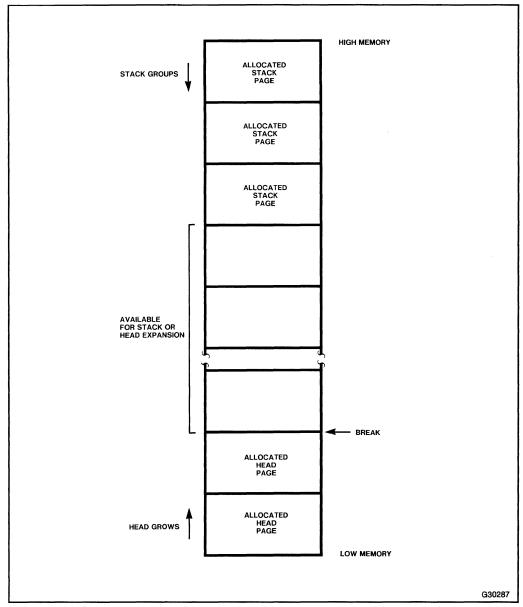

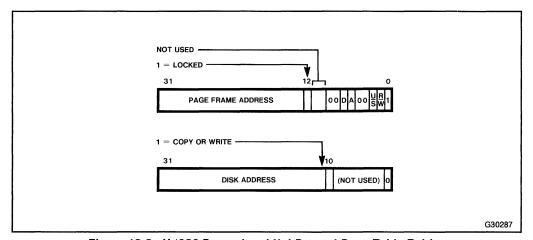

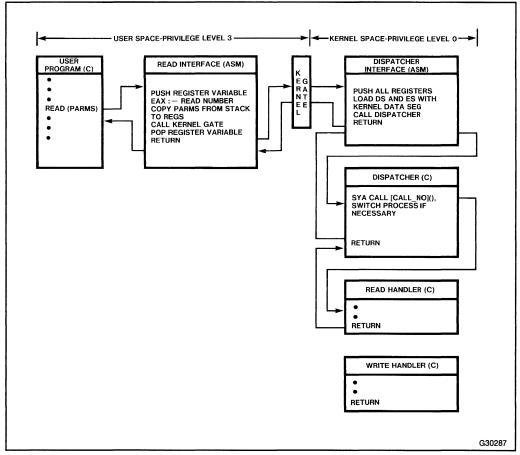

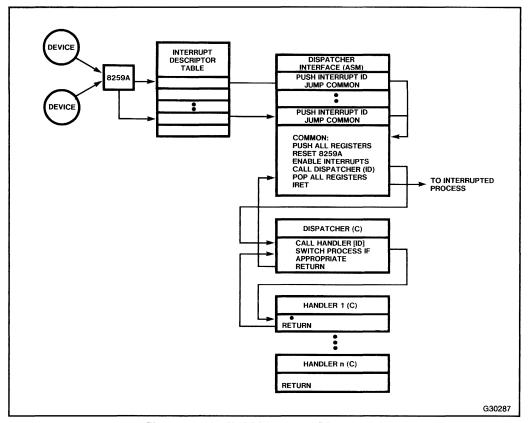

| 10-7<br>10-8<br>10-9<br>10-10 | U/386 Stack and Heap Expansion U/386 Present and Not-Present Page Table Entries U/386 System Call Dispatching U/386 Interrupt Dispatching | 10-13<br>10-15<br>10-17<br>10-19 |

|                               | Tables                                                                                                                                    |                                  |

| Table                         | Title                                                                                                                                     | Page                             |

| 2-1                           | Page Table Addressing Examples                                                                                                            | 2-21                             |

| 2-2                           | Not-Present Segment Fault Conditions                                                                                                      | 2-24                             |

| 6-1                           | Registers Following RESET                                                                                                                 | 6-2                              |

| 7-1                           | EM and MP Bit Interpretation                                                                                                              | 7-7                              |

| 9-1                           | Real and Virtual 8086 Mode Instruction Execution                                                                                          | 9-1                              |

| 9-2                           | Pseudodescriptor Attributes                                                                                                               | 9-2                              |

| 10-1                          | U/386 Kernel Segment Descriptors                                                                                                          | 10-10                            |

| 10-2                          | U/386 User Segment Descriptors                                                                                                            | 10-10                            |

| 10-3                          | U/386 Page Directory Entry Attributes                                                                                                     | 10-12                            |

| 10-4                          | U/386 Call Gate Attributes                                                                                                                | 10-18                            |

| 10-5                          | U/386 Kernel Exception Handling                                                                                                           | 10-20                            |

Tasks 1

# CHAPTER 1 TASKS

The 80386 is fundamentally a multitasking computer. Although the processor can be used in single task systems, most facilities of its system architecture are designed to support the concurrent execution of multiple tasks. For example, memory management, protection, and exception handling are all task-based. The 80386 can perform a task switch (context switch) upon direction from the operating system or automatically in response to an interrupt or exception. This chapter describes the 80386 facilities that an operating system can use to create and manage tasks; those aspects of tasking that relate to interrupt and exception handling are described in Chapter 3.

# 1.1 THE TASK EXECUTION ENVIRONMENT

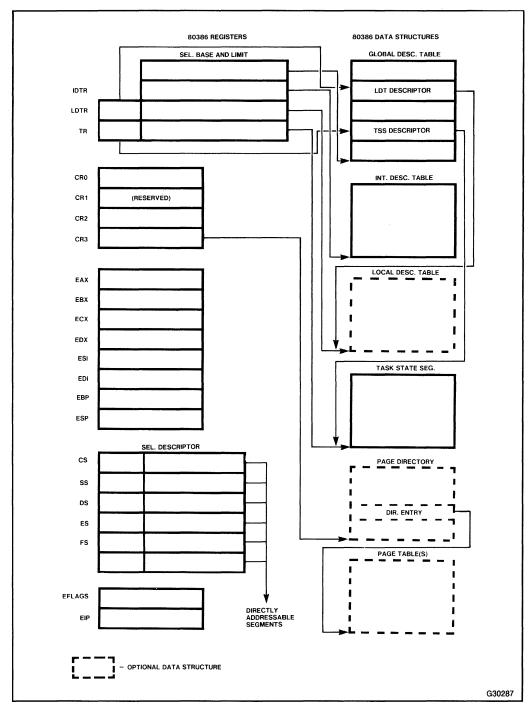

Figure 1-1 shows the architecture-defined registers and data structures that an 80386 task may use during its execution. Most of the data structures shown in Figure 1-1 are more closely related to interrupt handling and memory management than task management and are therefore described in later chapters. The task state segment (TSS), however, is central to task management and is the principal subject of this chapter.

# 1.2 TASK STATE SEGMENTS AND DESCRIPTORS

The state of a task can be considered in two parts: the *machine state*, consisting mainly of register values, and the *software state*, consisting of file descriptors, scheduling parameters, and other operating system-defined data. A multitasking operating system traditionally records each task's machine state and software state in a "task control block" or a similarly named record (or collection of records).

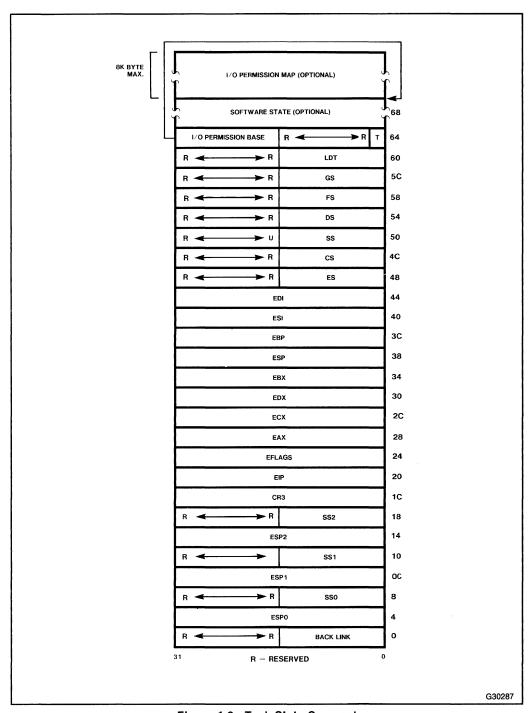

The 80386 system architecture defines a record that holds the machine state of a task. This record is called a task state segment and is illustrated in Figure 1-2. The operating system initializes the TSS of a new task, but the 80386 maintains the TSS, reading and writing it on task switches and reading it on privilege level changes. The 80386 specifies the format of only the first 26 double words, and, optionally, up to the last 8K bytes (the I/O Bit-map for the 64K I/O address space) of the TSS. An operating system is free to use the area between the I/O Bit-map and the TSS core (first 26 double words) to record a task's software state.

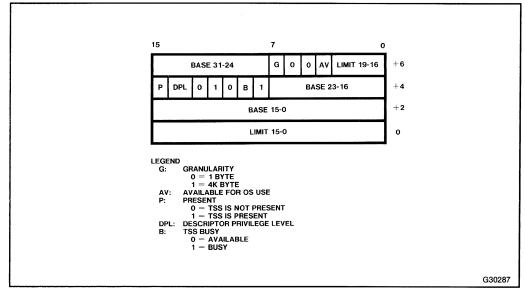

Because a TSS is an 80386-defined segment, it must have a descriptor. Figure 1-3 shows the format of an 80386 TSS descriptor. The base, limit, granularity, available, present, and descriptor privilege level fields are identical to their code and data segment descriptor counterparts (these are described in Chapter 2). Note that the TSS limit must account for the optional I/O permission map and the task software state, if these fields are defined and used by the operating system (the I/O permission map is described in Chapter 5). If no I/O permission map is present, the limit must be set to at least 68H (the length of the machine state data); if the operating system extends a TSS with software state information,

Figure 1-1. Task Execution Environment

Figure 1-2. Task State Segment

Figure 1-3. Task State Segment Descriptor

the limit can, but need not, cover the additional information. TSSs must reside in the global descriptor table (GDT) to give the processor access to all TSSs regardless of the task that is running (interrupt and exceptions can trigger task switches as described in Chapter 3). To prevent unauthorized task switches, TSS descriptors should be assigned privilege level 0.

The 80386 sets the busy (B) bit in a TSS descriptor to trap an attempt to invoke a task recursively; the operating system should initialize this bit to 0. In a normal task switch, the 80386 sets the busy bit of the new task and clears the busy bit of the old task. However, in a nested task switch, the 80386 leaves the old task's busy bit set. A nested task switch occurs when one task calls another or, more commonly, when the 80386 invokes an interrupt or exception handler that is implemented as a task (see Chapter 3). An attempt to invoke a task whose busy bit is set results in an invalid TSS exception.

## 1.3 TASK CREATION

The 80386-defined data structures shown in Figure 1-1 must be in place before switching to a new task. The GDT and the interrupt descriptor table (IDT) are system-wide resources, which can be created statically by the Intel System Builder utility, or by the operating system at initialization time, as discussed in Chapter 6. A new local descriptor table (LDT) must be created for a new task unless the new task shares the LDT of another task, or the system does not use LDTs; the criteria for associating tasks and LDTs are described in Chapter 2. If paging is enabled, the task needs a page directory and one or more page tables (alternatively, all tasks can share a single page directory and set of page tables). LDT, page directory, and page table creation are discussed in Chapter 2.

An operating system cannot initialize a TSS or a TSS descriptor by writing directly into the TSS or the GDT, but must use a data segment alias. Aliased segments are segments that overlap one another in the linear address space; they are described further in Chapter 2.

When initializing a TSS, operating systems should observe the following guidelines:

- Backlink: This field should be initialized to 0 to prevent an erroneously set NT (nested task) flag from causing an erroneous task switch. If a task's NT flag is set, the 80386 executes an IRET instruction by switching to the task whose selector is recorded in the backlink field. The 80386 sets the NT bit and updates the backlink field when a task is interrupted or incurs an exception whose handler is a task, or when a task calls another task. A task can set its NT bit with a POPF instruction, but it cannot update its backlink field without access to the operating system's TSS alias. By initializing the backlink to 0, the operating system makes the 80386 raise an invalid TSS fault if the task issues an IRET instruction when NT has been erroneously set.

- Privileged stack pointers: SS0, SS1, SS2, ESP0, ESP1, and ESP2 must contain the initial stack selectors and offsets for privilege levels 0-2 respectively. The operating system must initialize the fields that correspond to the privilege levels it, or other software, uses. For example, if an operating system runs user code at privilege level 3 and operating system code at privilege level 0, it must initialize SS0 and ESP0. When, as the result of a system call, an interrupt, or an exception, the 80386 changes from privilege level 3 to privilege level 0, it switches to a privileged stack by loading the SS segment register with SS0 and ESP register with ESP0.

- CR3: If paging is enabled, the TSS CR3 field must be initialized with the physical address of the task's page directory.

- EIP, EFLAGS, general, and segment registers: Initialize to values the task should have when it begins to run.

- LDT: Initialize with the selector for the task's LDT; this field must be set to zero (null selector) if a task does not use an LDT.

- T bit: By setting this bit, the operating system directs the 80386 to raise a debug trap when the processor switches to this task (see Chapter 3).

- I/O permission map base and optional I/O permission map: These fields can be used to grant a task access to selected I/O ports (see Chapter 5).

# 1.4 TASK TERMINATION

Task termination is generally a matter of operating system design and is little influenced by the 80386 system architecture. Typically, the termination process is divided between an operating system exit procedure and system reclamation task. Running in the context of the task to be terminated, the privileged exit procedure has direct access to the task's address space and software state. In brief, the exit procedure changes the task's software execution state to terminated, then calls the operating system dispatcher to run the next task. In more detail, the exit procedure disconnects the task from system resources, closing files, removing the task from any semaphores it may be waiting on, and the like. By severing these links, the exit procedure ensures that these resources are usable by other tasks when the task actually disappears. The exit procedure may be able to reclaim some of the task's memory,

but at least a small amount of memory (for example, the task's stacks, TSS, and page directory, if paging is enabled) must be left for the reclamation task to reclaim. Finally, the exit procedure calls the dispatcher to switch to another task. The operating system must ensure that the terminated task never runs again because most of its context has been destroyed by the exit procedure.

The reclamation task is a privileged operating system task that can access task-related data structures. The reclamation task may run periodically, scanning TSSs for terminated tasks, or it may run upon receipt of a message from the exit procedure (the message may contain the terminating task's TSS selector). If passed the terminated task's TSS selector, the reclamation task can find the terminated task's TSS descriptor in the GDT. From this descriptor the reclamation task can find the task's TSS, LDT, page directory, and page tables. The reclamation task can free both the memory these structures occupy and the task's TSS descriptor.

## 1.5 TASK SWITCHING

Deciding when to switch tasks is an operating system policy issue; the 80386 plays no part in such scheduling/dispatching decisions. (However, the 80386 can automatically dispatch task-based interrupt and exception handlers, as discussed in Chapter 3.) Once the operating system has decided to suspend the running task and run another task, the 80386 provides the mechanism to switch the machine context (the operating system must switch the software context).

Most operating systems use an 80386 JMP TSS instruction to direct the 80386 to switch tasks. There are other ways to direct the 80386 to switch tasks, but they are less commonly used. The CALL TSS instruction implements a nested task switch in which return to the calling task is implied; it can be useful for implementing coroutines and for invoking task-based interrupt and exception handlers (see Chapter 3). A JMP TASKGATE instruction also switches tasks. Because task gates can reside in LDTs and can be made accessible to selected privilege levels, this instruction can be used to extend task switching capabilities to selected privilege levels or tasks.

The TSS operand of the JMP TSS instruction is a segmented (selector and offset) pointer to the new task's TSS. Because a TSS is a segment, the 80386 uses only the selector part of the operand and ignores the offset part. JMP TSS is not a privileged instruction, but to execute it without faulting, the running code segment must be at least as privileged as the target TSS. If all TSS descriptors are defined with privilege levels of 0, only tasks running at privilege level 0 can switch tasks with a JMP TSS instruction.

A typical operating system encapsulates the task switching code in a procedure called a dispatcher. Other operating system procedures call the dispatcher when a task switch is, or may be, in order. In general, any operating system procedure that makes the running task unable to proceed, or makes a suspended task ready, calls the dispatcher. The dispatcher changes the software states of the old and new tasks, updates the list of ready tasks, and otherwise prepares for execution to transfer to another task. To switch the 80386 machine state from the old task to the new, the dispatcher issues a JMP TSS instruction, as shown in Figure 1-4.

Figure 1-4. Example Dispatcher

The JMP TSS instruction saves the task-specific machine state into the current TSS and loads the task-specific machine state from the new TSS. JMP TSS is thus equivalent to many MOV instructions (and a substantial amount of validation; for example, the 80386 ensures that the descriptor named in the JMP TSS instruction is in fact a TSS descriptor). The 80386 executes a JMP TSS essentially as follows (for the definitive description consult the 80386 Programmer's Reference Manual):

- Save general registers, segment registers, EFLAGS register, and EIP in current TSS.

- Clear old TSS descriptor's busy bit, so the old task can be resumed later.

- Load TR with new TSS selector and descriptor.

- Load general registers, segment registers, EFLAGS register, EIP, LDTR, and CR3 (page directory base address) registers from new TSS.

- Fetch the instruction pointed to by new task's CS:EIP. This is the instruction the task

would have executed next when it was last suspended (or it is the first instruction of a

newly created task).

An 80386 task switch does not switch the state of a numeric coprocessor because the coprocessor's context may not need to be switched with every task switch. Chapter 7 describes how to write an exception handler that switches the state of a coprocessor when necessary, eliminating the need for the dispatcher to switch it on every task switch.

The 80386 does not save system registers such as CR0, GDTR, and IDTR on a task switch because these registers represent system-wide resources that are shared by all tasks. The processor does not save LDTR or CR3 because these are not normally changed while a task is executing. (If an operating system changes LDTR or CR3, it must update the corresponding fields in the current task's TSS.)

Note that the 80386 does not save CR2, the page fault linear address, in the TSS (the TSS does not include a field for CR2). However, CR2 could contain task-related data if a task switch occurred during the handling of a page fault. Consequently, a page fault handler must save CR2 before allowing a task switch to occur. See Chapter 2 for details of page fault handling.

Before switching to the new task, the 80386 checks the new TSS descriptor and TSS for validity. These checks can raise the following faults:

- Invalid TSS (for example, the target segment is not a TSS)

- Segment fault (for example, the new TSS is not present, or a segment selected by the CS-GS fields of the new TSS is not present)

- Page Fault (for example, all or part of the new TSS is in a not-present page)

- General Protection Fault (for example, the privilege level of the new TSS is less than the current privilege level)

(The preceding is not an exhaustive list of the fault conditions that can be detected in a task switch; consult the 80386 Programmer's Reference Manual for details.) Although it is possible to recover from many of these faults, prudent operating system designs avoid faults during task switches. A fault that occurs late in a task switch increases interrupt latency by "stretching" the duration of the task switch instruction by the extra operations required to invoke the fault handler.

If, in a task switch, the T bit of the new TSS is set, the 80386 raises a debug exception after switching to the new task but before executing the new task's first instruction. This exception can be used to notify a debugger that a task being debugged is about to run.

# CHAPTER 2 MEMORY MANAGEMENT

An 80386 operating system designer can use the 80386 segmentation and paging facilities to implement any commonly used memory model, including "flat," "segmented," "paged," and "segmented paged." Memory can be unprotected, or segments or pages can be protected with attributes such as supervisor or user, or read-only. Segments or pages can permanently reside in physical memory or they can be swapped between memory and disk, to implement virtual memory.

Underlying the 80386's memory management flexibility are two common denominators, descriptor tables and page tables. The content of these tables expresses an operating system's memory model. This chapter shows how to set up and manage these tables.

In the 80386, segmentation and paging are independent of one another and are therefore covered in separate sections of this chapter. (Virtual memory is also covered separately because it is optional, even when paging is enabled.) Nevertheless, an operating system designer must consider segmentation and paging together in order to develop the design that best supports the operating system's needs. The final section of the chapter gives four examples of memory management designs that can be implemented on the 80386; two of these designs use both segmentation and paging.

# 2.1 SEGMENTATION

The 80386 logical address space is inherently segmented, but an operating system designer has great freedom in defining the segments. For example, in one operating system the logical address space might consist of a single segment that spans the entire 4-gigabyte linear address space. Another operating system might separate system from user by placing their code and data in different segments. A third operating system might map a task's private data to one segment and data shared by tasks to another segment. Thus, while every 80386 operating system uses segments, each operating system defines them to support its own protection and performance needs.

Two attributes give 80386 segments their flexibility:

- They can be as large as 4 gigabytes.

- They can overlap one another in the linear address space.

Operating systems that use segmentation actively can define many small segments, mapping them to distinct linear address ranges. Operating systems that are not segment-oriented can

define a few large overlapping segments; in the extreme case (all segments fully overlap one another), segmentation is effectively nullified.

# 2.1.1 Required Segments

Although a task in a segment-oriented operating system can have dozens, hundreds, or thousands of segments, even an operating system that defines a "flat" (effectively unsegmented) logical address space must provide each task with a minimal complement of segments. Every task must have a code segment (represented by the selector in CS) and a data segment (selector in DS). A task can have a separate stack segment or can use its data segment for a stack (the selector in SS defines the current stack segment). An extra segment is not required, but the string instructions assume a valid selector in ES. Loading the same selector into DS and ES makes string moves operate within the same segment. ES can be loaded whenever DS is loaded, or just before executing a string instruction.

The F and G data segments (represented by the selectors in FS and GS) are not required. In systems that define multiple data segments, compilers may be able to improve performance by maintaining frequently used data selectors in FS and GS, thereby reducing the number of times DS must be reloaded to make a segment addressable. Systems that address all data through DS/ES and SS can initialize FS and GS with null selectors to trap references that use these registers without initializing them. (Null selectors also improve task switch time by eliminating descriptor checking and loading.)

# 2.1.2 Segmentation Models

Segments allow processor protection to be applied to programmer-defined objects. Segments can be byte-variable in length up to one megabyte; segments from one megabyte to four gigabytes are defined in units of 4 Kbytes. An operating system, with compiler and linker support, can map programming units as small as individual procedures (or functions or subroutines) and data structures (such as arrays and records) to distinct segments. In addition to standard read and write permission checking, the 80386 can check segment accesses for proper type (code versus data), length, and privilege (a segment can be assigned one of four privilege levels). These run-time checks can uncover programming errors, such as bad array indexes and pointers, that cannot be detected at compile-time.

An operating system designer must balance the protection advantages of segments against their application fit, and their performance and storage costs. Some programming languages, for example, have a built-in view of memory that does not map naturally to segmentation. For example, the C language allows a pointer to uniformly address any object in a task's address space whether the object is a function, a constant, or a local variable allocated on the task's stack.

Run-time segment protection checking takes time. The 80386 minimizes the cost of segment protection by checking many segment attributes (such as length) in parallel with

logical-to-linear address translation. Other segment protection checks are made only when a segment register is loaded with a new selector as described below:

- Intersegment (far) jumps and calls reload CS with the target segment's selector and descriptor. When the 80386 loads a new selector into a segment register, it checks the associated descriptor for validity. For example, when loading CS, the processor ensures that the target segment is a code segment and is present in memory. Intersegment returns also take longer to execute than returns within the same segment; again, the processor checks the return address's descriptor. Overall, intersegment control transfers take several times as long as intrasegment transfers.

- Intersegment data references take longer when the selector for the new segment must be loaded into a data segment register; the 80386 checks the new segment's descriptor (for example, to ensure that it is a data segment) before loading it. If the new segment is to be the subject of a string instruction, ES must similarly be loaded. (Segment-oriented systems may be able to reduce DS loading by making some data references through ES, FS, and GS.) Overall, intersegment data references are usually more costly than intersegment transfers because they occur more frequently.

A task that uses multiple data segments or distinct data and stack segments must use 48-bit segmented (selector and offset) pointers to unambiguously identify the segment to which a pointer refers. (32-bit offset-only pointers implicitly refer to the segment whose descriptor is currently loaded in DS or SS.) Compared to 32-bit offset-only pointers, segmented pointers consume more storage space (they are pushed as two doublewords) and require an additional bus cycle to transfer to or from memory.

An 80386 operating system can control the amount of time the processor spends checking segments by selecting a model of segmentation. By employing segmentation judiciously, an operating system can strike a protection/performance balance that is consistent with its goals. Some representative models of segmentation are described below (others are possible):

- 1. The operating system defines one code segment and one data segment; both segments map the entire linear address space. DS, ES, and SS are loaded with the data segment selector. In this model, both code and data references are 32-bit offsets; after initialization, segment registers are never changed. This model provides the equivalent of an unsegmented, and, in the absence of paging, unprotected 4-gigabyte logical address space.

- 2. Similar to model 1, except that user segments are distinct from operating system segments; operating system segments map the full 4 Gbyte linear space, but user segments map a subset of the linear addresses. Operating system segments have greater privilege than user segments and are therefore protected from user access. This model uses 32-bit code and data pointers, except for system calls. A 48-bit code pointer is required to call an entry point in the operating system's code segment. (The user/supervisor type of protection provided by this model can also be implemented with page, rather than segment, protection.)

- 3. Similar to model 2, except that data and stack segments map different areas of the linear space. Because the data and stack segments do not overlap in the linear space, this model uses 48-bit data pointers. With separate stack and data segments, the 80386 can detect stack overflows, the stack is protected from bad data references, and the data segment is protected from bad stack references.

4. Same as model 3, except that major data structures are mapped to different data segments. This model uses 48-bit code and data pointers; CS changes on interrupts, exceptions, system calls, and procedure calls; DS, ES, FS, or GS changes to reference a new data structure; ES is changed to match DS before executing a string instruction (unless the instruction is an intersegment string move).

Each of the preceding models trades tighter protection for reduced performance. The actual performance differences between models depends on the frequency of intersegment, procedure calls, and system calls. In systems that tend to be pointer-intensive and procedure-callintensive (C programs are a good example) it may be wise to choose one of the first segment models listed above. Conversely, systems in which pointer and procedure call performance is not critical, or in which maximum protection is very important, can choose one of the later models.

# 2.1.3 Defining Segments

Having decided which segmentation model best fits an operating system's performance and protection goals, the operating system designer must express the model in the contents of 80386 descriptor tables. This section provides guidance for setting up and managing these tables.

## 2.1.3.1 DESCRIPTORS

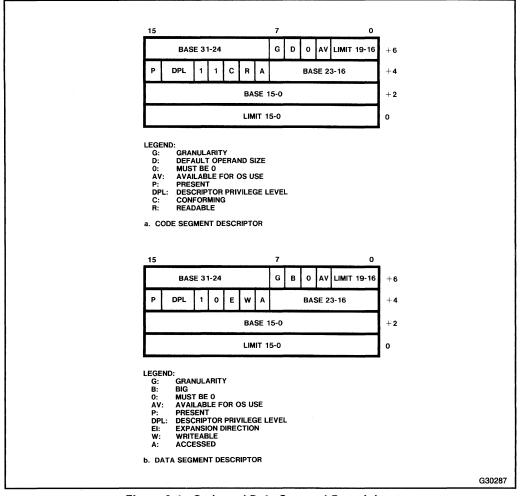

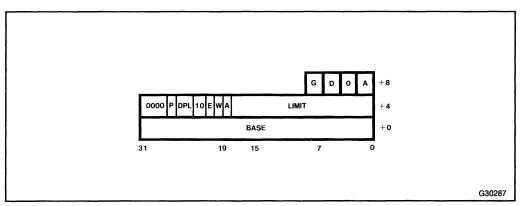

80386 segments are defined by segment descriptors (see Figure 2-1). A segment's descriptor defines the segment's location (base address and limit) in the linear address space and its protection attributes. The operating system (or the Intel System Builder utility) creates descriptors, but they are mainly interpreted and updated by the processor.

A task's descriptors completely define the linear addresses the 80386 can generate for the task. Any linear address that is not covered by a descriptor is inaccessible to a task because the processor cannot generate such an address. Thus, the distribution of descriptors among tasks, and the linear address ranges these descriptors cover, provides an initial level of control over accessibility to the linear address space. The second level of control over access to the linear space is provided by the protection attributes of a task's descriptors.

## 2.1.3.2 DESCRIPTOR TABLES

A task's logical address space map is defined by the segment descriptors in two descriptor tables, the global descriptor table (GDT) and the task's local descriptor table (LDT). These descriptor tables are variable in length to a maximum of 64 kilobytes, giving each a maximum capacity of 8,192 descriptors. The GDT holds descriptors that are global to all tasks; the LDT holds descriptors that are local to a single task, or are local to a group of closely related tasks. A task need not have an LDT, and tasks can share an LDT; for example, an operating system might define a "job" as group of tasks that shared a common pool of resources, including the same LDT. The descriptors in a task's LDT and the GDT fully define the linear addresses a task can generate. (Note, however, that the presence of a descriptor in the GDT or a task's LDT does not automatically grant access to a range of linear addresses; the

Figure 2-1. Code and Data Segment Descriptors

protection attributes of a descriptor can prevent a task from using the descriptor. Segment protection attributes are discussed in Section 2.1.6.)

The system registers GDTR and LDTR point to the global and local descriptor tables, respectively. GDTR contains the 32-bit linear address of the GDT and a 16-bit limit. At initialization time (see Chapter 6), the operating system loads GDTR with the LGDT instruction. Although GDTR can be reloaded during execution (provided that CPL=0), there is normally no reason to do so. The operating system must load LDTR with a selector for the current LDT; this selector must reference an LDT descriptor in the GDT. If a task does not have an LDT, LDTR can be loaded with a null selector (all 0-bits). The operating system also loads LDTR during initialization, either directly with the LLDT instruction or indirectly by means of a dummy task switch (see Chapter 6). On each task switch, the 80386

reloads LDTR from the new task's TSS. Because GDTR is constant, whereas LDTR (potentially) changes with every task switch, every task can share the segments defined in the GDT and yet have exclusive access to the segments defined in its LDT (if the task does not share its LDT with other tasks).

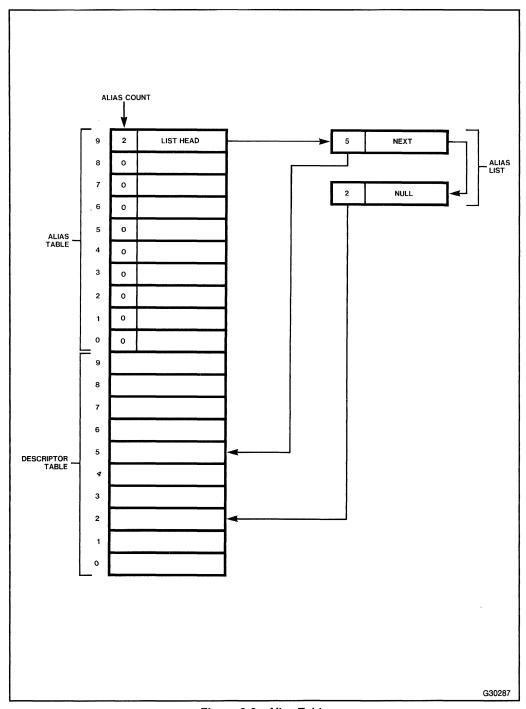

## 2.1.4 Aliases

Two descriptors are aliases if they define the same addresses in the linear address space. (Note that one segment alias can frame the linear addresses of multiple segments, potentially even the full 4-gigabyte linear address space.) Aliases can give alternative "views" of a segment to different tasks, or can give one view to the operating system and another to an application program. For example, a code segment is by definition unwriteable; although this attribute prevents an application program from erroneously overwriting its instructions, it also prevents an operating system from legitimately loading the application program's instructions into memory. By aliasing the code segment with a writeable data segment, the operating system can load the application program's instructions into the linear addresses defined by the code segment descriptor. As long as the application program does not have access to the data segment alias, it cannot modify its own code. As discussed in Section 2.1.5, aliases can also be used to share segments between tasks.

An operating system must define a data segment alias for the GDT, the IDT (interrupt descriptor table, described in Chapter 3), and for any 80386-defined segment that the operating system updates. The GDT and the IDT must be aliased because they are not addressable with logical addresses (there are no descriptors for these tables; the processor addresses them through the linear addresses in the GDTR and IDTR registers). Other system segments, such as TSSs and LDTs, must be aliased because of the need to update them upon a task switch or when a task's address space needs to be increased/decreased dynamically. The 80386 raises a general protection exception if software attempts to load their descriptors into data segment registers. The operating system can define one alias for each table or segment described here, or it can define a single alias that spans all of them (or even all of the linear address space). The alias(es) for system tables and system segments should be assigned privilege level 0 so that access to them is restricted to the most privileged level of the operating system (Section 2.1.6 describes privilege level and other segment protection mechanisms).

While they are useful, and even indispensable, segment aliases complicate an operating system. The principal problem presented by aliases is keeping the multiple descriptors consistent. Suppose, for example, an operating system increases the size of a segment. Typically, this means allocating a segment of the new length, copying the content of the old segment to the new segment, and, finally, freeing the old segment. If the old segment has aliases, however, the operating system must find and update the aliases so they point to the new segment rather than the old. Aliases also complicate segment deletion; the memory occupied by a segment cannot be freed until no aliases for the segment exist.

To manage segment aliases, an operating system must effectively extend descriptors with alias information. One way to extend descriptors is to define an alias table that has an entry for each GDT or LDT entry (see Figure 2-2). The alias table entry for a descriptor can

Figure 2-2. Alias Table

indicate the number of aliases for the segment and can point to a list of pointers to the aliases. The operating system can supply system calls that create and delete aliases; if the operating system makes these calls available to applications, it must check the parameters supplied in each invocation, since aliases can potentially permit access to memory that should not be allowed. (An application should not, for example, be permitted to alias operating system code or data.)

Operating systems that are not segment-oriented can simplify alias management by defining a single data segment alias that spans the entire linear address space. The operating system can then read or write any linear address via this alias and the alias need never be updated.

# 2.1.5 Sharing

For two (or more) tasks to share a segment, the tasks can either share a common descriptor for the segment, or they can hold aliases to the same segment. There are three ways to effect segment sharing.

- Because all tasks share all descriptors in the GDT, the simplest way to achieve intertask

segment sharing is to place a descriptor in the GDT. Although simple, this approach is

nonselective because every task shares the segment. Consequently, GDT slots are

normally defined to hold descriptors for system-wide resources, such as the operating

system's code and data, that would otherwise have to be duplicated in every task's LDT.

- Tasks can also share a descriptor by sharing an LDT. Although more selective than GDT-sharing, two tasks that share an LDT share all of their segments.

- Individual tasks can share individual segments by means of aliases in their LDTs. Aliases are the most precise form of intertask sharing and allow the sharing tasks to be given different views of the shared segment. For example, one task may be able to write a segment, whereas another task's alias for the same segment allows only reading.

# 2.1.6 Protection

A descriptor's protection fields allow an operating system to define the conditions under which the associated segment can be accessed. If an attempted access violates one of these conditions, the 80386 does not make the access but raises an exception. Exceptions are described in Chapter 3.

# 2.1.6.1 TYPE AND RIGHTS

The 80386 distinguishes between segments that contain code and segments that contain data; stack segments are data segments. When the code/data bit of a descriptor (bit 43, see Figure 2-1) is set, the 80386 interprets the corresponding segment as a code segment. The 80386 ensures that a data segment is used as a data segment and a code segment is used as a code segment. An attempt to write into a code segment or to transfer control to a data segment raises a general protection fault.

An operating system can restrict the operations a task may perform on a code or data segment by clearing the R (readable) bit of a code segment or the W (writeable) bit of a data segment (see Figure 2-1). When clear, these bits make a code segment unreadable and a data segment unwriteable. Code segments are by definition unwriteable and executable; data segments are by definition readable and unexecutable. A code segment can be further classified as conforming by setting its C (conforming) bit. Conforming code segments are described in Chapter 4. They provide a way to implement procedures that have no inherent privilege level, but execute at the privilege levels of their callers.

# 2.1.6.2 LIMIT

To detect a segment overrun, the 80386 compares the offset part of a logical address to the segment's limit. For example, suppose a task computes an address (an offset within the current code segment) and jumps to that address. If the task erroneously computes the offset as larger than any address in the segment, the 80386 does not perform the jump but raises a general protection exception.

A segment's limit is encoded in its descriptor as a combination of the G (granularity) bit and the concatenation of the limit fields. (In the rest of this section, "limit field" means the concatenation of the limit fields.) The limit field is 20 bits wide; the G bit tells the processor how to expand the limit field to 32 bits. If G=0, the segment's granularity is 1 byte; the 80386 computes the limit of a byte-granular segment by concatenating 12 high-order 0-bits to the limit field. If G=1, the segment's granularity is 4 Kbytes or one page (the term page, as used here, refers to a 4 Kbyte unit of memory and is independent of the 80386 paging facility). The 80386 computes the limit of a page-granular segment by concatenating the limit field to 12 low-order 1-bits. Segments up to 1 megabyte ( $2^{20}$  bytes) can be defined with byte granularity; page granularity must be used for larger segments. A segment with page granularity can span the entire linear address space ( $2^{20}$  pages = 4 Gbytes). Three examples of segment limit computation follow:

- 1. If G=1, base=1000H, and the limit field=0H, the descriptor defines a segment with base address 1000H (4096D) and a limit of FFFH (4095D). The associated segment is one page long and spans the second page frame of the linear address space. Note that the minimum size of a large-grain segment is 4 Kbytes.

- 2. If G=0, base=1000H, and the limit field=FFFH, the descriptor defines the same 4 Kbyte segment as the previous example.

- 3. If G=1, base=0, and limit field=FFFFFH, the descriptor defines a segment with base address 0 and limit of FFFFFFFH. The segment spans the entire 32-bit linear address space.

Byte-granular segments provide precise size checking, but have a limited size range (1 byte-1 megabyte); page-granular segments have a greater range (4 Kbytes-4 Gbytes), but limit checking is coarser. (A reference beyond a data structure allocated in a page-granular segment causes a limit violation only if the end of the data structure coincides with end of

the segment.) To prevent unintentional segment overlap, an operating system should allocate page-granular segments on 4 Kbyte linear address boundaries.

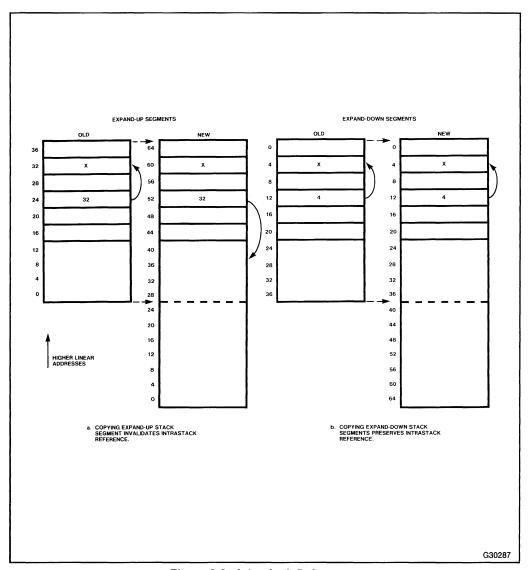

#### 2.1.6.3 EXPAND-DOWN SEGMENTS

The preceding description of the segment limit computation holds for expand-up segments, that is, segments whose E (expansion direction) bit is 0. The great majority of segments are expand-up segments. The 80386 provides expand-down data segments for operating systems that meet both of the following criteria:

- Stacks are defined as distinct segments (DS and SS contain different selectors).

- A stack is expanded by copying it to a larger segment (rather than by adding present pages to its segment).

Designers who do not plan to implement stacks in this way need not define expand-down segments and can skip the remainder of this section.

Implementing a stack with an expand-down segment preserves intrastack references if the stack is copied to a larger segment (see Figure 2-3). Stacks grow toward lower addresses; therefore, to expand a stack, the stack must be copied to the high end of a larger segment. If a stack in an expand-up segment is copied in this way, the offsets of the items on the stack change; when a stack in an expand-down segment is similarly copied, the offsets of the stack items do not change.

The 80386 provides two kinds of expand-down (E=1) data segments, small and big. A small expand-down segment is denoted by a B (big) bit that is 0; a large expand-down segment is denoted by a B bit that is 1. (The B bit has a second function for stack segments, whether expand-up or expand-down. When loaded into SS, a segment descriptor with B=0 directs the 80386 to use the 16-bit SP register for implicit stack references, such as those made by the PUSH, POP, CALL, and RET instructions. When B=1, the 80386 uses the 32-bit ESP register for the stack pointer.) A small expand-down segment can range from 0 to 64 Kbytes-1 in length; the G bit of a small expand-down segment must be 0. A big expand-down segment can range in size from 4 Kbytes-1 to 4 Gbytes-1, in increments of 4 Kbytes; the G bit of a big expand-down segment should always be 1.

Figure 2-4 summarizes the differences between expand-up and expand-down segments. An expand-up segment's lowest linear address is equal to its base address; its highest linear address (that is, the maximum offset that can be used to form an address in the segment) is a function of the segment's limit and G bit. The highest and lowest linear addresses of expand-down segments are expressed differently. The lowest linear address of an expand-down segment is equal to its base plus the quantity (limit-1), with the computation "wrapping around" at 4 Gbytes if necessary. "4 gigabyte wraparound" means that the processor ignores any overflow into bit 33 of the linear address; the linear address following FFFFFFFH is 0. The highest address of a small expand-down segment is base+FFFFH; the highest address of a big expand-down segment is base+FFFFFH. In both cases, the computation wraps around at 4 Gbytes if necessary (always true for big expand-down segments).

Figure 2-3. Intrastack References

Both small and big expand-down segments can be located anywhere in the linear address space. To define a small expand-down segment, set the base address to (highest address-64 Kbytes); set the limit to 1 greater than the desired segment size. A small expand-down segment can be expanded by reducing its limit if the memory between its lowest address and its base has not been allocated to another segment; otherwise the data in the segment can be copied to a larger segment. To define a large expand-down segment, set its base to (highest address minus 4 Gbytes); set the limit field to 1 greater than the desired size of the segment.

Figure 2-4. Expand-Up and Expand-Down Segment Comparison

#### **2.1.6.4 PRIVILEGE**

The DPL (descriptor privilege level) field defines a segment's privilege level; 0 is the most-privileged level and 3 is the least-privileged level. Unless a task is executing a conforming code segment, its current privilege level is equal to the privilege level of the code segment it is executing. (If the task is executing a conforming code segment, its current privilege is equal to the privilege level of the code segment that called the conforming segment.) When an instruction operand is a selector, the task's current privilege level can be reduced for the execution of that instruction by the RPL (requested privilege level) field in the selector. When RPL is 0, it has no effect on current privilege level. See Chapter 4 for a more detailed description of RPL.

A segment's privilege level defines the privilege required to access the segment. To read or write a data segment, a task must be at least as privileged as the target segment (numerically, the task's current privilege level must be less than or equal to the value coded in the target segment's DPL field). For example, a task running at privilege level 2 can access data segments whose privilege levels are 3 or 2, but cannot access data segments whose privilege levels are 1 or 0. To transfer control to another code segment by a JMP, CALL, RET, or IRET instruction, a task must have the same privilege level as the target segment. For the special cases of system calls, interrupts, and exceptions, in which a task's privilege level is numerically decreased while it executes a more privileged code segment, the 80386 provides special descriptors called gates. Gates are described in Chapters 3 and 4. (The 80386 does not allow a task to call to a less-privileged code segment because such a call implies that a return to a more-privileged segment is also allowed. Such a return mechanism, however, would permit tasks to enter more privileged code segments by returning to them.)

If, as is strongly recommended, the GDT and LDT data segment aliases are defined as privilege level 0 segments, only tasks executing privilege level 0 code segments can create descriptors. (There is no GDT selector and attempting to load an LDT selector into a data segment register results in a general protection exception.) Without the ability to manufacture descriptors, tasks running at privilege levels 3, 2, or 1 can increase their privilege only by transferring through the gates defined by the level 0 operating system.