#### **MNEMONIC INDEX**

| Mnemonic | Page | Mnemonic | Page | Mnemonic | Page |

|----------|------|----------|------|----------|------|

| AAA      | 6    | JG       | 15   | MOV      | 3    |

| AAD      | 8    | JGE      | 14   | MOVS     | 12   |

| AAM      | 8    | JL       | 14   | MUL      | 8    |

| AAS      | 8    | JLE      | 14   | NEG      | 7    |

| ADC      | 6    | JMP      | 13   | NOP      | 17   |

| ADD      | 5    | JNA      | 14   | NOT      |      |

| AND      | 10   | JNAE     | 14   | OR       | 11   |

| CALL     | 12   | JNB      | 15   | OUT      | 4    |

| CBW      | 9    | JNBE     | 15   | POP      | 4    |

| CLC      | 17   | JNE      | 14   | POPF     |      |

| CLD      | 17   | JNG      | 14   | PUSH     |      |

| CLI      | 17   | JNGE     | 14   | PUSHF    |      |

| CMC      | 17   | JNL      | 14   | RCL      | 10   |

| CMP      | 7    | JNLE     | 16   | RCR      | 10   |

| CMPS     | 12   | JNO      | 15   | REP      | 11   |

| CWD      | 9    | JNP      | 15   | RET      | 13   |

| DAA      | 6    | JNS      | 15   | ROL      | 9    |

| DAS      |      | JNZ      | 14   | ROR      |      |

| DEC      | 7    | 10       | 14   | SAHF     | 5    |

| DIV      | 8    | JP       | 14   | SAL      | 9    |

| ESC      | 17   | JPE      | 14   | SAR      |      |

| HLT      | 17   | JPO      | 15   | SBB      |      |

| IDIV     | 8    | JS       |      | SCAS     | 12   |

| IMUL     |      | JZ       |      | SHL      |      |

| IN       |      | LAHF     |      | SHR      |      |

| INC      |      |          | 5    | STC      |      |

| INT      |      |          | 5    | STD      |      |

| INTO     |      | LES      |      | STI      |      |

| IRET     |      | LOCK     |      | STOS     |      |

| JA       | 15   | LODS     |      | SUB      |      |

| JAE      | 15   |          | 15   |          | 10   |

| JB       |      |          | 15   |          | 17   |

| JBE      |      | LOOPNE _ |      | XCHG     |      |

| JCXZ     |      | LOOPNZ _ |      | XLAT     |      |

| JE       | 13   | LOOPZ    | 15   | XOR      | 11   |

MCS-86TASSEMBLY

LANGUAGE

REFERENCE

GUIDE

Mnemonics © Intel. 1978.

PROGRAMMING LANGUAGE SOFTWARE

Printed in U.S.A.

1084/2K/0386/PTW/AD

©Intel Corporation 1978 9800749-1

October 1978

RG-2

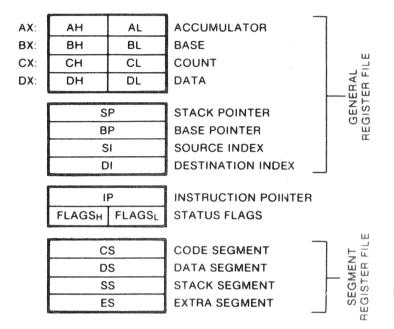

## 8086 REGISTER MODEL

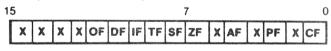

Instructions which reference the flag register file as a 16-bit object use the symbol FLAGS to represent the file:

X = Don't Care

AF: AUXILIARY CARRY — BCD

CF: CARRY FLAG

PF: PARITY FLAG

SF: SIGN FLAG

ZF: ZERO FLAG

DF: DIRECTION FLAG (STRINGS)

IF: INTERRUPT ENABLE FLAG

OF: OVERFLOW FLAG (CF ⊕ SF)

TF: TRAP — SINGLE STEP FLAG

#### OPERAND SUMMARY

"reg" field Bit Assignments:

| 16-Bit (w = 1) | 8-Bit (w = 0) | Segment |

|----------------|---------------|---------|

| 000 AX         | 000 AL        | 00 ES   |

| 001 CX         | 001 CL        | 01 CS   |

| 010 DX         | 010 DL        | 10 SS   |

| 011 BX         | 011 BL        | 11 DS   |

| 100 SP         | 100 AH        |         |

| 101 BP         | 101 CH        |         |

| 110 SI         | 110 DH        |         |

| 111 DI         | 111 BH        |         |

## SECOND INSTRUCTION BYTE SUMMARY

| mod | xxx | r/m |

|-----|-----|-----|

|     |     |     |

| mod | Displacement                                                                                               |

|-----|------------------------------------------------------------------------------------------------------------|

| 00  | DISP = 0*, disp-low and disp-high are absent                                                               |

| 01  | DISP = 0*, disp-low and disp-high are absent DISP = disp-low sign-extended to 16-bits, disp-high is absent |

| 10  | DISP = disp-high: disp-low<br>r/m is treated as a "reg" field                                              |

| 11  | r/m is treated as a "reg" field                                                                            |

|     |                                                                                                            |

| r/m | Operand Address    |

|-----|--------------------|

| 000 | (BX) + (SI) + DISP |

| 001 | (BX) + (DI) + DISP |

| 010 | (BP) + (SI) + DISP |

| 011 | (BP) + (DI) + DISP |

| 100 | (SI) + DISP        |

| 101 | (DI) + DISP        |

| 110 | (BP) + DISP*       |

| 111 | (BX) + DISP        |

DISP follows 2nd byte of instruction (before data if required).

## Operand Address (EA) Timing (clocks):

Add 4 clocks for word operands at ODD ADDRESSES.

Immed Offset = 6

Base (BX, BP, SI, DI) = 5

Base + DISP = 9

Base + Index (BP + DI, BX + SI) = 7

Base + Index (BP + SI, BX + DI) = 8

Base + Index (BP + DI, BX + SI) + DISP = 11Base + Index (BP + SI, BX + DI) + DISP = 12

<sup>\*</sup>except if mod = 00 and r/m = 110 then EA = disp-high; disp-low.

## **ASSEMBLER DIRECTIVES**

Symbol Definition:

EQU

LABEL

PURGE

Memory Reservation and

Data Definition:

DB

DW

DD

RECORD

Location Counter and

Segmentation Control:

SEGMENT/ENDS ORG

**GROUP**

**ASSUME**

PROC/ENDP

CODEMACRO/ENDM

Program Linkage:

NAME

**PUBLIC**

**EXTRN**

**END**

### PROCESSOR RESET REGISTER INITIALIZATION

DS = 0000H

SS = 00000H

ES = 0000H

No other registers are acted upon during reset.

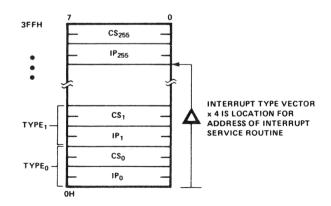

#### MCS-86™ RESERVED LOCATIONS

#### **Reserved Memory Locations**

Intel Corporation reserves the use of memory locations FFFFOH through FFFFH (with the exception of FFFFOH - FFFF5H for JMP instr.) for Intel hardware and software products. If you use these locations for some other purpose, you may preclude compatibility of vour system with certain of these products.

#### Reserved Input/Output Locations

Intel Corporation reserves the use of input/output locations F8H through FFH for Intel hardware and software products. Users who wish to maintain compatibility with present and future Intel products should not use these locations.

#### **Reserved Interrupt Locations**

Intel Corporation reserves the use of interrupts 0-31 (locations 00H through 7FH) for Intel hardware and software products. Users who wish to maintain compatibility with present and future Intel products should not use these locations.

Interrupts 0 through 4 (00H-13H) currently have dedicated hardware functions as defined below.

| Location | Function                                 |

|----------|------------------------------------------|

| 00H-03H  | Divide by zero                           |

| 04H-07H  | Single step                              |

| 08H-0BH  | Non-maskable interrupt                   |

| 0CH-0FH  | One-byte interrupt instruction           |

| 10H-13H  | Interrupt on overflow                    |

|          | 00H-03H<br>04H-07H<br>08H-0BH<br>0CH-0FH |

#### INTERRUPT POINTER TABLE

## 8086 INSTRUCTION

|     | _0                |                 |                |                 |               |               |                |                |

|-----|-------------------|-----------------|----------------|-----------------|---------------|---------------|----------------|----------------|

| i \ | 0                 | 1               | 2              | 3               | 4             | 5             | 6              | 7              |

| 0   | ADD<br>b,f,r/m    | ADD<br>w,f,r/m  | ADD<br>b,t,r/m | ADD<br>w,t,r/m  | ADD<br>b, ia  | ADD<br>w, ia  | PUSH<br>ES     | POP<br>ES      |

| 1   | ADC<br>b,f,r/m    | ADC<br>w,f,r/m  | ADC<br>b,t,r/m | ADC<br>w,t,r/m  | ADC<br>b,i    | ADC<br>w,i    | PUSH<br>SS     | POP<br>SS      |

| 2   | AND<br>b.f,r/m    | AND<br>w,f,r/m  | AND<br>b,t,r/m | AND<br>w,t,r/m  | AND<br>b,i    | AND<br>w.i    | SEG<br>=ES     | DAA            |

| 3   | XOR<br>b,f,r/m    | XOR<br>w.f.r/m  | XOR<br>b,t,r/m | XOR<br>w,t,r/m  | XOR<br>b,i    | XOR<br>w,i    | SEG<br>=SS     | AAA            |

| 4   | INC<br>AX         | INC<br>CX       | INC<br>DX      | INC<br>BX       | INC<br>SP     | INC<br>BP     | INC<br>SI      | INC<br>DI      |

| 5   | PUSH<br>AX        | PUSH<br>CX      | PUSH<br>DX     | PUSH<br>BX      | PUSH<br>SP    | PUSH<br>BP    | PUSH<br>SI     | PUSH<br>DI     |

| 6   |                   |                 |                |                 |               |               |                |                |

| 7   | JO                | JNO             | JB/<br>JNAE    | JNB/<br>JAE     | JE/<br>JZ     | JNE/<br>JNZ   | JBE/<br>JNA    | JNBE/<br>JA    |

| 8   | Immed<br>b,r/m    | immed<br>w,r/m  | Immed<br>b,r/m | Immed<br>is,r/m | TEST<br>b,r/m | TEST<br>w,r/m | XCHG<br>b,r/m  | XCHG<br>w,r/m  |

| 9   | NOP               | XCHG<br>CX      | XCHG<br>DX     | XCHG<br>BX      | XCHG<br>SP    | XCHG<br>BP    | XCHG<br>SI     | XCHG<br>DI     |

| A   | MOV<br>m - AL     | MOV<br>m - AX   | MOV<br>AL → m  | MOV<br>AX - m   | MOVS<br>b     | MOVS<br>w     | CMPS<br>b      | CMPS<br>w      |

| В   | MOV<br>i → AL     | MOV<br>i → CL   | MOV<br>i → DL  | MOV<br>i — BL   | MOV<br>i → AH | MOV<br>i → CH | MOV<br>i → DH  | M0V<br>i → BH  |

| С   |                   |                 | RET.<br>(i+SP) | RET             | LES           | LDS           | MOV<br>b,i,r/m | MOV<br>w,i,r/m |

| 0   | Shift<br>b        | Shift<br>w      | Shift<br>b,v   | Shift<br>W,V    | AAM           | AAD           |                | XLAT           |

| Ε   | LOOPNZ/<br>LOOPNE | LOOPZ/<br>LOOPE | L00P           | JCXZ            | IN<br>b       | IN<br>W       | OUT<br>b       | OUT<br>w       |

| F   | LOCK              |                 | REP            | REP             | HLT           | СМС           | Grp 1<br>b,r/m | Grp 1<br>w,r/m |

b = byte operation

d = direct

f = from CPU reg

i = immediate

ia = immed. to accum.

id = indirect

is = immed. byte, sign ext. I = long ie. intersegment

m = memory r/m = EA is second byte si = short intrasegment sr = segment register t = to CPU reg v = variable

w = word operation

z = zero

## SET MATRIX

| \    | Lo             |                |                  |                |                 |               |                 |                |

|------|----------------|----------------|------------------|----------------|-----------------|---------------|-----------------|----------------|

| Hi \ | 8              | 9              | A                | В              | С               | 0             | E               | F              |

| 0    | OR<br>b,f,r/m  | OR<br>w.f.r/m  | OR<br>b,t,r/m    | OR<br>w.t.r/m  | OR<br>b.i       | OR<br>w.i     | PUSH<br>CS      |                |

| 1    | SBB<br>b.f.r/m | SBB<br>w.f.r/m | SBB<br>b.t.r/m   | SBB<br>w.t.r/m | SBB<br>b.i      | SBB<br>w.i    | PUSH<br>DS      | POP<br>DS      |

| 2    | SUB<br>b,f,r/m | SUB<br>w.f.r/m | SUB<br>b.t.r/m   | SUB<br>w.t,r/m | SUB<br>b.i      | SUB<br>w.i    | SEG<br>CS       | DAS            |

| 3    | CMP<br>b.f.r/m | CMP<br>w.f.r/m | CMP<br>b.t.r/m   | CMP<br>w.t,r/m | CMP<br>b.i      | CMP<br>w.i    | SEG<br>DS       | AAS            |

| 4    | DEC<br>AX      | DEC<br>CX      | DEC<br>DX        | DEC<br>BX      | DEC<br>SP       | DEC<br>BP     | DEC<br>SI       | DEC<br>DI      |

| 5    | POP<br>AX      | POP<br>CX      | POP<br>DX        | POP<br>BX      | POP<br>SP       | POP<br>BP     | POP<br>SI       | POP<br>DI      |

| 6    |                |                |                  |                |                 |               |                 |                |

| 7    | JS             | JNS            | JP/<br>JPE       | JNP/<br>JPO    | JL/<br>JNGE     | JNL/<br>JGE   | JLE/<br>JNG     | JNLE/<br>JG    |

| 8    | MOV<br>b,f,r/m | MOV<br>w.f.r/m | MOV<br>b.t.r/m   | MOV<br>w.t.r/m | MOV<br>sr.t.r/m | LEA           | MOV<br>sr.f.r/m | POP<br>r/m     |

| 9    | CBW            | CWD            | CALL<br>I.d      | WAIT           | PUSHF           | POPF          | SAHF            | LAHF           |

| A    | TEST<br>b.i    | TEST<br>w.i    | STOS<br>b        | STOS<br>w      | LODS<br>b       | LODS<br>w     | SCAS<br>b       | SCAS<br>w      |

| В    | MOV<br>i → AX  | MOV<br>i → CX  | MOV<br>i → DX    | MOV<br>i → BX  | MOV<br>i → SP   | MOV<br>i → BP | MOV<br>i → SI   | MOV<br>i - DI  |

| C    |                |                | RET.<br>I.(i+SP) | RET<br>I       | INT<br>Type 3   | INT<br>(Any)  | INTO            | IRET           |

| 0    | ESC<br>0       | ESC<br>1       | ESC<br>2         | ESC<br>3       | ESC.            | ESC<br>5      | ESC<br>6        | ESC<br>7       |

| E    | CALL<br>d      | JMP<br>d       | JMP<br>I,d       | JMP<br>si.d    | IN<br>v,b       | IN<br>v.w     | OUT<br>v,b      | TUO<br>v,w     |

| F    | CLC            | STC            | CLI              | STI            | CLD             | STD           | Grp 2<br>b,r/m  | Grp 2<br>w.r/m |

|  |  |  | 180 |

|--|--|--|-----|

|  |  |  |     |

| mod r/m | 000  | 001 | 010  | 011          | 100       | 101        | 110  | 111  |

|---------|------|-----|------|--------------|-----------|------------|------|------|

| Immed   | ADD  | OR  | ADC  | SBB          | AND       | SUB        | XOR  | CMP  |

| Shift   | ROL  | ROR | RCL  | RCR          | SHL/SAL   | SHR        |      | SAR  |

| Grp 1   | TEST | _   | NOT  | NEG          | MUL       | IMUL       | DIV  | IDIV |

| Grp 2   | INC  | DEC | CALL | CALL<br>1.id | JMP<br>id | JMP<br>Lid | PUSH | _    |

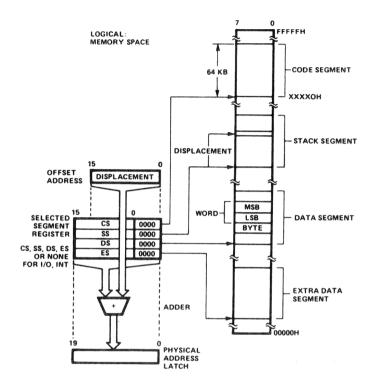

#### MEMORY SEGMENTATION MODEL

#### **SEGMENT OVERRIDE PREFIX**

0 0 1 reg 1 1 0

Timing: 2 clocks

## **USE OF SEGMENT OVERRIDE**

| Operand Register                      | Default | With Override Prefix |

|---------------------------------------|---------|----------------------|

| IP (code address)                     | CS      | Never                |

| SP (stack address)                    |         | Never                |

| BP (stack address or stack marker)    | SS      | BP + DS or ES, or CS |

| SI or DI (not incl. strings)          | DS      | ES, SS, or CS        |

| SI (implicit source addr for strings) | DS      | ES, SS, or CS        |

| DI (implicit dest addr for strings)   | ES      | Never                |

#### DATA TRANSFER

MOV = Move

Register/memory to/from register

100010dw mod reg r/m

Timing (clocks): register to register

memory to register 8+EA register to memory 9+EA

Immediate to register/memory

1 1 0 0 0 1 1 w mod 0 0 0 r/m data data if w=1

Timing: 10+EA clocks

Immediate to register

1 0 1 1 w reg data data if w=1

Timing: 4 clocks

Memory to accumulator

1 0 1 0 0 0 0 w addr-low addr-high

Timing: 10 clocks

Accumulator to memory

1 0 1 0 0 0 1 w addr-low addr-high

Timing: 10 clocks

Register/memory to segment register

10001110 mod 0 reg r/m

Timing (clocks): register to register 2

memory to register 8+EA

Segment register to register/memory

1 0 0 0 1 1 0 0 mod 0 reg r/m

Timing (clocks): register to register

register to register 2 register to memory 9+EA

**PUSH** = Push Register/memory

negister/memory

1 1 1 1 1 1 1 1 mod 1 1 0 r/m

Timing (clocks): register memory

Register

0 1 0 1 0 reg

Timing: 10 clocks

(Continued on following page)

10

16+EA

```

Seament register

XLAT = Translate byte to AL

0 0 0 reg 1 1 0

11010111

Timing: 10 clocks

Timing: 11 clocks

POP = Pop

LEA = Load EA to register

Register/memory

mod reg r/m

10001101

10001111

mod 0 0 0 r/m

Timing: 2+EA clocks

Timing (clocks):

register

17+FA

memory

LDS = Load pointer to DS

Register

11000101

mod reg r/m

0 1 0 1 1 req

Timing: 16+EA clocks

Timing: 8 clocks

LES = Load pointer to ES

Segment register

1 1 0 0 0 1 0 0 mod reg r/m

0 0 0 reg 1 1 1

Timing: 16+EA clocks

Timing: 8 clocks

LAHF = Load AH with flags

XCHG = Exchange

10011111

Register/memory with register

Timing: 4 clocks

1000011w mod reg r/m

SAHF = Store AH into flags

register with register

Timing (clocks):

10011110

memory with register

17+EA

Timing: 4 clocks

Register with accumulator

PUSHF = Push flags

10010 reg

10011100

Timing: 3 clocks

IN = Input to AL/AX from

Timing: 10 clocks

Fixed port

POPF = Pop flags

1110010w

port

10011101

Timing: 10 clocks

Timing: 8 clocks

Variable port (DX)

ARITHMETIC

1110110 w

ADD = Add

Reg./memory with register to either

Timing: 8 clocks

000000dw/mod reg r/m

OUT = Output from AL/AX to

Fixed port

Timing (clocks):

register to register

memory to register

9+EA

1110011w

port

register to memory

16+EA

Timing: 10 clocks

Immediate to register/memory

Variable port (DX)

100000sw mod000 r/m

data

data if s:w=01

1110111w

Timing (clocks):

immediate to register

Timing: 8 clocks

immediate to memory

17+EA

Mnemonics © Intel, 1978.

(Continued on following page) Mnemonics © Intel, 1978.

5

```

| mmediate to accu                         |                                                        |               |                | 100000sw         | mod 1 0 1 r/m                                        | data           | data if s:w=01 |

|------------------------------------------|--------------------------------------------------------|---------------|----------------|------------------|------------------------------------------------------|----------------|----------------|

| 0 0 0 0 0 1 0 w                          | data                                                   | data if w=1   |                | Timing (clocks): |                                                      |                | 4              |

| Timing: 4 clocks                         |                                                        |               |                | A state for a    |                                                      | n memory 17+EA | `              |

| ADC = Add with o                         |                                                        |               |                | Immediate from   |                                                      | data if w=1    | ì              |

| Reg./memory with                         |                                                        | r             |                | 0 0 1 0 1 1 0 w  | data                                                 | Uata II W=I    |                |

| 0 0 0 1 0 0 d w                          |                                                        |               |                | Timing: 4 clocks | *** * * * * * * * * * * * * * * * * * *              |                |                |

| Timing (clocks):                         | register to regis<br>memory to regi<br>register to mem | ster 9+EA     |                |                  | d register to eithe                                  | r              |                |

| Immediate to regi                        | 3                                                      |               | 1              | 0 0 0 1 1 0 d w  |                                                      |                | _              |

| 1 0 0 0 0 0 s w                          |                                                        | data          | data if s:w=01 | Timing (clocks): | register from re<br>memory from r                    | 9.0,0.         | 3<br><b>\</b>  |

| Timing (clocks):                         | immediate to re                                        | egister 4     |                |                  | register from n                                      |                | A              |

| mining (Clocks).                         | immediate to m                                         | 9.0.0.        |                | Immediate from   | register/memory                                      |                |                |

| Immediate to acc                         | umulator                                               |               |                | 100000sw         | mod 0 1 1 r/m                                        | data           | data if s:w=01 |

| 0 0 0 1 0 1 0 w                          | data                                                   | data if w=1   |                | Timing (clocks): | immediate from                                       | n register     | 4<br>\         |

| Timing: 4 clocks                         |                                                        |               |                | Immediate from   | accumulator                                          | -              |                |

| INC = Increment                          |                                                        |               |                | 0 0 0 1 1 1 0 w  | data                                                 | data if w=1    | 1              |

| Register/memory                          |                                                        |               |                | Timing: 4 clocks |                                                      |                | •              |

| 1 1 1 1 1 1 1 w                          | mod 0 0 0 r/m                                          |               |                | DEC = Decreme    |                                                      |                |                |

| Timing (clocks):                         | register                                               | 2<br>15+EA    |                | Register/memory  | /                                                    | _              |                |

|                                          | memory                                                 | ISTEA         |                | 1 1 1 1 1 1 1 w  | mod 0 0 1 r/m                                        |                |                |

| Register                                 |                                                        |               |                | Timing (clocks): |                                                      |                | 2              |

| 0 1 0 0 0 reg                            |                                                        |               |                |                  | memory                                               | 15+E/          | <b>A</b>       |

| Timing: 2 clocks                         |                                                        |               |                | Register         | 1                                                    |                |                |

| AAA = ASCII adju                         | ist for add                                            |               |                | 0 1 0 0 1 reg    | ]                                                    |                |                |

| 00110111                                 |                                                        |               |                | Timing: 2 clocks |                                                      |                |                |

| Timing: 4 clocks                         |                                                        |               |                | NEG = Change s   | +                                                    | 1              |                |

| DAA = Decimal a                          | djust for add                                          |               |                | 1 1 1 1 0 1 1 w  |                                                      |                |                |

| 00100111                                 |                                                        |               |                | Timing (clocks): | register<br>memory                                   | 16+E/          | 3<br>A         |

| Timing: 4 clocks                         |                                                        |               |                | CMP = Compare    | ,                                                    |                |                |

| <b>SUB</b> = Subtract<br>Reg./memory and | I register to eithe                                    | r             |                | Register/memory  | and register                                         | 1              |                |

| 0 0 1 0 1 0 d w                          | mod-reg r/m                                            |               |                | 0 0 1 1 1 0 d w  |                                                      | ]              | 2              |

| Timing (clocks):                         | register from remove from the                          | register 9+EA |                | Timing (clocks): | register with re<br>memory with r<br>register with m | egister 9+E/   |                |

|                                          | register from n                                        | nemorv 16+EA  |                |                  | I SCHOLOL WILLIAM                                    | 9 T L/         | •              |

Г

| Immediate with register/memory             |                | ODW Comment by Ass    |                                            |                        |

|--------------------------------------------|----------------|-----------------------|--------------------------------------------|------------------------|

| 1 0 0 0 0 0 s w mod 1 1 1 r/m data         | data if s:w=01 | CBW = Convert byte    | e to word                                  |                        |

| Timing (clocks): immediate with register   | 4              |                       |                                            |                        |

| immediate with memory 17-                  | +EA            | Timing: 2 clocks      |                                            |                        |

| Immediate with accumulator                 |                | CWD = Convert work    | d to double word                           |                        |

| 0 0 1 1 1 1 0 w data data if w=            | 1              | 10011001              |                                            |                        |

| Timing: 4 clocks                           |                | Timing: 5 clocks      |                                            |                        |

| AAS = ASCII adjust for subtract            |                | NOT = Invert          | LOGIC                                      |                        |

| 0 0 1 1 1 1 1 1                            |                |                       | 10.10                                      |                        |

| Timing: 4 clocks                           |                |                       | od 0 1 0 r/m                               | •                      |

| DAS = Decimal adjust for subtract          |                |                       | egister<br>nemory                          | 3<br>16+EA             |

| 0 0 1 0 1 1 1 1                            |                | SHL/SAL = Shift log   | ical/arithmetic left                       |                        |

| Timing: 4 clocks                           |                | 1 1 0 1 0 0 v w mo    | od 1 0 0 r/m                               |                        |

| MUL = Multiply (unsigned)                  |                | Timing (clocks): s    | single-bit register                        | 2                      |

| 1 1 1 1 0 1 1 w mod 1 0 0 r/m              |                |                       | single-bit memory<br>variable-bit register | 15+EA<br>8+4/bit       |

| Timing (clocks): 8-bit 71-                 | +EA            |                       | ariable-bit memory                         | 20+EA+4/bit            |

| 16-bit 124-                                | +EA            | SHR = Shift logical r | right                                      |                        |

| IMUL = Integer multiply (signed)           |                | 1 1 0 1 0 0 v w mo    | od 1 0 1 r/m                               |                        |

| 1 1 1 1 0 1 1 w mod 1 0 1 r/m              |                | Timing (clocks): s    | single-bit register                        | 2                      |

| • ( )                                      | +EA            |                       | single-bit memory<br>variable-bit register | 15+EA<br>8+4/bit       |

| 16-bit 144-                                | FEA            |                       | ariable-bit memory                         | 20+EA+4/bit            |

| AAM = ASCII adjust for multiply            |                |                       |                                            |                        |

| 1 1 0 1 0 1 0 0 0 0 0 0 1 0 1 0 D          |                |                       |                                            |                        |

| Timing: 83 clocks                          |                |                       |                                            |                        |

| DIV = Divide (unsigned)                    |                | SAR = Shift arithmeti |                                            |                        |

| 1 1 1 1 0 1 1 w mod 1 1 0 r/m              |                | 1 1 0 1 0 0 v w mo    |                                            | _                      |

|                                            | EA             | 3 (                   | ingle-bit register<br>ingle-bit memory     | 2<br>15+EA             |

| ,                                          | FEA            | V                     | ariable-bit register                       | 8+4/bit                |

| IDIV = Integer divide (signed)             |                |                       | ariable-bit memory                         | 20+EA+4/bit            |

| 1111011 w mod 111 r/m                      |                | ROL = Rotate left     |                                            |                        |

| Timing (clocks): 8-bit 112-<br>16-bit 177- |                |                       | d 0 0 0 r/m                                | •                      |

| AAD = ASCII adjust for divide              |                | 3 (                   | ingle-bit register<br>ingle-bit memory     | 2<br>15+EA             |

| 1 1 0 1 0 1 0 1 0 0 0 0 1 0 1 0            |                |                       | ariable-bit register<br>ariable-bit memory | 8+4/bit<br>20+EA+4/bit |

| Timing: 60 clocks                          |                | V                     | ariable-bit memory                         | ZUTEMT4/DIL            |

| 8 Mnemonics ♥ Intel, 1978.                 |                |                       | Mnemonics © Intel, 1978.                   | 9                      |

|                        | nod 0 0 1 r/m                                         |                            |                                                                                                       |  |  |  |  |

|------------------------|-------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| Timing (clocks):       | 10000117711                                           |                            | 1 1 1 1 0 1 1 w   mod 0 0 0 r/m   data   data if w                                                    |  |  |  |  |

| Timing (clocks):       | ,                                                     | 2<br>+EA<br>4/bit<br>4/bit | Timing (clocks): immediate with register 4 immediate with memory 10+EA Immediate data and accumulator |  |  |  |  |

| RCL = Rotate thro      | •                                                     |                            | 1 0 1 0 1 0 0 w data data if w=1                                                                      |  |  |  |  |

| 1 1 0 1 0 0 v w Ir     |                                                       | 1                          | Timing: 4 clocks                                                                                      |  |  |  |  |

| Timing (clocks):       | single-bit register single-bit memory 15              | 2<br>+EA<br>4/bit          | OR = Or Reg./memory and register to either  0 0 0 0 1 0 d w mod reg r/m                               |  |  |  |  |

| RCR = Rotate thro      | •                                                     | 4/ DIL                     | Timing (clocks): register to register 3                                                               |  |  |  |  |

|                        | nod 0 1 1 r/m                                         |                            | memory to register 9+EA register to memory 16+EA                                                      |  |  |  |  |

| Timing (clocks):       | single-bit register                                   | 2                          | Immediate to register/memory                                                                          |  |  |  |  |

| rinning (Clocks).      |                                                       | +EA                        | 1 0 0 0 0 0 0 w mod 0 0 1 r/m data data if w                                                          |  |  |  |  |

|                        | variable-bit register 8+- variable-bit memory 20+EA+- | 4/bit<br>4/bit             | Timing (clocks): immediate to register 4 immediate to memory 17+EA                                    |  |  |  |  |

| AND = And              |                                                       |                            | Immediate to accumulator                                                                              |  |  |  |  |

| Reg./memory and        | register to either                                    |                            | 0 0 0 0 1 1 0 w data data if w=1                                                                      |  |  |  |  |

| 001000dw               | nod reg r/m                                           |                            | Timing: 4 clocks                                                                                      |  |  |  |  |

| Timing (clocks):       | register to register 9+EA register to memory 16+EA    | ,                          | XOR = Exclusive or Reg./memory and register to either                                                 |  |  |  |  |

| mmediate to regis      | ,                                                     |                            | 0 0 1 1 0 0 d w mod reg r/m                                                                           |  |  |  |  |

|                        | nod 1 0 0 r/m data                                    | data if w=1                | Timing (clocks): register to register 3 memory to register 9+EA                                       |  |  |  |  |

| Timing (clocks):       | immediate to register 4                               |                            | register to memory 16+EA                                                                              |  |  |  |  |

| illing (clocks).       | immediate to register                                 | •                          | Immediate to register/memory                                                                          |  |  |  |  |

| mmediate to accu       | mulator                                               |                            | 1 0 0 0 0 0 0 w mod 1 1 0 r/m data data if w                                                          |  |  |  |  |

| 0 0 1 0 0 1 0 w        | data data if w=1                                      |                            | Timing (clocks): immediate to register 4 immediate to memory 17+EA                                    |  |  |  |  |

| rinning. 4 clocks      |                                                       | 1                          | Immediate to accumulator                                                                              |  |  |  |  |

| EST = And functi       | on to flags, no result                                | f                          | 0 0 1 1 0 1 0 w data data if w=1                                                                      |  |  |  |  |

| Register/memory a      | nd register                                           | l                          | Timing: 4 clocks                                                                                      |  |  |  |  |

| 1000010w               | nod reg r/m                                           |                            | STRING MANIPULATION                                                                                   |  |  |  |  |

| Timing (clocks):       | register to register 3<br>register with memory 9+EA   |                            | REP = Repeat                                                                                          |  |  |  |  |

| Continued on following | page                                                  |                            | Timing: 6 clocks/loop                                                                                 |  |  |  |  |

10

**MOVS** = Move String 1010010w Timing: 17 clocks CMPS = Compare String 1010011w Timing: 22 clocks SCAS = Scan String 1010111w Timina: 15 clocks LODS = Load String

1010110w

Timing: 12 clocks STOS = Store String

1010101w

Timing: 10 clocks

#### CONTROL TRANSFER

NOTE: Queue reinitialization is not included in the timing information for transfer operations. To account for instruction loading, add 8 clocks to timing numbers.

## CALL = Call

Direct within segment

11101000 disp-low disp-high

Timing: 11 clocks

Indirect within segment

1 1 1 1 1 1 1 1 mod 0 1 0 r/m

Direct intersegment

Timing: 13+EA clocks

10011010 offset-low offset-high Timing: 20 clocks seg-low seg-high

Indirect intersegment

1 1 1 1 1 1 1 1 mod 0 1 1 r/m

Timing: 29+EA clocks

JMP = Unconditional Jump Direct within segment

11101001 disp-low disp-high

Timing: 7 clocks

Direct within segment-short

11101011 disp

Timina: 7 clocks Indirect within seament

1111111 | mod 100 r/m

Timing: 7+EA clocks Direct intersegment

11101010 offset-low offset-high Timing: 7 clocks seg-low sea-hiah

Indirect interseament

1111111 mod 101 r/m

Timing: 16+EA clocks

**RET** = Return from CALL Within segment

11000011

Timing: 8 clocks

Within seg. adding immed to SP

11000010 data-low data-high

Timing: 12 clocks Intersegment

11001011

Timing: 18 clocks

Intersegment, adding immediate to SP

11001010 data-low data-high

Timing: 17 clocks

JE/JZ = Jump on equal/zero

01110100 disp

Timing (clocks): Jump is taken

Jump is not taken

8

| JL/JNGE = Jump         | on less/not greater or equal       |        |   | JNLE/JG = Jump   | on not less or equal/great         | er        |

|------------------------|------------------------------------|--------|---|------------------|------------------------------------|-----------|

| 0 1 1 1 1 1 0 0        | disp                               |        |   | 0 1 1 1 1 1 1 1  | disp                               |           |

| Timing (clocks):       | Jump is taken<br>Jump is not taken | 8<br>4 |   | Timing (clocks): | Jump is taken<br>Jump is not taken | 8<br>4    |

| JLE/JNG = Jump         | on less or equal/not greater       | •      |   | JNB/JAE = Jump   | on not below/above or eq           | ual       |

| 0 1 1 1 1 1 1 0        | disp                               |        |   | 01110011         | disp                               |           |

| Timing (clocks):       | Jump is taken<br>Jump is not taken | 8<br>4 | • | Timing (clocks): | Jump is taken Jump is not taken    | 8<br>4    |

| JB/JNAE = Jump         | on below/ not above or equ         | al     |   | JNBE/JA = Jump   | on not below or equal/abo          | ove       |

| 01110010               | disp                               |        |   | 01110111         | disp                               |           |

| Timing (clocks):       | Jump is taken<br>Jump is not taken | 8<br>4 |   | Timing (clocks): | Jump is taken<br>Jump is not taken | 8<br>4    |

| JBE/JNA = Jump         | on below or equal/not abov         | е      |   | JNP/JPO = Jump   | on not parity/parity odd           |           |

| 01110110               | disp                               |        |   | 01111011         | disp                               |           |

| Timing (clocks):       | Jump is taken<br>Jump is not taken | 8<br>4 |   | Timing (clocks): | Jump is taken Jump is not taken    | 8 4       |

| IP/JPE = Jump or       | n parity/parity even               |        |   | JNO = Jump on r  | not overflow                       |           |

| 0 1 1 1 1 0 1 0        | disp                               |        |   | 01110001         | disp                               |           |

| Timing (clocks):       | Jump is taken<br>Jump is not taken | 8<br>4 |   | Timing (clocks): | Jump is taken<br>Jump is not taken | 8 4       |

| JO = Jump on ove       | erflow                             |        |   | JNS = Jump on n  | ot sign                            |           |

| 01110000               | disp                               |        |   | 01111001         | disp                               |           |

| Timing (clocks):       | Jump is taken<br>Jump is not taken | 8<br>4 |   | Timing (clocks): | Jump is taken<br>Jump is not taken | 8<br>4    |

| JS = Jump on sig       | n                                  |        |   | LOOP = Loop CX   | times                              |           |

| 01111000               | disp                               |        |   | 11100010         | disp                               |           |

| Timing (clocks):       | Jump is taken<br>Jump is not taken | 8<br>4 |   | Timing (clocks): | Jump is taken<br>Jump is not taken | 9         |

| JNE/JNZ = Jump         | on not equal/not zero              |        |   | LOOPZ/LOOPE =    | Loop while zero/equal              |           |

| 01110101               | disp                               |        |   | 11100001         | disp                               |           |

| Timing (clocks):       | Jump is taken<br>Jump is not taken | 8<br>4 |   | Timing (clocks): | Jump is taken<br>Jump is not taken | 11<br>5   |

| JNL/JGE = Jump         | on not less/greater or equa        | I      |   | LOOPNZ/LOOPN     | IE = Loop while not zero/ i        | not equal |

| 01111101               | disp                               |        |   | 11100000         | disp                               |           |

| Timing (clocks):       | Jump is taken<br>Jump is not taken | 8<br>4 |   | Timing (clocks): | Jump is taken<br>Jump is not taken | 11<br>5   |

| Continued on following | g page)                            |        |   |                  | •                                  |           |

| 14                     | Macmonice © Intel 1978             |        |   |                  | Magmonics © Intel 1978             |           |

## JCXZ = Jump on CX zero

| 1 |   |   |   |   | _ |   |   |   |      |

|---|---|---|---|---|---|---|---|---|------|

|   | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | disp |

Timing (clocks): Jump is taken Jump is not taken

## 8086 CONDITIONAL TRANSFER OPERATIONS

| nstruction | Condition               | Interpretation                   |

|------------|-------------------------|----------------------------------|

| JE or JZ   | ZF = 1                  | "equal" or "zero"                |

| JL or JNGE | (SF xor OF) = 1         | "less" or "not greater or equal" |

| JLE or JNG | ((SP xor OF) or ZF) = 1 | "less or equal" or "not greater" |

| B or JNAE  | CF = 1                  | "below" or "not above or equal"  |

| DE INIA    | 105 - 75                |                                  |

JBE or JNA (CF or ZF) = 1 "below or equal" or "not above" JP or JPF PF = 1 "parity" or "parity even" JO OF = 1 "overflow"

JS SF = 1 "sign" JNE or JNZ ZF = 0"not equal" or "not zero" JNL or JGE (SF xor OF) = 0 "not less" or "greater or equal" JNLE or JG ((SF xor OF) or "not less or equal" or "greater"

JNB or JAE | CF = 0 "not below" or "above or equal" JNBE or JA (CF or ZF) = 0 "not below or equal" or "above" JNP or JPO PF = 0 "not parity" or "parity odd" JNO OF = 0"not overflow"

"not sian"

# INT = Interrupt

## Type specified

JNS

11001101 type Timing: 50 clocks

ZF) = 0

SF = 0

Type 3 11001100

Timing: 51 clocks

## INTO = Interrupt on overflow

11001110

Timing: 52 clocks if pass 4 clocks if fail

## IRET = Interrupt return

11001111 Timing: 24 clocks

16 Mnemonics © Intel, 1978.

## PROCESSOR CONTROL

#### STC = Set carry CLC = Clear carry

11111000 11111001

Timing: 2 clocks Timing: 2 clocks

**CMC** = Complement carry NOP = No operation

11110101 10010000 Timina: 3 clocks

Timing: 2 clocks

CLD = Clear direction STD = Set direction

11111101 11111100 Timing: 2 clocks

Timina: 2 clocks

CLI = Clear interrupt STI = Set interrupt

11111010 11111011 Timina: 2 clocks Timing: 2 clocks

HLT = Halt 11110100 10011011 Timing: 3 clocks Timing: 2 clocks

LOCK = Bus lock prefix ESC = Escape (to external device) 1 1 0 1 1 x x x | mod x x x r/m 111110000

WAIT = Wait

Timing: 7+EA clocks Timing: 2 clocks

## Footnotes:

if d = 1 then "to"; if d = 0 then "from"

if w = 1 then word instruction; if w = 0 then byte instruction if s:w = 01 then 16 bits of immediate data form the operand if s;w = 11 then an immediate data byte is sign extended to form the

16-bit operand if v = 0 then "count" = 1; if v = 1 then "count" in (CL) x = don't care

z is used for some string primitives to compare with ZF FLAG

AL = 8-bit accumulator AX = 16-bit accumulator CX = Count register

DS = Data segment DX = Variable port register

ES = Extra segment

Above/below refers to unsigned value

Greater = more positive; Less = less positive (more negative) signed values

See page 1 for Operand Summary. See page 2 for Segment Override Summary.

<sup>&</sup>quot;"Above" and "below" refer to the relation between two unsigned values, while "greater" and "less" refer to the relation between two signed values.