# THE INTEL MEMORY DESIGN HANDBOOK

**AUGUST 1973**

### THE INTEL MEMORY DESIGN HANDBOOK

#### **CONTENTS**

| 1. | Organization and Operation of Fixed Address RAM  | 1-1  |

|----|--------------------------------------------------|------|

|    | Introduction                                     | 1-1  |

|    | Designs Using Bipolar and Static MOS Circuits    | 1-3  |

|    | Dynamic MOS Memory — The 1103                    | 1-10 |

| 2. | Read Only Memories — ROMs and PROMs              | 2-1  |

|    | Introduction                                     | 2-1  |

|    | Electrically Programmable MOS ROMs               | 2-2  |

|    | PROMs — Field Programmable Bipolar ROMs          | 2-6  |

|    | Preparing Data for ROMs/PROMs                    | 2-8  |

|    | ROM Implementation of Generalized Logic          | 2-9  |

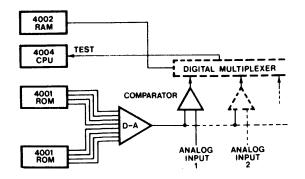

|    | Example of ROM Application                       | 2-12 |

| 3. | Serially Accessed Semiconductor Memory —         |      |

|    | SHIFT REGISTERS                                  |      |

|    | Introduction                                     |      |

|    | Principles of Operation                          |      |

|    | Circuit Considerations                           |      |

|    | Power Considerations in Shift Registers          |      |

|    | RAMs as Serial Memory                            | 3-7  |

|    | Application of Shift Registers                   | 3-8  |

| 4. | Other Memory Structures — CAMs, Buffer Memories, |      |

|    | and Multiport Memories                           | 4-1  |

|    | Introduction                                     | 4-1  |

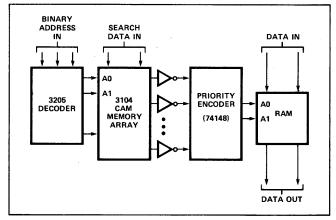

|    | Content Addressable Memory (CAM)                 | 4-2  |

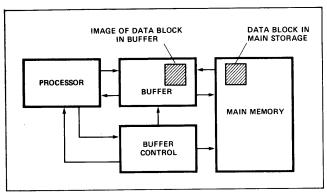

|    | Buffer Memories                                  | 4-5  |

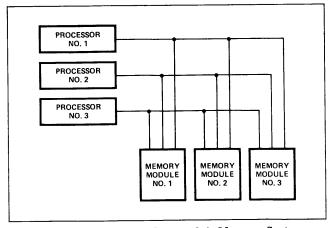

|    | Multiport Memories                               | 4-6  |

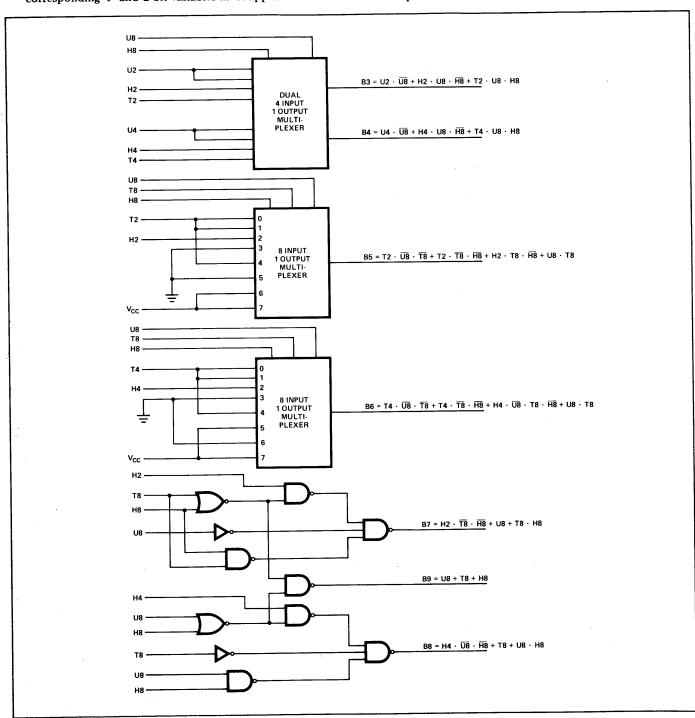

| 5. | BCD Addressing                                   | 5-1  |

| 6. | Appendices                                       | 6-1  |

|    | Appendix A — Silicon Gate MOS                    | 6-2  |

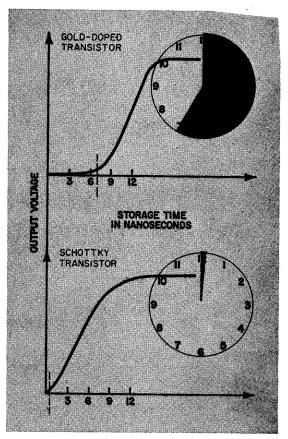

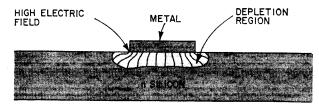

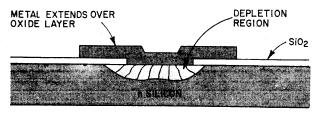

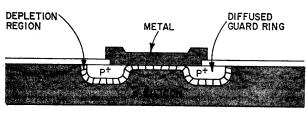

|    | Appendix B — Schottky Bipolar Technology         | 6-6  |

|    | Appendix C — Article Reprints                    | 6-7  |

|    |                                                  |      |

#### PREFACE

It is hoped that these notes will be of assistance to the designer who requires memory function in his system. The variety of semiconductor memory products is already quite extensive and is growing rapidly. This booklet has attempted to give some understanding of the characteristics of the types of memory now available and some hints about how to solve a few system design problems. However, the variety of applications is so broad that is has been possible only to very briefly touch upon a few of them.

#### INTRODUCTION

Memory function is one of the most important elements of a digital computer. Large computer systems often contain many types of memories: reels of tape and drawers of cards, disk cartridges, ferrite core or semiconductor main storage, fast registers, etc. Each of these different types of memory offers a means for storing and retrieving data (and programs which are also "data") for use by the computer system, yet they differ in cost, organization, retrieval time, etc.

Memory function is also important to many other systems which utilize digital processing. Digital filters, computer terminals, electronic cash registers, traffic-light controllers — all may require data storage to achieve their intended function.

Today there are many types of memory available to the designer. One of the most recent additions to the repertory of memory technologies is the semiconductor memory. In fact, there are many new semiconductor memory components, which utilize different technologies, and offer different organizations, operating characteristics, etc.

The purpose of this booklet is to offer the designer some basic information about the types of semiconductor memory available and how to utilize them effectively.

The booklet is divided into six parts. Part 1 describes basic random access, fixed-address memories (RAMs). This type of memory organization is most commonly used as the main memory of general purpose digital computers, and is also used to realize fast registers or scratch-pad memories, many types of buffer memories, etc. Part 2 discusses Read Only Memories (ROMs) and Programmable Read Only Memories (PROMs) which are also almost always random-access, fixed-address memories as well. ROMs/PROMs are used for data tables, control units, as the main memory of certain dedicated special purpose computers, and to replace general random logic. Part 3 discusses serially addressed memory (shift registers). Part 4 discusses memory organizations other than fixed address, such as Content Addressable Memory (CAMs), buffered memories, virtual memory, etc. Part 5 discusses Binary Coded Decimal (BCD) Addressing techniques. Part 6 includes selected article reprints of process technology and device applications.

NOTICE: The circuits contained herein are suggested applications only. Intel Corporation makes no warranties whatsoever with respect to the completeness, accuracy, patent or copyright status, or applicability of the circuits to a user's requirements. The user is cautioned to check these circuits for applicability to his specific situation prior to use. The user is further cautioned that in the event a patent or copyright claim is made against him as a result of the use of these circuits, Intel shall have no liability to user with respect to any such claim.

#### Part 1

# Organization and Operation of Fixed Address RAM

| 1 46                                                |

|-----------------------------------------------------|

| INTRODUCTION 1-:                                    |

| DESIGNS USING BIPOLAR AND STATIC                    |

| MOS CIRCUITS 1-3                                    |

| A. Buffer Circuits 1-0                              |

| B. Access Time Considerations 1-                    |

| C. Chip Select Decoding 1-6                         |

| D. Power Consideration 1-8                          |

| E. Paging Techniques for Access Time Reduction. 1-9 |

| DYNAMIC MOS MEMORY - THE 1103 1-10                  |

| A. Operation of the 1103                            |

| B. Chip Select                                      |

| C. Clock Signal Amplitudes 1-14                     |

| D. Array Connection of 1103s 1-14                   |

| E. System Timing                                    |

| F. Power Considerations 1-25                        |

| G. Application Examples 1-29                        |

| H. Protection Against Catastrophic Damage 1-31      |

| I. Summary1-32                                      |

|                                                     |

#### INTRODUCTION

As defined here, a random access memory is one in which the writing time and retrieval (access or cycle) times are essentially independent of the location into which the data is entered. By fixed address, it is meant that data is entered into a known, pre-determined location, and is retrieved from that same location. In a fixed address RAM the data does not move around in the memory except by external control.

For many years, there has been just one practical way to build a random access high speed memory — use ferrite cores. But suddenly, the designer of memory systems is confronted with a proliferation of new semiconductor memory devices and a host of new rules and considerations to face. The designer who is now in that position, facing a pile of data sheets, and wondering where to start, shouldn't give up hope. Semiconductor memories are easy to use and offer high performance. Most important of all, some of the newest semiconductor components cost less per bit than core memory.

First consider some of the types of RAM building blocks now available. These can be first divided into three basic categories, related to the technology and circuit techniques used for their implementation:

#### 1. Bipolar

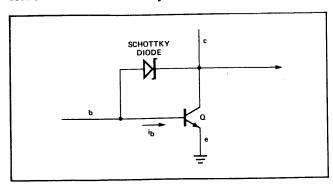

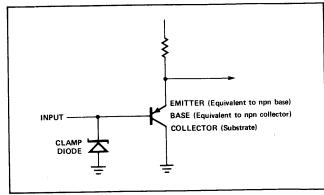

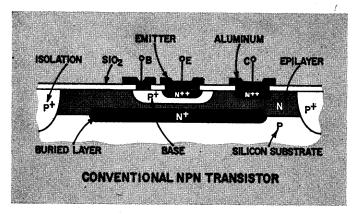

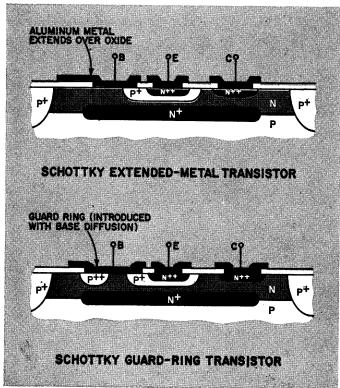

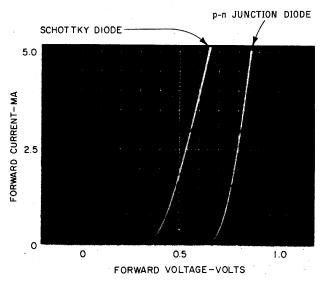

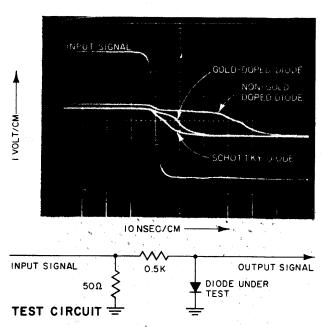

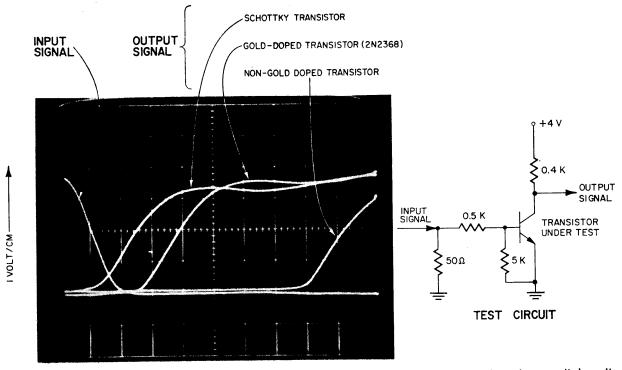

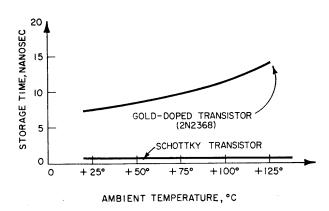

Bipolar technology is most familiar to the logic designer in the form of RTL, TTL, ECL, and other high performance low voltage circuit families. Bipolar circuits are so called because the technology primarily realizes npn bipolar junction transistors. Other components which can be integrated include resistors and junction diodes. A more recently developed bipolar technology, the Schottky technology, also allows Schottky diodes, and substrate and lateral pnp transistors.

Bipolar semiconductor memories offer high performance and are usually directly compatible with one or more of the standard bipolar logic families. Presently available are bipolar memories of up to 256 bits per chip. When compared to MOS memories, bipolar units are usually faster, but cost more and usually dissipate more power.

#### 2. Static MOS

Both static and dynamic MOS circuits use insulated gate field effect transistors as the primary circuit element. A few circuits may also include diffused resistors. However, in static circuits, the devices are used as if they were DC amplifiers while in dynamic circuit extensive use is made of capacitances for temporary storage.

In general, static MOS circuits are easier to use in systems than dynamic MOS circuits, but require more power and cost more per circuit function. With the availability of newer (low threshold voltage) MOS technology, many static MOS circuits can be directly interfaced to TTL or DTL logic circuits.

Static MOS designs are available in both n and p channel technologies. The n channel MOS technology offers even easier interface to TTL than the p channel technology. Static MOS memories are now available with up to 1024 bits per chip. These memories are usually slower than bipolar memories of a similar size by a factor of 5 to 10, but cost less because of the inherently higher yield and smaller size of the MOS devices.

#### 3. Dynamic MOS

Dynamic MOS circuits make use of temporary storage of data on the parasitic capacitances within the circuit. Due to leakages associated with junctions within the circuit, the charge on these capacitances may leak off in a few milliseconds. To prevent loss of data, this charge must be restored (refreshed). Restoration of the charge is achieved by regenerating or recirculating the data. Dynamic circuits usually require externally generated clock voltages. These clock voltages are usually too high to be generated with ordinary integrated circuits, so special ICs or discrete circuit components must often be used. As a result, dynamic circuits are usually more difficult to interface to standard bipolar logic families than the other types of circuits described above.

Although more difficult to use, dynamic MOS circuits offer some very significant advantages. The chip area required per unit function is much smaller than for either bipolar or static MOS. This high functional density combined with the higher yield or silicon-gate MOS technology, makes the dynamic MOS circuit the most economical of the three approaches, and permits large amounts of memory to be integrated on a single chip. 1024 bit dynamic MOS memories have been available for some time and larger units are in development. Speeds possible with dynamic MOS circuits are much faster than for static MOS, although usually not quite as fast as for bipolar circuits. Thus, because high functional density can be combined with high performance, dynamic MOS circuits are potentially the strongest contenders for use in large random access memory systems. Dynamic MOS circuits also offer the lowest power dissipation per function of the three basic approaches. In many cases, such circuits are designed so that they dissipate power only during access or data regeneration operations.

These properties are summarized in Table 1.1 below. Samples of different types of semiconductor memory elements are shown together with the technology used.

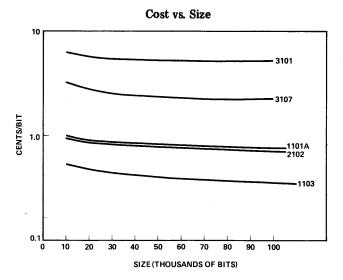

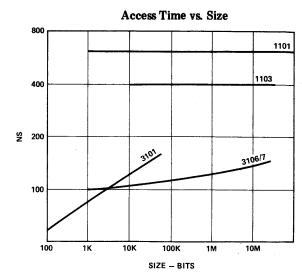

The access times and operating powers given in Table 1.1 refer to the memory parts themselves. However, when used in systems, actual access and cycle times are usually somewhat greater and may be affected significantly by memory size. In addition, system cost per bit may be a significant function of memory size. Figure 1.1 gives relative cost and access time for systems over a range of memory sizes for each of the products described above. Additional components for memory systems are assumed to be drawn from TTL logic families.

From the charts of Figure 1.1, the relative speed and cost of the different approaches can be determined. If speed is unimportant and a relatively large memory must be built, then the 1103 dynamic MOS RAM is the obvious choice. However, when the memory needed is small, one of the other components may be more economical, because they require less peripheral and control circuitry than does the dynamic MOS. In other cases, very high speed may be required so that one of the bipolar products must be used.

Table 1.1. Organization and Operation of Fixed Address RAM

|   | Part No. | Technology                 | Configuration | Access/Cycle | Operating Power/Bit | Standby Power/Bit |

|---|----------|----------------------------|---------------|--------------|---------------------|-------------------|

|   | 3101     | Bipolar                    | 16 x 4        | 60/60 ns     | 8 mW                | 8mW               |

|   | 3101A    | Bipolar                    | 16 x 4        | 35/35 ns     | 8mW                 | 8 mW              |

|   | 3106/7   | Bipolar                    | 256 x 1       | 80/80 ns     | 2.5 mW              | 2.5 mW            |

| ١ | 3106A/7A | Bipolar                    | 256 x 1       | 60/60 ns     | 2.5 mW              | 2.5 mW            |

|   | 1101A    | Static MOS -               | 256 x 1       | 1500/1500 ns | 2.5 mW              | .14 mW            |

|   | 2102     | Static MOS -<br>n-channel  | 1024 x 1      | 1000/1000 ns | .35 mW              | .09 mW            |

|   | 1103     | Dynamic MOS -<br>p-channel | 1024 x 1      | 300/600 ns   | .45 mW              | .06 mW            |

Figure 1.1. Memory System Characteristic vs. Size

Having chosen a suitable memory part for the basic building block of the system, the designer must next organize the system. The design of the static MOS memories is quite similar to that of bipolar memories. However, dynamic MOS random access memories may require a number of additional considerations,

# DESIGNS USING BIPOLAR and STATIC MOS CIRCUITS

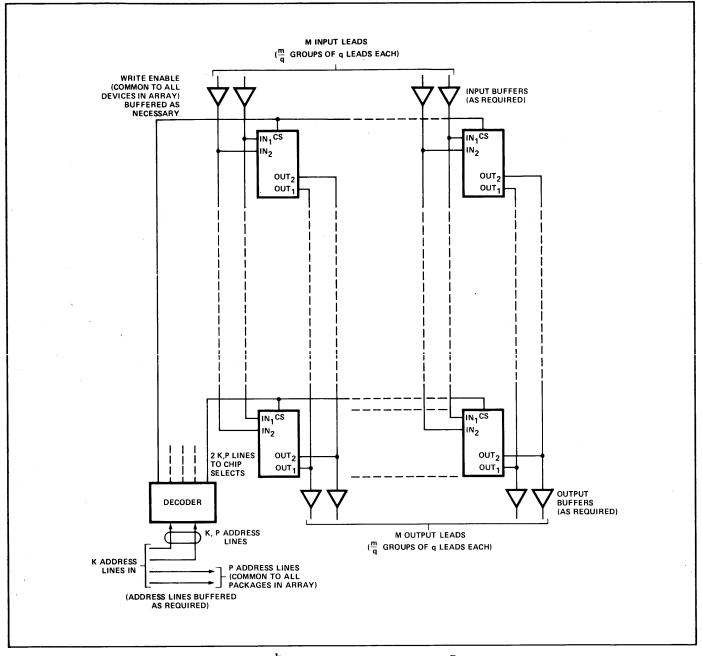

Fixed address RAMs are usually organized as [some number] N words of [some number] M bits each. N may be any value from 8 to 16 for scratch pad memories to several million for very large computer memories. M usually falls in the range of 6 to several hundred. Because most computers use binary arithmetic, the address which selects one of the N words is usually a binary value of some k bits, with N designed to be equal to a power of two, that is,  $2^k$ .

To some extent, these organizations are the result of ferrite core economics, for core memory costs are usually lowest when  $N=M^4$ . Semiconductor memory offers greater freedom of organization, with the organization limits being determined by the size of the basic building blocks, i.e., memory components. Not all words of a semiconductor memory need have the same number of bits, nor is it necessary for N to always be exactly some power of two. For example, when using  $1024 \times 1$  memory components such as the 1103 or 2102, a memory of 3036 or 5120 words could easily be constructed with a cost per bit about the same as for a 4096 word memory.

In general, each semiconductor memory chip realizes some

$2^P$  words of q bits each. As long as N is a multiple of  $2^P$  and M a multiple of q, an N word by M bit memory can be realized without wasting bits.

To build an N word by M bit memory from  $2^P$  word x q bit components, the components are effectively laid out in a two dimensional array. The array must include a total of  $N/2^P$  rows and M/q columns.

All of the semiconductor memory components listed in Table 1.1 are designed to make the connection in arrays as easy as possible, and with as few additional components as possible.

All permit several devices to have inputs and outputs connected to common input and output busses. One chip at a time is enabled for writing or reading (placing its data on an output bus) by means of a chip select signal.

To wire an array of  $2^P$  word by q bit chips as an  $N=2^k$  word memory, the array will contain  $2^{k-p}$  rows of M/q circuits (chips or packages) each.

Of the k address lines to the memory, p will be common to all chips. The remaining k-p address lines will be decoded

Figure 1.2. Organization of 2<sup>k</sup> Word by m Bit Memory from 2<sup>p</sup> Word by q Bit Memory

to generate  $2^{k-p}$  row select signals. One of these two select signals drives all of the chip select leads in the row.

Figure 1.2 shows this basic organization.

These general rules apply to most of the memory products listed in Table 1.1. Because the remaining considerations, buffer circuitry, etc. are quite different for dynamic MOS system than for bipolar and static MOS, the remainder of this section has been divided into two segments.

In general, the rules of wiring the array of Figure 1.2 are as follows:

1. All corresponding power supply leads are made common throughout the array. In general, a two dimensional grid should be used when possible. (See Figure 1.3.)

- 2. The write enable signal is made common throughout the array.

- 3. All corresponding addresses are made common throughout the array.

- 4. Corresponding data input and data output leads are made common within array columns.

- 5. Corresponding chip select leads are made common within each row. The function of the chip select leads is to permit the array interconnection. When conditions for chip (i.e., row) selection are not met, no input signal can affect the contents of that row, nor does any unselected chip affect the signals on the data output line to which it is attached. Thus the chip select leads permit output leads to be OR-

tied and eliminates the necessity to decode the write pulse signals.

The array of Figure 1.2 can be conveniently laid out using two printed circuit layers. In Figure 1.2, buffer circuits on address and data input and outputs have been indicated. The degree to which such buffer circuits are necessary is a function of the type of circuit used, the loading that can be tolerated by the external circuits, and the degradation in access and cycle time which is acceptable.

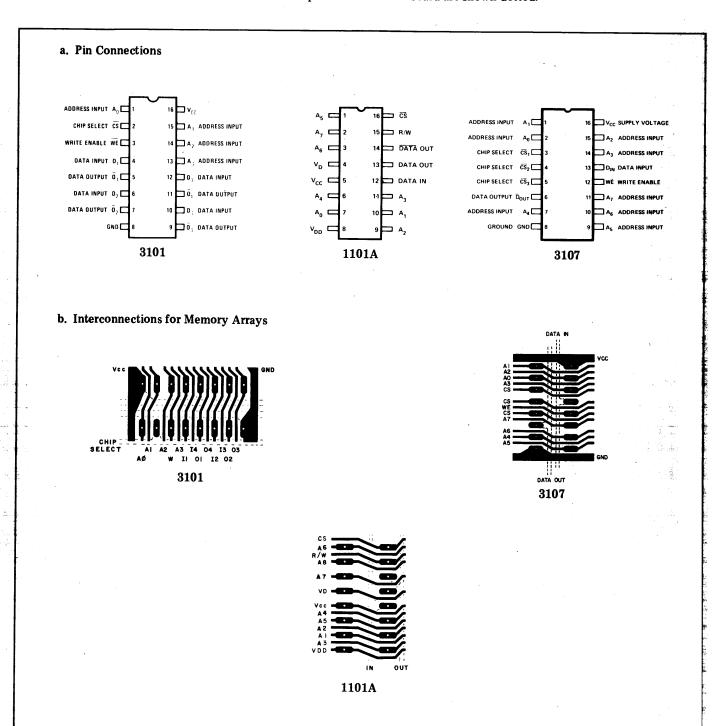

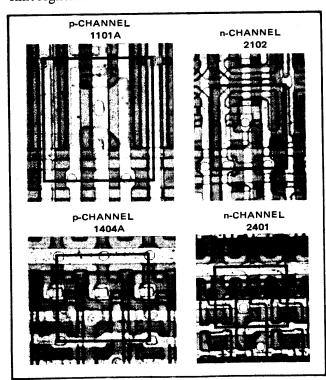

Figure 1.3a shows the pin connections for three of the parts

mentioned in table 1.1 and Figure 1.3b shows typical layouts for each of the memory parts included in this category, with the orientation of all layouts chosen so that chip selects run horizontally in rows and data leads run vertically in columns. The remaining leads are run in the most convenient direction. All of these layouts make use of leads running between the pins of the dual in line package. To prevent solder shorts, these lines are run on the component side of the board. In Figure 1.3b the lines on the soldered side of the board are shown dotted.

Figure 1.3. Printed Circuit Layout of Memory Arrays

#### A. BUFFER CIRCUITS

#### A.1 TTL to P-channel MOS

As an example of interfacing TTL to p-channel static MOS circuitry, consider the input requirements for the 1101A memory, which is realized with p-channel (low-threshold voltage) silicon gate MOS technology.

1101A inputs are essentially purely capacitive, so that when driving the 1101A memory arrays, the primary considerations involve: □ the effects of significant capacitive loads on address and data line buffers, and □ guaranteeing proper voltage levels on these lines.

Because 1101A memory arrays are usually relatively slow, the speed degradation associated with capacitive loads are usually not so important as the effects of reflecting large capacitive loads back into the driving capacity.

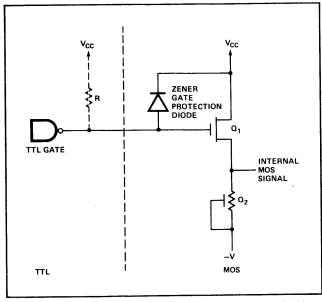

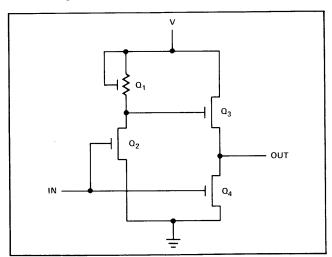

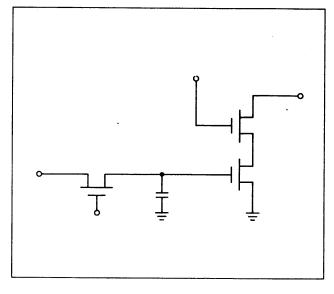

Figure 1.4 shows the nature of the TTL to 1101A static MOS interface. In Figure 1.4, Q<sub>1</sub> conducts when the TTL gate output is sufficiently negative with respect to  $V_{\hbox{\footnotesize CC}}$  (at least 4.5V below VCC). The ratio of geometries between  $Q_1$  and  $Q_2$  is chosen so that when  $Q_1$  conducts, the internal MOS signal line is brought within a volt or two of V<sub>CC</sub>. When the TTL gate output is high, Q1 does not conduct, and the internal MOS line is drawn toward the -V supply by  $Q_2$ . This high level must be no lower than  $V_{\rm CC}$  -2V. Resistor R should be added to guarantee proper operating levels, as TTL outputs without the resistor are only guaranteed to reach  $V_{\rm CC}$  -2.35V (7400 series). Note that the input signal voltage is referenced to VCC. It is, therefore, important that V<sub>CC</sub> be adequately bypassed to the TTL ground line. VCC is normally the same supply as used for the TTL logic. When driving p-channel MOS, it is undesirable to allow this voltage to fall too low, for noise immunity may suffer. Because the MOS input draws no DC current for normal bias, a very large number of devices may be driven by a single TTL gate, although the capacitive loading in large arrays may cause some speed degradation.

Figure 1.4. TTL to p-channel MOS Interface (1101A)

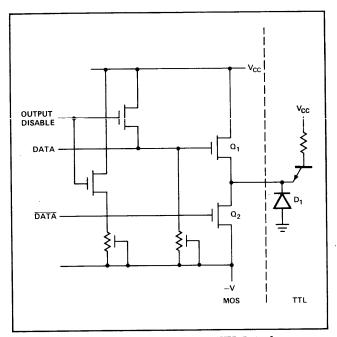

The output of the p-channel MOS circuit can be designed to drive a TTL or low power TTL (LPTTL) gate. The 1101A can drive at least one TTL gate over the full temperature range of 0 to  $70^{\circ}$  C. Figure 1.5 shows the nature of the p-channel MOS to TTL interface. Parts which are disabled (not enabled by chip select) have neither  $Q_1$  nor  $Q_2$  conducting. For a logic "1",  $Q_1$  conducts, providing a 1 level very nearly at  $V_{CC}$ . However, for a logic "0",  $Q_2$  conducts. For the 1101A,  $Q_2$  sinks at least 2.0 mA when the output is at .45V above ground, thus exceeding the minimum TTL sinking requirement of 1.6 mA. Typically, the excess sinking current capability of the 1101A causes the TTL input clamp diode  $D_1$  to be forward biased (at around -.7V with respect to ground) so that some TTL substrate current flows. The maximum current from the 1101A is  $13 \, \text{mA}$  at  $-1 \, \text{V}$ .

Figure 1.5. P-channel MOS to TTL Interface

#### A.2 TTL to N-channel MOS (2102)

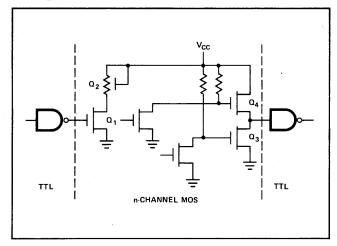

The 2102 is an n-channel 1024 word by 1 bit memory. It is ideally suited for applications where high performance, low cost, large bit storage, and simple interfacing are important design objectives. The 2102 requires only a single +5V power supply. The 2102 has operating conditions which are almost identical to TTL, so that interfacing the 2102 to TTL is far easier than for p-channel MOS devices. Figure 1.6 shows the nature of the input and output interfaces.

Within the n-channel circuit, the signal voltage levels are very much like TTL levels. When the TTL output is high,  $Q_1$  conducts, producing a low internal level. When the TTL output is low,  $Q_1$  is off, and  $Q_2$  produces a high internal level. Input requirements are for high input levels of 2.2V or greater and low input levels of .65V or less. As a result, noise margins are somewhat less than those of TTL circuitry.

Figure 1.6. N-channel TTL Interface

However, the slower n-channel circuits do not respond as rapidly to noise as bipolar TTL circuits. This slower response somewhat compensates for the reduced noise margins.

The output circuit is capable of driving one 1.6mA TTL load with .3mA in reserve. However, when OR-tying several devices in an array, this .3mA is needed to compensate for output leakage currents. These output leakages ( $100\mu A$  maximum) are equivalent to conduction currents in output transistor  $Q_4$  of disabled devices. As a result, no more than 4 devices (2102s) should be OR-tied when driving a standard TTL load. For larger arrays, OR-tie capability can be increased by an LPTTL buffer stage, or by organizing the memory in 4k word modules each with its own output buffer. These output buffers might be open-collector TTL gates enabling data onto a bus or might be realized using multiplexers. The TTL circuits may be operated from the power supply provided for the 2102s.

#### A.3 Bipolar Buffer Considerations

Once a bipolar memory has been laid out using the techniques shown in Figures 1.2 and 1.3, the signals at the periphery must be properly dealt with.

The 3101, 3101A, 3106, 3106A, and 3107 memories are all designed using a Schottky technology, and except for the 3101, have input loads less than 1/6 that of standard TTL.

In spite of these small loading factors, buffering is usually necessary because the large number of inputs which must be driven represent a significant capacitive load. Because of TTL loading restrictions, several levels of buffering may be necessary.

The bipolar components listed have either open collector outputs (3101, 3101A, 3107, 3107A) or three-state output (3106, 3106A).

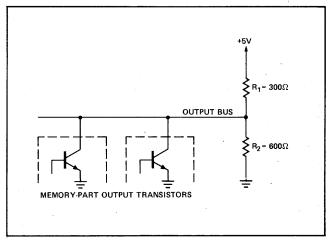

Those components with open collector output require a pull-up resistor or a resistor terminator. When the output is going from "1" to "0", discharge current for load capacitance is provided by the output transistor in the memory

device. When the output goes from "0" to "1", the capacitor charging current is provided by a pull-up resistor. A resistive terminator circuit may be used to reduce the time constant of the output circuit, yet still not exceed the current sinking capacity of the output devices. Such a circuit is shown in Figure 1.7. This terminator reduces the time for the one to zero transition, while slightly degrading the zero to one transition. For such memories as the 3101, a net reduction in worst case access time results.

Figure 1.7. Resistor Terminator for Bipolar Outputs

#### B. ACCESS TIME CONSIDERATIONS

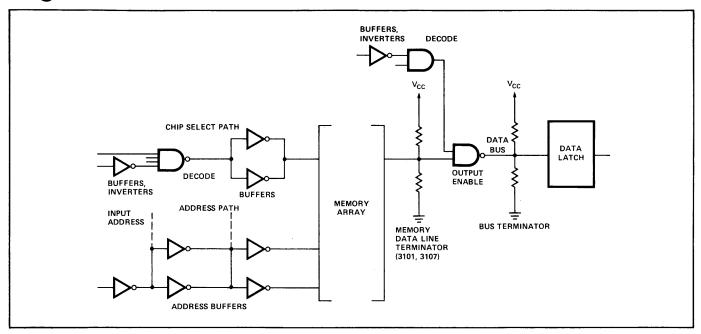

To estimate the access time of a system using these semiconductor memory elements, the worst case path for the addressing mode used must be found. Figure 1.8 shows symbolically some of the paths in a typical memory system.

To estimate the access time, the longest path through the system is found (taking into consideration the differences in delay for chip select and address inputs, and including any delays due to wire, excessive capacitive loading, etc.). Note that, as a general rule, every increase in memory size by a factor of 8 to 10 requires at least one more level of buffering on all inputs and requires one or more levels of multiplexing on outputs. Therefore, access time in TTL-buffered systems tends to increase by 20 to 30 nsec. for each order of magnitude increase in memory size, until the physical size of the memory also contributes significant delay.

All of the parts described allow an OR-tie connection of output leads. However, each additional device connected to the output adds capacitive loading to the output line. When very large memory arrays are used, this capacitive loading may seriously increase access time due to the time required for the output line to be charged or discharged. In general, the access time is incurred by an amount approximately equal to the time constant of the data line.

Three state outputs are provided on the 3106 and 3106A as opposed to open collector outputs on the 3107 and 3107A. Some designers prefer the three-state output because of its increased capacitance driving capability and ability to handle more TTL loads on the bus. (Total TTL load driving capability is reduced by the pull-up re-

Figure 1.8. Possible Delay Paths in 1101A, 3101 and 3106/7 Systems

sistor loading.) Other designers object to the increased system noise and power supply spiking which may take place if the switching of the various three-state devices on a bus line are not carefully synchronized.

#### C. CHIP SELECT DECODING

Each of the buffered arrays described above presents a number of address leads, together with one or more chip selects per row. The address leads perform selection of a single word from each row while chip select leads act to select which row will deliver data to (or accept data from) the outside of the array.

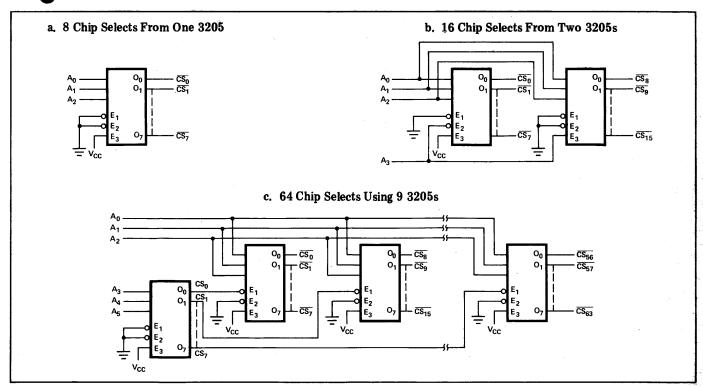

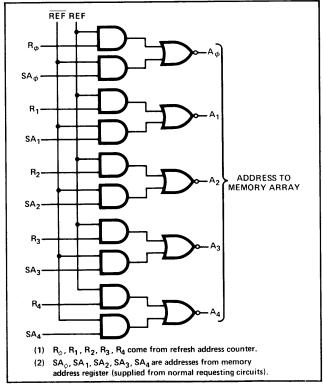

To select a single word location in an array of  $2^p$  words requires p binary address bits. If each memory device contains  $2^n$  words,  $2^{p-n}$  rows must be used in the memory device array. To select a word, n of the address leads are sent to the array as common addresses and p-n are decoded to provide row selection. The chip select signals are used in conjunction with row select decoding.

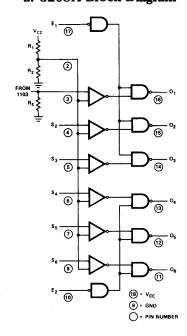

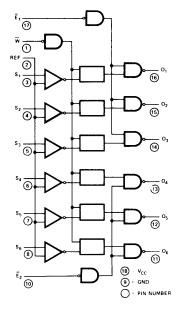

For the 1101A and 3101A memory devices, which have a single chip select input, the additional address bits are decoded such that the chip select for the selected row is low, and all others remain high. For memory parts with multiple chip selects such as the 3106/7, the multiple chip select inputs may be used to decode some of the additional address bits. Examples of chip select decoding are shown in Figure 1.9. For small arrays, there may be sufficient chip select inputs to decode all of the additional address bits.

Figure 1.9 shows how the 3205 one of eight decoder can be used to decode 3 to 6 additional address input leads and generate 8 to 64 chip select signals. These chip select signals are compatible with 3101, 3101A, 3106, 3106A,

3107, 3107A, and with the 1101A (if pull-up resistors are added to the outputs of the 3205).

#### D. POWER CONSIDERATIONS

The random access memory products discussed above all dissipate power at significantly greater levels per package than most LSI and MSI components. In addition, the array wiring shown provides much denser packing than is commonly achieved with random logic. As a result, the power dissipation per unit area of circuit board can approach an order of magnitude greater than ordinary TTL logic. The system designer must insure an adequate flow of cooling air in any design which uses more than a few packages.

Power distribution is also important. Although most static MOS and bipolar devices draw relatively constant current from the power supplier, MOS output circuits, particularly those of p-channel MOS, can contribute significant transients to power supplies. Bipolar devices with relatively low pull-up resistors and those with three state outputs can also introduce significant transients. To insure proper operation of both memory and the surrounding logic circuitry, power supplies should be adequately bypassed. Ceramic capacitors in the .001 to .05 $\mu$ fd range are recommended, with one capacitor being used for every one to 10 parts. Bypassing requirements are usually less stringent for multi-layer boards using power and ground planes.

Two of the static memory components described here, the 2102 and the 1101A, offer reduced standby power modes of operation. These parts have been designed such that the memory cells can operate on reduced voltages without loss of data. In addition, the 1101A provides separate power leads for the memory cells and the peripheral decoders.

To enter standby mode, the chips should all be deselected, and in the read mode, before the voltages are lowered. For

Figure 1.9. Chip Select Decoding Using The 3205

the 2102, all addresses should be held low to achieve the greatest power savings. Power supplies should switch to the voltages (standby or operating voltage) without "glitches" or overshoot. At least one microsecond cycle time should be allowed between the last access or write cycle before power is lowered, and one microsecond cycle time should be allowed after normal voltages are restored before operating the memory. Table 1.2 shows the possible power saving.

Table 1,2, 'Low Power Standby - Static MOS Memories

| Device | Normal Power | Standby Power |

|--------|--------------|---------------|

| 1101A  | 720 mW       | 370 mW        |

| 2102   | 370 mW       | 90 mW         |

#### E. PAGING TECHNIQUES FOR ACCESS TIME REDUCTION

Semiconductor memory systems may exhibit different access times for different address changes. For example, when only the multiplexer control bits are changed for multiplexer connected modules, the access time for new data fetched from within an array is equal to the multiplexer switching time. Similarly, the chip select access for 1101As is much faster than the address-change access. In the 3106/7, access for addresses  $A_0$  to  $A_3$  is typically much faster than that of addresses  $A_4$  through  $A_7$ .

It is often possible to organize a memory system such that some address bit changes result in shorter access times than others. Simple circuits may be added which compare the new address with the old to signal whether fast or slow access will be obtained.

#### **DYNAMIC MOS MEMORY--THE 1103**

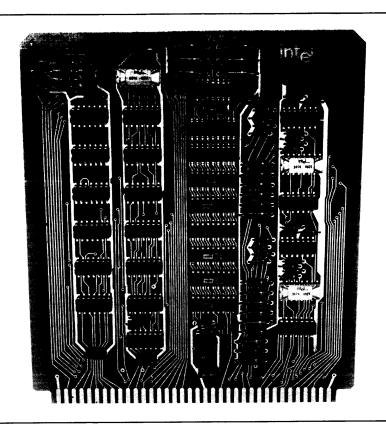

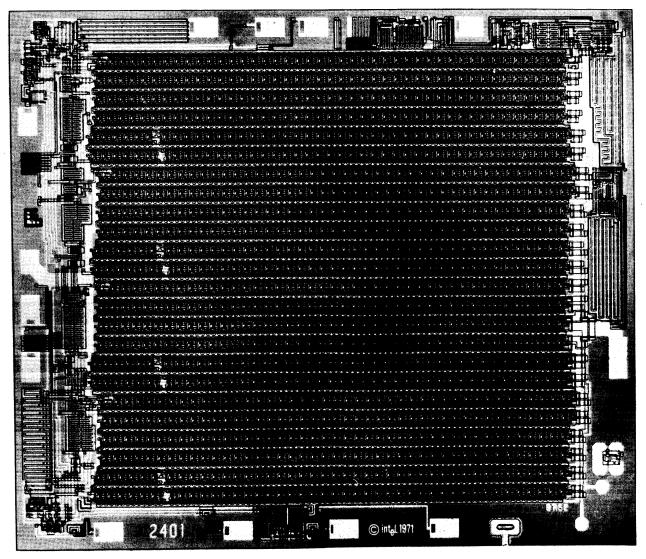

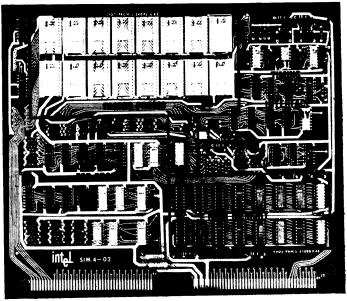

The Intel 1103, a 1024-bit, dyanmic, silicon-gate, MOS random access memory chip, has become one of the most important semiconductor components ever produced. The memory system designer should consider this component for new random access memory system designs, as it offers significant advantages over cores in cost, system flexibility, and performance. Fourteen out of eighteen computer mainframe manufacturers throughout the world are now using the 1103 memory. With more than a dozen semiconductor manufacturers having announced their intentions to second source the 1103, this product is assured a position as an industry standard.

Because the 1103 is such an important component, and because dynamic MOS circuits require a number of unique considerations, this special section has been devoted exclusively to the 1103. This section is divided into articles on the principles of operation of the 1103, basic system design using the 1103, special considerations such as minimizing power consumption in 1103 memories, and examples of 1103 system design.

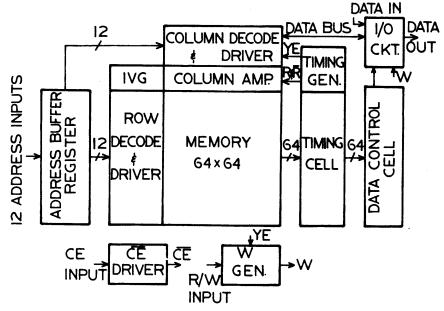

#### A. OPERATION OF THE 1103

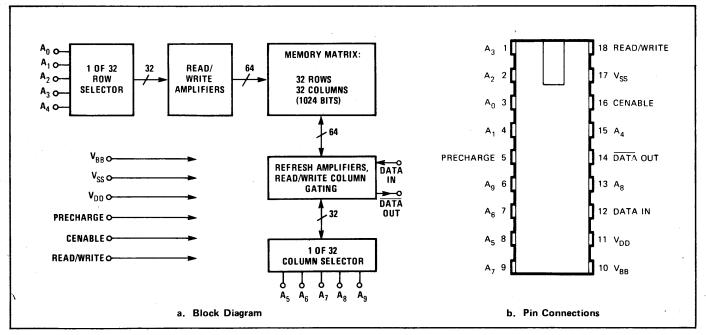

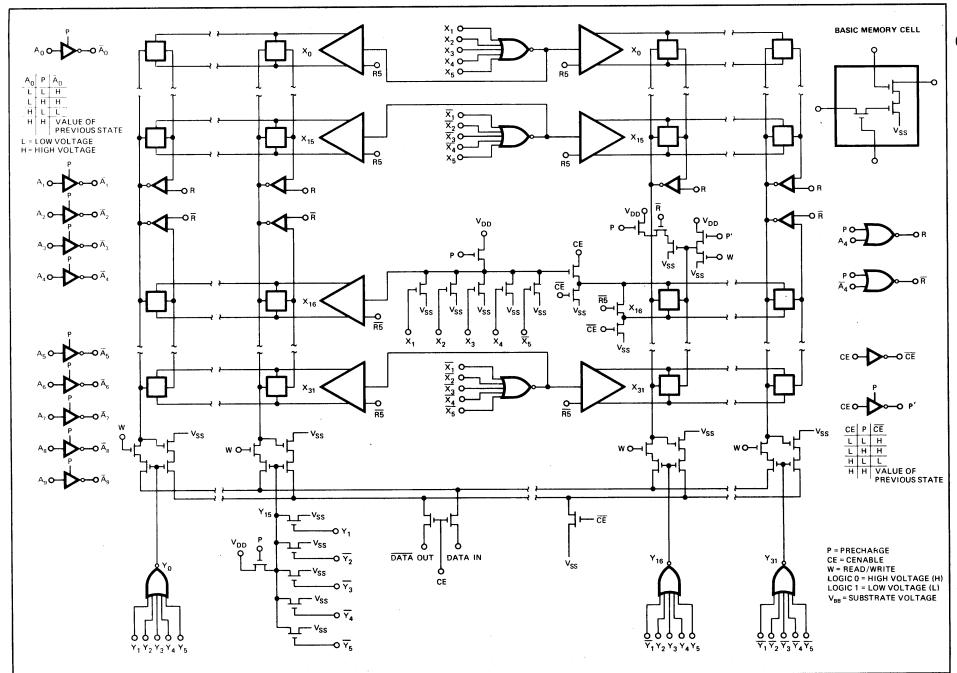

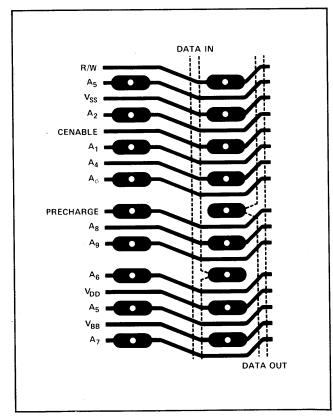

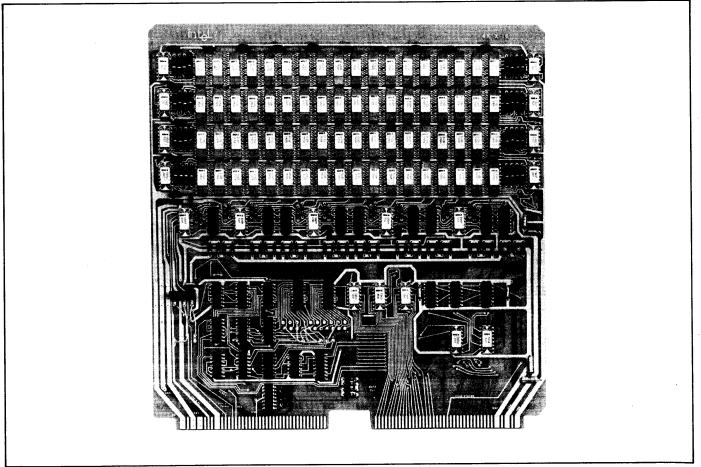

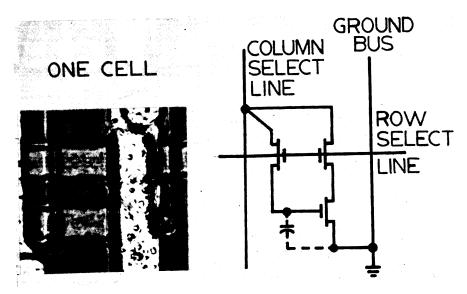

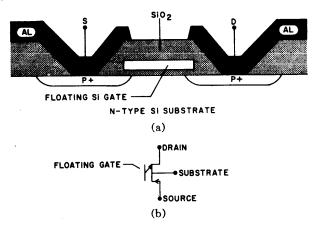

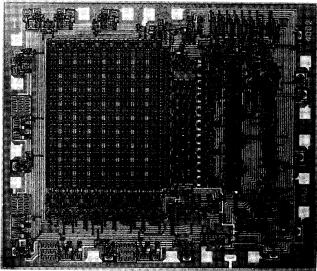

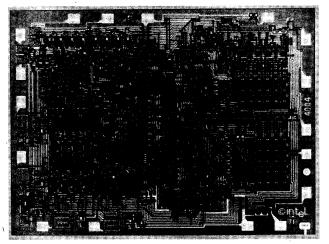

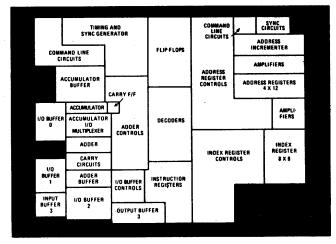

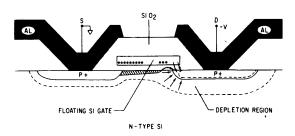

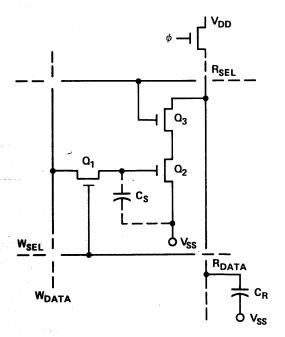

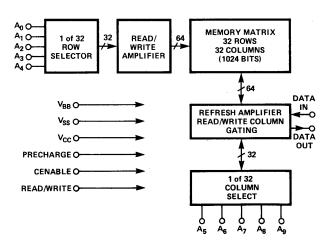

The Intel 1103 is a 1024-bit random-access, fully decoded, read-write memory utilizing the cell shown in Figure A-7b. shown in the Appendix, for storage. It is mounted in an 18 lead dual in-line package. Figure 1.10a shows a block diagram of the part, while Figure 1.10b shows the pin connections. A more complete diagram is shown in Figure 1.11.

The memory is organized as 32 rows of 32 cells each. Five address lines,  $A_0$  through  $A_4$ , are decoded to select one row of cells. When accessed, the contents of this row are transferred to a row of 32 refresh amplifiers. In the course of a memory cycle, whether read or write, the data is regenerated and written back into the selected row of cells. Address bits  $A_5$  through  $A_9$  are decoded to select one refresh amplifier for communication with the data input and output terminals. Data output is sensed as a current. Activation of the "write" clock effectively disconnects the refresh amplifier outputs from the write data lines and permits the signal on the data input line to over ride the signal at the output of the selected refresh amplifier.

Figure 1.10. Block Diagram and External Connections of 1103

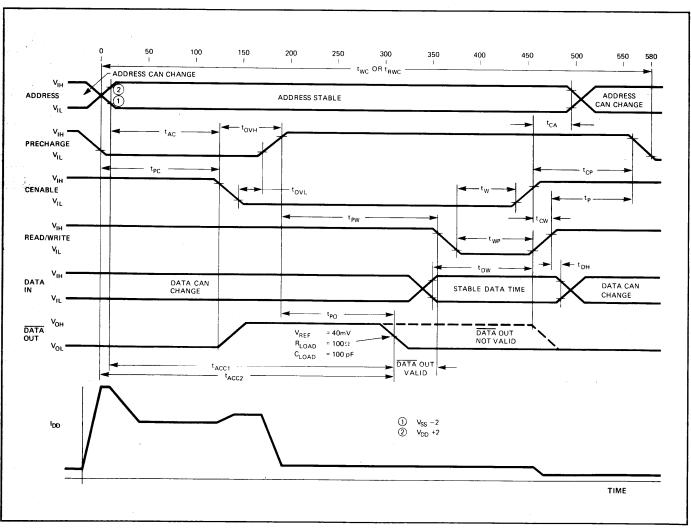

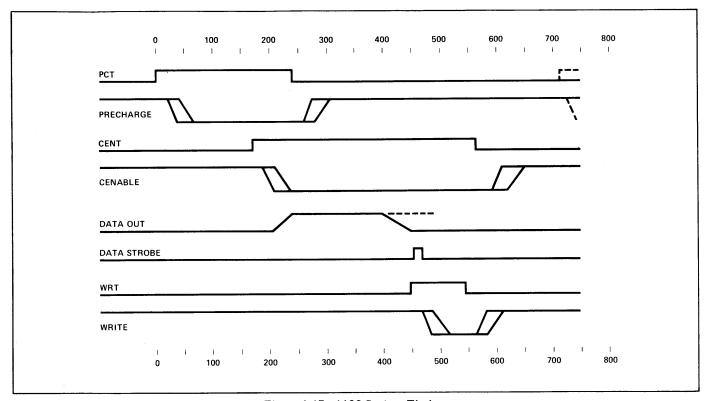

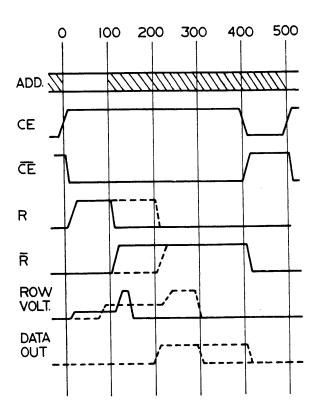

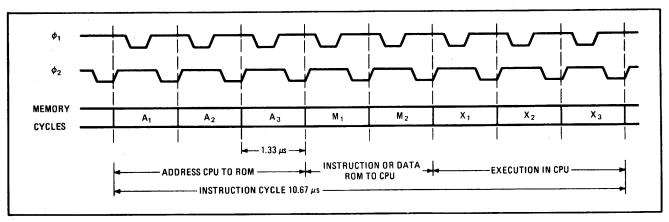

Figure 1.12 shows the basic timing of the 1103 memory cycle. The timing values specified for each of the input signals (shown in Table 1.3) are those guaranteed to permit operation over the specified operating temperature range.\*

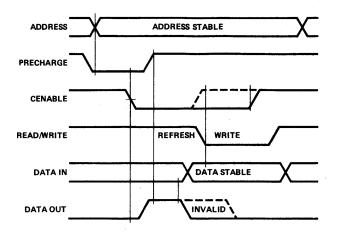

The cycle timing is established by the three clock signals: precharge, cenable, and write. Initially (prior to execution of a memory cycle) all clocks are at their high state, at a voltage approximately equal to  $V_{SS}$ .

To begin a cycle, precharge is first brought low, to approximately  $V_{DD}$  potential. Referring to Figures 1.11 and 1.12, this operation activates the row and column decoders, and also charges all read and write data lines negatively (i.e., to the equivalent of a logic "high" state for the p-channel MOS). In the discussion which follows, clocks, etc. are considered "on" at  $V_{DD}$  level, and "off" at  $V_{SS}$  level. "High and low" refer to the magnitude of charge with respect to the MOS substrate.

\*While individual units may be operable typically at much high speeds than the guaranteed values, particularly at room temperature, the designer of a production system should observe all of the limits specified in the data sheet.

The decoder circuitry is somewhat faster than the line charging circuitry, so addresses need not be stable until somewhat after precharge is applied. The system designer may take advantage of this characteristic in several ways; for example, to utilize a less expensive (slower) address driver. Of course, addresses may be provided before precharge is turned on.

After precharge and addresses have been present long enough for the data lines to charge and decoders to stabilize, the cenable clock may be turned on - i.e., dropped to its low state. At this time, the desired read-select line is activated and the read-data line charging circuits are disabled.

These data lines begin to discharge selectively, with the signals on them approaching values corresponding to the complements of the data stored in the selected row of cells.

As the read-data lines selectively discharge, the precharge signal is turned off, i.e., raised high to  $V_{SS}$ . This action removes the charging signal on the write-data lines, and closes a path so that the write-data lines may be selectively discharged. The write-select line corresponding to the selected read-select line is also activated, so that restoration of the cell contents occurs. The signal level on the write-data line is a function of the overlap time between precharge

Figure 1.12. 1103 Timing - Minimum Read/Write Cycle and Supply Current Variation

and cenable. If this overlap is too short, the read-data lines will not have discharged sufficiently when the discharge path from the refresh amplifiers to the write-data lines is closed. As a result, high (negative) levels written into the cells may be reduced.

If, however, the overlap time is excessive, weak lows within the cells may result in some discharge of the read lines before closure of the write path back, so that cells with weak lows have higher levels (ever weaker lows) written back into them, eventually resulting in lows changing to highs. This problem is somewhat aggravated by the small but unavoidable capacitive coupling between the data and select lines and the cell storage capacitor.

When cenable is turned on, a path for current to flow from  $V_{SS}$  to output exists, for one column decoder is enabled and all write-data lines have been charged high (negatively). If the selected cell (the cell at the intersection of the selected column and selected row) contains a low, the write-data line will be discharged after precharge is removed and the

output current will be cut off. If, however, the selected cell has been negatively charged, the output current will continue to flow.

Cenable must remain present (after precharge turn off) for sufficient time to allow the contents of the selected row of cells to be refreshed. Even after cenable is turned off (raised to  $\mathbf{V}_{SS}$ ) the addresses should remain for a few ( $\mathbf{t}_{ca}$  = 20) nsec to allow completion of internal operations. Precharge should not be applied again until cenable has remained off for at least  $\mathbf{t}_{cp}$  = 85 nsec.

If the memory cycle must include a write operation (with or without a read operation) all sequences proceed as above. However, before cenable is removed, but after a sufficient time has been allotted for stabilization of the write data lines, the write line may be activated. As a result, the read data lines are discharged, effectively disconnecting the refresh amplifiers from the write data line. Thus, a direct path from the data input to the selected cell is established.

Table 1.3. Timing Specifications for 1103

AC CHARACTERISTICS  $T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ ,  $V_{SS} = 16 \pm 5\%$ ,  $(V_{BB} - V_{SS}) = 3.0 \text{V}$  to 4.0 V,  $V_{DD} = 0 \text{V}$

| DEAD | WRITE. | AND | DEAD | /WDITE | CVCI | E  |

|------|--------|-----|------|--------|------|----|

| READ | WHILE. | ANU | READ | /WKIIE | LIL  | ┏. |

| SYMBOL              | TEST                              | MIN.       | TYP. | MAX. | UNIT | CONDITIONS |

|---------------------|-----------------------------------|------------|------|------|------|------------|

| t <sub>REF</sub>    | TIME BETWEEN REFRESH              |            |      | 2    | ms   |            |

| t <sub>AC</sub> (1) | ADDRESS TO CENABLE SET UP TIME    | 115        |      |      | ns   |            |

| tc∧                 | CENABLE TO ADDRESS HOLD TIME      | 20         |      |      | ns   |            |

| t <sub>PC</sub> (1) | PRECHARGE TO CENABLE DELAY        | 125        |      |      | ns   |            |

| tovL                | PRECHARGE & CENABLE OVERLAP, LOW  | 25         |      | 75   | ns   |            |

| t <sub>CP</sub>     | CENABLE TO PRECHARGE DELAY        | <b>8</b> 5 |      |      | . ns |            |

| t <sub>ovh</sub>    | PRECHARGE & CENABLE OVERLAP, HIGH |            |      | 140  | ns   |            |

#### READ CYCLE

| SYMBOL                | TEST                             | MIN. | TYP. | MAX. | UNIT | COND                                | ITIONS                                                                                                  |

|-----------------------|----------------------------------|------|------|------|------|-------------------------------------|---------------------------------------------------------------------------------------------------------|

| t <sub>RC</sub> (1)   | READ CYCLE                       | 480  |      |      | ns   |                                     |                                                                                                         |

| t <sub>POV</sub>      | PRECHARGE TO END OF CENABLE      | 165  |      | 500  | ns   |                                     |                                                                                                         |

| t <sub>PO</sub>       | END OF PRECHARGE TO OUTPUT DELAY |      |      | 120  | ns   |                                     | t₁ = 20 ns                                                                                              |

| t <sub>ACCI</sub> (1) | ADDRESS TO OUTPUT ACCESS         | 300  |      |      | ns   | tACmin + toVLmin + tPOmax + 2 tT    | $C_{\text{LOAD}} = 100 \text{ pF}$<br>$R_{\text{LOAD}} = 100\Omega$<br>$V_{\text{REF}} = 40 \text{ mV}$ |

| t <sub>ACC2</sub> (1) | PRECHARGE TO OUTPUT ACCESS       | 310  |      |      | ns   | tecmin + tovemin<br>+ teomax + 2 tr |                                                                                                         |

#### WRITE OR READ/WRITE CYCLE

| SYMBOL               | TEST                             | MIN. | TYP. | MAX. | UNIT | CONDITIONS                                         |

|----------------------|----------------------------------|------|------|------|------|----------------------------------------------------|

| t <sub>wc</sub> (1)  | WRITE CYCLE                      | 580  |      |      | ns   | $rac{1}{2}$ $t_r = 20 \text{ ns}$                  |

| t <sub>RWC</sub> (1) | READ/WRITE CYCLE                 | 580  |      |      | ńs   | J                                                  |

| tew                  | PRECHARGE TO READ/WRITE DELAY    | 165  |      | 500  | ns   |                                                    |

| twe                  | READ/WRITE PULSE WIDTH           | 50   |      |      | ns   |                                                    |

| tw                   | READ/WRITE SET UP TIME           | 80   |      |      | ns   |                                                    |

| tow                  | DATA SET UP TIME                 | 105  |      |      | ns   |                                                    |

| t₀н                  | DATA HOLD TIME                   | 10   |      |      | ns   |                                                    |

| t <sub>PO</sub>      | END OF PRECHARGE TO OUTPUT DELAY |      |      | 120  | ns   | $C_{LOAD} = 100 \text{ pF}$ $R_{LOAD} = 100\Omega$ |

| t <sub>P</sub>       | TIME TO NEXT PRECHARGE           | 0    |      |      | ns   | $V_{REF} = 40 \text{ mV}$                          |

| tcw                  |                                  |      |      | 0    | ns   |                                                    |

Note 1: ,These times will degrade by 40 ns (worst case) if the maximum values for V<sub>IL</sub> (for precharge, cenable and read/write inputs) go to V<sub>SS</sub>-14.2V @ 0°C and V<sub>SS</sub>-14.5V @ 70°C as defined on page 2.

A signal on this input will then overwrite the contents of the cell. If the read/write line remains "on" ( $V_{DD}$  potential) after cenable goes off ( $t_{\rm cw}>0$  nsec), those conditions caused by excessive overlap time are aggravated and improper operation of the device may result.

The timing specifications for operating the 1103 are shown in Table 1.3. All the time values listed, except  $tp_0$ ,  $t_{ACC1}$ , and  $t_{ACC2}$  are generated by the system in which the 1103 is installed. These times should be kept within their stated limits if proper operation over the full temperature range is to be achieved. In addition to these stated limits, the precharge duty cycle should be held below 40% to keep power dissipation at an acceptable value.

The time designated  $tp_0$  which refers to the time delay observed between the turn-off of precharge and the availability of data at the 1103 output terminals, is a characteristic of the part. When operated within the proper voltage and timing limits, this delay is guaranteed not to exceed the stated value of 120 nsec.

The two access times,  $t_{ACC1}$  and  $t_{ACC2}$  represent a combination of system operating parameters and characteristics of the 1103. Thus, the stated "minimum" values of 300 and 310 nsec represent the shortest access times which can be guaranteed when parts are operated within the limits specified and with rise and fall times of 20 nsec. As will be discussed later, system access times will exceed these values because of the additional delays and tolerance introduced by the rest of the system.

#### B. CHIP SELECT

In operation, the cenable clock also acts as a chip select. That is, precharge and write signals may be applied at their normal times in the cycle, but if cenable is not applied, the part will neither deliver current to the output terminal nor will the contents of any cell be altered. However, no refreshing of memory content takes place during such a cycle.

#### C. CLOCK SIGNAL AMPLITUDES

To guarantee operation of the 1103 over the full temperature range, the clock amplitudes (precharge, cenable and write) must be maintained at the levels defined below in Table 1.4.

The reduced performance specification given in Table 1.4b allows simpler clock-driver designs or permits wider power supply variations for a given clock driver design, but requires adding  $40\,\mathrm{ns}$  to  $t_{PC}$  and  $t_{AC}$ . As a result, access and cycle times are increased by at least  $40\,\mathrm{ns}$ , when this less stringent specification is used.

Table 1.4

A. Clock Signal Amplitudes — Full Performance

| Signal                                    | Minimum        | Maximum         |

|-------------------------------------------|----------------|-----------------|

| $ m V_{IH}$ (high) @ $ m 0^{o}C$          | $V_{SS} - 1.0$ | $V_{SS} + 1.0$  |

| V <sub>IH</sub> (high) @ 70°C             | $V_{SS} - 0.7$ | $V_{SS} + 1.0$  |

| V <sub>II.</sub> (low) @ 0 <sup>o</sup> C | $V_{SS} - 17$  | $V_{SS} - 14.7$ |

| $V_{IL}$ (low) @ $70^{o}$ C               | $v_{SS} - 17$  | $V_{SS}-15.0$   |

#### B. Clock Signal Amplitudes - Reduced Performance

| Signal                         | Minimum         | Maximum        |

|--------------------------------|-----------------|----------------|

| V <sub>IH</sub> (high) @ 0°C   | $V_{SS}$ $-1.0$ | $V_{SS} + 1.0$ |

| $V_{IH}$ (high) @ 70°C         | $V_{SS} = 0.7$  | $V_{SS} + 1.0$ |

| $V_{IL}$ (low) @ $0^{\circ}$ C | $V_{SS}-17$     | $V_{SS}-14.2$  |

| $V_{IL}$ (low) @ $70^{o}$ C    | $V_{SS}-17$     | $V_{SS}-14.5$  |

NOTE: The maximum value for  $V_{IL}$  and the minimum value of  $V_{IH}$  are linear functions of temperature over the range 0 to  $70^{\circ}C$  and can be calculated using a straight line relationship.

#### D. ARRAY CONNECTION OF 1103s

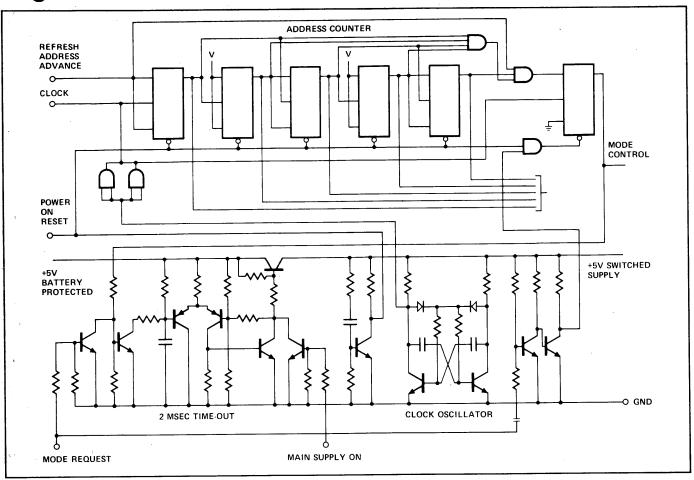

To design a memory system with 1103s, a number of factors must be considered. The system must be capable of generating the timing for the various clocks, etc. and distributing these signals at the proper voltage levels to the 1103s. Suitable power must be distributed to the 1103s and peripheral circuitry, and means must be provided to prevent catastrophic damage to the memory array in the event of peripheral circuit failure. Refresh control circuits may also have to be provided to guarantee that all memory cells retain data.

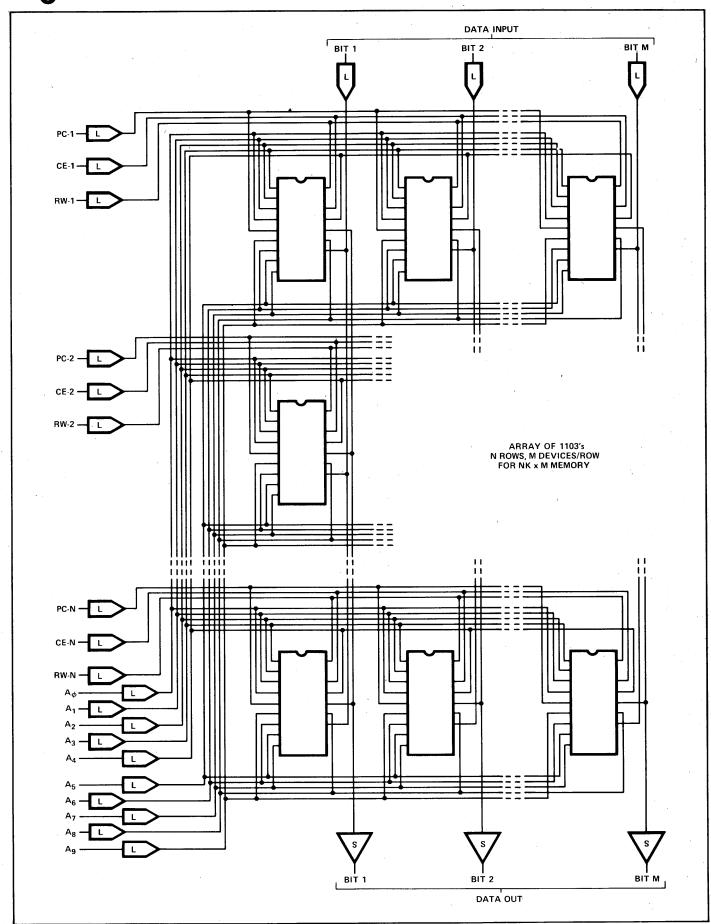

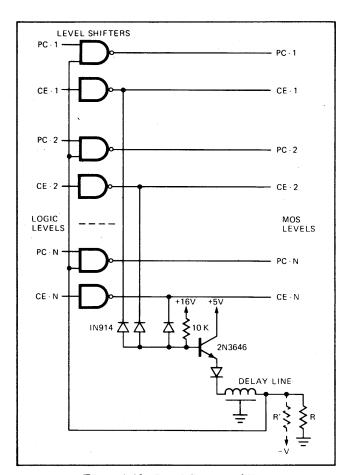

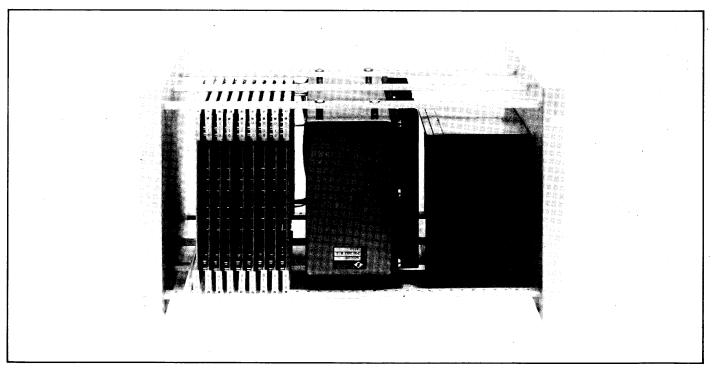

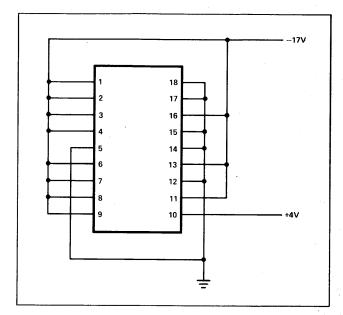

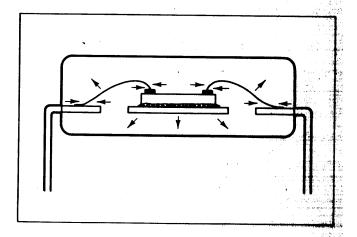

The nature of the 1103 permits a number of units to be wired in a rectangular array much like that used for bipolar and static MOS circuits. In this way, several thousand words of some selected number of bits can be realized with a single set of peripheral interface circuits. Figure 1.13 shows how 1103s may be so wired. When making access to an array such as that of Figure 1.13, the cenable clock is used to select a row of 1103s, while the 10 address lines select the word from within the selected row. In most cases, the system designer will probably find it most convenient to generate timing signals for the 1103 memory system using one of the standard high speed integrated circuit logic families such as TTL or ECL. To operate the 1103, the generated signals must be converted from the logic family levels to MOS levels. Similarly, the outputs from the 1103 must be converted back to suitable logic levels. In Figure 1.13, the small blocks labelled L represent level shifters from the ECL or TTL levels to MOS levels (e.g. the Intel 3207A), while the blocks labelled S are sense amplifiers (e.g., the Intel 3208A or 3408A) which convert the output current from the 1103s back to TTL or ECL levels.

The power supply connections are not shown in Figure 1.13. In practice,  $V_{BB}$ ,  $V_{SS}$ , and  $V_{DD}$  connections are each made common throughout the array. It is especially important to

Figure 1.13. 1103 Array

provide adequate distribution for these supplies as will be described in the section on printed circuit layout.

#### D.1 Level Shift Circuits for TTL Interface

The function of the level shift circuits is to convert from the TTL or ECL levels used by the system to MOS levels. To avoid degrading the performance of the system, fast rise and fall times must be maintained into the load represented by the array of 1103s. The level shifter must also be capable of holding the shifted level within rated tolerances for the signal line being driven. The levels for clock and address lines are referenced with respect to VSS. However, in actual practice, most level shifters use ground or the VDD supply as a reference value for the low level. As a result, the offset from ground which is characteristic of the level shifter, when combined with normal power supply variation, may result in an insufficiently negative level for some of the input signals. To give the system designer some freedom in his choice of drivers, the 1103 is characterized for two different levels of clock drive signals as outlined in Table 1.4. In many cases, a driver with a higher offset voltage may have lower cost or better load drive capability than those with low offset voltages. The designer may choose to sacrifice some speed to permit use of a net lower cost set of level shifters. Tables 1.4, 1.5, and 1.6 list some of the characteristics of the 1103 which are relevant to level shifter design.

The signal lines from an 1103 memory array represent significant capacitive loads. For example, consider a 4096 word, 16 bit per word memory array. If a connection equivalent to that of Figure 1.13 is used, the array will consist of 4 rows of 16 devices each. The worst case capacitances due to the memory parts are then as follows:

Each of 10 address lines  $64 \times 7 \, pF = 488 \, pF$ Each of 4 precharge lines  $16 \times 18 \, pF = 288 \, pF$ Each of 4 cenable lines  $16 \times 18 \, pF = 288 \, pF$ Each of 4 write lines  $16 \times 15 \, pF = 240 \, pF$ Each of 16 data input lines  $4 \times 5 \, pF = 20 \, pF$

In addition to these loads, the wiring capacitance of the printed board, etc., used to connect the array must also be considered. To estimate the average charging and discharging current I required to change the voltage by a value of  $\Delta E$  on a capacitor of value C in a time  $\Delta t$ , the relationship  $I = C\Delta E/\Delta t$  may be used.

If C is in picofarads (pF), E in volts and t in ns, the units of

| SYMBOL                 | TEST                                                         | MIN.                 | TYP. MAX.             | UNIT       | CONDITIONS            |

|------------------------|--------------------------------------------------------------|----------------------|-----------------------|------------|-----------------------|

| ILI                    | INPUT LOAD CURRENT (ALL INPUT PINS)                          |                      | 1                     | μ <b>Α</b> | V <sub>IN</sub> = 0V  |

| lLO                    | OUTPUT LEAKAGE CURRENT                                       |                      | 1                     | μА         | V <sub>OUT</sub> = 0V |

| V <sub>IL1</sub> (1)   | INPUT LOW VOLTAGE (ALL ADDRESS & DATA-IN LINES)              | V <sub>SS</sub> -17  | V <sub>SS</sub> -14.2 | ٧          | T <sub>A</sub> = 0°C  |

| V <sub>IL2</sub> (1)   | INPUT LOW VOLTAGE (ALL ADDRESS & DATA-IN LINES)              | V <sub>SS</sub> -17  | V <sub>SS</sub> -14.5 | ٧          | T <sub>A</sub> = 70°C |

| V <sub>IL3</sub> (1,2) | INPUT LOW VOLTAGE (PRECHARGE<br>CENABLE & READ/WRITE INPUTS) | V <sub>SS</sub> -17  | V <sub>SS</sub> -14.7 | ٧          | $T_A = 0^{\circ}C$    |

| V <sub>IL4</sub> (1,2) | INPUT LOW VOLTAGE (PRECHARGE<br>CENABLE& READ/WRITE INPUTS)  | V <sub>SS</sub> -17  | V <sub>SS</sub> -15.0 | ٧          | T <sub>A</sub> = 70°C |

| V <sub>IH1</sub> (1)   | INPUT HIGH VOLTAGE (ALL INPUTS)                              | V <sub>SS</sub> -1   | V <sub>SS</sub> +1    | ٧          | T <sub>A</sub> = 0°C  |

| V <sub>IH2</sub> (1)   | INPUT HIGH VOLTAGE (ALL INPUTS)                              | V <sub>SS</sub> -0.7 | V <sub>SS</sub> +1    | ٧          | T <sub>A</sub> = 70°C |

Table 1.5. Input Level Requirements - 1103 Address and Data Lines

Note 2: The maximum values for V<sub>IL</sub> (for precharge, cenable & read/write) may be increased to V<sub>SS</sub>-14.2 @ 0°C and V<sub>SS</sub>-14.5 @ 70°C (same values as those specified for the address & data-in lines) with a 40 ns degradation (worst case) in t<sub>AC</sub>, t<sub>PC</sub>, t<sub>RC</sub>, t<sub>WC</sub>, t<sub>ACC1</sub> and t<sub>ACC2</sub>.

| Table 1 6  | Canacitance | Value   | f 1103 | Signal Lines <sup>1</sup> | ٠ |

|------------|-------------|---------|--------|---------------------------|---|

| Table 1.0. | Cabacitance | value o | T TIVO | DIRITAL LINES             | • |

| SYMBOL           | TEST                         | TYP. | PLASTIC PKG.<br>MAX. | CERAMIC PKG.<br>MAX. | UNIT | CONDITIONS                                                                            |

|------------------|------------------------------|------|----------------------|----------------------|------|---------------------------------------------------------------------------------------|

| CAD              | ADDRESS CAPACITANCE          | 5    | 7                    | 12                   | pF   | $V_{IN} = V_{SS}$                                                                     |

| CPR              | PRECHARGE CAPACITANCE $_{c}$ | 15   | 18                   | 19.5                 | pF   | $V_{IN} = V_{SS}$                                                                     |

| C <sub>CE</sub>  | CENABLE CAPACITANCE          | 15   | 18                   | 21                   | pF   | $V_{IN} = V_{SS}$ $f = 1 MHz$                                                         |

| C <sub>Rw</sub>  | READ/WRITE CAPACITANCE       | 11   | 15                   | 19.5                 | pF   | $V_{IN} = V_{SS}$ All Unused Pins Are                                                 |

| C <sub>INI</sub> | DATA INPUT CAPACITANCE       | 4    | 5                    | 7.5                  | pF   | $ \begin{array}{c c} CENABLE = 0V & At A.C. \\ V_{IN} = V_{SS} & Ground \end{array} $ |

| C <sub>IN2</sub> | DATA INPUT CAPACITANCE       | 2    | 4                    | 6.5                  | pF   | $ \begin{array}{l} CENABLE = V_{SS} \\ V_{IN} = V_{SS} \end{array} $                  |

| Соит             | DATA OUTPUT CAPACITANCE      | 2    | 3                    | 7                    | pF   | Vour = 0V                                                                             |

<sup>\*</sup>This parameter is periodically sampled and is not 100% tested. They are measured at worst case operating conditions.

Note 1: The maximum values for V<sub>IL</sub> and the minimum values for V<sub>IH</sub> are linearly related to temperature between 0°C and 70°C. Thus any value in between 0°C and 70°C can be calculated by using a straight-line relationship.

current I will be mA. Thus, for 20 ns rise and fall times and 16 volt transitions, each of the precharge and cenable lines will require a drive current which averages about 230 mA over the transition. The peak charging current may be somewhat higher than this value. Thus, the circuits used to drive 1103 arrays must be capable of providing high peak currents.

Although a capacitive load dissipates no power, when a capacitive load is charged, energy is drawn from the driver power supply. Some of this energy is dissipated by the driver while the remainder is stored in the capacitor. When the capacitor is discharged, its stored energy is dissipated in the driver. If a capacitor C is first charged to a voltage V and then discharged back to ground at a rate of f times per second, the minimum average current I drawn from the driver power supply will be given by I = fCV. If f is in megahertz, C in picofarads, and V in volts, I will be in microamps. If the power supply is also of voltage V, the power dissipated by the driver due to the capacitive load is given by  $P = fCV^2$ , where P is in microwatts if the same units listed above are used. Thus, worst case dissipation due to this factor for a precharge or cenable driver in the 4k x 16 memory listed above would be about 120 mW per driver at V = 16 volts, C = 288 pF and f = 1.6 MHz. This dissipation must be added to any other dissipation associated with the driver.

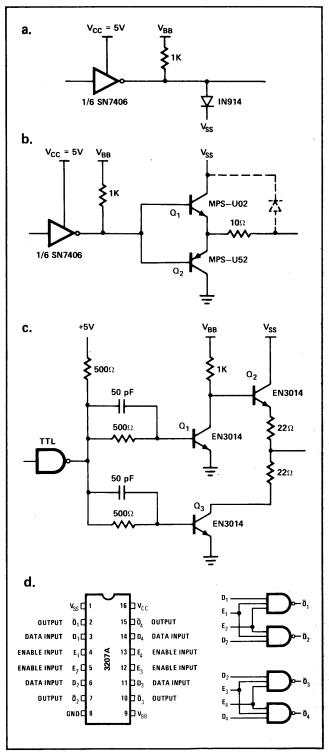

The capacitive loading associated with the array may also produce ringing if the leads from the drivers to the array have any significant inductance. Series damping resistors must usually be used. The choice of the damping resistor will usually be a function of the layout used and the number of 1103s driven. In Figures 1.14 and 1.15 a nominal value of 10 ohms is shown in several of the circuits. In some cases a different value may be found to give better results. Figure 1.14 illustrates a number of level shifters for use with TTL logic.

Table 1.7 lists some of the characteristics of these drivers. The level shifter of Figure 1.14a is used primarily for driving data input lines. In very small arrays, or arrays where degraded performance can be tolerated, it may be used for driving address lines as well. A load resistor of 1k is shown, however, other values may be used. Of course, higher values reduce power dissipation but degrade speed. Lower load resistor values will speed up the level shifter, but increase power dissipation and may, if too low, exceed the current sinking capability of the driving gate.

The capacitive load driving capability of the driver of Figure 1.14a may be increased by adding a booster stage, as shown in Figure 1.14b. The complementary emitter follower considerably increases capacitive drive capability, as can be seen from Table 1.7. However, the emitter base drop of transistor  $Q_2$  in Figure 1.14b raises the low output level to about +1 volt. If  $V_{SS}$  is allowed to fall to 15.2 volts, the output may fall out of the specified operating range at elevated temperatures and degrade the performance.

When using a driver such as that of Figure 1.14b, the designer has several choices:

1. He can restrict the allowable range (or tolerances) of the

Figure 1.14. TTL to 1103 Interface Circuits

$V_{\rm SS}$  supply to values which do not require speed degradation. For example, a  $V_{\rm SS}$  range of 15.7 to 16.8 allows precharge, etc. inputs not to exceed  $V_{\rm SS}$  -14.7 and still maintains  $V_{\rm SS}$  in the proper range.

2. He can raise  ${\rm V}_{SS}$  by approximately 1V and compensate by biasing the  ${\rm V}_{DD}$  return from the 1103 array at about +1V. (A diode in series with the  ${\rm V}_{DD}$  return results in a nominal 0.7V  ${\rm V}_{DD}$  return value, but requires some reduction in allowable  ${\rm V}_{SS}$  tolerances.)

|                                                | Driver (A)              | Driver B                              | Driver C               |

|------------------------------------------------|-------------------------|---------------------------------------|------------------------|

| I Low Voltage (V <sub>OL</sub> )               |                         |                                       |                        |

| No Load                                        | 0.25V                   | ≈0√                                   | 0.04V                  |

| Sinking 3 mA                                   | _                       | +0.97V                                | 0.14V                  |

| II High Voltage (V <sub>OH</sub> )             |                         |                                       |                        |

| No Load                                        | V <sub>SS</sub> + 0.65V | V <sub>SS</sub> ± 0.01V               | $V_{SS} \pm 0.01V$     |

| Source - 3 mA                                  | -                       | V <sub>SS</sub> - 0.05V               | $V_{SS} = 0.12V$       |

| Sink x 0.5 mA                                  |                         | V <sub>SS</sub> + 0.01 <sup>(1)</sup> | $V_{SS} + 0.45V^{(1)}$ |

| III Rise time (t <sub>R</sub> ) <sup>(2)</sup> |                         |                                       |                        |

| 10 pF                                          | 25 ns                   | 25 ns                                 | 10 ns                  |

| 50 pF                                          | 90 ns                   | 25 ns                                 | 15 ns                  |

| 100 pF                                         | _                       | 25 ns                                 | 20 ns                  |

| 200 pF                                         | _                       | 25 ns                                 | 25 ns                  |

| 470 pF                                         | _                       | 40 ns                                 | 50 ns                  |

| IV Fall time (t <sub>F</sub> ) (2)             |                         |                                       |                        |

| 10 pF                                          | 12 ns                   | 6 ns                                  | 6 ns                   |

| 50 pF                                          | 20 ns                   | 8 ns                                  | 9 ns                   |

| 100 pF                                         | _                       | 10 ns                                 | 12 ns                  |

| 200 pF                                         | _                       | 14 ns                                 | 20 ns                  |

| 470 pF                                         | _                       | 24 ns                                 | 35 ns                  |

This voltage level is a function of transistor reverse gain. A diode clamp to  $V_{SS}$  is recommended.

The driver of Figure 1.14b holds the output line very close to  $V_{SS}$  when the output is high. However, if the layout permits positive transients to be capacitively coupled to the driver line, the driver may not be capable of holding the line within tolerance. The reason for this is that the positive transient clamping capability of the driver is a function of the reverse gain of transistor  $Q_2$ . To insure that the high output remains within limits, it may be necessary to add a clamp diode (shown dotted in Figure 1.14b from the output line to  $V_{SS}$ ).

The driver shown in Figure 1.14c has somewhat reduced capacitive load driving capability from that of Figure 1.14b, but does not have the offset problem for low outputs. Again, positive transient clamping for high outputs is limited by the reverse gain of transistor  $\mathbf{Q}_2$  so a diode clamp to  $\mathbf{V}_{SS}$  may be desirable.

Figure 1-14d shows a monolithic integrated quad level shifter and driver, the 3207A, that is available from Intel. Each of the 4 drivers in the 16 pin dual in-line package can drive up to 200 pF, with rise and fall times under 30 and 35 ns. respectively.

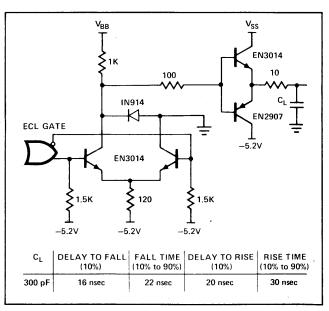

#### D.2 Level Shift Circuits for ECL Interface

In Figure 1.15, a circuit for converting from ECL levels (ECL biased between ground and -5.2V) to MOS levels

$(V_{DD}={\rm GND},\,V_{SS}=+16)$  is shown together with the performance characteristics of the circuit. This circuit does not have significant negative offset, but may require a diode clamp to  $V_{SS}$  to reduce positive going, capacitively—coupled noise on the output line. A negative clamp to ground may also be desirable, as ringing can sometimes result in charging the output line to an excessively negative value. Excessively negative clock values may effectively reduce the timing tolerances for  $t_{OVL}$ .

Figure 1.15. ECL to MOS Level Converter

<sup>2.</sup> These values are measured between the 10% and 90% points.

#### **D.3** Sense Amplifier Circuits

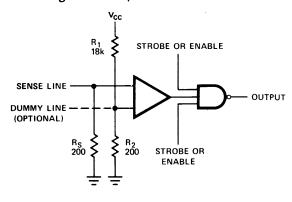

The output of the 1103 is a current which is present for a logic "1" output and absent for a logic "0". This current is usually converted to a logic level by a sensitive differential amplifier which measures the voltage drop across a resistor of a few hundred ohms. Larger resistor values slow performance, while smaller values result in very small signals which are difficult to sense. Table 1.8 lists some of the relevant 1103 output characteristics.

Figure 1.16 shows several different circuits for converting the 1103 output current back to standard logic levels. The first choice for a sense amplifier is the Intel 3208A or 3408A. The 3208A, shown in Figure 1.16a, is a hex sense amplifier specifically designed for use with the 1103. The 3408A, shown in Figure 1.16b, is similar to the 3208A, but includes an internal hex latch so that the 1103 outputs may be stored and delivered to the data bus at a later time.

In Figure 1.16a, a sense resistor  $R_s$  is shown. In practice each sense input which is used would have a sense resistor  $R_s$  to ground. Reference voltage for the 3208A (or 3408A) is generated by the voltage divider consisting of resistors  $R_1$  and  $R_2$ .

The reference voltage of the 3208A and 3408A may be derived from either  $V_{SS}$  or  $V_{CC}$ . The output current of the 1103 is directly proportional to  $V_{SS}$ . To maintain close tracking of 1103 output current and sense amp. reference voltage, it is recommended that the reference voltage for the sense amp. be derived from  $V_{SS}$ . Due to the sensitivity of the sense amplifier input, the reference voltage must be well filtered and decoupled from noise and ripple. Any noise at the reference line may be falsely recognized as an input signal.

The choice of sense resistor for use with the 3208A and 3408A is influenced by two considerations. Larger values of resistor produce larger 1103 output voltages, but increase the time constant of the data output bus, and therefore increase the access time of the memory. Lower values result in high speed, but reduce the noise immunity of the system. If the resistor is too small, the minimum output "1" level of the 1103 may not be large enough to exceed the "1" threshold of the sense amp. An optimum value of sense resistor and reference voltage may be defined as the values which result in the last added circuit delay given a desired amount of noise immunity. The optimum value may be computed

easily if the following assumptions are used (also see note below):

- 1. The added delay due to an increase in data bus time is approximately equal to the increase in time constant.

- 2. The added delay due to a change in current sensing level for the 1103 can be estimated at  $.1\,\rm ns/\mu A$  that is, if the equivalent current level for sensing zeroes from the 1103 is reduced by  $10\mu\rm A$ , the time delay is increased by 1 nsec.

Based on these assumptions, the optimum value of reference voltage is given by the equation:

$$V_{ref} = I_{min} \sqrt{\frac{2 \times V_N + V_T}{10C}}$$

where  $V_{ref}$  is in millivolts and

$I_{min}$  = minimum "1" level output current of the 1103 in  $\mu$ A.  $V_N$  = desired noise immunity in mV.

$V_T$  = maximum threshold variation ( $V_{SH}$ -  $V_{SL}$ ). For 3208A = 50 mV, for 3408A = 60 mV.

C = data bus capacitance in pF.

If  $V_{ref}$  falls outside the range of 100 to 200 mV, then the value (100 mV or 200 mV) which is closest to  $V_{ref}$  should be used as  $V_{ref}$ .

Once  $V_{ref}$  has been chosen, the value for the sense resistor  $R_S$  is given by

$$\mathbf{R}_{S} = \frac{(1000) \times (\mathbf{V}_{ref} + \mathbf{V}_{N})}{\mathbf{I}_{min}}$$

where  $\mathbf{R}_S$  is in ohms,  $\mathbf{V}_{ref}$  and  $\mathbf{V}_N$  are in millivolts, and  $\mathbf{I}_{min}$  is in  $\mu\mathbf{A}.$

Using these assumptions, the increase in access time  $\Delta T_A$  of the memory is given by

$$\Delta T_A = t_{sa} + \left[ I_{ref} - \left( \frac{V_{ref} - V_T - V_N}{R_S \times .001} \right) \right] \times \frac{1}{10} + \left[ \frac{R_S - 100}{1000} \right] \times C$$

where  $t_{sa}$  = sense amplifier delay in nsec,  $I_{ref}$  = defined measuring current for 1103 access time and  $V_{ref}$ ,  $I_{min}$ ,  $R_{s}$ ,  $V_{T}$  and C are as defined above.

As an example, consider a data bus capacitance of 100 pF and desired noise immunity of 25 mV. Then for an 1103

Table 1.8. Output Characteristics of the 1103

| I <sub>OH1</sub> | OUTPUT HIGH CURRENT | 600 | 900      | 4000 | μΑ | TA = 25°C                | ]                       |

|------------------|---------------------|-----|----------|------|----|--------------------------|-------------------------|

| 10н2             | OUTPUT HIGH CURRENT | 500 | 800      | 4000 | μΑ | T <sub>A</sub> = 70°C    |                         |

| loL              | OUTPUT LOW CURRENT  |     | See Note |      | 1  |                          | – R <sub>S</sub> ≖ 100Ω |

| V <sub>OH1</sub> | OUTPUT HIGH VOLTAGE | 60  | 90       | 400  | mV | $T_A = 25^{\circ}C$ ,    |                         |

| V <sub>OH2</sub> | OUTPUT HIGH VOLTAGE | 50  | 80       | 400  | mV | T <sub>A</sub> = 70°C, _ |                         |

| VOL              | OUTPUT LOW VOLTAGE  |     | See Note |      |    | <b>⊣</b>                 |                         |

NOTE: The output current for the low state is the sum of the 1103 leakage and externally coupled noise.  $V_{OL} = I_{OL} \cdot R_S$

with  $I_{min} = 500\mu A$  and  $I_{ref} = 400\mu A$ ,

$$V_{ref} = 500 \sqrt{\frac{100}{10 \times 100}} = 150 \,\text{mV}$$

$$\mathbf{R}_{S} = \left(\frac{175}{500}\right) \times 1000 = 350\Omega$$

$$\Delta T_A = 20 + \left[ \frac{400}{10} - \frac{750}{35} \right] + \frac{350 - 100}{1000} \times 100 = 64 \text{ nsec}$$

Thus the sense amp (3208A) circuitry contributes an additional 64 ns to the access time of the system.

#### a. 3208A Block Diagram

#### b. 3408A Block Diagram

#### c. Using SN75107/75108

#### d. Using Low Power TTL

f. Conversion to ECL Levels

Figure 1.16. Sense Amplifiers

Figure 1.16 also shows several other circuits for converting the output current to logic levels.

The circuit shown in Figure 1.16c uses one half of a SN5107 or SN75108 line receiver as a sense amplifier. The SN75108 requires a differential signal of at least 25 mV for guaranteed operation. The high input side may require up to  $75\mu\mathrm{A}$  input current. The SN75107/8 may be used with balanced or unbalanced input. In Figure 1.16c the SN75108 is shown with a balanced input circuit. Current from the 1103 array is sensed across resistor  $\mathrm{R}_{\mathrm{S}}$ .

The reference threshold is established by the combination of resistors  $R_1$  and  $R_2$ , with  $R_2$  usually made equal to  $R_S$ . Using the minimum "1" level current of  $500\mu A$  from the 1103 and the  $25\,\mathrm{mV}$  and  $75\mu A$  characteristic of the SN75108, the reference level must be less than  $(.50-.075)R_S-25\,\mathrm{mV}$ , where  $R_S$  is in ohms. However, the reference level must be in excess of  $25\,\mathrm{mV}$  for proper detection of zeroes. For this reason,  $R_S$  must be larger than  $100\Omega$  when using the 75108. A value of 200 to  $400\Omega$  is more appropriate.

In some systems, the effects of capacitively coupled noise on the data output line may be reduced by adding a dummy line in the array. This dummy line runs parallel to the sense line, but makes no connection. The noise signals then couple more or less equally into both lines and appear as common mode signals at the inputs to the SN75108. However, the output currents from the 1103s couple into only one line, and therefore contribute to a differential between the lines.

The SN75108 may be also used as an unbalanced sense amplifier by grounding one of the differential inputs and adding a negative bias current to the sense line input. This current may be supplied by a suitable resistor returned to a negative supply voltage.

The two versions of the part differ in that the SN75107 has a totem-pole TTL output, while the SN75108 has an open collector output. The SN75108 may be used to advantage in large systems, where several memory modules may share a common data bus.

A comparator, such as the  $\mu$ A710 or MC1710, could be used as a sense amplifier in a similar fashion. The tighter differential voltage tolerance (6.5 mV vs. 25 mV) and lower bias current (40 $\mu$ A to 75 $\mu$ A) permit lower sense resistor values. However, the lack of strobe signal input and/or open collector output, and the more awkward power supplies required by the 710 make it a less desirable choice.

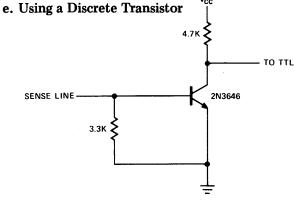

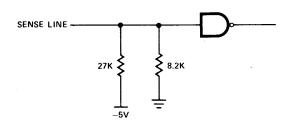

Unlike the 3208A and 3408A, the SN75108 requires an additional negative supply for its operation. Where performance can be sacrificed, sensing can also be done without an extra supply by using circuits such as those of Figure 1.16d and 1.16e. In Figure 1.16d, low power TTL is biased to allow direct sensing of the output current. In Figure 1.16e a discrete transistor circuit is used for sensing. Each of these circuits adds significantly to the access time of the system.

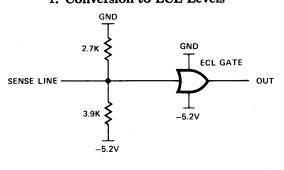

Figure 1.16f shows one possible connection for conversion to ECL levels. In this circuit the 1103 output terminals

are biased about 1.5V negative with respect to  $V_{DD}$ . The relatively high impedance required adds delay to the system as described above. Another means for conversion to ECL levels is to use a discrete pnp transistor difference amplifier between the 1103 sense line and the ECL gate.

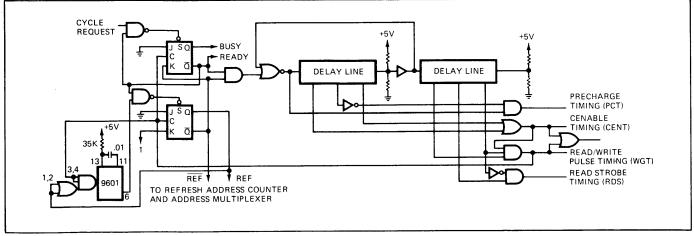

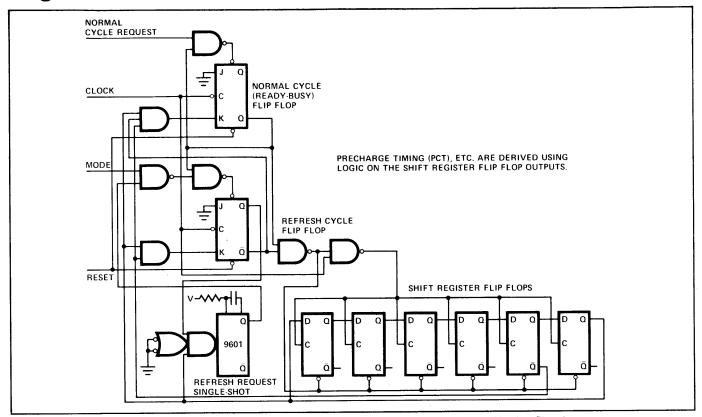

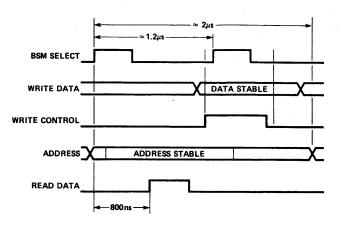

#### E. SYSTEM TIMING

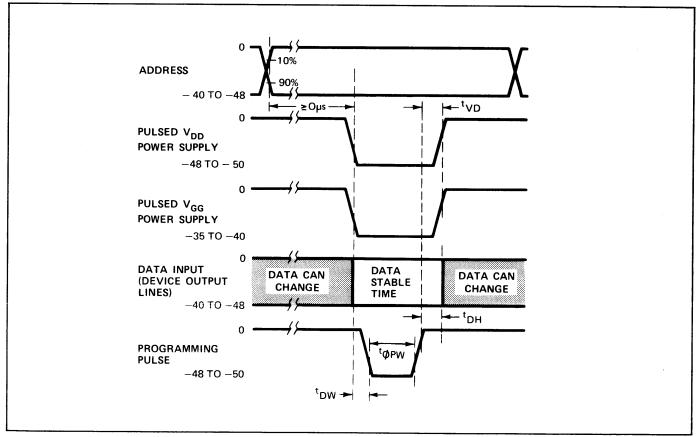

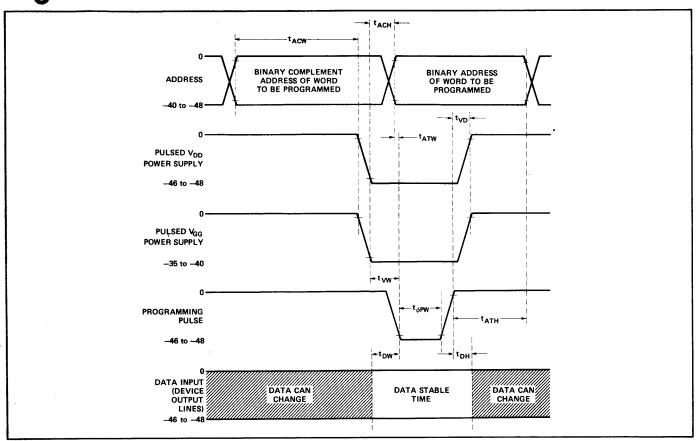

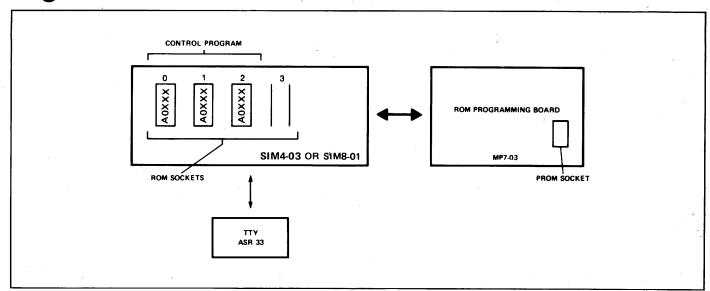

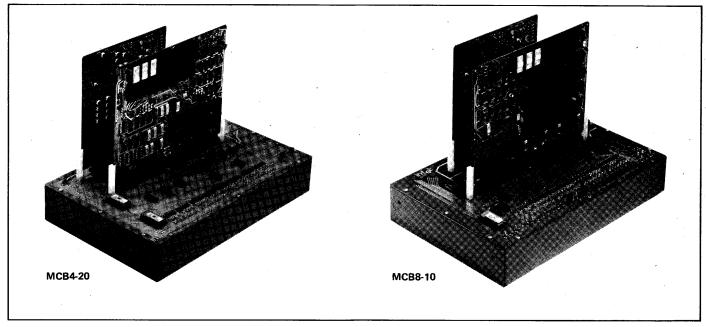

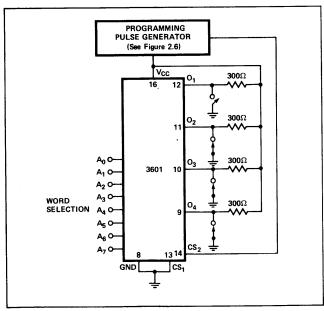

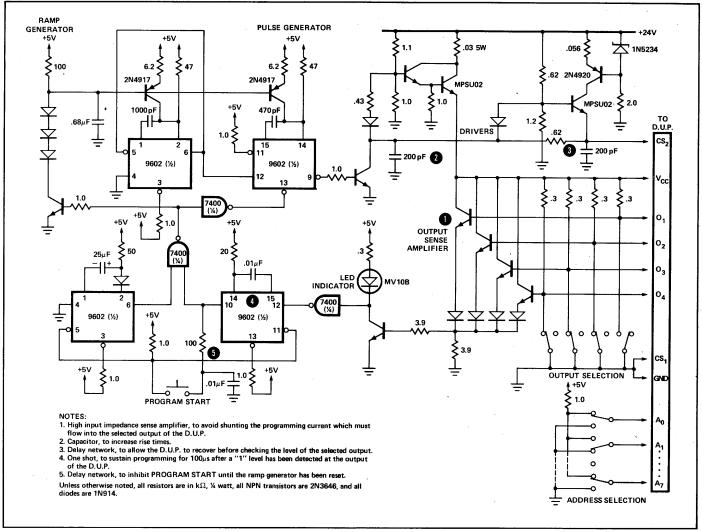

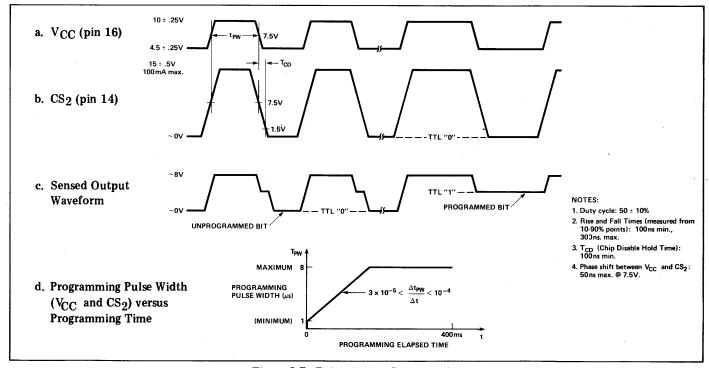

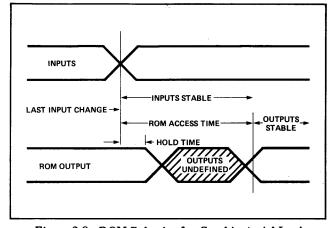

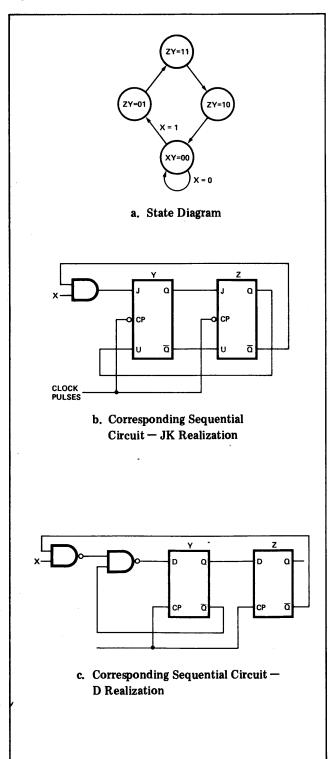

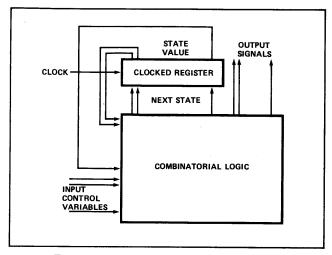

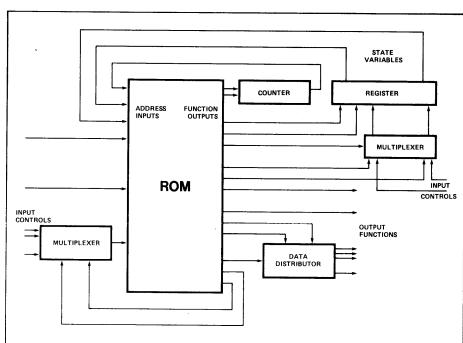

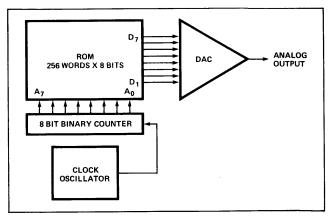

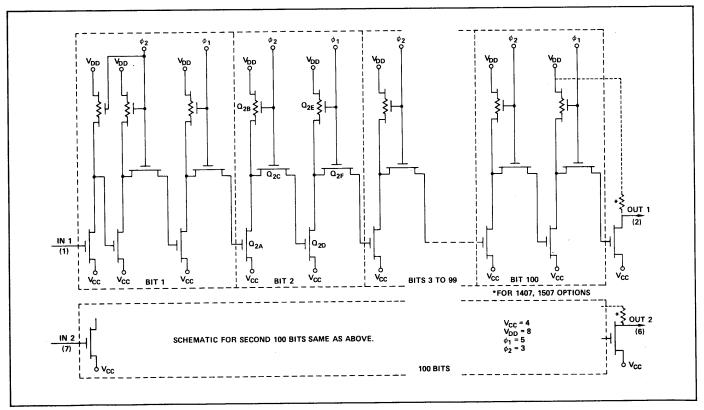

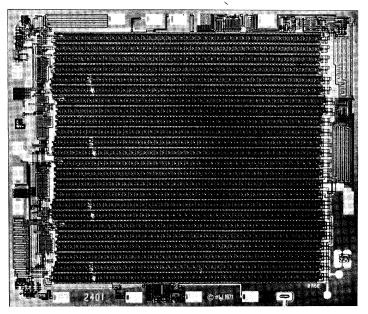

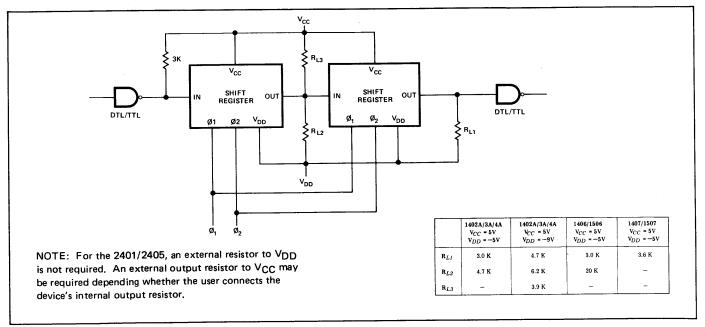

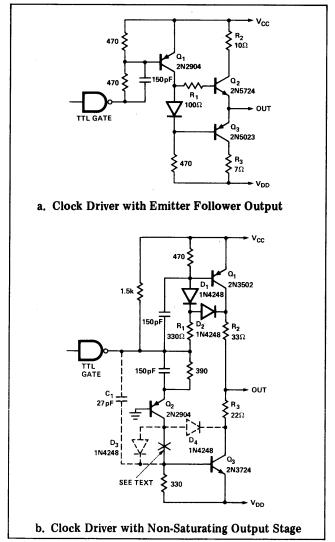

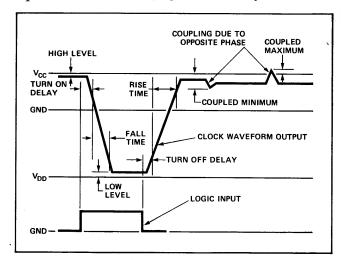

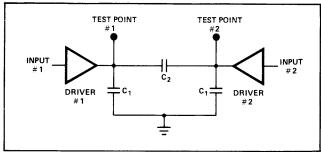

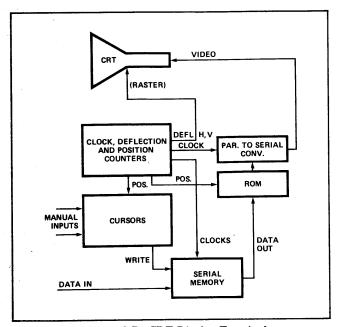

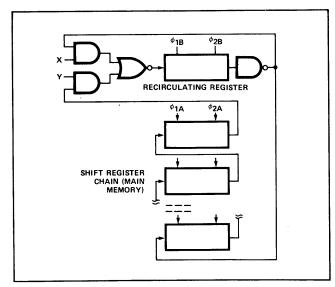

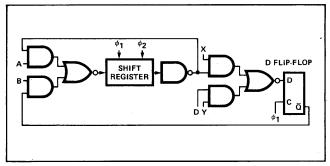

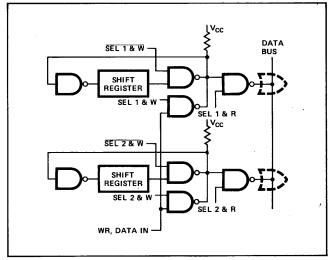

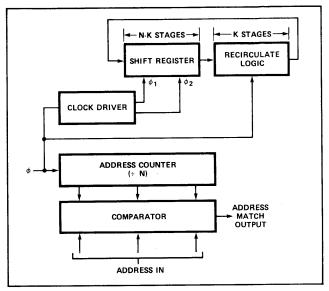

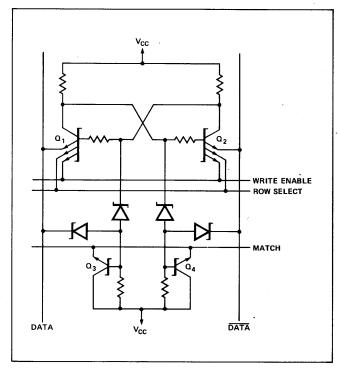

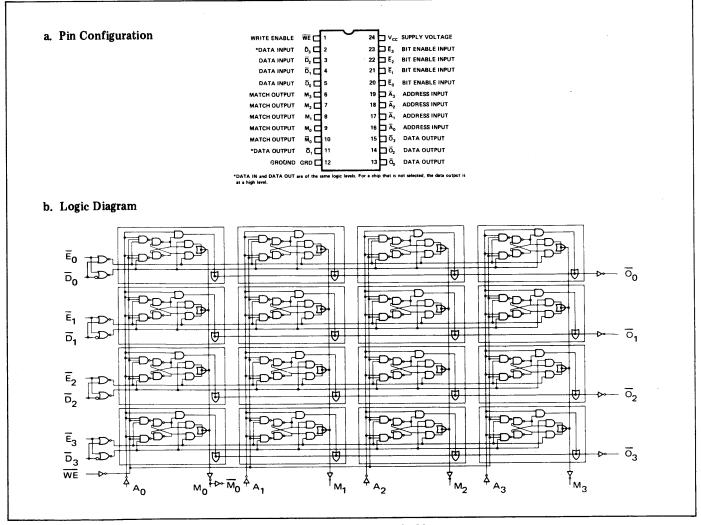

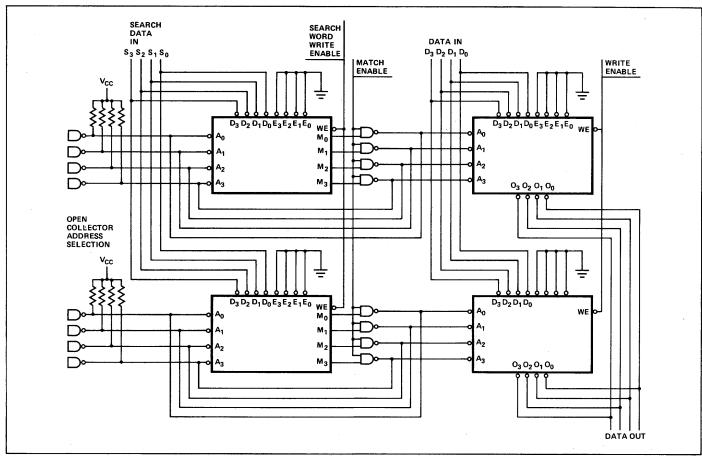

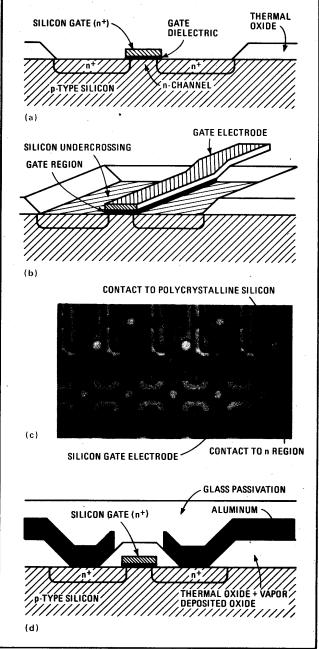

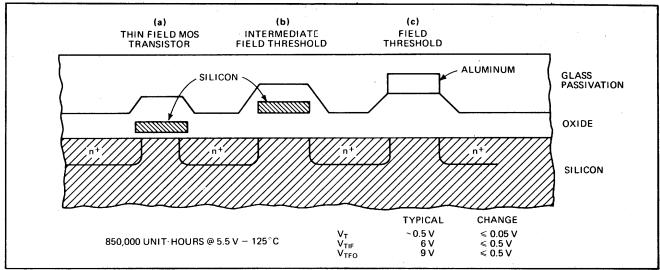

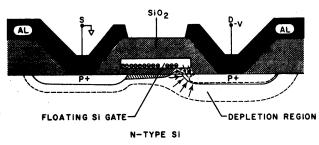

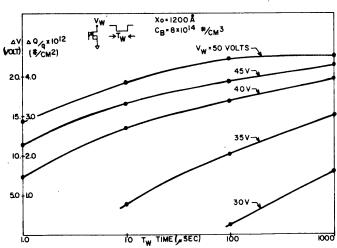

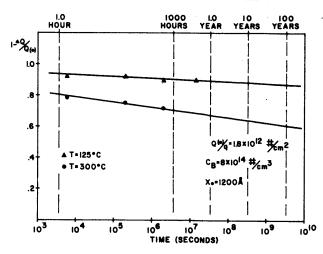

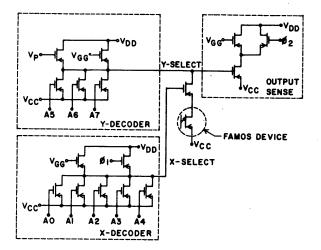

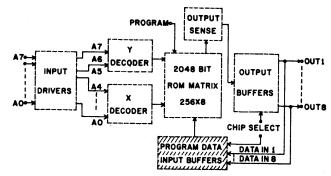

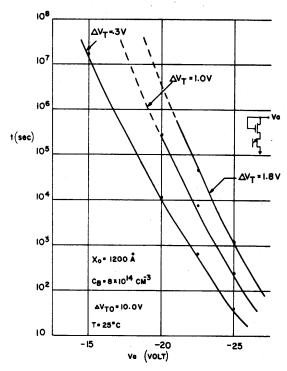

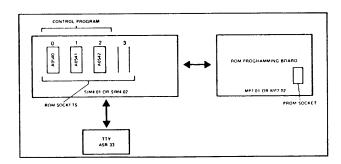

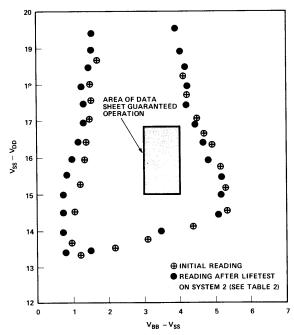

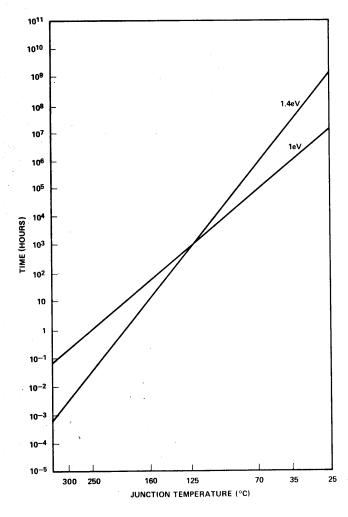

Many potential users of the 1103 have experienced some confusion as to the meaning of "minimum" and "maximum" as used in relation to the 1103 specifications. For a system-generated time value, such as  $t_{PW}$  or  $t_{OVL}$  the value, as measured at the terminals of any 1103, must fall within the stated limits. That is, for example, the time between turn-on of cenable and turn-off of precharge  $(t_{OVL})$  must fall within the range of 25 to 75 nsec. Operation outside of this range may cause inferior performance. Those time values which represent direct measurement of 1103 properties, such as  $t_{P0}$  (the time from precharge turnoff until data is available at the output) are specified as not to exceed the stated maximum values. However, 1103 access and cycle times  $(t_{ACC1}, t_{ACC2}, t_{WC}, t_{TWC}, t_{RC})$  represent a combination of system driving characteristics and 1103 characteristics. The minimum values stated represent the minimum system cycle time (or system access time) for which all parts are guaranteed to operate. These minimum values are achieved by operating with all drive signal timing values set to their minima and the access time strobing signal set at a value corresponding to the maximum  $t_{P0}$ . Of course, by selecting devices, a cycle faster than the stated minimum might be achieved. In a practical system, skews in driver and logic circuitry will usually prevent operation with all time values set at their minima, and delays in sense amplifier and latches will add to access time.