# i860 <sup>™</sup> 64 – BIT MICROPROCESSOR HARDWARE DESIGN GUIDE

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

376, 386, 386SX, 387, 387SX, 486, 4-SITE, Above, BITBUS, COMMputer, CREDIT, Data Pipeline, ETOX, Genius, i, î, i860, ICE, iCEL, iCS, iDBP, iDIS, IPICE, iLBX, i<sub>m</sub>, iMDDX, iMMX, Inboard, Insite, Intel, int<sub>e</sub>l, Intel376, Intel386, int<sub>e</sub>IBOS, Intel Certified, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, iOSP, iPDS, iPSC, iRMK, iRMX, iSBC, iSBX, iSDM, iSXM, KEPROM, Library Manager, MAPNET, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, ONCE, OpenNET, OTP, PC BUBBLE, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Quick-Frase, Quick-Pulse Programming, Ripplemode, RMX/80, RUPI, Seamless, SLD, SugarCube, UPI, and VLSiCEL, and the combination of ICE, iCS, iRMX, iSBC, iSBX, iSXM, MCS, or UPI and a numerical suffix.

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

CHMOS and HMOS are patented processes of Intel Corp.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 58130 Santa Clara, CA 95052-8130

CINTEL CORPORATION 1989

## PREFACE

#### **Preface**

The Intel i860<sup>™</sup> 64-bit Microprocessor combines capabilities of supercomputers and 3D graphics workstations in a single VLSI component. The versatile 64-bit design of the i860 microprocessor balances performance across integer, floating point, and graphics processing capability. Its parallel architecture achieves high throughput with RISC design techniques, pipelined processing units, wide data paths, large on-chip caches and fast one micron CHMOS IV\* silicon technology.

This manual provides the basic information required to implement an i860 Microprocessor based system. It explains all the hardware details of the processor. The design examples published in this manual are NOT TESTED. The tested examples will be published at a later date.

Although the main users of this manual are hardware design engineers. It contains basic hardware information which is of value to the software engineers and programmers. These readers should reference the first three chapters only.

#### RELATED PUBLICATIONS

In this manual, the i860 microprocessor is presented from a hardware perspective. Information on the software architecture, instruction set and programming can be found in these related Intel publications:

\* i860 Microprocessor Programmers Reference Manual, Order Number 240329

Information on the device specification for the i860 microrocessor is available in the  $i860^{\text{TM}}$  Microrocessor Data Sheet, Order Number 240296. Always refer to the most recent version of the device specification.

#### ORGANIZATION OF THE MANUAL

- \* Chapter 1, "Introduction to i860 64-bit Microprocessor". This chapter provides an overview of the features of the "i860 Microprocessor" and the advantages to the system designers. It also provides the insight to i860 microprocessor applications.

- \* Chapter 2, " Internal Architecture ". This chapter describes the internal architecture of the i860 Microprocessor.

- \* CHMOS is the patented process of Intel Corporation

- \* Chapter 3, \* Local Bus Interface \*. This chapter discusses the i860 Microprocessor local bus interface. This includes the signal descriptions, bus operation and local bus interface guidelines.

- \* Chapter 4, " Memory Interfacing ". This chapter discusses techniques for designing memory subsystems for the i860 microprocessor.

- \* Chapter 5, " I/O Interface ". This chapter discusses techniques for connecting I/O devices to an i860 microprocessor system.

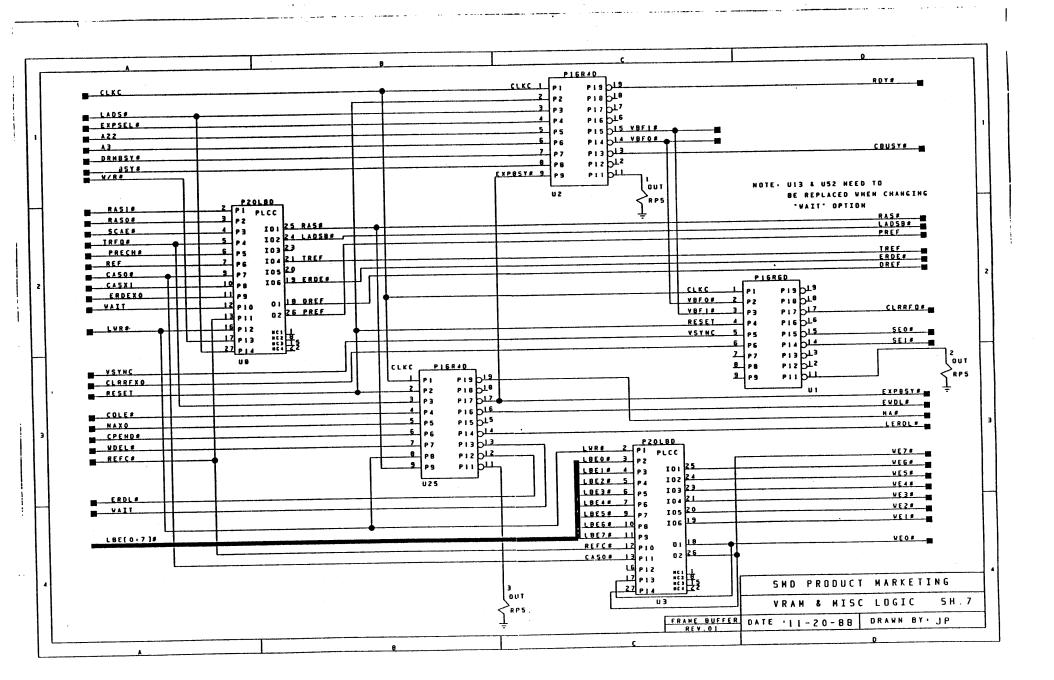

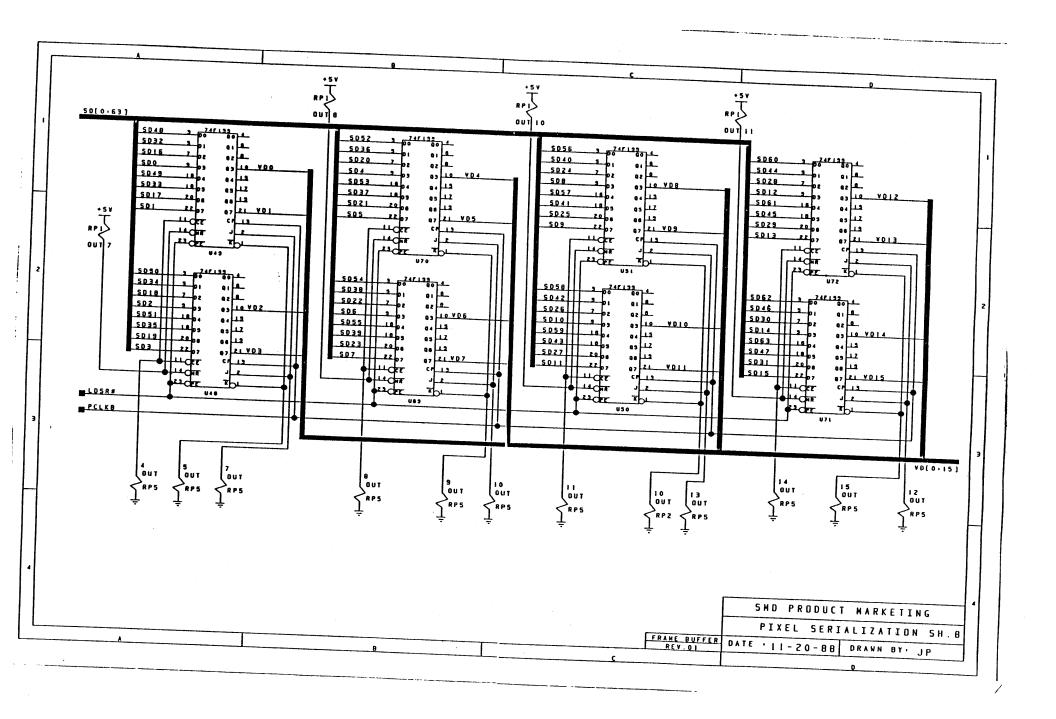

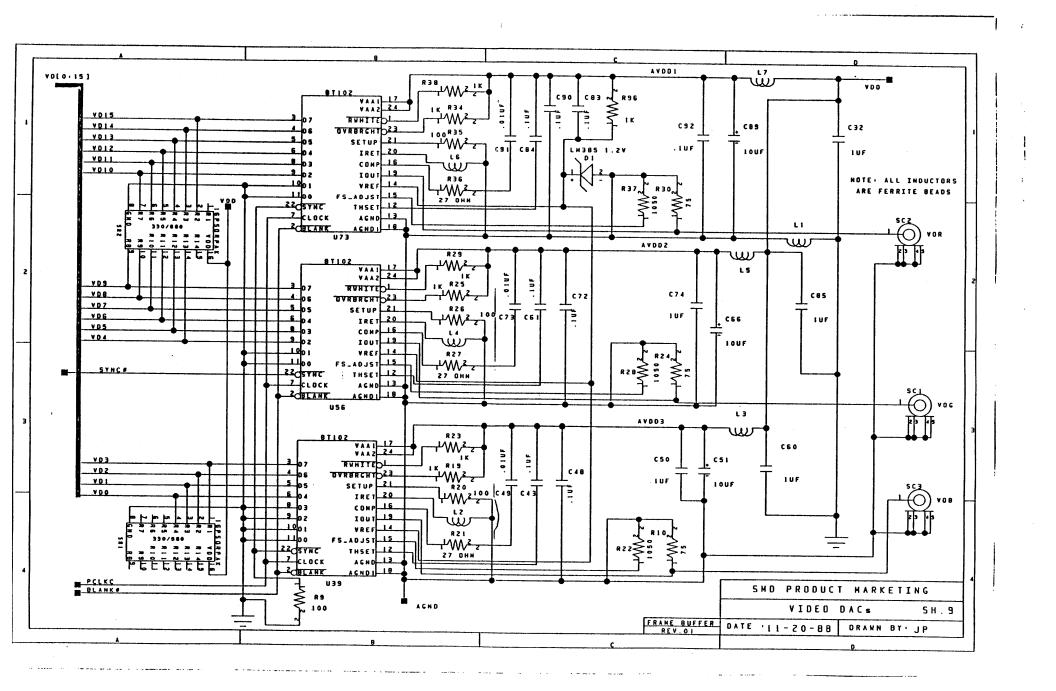

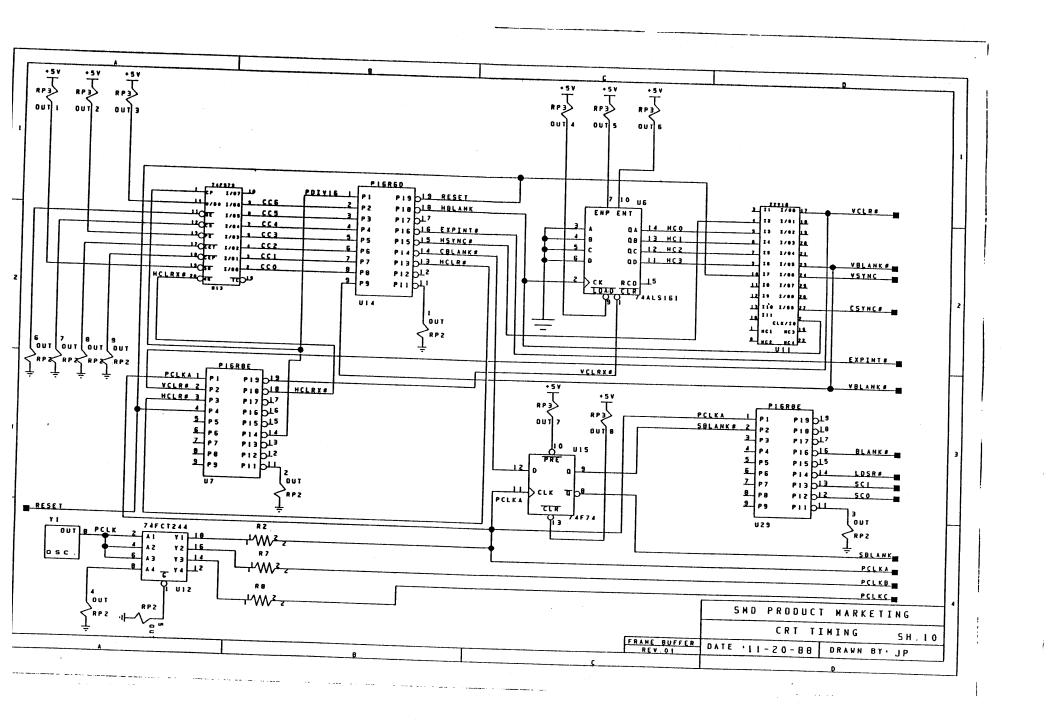

- \* Chapter 6, " Graphics Subsystem Example ". This chapter discusses a design example for implementing an i860 microprocessor based graphics subsystem example.

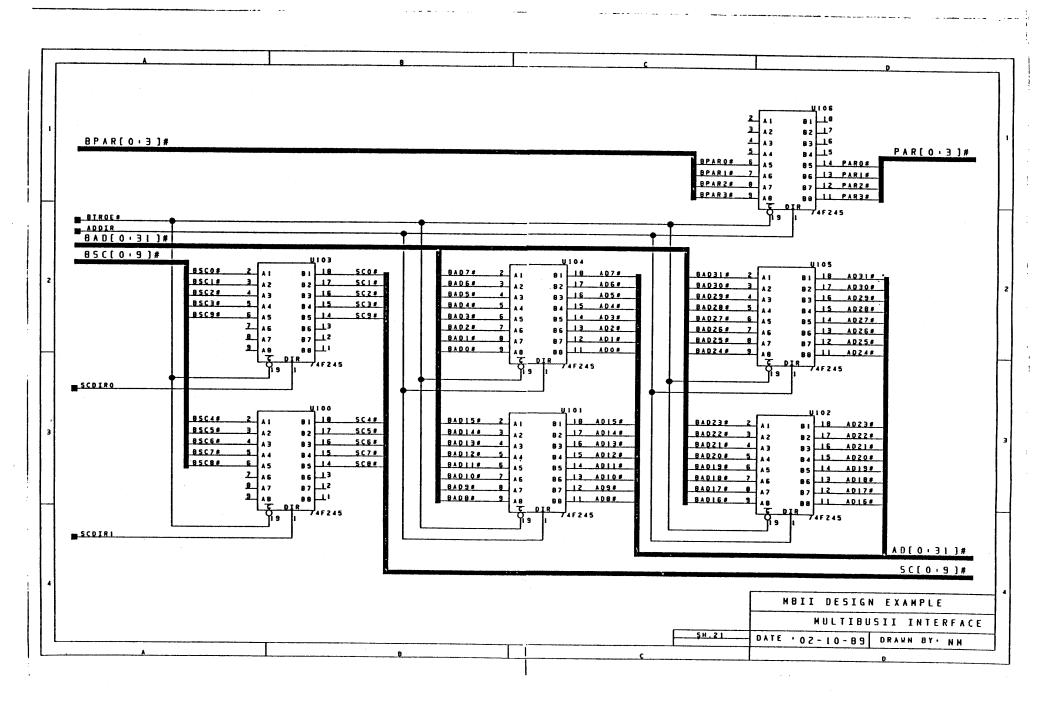

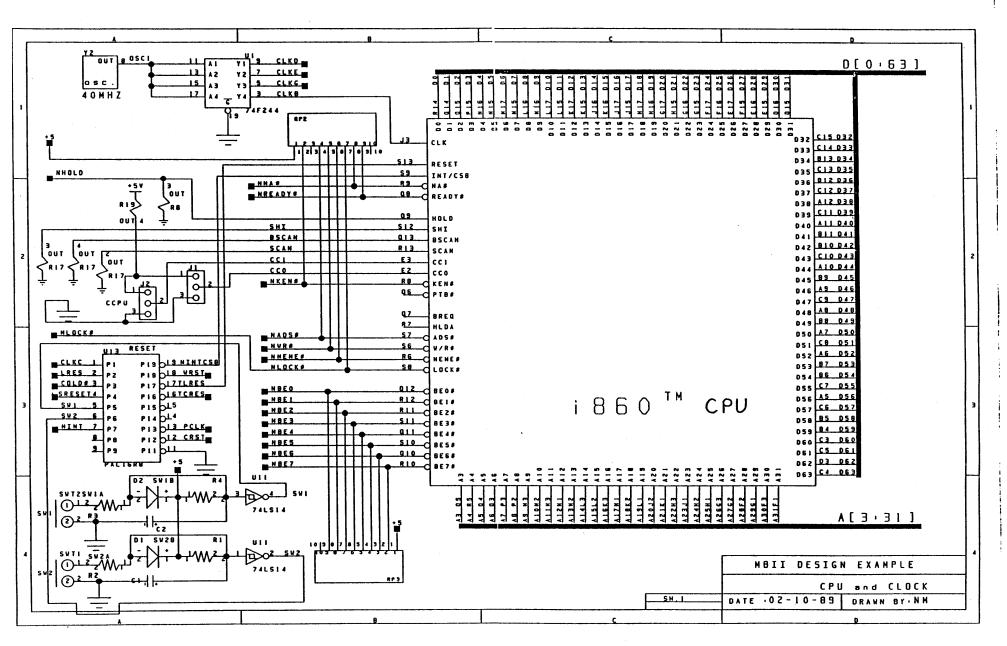

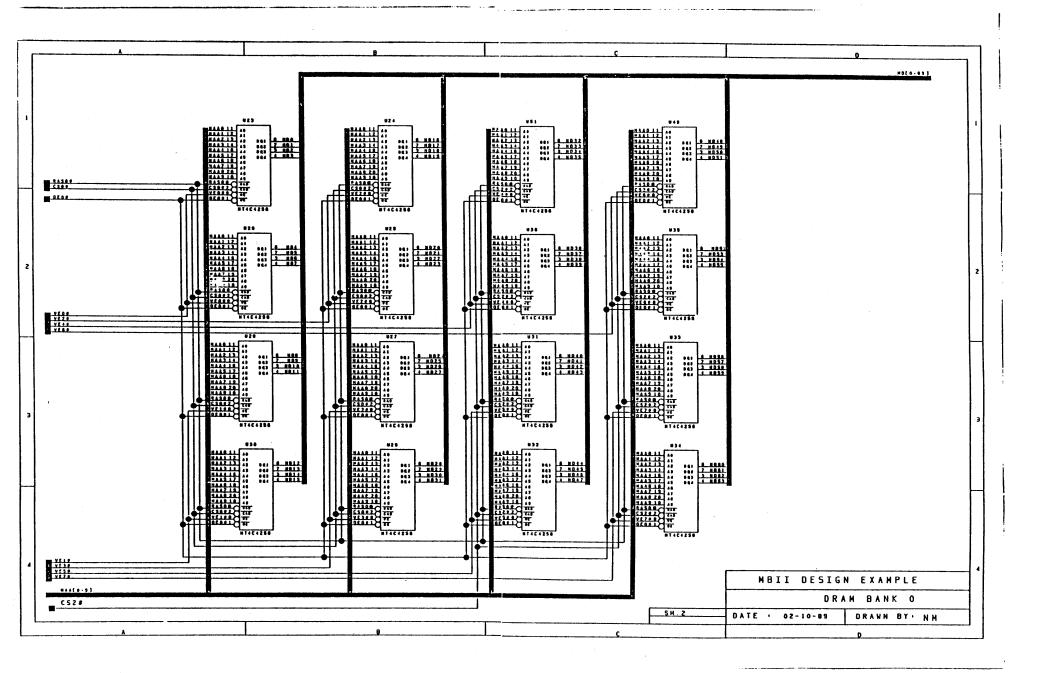

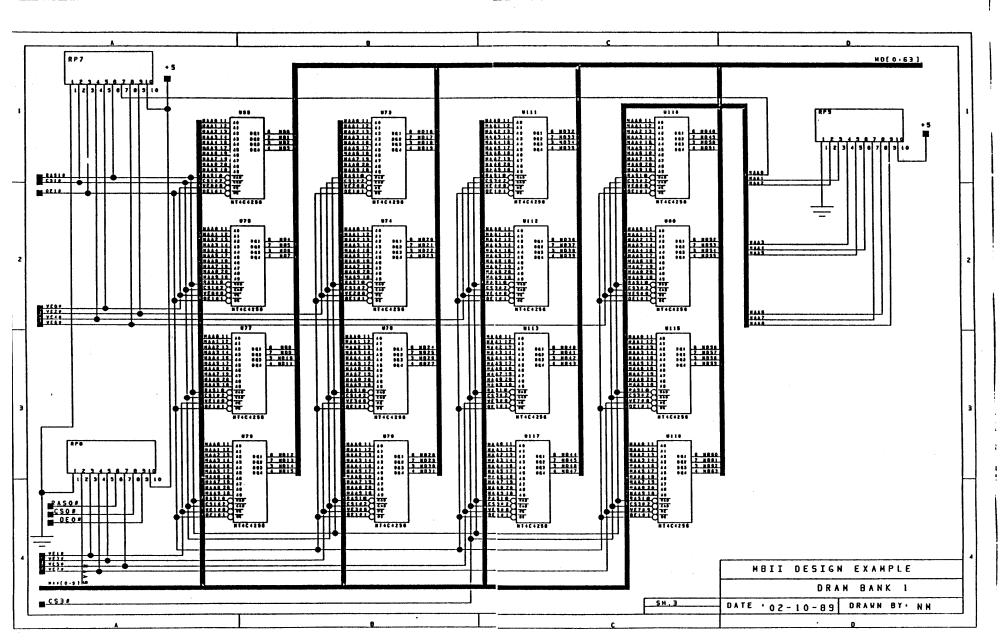

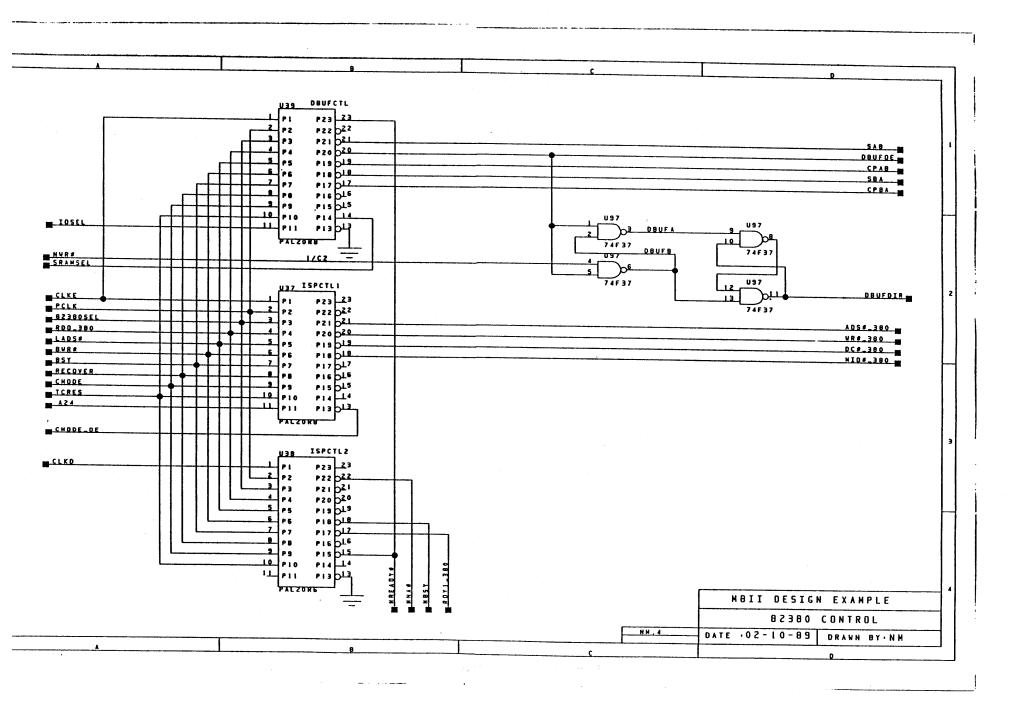

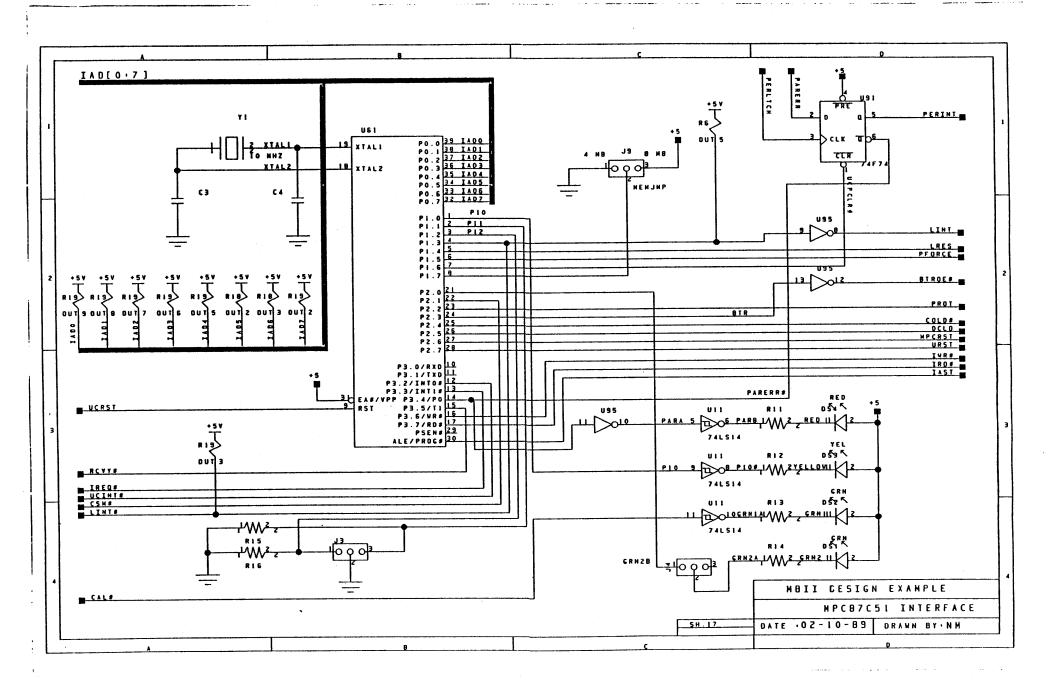

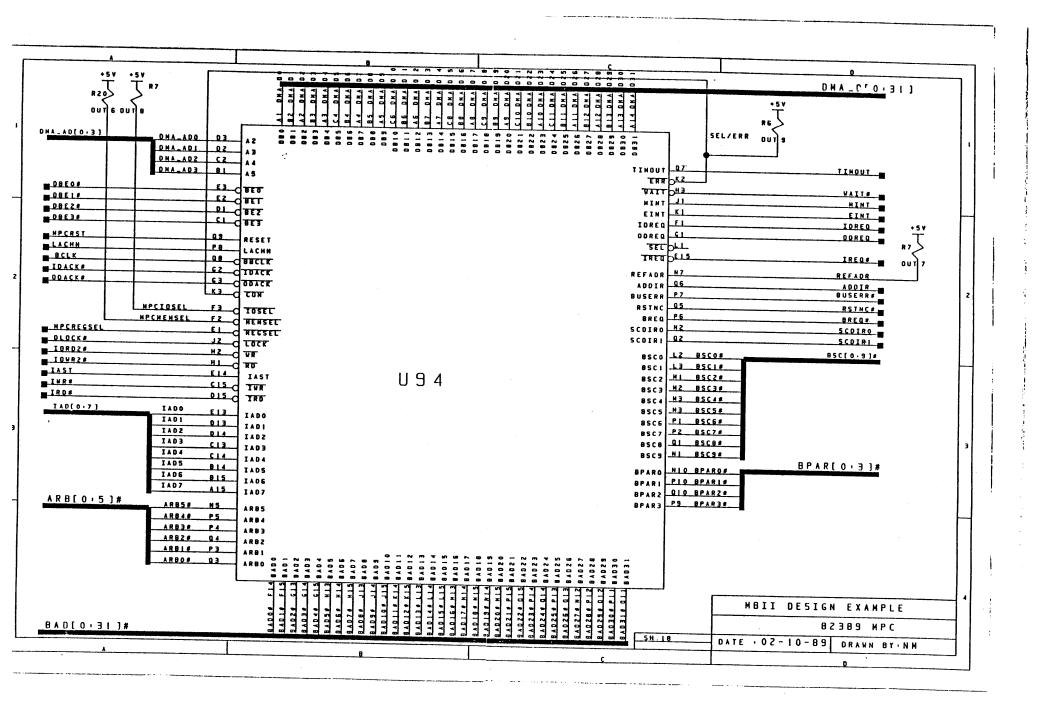

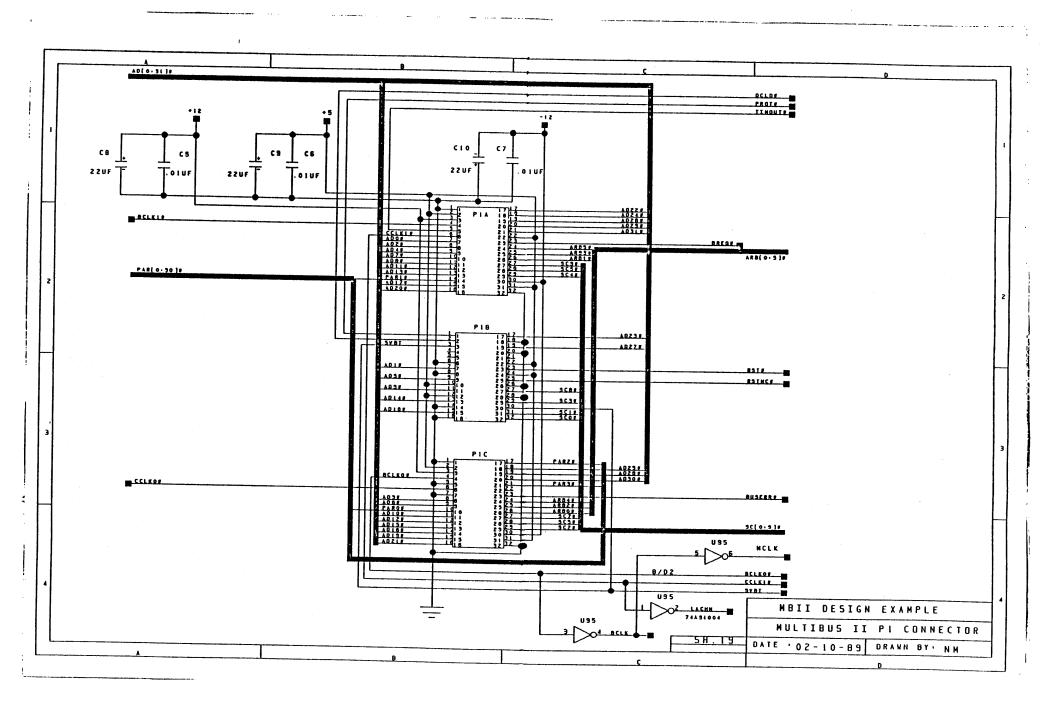

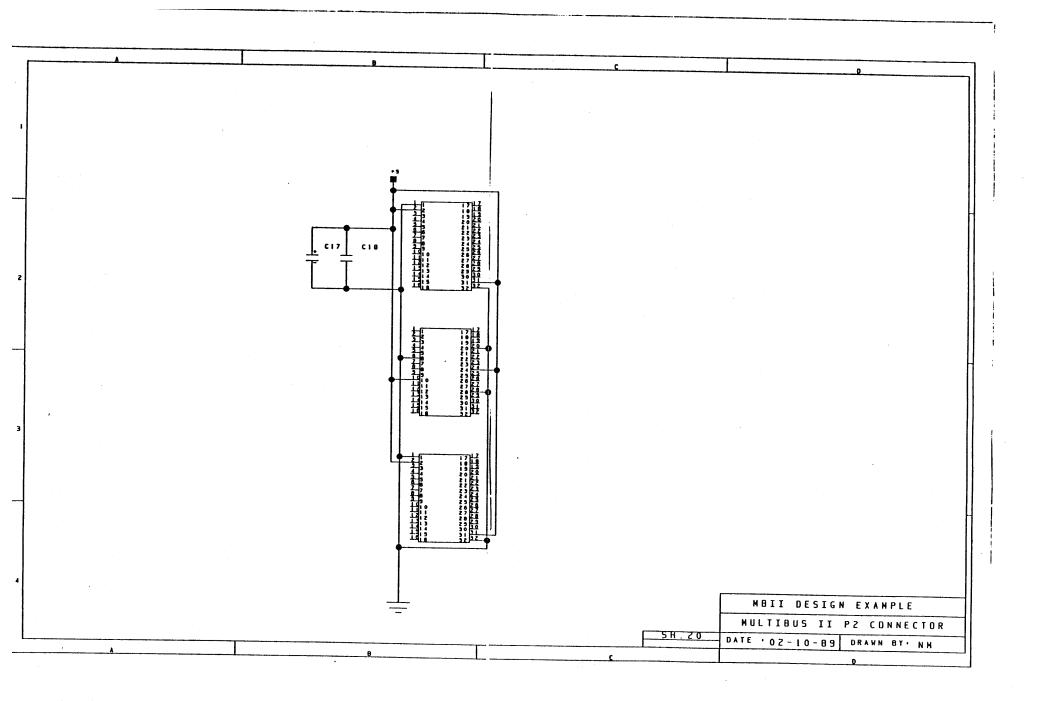

- \* Chapter 7, " MULTIBUS II and i860 Microprocessor". This chapter provides a design example for the MULTIBUS II board built around the i860 microprocessor.

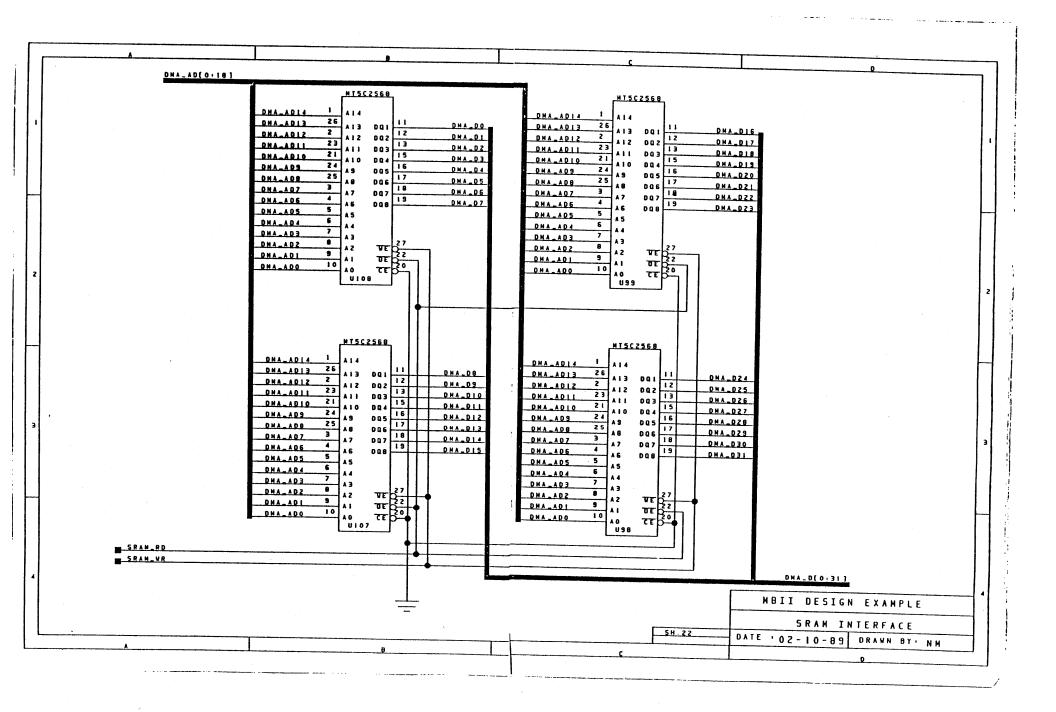

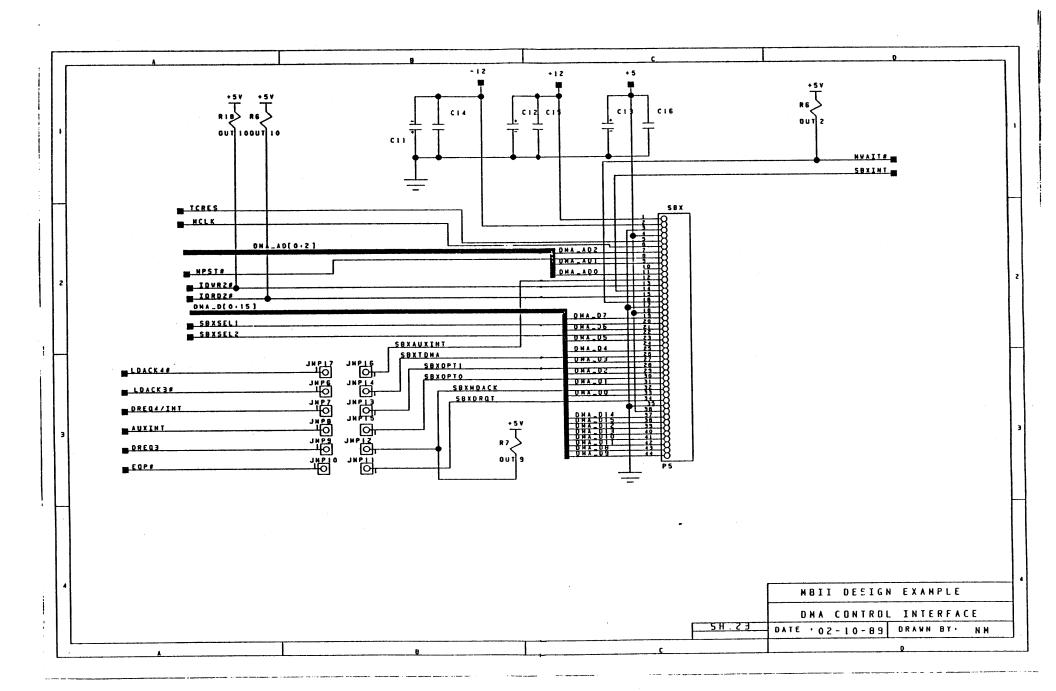

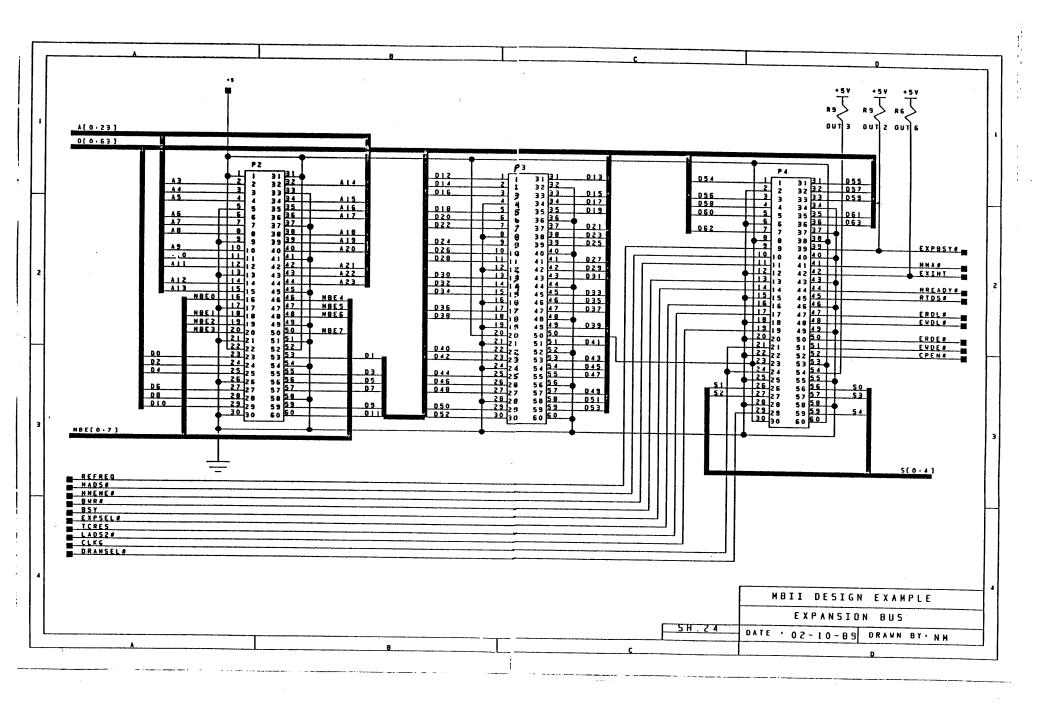

- \* Appendix A and B provides the UNTESTED schematics of i860 microprocessor Graphics Frame Buffer Board and the Multibus II board. Appendix A is to be used in conjunction with Chapter 6. Appendix B contains the DRAM interfacing for Chapter 4 and the MULTIBUS II interface for Chapter 7.

| CHAPTER                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                   | PAGE                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| INTRODUC                                                                                                                                  | TION TO 1860™ 64-BIT MICROPROCESSOI                                                                                                                                                                                                                                                                                                                                                 | 3                                            |

| 1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.2.3<br>1.2.4<br>1.2.5<br>1.2.6<br>1.2.7<br>1.2.8<br>1.2.9<br>1.2.10<br>1.2.11<br>1.2.12<br>1.3<br>1.3.1 | Processor characteristics Processor overview. Pipelining and parallelism. Reduced instruction set architecture. Registers Address space Floating point operations Graphics support. Caches. Paging Unit Debugging support External interface. Clock requirements. Packaging/power requirements. System configuration. Private and shared memory configuration Application overview. | 1-9                                          |

| CHAPTER 1                                                                                                                                 | rwo                                                                                                                                                                                                                                                                                                                                                                                 |                                              |

| INTERNAL .                                                                                                                                | ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                        |                                              |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>2.3<br>2.3.1<br>2.4<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.4      | Floating point adder unit.  Floating point multiplier unit.  Dual operation feature.  Dual instruction mode.  Floating-point computation throughput.  Paging unit.  Paging algorithm.  On chip caches and bus control.  Instruction cache unit.                                                                                                                                     | 2-13<br>2-14<br>2-16<br>2-17<br>2-17<br>2-18 |

|         | :                                             |              |

|---------|-----------------------------------------------|--------------|

| 2.5     | Bus and cache control unit                    | PAGE         |

| 2.4.6   |                                               | 2-20<br>2-21 |

| 2.5     | Graphics unit                                 | 2-21         |

|         |                                               | 2-21         |

| CHAPTE  | R 3                                           |              |

| LOCAL E | BUS INTERFACE                                 |              |

| 3.1     | i860 microprocessor external interface        |              |

|         | and bus signals                               | 3-1          |

| 3.1.1   | i860 microprocessor buses                     |              |

| 3.1.2   | i860 microprocessor output signals            |              |

| 3.1.3   | Input signals                                 | 3-1          |

| 3.1.4   | Power and ground pins                         | 3-4          |

| 3.2     | Bus characteristics                           | 3-4          |

| 3.3     | Bus transfer operations                       | 3-5          |

| 3.3.1   | 64-bit bus and byte                           | 3-6          |

| 3.3.2   | Basic bus operation                           | 3-9          |

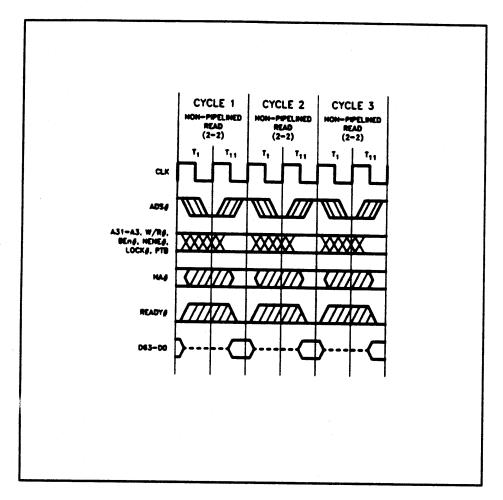

| 3.3.3   | Nonpipelined bus operation                    | 3-10         |

| 3.3.3.1 | Nonpipelined read operations                  | 3-11         |

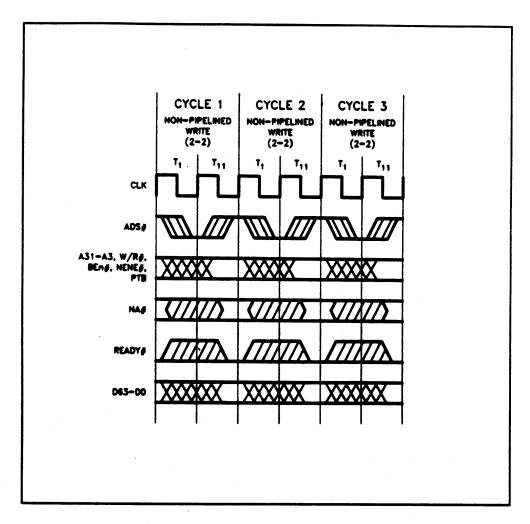

| 3.3.3.2 | Nonpipelined write cycles                     | 3-12         |

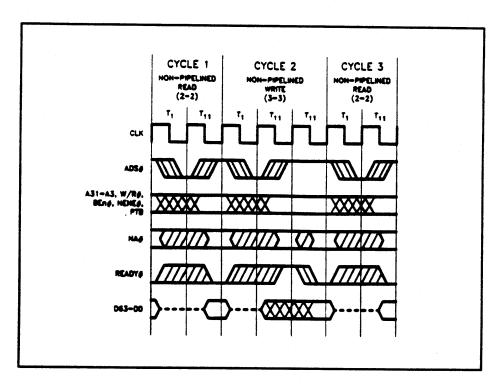

| 3.3.3.3 | Write cycles following read cycles            | 3-14         |

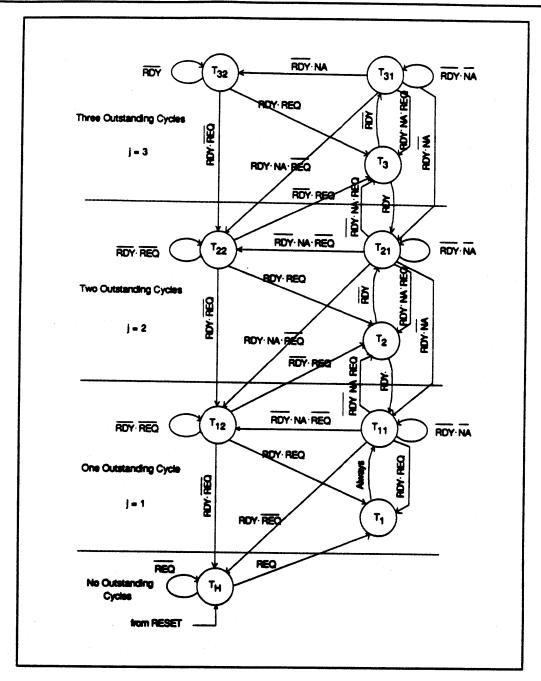

| 3.3.4   | Pipelined operations                          | 3-15         |

| 3.3.4.1 | Pipelined and interleaved memory banks        | . 3-16       |

| 3.3.4.2 | Ordering of data during pipelined operations. |              |

| 3.3.4.3 | Bus state machine for pipelining              | 3-17         |

| 3.3.4.4 | Pipelined read and write cycles               | 3-20         |

| 3.3.5   | 8-bit transfers for bootstrapping (CS8 mode). | 3-22         |

| 3.4     | Bus control operations                        | 3-23         |

| 3.4.1   | Page mode, static column DRAMs and next       |              |

|         | near operation                                | 3-23         |

| 3.4.2   | Bus hold, hold acknowledge, bus request       | 3-24         |

| 3.4.3   | Bus lock                                      | 3-27         |

| 3.4.3.1 | Supervisor Mode activation of lock number     | . 3-28       |

| 3.4.3.2 | User-mode activation of lock number           |              |

| 3.4.3.3 | Bus lock during page table update             | 3-29         |

| 3.5     | Cache control operations                      | 3-30         |

| 3.6     | Traps and interrupts                          | 3-31         |

| 3.7     | Test support functions                        | 3-33         |

| 3.7.1   | Normal mode operation                         | 3-34         |

| 3.7.2   | Serial mode operation                         | 3-34         |

| 3.8     | Reset and clock circuit                       | 3-35         |

|         |                               | PAGE  |

|---------|-------------------------------|-------|

| CHAPTER | R 4                           |       |

| MEMORY  | INTERFACING                   |       |

| 4.0     | Introduction                  | 4-1   |

| 4.1     | CPU features                  | 4-2   |

| 4.1.1   | The KEN# input                | 4-2   |

| 4.1.2   | Bus pipelining                | 4-3   |

| 4.1.3   | The next near pin             | 4-4   |

| 4.1.4   | Write data function           | 4-4   |

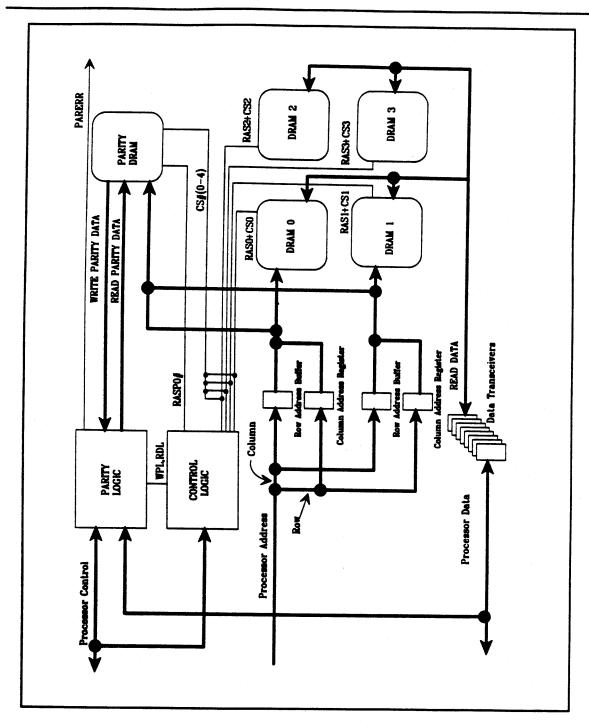

| 4.2     | DRAM subsystem overview       | . 4-6 |

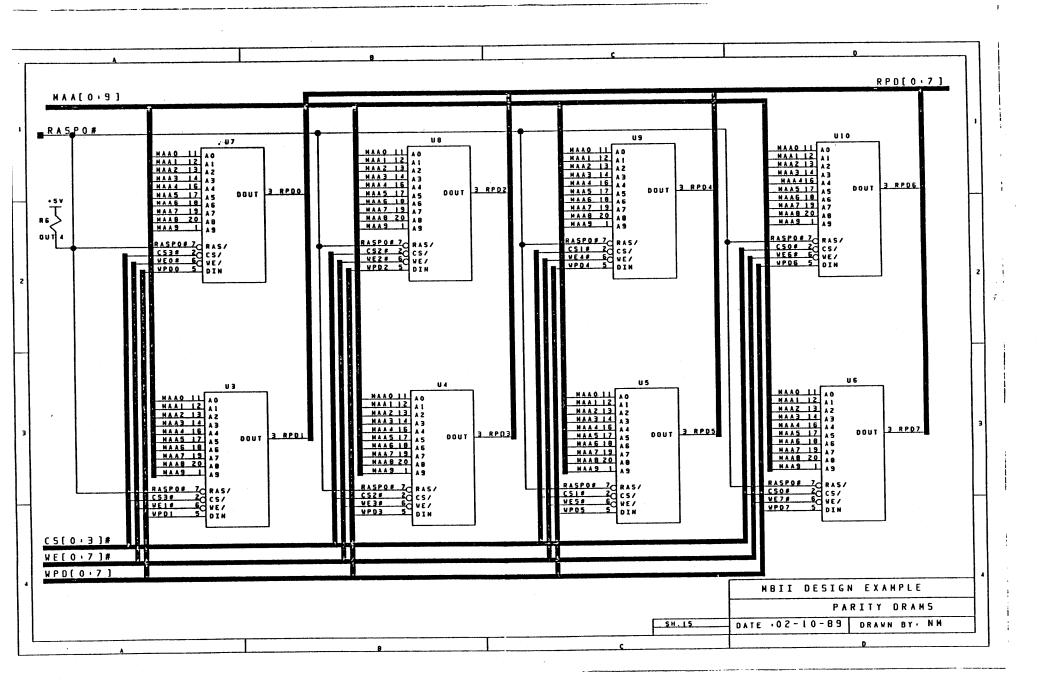

| 4.2.1   | Address path logic            | 4-6   |

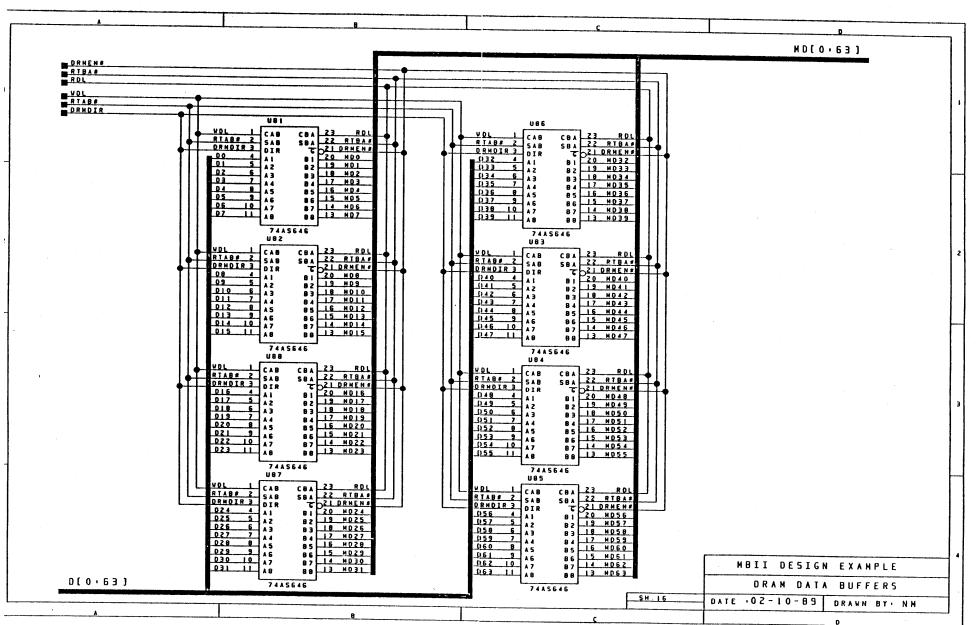

| 4.2.2   | Data path logic               | 4-7   |

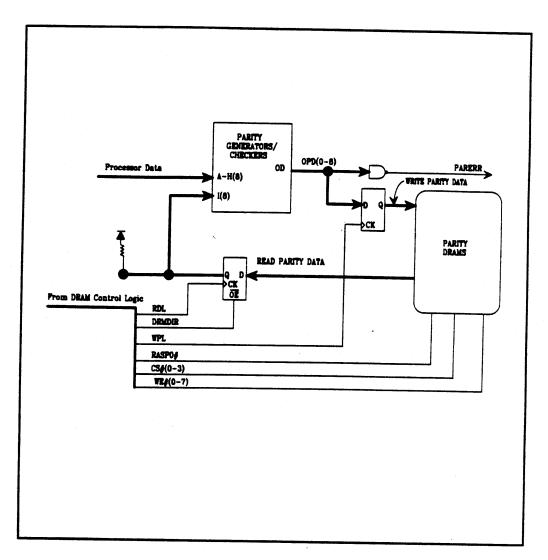

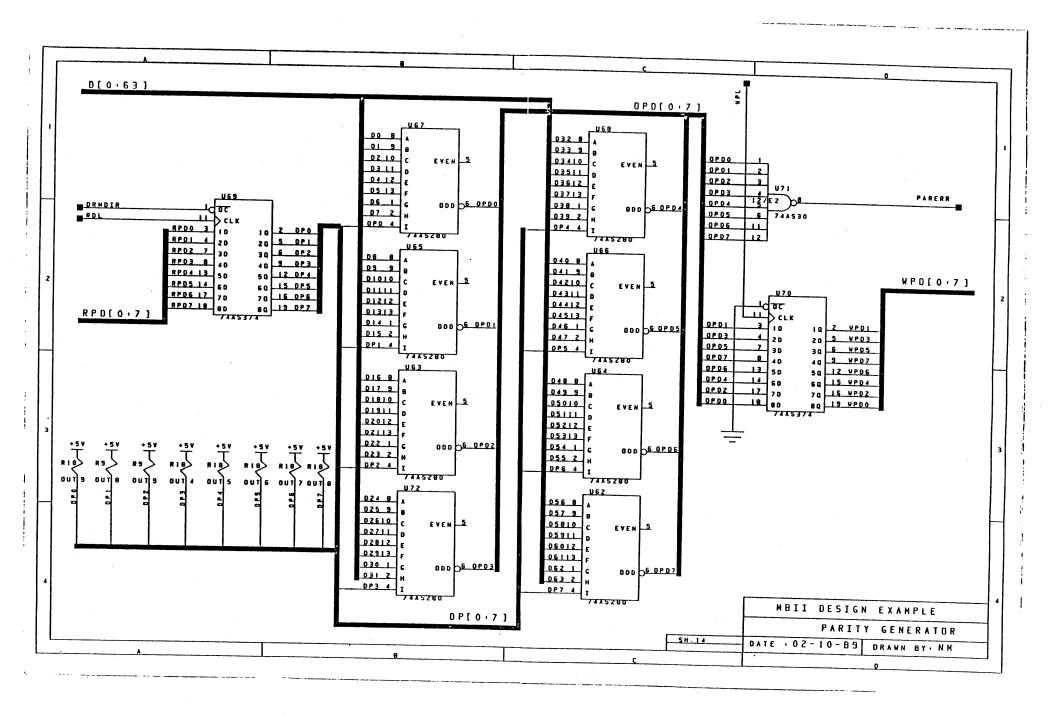

| 4.2.3   | Parity logic                  | 4-7   |

| 4.2.4   | Control logic                 | 4-9   |

| 4.3     | Subsystem function            | 4-11  |

| 4.3.1   | Signal description            | 4-11  |

| 4.3.1.1 | Processor interface           | 4-11  |

| 4.3.1.2 | Data path logic control       | 4-11  |

| 4.3.1.3 | Address path logic control    | 4-12  |

| 4.3.1.4 | Controller signals            | 4-12  |

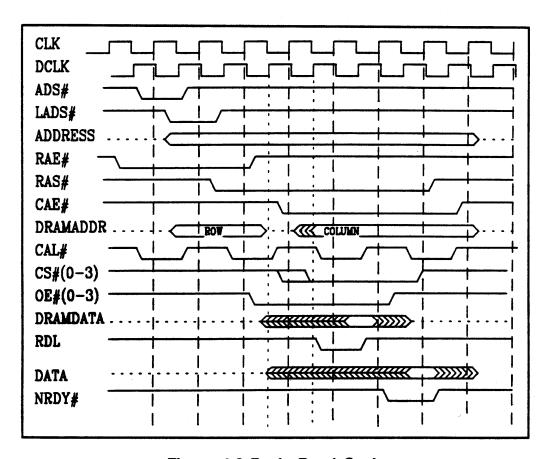

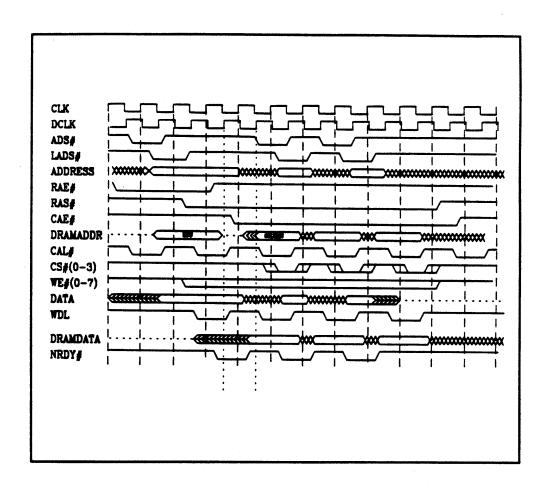

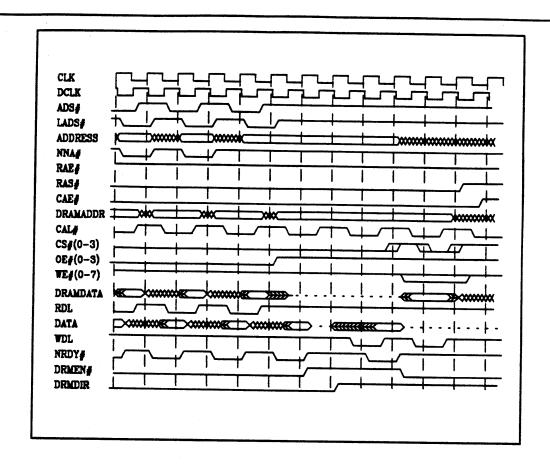

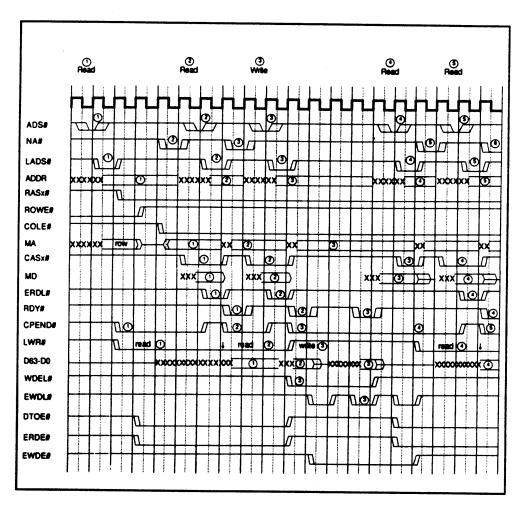

| 4.3.2   | Basic read cycle              | 4-14  |

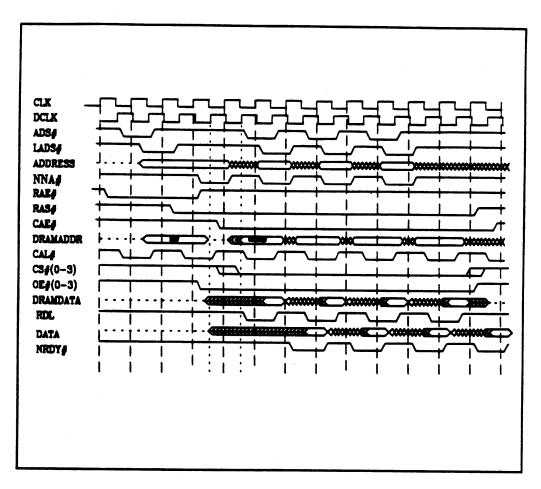

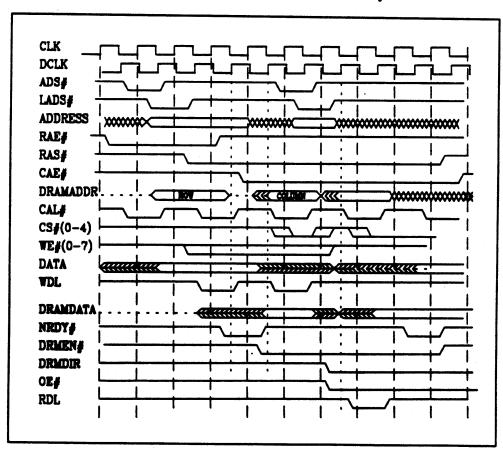

| 4.3.3   | Pipelined read cycles         | 4-15  |

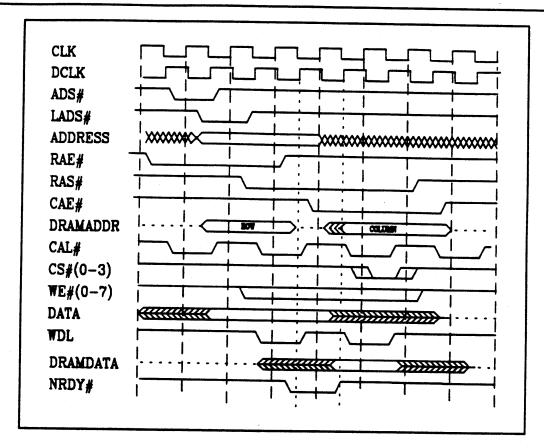

| 4.3.4   | Basic write cycle             | 4-17  |

| 4.3.4.1 | Consecutive write cycles      | 4-18  |

| 4.3.5   | Consecutive bus cycles        | 4-19  |

| 4.3.5.1 | Write followed by read cycles | 4-20  |

| 4.3.5.2 | Read followed by write cycles | 4-21  |

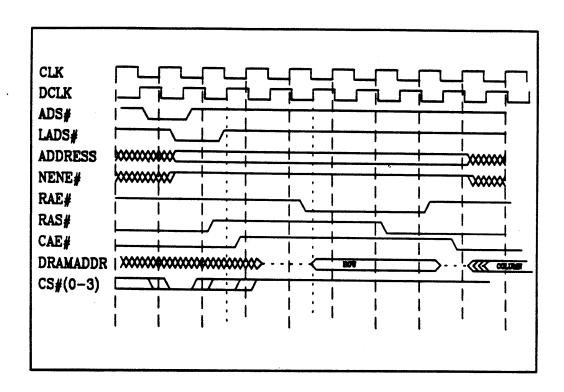

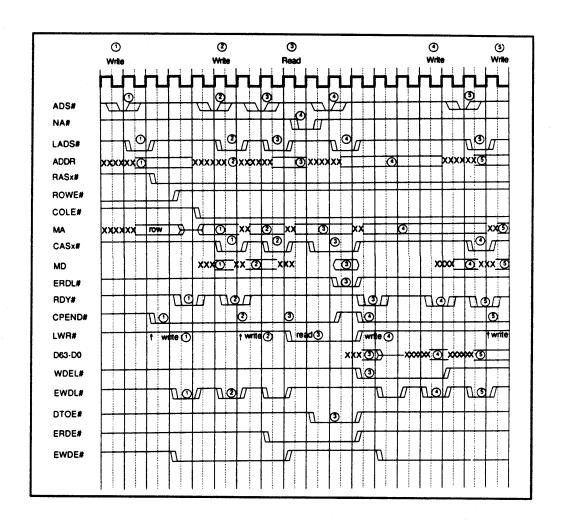

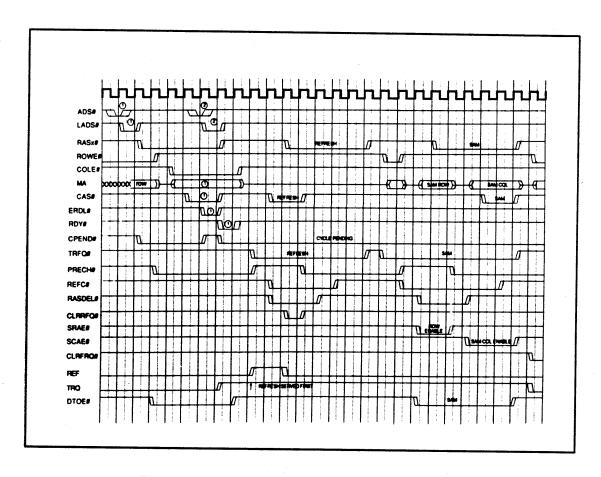

| 4.3.6   | Page miss cycles              | 4-22  |

| 4.3.7   | Refresh cycles                | 4-24  |

| 4.4     | Parity circuit                | 4-25  |

| 4.4.1   | Circuit overview              | 4-25  |

| 4.4.2   | Dedicated signals             | 4-25  |

| 4.4.3   | Parity function               | 4-27  |

| CHAPTER                                                                                                                                  | 5                                                                                                                                                                                                                                                                                                                               |                                                                          |  |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|

| I/O INTERFACING                                                                                                                          |                                                                                                                                                                                                                                                                                                                                 |                                                                          |  |

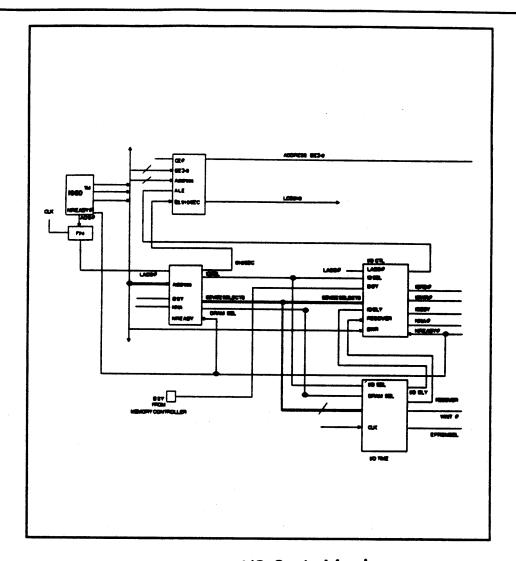

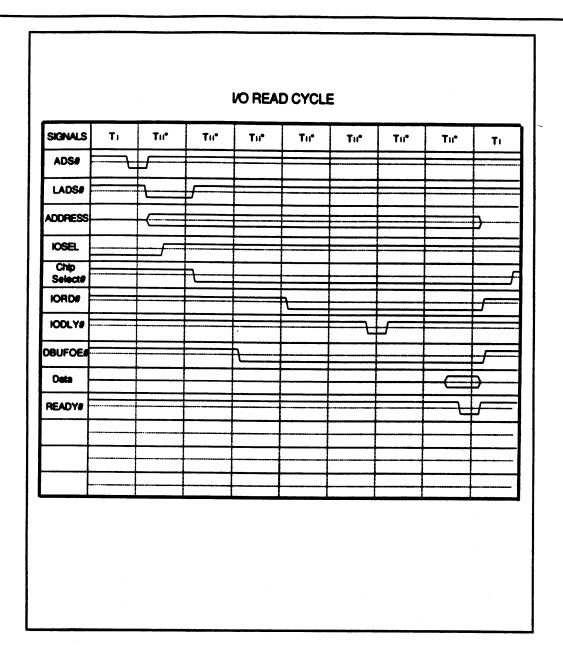

| 5.1<br>5.1.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.3<br>5.3.1<br>5.3.2<br>5.4<br>5.4.1<br>5.4.2<br>5.4.2.1<br>5.4.2.1 | Overview. i860 <sup>™</sup> I/O subsystem. Generating I/O control signals. I/O control logic Address decode and chip select. IORD#/IOWR# Ready # Recovery time I/O cycles. Read cycle timing. Write cycle timing. Design Examples 82510 interface EPROM interface Double copy load. EPROM timings DMA Interface recommendations | 5.6<br>5.7<br>5.7<br>5.7<br>5.10<br>5.12<br>5.13<br>5.16<br>5.16<br>5.19 |  |

| CHAPTER                                                                                                                                  | 6                                                                                                                                                                                                                                                                                                                               |                                                                          |  |

| GRAPHICS                                                                                                                                 | SUBSYSTEM                                                                                                                                                                                                                                                                                                                       |                                                                          |  |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.3<br>6.3.1<br>6.3.2<br>6.4<br>6.4.1<br>6.4.2<br>6.4.3                                                  | Introduction.  Graphics and the i860 microprocessor.  Performance  Processor bus bandwidth  3-D graphics example.  Features.  Testing  System overview  Expansion bus interface  Data transceiver/latch control.  Address Transceiver/Latch                                                                                     | 6.1<br>6.2<br>6.2<br>6.2<br>6.2<br>6.3<br>6.4<br>6.4<br>6.4              |  |

| •       |                                      | PAGE         |

|---------|--------------------------------------|--------------|

| 6.4.5   | Serial row/column address generation | 6.4          |

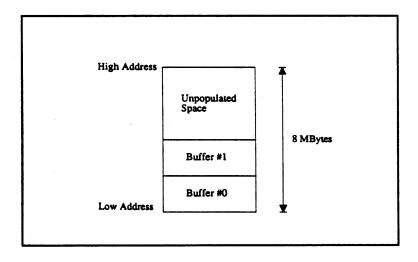

| 6.4.6   | Double buffering                     | 6.5          |

| 6.4.7   | Expansion interrupt/buffer switch    | 6.5          |

| 6.4.8   | CRT timing generation                | 6.5          |

| 6.4.9   | Pixel serializer                     | 6.5          |

| 6.4.10  | Video DACs                           | 6.5          |

| 6.5     | Operation                            | 6.5          |

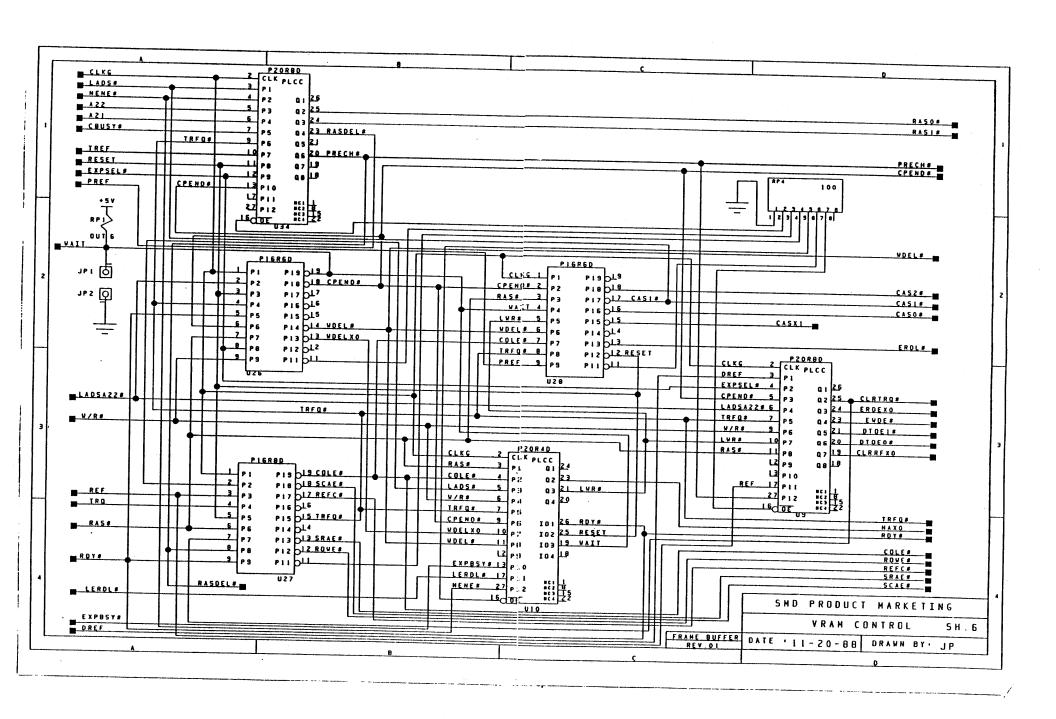

| 6.5.1   | VRAM control                         | 6.5          |

| 6.5.1.1 | Speed mode                           | 6.6          |

| 6.5.1.2 | Processor-initiated cycles           | 6.7          |

| 6.5.1.3 | Refresh/RAM-to-SAM transfer cycles   | 6.9          |

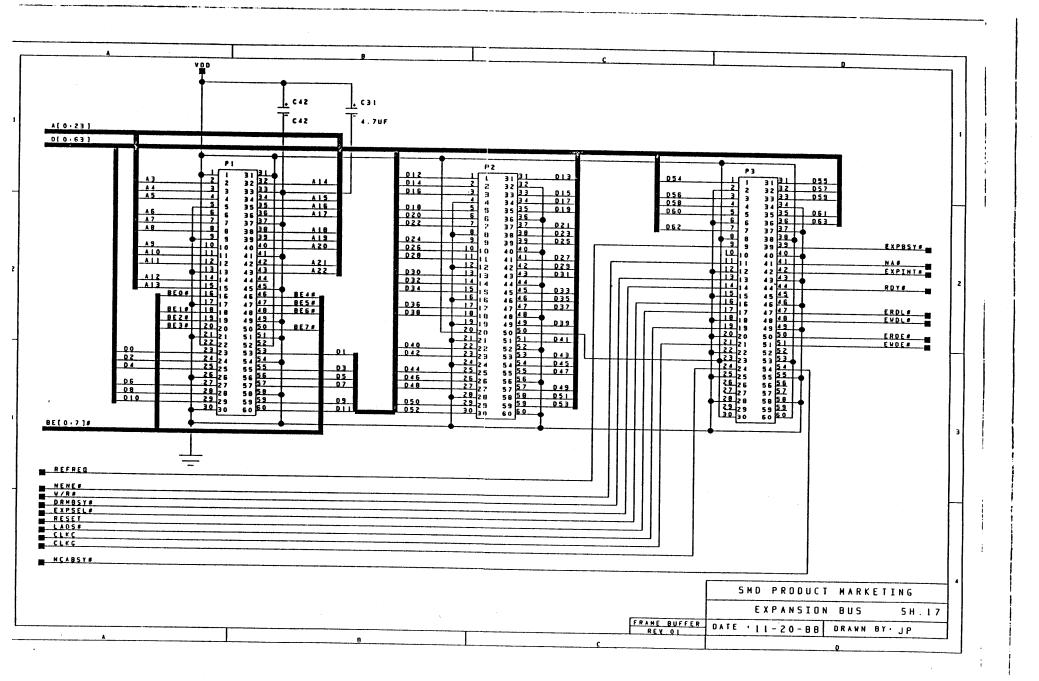

| 6.5.2   | Expansion bus interface              | 6.10         |

| 6.5.2.1 | Expansion select                     | 6.10         |

| 6.5.2.2 | Data transceiver/latch sharing.      | 6.10         |

| 6.5.3   | CRT timing logic.                    | 6.10         |

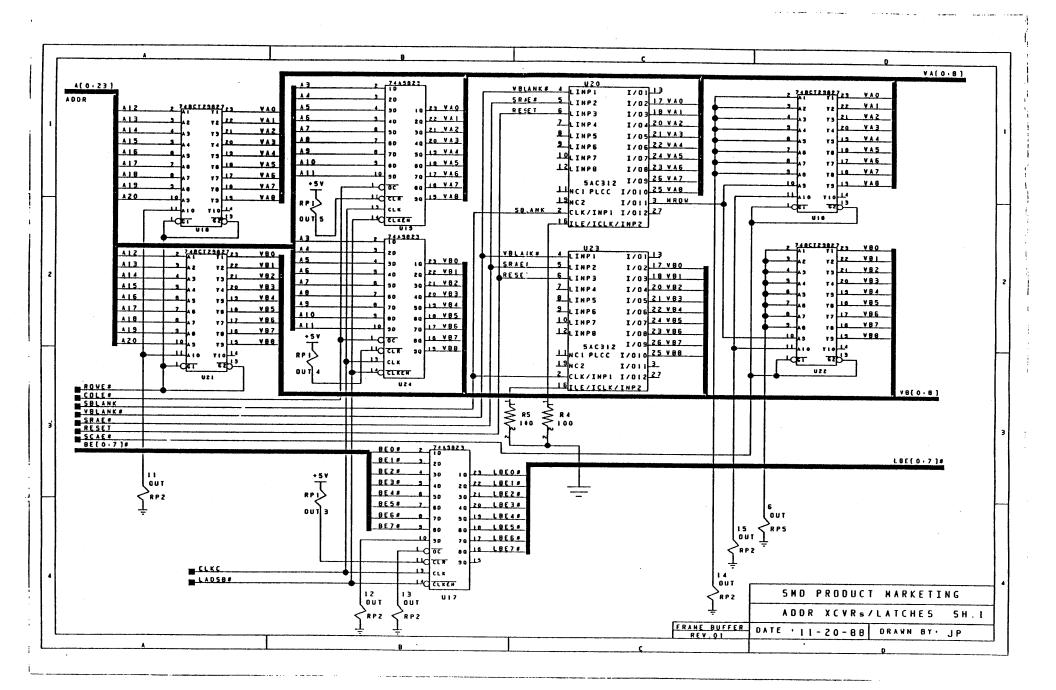

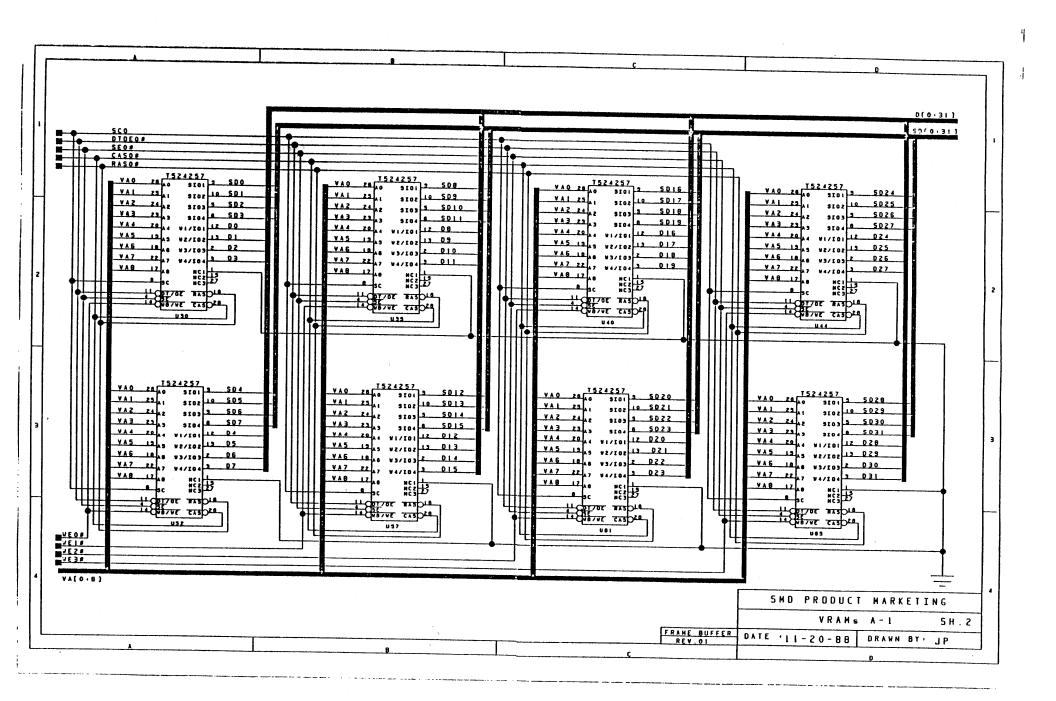

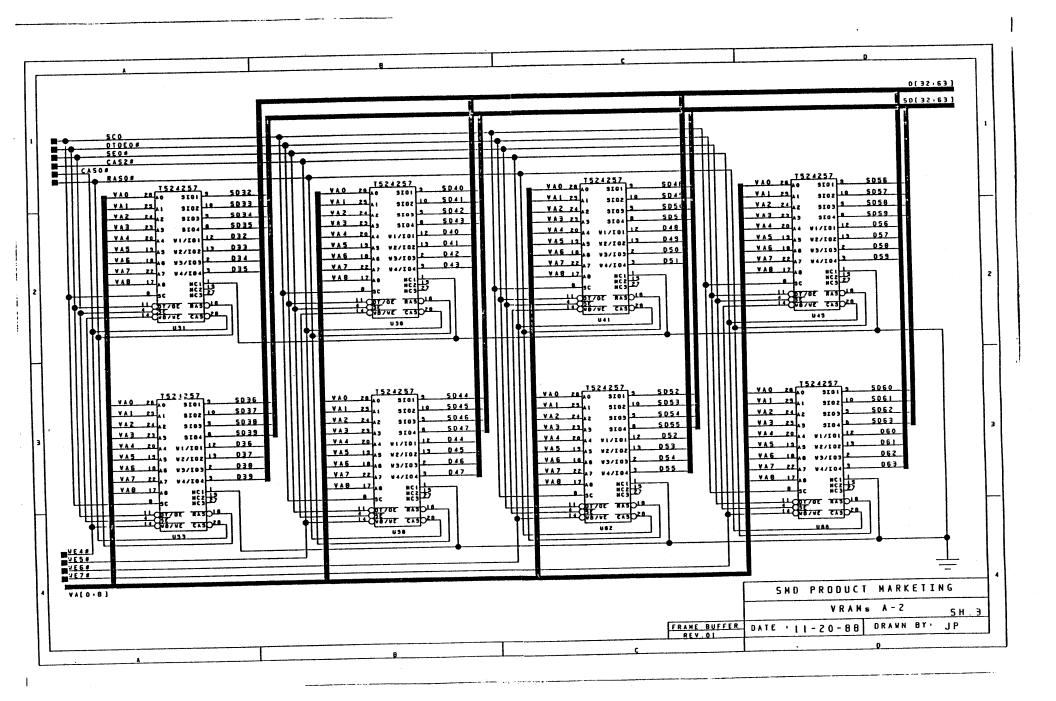

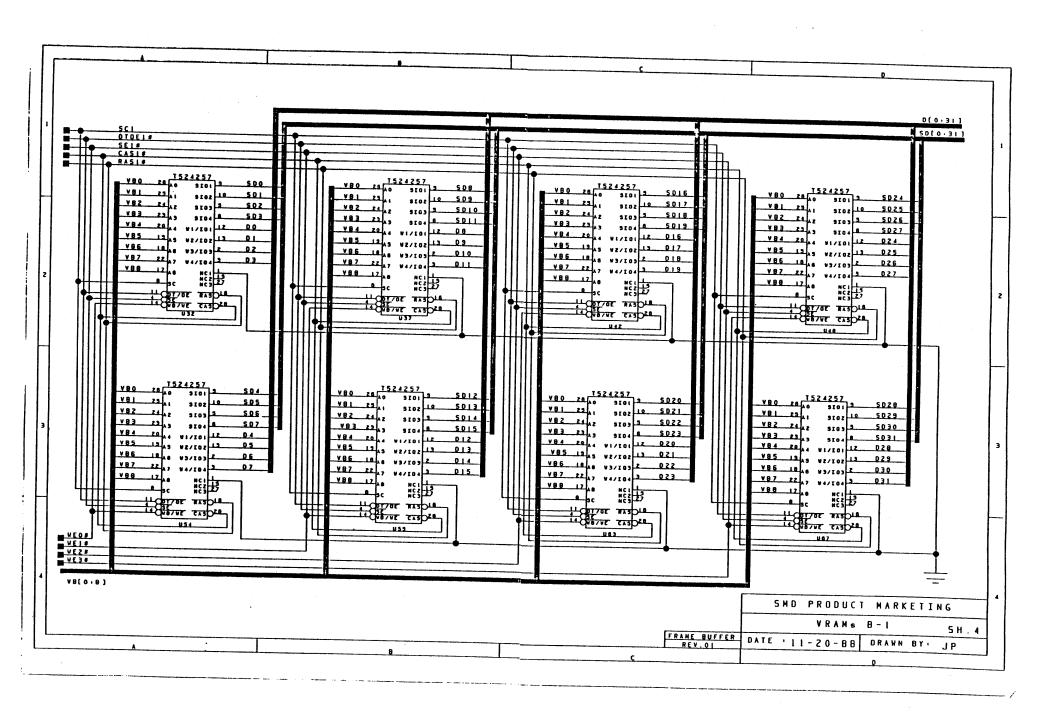

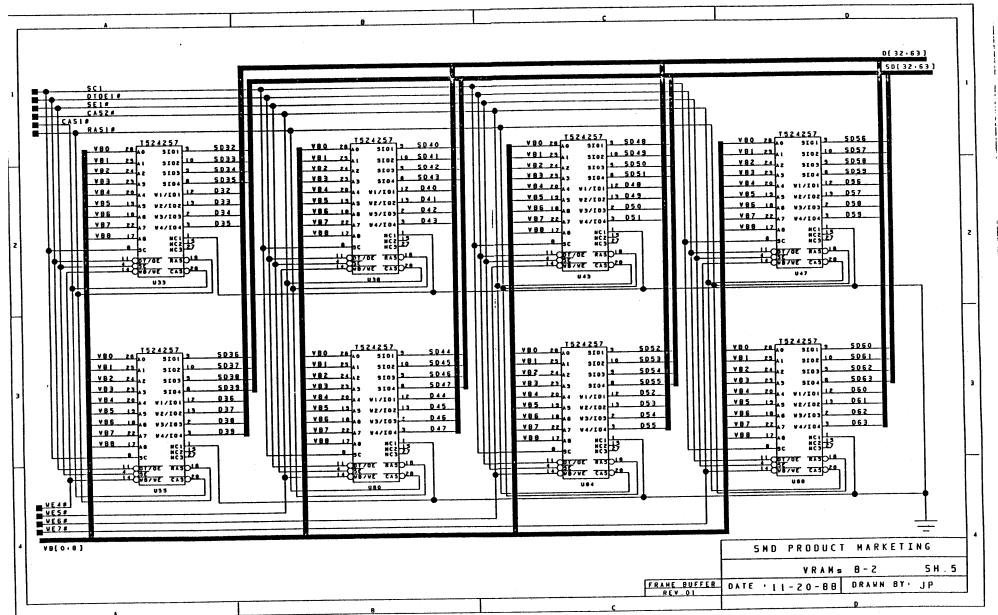

| 6.6     | Appendix                             | 6.14         |

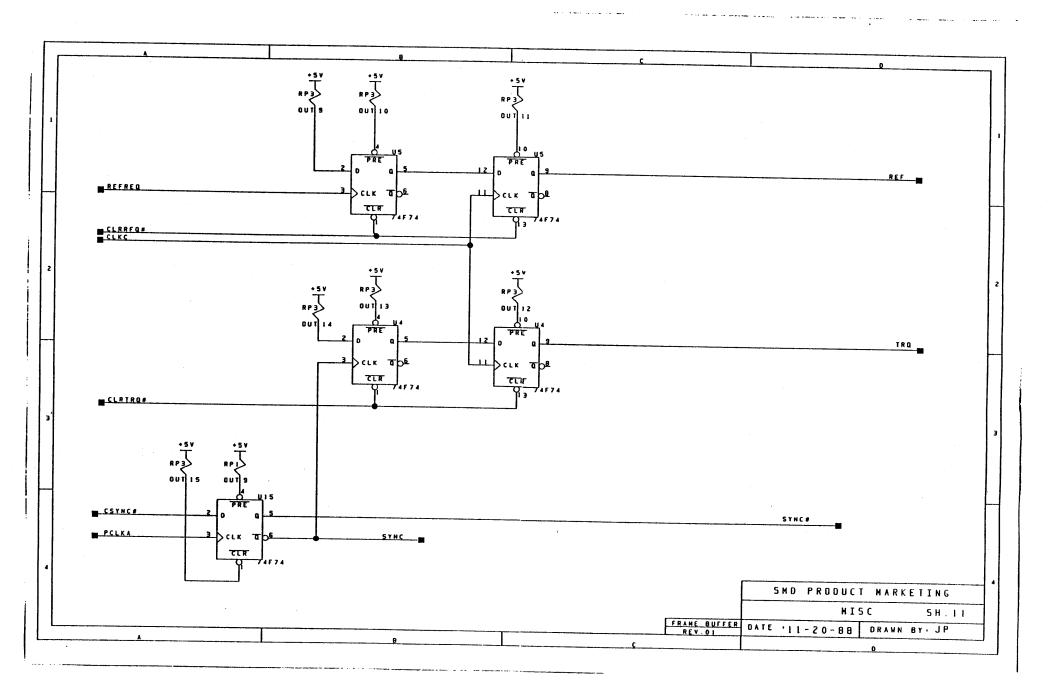

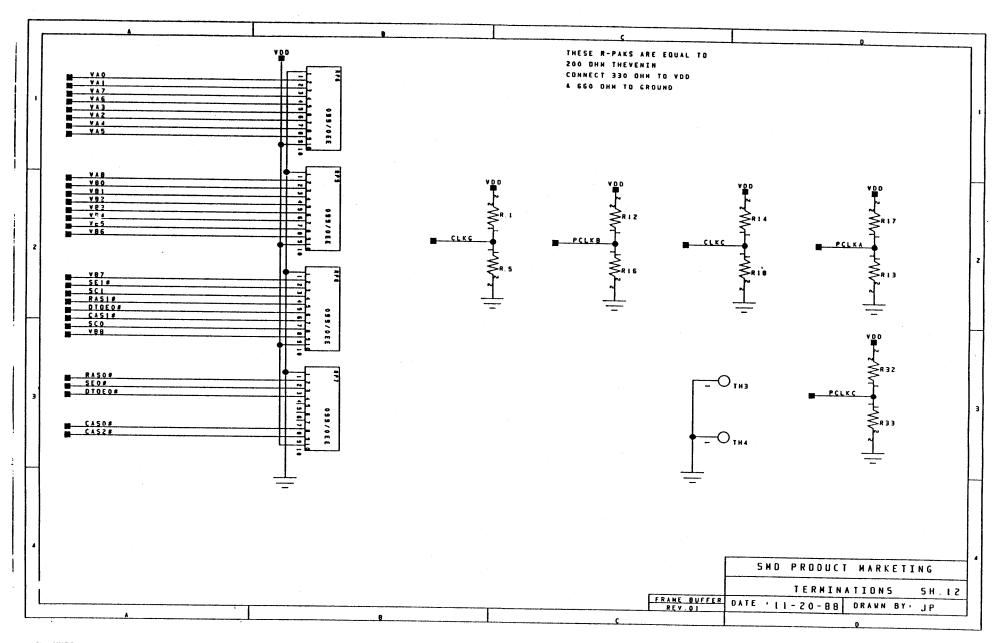

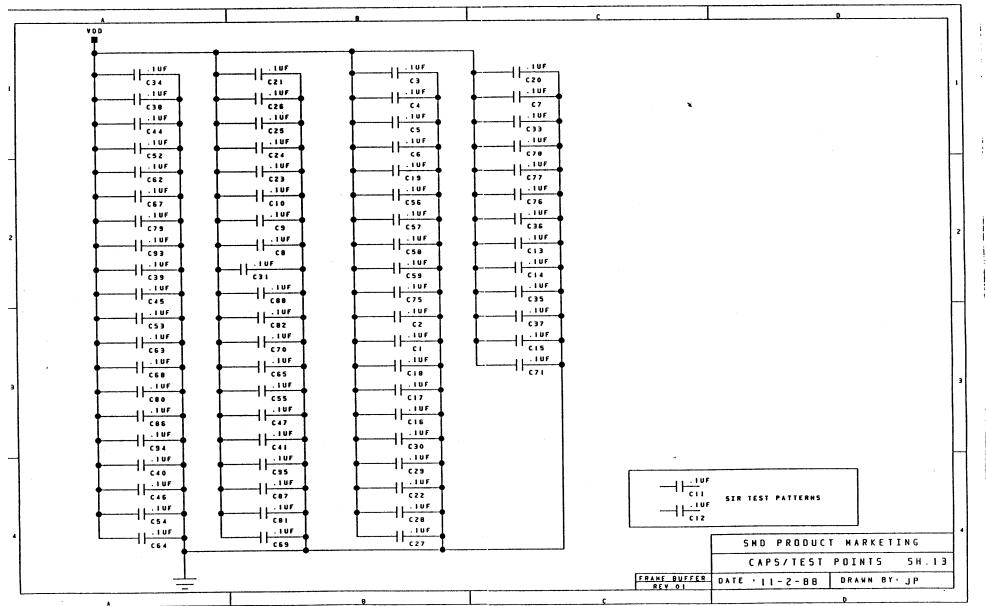

| 6.6.1   | Schematics Description               | 6.14         |

| CHAPTE  | R 7                                  |              |

| •       |                                      |              |

| MULTIBU | IS II AND 1860 MICROPROCESSOR        |              |

| 7.1     | i860 microprocessor CPU board        | 7 1          |

| 7.2     | Multibus II standard                 | . 7.1<br>7.1 |

| 7.2.1   | Parallel system bus (iPSB)           | 7.3          |

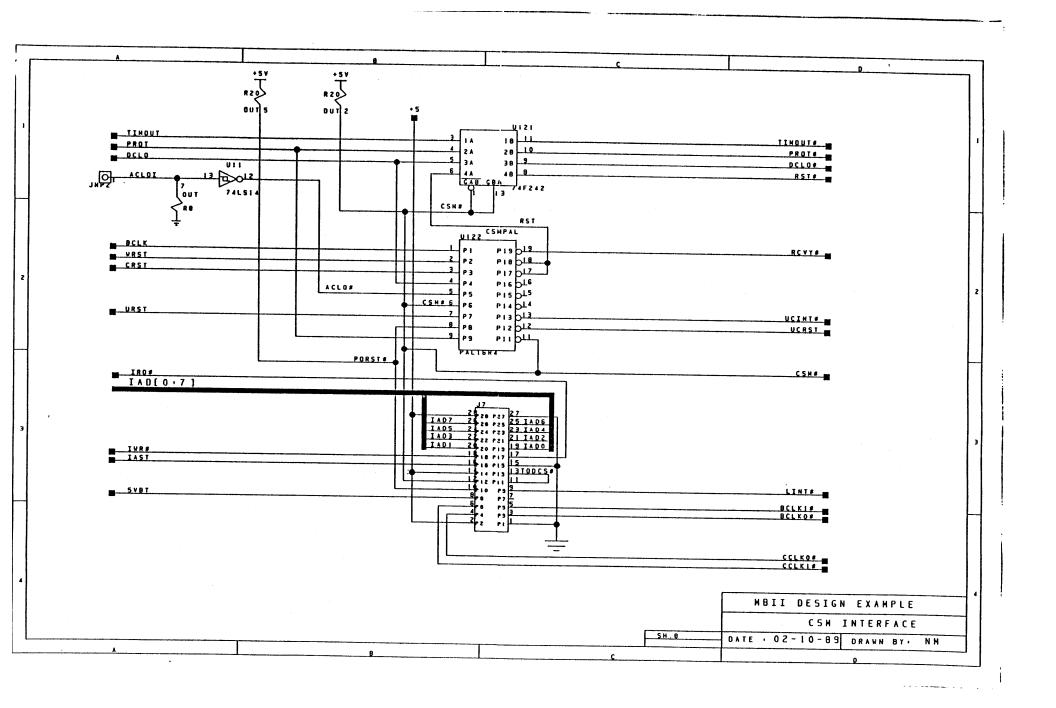

| 7.2.2   | Message passing coprocessor          | 7.6<br>7.6   |

| 7.2.2.1 | MPC interface to iPSB                | 7.6          |

| 7.2.2.2 | MPC local bus interface              | 7.7          |

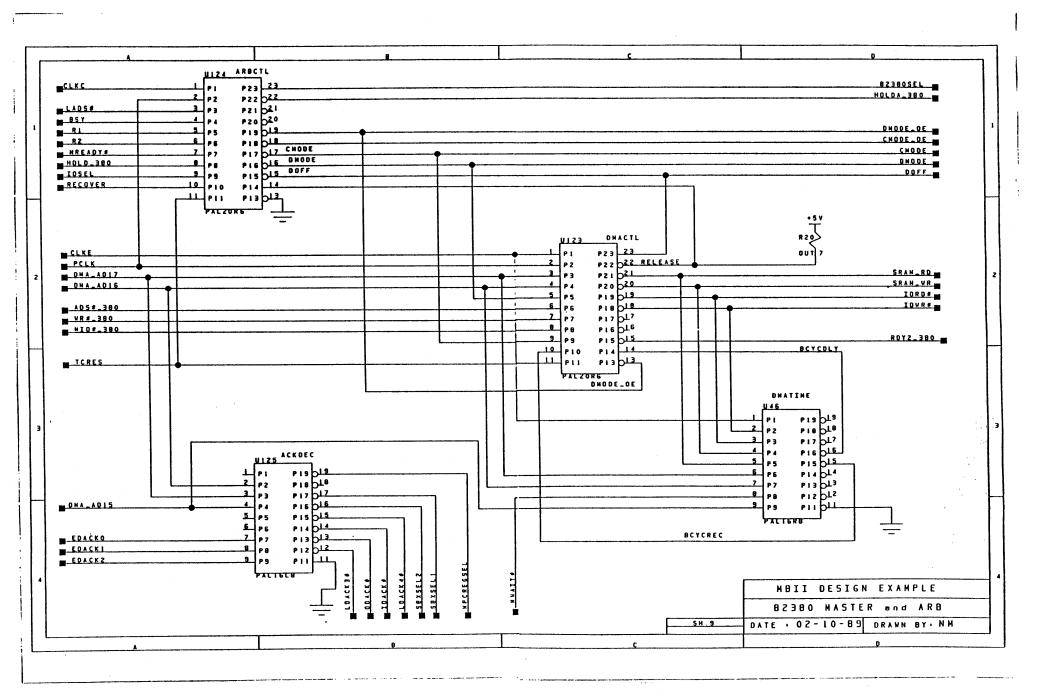

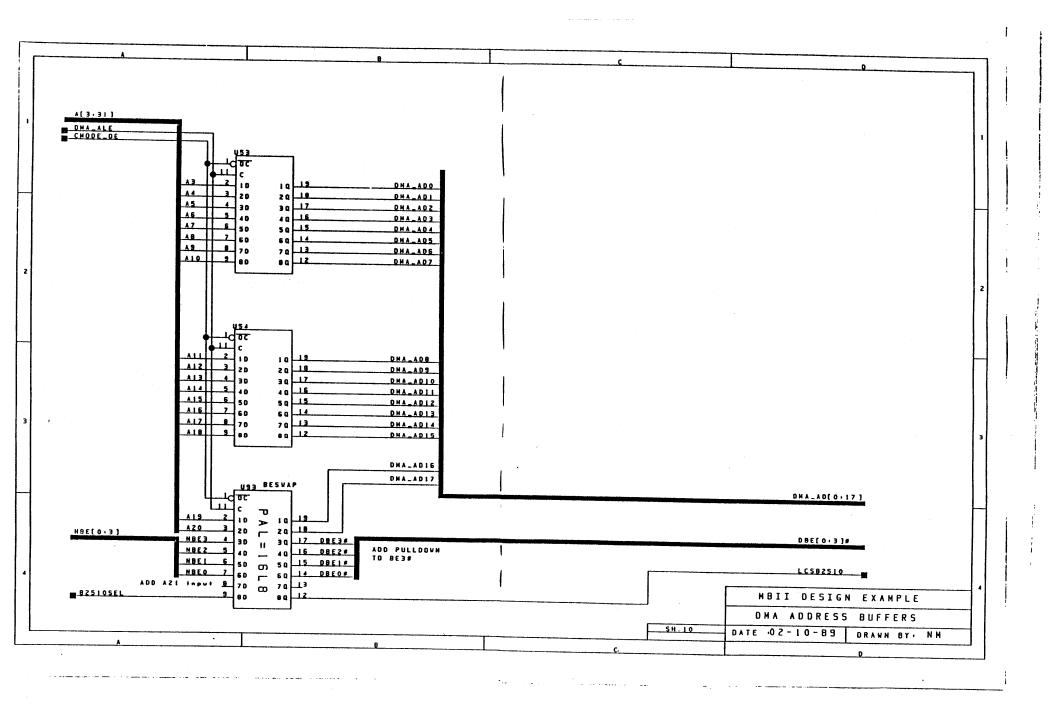

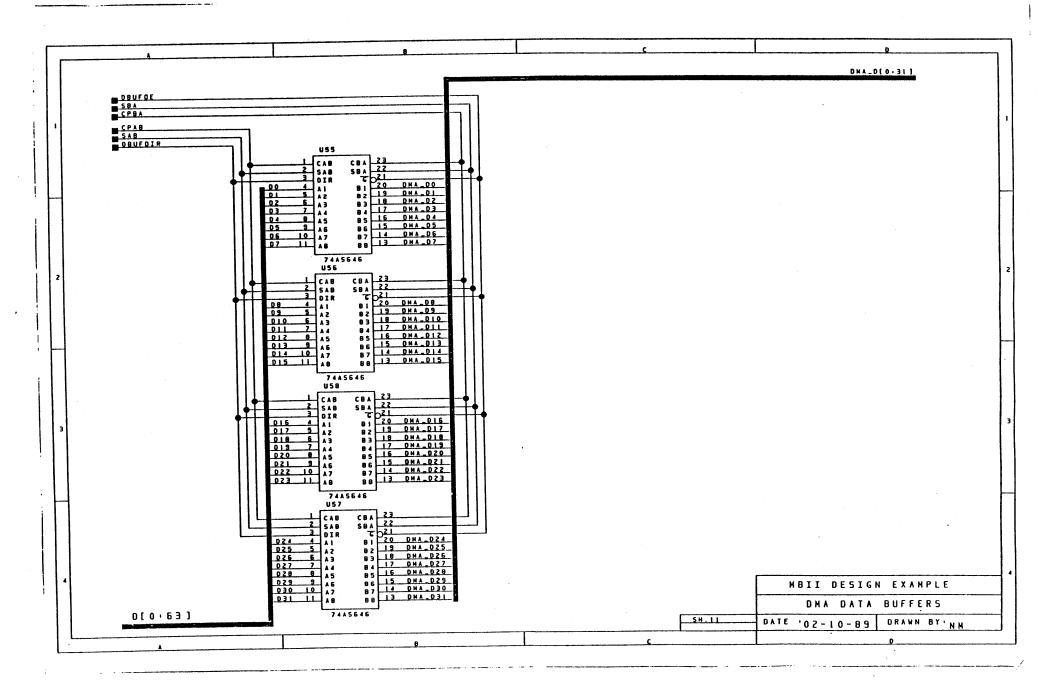

| 7.2.2.3 | MPC DMA interface                    | 7.8          |

| 7.3     | i860 Microprocessor bus interface    | 7.8          |

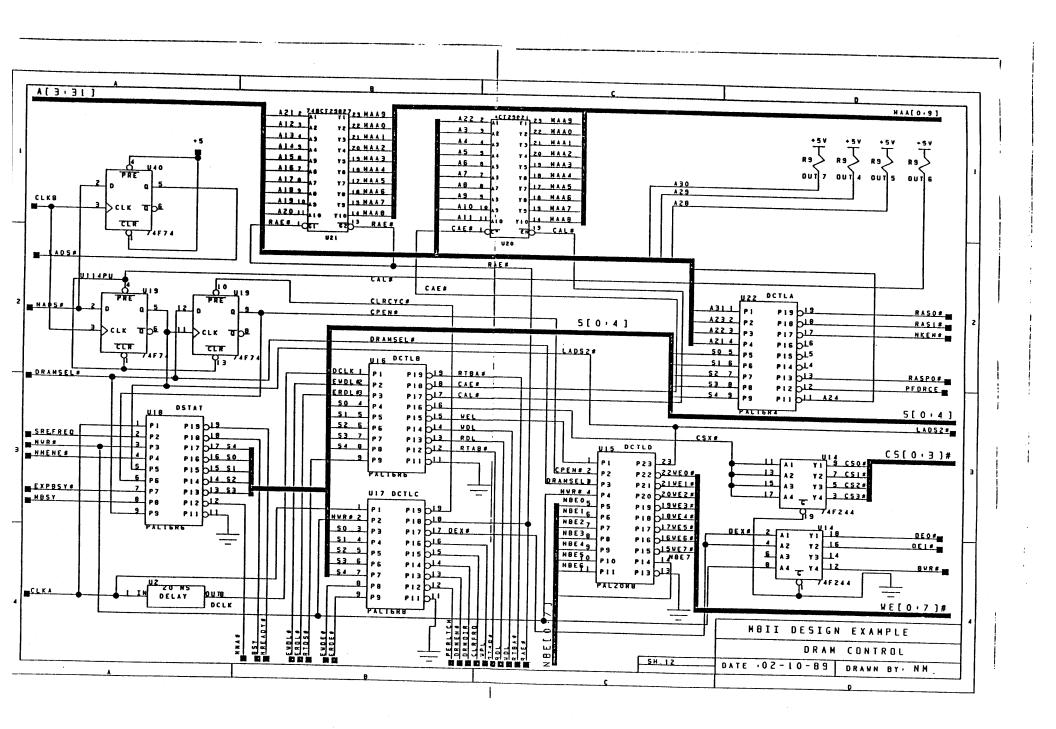

| 7.4     | DRAM system                          | 7.9          |

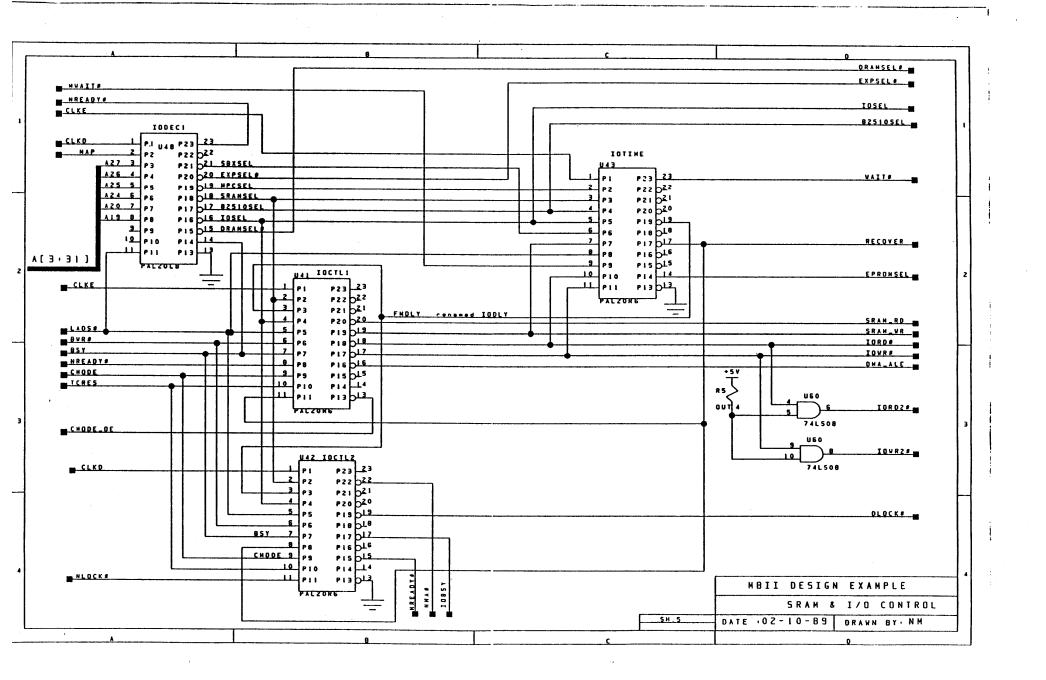

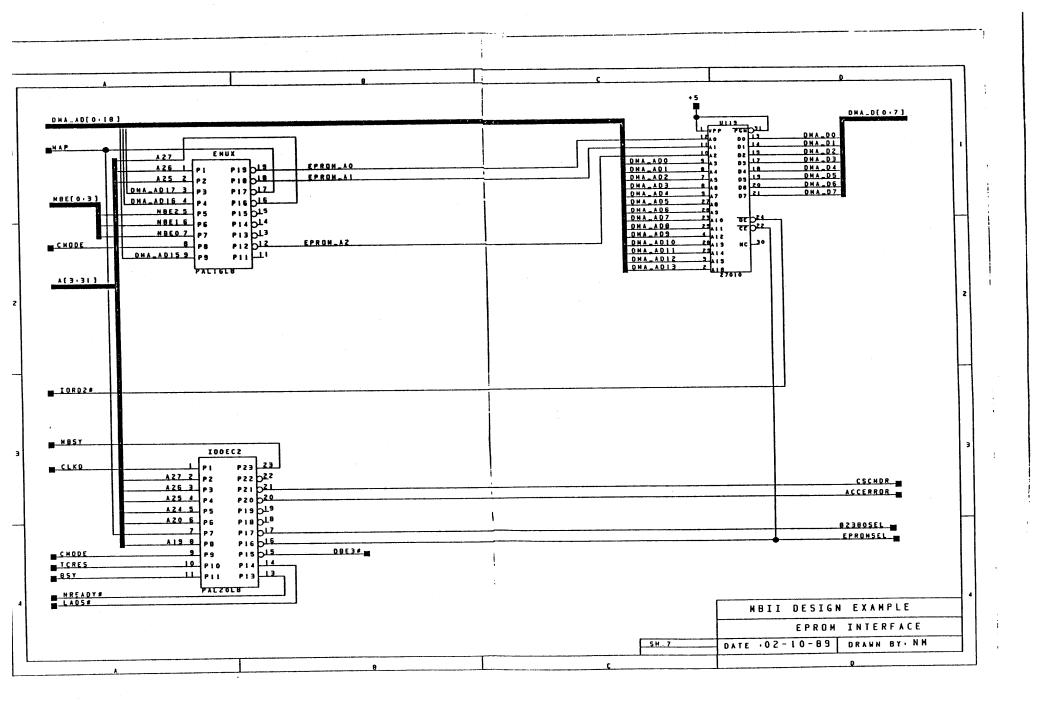

| 7.5     | Local I/O system                     | 7.9          |

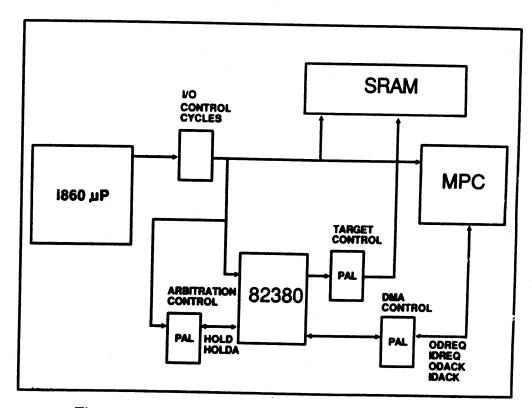

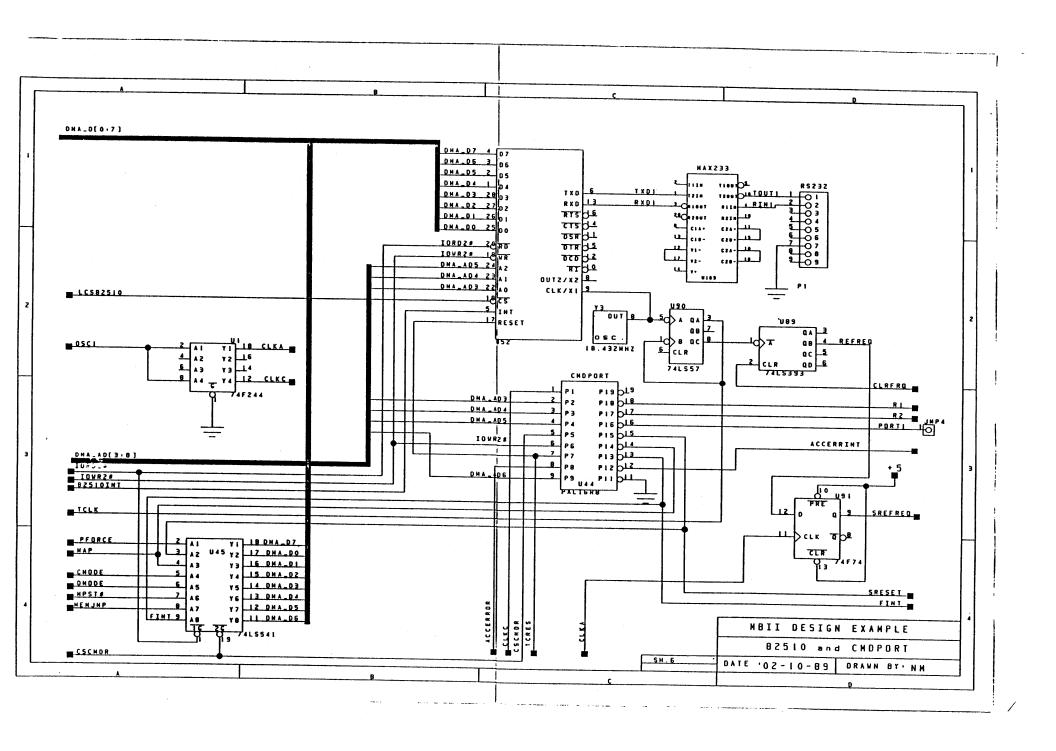

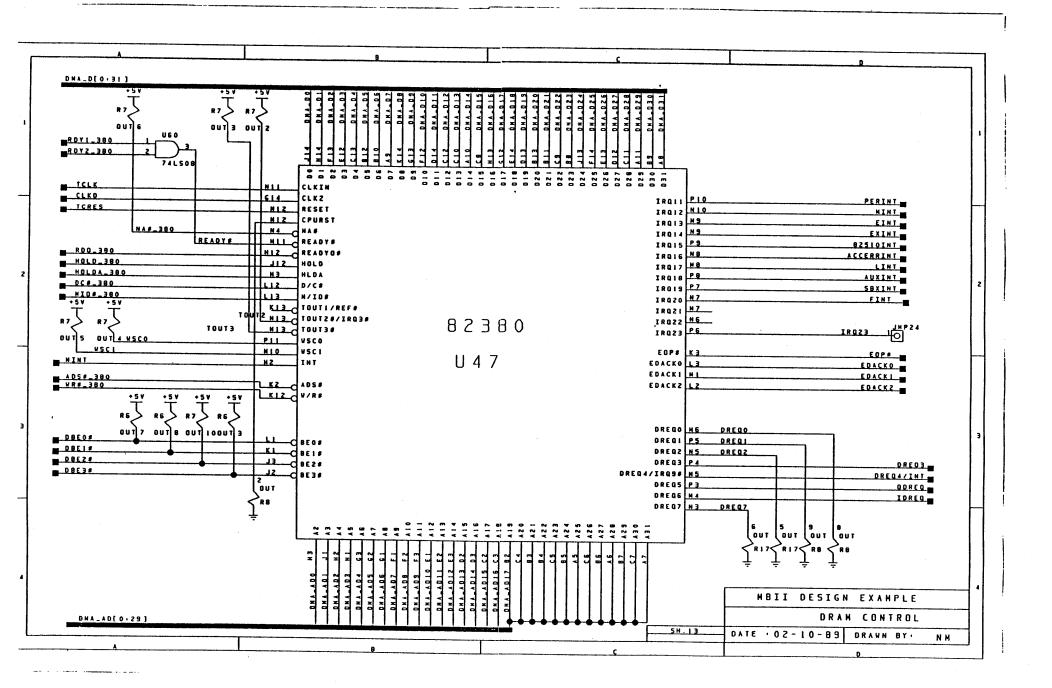

| 7.5.1   | 82380 integrated systems peripheral  | 7.9          |

| 7.5.2   | SBX connector                        | 7.10         |

| 7.6     | DMA control and SRAM message system  | . 7.10       |

| 7.6.1   | DMA channels                         | 7.11         |

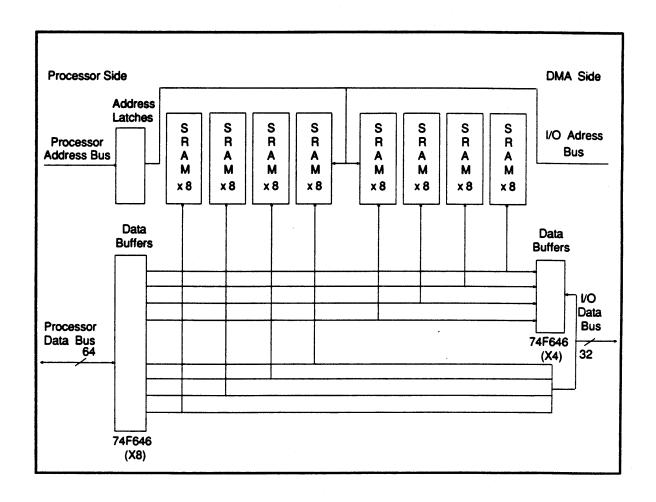

| 7.6.2   | SRAM message area                    | 7.13         |

| 7.7     | Expansion connector                  | 7.16         |

| 7.7.1   | Memory expansion                     | 7.16         |

| 7.7.2   | Intelligent expansion                | 7.17         |

Appendix A: Schematics of the Graphics frame buffer board

Appendix B: Schematics of the Multibus II design

| FIGURE     | TITLES                                                              | PAGES        |

|------------|---------------------------------------------------------------------|--------------|

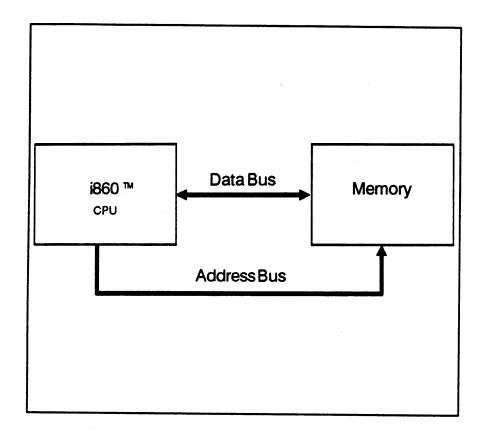

| 1.1        | Stand alone System Configuration                                    | 1-10         |

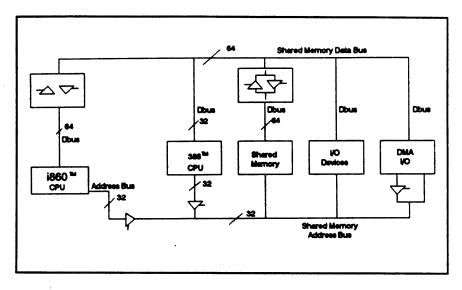

| 1.2        | Shared Memory Configuration                                         | 1-11         |

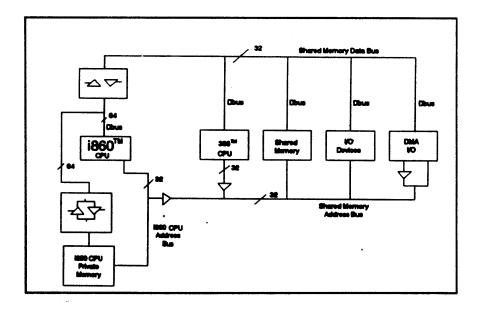

| 1.3<br>2.1 | Combined shared and Private Memory Configuration                    |              |

| 2.1        | Block diagram of i860 microprocessor                                | 2-2          |

| 2.2        | Pipelined Instruction Execution                                     | 2-8          |

| 2.4        | Dual-Operation Data Paths Dual-Instruction Mode                     | 2-11         |

| 2.5        |                                                                     | 2-12         |

| 3.1        | Paging Algorithm Implementation                                     | 2-15         |

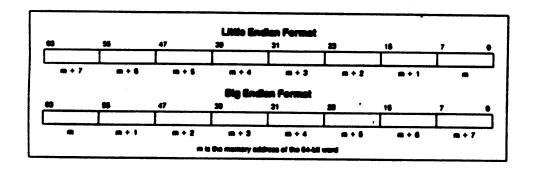

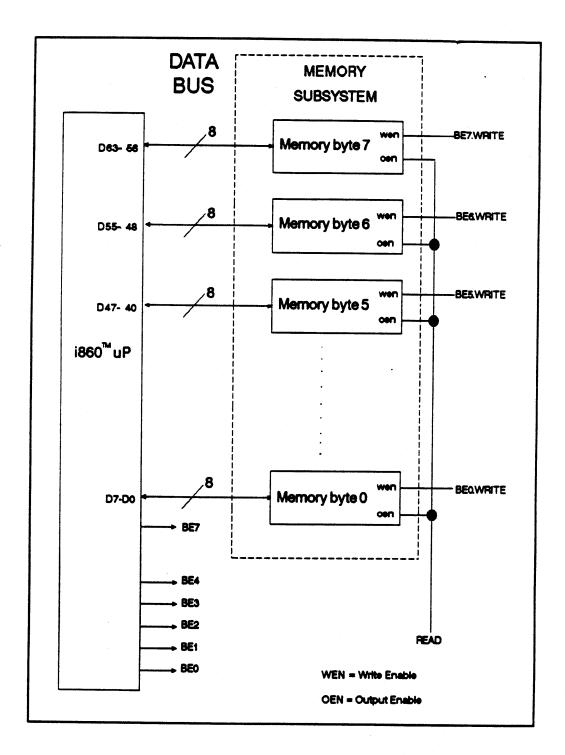

| 3.2        | Little Endian Big Endian Memory Format  Byte Enable Control Signals | 3-6          |

| 3.3        | Non-Pipelined Bus State Machine                                     | 3-8          |

| 3.4        | Fastest Read/Write Cycles                                           | 3-10         |

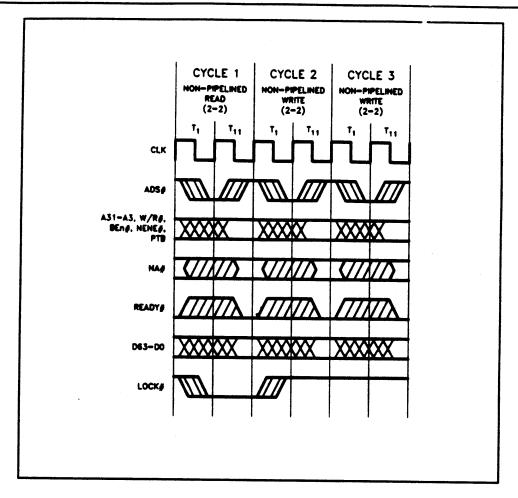

| 3.5        | Fastest Write Cycles                                                | 3-14         |

| 3.6        | Fastest Read/Write Cycles                                           | 3-13         |

| 3.7        | Memory operation pipelining                                         | 3-14         |

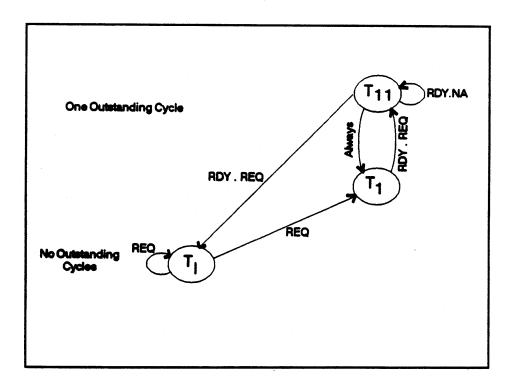

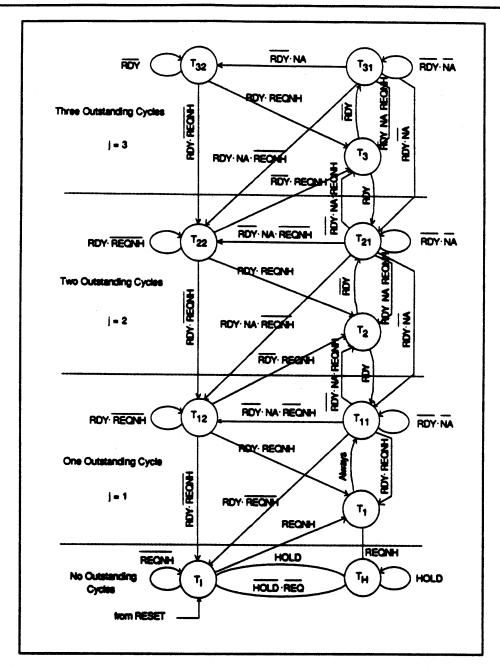

| 3.8        | Pipelined Bus State Machine                                         | 3-16         |

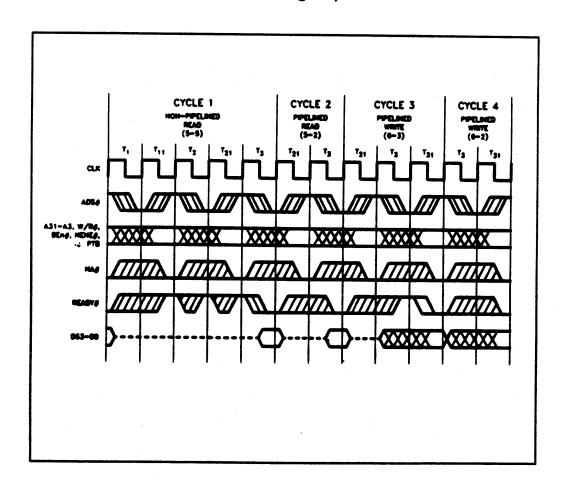

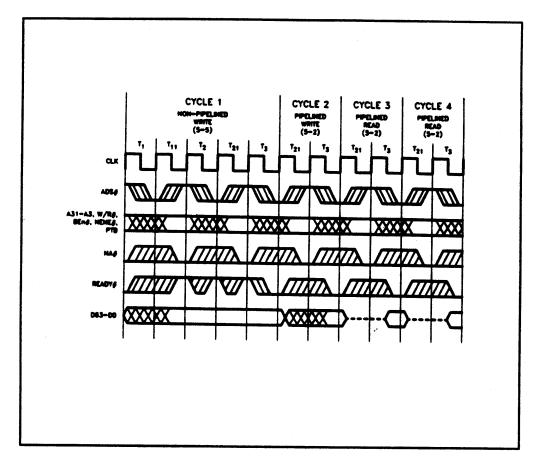

| 3.9        | Pipelined Read Followed by Pipelined Write                          | 3-10         |

| 3.10       | Piplined Write Followed by Pipelined Read                           | 3-20<br>3-21 |

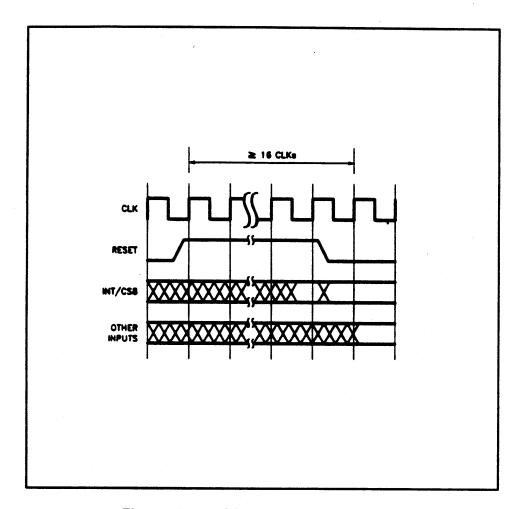

| 3.11       | CS8 and RESET Activity                                              | 3-21         |

| 3.12       | Pipelined Bus State Machine Including Hold State                    | 3-25         |

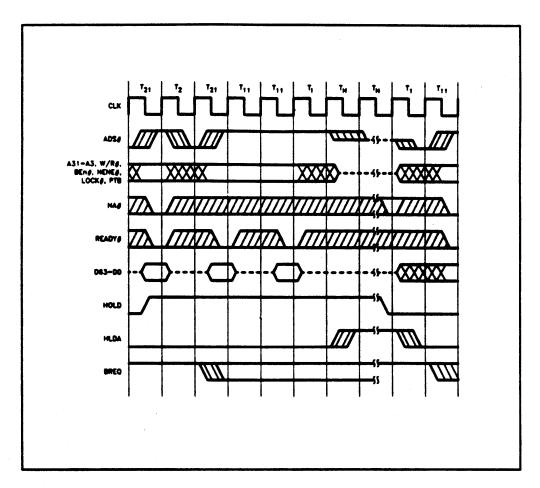

| 3.13       | HOLD, HLDA, and BREQ                                                | 3-25<br>3-27 |

| 3.14       | Locked Cycles                                                       | 3-30         |

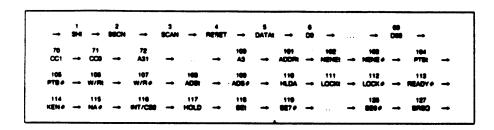

| 3.15       | Boundary Scan Chain                                                 | 3-35         |

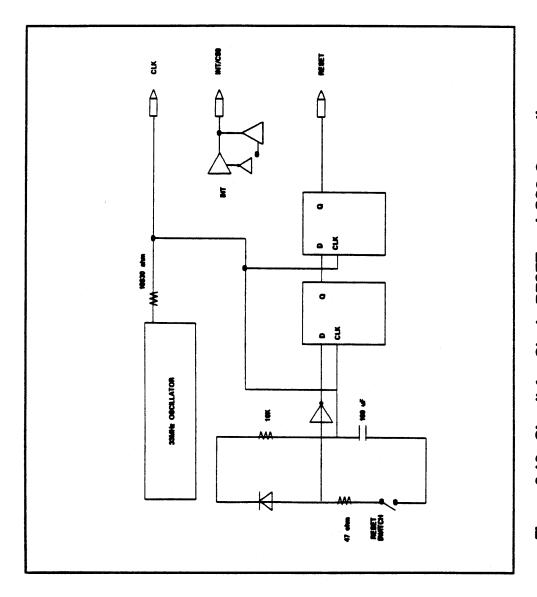

| 3.16       | Circiut for Clock, RESET and CS8 Generation                         | 3-37         |

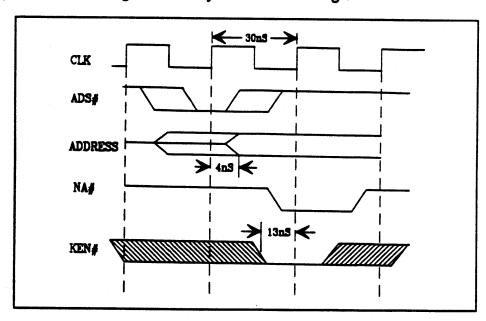

| 4.1        | KEN# Timing                                                         | 4-2          |

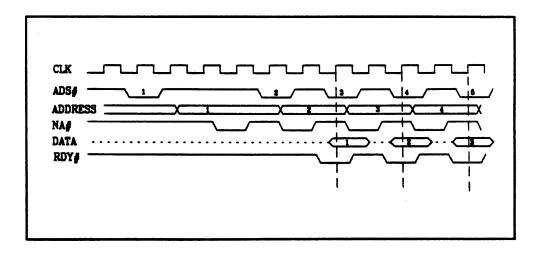

| 4.2        | BUS Pipelining                                                      | 4-3          |

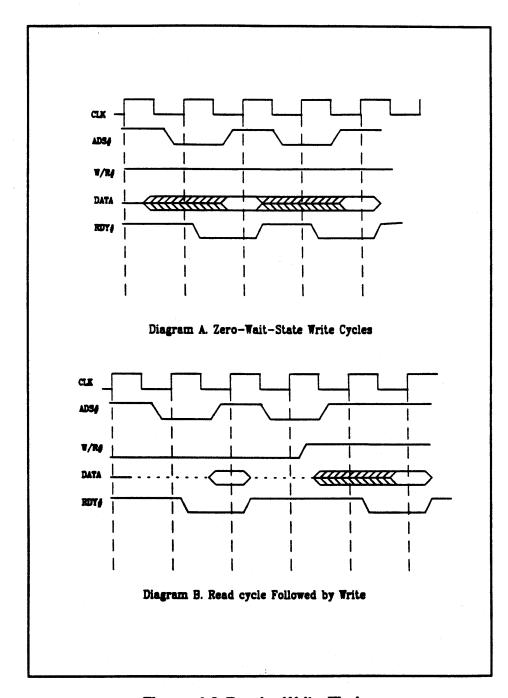

| 4.3        | Read-Write Timing                                                   | 4-5          |

| 4.4        | Maximum Example configuration                                       | 4-8          |

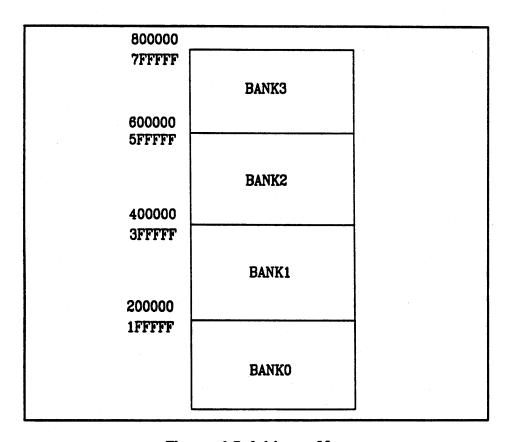

| 4.5        | Address Map                                                         | 4-9          |

| 4.6        | Basic Read Cycle                                                    | 4-13         |

| 4.7        | Pipelined Read Cycles                                               | 4-16         |

| 4.8        | Basic Write Cycles                                                  | 4-18         |

| 4.10       |                                                                     | 4-20         |

| 4.11       | Pipelined Read followed by Write Cycles                             | 4-22         |

| 4.12       | Page Miss Cycle                                                     | 4-23         |

| 4.13       | Balle Block Br                                                      | 4-26         |

| FIGURES | TITLES                                           | PAGES |

|---------|--------------------------------------------------|-------|

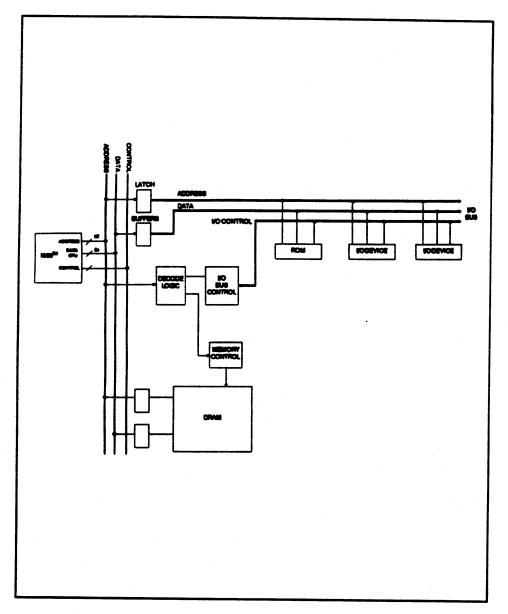

| 5.1     | i860 Microprocessor System                       | 5-2   |

| 5.2     | I/O Microprossor System                          | 5-2   |

| 5.3     | Read Cycle Timings                               | 5-9   |

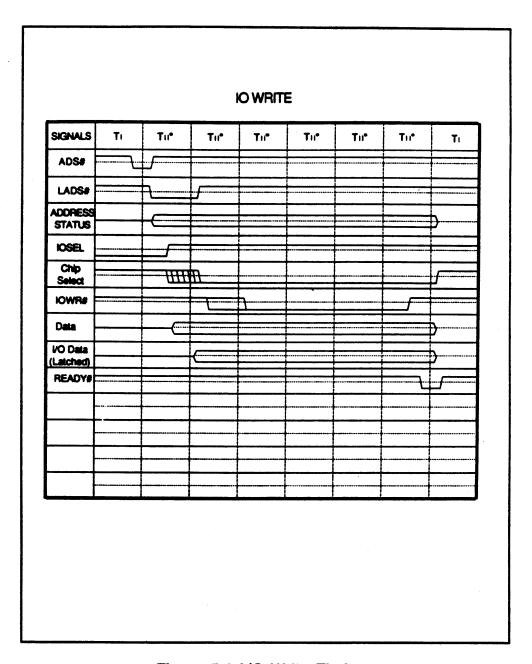

| 5.4     |                                                  | 5-11  |

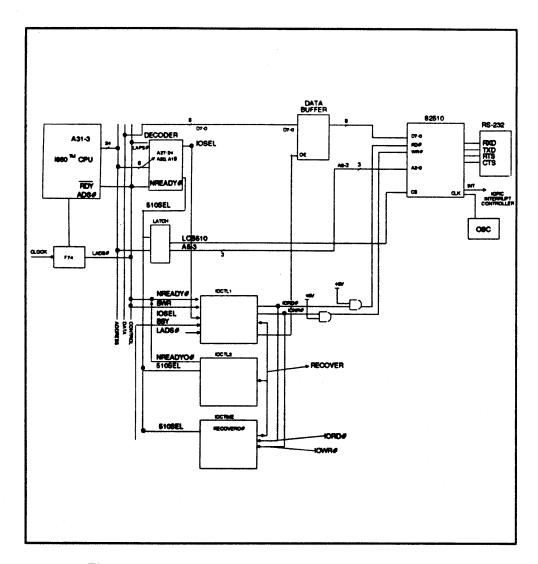

| 5.5     | i860 Processor Interface to 82510                | 5-15  |

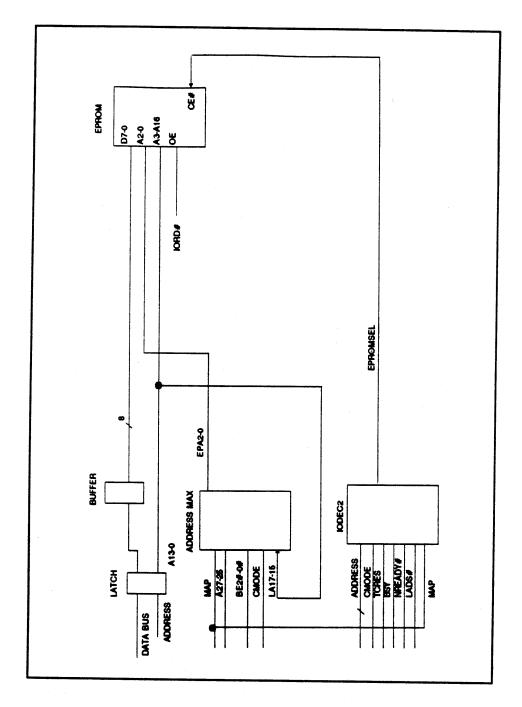

| 5.6     | i860 EPROM Interface                             | 5-18  |

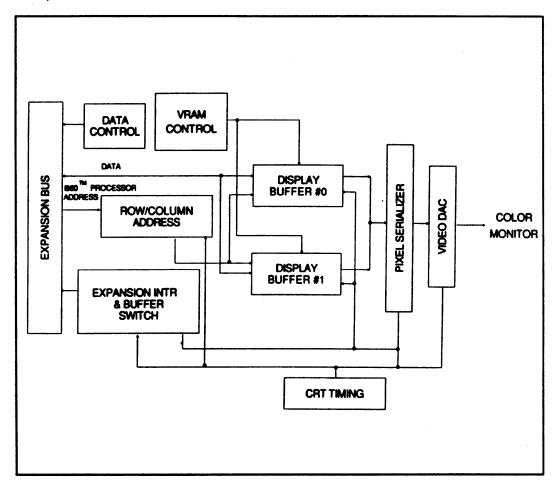

| 6.1     | i860 Processor Based Graphics Frame Buffer Board | 6-3   |

| 6.2     |                                                  | 6-6   |

| 6.3     | Write/Read/Write Operation(0 wait state write)   | 6-7   |

| 6.4     | Refresh RAM to SAM Transfers                     | 6-8   |

| 6.5     | Expansion Space                                  | 6-9   |

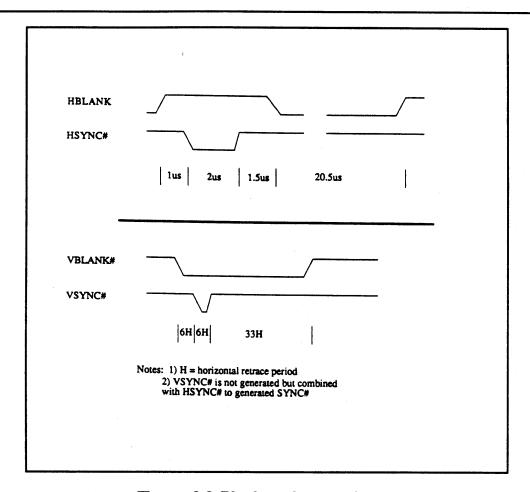

| 6.6     | Blank and Sync Signals                           | 6-11  |

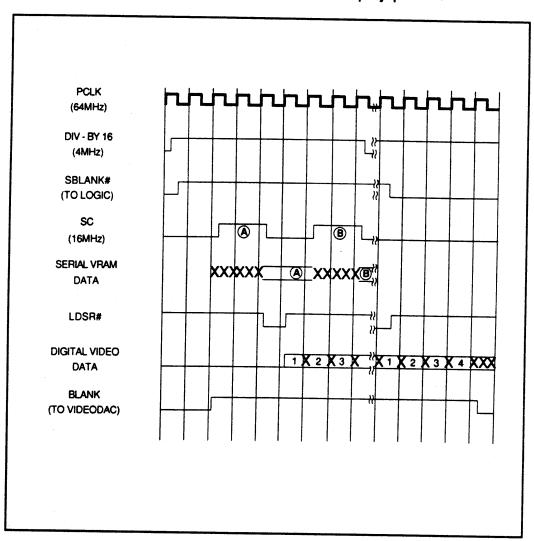

| 6.7     |                                                  | 6-12  |

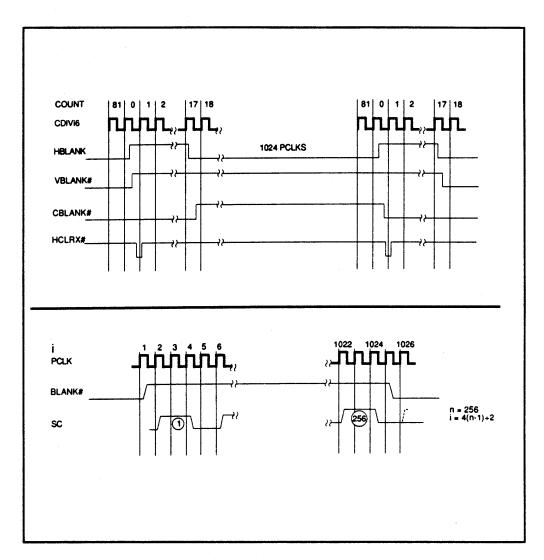

| 6.8     | Blank Signals                                    | 6-13  |

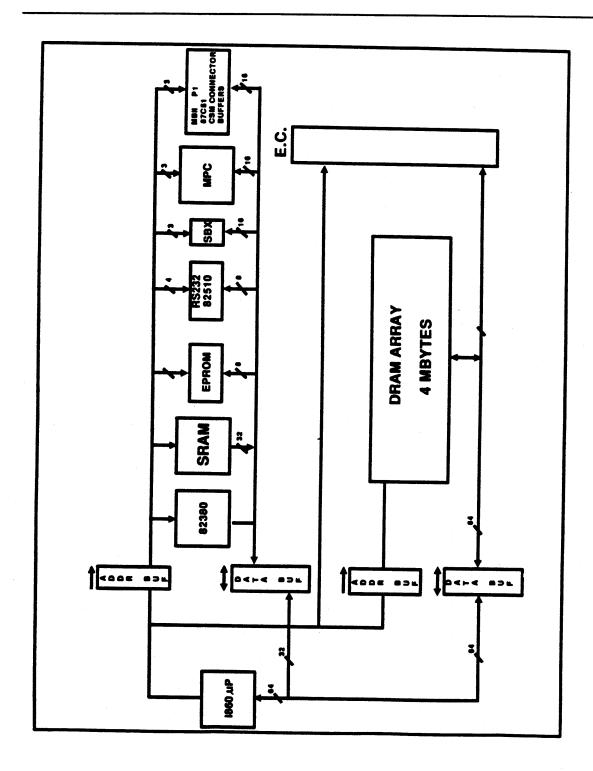

| 7.1     | i860 Microprocessor Based MULTIBUS II Board      | 7-2   |

| 7.2     | PSB Bus Cycle Timing                             | 7-4   |

| 7.3     | MPC Signal Groups                                | 7-5   |

| 7.4     | Fly-by Transger with SRAM Read and I/O Write     | 7-12  |

| 7.5     | SRAM Message Area using 32-bit Bus               | 7-14  |

| 7.6     | SRAM Message Area Using 64-bit Bus               | 7-15  |

| 7.7     | DMA system Arbitration and Control               | 7.16  |

| TABLES  | TITLES                                           | PAGES |

| 3.1     | Pin Summary                                      | 3.5   |

| 3.2     | Write Byte Enable Combination                    | 3.9   |

| 3.3     | Types of Traps                                   | 3.32  |

| 3.4     | Test Mode Selection                              | 3.33  |

| 3.5     | Test Mode Latches                                | 3.34  |

| 3.6     | Output Pin Status During Reset                   | 3.36  |

## **CHAPTER 1**

## INTRODUCTION TO THE 1860™ 64- BIT MICROPROCESSOR

This Chapter provides an overview of the i860<sup>™</sup> microprocessor, its characteristics, possible system configurations and applications.

The i860 microprocessor combines capabilities of supercomputers and 3-D graphics workstations in a single component. Its integer performance makes it ideal for superminicomputers. The i860 microprocessor uses pipelining, parallelism and reduced instruction set computer (RISC) design techniques for high performance. With over one million transistors it integrates an integer unit, a floating-point unit, a graphics unit, memory management and separate data and instruction caches.

The i860 microprocessor executes up to two instructions in parallel and makes extensive use of pipelining. High integration and wide data paths reduce bottlenecks in fetching instructions or data from on-chip caches.

#### 1.1 Processor Characteristics

The i860 microprocessor offers a high level of integration with a million transistor design. This allows a single board design. To complete a processor system all that is needed is four address latches, 8 data tranceivers, clock generator circuit, one EPROM for bootstrapping, a 64-bit wide memory and a few PALs. The i860 microprocessor integrates the following features:

- . Integer Processing Unit

- . On-chip floating-point and graphics unit.

- . On-chip memory management unit

- . 8 Kbyte data cache with 128-bit internal data path

- . 4 Kbyte instruction cache with 64-bit internal data path

The i860 microprocessor uses RISC design techniques. These allow the integer logic to match the speed of the floating-point logic. The integer instruction set controls the entire chip. It can execute any language or portable operating system. RISC design features are:

- . Load and store architecture

- . 32 general purpose 32-bit registers

- . Delayed branching

- . Register scoreboarding

- . Register bypassing

- . Single-cycle loop instruction

- . Branch taken/not-taken instruction fetching optimization

The on-chip graphics and floating-point support of the i860 microprocessor support simulation and 3-D displays. The integer instructions can be used to feed data to the graphics and floating-point hardware. These units are pipelined to produce up to two floating-point results per clock. Some of the features related to the graphics and floating-point unit are:

- . Separate adder and multiplier units.

- . Pipelined/parallel floating-point hardware

- . Graphics instructions and hardware optimized for 3-D

- . 8-, 16- or 32-bit color or black and white pixel data types

- . Single- and double precision IEEE floating-point standard

The i860 microprocessor's high-performance design uses wide buses and pipelined logic to sustain many parallel operations. The level of performance of the i860 microprocessor is difficult to achieve in multichip systems due to the need for many wide buses. The high-performance design applies to the external bus as well, maximizing the possible performance that can be obtained from DRAM memory. Some of the performance related features are:

- . 64-bit design

- . Sustains three operations per clock

- . Dual-instruction mode

- . 33/40 MHz operating frequency

- . Executes 85K Dhrystones at 40 MHz

- . 80 Mflops peak in single-precision

- . 60 Mflops peak in double-precision

- . 320 Mbyte/sec instruction cache bandwidth at 40 MHz

- . 640 Mbyte/sec data cache bandwidth at 40 MHz

- . 160 Mbyte/sec external bus bandwidth at 40 MHz

- . Fast data movement with 128-bit load and store instructions

- . External bus allows up to three pipelined bus cycles.

The i860 microprocessor has virtual memory and multiprocessor support. These support common operating systems like UNIX\*. All memory references are fully restartable in case of virtual memory faults. Full support is provided for synchronizing operation between multiple CPUs. Features related to virtual memory and multiprocessor support are:

- . 32-bit (4 gigabyte) address space with on-chip paging unit

- . Support for demand paging

- . 4 Kbyte page size

- . On-chip 64-entry translation lookaside buffer (TLB)

- . User level/supervisor level protection

- . Bus locking across multiple instructions

- . Cache control

- . Trap mechanism for interrupts and faults

The i860 microprocessor implementation simplifies system design. It has a conventional microprocessor bus. Standard READY# signal is used to allow accesses to slow memories. Software development is assisted by specialized hardware debugging capabilities. Some of the additional implementation features to facilitate hardware design and software development are:

- . 1X clock

- . Optimizations for use of page mode and static mode dynamic RAMs

- . Pin boundary scanning for component or board testing

- . CHMOS-IV\* 1-micron technology/TTL compatible

- . 3 watt power dissipation at 40 Mhz

- . Single 8-bit EPROM can boot system

- . On-chip debugging support

#### 1.2 Processor Overview

This section provides a quick overview of the i860 microprocessor. The processor architecture will be discussed in greater detail in Chapter 2, and the external interface in Chapter 3.

## 1.2.1 Pipelining And Parallelism

Pipelining is a technique which divides tasks into a series of smaller subtasks, which can be performed quickly and concurrently with one another. By means of pipelining, several data items can be acted on simultaneously; although several clock cycles are needed to complete an operation, a new result is produced each clock. Pipelining is used throughout the i860 microprocessor to achieve maximum performance.

Parallelism allows two or more operations to execute simultaneously. The i860 microprocessor supports parallelism allowing multiplication and addition to execute simultaneously within the floating-point unit. Parallelism also allows the integer and floating-point units to execute simultaneously. The i860 microprocessor can execute an integer instruction and two floating-point operations in the same clock to achieve three operations per clock cycle.

## 1.2.1 Instruction Set Architecture

The core unit executes the basic instruction set including arithmetic, logical, shift and program control instructions. The core unit, floating-point unit and graphics unit are all implemented using RISC principles. All instructions execute in only one clock cycle.

The i860 microprocessor uses a load and store architecture. Only load and store instructions can access memory data. All other instructions use only registers to perform operations. Integer and floating-point instructions use two operand registers and a destination register for the result.

The i860 microprocessor employs special branching techniques to avoid interruptions to the flow of data through pipelines. An optimized set of conditional branch and loop instructions minimizes pipeline breaks. Use of a branch-taken or branch-not-taken version of the conditional branch instruction selects whether to pre-fetch the upcoming sequential instruction or the branch target address. Delayed branching is also used to avoid breaks by executing the instruction following the branch.

## 1.2.3 Registers

The i860 microprocessor provides 32 32-bit integer registers for the core unit and another 32 32-bit floating-point registers that are used in the floating-point unit, the graphics unit and for extended arithmetic instructions. The floating-point registers can also be used in pairs as double-precision registers. Quadword memory load instructions use four floating-point registers. Register r0 of the integer registers and f0 and f1 of the floating-point registers are special in that they return a zero value when read and are treated as a null destination when stored into.

## 1.2.4 Address Space

The i860 microprocessor can address up to four gigabytes of memory and memory-mapped I/O locations. Programmers can access memory space as 8-, 16-, 32-, 64- and 128-bit quantities. 8- and 16-bit operands are automatically aligned to the low order bits of a 32-bit register on a load and are moved back to appropriate byte address locations on a store. Only the bytes involved in store operations are enabled for writing. An improperly aligned data access causes a trap.

## 1.2.5 Floating-Point Operations

The floating-point unit supports the ANSI/IEEE 754-1985 Standard for Binary Floating-Point Arithmetic and supports both single- and double-precision operands. Traps are detect all floating-point exceptions. Hardware implements all rounding modes in order to support the standard with minimal overhead. The floating-point unit provides a full complement of operations to permit efficient implementation of all low-level and high-level functions defined by the standard.

The parallel floating-point adder unit and multiplication unit have been designed to efficiently perform matrix manipulation, series expansion and signal processing algorithms. The pipelined, parallel operation in dual-instruction mode of the floating-point unit and integer unit can provide or emulate the capability of vector processing instructions found in supercomputers, but with added flexibility.

A set of floating-point register load instructions provides 32-, 64- and 128-bit operands for the floating-point unit while it operates in dual-instruction mode.

## 1.2.6 Graphics Support

The graphics unit supports instructions for 3-D color or black and white algorithms. 8-,16- or 32-bit pixel formats are supported. It supports efficient implemention of Phong/Gouraud shading operations. A Z-buffer check instruction is provided to detect the closest surface of a 3-D image. The 3-D graphics hardware uses much of the floating-point point hardware.

#### 1.2.7 Caches

Two on-chip caches help to sustain the i860 microprocessor's high performance. The 8 Kbyte data cache is a two-way set-associative memory with a 32-byte line size and a 128-bit data path. It uses a write-back technique on memory write operations. This technique delays the external write operations needed to maintain consistency between the cache and external memory. With this approach, multiple write operations to the same location, do not result in needless multiple bus operations. When write operations to external memory are performed they use two 128-bit wide write buffers which post the write operations and delays them until the memory subsystem is not in use.

The 4 Kbyte instruction cache is also implemented as a two-way set associative memory. It provides a 64-bit wide internal datapath. The instruction cache is read-only; writes to memory do not update the code cache. A separate flush instruction is available to invalidate the contents of code cache, if the need arises.

Since the data and instruction caches map virtual addresses to data, the data and instruction caches can operate in parallel with the translation lookaside buffer (TLB). Data can be obtained in one clock cycle when there is a hit in the cache.

## 1.2.8 Paging Unit

The on-chip paging unit converts 32-bit virtual memory addresses to 32-bit physical addresses. Each page is 4 Kbytes in size. Supervisor and user level read and write memory protection is provided on a per page basis. Supervisor pages can be write-protected to perform copy-on-write operations for supervisor data.

A translation lookaside buffer (TLB) acts as a 64-entry cache for the virtual memory tables. These tables map virtual page addresses to physical page addresses and provide protection rights. The TLB makes memory management more efficient by operating in parallel with the data and instruction caches. The TLB performs instruction and data address translation simultaneously and in one clock cycle. Translation buffer cache misses and updates are handled automatically in hardware.

## 1.2.9 Debugging Support

The i860 microprocessor provides a debug hardware support trap which can be activated when reading, writing or both at an address stored in the data breakpoint register. The address can refer to data inside the caches or off-chip.

#### 1.2.10 External Interface

This section outlines the functions provided by the i860 microprocessor's external interface. These functions are detailed in Chapter 3.

The external interface pin-out consists of a 29-bit address bus, an 8-bit byte enable control bus, a 64-bit data bus, 19 other signals and 48 power and ground pins. The external bus is timed relative to a clock. All outputs are valid before the end of a clock period. All inputs are synchronous to the clock.

## A. Two-Level Bus Pipelining of Local Bus

The i860 microprocessor permits up to two levels of pipelining in external memory operations, providing throughput beyond the cycle or access time of the components used. A two level configuration allows three operations to occur simultaneously and triples memory throughput; while the total cycle time is six clocks, 64 bits of data are transferred every two clocks. Pipelining permits a high-performance memory system while using low-cost DRAMs. Even with a single bank of DRAMs, pipelining allows

overlapping of accesses to the same DRAM page.

## **B.** Bus Arbitration Support

The i860 microprocessor provides three signals to control bus and control line arbitration: the input line HOLD (bus hold request) and the output lines HLDA (hold acknowledge) and BREQ (bus request). HOLD and HOLDA provide a handshake with other processors or an arbitration circuit to allow several processors to share the external buses. The processor can operate out of its internal cache for periods of time and uses the BREQ signal to indicate that it is waiting to use the external bus.

## C. DRAM Interface Support (Page-Mode and Static Column)

The i860 microprocessor provides support for page mode and static column DRAMs. These provide faster memory cycles when sequential reads or writes take place from the same row address in a DRAM component. This occurs often since cache updates typically involve four 64-bit sequential read cycles and the write buffers often group together four sequential write cycles.

The i860 microprocessor provides a next near signal (NENE#) to reduce the amount of external circuitry needed to support page mode and static column DRAMs. The signal is asserted when successive current cycles are in the same DRAM page. The size of the DRAM can be programmed.

#### D. Cache Control

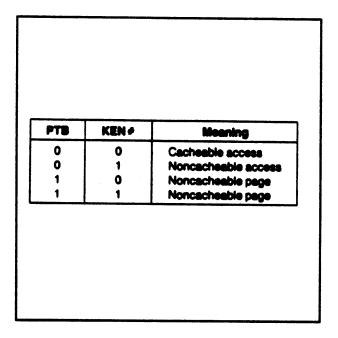

The i860 microprocessor supports memory mapped I/O, external caches and multiple CPUs. All of these require correct use of caching. The cache enable input signal (KEN#) and page table bit output signal (PTB) control and monitor the data and instruction caches. The KEN# signal input is used by external logic to tell the processor when read data should not be cached. This prevents the processor from caching shared memory in a multiprocessor system and alleviates inconsistencies when two or more processors are accessing the same area of memory. All read operations from memory mapped I/O locations must deassert KEN#.

The page table bit (PTB) output signal operates in two modes. In one mode it indicates whether the software has disabled updates to the data or code cache during the current read cycle. In its other mode of operation it indicates whether the software has disabled the use of an external cache for the current cycle. This kind of software control of caching is done on a page by page basis, only when paging operation is enabled. The software controls the use of the cache in order to guarantee the

consistency of shared data in a multiprocessor environment.

## E. Locked Memory Cycles.

The external LOCK# pin indicates that the i860 microprocessor is performing a set of memory cycles that should not be interrupted. The memory subsystem cannot be accessed by other processors while this pin is active. Multiple instructions can be executed while the lock signal is active. Operations like compare and swap are possible. All semaphore operations can be implemented. HOLD is not recognized during locked operations.

# F. Eight-Bit Bus Access For Bootstrapping Operation (CS8)

The INT/CS8 input pin can establish 8-bit code accesses upon hardware reset. This feature allows bootstrapping from an 8-bit external EPROM or ROM device and reduces the number of parts needed to complete a board. Only code accesses are affected in this mode. This mode only works immediately after activation of RESET. A control register allows software to disable this mode, but not to reenable it.

# G. Boundary Scan To Simplify Board Level Testing

The i860 microprocessor allows all the input pins to be serially sampled. Likewise, the state of all the output pins can assume a value set by serial input data. This precludes the need for complex programs that are normally needed to manipulate pins and permit the exercise and test of board logic circuitry with the i860 microprocessor installed.

## 1.2.11 Clock Requirements

The i860 microprocessor uses an external TTL compatible clock that runs at 40 Mhz. This clock synchronizes the internal functional blocks of the processor, and synchronizes the external signals. Most logic connected to the i860 CPU will also use this clock.

# 1.2.12 i860 Microprocessor Packaging And Power Requirements

The i860 microprocessor is available in a 168-pin pin-grid array (PGA) package with 120 signal pins and 48 power and ground pins. All the power and ground pins must be connected. Low-inductance bypass capacitors should be used around the i860 CPU to handle current surges when all the address and data lines change state

simultaneously. Direct current power dissipation when running at 33 Mhz is two watts at normal operation and three watts at peak operation. A heat sink may be used to keep the case temperature within specification depending on airflow.

## 2. System Configuration

The i860 microprocessor is suitable as a central processor in a mainframe computer or engineering workstation. It will usually be configured as a stand-alone processor with private memory and a memory mapped I/O subsystem.

Other configurations employ the i860 microprocessor as an application accelerator. In this case a communications bus will exist between the i860 and the host. This bus should be allow quick data transfers.

The processor may also be used in a multiprocessor system. The i860 CPU may work in a loosely-coupled fashion, communicating through shared memory or through a link of independent memories. The LOCK# signal must be used to guarantee atomic multiple cycle memory accesses.

The i860 microprocessor provides several functions for multiprocessing support. Bus granting logic (HOLD, HOLDA, BREQ) eases the interface with other processors and with DMA. The cache enable/disable logic is used to maintain consistency between internal caches and shared memory. The capability for locked external cycles allow implementation of semaphores for use with shared memory.

## 1.3.1 Private and shared memory configuration

Peak performance for a multiprocessor i860 system requires minimal contention for the use of memory. Typically, this is achieved by providing each i860 microprocessor with its own private memory, along with memory that can be shared.

Multiprocessor systems not requiring peak performance can use shared memory only. This results in a simpler and lower-cost implementation. The memory subsystem can prioritize access to the shared memory between the processors to maximize efficiency.

Figure 1.1 Stand-Alone System Configuration

Figure 1.2 Shared Memory Configuration

Figure 1.3 Combined Shared and Private Memory Configuration

## 1.4. Application Overview

The i860 microprocessor is designed for use in a wide range of applications. The processor's support of demand-paged virtual memory and the IEEE Floating Point Standard makes it especially suitable as a main processing engine for high-performance engineering workstations and mainframe computers and supercomputers.

The i860 power can support computational intensive applications such as electronics or mechanical systems simulations. The power of the hardware 3-D graphics support real-time graphics applications of all tupes.

The i860 microprocessor eliminates the need for special-purpose signal, graphics or floating-point processors. The processor can be used for high-performance embedded controller applications, or as an applications accelerator for existing systems.

\* i860, 386 and 486 are trademarks of Intel Corporation. UNIX is a trademark of AT&T. OS/2 is a trademark of IBM.

|  |  |   | - |  |

|--|--|---|---|--|

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  | , |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

# Internal Architecture

2

## **CHAPTER 2**

## INTERNAL ARCHITECTURE

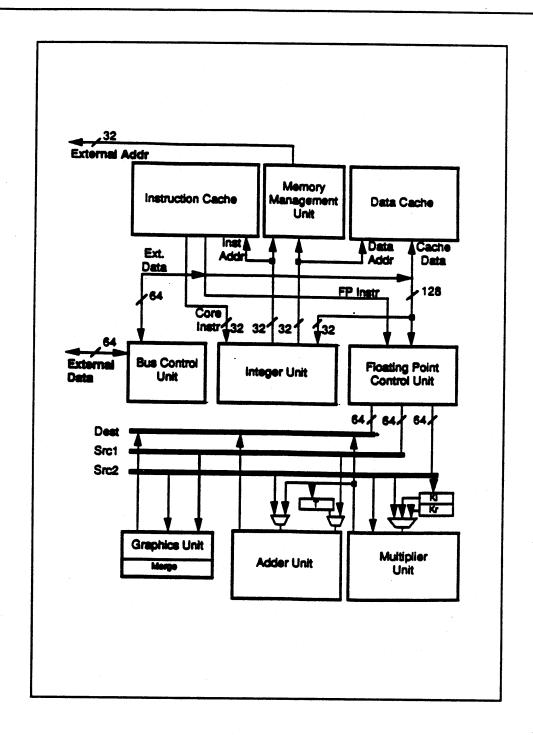

The i860<sup>™</sup> microprocessor incorporates capabilities of a supercomputer and graphics workstation in its architecture. The i860 microprocessor architecture defines the functional aspects of the target computer system, consisting of registers, arithmetic data paths, memory hierarchy, and control logic. The i860 microprocessor architecture obtains its performance by a combination of larger data paths, increased local access to data and instructions (caches and registers), a larger number of important functions included on-chip, and greater levels of pipelining and parallelism. This architecture allows up to three operations per clock to be executed.

The programmer controls the parallelism to manage data flow to and from the floating-point unit. The on-chip cache provides storage for instructions and data. Wide buses can transfer an instruction pair and two double-precicion floating-point operands each clock. A programmer can use the data cache as large bank of vector floating-point registers.

The i860 Microprocessor architecture consists of nine units:

Core Execution Unit

Floating-Point Control Unit

Floating-Point Adder Unit

Floating-Point Multiplier Unit

Paging Unit

Data Cache Unit

Instruction Cache Unit

Bus and Cache Control Unit

**Graphics Unit**

The arrangement of these nine units is shown in Figure 2.1. This chapter describes how these nine units interact to interpret the instructions.

Figure 2.1 Block diagram of i860 microprocessor

#### 2.1 CORE EXECUTION UNIT

The core execution unit is the center of intelligence for the i860 microprocessor and is responsible for its overall operation. It fetches both integer and floating-point instructions. It decodes and executes integer, logical, control-transfer, load/store, exception handling, and cache flushing instructions. It can perform loads and stores to and from the integer register file and the floating-point register file. It also includes a special pixel store instruction that facilitates implementation of the Z-buffer hidden-surface elimination algorithm.

The core execution unit includes a register file containing 32, 32-bit integer registers, a 32-bit ALU, a barrel shifter, two 32-bit processor status registers, a data breakpoint register, a fault instruction register and control logic.

The integer registers, labeled r0 through r31, are accessible by arithmetic operations and load/store instructions. These registers are used for address computation and scalar integer computations. All the registers can be read and written except r0, which always reads a value of zero. Writes to r0 are ignored. r0 works in combination with a number of instructions to modify and extend their function. For example, to check if a register contains a zero, the or instruction can be used with the other source operand and destination as r0. The register bank remains unmodified as a result, and the condition code CC indicates if the given register contains a zero.

The processor status register (PSR) and extended processor status register (EPSR) are 32-bit read/write registers which contain various information on the status of the current process. They provide information such as condition code bit status, loop condition code, interrupt control and status, trap flags, data breakpoint control, pixel information, processor identification, etc. Refer to the i860 microprocessor Programmer's Reference Manual for more information.

The extended processor status register (EPSR) is a 32-bit read/write register which contains additional state information beyond what is contained in the PSR. This information includes the processor type (value of one for the i860 Microprocessor), step number to distinguish among different revisions, data cache size field, and five flags: the overflow flag, big-endian mode bit, page table bit Mode, write-protect mode bit, and the interlock bit. Refer to the i860 Microprocessor Programmer's Reference Manual for more information.

The data breakpoint register (DB) contains a breakpoint address. It is used to generate traps when loads or stores are made from or to this address, and is thus useful for debugging. Refer to the i860 Microprocessor Programmer's Reference Manual for details.

The core execution unit contains logic for handling exceptions and external interrupts. When an exception condition or an external interrupt occurs, the processor transfers control to the trap handler. Refer to i860 Microprocessor Programmer's Reference Manual for details.

The 32-bit instructions are fetched into the core execution unit from the instruction cache given the next instruction's address provided by the core execution unit. If this address location is not in the cache (a cache miss), the 32-bit instruction is fed to the core execution unit from the external memory, while the corresponding Instruction Cache block is simultaneously filled.

The core execution unit is designed according to RISC principles, as explained in Chapter 1. It uses a pipelined organization that maximizes performance. The instructions are made purposefully simple using a Load/Store architecture. Emphasis is placed on minimizing circuit delays and economizing chip space in order to include the other processing units that are essential to overall high performance -- the floating-point unit, graphics unit, paging unit, caches and register banks. Pipelining is coupled with register bypassing, scoreboarding, and delayed branching to further enhance performance.

Execution pipelining is transparent for arithmetic, logic and shift instructions. These instructions appear to operate in one clock cycle with the destination register already loaded by the time the next instruction begins executing. However, this is not actually the case. Due to the delay required in storing to and reading from a register, the processor detects if the last instruction's destination is used as an operand in the current instruction. If it is, it bypasses the register bank and operand value directly from the bus (in parallel with the previous destination register). This technique is known as register bypassing, and is invisible to the programmer.

Unlike arithmetic and logic operations, load operations require a minimum of two clock cycles to provide a valid result for the destination register. Because of the extra delay needed to get the valid result, the code should be arranged so that a reference to a register does not directly follow a load instruction to that same register. For this case the instruction directly following the load can execute while the load operation is finishing. However, when the register operand of the current instruction is the same as the destination of an immediately preceding load, the hardware automatically detects this and freezes the clock until the data is present. This technique is called scoreboarding.

The use of register bypassing and scoreboarding allows load and store instructions to be executed at an effective rate of one instruction per clock cycle, assuming the data and instructions are found in their respective caches. When a cache miss occurs, the hardware will automatically resolve potential problems by freezing execution if the data is needed.

Branch instructions can also have the effect of locking the pipeline for one or more clock cycles. To avoid this waste, several techniques are used as described below.

An extra clock cycle is always required on a successful branch in order to refill the instruction pipeline. The i860 microprocessor uses a technique called delayed branching, in which the instruction following the branch is always executed. The system software or the programmer is responsible for reorganizing the program to take advantage of this technique. If no useful instruction can be found for the instruction following the branch, then an operation which does nothing must be used, (e.g. or r0, r0, r0).

A common cause of pipeline breaks is the prefetching of the wrong address on a conditional branch. To avoid this, the i860 \*\* Microprocessor provides an optimized set of conditional branch and loop instructions. Conditional branch instructions come in two flavors -- one that prefetches the next sequential instruction, and one that prefetches the branch target address. The compiler or assembler programmer is responsible for using the most desirable flavor of the instruction. Conditional branches at the end of loops, for instance, are usually selected to prefetch the branch destination since code within a loop is executed more often than the code that exits from the loop.

By using the above techniques, it is possible to execute core unit instructions at the peak rate of one per clock quite consistently, thus providing a rate of 40 MIPs (40 MHz clock) of native integer operation performance.

The core unit can operate in parallel with the floating point unit. This operation is known as dual instruction mode and is explained in detail in Section 2.2.6.

#### 2.2 FLOATING-POINT UNIT

In addition to the core execution unit, which handles integer instructions, another very important unit is the floating-point control unit, which processes floating-point instructions. The pipelined floating-point unit, along with the on-chip cache, enables the 40 MHz i860 microprocessor to achieve a peak execution rate of up to 80 MFLOPs for single-precision and up to 60 MFLOPs for double-precision operations.

The floating-point unit consists of: the floating-point register bank, floating-point adder, floating-point multiplier, floating-point status register and floating-point control unit.

Floating-point data types, floating-point instructions, and exception handling all support the IEEE Standard for Binary floating-point arithmetic (ANSI/IEEE Std 754-1985) for both single- and double-precision data types. The floating-point status register holds information about the result of the operation. A complete set of traps includes tests for invalid source operands such as NaN (not a number), denormalized numbers, and infinities, as well as tests for errors in the result, such as overflow and underflow. The cause of the traps can be determined by examining the value in the floating-point status register. The floating-point traps permit implementation of the IEEE Standard in a very efficient manner.

Due to the low-level instruction set philosophy of the i860 microprocessor architecture, high-level functions defined by the IEEE Standard, such as square root, SIN, and COS are not implemented directly by the hardware. The facilities of the floating-point unit, however, allow for a very efficient implementation of these functions, that actually outperforms dedicated floating-point processors.

Intel provides an IEEE trap handler program, as well as a software library, that provides i860 microprocessor programs with the full set of functions supported by the IEEE standard.

#### 2.2.1 FLOATING-POINT REGISTER BANK

The floating-point unit is provided with its own register bank. It contains 32 floating-point registers, each 32-bits wide, labeled f0 through f31. The registers can also be accessed in pairs for 64-bit double-precision values or 64-bit integer values. For this purpose, only even registers are used, (e.g. f2, f4, etc.). Load and store instructions also support the transfer of 128-bits worth of data (e.g. two double-precision operands). The registers are used in groups of four for this purpose, (e.g. f4, f8, f12, etc.). Registers f0 and f1 are special in that, when read, they always provide a value of zero, and writing into them has no effect. These registers modify and extend the

function of the floating-point instructions. Two null registers are required in order to provide a 0-operand and void destination when using double-precision operations.

The floating-point register bank (refer to Figure 2.1) allows multiple operations to occur in parallel. It contains two read ports, one write port, and two bidirectional ports. All these ports are 64-bits wide and can be used concurrently.

The two 64-bit source operands provided by the floating-point registers are used as data input to the floating-point multiplier unit (FPMU), the floating-poina Adder unit (FPAU) or the graphics unit. A 64-bit input port to the floating-point registers transfers the result of the operations. The 64-bit integer instructions and graphics instructions also use this register bank for their source and destination operands.

Two 64-bit bi-directional ports between the data cache and the floating-point register bank allow transfers of up to 128 bits. A 64-bit bus can connect either of these two buses to the data bus on the bus cache control unit. This bus allows 64-bit transfers to and from external memory. The transfers are performed by the various floating-point load and store instructions. These transfers are controlled by the core unit and can occur in parallel with the floating-point instructions, as explained in Section 2.2.6.

## 2.2.2 PIPELINED AND SCALAR OPERATIONS

The floating-point unit uses parallelism to increase the rate of operations performed. One type of parallelism used in the floating-point unit is known as "pipelining." A pipelined architecture treats each operation as a series of more primitive operations called stages. These can be executed in parallel. Consider the floating-point adder unit as an example. Let "A" represent the operation of the adder, and let the stages be represented by A[1], A[2] and A[3]. The stages are designed such that the A[i+1] stage for one ADD instruction can execute in parallel with the A[i] stage for the next ADD instruction. Since each A[i] stage can perform its task in a single clock, and three instructions can be in executing in parallel, one Add operation per clock is achieved.

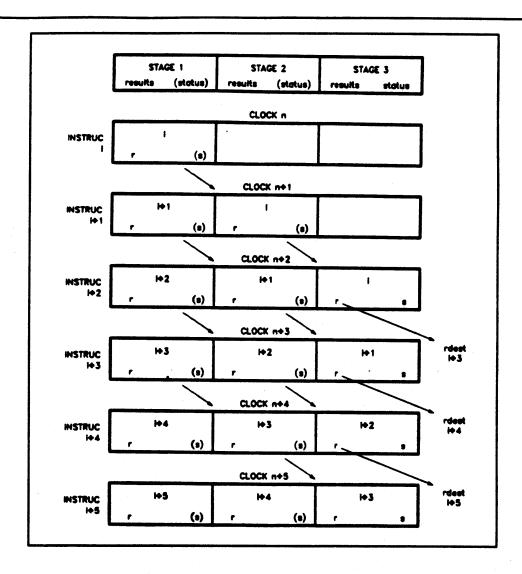

Pipelining within the floating-point multiplier unit can be described similarly, except that it requires two clocks per stage on double-precision operations. The resulting status-bits in the FSR reflect the result of the last completed operation within the pipeline. Pipelined instruction execution is shown in Figure 2.2.

The functions performed by each stage of the pipeline are not documented. Programs should not rely on specific actions, only that the pipeline is of fixed length.

Figure 2.2 Pipelined Instruction Execution.

In addition to pipelined execution, the i860 Microprocessor can also execute floating-point operations in scalar mode. In this mode, the floating-point unit does not initiate a new operation until the previous floating-point operation is completed, so that the scalar operation passes through all the stages of its pipeline before a new operation is started. Scalar mode is used when the next operation depends upon the result of the previous floating-point operations, or when the compiler or assembly language programmer wishes to avoid the added complexity of pipelining.

#### 2.2.3 FLOATING-POINT ADDER UNIT

The floating-point adder unit of the i860 microprocessor supports both double- and single-precision IEEE 754 format and operates in two modes: scalar or pipelined mode. In scalar mode, three clocks are required to complete an add, subtract or compare operation. In pipeline mode, one result per clock for either a single- or double-precision operation is obtained.

The adder unit supports the following precision combinations between inputs and results: single to double, double to double and single to double. For this reason, the adder is also used to perform data precision conversions. Some of the instructions executed exclusively by the adder unit are: Floating-point add (FADD)

Floating-point subtract (FSUB)

Pipelined floating-point comparisons: (pfgt.p, pfeq.p)

## 2.2.4 FLOATING-POINT MULTIPLIER UNIT

The floating-point multiplier unit performs floating-point multiplication in accordance with the IEEE standard. It is organized as a three-stage pipeline. In pipelined mode, the multiplication throughput is one clock for single-precision and two clocks for double-precision.

The multiplier unit also supports a reciprocal instruction which is used to implement division and square-root operations by means of an iterative process. A small macro (or function) can be developed based on these instructions to perform the full division or square root.

Some instructions allow the multiplier unit to operate in parallel with the adder unit in a variety of flexible ways, thereby doubling the number of operations per clock.

#### 2.2.5 DUAL OPERATION FEATURE

Dual operation is a special feature of the i860 microprocessor which allows the floating-point adder and multiplier unit to work in parallel, thus doubling the number of floating-point operations performed. Both add-and-multiply and subtract-and-multiply operations are supported.

The instruction formats for add-and-multiply and subtract-and-multiply allow specification

of only two source operands and one destination. However, when operating the adder and multiplier in parallel, two pairs of operands and two destinations are needed for the general case. To overcome this limitation, the adder and multiplier can be configured in a variety of ways that are specially suitable for such problems as:

matrix manipulation (e.g., solving linear equations) infinite series calculations (e.g., SIN function calculation) signal processing applications (e.g., fast Fourier transform) graphics (e.g., coordinate transformations)

For this purpose, three special registers are used -- KR, KI and T. Both KR and KI can be used to hold constants or temporary values. These values can be loaded when used as operand inputs to the multiplier, and can later supply the value, without the need for an explicit instruction operand. T can act as a transfer register to hold the value of the result of a multiplication, which can be passed on as an operand to the adder on a later instruction.

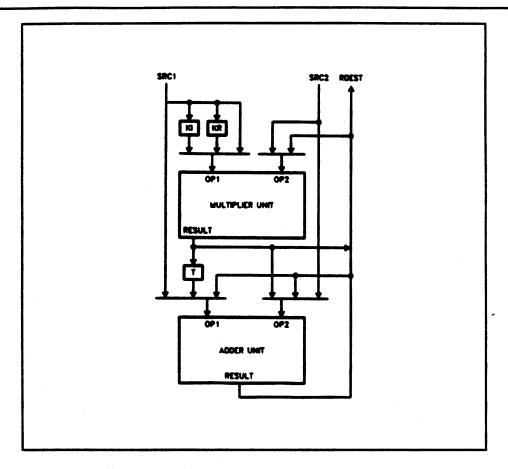

The data paths available are shown in Figure 2.3. Possible configurations can be selected as follows:

Operand 1 of the multiplier can be KR, KI, or scrl.

Operand 2 of the multiplier can be scr2 or the last stage of the adder pipeline.

Operand 1 of the adder can be scrl, the T-register, or the last stage result of the adder pipeline.

Operand 2 of the adder can be scr2, the last-stage result of the multiplier pipeline, or the last-stage result of the Adder pipeline.

In addition to the selection of operands, the instruction can choose whether to load KI, KR, or T as part of its operation. The possible operand data path selections and loading options allow a large number of possible combinations. Many of these combinations are functionally redundant or of no interest. Each instruction format for add-and-multiply and subtract-and-multiply supports 16 different instructions, and each of these instructions provides a different configuration of operand data path and KI, KR, or T loading selection. The configurations have been specially selected to streamline the implementation of the applications previously mentioned. Refer to the i860 Microprocessor Programmer's Reference Manual for further details.

Figure 2.3 Dual-operation Data Paths.

## 2.2.6 DUAL-INSTRUCTION MODE

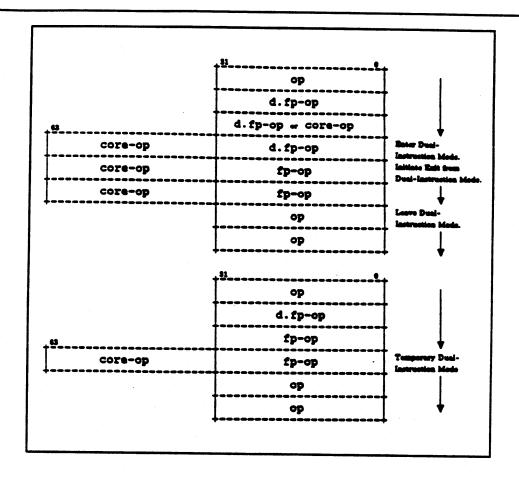

The i860 microprocessor also provides an additional form of parallelism, which results from the ability to execute a core instruction and a floating-point instruction simultaneously. This parallel instruction execution is referred to as dual-instruction mode. When executing in this mode, the instruction sequence consists of 64-bit aligned instruction pairs with a floating-point instruction in the lower 32 bits and a core instruction in the upper 32 bits. Figure 2.4 identifies the instructions executed by the core unit and those executed by the floating-point unit.

Figure 2.4 Dual-instruction Mode.

Enabling and disabling dual and single instruction mode is controlled by software. The d.fp-op in Figure 2.4 indicates the instructions responsible for enabling the dual-instruction mode. As shown in the Figure, there is a one-instruction delay between the instruction that does the enabling or disabling and the instruction which performs the operation.

Note that when a 64-bit dual-instruction pair directly follows a delayed branch instruction in dual-instruction mode, both 32-bit instructions are executed.

Further details regarding the use of dual-mode instructions are provided in the i860 Microprocessor Programmer's Reference Manual.

#### 2.2.7 FLOATING-POINT COMPUTATION THROUGHPUT

The combination of the dual-instruction mode feature with pipelined dual operation allows the i860 Microprocessor to achieve a sustained 80 MFLOPs in single-precision and 60 MFLOPs in double-precision for inner loops of common computations. Assuming the code is in the cache, no visible memory cycles are needed to fetch the instructions.

The dual-instruction mode allows the loading and storing of operands and the updating of array indexes and loop control information to be performed in parallel with floating-point execution. A load or a store (core unit instruction) can transfer up to four single-precision operands or two double-precision operands, assuming these operands are adjacent to each other in memory within some data array. Loads and stores take one clock cycle if the data is in the cache, and two clock cycles if fetched from external memory. If the operands are from memory, instructions can continue to be executed in the pipeline as long as they don't access the registers being loaded. Thus, indexing, loop-control, and operand loading can typically take place in parallel with the floating-point computation, maintaining the sustained rate.

In pipelined mode, two single-precision floating-point operations can be executed per clock cycle resulting in a rate of (2 operations/clock) X(40 MHz/sec) = 80 MFLOPs. For double-precision, addition requires one clock cycle, while multiplication requires two. For algorithms that require two floating-point additions and one multiplication for each iteration, two adds and one multiply can be done in parallel in two clock cycles. This results in three operations in two clock cycles, or (3-operations/2-cycles) X(40 MHz) = 60 MFLOPs. Algorithms requiring a double-precision multiply and add for every iteration execute at two operations per two clock cycles (due to the multiply two-clock bottleneck), resulting in an execution rate of 40 MFLOPs.

#### 2.3 PAGING UNIT

The paging unit provides the i860 microprocessor with the capability of supporting an efficient implementation of demand-paged virtual memory. Demand-paged virtual memory allows programs to use a larger, virtual memory space, which is actually supported by a smaller real (or physical) memory space. The paging unit, in combination with the appropriate memory management software, automatically allocates physical pages of memory to virtual page addresses as they are needed (on demand). Typically, when all of physical memory is used up, physical memory is swapped out to disk, and pages are reallocated.

The paging unit provides the ability to translate virtual addresses used by the

processor to physical addresses that correspond to locations in the external memory. It also provides page-level protection based on access rights, as well as two levels of privilege: user and supervisor.

Address translation and memory protection are optional. They are enabled by the aAddress translation enable (ATE) bit in the directory base register. If this bit is not set, the physical address is the same as the virtual address, and no translation or access-rights checking is performed. The ATE bit is cleared upon reset. i860 microprocessor paging unit functions the same and uses the same page table entgry formats as the Intel 386<sup>TM</sup>/486<sup>TM</sup> Microprocessors.

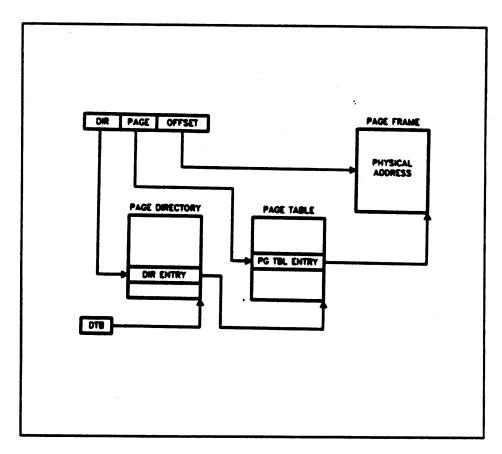

#### 2.3.1 PAGING ALGORITHM

A virtual address is mapped to a physical address according to a set of tables called page tables. The address is divided into a page address and an offset. A page is a collection of data that occupies the space of a page frame in main memory, or some location in secondary storage when there is insufficient space in main memory. A page frame consists of 4K bytes of contiguous physical memory starting on a 4K-byte boundary. The upper 20 bits of the 32-bit address of a page frame is referred to as the page address. In the i860 microprocessor, both virtual and physical addresses are 32 bits wide. They both consist of a 20-bit page address and a 12-bit offset. The concatenation of the two provides a complete 32-bit byte address.

The address translation algorithm uses two levels of page tables. The two levels are referred to as the page directory and the page tables. Both levels of page tables are a page (4096 bytes) in size, consisting of 1024, 32-bit entries.

The directory-base register, DIRBASE, contains a 20-bit field which points to the page address of the page directory. Only one page directory table is active at any given time. The entries of the page directory contain the physical addresses of all the page tables used for the mapping process, or contain entries indicating that the given page tables (corresponding to virtual segments of address space) are not present in physical memory. The page tables themselves contain physical page addresses for all the valid virtual pages, or entries indicating that the given virtual memory address is not present in physical memory.

The algorithm mapping virtual memory to physical memory is fully implemented by the hardware and is depicted in Figure 2.5. The most-significant 10 bits of the virtual address are used as an index into the page directory, which selects a specific page table. The next 10 bits are used as an index into the selected page table, selecting a page frame address. The last 12 bits act as an offset into the page frame address,

building up a full 32-bit physical byte address. This then, completes the virtual to physical address conversion.

I,f during a memory transfer, the page directory or page table indicates that a selected page table or page frame is not present (by means of a zero in the present bit of the table entry), a trap occurs, allowing the software to validate the page by reading it from disk. The page table entries also provide the write, user, cache disable, accessed and dirty bits, as well as three user-defined bits. These bits, along with the write protect bit in the extended processor status register, are used to provide page-level protection rights, page cacheability information, and information needed to implement an efficient replacement algorithm for swapping out page frames when main memory is full. More details are provided in the i860 Microprocessor Programmer's Reference Manual.

Figure 2.5 Paging Algorithm Implementation.

To avoid accessing the page directory and page table for every address translation, the i860 microprocessor implements an on-chip translation look-aside buffer (TLB), which is a cache that directly translates a virtual page address to a physical address, and provides the additional bits from the page tables needed to provide protection and information for replacement algorithms. TLB translation requires one clock cycle and is typically invisible because of the processor's pipelining.

The TLB is implemented as a 4-way, set-associative cache, mapping a total of 64 page table entries. Because each page table entry maps 4 Kbytes of address space, a total of 4K X 64 or 256 Kbytes of memory are mapped at any one time by the TLB. When there is a miss in the TLB and the page tables in memory are used, an entry in the TLB is automatically replaced by the new mapping. Selection of which entry to replace is performed by a proprietary LRU-like (least recently used) algorithm.

# 2.4 ON-CHIP CACHES AND BUS CONTROL

The i860 microprocessor contains both an instruction and data cache. Being integrated so close to the processor, and having been carefully designed for minimum delay, cache storage can operate much faster than external memory. In addition, having both caches on-chip, they can operate in parallel. Thus, the processor can simultaneously read instructions (instruction cache), read or write data (data cache), and translate virtual addresses(TLB). The caches also provide wide data-paths: the instruction cache is 64-bits wide, and the data cache is 128-bits wide. Also, on-chip caches reduce the need for external caches, which reduces the total system cost and makes available valuable PC-board real estate.

Both the data and instruction caches are virtually addressed. This not only provides for faster operation, but allows the TLB to perform its virtual address to physical translation in parallel with the operation of the cache. If one of the caches determines that it does not have the contents of the required virtual address (a cache miss), the TLB will at that point be ready with a physical address with which to begin an external memory cycle.

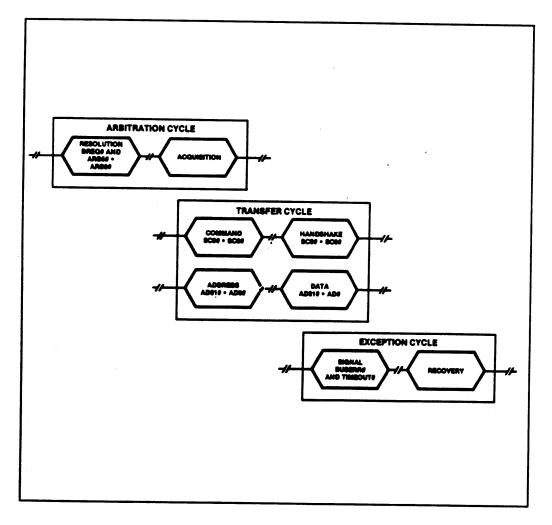

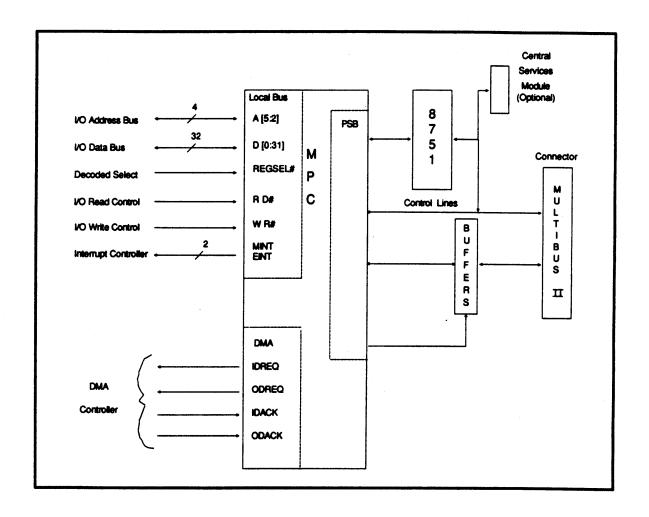

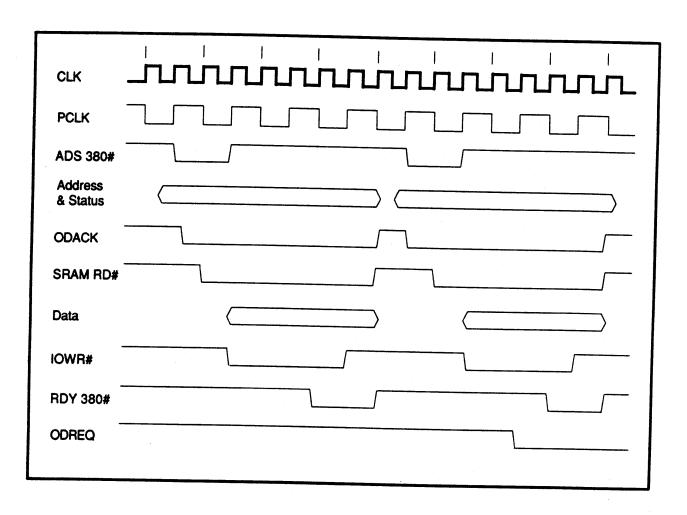

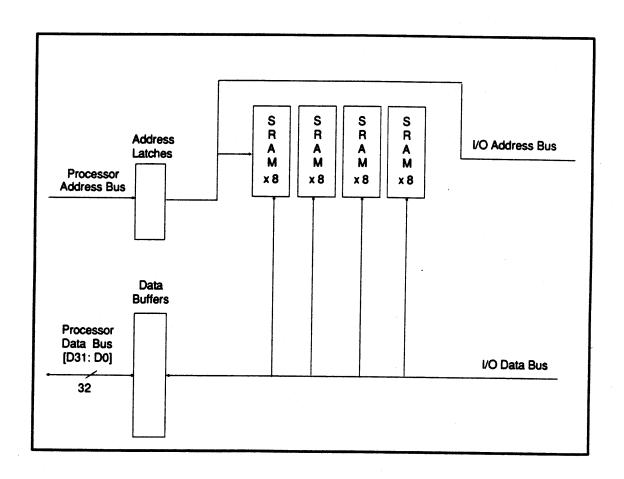

Both the instruction and data caches are implemented as a two-way set associative memory which maps a virtual address to a 32-byte block of data. These blocks correspond to 32 consecutive bytes loaded from an address having zero for the least-significant five bits. When transferring data to or from the cache, the processor will use the desired set of bytes from this 32-byte group. Allocation and replacement for both caches is always performed using blocks of 32 bytes. The i860 microprocessor uses a wrap-around technique which makes more efficient the process of filling a