intel

# 80960KB Hardware Designer's Reference Manual

## **LITERATURE**

To order Intel literature write or call:

Intel Literature Sales P.O. Box 58130 Santa Clara, CA 95052-8130 Toll Free Number: (800) 548-4725\*

Use the order blank on the facing page or call our **Toll Free** Number listed above to order literature. Remember to add your local sales tax and a 10% postage charge for U.S. and Canada customers, 20% for customers outside the U.S. Prices are subject to change.

#### 1988 HANDBOOKS

Product line handbooks contain data sheets, application notes, article reprints and other design information.

| NAME                                                                           | ORDER NUMBER | **PRICE IN<br>U.S. DOLLARS |

|--------------------------------------------------------------------------------|--------------|----------------------------|

| COMPLETE SET OF 8 HANDBOOKS<br>Save \$50.00 off the retail price of \$175.00   | 231003       | \$125.00                   |

| AUTOMOTIVE HANDBOOK (Not included in handbook Set)                             | 231792       | \$20.00                    |

| COMPONENTS QUALITY/RELIABILITY HANDBOOK (Available in July)                    | 210997       | \$20.00                    |

| EMBEDDED CONTROLLER HANDBOOK (2 Volume Set)                                    | 210918       | \$23.00                    |

| MEMORY COMPONENTS HANDBOOK                                                     | 210830       | \$18.00                    |

| MICROCOMMUNICATIONS HANDBOOK                                                   | 231658       | \$22.00                    |

| MICROPROCESSOR AND PERIPHERAL HANDBOOK (2 Volume Set)                          | 230843       | \$25.00                    |

| MILITARY HANDBOOK (Not included in handbook Set)                               | 210461       | \$18.00                    |

| OEM BOARDS AND SYSTEMS HANDBOOK                                                | 280407       | \$18.00                    |

| PROGRAMMABLE LOGIC HANDBOOK                                                    | 296083       | \$18.00                    |

| SYSTEMS QUALITY/RELIABILITY HANDBOOK                                           | 231762       | \$20.00                    |

| PRODUCT GUIDE Overview of Intel's complete product lines                       | 210846       | N/C                        |

| DEVELOPMENT TOOLS CATALOG                                                      | 280199       | N/C                        |

| INTEL PACKAGING OUTLINES AND DIMENSIONS Packaging types, number of leads, etc. | 231369       | N/C                        |

| LITERATURE PRICE LIST List of Intel Literature                                 | 210620       | N/C                        |

<sup>\*</sup>Good in the U.S. and Canada

<sup>\*\*</sup>These prices are for the U.S. and Canada only. In Europe and other international locations, please contact your local Intel Sales Office or Distributor for literature prices.

# LITERATURE SALES ORDER FORM

| TY:                                                    |                                                             | STATE: ZIP:                         |

|--------------------------------------------------------|-------------------------------------------------------------|-------------------------------------|

| OUNTRY:                                                |                                                             |                                     |

| HONE NO.: ()                                           |                                                             |                                     |

| ORDER NO.                                              | TITLE                                                       | QTY. PRICE TOTA                     |

|                                                        |                                                             | ×=                                  |

|                                                        |                                                             | ×=                                  |

|                                                        |                                                             | ×=                                  |

|                                                        |                                                             | ×=                                  |

| <del></del>                                            |                                                             | ×=                                  |

|                                                        |                                                             |                                     |

|                                                        |                                                             | ×=                                  |

|                                                        |                                                             | ×=                                  |

| <u> </u>                                               |                                                             | ×=                                  |

|                                                        |                                                             | ×=                                  |

|                                                        |                                                             | ×=                                  |

|                                                        |                                                             | Subtotal                            |

|                                                        |                                                             | Must Add Your                       |

|                                                        |                                                             | Local Sales Tax                     |

| Must add appropriate posta<br>10% U.S. and Canada, 20° |                                                             | Postage                             |

| <del> </del>                                           |                                                             | Total                               |

|                                                        |                                                             | Order, or company purchase order pa |

| inter Literature Sales. All                            | ow 2-4 weeks for delivery.<br>] American Express Expiration |                                     |

should contact their local Intel Sales Office or Distributor

European Literature Order Form in back of book.

listed in the back of most Intel literature.

Call Toll Free: (800) 548-4725 for phone orders

P.O. Box 58130

Santa Clara, CA 95052-8130 Mail To: Intel Literature Sales

P.O. Box 58130

Santa Clara, CA 95052-8130

# 80960KB HARDWARE DESIGNER'S REFERENCE MANUAL

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

Above, BITBUS, COMMputer, CREDIT, Data Pipeline, FASTPATH, GENIUS, i,  $\hat{\mathbf{1}}$ , ICE, iCEL, iCS, iDBP, iDIS, I<sup>2</sup>ICE, iLBX, i<sub>m</sub>, iMDDX, iMMX, Inboard, Insite, Intel, int<sub>e</sub>ll, int<sub>e</sub>lBOS, Intel Certified, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, iOSP, iPDS, iPSC, iRMK, iRMX, iSBC, iSBX, iSDM, iSXM, KEPROM, Library Manager, MAP-NET, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, MultiSERVER, ONCE, OpenNET, OTP, PC-BUBBLE, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Quick-Pulse Programming, Ripplemode, RMX/80, RUPI, Seamless, SLD, SugarCube, SupportNET, UPI, and VLSiCEL, and the combination of ICE, iCS, iRMX, iSBC, iSBX, iSXM, MCS, or UPI and a numerical suffix, 4-SITE.

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Distribution Mail Stop SC6-59 3065 Bowers Avenue Santa Clara, CA 95051

| CHAPTER 1                                              |

|--------------------------------------------------------|

| INTRODUCTION TO THE 80960KB MICROPROCESSOR             |

| Architectural Attributes for Embedded Computing        |

| Load/Store Design 1-1                                  |

| Large General-Purpose Register Sets                    |

| Small Number of Addressing Modes1-3                    |

| Simplified Instruction Format                          |

| Overlapped Execution                                   |

| Minimum cycle operation                                |

| Additional 80960KB Architectural Enhancements 1-4      |

| Floating-point Operation                               |

| Debug Capabilities                                     |

| Standard Bus Interface                                 |

| Inter-Agent Communication/Coprocessor Capabilities 1-5 |

| Summary                                                |

|                                                        |

| CHAPTER 2                                              |

| 80960KB SYSTEM ARCHITECTURE                            |

| Overview of a Single Processor System Architecture 2-1 |

| 80960KB Processor and the L-Bus                        |

| Memory Module                                          |

| I/O Module                                             |

| Summary 2-3                                            |

| OLIABTED O                                             |

| CHAPTER 3                                              |

| THE 80960KB PROCESSOR AND THE LOCAL BUS                |

| Overview of the 80960KB L-Bus                          |

| Basic L-Bus States                                     |

| L-Bus Signal Groups                                    |

| Address/Data                                           |

| Control                                                |

| L-Bus Transactions 3-8                                 |

| Clock Signal                                           |

| Basic Read 3-8                                         |

| Basic Write 3-1                                        |

| Burst 3-12                                             |

| Timing Generation 3-14                                 |

| 80960KB Processor Clock Requirements                   |

| Clock Generation                                       |

| Arbitration                                            |

| Single 80960KB Processor on the L-Bus                  |

# $\text{intel}^{^{\circ}}$

| State Diagram                                              |      |

|------------------------------------------------------------|------|

| Arbitration Timing                                         | 3-19 |

| Two 80960KB Processors on the L-Bus                        | 3-20 |

| Bus states for Two 80960KB Processors                      | 3-21 |

| Arbitration Timing for Two 80960KB Processors on the L-Bus |      |

| Bus Exchange Example Between Two 80960KB Processors        | 3-23 |

| A Peripheral Device As the Default Bus Master              | 3-24 |

| Inter-Agent Communication (IAC)                            |      |

| Overview of IAC Operations                                 | 3-26 |

| IAC Messages                                               | 3-26 |

| Hardware Requirements for External IAC Messages            | 3-27 |

| Message Buffers                                            | 3-27 |

| IAC Pin Logic                                              |      |

| External Priority Register                                 |      |

| Hardware Requirements                                      |      |

| External Priority and IAC Messages                         |      |

| Interrupts                                                 |      |

| Interrupt Signals                                          | 3-29 |

| Interrupt Control Register                                 |      |

| Using the Four Direct Interrupt Pins                       |      |

| Using an External Interrupt Controller                     |      |

| Using IAC Requests for Interrupts                          | 3-32 |

| Synchronization                                            | 3-32 |

| RESET and Initialization                                   |      |

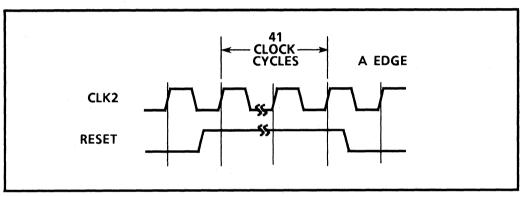

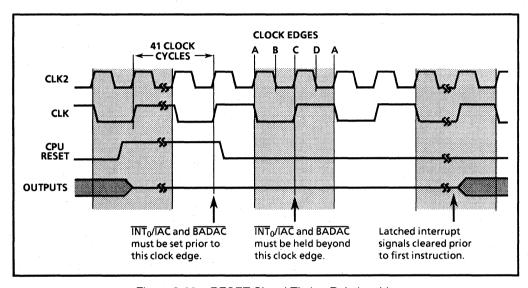

| RESET Timing Requirements                                  |      |

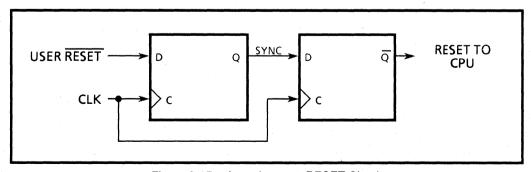

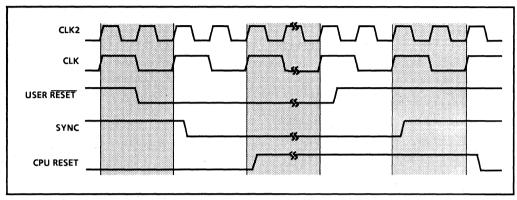

| RESET Timing Generation                                    | 3-33 |

| Initialization                                             |      |

| Error Signals                                              |      |

| Summary                                                    |      |

|                                                            |      |

| CHAPTER 4                                                  |      |

| MEMORY INTERFACE                                           |      |

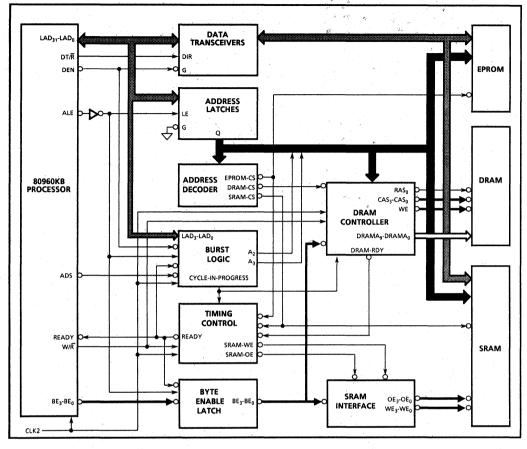

| Basic Memory Interface                                     | 4-1  |

| Data Transceivers                                          | 4-1  |

| Address Latch/Demultiplexer                                |      |

| Address Decoder                                            |      |

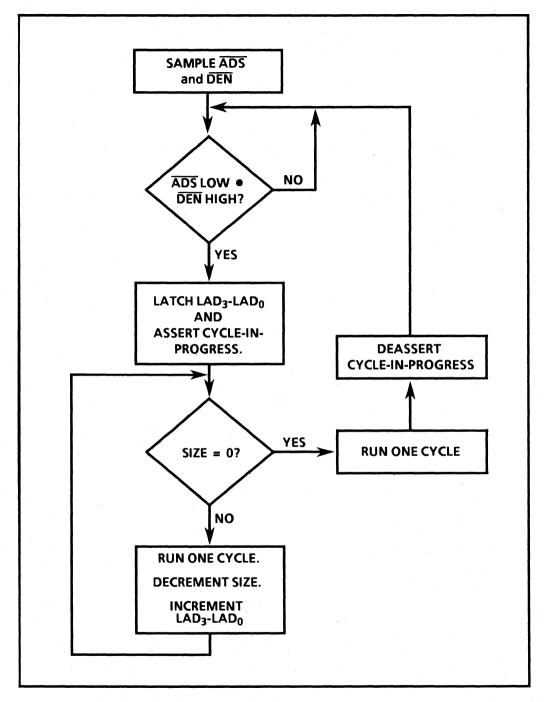

| Burst Logic                                                | 4-3  |

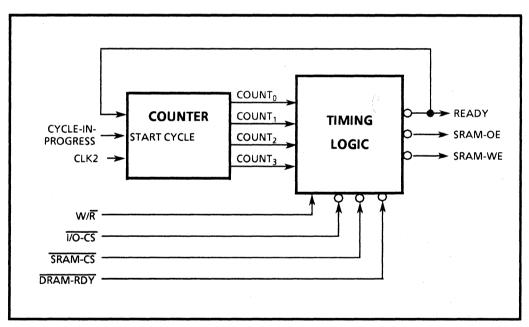

| Timing Control Logic                                       | 4-5  |

| Byte Enable Latch                                          |      |

| SRAM Interface                                             | 4-6  |

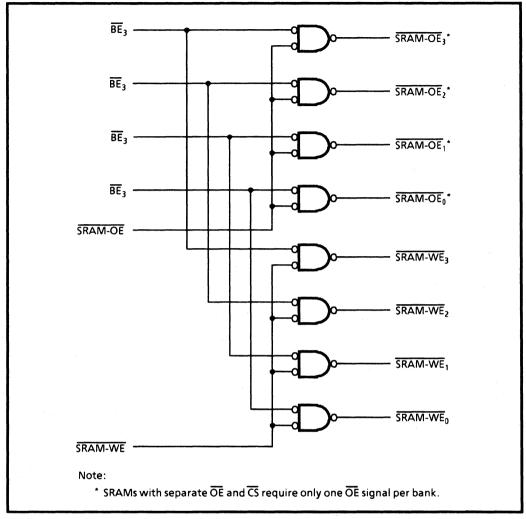

| SRAM Interface Logic                                       | 4-6  |

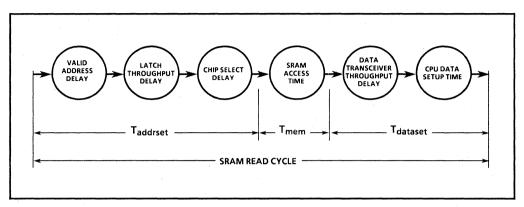

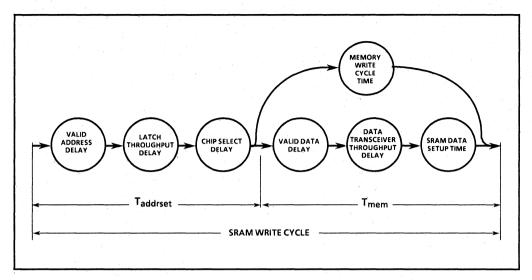

| SRAM Timing Considerations                                 | 4-7  |

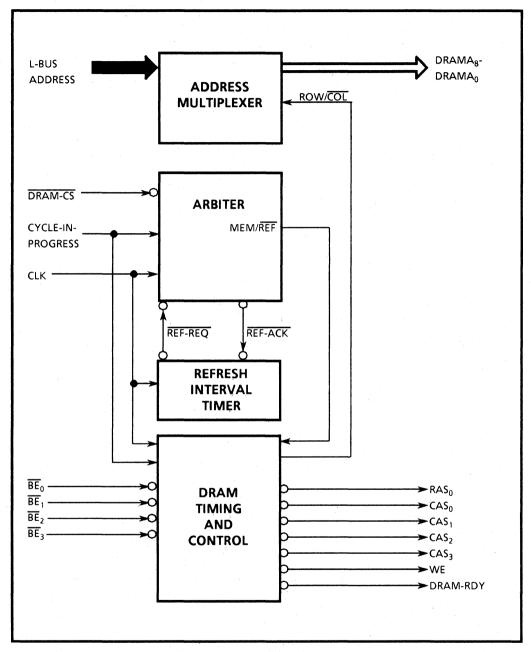

| DRAM Controller                                            | 4-11 |

| Address Multiplexer                                        |      |

# intel®

| Refresh Interval Timer 4-13 Arbiter 4-13 DRAM Timing and Control 4-13 Timing Considerations for the DRAM Controller 4-15 DRAM Interleaving 4-15 Summary 4-20                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 5 I/O INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

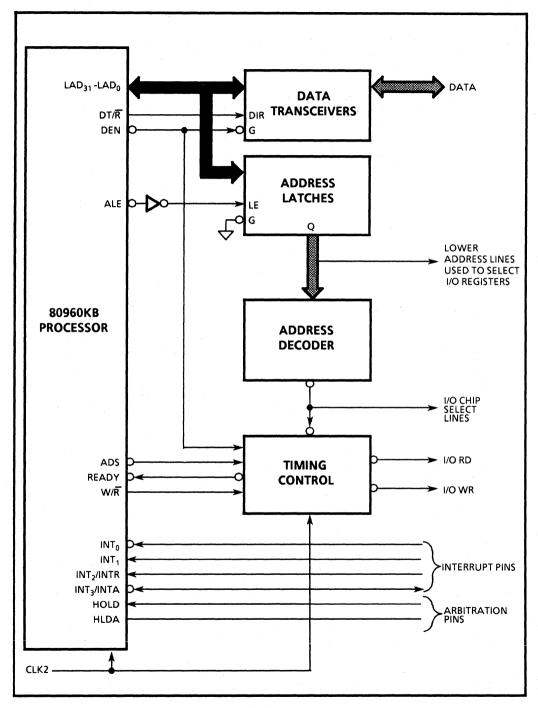

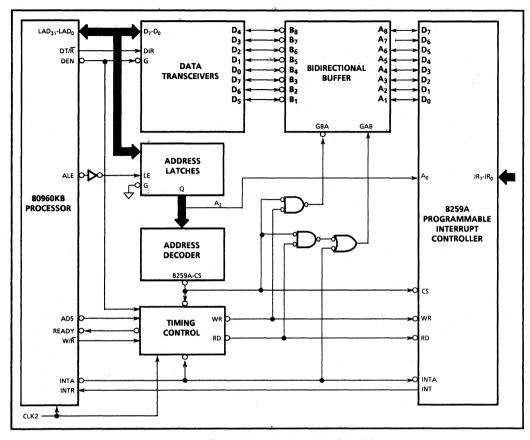

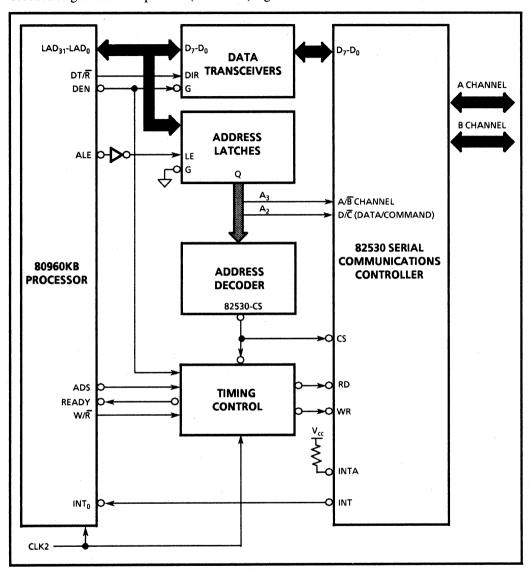

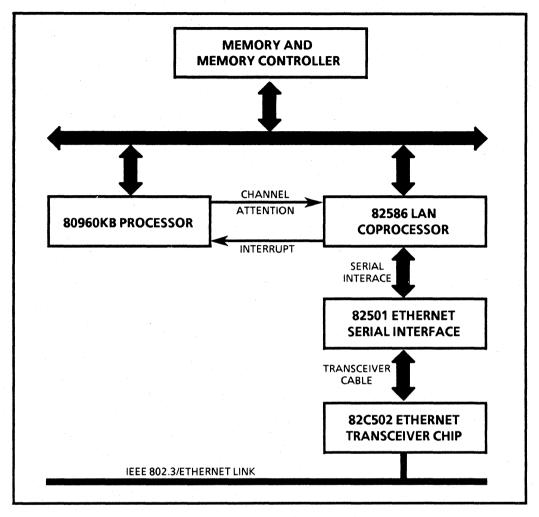

| Interfacing to 8-bit and 16-bit Peripherals 5-1 General System Interface 5-1 Data Transceivers 5-3 Address Latch/Demultiplexer 5-3 Address Decoder 5-3 Timing Control Logic 5-4 I/O Interface Design Examples 5-5 8259A Programmable Interrupt Controller 5-5 Interface 5-5 Operation 5-7 82530 Serial Communication Controller Example 5-7 82586 Local Area Network Coprocessor Example 5-9 Interface 5-10 Operation 5-12 82786 Graphics Coprocessor Example 5-14 Interface 5-15 Operation 5-15 Summary 5-19                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1-1. Local Register Set       1-2         1-2. Global Register Set       1-3         2-1. Basic 80960KB System Configuration       2-2         3-1. Basic L-Bus States       3-2         3-2. L-Bus Signal Groups       3-3         3-3. Byte Enable Timing Diagram       3-5         3-4. Clock Relationships       3-8         3-5. 80960KB Processor Read Transaction       3-10         3-6. 80960KB Processor Write Transaction       3-12         3-7. 80960KB Processor Burst Read Transaction       3-13         3-8. 80960KB Processor Burst Write Transaction       3-14 |

# intel®

|        | System Clock Pulse                                             |      |

|--------|----------------------------------------------------------------|------|

| 3-10.  | Clock Generation Circuit                                       | 3-16 |

|        | Clock Timing Waveforms                                         |      |

|        | L-Bus States with Arbitration                                  |      |

|        | Arbitration Timing Diagram for a Bus Master                    |      |

| 3-14.  | Arbitration Connection Between Two 80960KB Processors          | 3-21 |

| 3-15.  | L-Bus States for Secondary Bus Master                          | 3-22 |

| 3-16.  | Arbitration Timing Diagram for an SBM                          | 3-23 |

| 3-17.  | Example of a Bus Exchange Transaction                          | 3-24 |

| 3-18.  | Forced Relinquishment Timing Diagram for an SBM                | 3-25 |

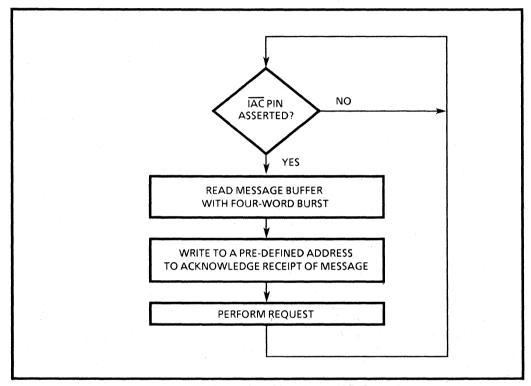

| 3-19.  | Example Flow Chart for an IAC Operation                        | 3-26 |

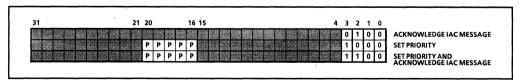

| 3-20.  | Data Settings                                                  | 3-27 |

| 3-21.  | Data Settings Physical Address Interpretation for IAC Messages | 3-28 |

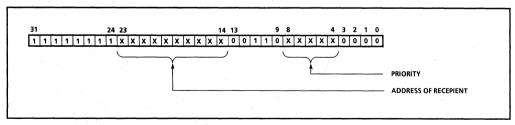

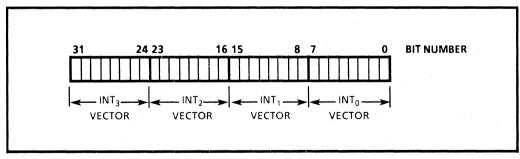

| 3-22.  | Interrupt Control Register                                     | 3-30 |

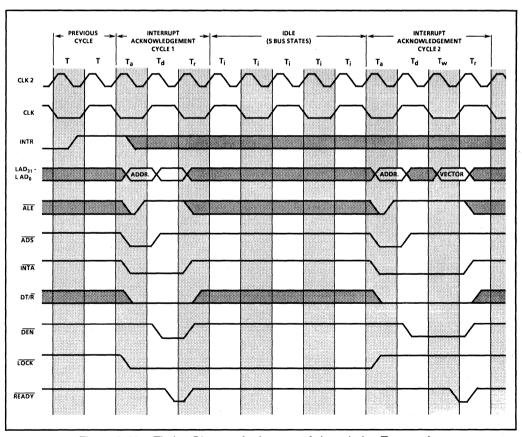

| 3-23.  | Timing Diagram for Interrupt Acknowledge Transaction           | 3-31 |

| 3-24.  | RESET Timing Diagram                                           | 3-33 |

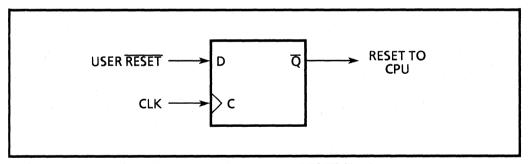

|        | Asynchronous RESET Circuit                                     |      |

|        | Diagram for RESET Timing Generation                            |      |

|        | Synchronous RESET Circuit                                      |      |

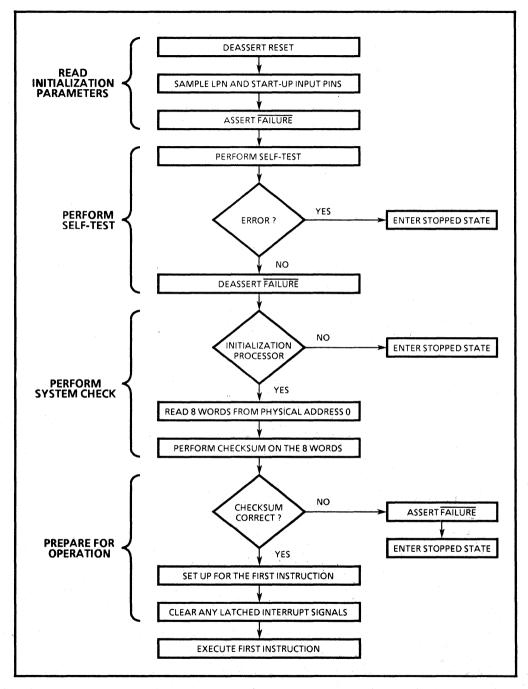

|        | Initialization Flow Chart                                      |      |

|        | RESET Signal Timing Relationship                               |      |

|        | Simplified Block Diagram for Memory Interface Logic            |      |

| 4-2.   | Burst Logic Flow Chart                                         | 4-4  |

| 4-3.   | Timing Control Logic Block Diagram                             | 4-5  |

| 4-4.   | Block Diagram for SRAM Interface                               | 4-7  |

| 4-5.   | Critical Timing Path for SRAM Read Operation                   | 4-8  |

|        | Critical Timing Path for SRAM Write Transaction                |      |

| 4-7.   | DRAM Controller Block Diagram                                  | 4-12 |

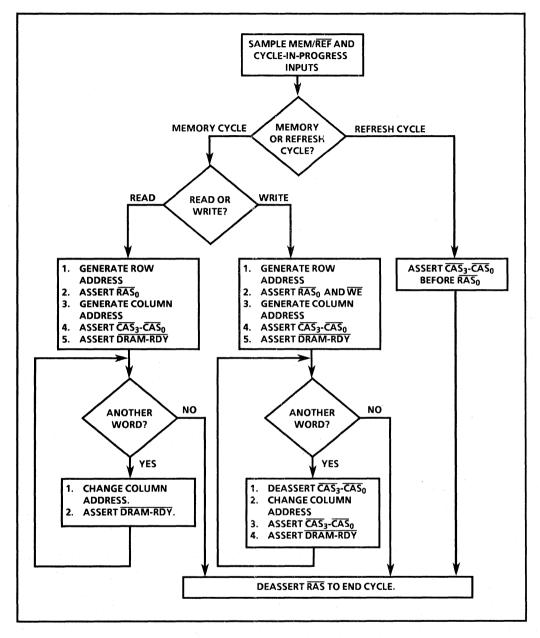

| 4-8. l | Flow Chart for DRAM Timing and Control Logic                   | 4-15 |

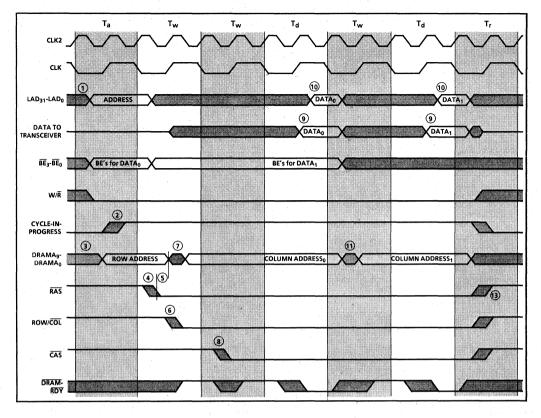

| 4-9. · | Timing Diagram for Two-word DRAM Read Transaction              | 4-18 |

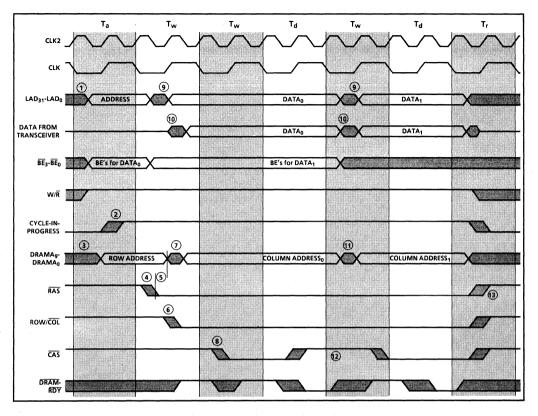

| 4-10.  | Timing Diagram for Two-word DRAM Write Transaction             | 4-19 |

|        | Simplified General System Interface                            |      |

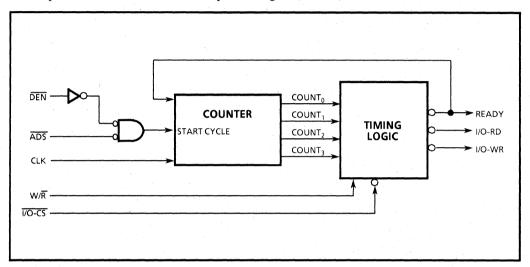

|        | Timing Control Block Diagram                                   |      |

|        | Block Diagram for 8259A Interface                              |      |

|        | Block Diagram for 82530 Interface                              |      |

|        | LAN Station                                                    | 5-10 |

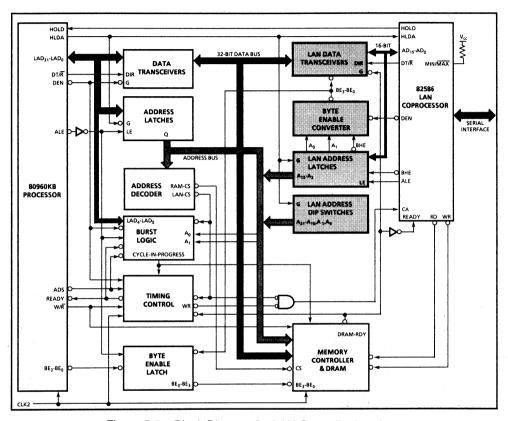

| 5-6.   | Block Diagram for LAN Controller Interface                     | 5-11 |

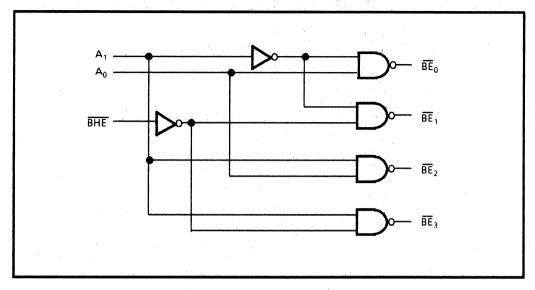

| 5-7.   | Byte Enable Generation Circuit                                 | 5-12 |

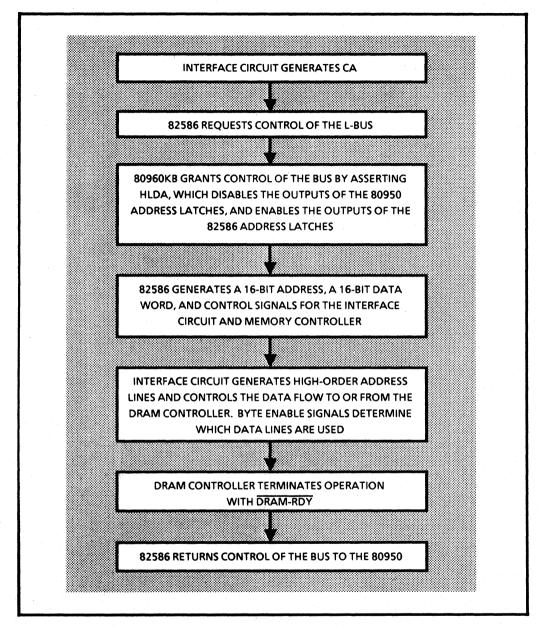

|        | Operational Flow Diagram for 82586 Interface                   |      |

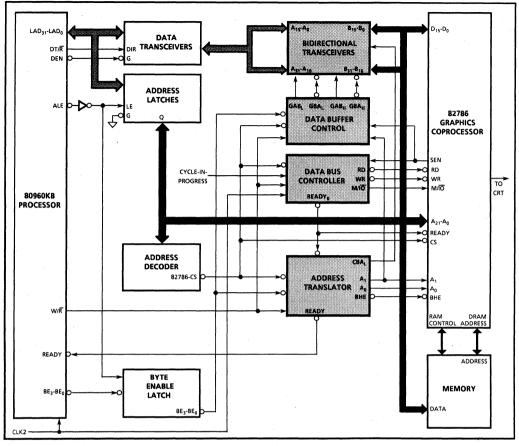

| 5-9.   | Block Diagram for 82786 Interface                              | 5-16 |

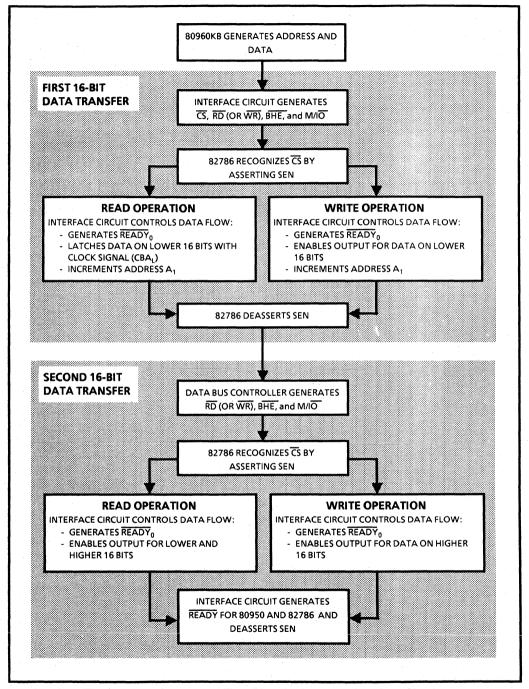

| 5-10.  | Operational Flow Diagram for 82786 Interface Circuit           | 5-18 |

# intel®

## **TABLE OF CONTENTS**

# **Tables**

| 3-1. | SIZE Signal Decoding        | 3-4  |

|------|-----------------------------|------|

| 3-2. | Byte Enable Signal Decoding | 3-5  |

| 3-3. | Summary of L-Bus Signals    | 3-7  |

| 3-4. | Combination of Bus Masters  | 3-18 |

| 4-1. | Byte Enable Signal Decoding | 4-6  |

# Preface

## **PREFACE**

This manual serves as the definitive hardware reference guide for system designs using the 80960KB and 80960KA processors (for clarity, references to the 80960KB apply to both the 80960KA and 80960KB processors). Hardware designers can use this manual as a guideline for developing microprocessor systems. Readers of this manual should be familiar with the operating principles of microprocessors and with the 80960KB data sheet.

This manual presents the 80960KB system design from a hardware perspective. Other information on the software architecture, instruction set, and programming of the 80960KB processor can be found in the 80960KB CPU Programmer's Reference Manual.

Together with the 80960KB Hardware Designer's Reference Manual, these publications provide a complete description of the 80960KB system for hardware and software designers.

#### MANUAL ORGANIZATION

This manual, divided into five chapters, describes how to build a hardware system using the 80960KB processor. The list below shows a synopsis of each chapter.

- Chapter 1 briefly introduces the 80960KB component architecture.

- Chapter 2 presents an overview of the 80960KB hardware system design, which includes a system configuration illustrating the various components that constitute a 80960KB system.

- Chapter 3 describes the local bus and the interface to the 80960KB processor. This

chapter includes detailed signal descriptions and discusses timing generation, arbitration,

interrupt handling, and initialization.

- Chapter 4 discusses techniques for designing memory subsystems.

- Chapter 5 presents guidelines on how to interface I/O devices to the local bus.

Wherever appropriate, design examples are included in the chapters. These designs are based upon functional 80960KB boards and systems, and are simplified for ease of understanding. The simplified versions of these designs have not been tested except for the figures that show the part numbers.

#### **NOTATION CONVENTIONS**

This manual uses the following style conventions.

- Integer numbers are presented in decimal notation unless otherwise indicated by the subscript "H" for hexidecimal or "B" for binary.

- An active low signal is represented by a line over the signal name. For example, READY is an active low signal.

# Introduction to the 80960KB Microprocessor

1

# CHAPTER 1 INTRODUCTION TO THE 80960KB MICROPROCESSOR

The 80960KB is the first 32-bit microprocessor designed especially for embedded applications. At an operating frequency of 20 MHz, this high performance processor can sustain an instruction execution rate of seven and one-half million instructions per second (MIPS), and burst rates of 20 MIPS<sup>1</sup>. The 80960KB processor enhances embedded system performance by integrating special features to eliminate the need for additional peripheral devices and the associated software overhead. For instance, the 80960KB processor offers an on-chip floating-point processing unit, an improved interrupt handling capability, and support for debugging and tracing.

This chapter describes the architectural attributes and enhancements of the 80960KB processor for embedded computing.

#### ARCHITECTURAL ATTRIBUTES FOR EMBEDDED COMPUTING

For over a decade, Intel has designed a large variety of 8- and 16-bit microcontrollers to fit the needs of embedded applications. Based on this experience, several architectural attributes shared by both microcontrollers and microprocessors can be implemented that benefit embedded applications and enhance microprocessor performance. Because the 80960KB processor incorporates these attributes (listed below) in its architecture, embedded applications are easy to design, perform well, and get to market fast.

- Simple load/store design

- Large general-purpose register sets

- Boolean and bit-field instructions

- Small number of operations and addressing modes

- Simplified instruction format

- Minimum cycle operation

### Load/Store Design

In the 80960 family architecture, operations are register-to-register, with only LOAD and STORE instructions accessing memory. This attribute simplifies the instruction set and shortens cycle time.

The 80960KB processor uses LOAD and STORE instructions to access memory. It further minimizes accesses to memory by providing a 512-byte, direct-mapped instruction cache. When a memory access is required, the processor can perform a burst transaction that accesses up to four data words with one word transferred every clock cycle.

<sup>&</sup>lt;sup>1</sup>DEC VAX 11/780 equals 1 MIPS

## **Large General-Purpose Register Sets**

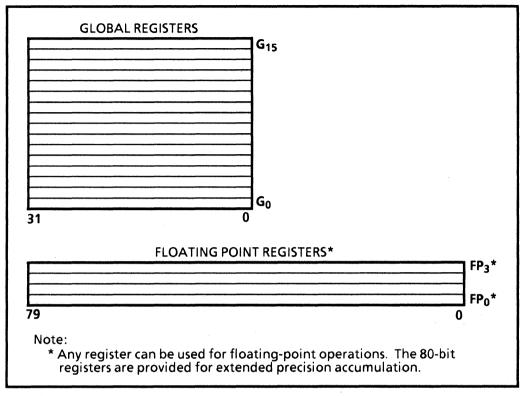

Because the instructions operate on operands within registers, the 80960 family uses many registers. The 80960KB processor features large, versatile register sets. For maximum flexibility, each processor provides 32 32-bit registers and four 80-bit floating-point registers.

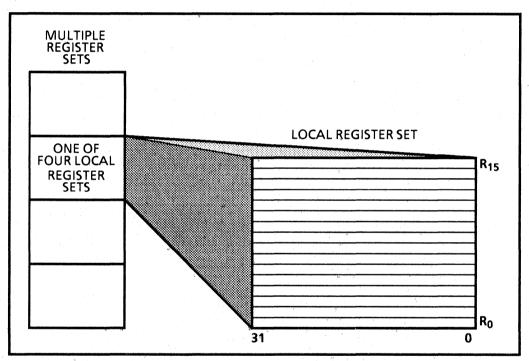

There are two types of general-purpose registers: local and global. The processor automatically accesses the 16 local registers when a procedure call is performed. Multiple sets of local registers are stored on-chip to further increase the efficiency of this register set, as shown in Figure 1-1. The register cache holds up to four local register frames, which means that up to three procedure calls can be made without having to access the procedure stack resident in memory.

Figure 1-1: Local Register Set

The 20 global registers retain their contents across procedure boundaries. The global registers consist of sixteen 32-bit registers ( $G_{15}$  through  $G_0$ ) and four 80-bit registers ( $FP_3$  through  $FP_0$ ), as shown in Figure 1-2. While all registers can be used for floating-point operations, the 80-bit registers are used for accumulation of extended precision results.

Figure 1-2: Global Register Set

## **Small Number of Addressing Modes**

The 80960 family uses relatively few addressing modes to facilitate a fast, simple interpretation by the control engine. The 80960KB processor provides simple, fast addressing modes, as well as a few complex addressing modes to allow optimizations for code density.

# **Simplified Instruction Format**

A simplified instruction format eases the hardwired decoding of instructions, which again speeds control paths. The 80960KB processor's instruction formats are simple and word aligned; all instructions are one word long except for one class that uses the subsequent word as a 32-bit displacement. To further enhance performance, the instructions do not cross word boundaries. This feature eliminates a pipeline stage (that would have to align instructions) and decreases instruction execution time.

## **Overlapped Execution**

To optimize performance, the 80960KB processor overlaps instruction execution by means of write buffering and register scoreboarding. Write buffering allows a write instruction to proceed as soon as it is placed in the buffer. It does not have to wait for the actual write operation to occur on the L-bus.

Similarly, register scoreboarding is a design technique that allows the 80960KB to continue execution of instructions when it encounters a LOAD instruction. When the LOAD instruction begins, the 80960KB sets a scoreboard bit on the target register. After the target register is loaded with data, the processor resets the bit. While the data is being retrieved, additional instructions that do not reference the target register can be executed. The 80960KB ensures that these additional instructions do not reference the target register by checking the scoreboard bit transparently (no software required). Thus, the scoreboard feature reduces the effect of slow memory speed and provides a useful tool for optimizing procedures.

## Minimum cycle operation

The 80960KB processor executes most of the core instructions in a single clock cycle. For these instructions, the 80960KB processor uses hardwired logic rather than microcode to execute the instruction.

The 80960KB also supports a number of important multicycle instructions, such as 32-bit multiply and divide instructions. These auxiliary functions require more than one clock cycle because it is more efficient to use microcode than hardwired logic. On the other hand, the integration of these functions on-chip eliminates much software overhead and the negative effects on code density that would be otherwise required. Thus, the additional functionality of the 80960KB enhances overall system performance while keeping code size small.

#### **ADDITIONAL 80960KB ARCHITECTURAL ENHANCEMENTS**

The 80960KB incorporates two useful features: an on-chip floating-point processing and debugging functions. The floating-point unit can be used for applications that require precision, such as machine-control operations. The debugging function significantly decreases development time.

# Floating-point Operation

The on-chip floating-point unit of each processor improves the performance of floating-point calculations by eliminating bus overhead used to transfer operands to a coprocessor. The processor provides hardware support for both mandatory and recommended portions of IEEE standard 754 for floating-point arithmetic, exponential, logarithmic, and other transcendental functions. By integrating the floating-point unit on-chip, the 80960KB processor reduces the overall chip count for a system, decreases power consumption, and increases overall performance and reliability.

# **Debug Capabilities**

The processor provides extensive system debug capabilities, an important feature for embedded computing where the ability to instrument an application may be limited. The 80960KB processor allows breakpoint instructions that stop program execution on various events, such as procedure calls, or certain instructions. Another debug facility traces the activity of the processor while it is executing a program. Tracing is done by recording the addresses of instructions that cause trace events to occur. For example, a trace event can occur on the execution of a specific instruction, branch, or procedure call. To ensure that the 80960KB is operating properly, the processor performs a self-test when it is reset. If the self-test is successful, the 80960KB begins operation, otherwise it enters the stopped state.

#### STANDARD BUS INTERFACE

The advanced features of the 80960KB processor are implemented using a performance-optimized bus interface. The processor uses a high bandwidth local bus (L-bus) that consists of standard signal groups: a 32-bit multiplexed address/data path and control signals for data transactions. Because of the large amount of caching, the L-bus supports burst transactions that transfer up to four successive data words. Transactions on the L-bus can use 8-, 16-, and 32-bit data types and address up to 4G bytes of physical memory. Bus arbitration can be accomplished by simply using the hold request/hold acknowledge protocol.

#### INTER-AGENT COMMUNICATION/COPROCESSOR CAPABILITIES

The 80960KB processor offers a flexible way to manage interrupts. It accepts interrupts in one of three ways: by communicating with an external interrupt controller using the standard Interrupt/Interrupt Acknowledge signals, by activating the on-chip interrupt controller, or by accepting an inter-agent communication (IAC) message. This allows the 80960KB to act as a coprocessor on a shared bus with another CPU.

#### SUMMARY

The 80960KB processor optimizes embedded system performance by using a new 32-bit architecture. The 80960 family architecture includes a load/store design, large general purpose register sets, fast addressing modes, a simplified instruction format, and minimized instruction execution cycles.

To further enhance system performance, the 80960KB processor provides floating-point operation, interrupt controller capabilities, and debug functions. By intergrating these functions on-chip, the 80960KB reduces the power requirements and overall chip count for a system.

As a result of the 80960 architecture, the 80960KB processor provides unprecedented performance. For a speed selection of 20 MHz, it can sustain an instruction execution rate of over seven and one-half million MIPS and burst rates of 20 MIPS, speeds comparable to that of super minicomputers. The high instruction execution rates are made possible through a innovative design that incorporates an on-chip instruction cache with burst-transfer capability.

# CHAPTER 2 80960KB SYSTEM ARCHITECTURE

This chapter illustrates the flexibility and power of the 80960KB system architecture using the advanced 32-bit 80960KB processor. This chapter examines system configurations from a general perspective to explain the design concepts. Subsequent chapters describe the details of the system design.

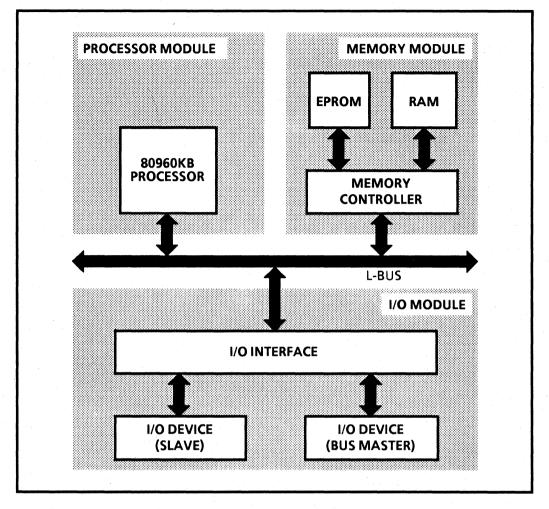

#### **OVERVIEW OF A SINGLE PROCESSOR SYSTEM ARCHITECTURE**

The central processing module, memory module, and I/O module form the natural boundaries for the hardware system architecture. The modules are connected together by the high bandwidth 32-bit multiplexed L-bus, which can transfer data at a maximum sustained rate of 53M bytes per second for an 80960KB processor operating at 20 MHz.

Figure 2-1 shows a simplified block diagram of a possible system configuration. The heart of this system is the 80960KB processor, which fetches program instructions, executes code, manipulates stored information, and interacts with I/O devices. The high bandwidth L-bus connects the 80960KB processor to memory and I/O modules. The 80960KB processor stores system data and instructions and programs in the memory module. By accessing various peripheral devices in the I/O module, the 80960KB processor supports communication to terminals, modems, printers, disks, and other I/O devices.

#### 80960KB Processor and the L-Bus

The 80960KB processor performs bus operations using multiplexed address and data signals and provides all the necessary control signals. For example, standard control signals, such as Address Latch Enable ( $\overline{ALE}$ ), Address/Data Status ( $\overline{ADS}$ ), Write/Read command (W/ $\overline{R}$ ), Data Transmit/Receive (DT/ $\overline{R}$ ), and Data Enable ( $\overline{DEN}$ ) are provided by the 80960KB processor. The 80960KB processor also generates byte enable signals that specify which bytes on the 32-bit data lines are valid for the transfer.

The L-bus supports burst transactions, which access up to four data words at a maximum rate of one word per clock cycle. The 80960KB processor uses the two low-order address lines to indicate how many words are to be transferred. The 80960KB processor performs burst transactions to load the on-chip 512-byte instruction cache to minimize memory accesses for instruction fetches. Burst transactions can also be used for data accesses.

To transfer control of the bus to an external bus master, the 80960KB processor provides two arbitration signals: hold request (HOLD) and hold acknowledge (HLDA). After receiving HOLD, the processor grants control of the bus to an external bus master by asserting HLDA.

Figure 2-1: Basic 80960KB System Configuration

The 80960KB processor provides a flexible interrupt structure by using an on-chip interrupt controller, an external interrupt controller, or both. The type of interrupt structure is specified by an internal interrupt vector register. For a system with multiple processors, another method is available, called inter-agent communication (IAC) where a processor can interrupt another processor by sending an IAC message.

Complete details of the L-bus and bus operations are discussed in Chapter 3.

# **Memory Module**

A memory module can consist of the memory controller, Erasable Programmable Read Only Memory (EPROM), and static or dynamic Random Access Memory (RAM). The memory controller first conditions the L-bus signals for memory operation. It demultiplexes the address

and data lines, generates the chip select signals from the address, detects the start of the cycle for burst mode operation, and latches the byte enable signals.

The memory controller generates the control signals for EPROM, SRAM, and DRAM. In particular, it provides the control signals, multiplexed row/column address, and refresh control for dynamic RAMs. The controller can be designed to accommodate the burst transaction of the 80960KB processor by using the static column mode or nibble mode features of the dynamic RAM. In addition to supplying the operation signals, the controller generates the  $\overline{READY}$  signal to indicate that data can be transferred to or from the 80960KB processor.

The 80960KB processor directly addresses up to 4G bytes of physical memory. The processor does not allow burst accesses to cross a 16-byte boundary to ease the design of the controller. Each address specifies a four-byte data word within the block. Individual data bytes can be accessed by using the four byte enable signals from the 80960KB processor.

Chapter 4 provides design guidelines for the memory controller.

#### I/O Module

The I/O module consists of the I/O components and the interface circuit. I/O components can be used to allow the 80960KB processor to use most of its clock cycles for computational and system management activities. Time consuming tasks can be off-loaded to specialized slave-type components, such as the 8259A Programmable Interrupt Controller, or the 82530 Serial Communication Controller. Some tasks may require a master-type component, such as the 82586 Local Area Network Control.

The interface circuit performs several functions. It demultiplexes the address and data lines, generates the chip select signals from the address, produces the I/O read or I/O write command from the processor's W/R signal, latches the byte enable signals, and generates the  $\overline{READY}$  signal. Because these functions are the same as some of the functions of the memory controller, the same logic can be used for both interfaces. For master-type peripherals that operate on a 16-bit data bus, the interface circuit translates the 32-bit data bus to a 16-bit data bus.

The 80960KB processor uses memory-mapped addresses to access I/O devices. This allows the CPU to use many of the same instructions to exchange information for both memory and peripheral devices. Thus, the powerful memory-type instructions can be used to perform 8-, 16-, and 32-bit data transfers.

Chapter 5 describes design guidelines for the I/O interface by examining representative design examples.

#### SUMMARY

The basic hardware system configuration is modular and flexible. The processor, memory, and I/O modules form the natural boundaries in the basic hardware system architecture. The high-bandwidth L-bus that supports burst transfers is used for the data path between the 80960KB processor and other modules.

#### 80960KB SYSTEM ARCHITECTURE

This chapter presents an overview for basic hardware system design. The next three chapters discuss the details of the L-bus, memory modules, and I/O modules.

# CHAPTER 3 THE 80960KB PROCESSOR AND THE LOCAL BUS

The 32-bit multiplexed local bus (L-bus) connects the 80960KB processor to memory and I/O and forms the backbone of any 80960KB processor based system. This high bandwidth bus provides burst-transfer capability allowing up to four successive 32-bit data word transfers at a maximum rate of one word every clock cycle. In addition to the L-bus signals, the 80960KB processor uses other signals to communicate to other bus masters. This chapter, which describes these signals and the associated operations, follows the outline shown below:

- L-bus states and their relationship to each other

- L-bus signal groups, which consist of address/data and control

- L-bus read, write, and burst transactions

- L-bus timing analyses and timing circuit generation

- Related L-bus operations such as arbitration, interrupt, and reset operations

#### **OVERVIEW OF THE 80960KB L-BUS**

The L-bus forms the data communication path between the various components in a basic 80960KB hardware system. The 80960KB processor utilizes the L-bus to fetch instructions, to manipulate information from both memory and I/O devices, and to respond to interrupts. To perform these functions at a high data rate, the 80960KB processor provides a burst mode, which transfers up to four data words at a maximum rate of one 32-bit word per clock cycle. The 80960KB L-bus has the following features:

- 32-bit multiplexed address/data path

- High data bandwidth relative to the speed selection of the 80960KB processor

- Four byte enables and a four-word burst capability that allow transfers from 1 to 16 bytes in length

- Support for TTL latches and buffers.

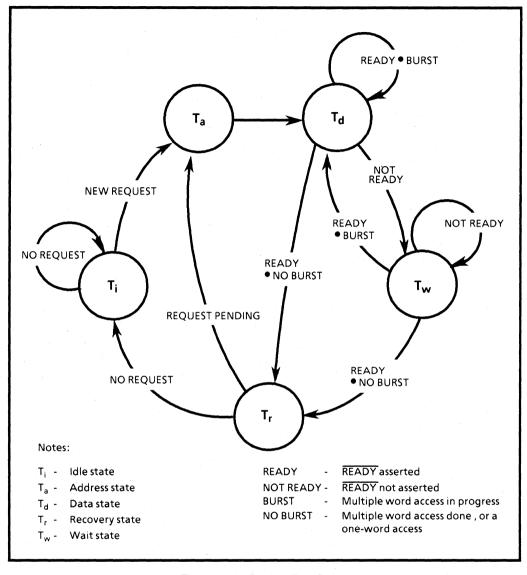

#### **BASIC L-BUS STATES**

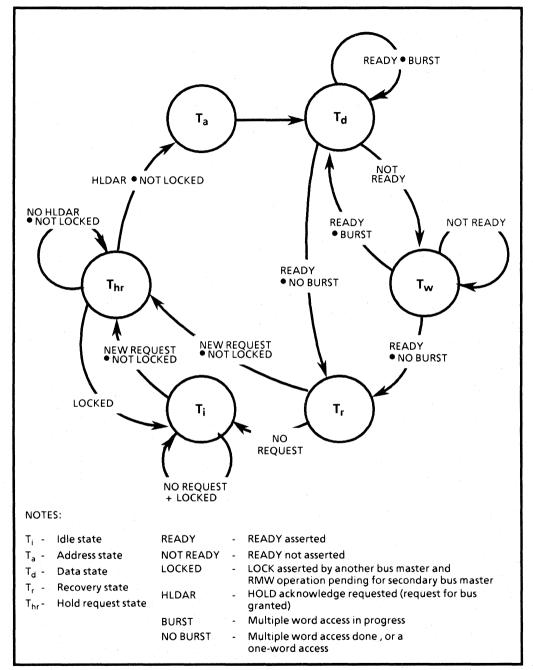

The L-bus has five basic bus states: idle  $(T_i)$ , address  $(T_a)$ , data  $(T_d)$ , recovery  $(T_r)$ , and wait  $(T_w)$ . During system operation, the 80960KB processor continuously enters and exits different bus states as shown in Figure 3-1. This state diagram assumes that only one bus master resides on the L-bus.

The processor occupies the  $T_i$  state when no address/data transfers are in progress. When a new request is received, the 80960KB processor enters the  $T_a$  state to transmit the address.

Figure 3-1: Basic L-Bus States

Following a  $T_a$  state, the 80960KB processor enters a  $T_d$  state to transmit or receive data on the address/data lines provided that the data is ready (indicated by the assertion of  $\overline{READY}$  at the input of the processor). If the data is not ready, the processor enters a  $T_w$  state and remains in this state until data is ready.  $T_w$  states may be repeated as many times as necessary to allow sufficient time for the memory or I/O device to respond.

After a data word is transferred, the 80960KB processor exits the  $T_d$  or  $T_w$  state for a single word transfer or enters the  $T_d$  state again to transfer another data word for a burst transaction. If the next data word is not ready during the next clock cycle for a burst transaction, the processor enters the  $T_w$  state again.

When the 80960KB processor completes the data transfer of all the data words (one or up to four), it enters the recovery  $(T_r)$  state to allow sufficient time for devices (such as memories) on the bus to recover. The processor returns to the  $T_i$  state if no new request is pending, or enters the  $T_a$  state if a new request is pending.

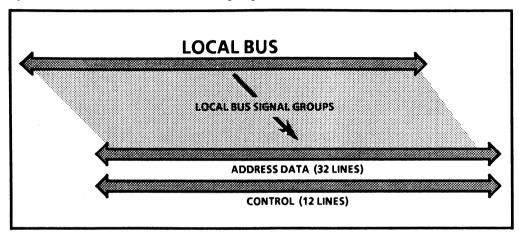

#### L-BUS SIGNAL GROUPS

The L-bus states are used to define some of the L-bus signals. As shown in Figure 3-2, the signals on the L-bus consist of two basic groups: address/data, and control.

Figure 3-2: L-Bus Signal Groups

#### Address/Data

The address/data signal group consists of 32 bidirectional lines. These signals are multiplexed and serve a dual purpose depending upon the bus state.

LAD<sub>31</sub>-LAD<sub>2</sub>

**Local Address/Data**<sub>31</sub> through **Local Address/Data**<sub>2</sub> represent the **address** signals on the L-bus during the  $T_a$  state.  $LAD_2$  is the least significant bit, and  $LAD_{31}$  is the most significant address bit.  $LAD_{31}$  through  $LAD_2$  contain a physical word address.  $LAD_1$  and  $LAD_0$  specify the number of data words to transfer for a burst transaction. The address/data signals float to a high impedance state when not activated.

SIZE  $(LAD_1-LAD_0)$

The **SIZE** signal indicates whether one, two, three, or four words are transferred during the current transaction. During a  $T_a$  state, LAD<sub>1</sub> and LAD<sub>0</sub> represent the word size signals. The encoding is shown in Table 3-1.

Table 3-1: SIZE Signal Decoding

| WORD SELECTION | LAD <sub>1</sub> | LAĎ <sub>0</sub> |

|----------------|------------------|------------------|

| 1 WORD         | LOW              | LOW              |

| 2 WORDS        | LOW              | HIGH             |

| 3 WORDS        | HIGH             | LOW              |

| 4 WORDS        | HIGH             | HIGH             |

$LAD_{31}$ - $LAD_{0}$

**Local Address/Data**<sub>31</sub> through **Local Address/Data**<sub>0</sub> represent the **data** signals on the L-bus during the  $T_d$  and  $T_w$  states.  $LAD_0$  is the least significant, and  $LAD_{31}$  is the most significant address bit. The address/data signals float to a high impedance state when not activated.

#### Control

The control signal group consists of 12 signals that permit the transfer of data. These signals can be used to control data buffers, address latches, and other standard interface logic.

**ALE**

The **Address Latch Enable** is an active low signal that can be used to latch the address from the 80960KB processor.  $\overline{ALE}$  is asserted during the  $T_a$  state and deasserted before the beginning of the  $T_d$  state.  $\overline{ALE}$  floats to a high impedance level when the processor is not operating on the bus (i.e., it is in the idle state), or is at the end of any bus access.

ADS

**Address/Data Status** is an active low signal that is driven by the 80960KB processor to indicate an address state.  $\overline{ADS}$  is asserted during every  $T_a$  state and deasserted during the following  $T_d$  and  $T_w$  states. For a burst transaction,  $\overline{ADS}$  is asserted again every  $T_d$  (and  $T_w$ ) state where  $\overline{READY}$  was asserted in the prior cycle. The  $\overline{ADS}$  signal is an open drain output.

DT/R

**Data Transmit/Receive** indicates the direction of data flow to or from the L-bus. For a read operation or an interrupt acknowledgement,  $DT/\overline{R}$  is low during the  $T_a$ ,  $T_w$ , and  $T_d$  states to indicate that data flows into the 80960KB processor. For a write operation,  $DT/\overline{R}$  is high during the  $T_a$ ,  $T_w$ , and  $T_d$  states to indicate that data flows from the 80960KB processor.  $DT/\overline{R}$  never changes states when  $\overline{DEN}$  is asserted. The  $DT/\overline{R}$  line is an open drain output of the 80960KB processor.

**DEN**

**Data Enable** is an active-low signal that can be used to enable data transceivers.  $\overline{DEN}$  is asserted during all  $T_d$  and  $T_w$  states. The  $\overline{DEN}$  line is an open drain output of the 80960KB processor.

W/R

The **Write/Read** signal instructs a memory or I/O device to write or read data on the L-bus. The 80960KB processor asserts W/ $\overline{R}$  during a  $T_a$  state. The signal remains valid during subsequent  $T_d$  and  $T_w$  states. W/ $\overline{R}$  is an open drain output of the 80960KB processor.

$\overline{BE}_3 - \overline{BE}_0$

The **Byte Enable** output signals of the 80960KB processor specify which bytes (up to four) on the 32-bit data bus are transferred during the transaction. Table 3-2 shows the decoding scheme.

| BYTE ENABLE SIGNAL | ADDRESS LINE SELECTION               |

|--------------------|--------------------------------------|

| BE <sub>0</sub>    | LAD <sub>7-</sub> LAD <sub>0</sub>   |

| BE <sub>1</sub>    | LAD <sub>15-</sub> LAD <sub>8</sub>  |

| BE₂                | LAD <sub>23-</sub> LAD <sub>16</sub> |

| BE₃                | LAD <sub>31-</sub> LAD <sub>24</sub> |

Table 3-2: Byte Enable Signal Decoding

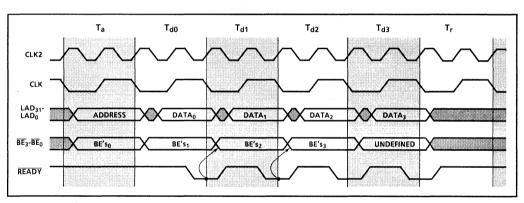

The byte enable signals are valid from the 80960KB processor before data is transferred, as shown in Figure 3-3 (assumes no wait states). The byte enable signals that are valid for the first data word are specified during the  $T_a$  state. For a four-word burst transaction, the byte enable signals that are valid for the second word are asserted during the first data state  $(T_{d0})$ , for the third word during the second data state  $(T_{d1})$ , and for the fourth word during the third data state  $(T_{d2})$ . The byte enable signals are undefined during the last data state  $(T_{d3})$  of the last word transferred.

Figure 3-3: Byte Enable Timing Diagram

Although not shown in the diagram, the byte enable signals of each word are latched internally by the 80960KB processor and remain valid during every data or wait state until  $\overline{READY}$  is applied. After  $\overline{READY}$  is applied the byte enable signals change during the next  $T_d$  state or become undefined for the last data transfer.

The 80960KB processor asserts only adjacent byte enables. For example, the 80960KB processor does not perform a bus operation with only  $\overline{BE}_0$  and  $\overline{BE}_2$  active.

The Byte Enable lines are open drain outputs.

READY

**READY** signal indicates that the data on the L-bus can be sampled (read) or removed (write) by the 80960KB processor. If  $\overline{\text{READY}}$  is not asserted following  $T_a$  state or in between  $T_d$  states, a  $T_w$  state is generated. The  $\overline{\text{READY}}$  is an active-low input signal to the 80960KB processor.

**LOCK**

Bus **Lock** prevents other bus masters from gaining control of the L-bus during a bus operation. It is activated by certain 80960KB processor operations and instructions.

The 80960KB processor uses the bus  $\overline{LOCK}$  signal when it performs a RMW memory operation. When the processor performs a RMW-Read operation, it asserts the  $\overline{LOCK}$  signal during the  $T_a$  state and holds  $\overline{LOCK}$  asserted. If the  $\overline{LOCK}$  signal was already asserted, the processor waits until this signal is deasserted before performing the RMW-Read operation. The processor deasserts the  $\overline{LOCK}$  signal during the  $T_a$  state when it performs a RMW-Write operation.

The 80960KB processor asserts the  $\overline{LOCK}$  signal during the interrupt acknowledge sequence.  $\overline{LOCK}$  is an input and an open drain output.

**CACHE**

The Cacheable signal specifies whether the data is cacheable. If the 80960KB processor asserts CACHE during the  $T_a$  state, then the data is cacheable. The CACHE signal is undefined during the  $T_d$  and  $T_w$  states. The CACHE signal floats to a high impedance state when the L-bus is not acquired.

Table 3-3 summarizes the L-bus signals.

Table 3-3: Summary of L-Bus Signals

| SIGNAL<br>GROUP           | SIGNAL<br>SYMBOL                                  | SIGNAL FUNCTION                           | ACTIVE<br>STATE                                  | DIRECTION | TYPE OF<br>OUTPUT |

|---------------------------|---------------------------------------------------|-------------------------------------------|--------------------------------------------------|-----------|-------------------|

| LOCAL<br>ADDRESS/<br>DATA | ADDRESS<br>(LAD <sub>31</sub> -LAD <sub>2</sub> ) | 32-BIT ADDRESS                            | T <sub>a</sub>                                   | 0         | 3-STATE           |

|                           | DATA<br>(LAD <sub>31</sub> -LAD <sub>0</sub> )    | 32-BIT DATA                               | T <sub>d</sub> , T <sub>w</sub>                  | 1/0       | 3-STATE           |

|                           | SIZE<br>(LAD <sub>1</sub> -LAD <sub>0</sub> )     | SPECIFIES NUMBER OF<br>WORDS TO TRANSFER  | T <sub>a</sub>                                   | 0         | 3-STATE           |

| CONTROL                   | ALE                                               | ENABLES ADDRESS<br>LATCH                  | T <sub>a</sub>                                   | 0         | 3-STATE           |

|                           | ĀDS                                               | IDENTIFIES AN ADDRESS<br>STATE            | $T_a, T_d^1, T_w^1$                              | 0         | OPEN DRAIN        |

|                           | DT∕R                                              | CONTROLS DIRECTION OF DATA FLOW           | T <sub>a</sub> , T <sub>d</sub> , T <sub>w</sub> | 0         | OPEN DRAIN        |

|                           | DEN                                               | ENABLES DATA<br>TRANSCEIVER/LATCH         | T <sub>d</sub> , T <sub>w</sub>                  | 0         | OPEN DRAIN        |

|                           | W/R                                               | READ/WRITE COMMAND                        | T <sub>a</sub> , T <sub>d</sub> , T <sub>w</sub> | 0         | OPEN DRAIN        |

|                           | $\overline{BE}_3\text{-}\overline{BE}_0$          | SPECIFIES WHICH DATA<br>BYTES TO TRANSFER | $T_a, T_d^2, T_w^2$                              | 0         | OPEN DRAIN        |

|                           | READY                                             | INDICATES DATA IS<br>READY TO TRANSFER    | T <sub>d</sub> , T <sub>w</sub>                  | <b>I</b>  |                   |

|                           | <u>LOCK</u>                                       | LOCKS BUS                                 | ANY                                              | 1/0       | OPEN DRAIN        |

|                           | CACHE                                             | INDICATES CACHEABLE<br>TRANSACTION        | T <sub>a</sub>                                   | 0         | 3-STATE           |

Additional pins are used by the 80960KB processor to control the execution of instructions and to interface to other bus masters. These pins include the arbitration, interrupt, error, and reset signals. Each of these signal groups are explained in separate sections.

#### L-BUS TRANSACTIONS

The 80960KB processor uses the L-bus signals to perform transactions, which are simply L-bus operations where data is transferred to (or from) the CPU from (or to) another component. During a transaction, the 80960KB processor can transfer up to four words of data for a single address to enhance system throughput. This is especially useful when loading cache memory.

### **Clock Signal**

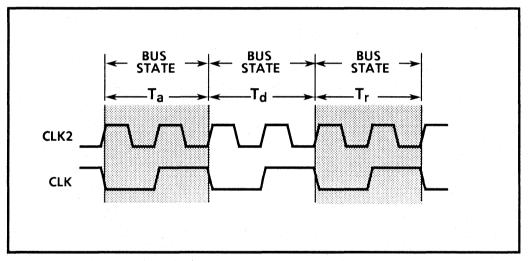

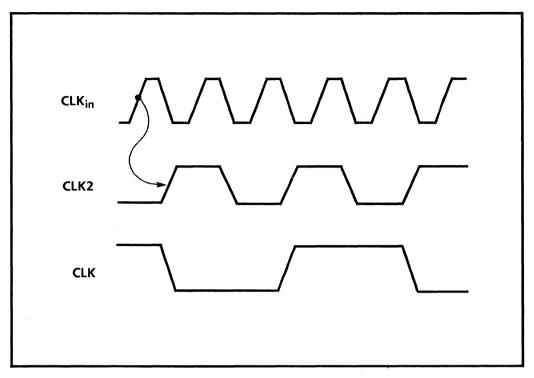

The 80960KB hardware system typically uses two clock signals, CLK2 and CLK, to synchronize the transitions between L-bus states. CLK2 is the clock input to the 80960KB and is double the specified processor frequency. CLK is the clock input signal to the peripheral devices, and it is the operating frequency of the 80960KB processor. Figure 3-4 shows the relationship between the system CLK2 and CLK.

Figure 3-4: Clock Relationships

#### **Basic Read**

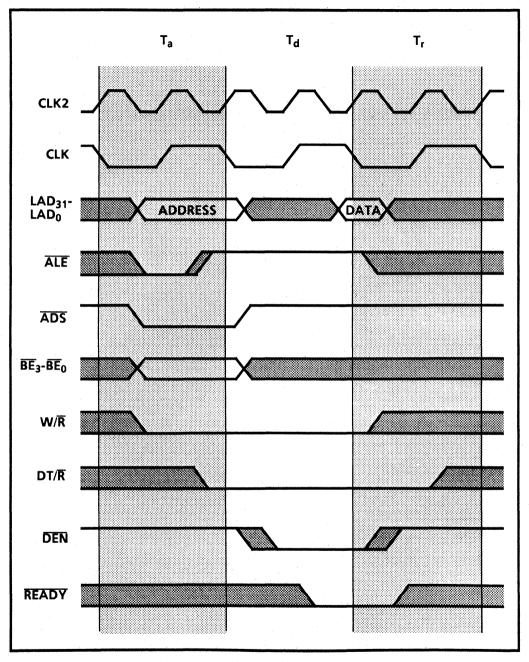

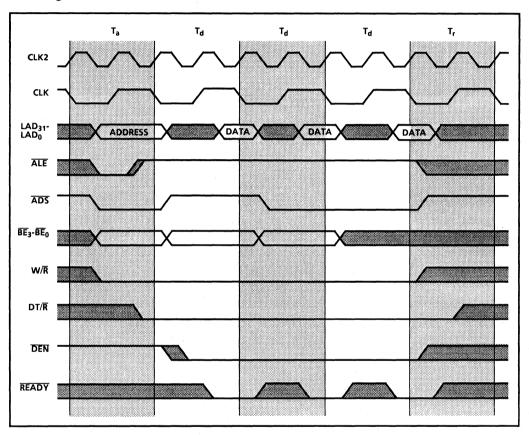

The basic transaction reads or writes one data word. Figure 3-5 shows a typical timing diagram for a basic read transaction (for exact timings, see the 80960KB processor data sheet). A read transaction may be preceded and succeeded by any type of bus transaction. The following sequence of events explains the flow of the timing diagram. For simplicity, no wait states are shown.

- 1. The 80960KB processor generates several signals during the  $T_a$  state.

- It transmits the address on the address/data lines. LAD<sub>1</sub> and LAD<sub>0</sub> specify a single word transaction.

- It asserts ALE. An ALE signal can be used to latch the address.

- It asserts ADS.

- It asserts  $\overline{BE}_3$ - $\overline{BE}_0$  to specify which bytes are used when reading the data word.

- It brings  $W/\overline{R}$  low to denote a read operation.

- It brings  $DT/\overline{R}$  signal low.  $DT/\overline{R}$  can be used for the direction input to data transceivers.

- 2. During the T<sub>d</sub> state, several actions occur.

- The 80960KB processor reads the data on the address/data lines.

- The 80960KB processor asserts  $\overline{DEN}$ .  $\overline{DEN}$  can be used to enable data transceivers.  $\overline{READY}$  is asserted by external timing logic and data is transmitted from the storage devices. If  $\overline{READY}$  is not asserted, the data transfer is delayed generating a  $T_w$  state. The  $T_w$  state is repeated, until  $\overline{READY}$  is asserted.

- 3. The  $T_r$  state follows the data state. This allows the system components adequate time (one processor clock cycle) to remove their outputs from the bus before the 80960KB processor generates the next address on the address/data lines. During the  $T_r$  state  $W/\overline{R}$ ,  $DT/\overline{R}$ , and  $\overline{DEN}$  become inactive.

Figure 3-5: 80960KB Processor Read Transaction

#### **Basic Write**

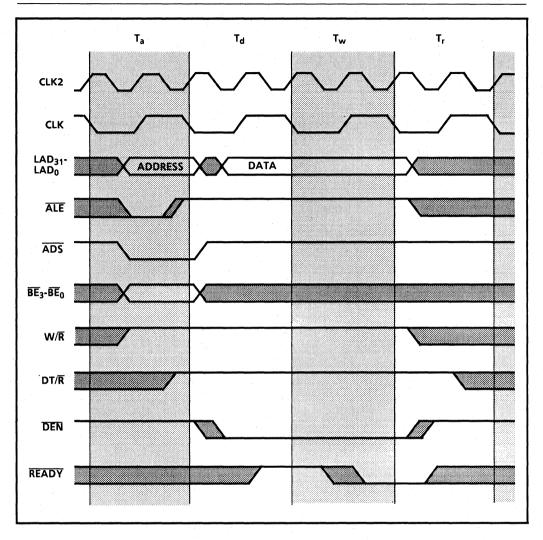

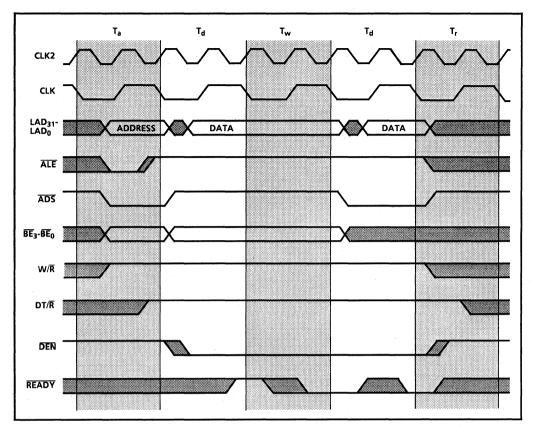

Figure 3-6 shows a typical timing diagram for a basic write transaction with one wait state. Like the read transaction, a write operation may be preceded and succeeded by any type of bus transaction. The following sequence of events explains the flow of the timing diagram.

- 1. Similar to the read transaction, the 80960KB processor generates several signals during the T<sub>a</sub> state.

- It transmits the address on the address/data lines. LAD<sub>1</sub> and LAD<sub>0</sub> specify a single word transaction.

- It asserts ALE. An ALE signal can be used to latch the address.

- It asserts ADS.

- It asserts  $\overline{BE}_3$ - $\overline{BE}_0$  to specify which bytes are used when writing the data word.

- It brings  $W/\overline{R}$  high to denote a write operation.

- It brings DT/R signal high. DT/R can be used for the direction input to data transceivers.

- 2. During the T<sub>d</sub> state, several actions occur.

- The 80960KB places the data on the address/data lines.

- The 80960KB processor asserts  $\overline{DEN}$ .  $\overline{DEN}$  can be used to enable data transceivers.

- READY is not asserted by external timing logic. Consequently, data is held on the LAD lines.

- 3. During the  $T_w$  state  $\overline{READY}$  is asserted and the data is written to the storage device. Note that the  $W/\overline{R}$ ,  $DT/\overline{R}$ , and  $\overline{DEN}$  remain constant until the bus state after  $\overline{READY}$  is asserted.

- 4. The  $T_r$  state follows the wait state. During the  $T_r$  state  $W/\overline{R}$ ,  $DT/\overline{R}$ , and  $\overline{DEN}$  become inactive.

Figure 3-6: 80960KB Processor Write Transaction

### **Burst**

The 80960KB processor supports burst transactions that read or write up to four words at a maximum rate of one word every processor clock cycle. Burst transactions are always contained within a 16-byte boundary. If a transaction crosses a 16-byte boundary, the 80960KB processor automatically splits the transaction into two accesses.

The byte enable signals are valid for each word to allow partial-word write operations for a burst write transaction. The CACHE output signal during a  $T_a$  state applies to all words of a burst transaction.

A burst read or write transaction is similar to a basic read or write operation. It differs primarily in the number of data words transferred: the basic transaction always transfers one data word, the burst transaction transfers up to four data words. For a burst transaction, the byte enable signals are applied during the  $T_a$  state, and subsequently during every  $T_d$  or  $T_w$  state before the data word is transferred. Figure 3-7 shows the timing for a three-word burst read transaction without wait states. Figure 3-8 shows the timing for a two-word burst write transaction with a wait state occurring during the transfer of the first word. Note that the byte enable signals remain constant until the data state after  $\overline{READY}$  is asserted.

Figure 3-7: 80960KB Processor Burst Read Transaction

Figure 3-8: 80960KB Processor Burst Write Transaction

#### TIMING GENERATION

In an 80960KB processor-based system, timing signals must be generated for the clock and reset inputs. To generate these signals, discrete logic should be utilized to minimize skew and maintain the rise and fall times as short as possible. This section describes a typical circuit that synthesizes the clock signal. The RESET timing generation is discussed in the "RESET and Initialization" section on page 3-33.

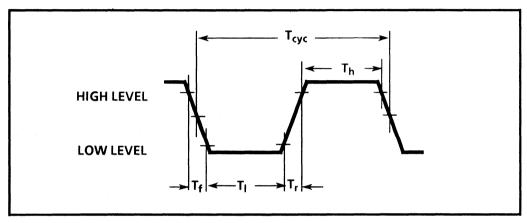

### **80960KB Processor Clock Requirements**

In order to design a clock generator, the clock input specifications to the 80960KB processor are examined first. The clock (CLK2) waveform is shown in Figure 3-9. The clock pulse is specified by five parameters listed below:

- The clock fall time (t<sub>f</sub>)

- The clock low time (t<sub>1</sub>)

- The clock rise time (t<sub>r</sub>)

- The clock high time (t<sub>h</sub>)

- The clock period (t<sub>cvc</sub>)

The time required to go from 90% of the difference between the high and low voltage levels to 10% of the difference (or from low to high) is defined as the clock fall (rise) time. The clock low time specifies the time required for the clock to remain within 10% of the low voltage level. Similarly, the clock high time specifies the required time for the clock pulse to remain within 10% of the high voltage level. The clock period is the sum of  $t_f + t_l + t_r + t_h$ .

Figure 3-9: System Clock Pulse

The clock generator must have fast enough rise and fall times to comply with the requirements for high and low time and the overall clock period. For example, consider a clock pulse with a 50% duty cycle at 40 MHz. The clock period is specified at minimum of 25 ns, low time at minimum of 8 ns, and high time at minimum of 8 ns. This implies that the sum of the rise and fall time must not be greater than 9 ns. Thus, the clock generator should be designed to have rise and fall times not greater than 4.5 ns each.

Besides specifying a maximum clock rate, the 80960KB processor requires a minimum CLK2 rate of 8 MHz to maintain the state of the internal dynamic cells. Due to this minimum frequency requirement, the 80960KB processor cannot be single-stepped by disabling the clock.

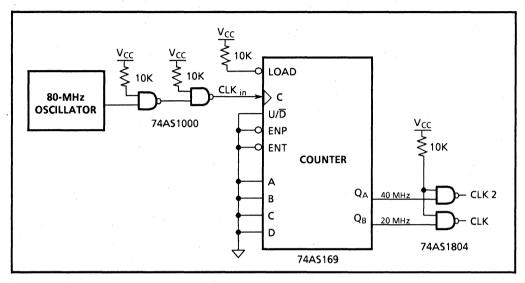

#### **Clock Generation**

Figure 3-10 shows an example of a clock generator that produces two clock pulses, one double the frequency of the other with the skew between the pulses in the range of 1 to 3 ns. This particular circuit produces a 40-MHz clock at 50% duty cycle with rise and fall times of less than 4 ns. The circuit design consists of four devices: an oscillator, a pulse shaping network, a synchronous up/down counter, and a NAND gate driver. The output of the 80-MHz hybrid clock oscillator connects to the pulse shaping network (two NAND gates in series), which in turn feeds into the clock input of the up/down counter. This counter produces a 40-MHz CLK2 output signal and a 20-MHz CLK output signal. Because the outputs of the counter are

synchronous, the skew between CLK2 and CLK is typically less than 2 ns. To provide adequate signal margin and maintain fast rise and fall times, the two clock signals are conditioned by the NAND gate driver. The timing waveforms of the clock circuit are shown in Figure 3-11.

If the opposite phase CLK is preferred,  $U/\overline{D}$  pin can be connected to  $V_{\rm CC}$ .

Figure 3-10: Clock Generation Circuit

Figure 3-11: Clock Timing Waveforms

The hybrid clock oscillator typically requires 5 ms to stabilize after power is applied. The 80960KB processor cannot begin to execute instructions until after the clock and  $V_{CC}$  have reached their DC and AC specifications. The RESET signal can be used to control the start of the CPU execution when power is applied. This is discussed in the "RESET and Initialization" section on page 3-33.

#### **ARBITRATION**

When multiple bus masters exist, an arbitration protocol is used to exchange control of the bus. The protocol assumes that there are two bus masters: one that controls the bus by default, and the other that requests control of the bus when it performs an operation, such as a DMA controller. More than two bus masters may exist on the L-bus, but this requires external arbitration logic. There should be no more than two 80960KB processors, however, on an L-bus.

Assuming that there are only two bus masters, this section examines the bus arbitration, bus states, and timing diagrams for different combinations of bus masters, as shown in Table 3-4.

|        | Bus Master Combination                         |                                               |  |  |

|--------|------------------------------------------------|-----------------------------------------------|--|--|

|        | Bus Master that Controls the Bus<br>by Default | Bus Master that Requests<br>Contol of the Bus |  |  |

| CASE 1 | 80960KB PROCESSOR                              | I/O DEVICE                                    |  |  |

| CASE 2 | 80960KB PROCESSOR                              | 80960KB PROCESSOR                             |  |  |

| CASE 3 | I/O DEVICE                                     | 80960KB PROCESSOR                             |  |  |

Table 3-4: Combination of Bus Masters

### Single 80960KB Processor on the L-Bus

For the first case, the 80960KB processor controls the L-bus, and a master I/O peripheral, such as a DMA controller, requests control of the bus for operations. The 80960KB processor and the I/O peripheral exchange control of the bus with two signals: the hold request (HOLD) and hold acknowledge (HLDA) signals.

HOLD is an input signal of the 80960KB processor, which indicates that the master I/O peripheral is requesting control of the L-bus. When HOLD is asserted, the 80960KB processor surrenders control of the bus after it completes the current bus transaction. The 80960KB processor acknowledges transfer of control of the L-bus to the other bus master by asserting the HLDA.

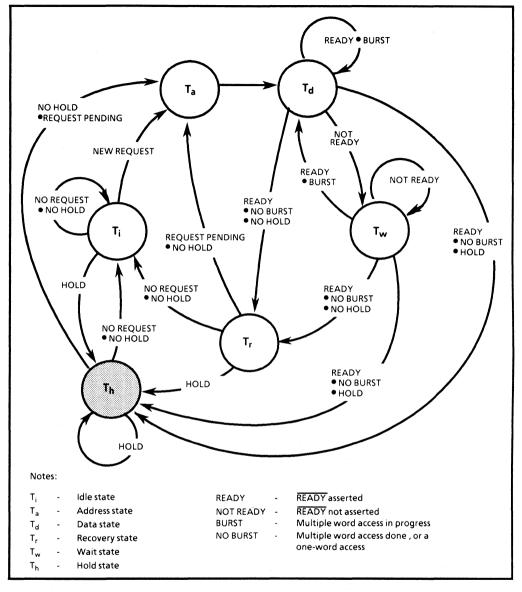

## State Diagram

Figure 3-12 shows the state diagram for a L-bus with an I/O peripheral bus master. This state diagram consists of the hold state  $(T_h)$  in addition to the five basic states described in the "Basic L-Bus State" section on page 3-1. The 80960KB processor enters the  $T_h$  state when it surrenders the control of the bus. It can enter the  $T_h$  state from the  $T_i$  or  $T_r$  state. When the 80960KB processor regains control of the L-bus, it enters the  $T_a$  state if a new request is pending or a  $T_i$  state if no new request is pending.

Figure 3-12: L-Bus States with Arbitration

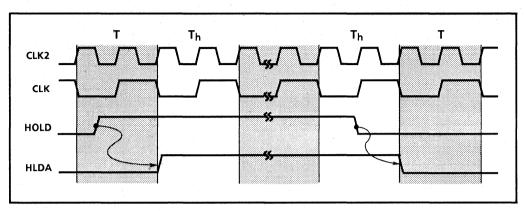

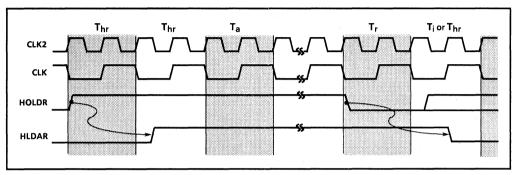

# **Arbitration Timing**

Figure 3-13 shows the arbitration timing diagram. The "T" state represents the last cycle of a transaction in which the  $\overline{READY}$  signal was asserted or a  $T_i$  state. The 80960KB processor receives a request to relinquish control of the bus when HOLD is asserted. After the 80960KB processor completes the current transaction, it responds to this request by floating the three-state output signals and deasserting the open drain output signals. The HLDA output signal,

however, remains active and is asserted as the 80960KB processor enters a  $T_h$  state. During the  $T_h$  state, the CPU ignores all input signals except HOLD and RESET. When the HOLD input signal is deasserted, the 80960KB processor exits the  $T_h$  state and deasserts HLDA.

Figure 3-13: Arbitration Timing Diagram for a Bus Master

#### Two 80960KB Processors on the L-Bus

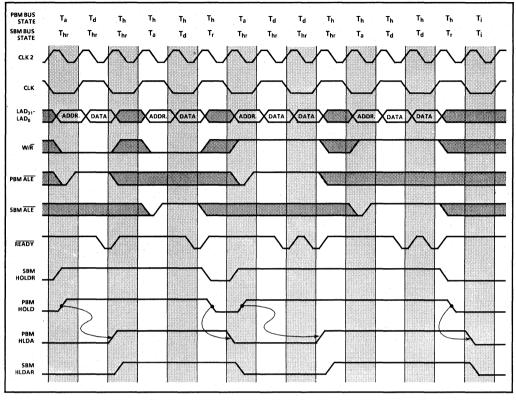

For the next case, two 80960KB processors reside on the L-bus. During initialization, one is designated as the Primary Bus Master (PBM), the other as the Secondary Bus Master (SBM). The exchange protocol that is used guarantees that neither device is kept off the bus indefinitely. The 80960KB processors use two pins for bus arbitration: the HOLD input pin, and the HLDA output pins. These input and output pins for the SBM are interpreted differently, however.

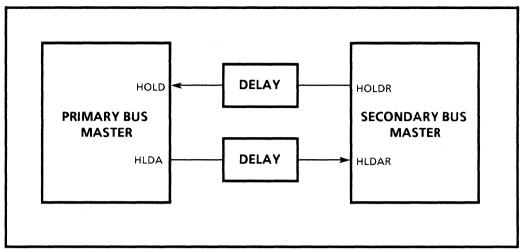

When the SBM is initialized, the pin normally used for HOLD input signal is interpreted as the hold acknowledge request (HLDAR) input signal. The assertion of HLDAR indicates that the PBM relinquished control of the L-bus. Similarly, the HLDA output signal of the SBM is interpreted as the hold request (HOLDR) output signal. The SBM asserts HOLDR to request acquisition of the L-bus. Thus, bus arbitration between two 80960KB processors can be accomplished by connecting HOLD of the PBM to HOLDR of the SBM, and HLDA of the PBM to the HLDAR of the SBM, as shown in Figure 3-14.

When using the connection shown in Figure 3-14, a delay must be inserted between the input and output signals because the minimum clock-to-output delay is less than the maximum hold time of the input signals. The delay time must be greater than 5 ns, but less than the clock period minus the setup time minus the maximum clock-to-output delay (5 ns  $\leq$  Delay  $\leq$  T<sub>Period</sub> - T<sub>Setup</sub> - T<sub>Clock-to-Output</sub>).

Figure 3-14: Arbitration Connection Between Two 80960KB Processors

#### Bus states for Two 80960KB Processors

The state diagram for the SBM is shown in Figure 3-15. Because there are two 80960KB processors, the  $\overline{LOCK}$  signal is included in the state diagram. The SBM requests control of the L-bus by asserting HOLDR and subsequently enters the hold request  $(T_{hr})$  state provided that the bus is not locked (locked means that  $\overline{LOCK}$  is asserted by the PBM and the SBM has a RMW operation pending). The SBM remains in the  $T_{hr}$  state until it acquires control of the L-bus by receiving HLDAR. The SBM returns to the  $T_i$  state by deasserting HOLDR provided that the following two conditions exist:

- A RMW operation is pending

- The PBM asserted  $\overline{LOCK}$  while the SBM was in the  $T_{hr}$  state.

The SBM gains control of the bus when HLDAR is asserted provided that the bus is not locked. After gaining control of the L-bus, the SBM performs the operations, and enters a  $T_w$  state if necessary. At the end of a transaction, the SBM goes to the  $T_r$  state and deasserts HOLDR for at least one processor clock cycle to allow another peripheral bus master to gain access if needed. If another request is pending, the SBM enters the  $T_{hr}$  state and asserts HOLDR provided the bus is not locked. The PBM never forces the SBM off the bus.

Figure 3-15: L-Bus States for Secondary Bus Master

### Arbitration Timing for Two 80960KB Processors on the L-Bus

Figure 3-16 shows the timing diagram for acquiring and relinquishing the L-bus by an SBM. The SBM enters into the Hold Request  $(T_{hr})$  state and asserts the HOLDR signal. It remains in the  $T_{hr}$  state until HLDAR is asserted, which indicates that the SBM can utilize the L-bus during the next state. When the bus is no longer required, HOLDR is deasserted during the state following the last  $\overline{READY}$  signal. Except for HOLDR, the output signals of the SBM go into a high impedance state or are deasserted for the case of open-drain outputs.

Figure 3-16: Arbitration Timing Diagram for an SBM

### Bus Exchange Example Between Two 80960KB Processors

Figure 3-17 shows an example of bus arbitration between a PBM and an SBM using the arbitration signals. Each bus master performs a one-word read and a two-word write transaction to demonstrate the fastest possible bus exchanges.

Figure 3-17: Example of a Bus Exchange Transaction

While the PBM is performing a read transaction, the SBM requests control of the L-bus by asserting HOLDR and entering the  $T_{\rm hr}$  state. It remains in this state until the PBM grants the request by asserting HLDA after the read transaction is completed. After granting the request, the PBM enters the  $T_{\rm h}$  state and remains in this state until its HOLD signal is deasserted. When the SBM completes the read transaction, it deasserts HOLDR and gives control back to the PBM.

The PBM now performs a two-word write transaction after deasserting the HLDA. The SBM requests control of the bus again by asserting the HOLDR signal and enters the  $T_{hr}$  state. When the PBM completes the two-word write transaction, it grants the request by asserting HLDA and enters the  $T_h$  state. The SBM receives the signal on the HLDAR input and performs a two-word write transaction. When the SBM completes the transaction, the control of the L-bus is transferred to the PBM, and both the PBM and the SBM enter the  $T_i$  state.

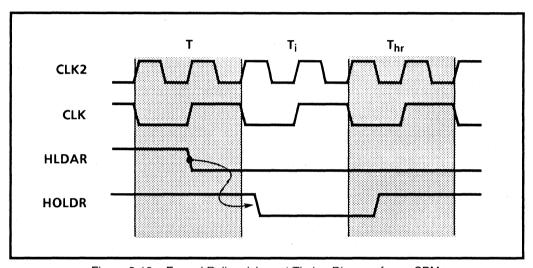

# A Peripheral Device As the Default Bus Master

Another case exists where a peripheral device controls the L-bus, and the 80960KB processor requests control of the bus to perform operations. This alternative is not advisable because it hinders system performance. The exchange protocol is identical to the one described in the

previous section. The 80960KB processor is an SBM and uses two pins for bus arbitration: the HOLDR input pin and the HLDAR output pin. The state diagram is similar to the one shown in Figure 3-15. The lock conditions are not used for this case, however.

The peripheral device grants control of the L-bus bus asserting HLDAR when the SBM requests use of the L-bus. The peripheral device can obtain control of the L-bus again by deasserting HLDAR. If this occurs, the 80960KB processor surrenders control of the bus after it completes the current transaction, as shown in Figure 3-18. At that time, the 80960KB processor deasserts the HOLDR signal and places the other output signals into a high impedance state or a deasserted open drain level. The 80960KB processor may request access to the L-bus by asserting HOLDR again.

Figure 3-18: Forced Relinquishment Timing Diagram for an SBM

# **INTER-AGENT COMMUNICATION (IAC)**

The IAC mechanism gives 80960KB processors the capability to send and receive messages to one another and to other bus agents. The IAC mechanism is essentially a non-maskable interrupt with pre-defined service routines. These routines are implemented in the 80960KB processor and are used to perform control functions such as purging the instruction cache, setting breakpoint registers, or stopping and starting the processor. By using IAC messages, external agents can remotely control the 80960KB. This allows easy integration of the 80960KB into system environments.

IAC messages can also be used to generate interrupts that behave exactly the same as hardwired interrupts. Since the interrupt vector is encoded in the IAC message, any of the 248 possible interrupt service routines can be invoked. For further information on IAC message definitions see the 80960KB CPU Programmer's Reference Manual.

### **Overview of IAC Operations**