# Intel 21554 Embedded PCI-to-PCI Bridge for the VMICPCI-7697 CompactPCI CPU

**Product Manual**

Volume II Preliminary Draft

#### COPYRIGHT AND TRADEMARKS

© Copyright July 1998. The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC's products to improve reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC's Standard Conditions of Sale.

AMXbus, BITMODULE, COSMODULE, DMAbus, Instant OPC wizard logo, IOWorks Access, IOWorks Foundation, IOWorks man figure, IOWorks Manager, IOWorks Server, MAGICWARE, MEGAMODULE, PLC ACCELERATOR (ACCELERATION), Quick Link, RTnet, Soft Logic Link, SRTbus, TESTCAL, "The Next Generation PLC", The PLC Connection, TURBOMODULE, UCLIO, UIOD, UPLC, Visual Soft Logic Control(Ier), VMEaccess, VMEmanager, VMEmonitor, VMEnet, VMEnet II, and VMEprobe are trademarks of VMIC.

(I/O man figure)

(Instant OPC wizard logo)

(IOWorks man figure)

The I/O man figure, IOWorks, UIOC, Visual IOWorks, and WinUIOC are registered trademarks of VMIC.

ActiveX is a trademark and Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, Windows NT, and XENIX are registered trademarks of Microsoft Corporation.

MMX is a trademark and Pentium is a registered trademark of Intel Corporation.

PICMG and CompactPCI are registered trademarks of PCI Industrial Computer Manufacturers' Group.

Other registered trademarks are the property of their respective owners.

This document is reprinted by permission of Intel Corporation, Copyright Intel Corporation 1995.

#### **VMIC**

#### All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless granted express written permission from VMIC.

# VMICPCI-7697 Serial ROM for the 21554

# Introduction

The VMICPCI-7697 is shipped with a default configuration for the SROM used to load the 21554 Embedded PCI bridge chip at power up and reset.

The contents of the SROM are as follows:

#### VMICPCI-7697 21554 SROM Code

;Preload enable (bit 7 set for preload enable)

:00 80

:01 00

:02 00

:03 00

;Primary Class Code

:04 00

:05 80

:06 06

;Subvendor IDs

:07 97

:08 76

:09 4A

:0A 11

;Primary Min GNT, Max Lat

:0B 00 :0C 00

# VMICPCI-7697 21554 SROM Code (Continued)

```

;Secondary Class Code

:0D 00

:0E 80

:0F 06

;Secondary Min GNT, Max Lat

:10 00

:11 00

;Downstream Mem 0 - CSRs only (Set a 4K window size) FFFFF000

:12 00

:13 F0

:14 FF

:15 FF

;Downstream Mem 1 or I/O (Set 256 byte I/O window size) FFFFF01

:16 01

:17 FF

:18 FF

:19 FF

;

Downstream Mem 2 (Set 1 MB memory window size) FFF00000

:1A 00

:1B 00

:1C F0

:1D FF

;Downstream Mem 3

:1E 00

:1F 00

:20 00

:21 00

;Downstream Mem 3 Upper 32

:22 00

:23 00

:24 00

:25 00

```

# VMICPCI-7697 21554 SROM Code (Continued)

```

;Expansion ROM (Set 1 MB expansion ROM size)

:26 01

:27 F0

;Upstream Mem 0 or I/O (Set 256 byte I/O window size) FFFFFF01

:28 01

:29 FF

:2A FF

:2B FF

;Upstream Mem 1 (Set 256 MB memory window size) F0000000

:2C 00

:2D 00

:2E 00

:2F F0

;Chip Control 0

:30 00

;Clear lockout bit

:31 00

;Chip Control 1

:32 00

;LUT disable, I2O disable

:33 90

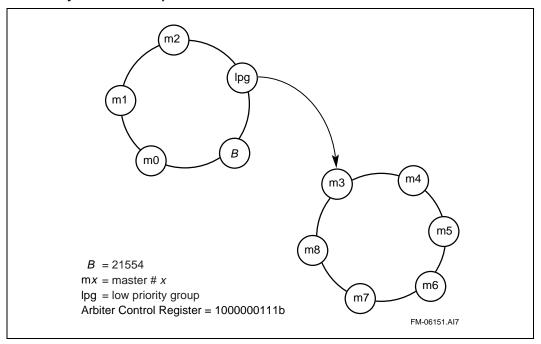

;Arbiter control (Sets internal 21554 secondary bus req. to high priority ring)

:34 00

:35 02

;System error disable

:36 00

:37 00

;Power management

:38 00

:39 00

:3A 00

```

## VMICPCI-7697 21554 SROM Code (Continued)

:3B 00

:3C 00

:3D 00

:3E 00

:3F 00

:40 00

:41 00

:42 00

Upstream or Outbound means going out to the CPCI backplane from the local processor, Downstream or Downstream or inbound means coming into the local CPU bus from the CPCI backplane.

The CPCI-7697, 21554 bridge will be programmed as follows:

The outbound memory window is 256MBytes, inbound is 1MByte.

Both I/O windows are 256 bytes, inbound and outbound.

Address translation registers power up at 0 values such that the mapping forces the absolute address to 0 for outbound and inbound memory and I/O windows.

The user MUST load program the translation offset registers if a value other than Zero is required.

## **Intel Corporation Reprint Information**

All of the following material in this manual was provided by Intel Corporation and is reprinted here within with permission. No corrections or updates were made by VMIC.

# 21554 PCI-to-PCI Bridge for Embedded Applications

**Hardware Reference Manual**

September 1998

Order Number: 278091-001

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 21554 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1998

\*Third-party brands and names are the property of their respective owners.

| 1 | Prefa                                                               | e                                                                       | 1-                                                                                                                                | -1                                                         |

|---|---------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

|   | 1.1<br>1.2                                                          | Manual Organization                                                     | 1-<br>1-<br>1-<br>1-<br>1-                                                                                                        | -2<br>- <b>2</b><br>- <b>2</b><br>- <b>2</b><br>- <b>2</b> |

| 2 | Intro                                                               | uction                                                                  | 2-                                                                                                                                | -1                                                         |

|   | 2.1<br>2.2<br>2.3                                                   | Features Comparing 21554 and Standard PCI-to-PCI Architectural Overview | Bridge2-                                                                                                                          | -4                                                         |

| 3 | Sign                                                                | Pins                                                                    | 3-                                                                                                                                | -1                                                         |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10 | Primary PCI Bus Interface Signals                                       | Signals       3-         on Signals       3-         3-       3-         3-       3-1         3-1       3-1         3-1       3-1 | -5<br>-6<br>-9<br>-9<br>10<br>11                           |

| 4 | PCI E                                                               | us Operation                                                            | 4-                                                                                                                                | -1                                                         |

|   | 4.1                                                                 | PCI Bus Operation                                                       | 4-<br>2 Transactions                                                                                                              | -1<br>-2<br>-2<br>-3<br>-3                                 |

|   |                                                                     | 4.1.3.3 Prefetchable Read Transact 64-bit Extension                     | 4-<br>4-<br>4-<br>ions Using the                                                                                                  | -5<br>-6<br>-6                                             |

|   |                                                                     | 4.1.3.4 Read Performance Features 4.1.4 Target Terminations             | 4-<br>ed by the 215544-                                                                                                           | -8<br>-8                                                   |

|   |                                                                     | 4.1.5 Ordering Rules                                                    | •                                                                                                                                 |                                                            |

| 5 | Add | ress De    | coding                                                                                                                         | 5–1  |

|---|-----|------------|--------------------------------------------------------------------------------------------------------------------------------|------|

|   | 5.1 | 21554      | CSR Address Decoding                                                                                                           | 5–1  |

|   | 5.2 | Expans     | sion ROM Address Decoding                                                                                                      | 5–1  |

|   | 5.3 | Memor      | ry Transaction Address Decoding                                                                                                | 5–2  |

|   |     | 5.3.1      | Using the BAR Setup Registers                                                                                                  | 5–2  |

|   |     | 5.3.2      | Direct Address Translation                                                                                                     |      |

|   |     | 5.3.3      | Lookup Table Based Address Translation                                                                                         | 5–6  |

|   |     |            | 5.3.3.1 Lookup Table Entry Format                                                                                              | 5–8  |

|   |     | 5.3.4      | Forwarding of 64-Bit Address Memory Transactions                                                                               | 5–8  |

|   | 5.4 | I/O Tra    | Insaction Address Decoding                                                                                                     |      |

|   |     | 5.4.1      | Indirect I/O Transaction Generation                                                                                            |      |

|   |     | 5.4.2      | Subtractive Decoding of I/O Transactions                                                                                       | 5–11 |

|   | 5.5 | 21554      | Base Address Register Summary                                                                                                  | 5–11 |

| 6 | Con | figuration | on Accesses                                                                                                                    | 6–1  |

|   | 6.1 | Type 0     | Accesses to the 21554 Configuration Space                                                                                      | 6–1  |

|   | 6.2 |            | on of Configuration Transactions by 21554                                                                                      |      |

| _ |     |            | ,                                                                                                                              |      |

| 7 | Con | riguration | on Space Registers                                                                                                             | 7–1  |

|   | 7.1 | Config     | uration Space Address Map                                                                                                      | 7–2  |

|   | 7.2 | Config     | uration Register Description                                                                                                   | 7–5  |

|   |     | 7.2.1      | Shared Standard PCI Registers                                                                                                  |      |

|   |     |            | 7.2.1.1 Vendor ID Register                                                                                                     |      |

|   |     |            | 7.2.1.2 Device ID Register                                                                                                     |      |

|   |     |            | 7.2.1.3 Revision ID (RevID) Register                                                                                           |      |

|   |     |            | 7.2.1.4 BiST Register                                                                                                          |      |

|   |     |            | 7.2.1.5 Header Type Register                                                                                                   |      |

|   |     |            | 7.2.1.7 Subsystem ID Register                                                                                                  |      |

|   |     | 7.2.2      | Primary and Secondary Standard PCI Registers                                                                                   |      |

|   |     |            | 7.2.2.1 Primary and Secondary Command Registers                                                                                |      |

|   |     |            | 7.2.2.2 Primary and Secondary Status Registers                                                                                 |      |

|   |     |            | 7.2.2.3 Primary and Secondary Class Code Registers                                                                             |      |

|   |     |            | <ul><li>7.2.2.4 Primary and Secondary Cache Line Size Registers</li><li>7.2.2.5 Primary Latency and Secondary Master</li></ul> |      |

|   |     |            | Latency Timer Registers                                                                                                        | 7–11 |

|   |     |            | 7.2.2.6 Primary and Secondary Interrupt Line Registers                                                                         |      |

|   |     |            | 7.2.2.7 Primary and Secondary Interrupt Pin Registers                                                                          |      |

|   |     |            | 7.2.2.8 Primary and Secondary Minimum Grant Registers                                                                          |      |

|   |     |            | 7.2.2.9 Primary and Secondary Maximum Latency Registers                                                                        |      |

|   |     |            | 7.2.2.10Enhanced Capabilities Pointer Register                                                                                 |      |

|   |     |            | 7.2.2.11Power Management Capability ID Register                                                                                |      |

|   |     |            | 7.2.2.13Power Management Capabilities Register                                                                                 |      |

|   |     |            | 7.2.2.14Power Management Control and Status Register                                                                           |      |

|   |     |            | 7.2.2.15PMCSR Bridge Support Extensions                                                                                        |      |

|   |     |            | 7.2.2.16Power Management Data Register                                                                                         |      |

|   |     |            | 7.2.2.17Vital Product Data (VPD) ECP Register                                                                                  |      |

|   |     |            | 7.2.2.18Vital Product Data (VPD) Next Pointer Register                                                                         | 7–16 |

|   |     |            | 7.2.2.19Vital Product Data (VPD) Address Register                                                                              |      |

|   |     |            | 7.2.2.20VPD Data Register                                                                                                      |      |

|   |     |            | 7.2.2.21Compact PCI Hot-Swap Capability Identifier Register                                                                    | /–17 |

|   |      |         | 7.2.2.23Compact PCI Hot-Swap Control Register            |      |

|---|------|---------|----------------------------------------------------------|------|

|   |      | 7.2.3   | Primary and Secondary Address Registers                  |      |

|   |      | 1.2.0   | 7.2.3.1 Primary CSR and Downstream Memory 0              |      |

|   |      |         | Base Address Register                                    | 7_10 |

|   |      |         | 7.2.3.2 Secondary CSR Memory Base Address Registers      | 7-20 |

|   |      |         | 7.2.3.3 Primary and Secondary CSR I/O Base Address       |      |

|   |      |         | Register                                                 | 7–20 |

|   |      |         | 7.2.3.4 Downstream I/O or Memory 1 and Upstream          |      |

|   |      |         | I/O or Memory 0 BAR                                      | 7–21 |

|   |      |         | 7.2.3.5 Downstream Memory 2 and 3 BAR, Upstream          |      |

|   |      |         | Memory 1 BAR                                             | 7–22 |

|   |      |         | 7.2.3.6 Upper 32 Bits Downstream Memory 3 Base           |      |

|   |      |         | Address Register                                         | 7–23 |

|   |      |         | 7.2.3.7 Upstream Memory 2 Base Address Register          | 7–23 |

|   |      |         | 7.2.3.8 Primary Expansion ROM Base Address Register      | 7–24 |

|   |      |         | 7.2.3.9 Downstream I/O or Memory 1 and Upstream          |      |

|   |      |         | I/O or Memory 0 Translated Base Register                 | 7–25 |

|   |      |         | 7.2.3.10Downstream Memory 0, 2, 3, and Upstream          |      |

|   |      |         | Memory 1 Translated Base Register                        | 7–26 |

|   |      |         | 7.2.3.11Downstream I/O or Memory 1 and Upstream          |      |

|   |      |         | I/O or Memory 0 Setup Registers                          | 7–27 |

|   |      |         | 7.2.3.12Downstream Memory 0, 2, 3, and Upstream          |      |

|   |      |         | Memory 1 Setup Registers                                 | 7–28 |

|   |      |         | 7.2.3.13Upper 32 Bits Downstream Memory 3 Setup Register |      |

|   |      |         | 7.2.3.14Primary Expansion ROM Setup Register             |      |

|   |      | 7.2.4   | Configuration Transaction Generation Registers           | 7–30 |

|   |      |         | 7.2.4.1 Downstream and Upstream Configuration            |      |

|   |      |         | Address Registers                                        | 7–30 |

|   |      |         | 7.2.4.2 Downstream Configuration Data and Upstream       | 7.04 |

|   |      |         | Configuration Data Registers                             |      |

|   |      |         | 7.2.4.3 Configuration Own Bits Register                  | 7-32 |

|   |      | 705     | 7.2.4.4 Configuration Control and Status Register        |      |

|   |      | 7.2.5   | Device-Specific Control and Status Registers             |      |

|   |      |         | 7.2.5.1 Chip Control 0 Register                          | 7–34 |

|   |      |         | 7.2.5.2 Chip Control 1 Register                          | 7-37 |

|   |      |         | 7.2.5.3 Reset Control Register                           | 7–39 |

|   |      |         | 7.2.5.4 Chip Status Register                             | 7-40 |

|   |      |         | 7.2.5.5 Arbiter Control Register                         |      |

|   |      |         | 7.2.5.6 Primary SERR# Disable Register                   |      |

|   | 7.0  | Carial  | 7.2.5.7 Secondary SERR# Disable Register                 |      |

|   | 7.3  | Senai   | ROM Configuration Data Preload Format                    |      |

| 3 | Cont | rol and | d Status Registers                                       | 8–1  |

|   | 8.1  | CSR A   | Address Map                                              | 8–2  |

|   | 8.2  |         | Descriptions                                             |      |

|   | 0    | 8.2.1   | I/O and Configuration Transaction Generation Registers   |      |

|   |      | 0.2.1   | 8.2.1.1 Downstream /Upstream Configuration Address       |      |

|   |      |         | and Data, Control, Status Registers                      | 8_4  |

|   |      |         | 8.2.1.2 Downstream I/O Address and Upstream I/O          |      |

|   |      |         | Address Registers                                        | 8–5  |

|   |      |         | 8.2.1.3 Downstream I/O Data and Upstream I/O Data        |      |

|   |      |         | Registers                                                | 8–5  |

|   |      |         | 8.2.1.4 I/O Own Bits Registers                           | 8–6  |

|   |      |         | 3                                                        |      |

|    |       |          | 8.2.1.5 I/O Control and Status Register                                                                                              | 8–8  |

|----|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------|------|

|    |       | 8.2.2    | 8.2.1.7 Lookup Table Data Register                                                                                                   |      |

|    |       | 0.2.2    | 8.2.2.1 I2O Inbound Queue                                                                                                            |      |

|    |       |          | 8.2.2.2 I2O Outbound Queue                                                                                                           |      |

|    |       |          | 8.2.2.3 I2O Outbound Post List Status                                                                                                |      |

|    |       |          | 8.2.2.4 I2O Outbound Post_List Interrupt Mask                                                                                        |      |

|    |       |          | 8.2.2.5 I2O Inbound Post_List Status                                                                                                 |      |

|    |       |          | 8.2.2.6 I2O Inbound Post_List Interrupt Mask                                                                                         |      |

|    |       |          | 8.2.2.7 I2O Inbound Free_List Head Pointer                                                                                           |      |

|    |       |          | 8.2.2.8 I2O Inbound Post_List Tail Pointer                                                                                           |      |

|    |       |          | 8.2.2.9 I2O Outbound Free_List Tail Pointer                                                                                          |      |

|    |       |          | 8.2.2.10I2O Outbound Post_List Head Pointer                                                                                          |      |

|    |       |          | 8.2.2.11I2O Inbound Post_List Counter                                                                                                |      |

|    |       |          | 8.2.2.12I2O Inbound Free_List Counter                                                                                                |      |

|    |       |          | 8.2.2.13I2O Outbound Post_List Counter                                                                                               |      |

|    |       | 0.00     | 8.2.2.14I2O Outbound Free_List Counter                                                                                               |      |

|    |       | 8.2.3    | Address Registers                                                                                                                    |      |

|    |       | 0.0.4    | 8.2.3.1 Upstream Memory 2 Lookup Table                                                                                               |      |

|    |       | 8.2.4    | Interrupt Registers                                                                                                                  | 8–15 |

|    |       |          | 8.2.4.1 Primary Clear IRQ and Secondary Clear IRQ                                                                                    | 0.45 |

|    |       |          | Registers                                                                                                                            |      |

|    |       |          | <ul><li>8.2.4.2 Primary Set IRQ and Secondary Set IRQ Registers</li><li>8.2.4.3 Primary Clear IRQ Mask and Secondary Clear</li></ul> | 0–10 |

|    |       |          | IRQ Mask Registers                                                                                                                   | 8_16 |

|    |       |          | 8.2.4.4 Primary Set IRQ Mask and Secondary Set IRQ                                                                                   |      |

|    |       |          | Mask Registers                                                                                                                       | 8_16 |

|    |       |          | 8.2.4.5 Chip Status CSR                                                                                                              |      |

|    |       |          | 8.2.4.6 Chip Set IRQ Mask Register                                                                                                   |      |

|    |       |          | 8.2.4.7 Chip Clear IRQ Mask Register                                                                                                 |      |

|    |       |          | 8.2.4.8 Upstream Page Boundary IRQ 0 Register                                                                                        |      |

|    |       |          | 8.2.4.9 Upstream Page Boundary IRQ 1 Register                                                                                        |      |

|    |       |          | 8.2.4.10Upstream Page Boundary IRQ Mask 0 Register                                                                                   |      |

|    |       |          | 8.2.4.11Upstream Page Boundary IRQ Mask 1 Register                                                                                   |      |

|    |       | 8.2.5    | ROM Registers                                                                                                                        |      |

|    |       |          | 8.2.5.1 ROM Setup Register                                                                                                           |      |

|    |       |          | 8.2.5.2 ROM Data Register                                                                                                            |      |

|    |       |          | 8.2.5.3 ROM Address Register                                                                                                         |      |

|    |       |          | 8.2.5.4 ROM Control Register                                                                                                         |      |

|    |       | 8.2.6    | Control and Miscellaneous Registers                                                                                                  |      |

|    |       |          | 8.2.6.1 Scratchpad 0 Through Scratchpad 7 Registers                                                                                  | 8–23 |

| 9  | 120 S | upport   |                                                                                                                                      | 9–1  |

|    | 9.1   | • •      | d Message Passing                                                                                                                    |      |

|    | 9.1   |          |                                                                                                                                      |      |

|    |       |          | ınd Message Passing                                                                                                                  |      |

|    | 9.3   | wiiscell | aneous Notes                                                                                                                         | 9-4  |

| 10 |       | •        | d Scratchpad Registers                                                                                                               |      |

|    | 10.1  |          | ot Support                                                                                                                           |      |

|    | 10.2  |          | ell Interrupts                                                                                                                       |      |

|    | 10.3  | Scratch  | npad Registers                                                                                                                       | 10–2 |

|    |       |          |                                                                                                                                      |      |

| 11             | Parai  | IIEI ROM Interface                                                         | 11–1         |

|----------------|--------|----------------------------------------------------------------------------|--------------|

|                | 11.1   | Parallel ROM Read by CSR Access                                            | 11–2         |

|                | 11.2   | Parallel ROM Write by CSR Access                                           |              |

|                | 11.3   | Parallel ROM Dword Read                                                    | 11–5         |

|                | 11.4   | Access Time and Strobe Control                                             |              |

|                | 11.5   | Attaching Additional Devices to the ROM Interface                          | 11–6         |

| 12             | Seria  | I ROM Interface                                                            | 12–1         |

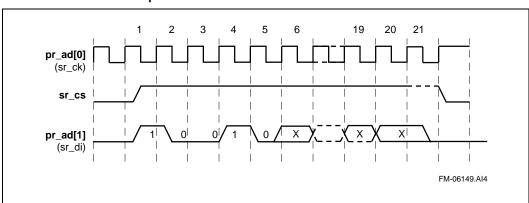

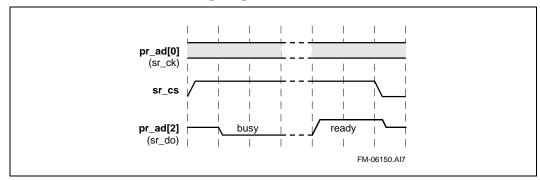

|                | 12.1   | Serial ROM Preload Operation                                               | 12–1         |

|                | 12.2   | Serial ROM Operation by CSR Access                                         | 12–2         |

| 13             | Arbit  | ration                                                                     | 13–1         |

|                | 13.1   | Primary PCI Bus Arbitration                                                | 13–1         |

|                | 13.2   | Secondary PCI Bus Arbitration                                              | 13–1         |

|                |        | 13.2.1 Secondary Bus Arbitration Using the Internal Arbiter                |              |

|                |        | 13.2.2 Secondary Bus Arbitration Using an External Arbiter                 | 13–3         |

| 14             | Error  | · Handling                                                                 | 14–1         |

|                | 14.1   | Parity Errors                                                              | 14–1         |

|                | 14.2   | System Error (SERR#) Reporting                                             | 14–4         |

| 15             | Cloc   | king                                                                       | 15–1         |

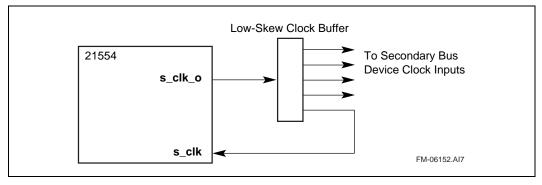

|                | 15.1   | 21554 Secondary Clock Outputs                                              | 15–1         |

| 16             | Initia | lization Requirements                                                      | 17–1         |

|                | 16.1   | Reset Behavior                                                             | 17–1         |

|                |        | 16.1.1 Central Function During Reset                                       | 17–2         |

|                | 16.2   | 21554 Initialization                                                       | 17–3         |

|                |        | 16.2.1 Initialization with Serial ROM, Local Processor, and Host Processor | 17_4         |

|                |        | 16.2.2 Initialization Without Serial Preload                               |              |

|                |        | 16.2.3 Initialization Without Local Processor                              |              |

|                |        | 16.2.4 Initialization Without Local Processor and Serial Preload           |              |

|                |        | 16.2.5 Initialization Without Host Processor                               |              |

|                | 16.3   | Power Management Support                                                   |              |

|                |        | 16.3.1 Transitions Between Power Management States                         |              |

|                |        | 16.3.2 PME# Support                                                        |              |

|                | 10.4   | 16.3.3 Power Management Data Register                                      |              |

|                | 16.4   | Compact PCI Hot-Swap Functionality                                         | 17—7<br>17 C |

|                |        | 16.4.2 Add-In Card Removal                                                 |              |

| 17             | Diag   | nostic Mechanisms                                                          |              |

| • •            | 17.1   | Test Access Port Controller                                                |              |

|                | 17.1   | 17.1.1 Initialization                                                      |              |

|                | 17.2   | Instruction Register                                                       |              |

|                | 17.2   | Bypass Register                                                            |              |

|                | 17.4   | Boundary-Scan Register                                                     |              |

| 18             | VPD    | Support                                                                    |              |

| - <del>-</del> | 18.1   | Reading VPD Information                                                    |              |

|                | 10.1   | 1.000mg vi D IIII0IIII0I0II                                                | 10 - 1       |

|         | 18.2         | Writing VPD Information                                       | 18–2 |

|---------|--------------|---------------------------------------------------------------|------|

| 19      | Spec         | ial Applications                                              | 19–1 |

|         | 19.1         | Primary Bus VGA Support                                       | 19–1 |

|         | 19.2         | Secondary Bus VGA Support                                     |      |

| 20      | Seria        | I ROM and Register Reset Summary                              | 20–1 |

|         | 20.1         | Serial ROM Preload Sequence                                   | 20–1 |

|         | 20.2         | Register Reset and Access Summary                             |      |

|         | 20.3         | CSR Register Summary                                          |      |

| Figures | <b>;</b>     |                                                               |      |

|         | 2-1          | 21554 Intelligent Controller Application                      | 2–4  |

|         | 2-2          | 21554 Microarchitecture                                       |      |

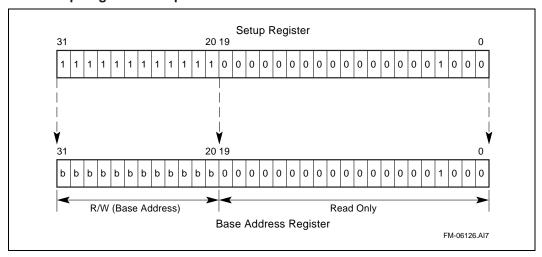

|         | 5-1          | BAR Setup Register Example                                    | 5–3  |

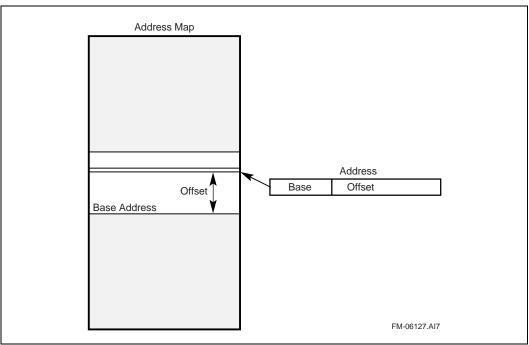

|         | 5-2          | Address Format                                                |      |

|         | 5-3          | Direct Offset Address Translation                             |      |

|         | 5-4          | Downstream Address Translation Example                        |      |

|         | 5-5          | Address Translation Using Lookup Table                        |      |

|         | 5-6          | Upstream Lookup Table Address Translation                     |      |

|         | 5-7          | Lookup Table Entry Format                                     |      |

|         | 5-8          | Dual-Address Transaction Forwarding                           |      |

|         | 7-1          | Primary Interface Configuration Space Address Map             |      |

|         | 7-2          | Secondary Interface Configuration Space Address Map           |      |

|         | 7-3          | Device-Specific Configuration Address Map                     |      |

|         | 8-1          | CSR Register Map (Sheet 1 of 2)                               |      |

|         | 8-2          | CSR Register Map (Sheet 2 of 2)                               |      |

|         | 11-1         | Parallel and Serial ROM Connections                           |      |

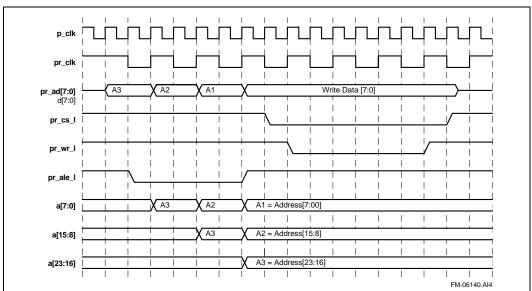

|         | 11-2         | Parallel ROM Read Timing                                      |      |

|         | 11-3         | Parallel ROM Write Timing                                     |      |

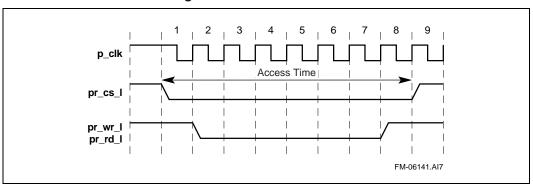

|         | 11-4         | Read and Write Strobe Timing                                  |      |

|         | 11-5         | Attaching Multiple Devices on the ROM Interface               |      |

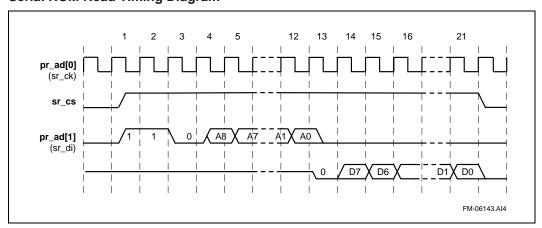

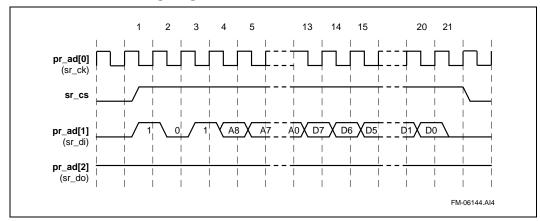

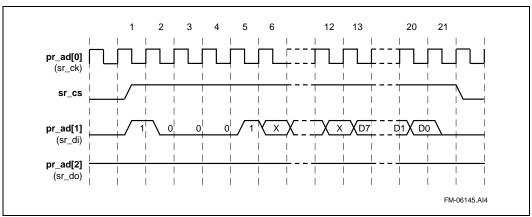

|         | 12-1<br>12-2 | Serial ROM Read Timing DiagramSerial ROM Write Timing Diagram |      |

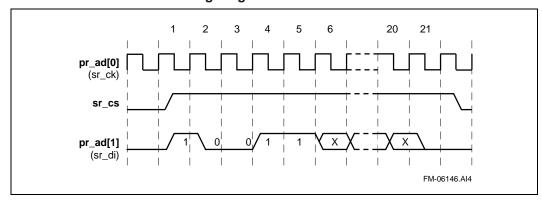

|         | 12-2         | Serial ROM Write All Timing Diagram                           |      |

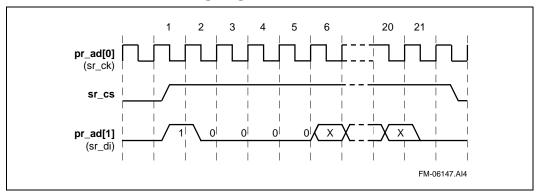

|         | 12-3         | Serial ROM Write Enable Timing Diagram                        |      |

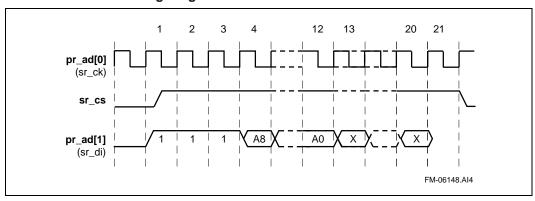

|         | 12-4         | Serial ROM Write Disable Timing Diagram                       |      |

|         | 12-3         | Serial ROM Erase Timing Diagram                               |      |

|         | 12-0         | Serial ROM Erase All Operation                                |      |

|         | 12-7         | Serial ROM Check Status Timing Diagram                        |      |

|         | 13-1         | Secondary Arbiter Example                                     |      |

|         | 15-1         | Synchronous Secondary Clock Generation                        |      |

|         | 16-1         | Compact PCI Hot-Swap Connections                              |      |

|         |              |                                                               |      |

# Tables

| 2-1        | 21554 and PPB Feature Comparison                             | 2–6  |

|------------|--------------------------------------------------------------|------|

| 3-1        | Signal Pin Functional Groups                                 | 3–1  |

| 3-2        | Signal Type Abbreviations                                    |      |

| 3-3        | Primary PCI Bus Interface Signals                            |      |

| 3-4        | Primary PCI Bus Interface 64-Bit Extension Signals           |      |

| 3-5        | Secondary PCI Bus Interface Signals                          |      |

| 3-6        | Secondary PCI Bus Interface 64-Bit Extension Signals         |      |

| 3-7        | Secondary PCI Bus Arbitration Signals                        |      |

| 3-8        | Clock Signals                                                |      |

| 3-9        | Power Management, Hot Swap, and Reset Signals                |      |

| 3-10       | ROM Interface Signals                                        |      |

| 3-11       | Miscellaneous Signals                                        |      |

| 3-12       | JTAG Signals                                                 |      |

| 4-1        | Delayed Write Transaction Target Termination Returns         |      |

| 4-2        | Delayed Read Transaction Target Termination Returns          |      |

| 4-3        | Prefetch Boundaries                                          |      |

| 4-4        | 21554 Transaction Ordering Rules                             |      |

| 5-1        | Upstream Memory 2 Window Size                                |      |

| 5-1        | Base Address Register Summary                                |      |

| 5-∠<br>7-1 | Register Access                                              |      |

| 7-1<br>7-2 |                                                              |      |

| 7-2<br>7-3 | Primary and Secondary Command Registers                      |      |

|            | Primary and Secondary Status Registers                       |      |

| 7-4        | Primary and Secondary Class Code Registers                   |      |

| 7-5        | Primary and Secondary Cache Line Size Registers              |      |

| 7-6        | Primary Latency and Secondary Master Latency Timer Registers |      |

| 7-7        | Primary and Secondary Interrupt Line Registers               |      |

| 7-8        | Primary and Secondary Interrupt Pin Registers                |      |

| 7-9        | Primary and Secondary Minimum Grant Registers                |      |

| 7-10       | Primary and Secondary Maximum Latency Registers              |      |

| 7-11       | Enhanced Capabilities Pointer Register                       |      |

| 7-12       | Power Management Capability ID Register                      |      |

| 7-13       | Power Management Next Item Pointer Register                  |      |

| 7-14       | Power Management Capabilities Register                       |      |

| 7-15       | Power Management Control and Status Register                 |      |

| 7-16       | PMCSR Bridge Support Extensions                              |      |

| 7-17       | Power Management Data Register                               |      |

| 7-18       | Vital Product Data (VPD) ECP Register                        |      |

| 7-19       | Vital Product Data (VPD) Next Pointer Register               |      |

| 7-20       | Vital Product Data (VPD) Address Register                    |      |

| 7-21       | VPD Data Register                                            |      |

| 7-22       | Compact PCI Hot-Swap Capability Identifier Register          | 7–17 |

| 7-23       | Compact PCI Hot-Swap Next Pointer Register                   | 7–18 |

| 7-24       | Compact PCI Hot-Swap Control Register                        |      |

| 7-25       | Primary CSR and Downstream Memory 0 Base Address Register    |      |

| 7-26       | Secondary CSR Memory Base Address Registers                  |      |

| 7-27       | Primary and Secondary CSR I/O Base Address Register          |      |

| 7-28       | Downstream I/O or Memory 1 and Upstream I/O or Memory 0 BAR  | 7–21 |

| 7-29       | Downstream Memory 2 and 3 BAR, Upstream Memory 1 BAR         | 7–22 |

| 7-30         | Upper 32 Bits Downstream Memory 3 Base Address Register | 7–23 |

|--------------|---------------------------------------------------------|------|

| 7-31         | Upstream Memory 2 Base Address Register                 |      |

| 7-32         | Primary Expansion ROM Base Address Register             |      |

| 7-33         | Downstream I/O or Memory 1 and Upstream I/O or          |      |

|              | Memory 0 Translated Base Register                       | 7–25 |

| 7-34         | Downstream Memory 0, 2, 3, and Upstream Memory 1        |      |

|              | Translated Base Register                                | 7–26 |

| 7-35         | Downstream I/O or Memory 1 and Upstream I/O or          |      |

|              | Memory 0 Setup Registers                                | 7–27 |

| 7-36         | Downstream Memory 0, 2, 3, and Upstream                 |      |

|              | Memory 1 Setup Registers                                |      |

| 7-37         | Upper 32 Bits Downstream Memory 3 Setup Register        | 7–29 |

| 7-38         | Primary Expansion ROM Setup Register                    | 7–29 |

| 7-39         | Downstream and Upstream Configuration Address Registers | 7–30 |

| 7-40         | Downstream Configuration Data and Upstream              |      |

|              | Configuration Data Registers                            | 7–31 |

| 7-41         | Configuration Own Bits Register                         | 7–32 |

| 7-42         | Configuration Control and Status Register               | 7–33 |

| 7-43         | Chip Control 0 Register                                 | 7–34 |

| 7-44         | Chip Control 1 Register                                 | 7–37 |

| 7-45         | Reset Control Register                                  |      |

| 7-46         | Chip Status Register                                    |      |

| 7-47         | Arbiter Control Register                                |      |

| 7-48         | Primary SERR# Disable Register                          |      |

| 7-49         | Secondary SERR# Disable Register                        |      |

| 7-50         | Autoload Sequence                                       |      |

| 7-51         | Power Management and BiST Autoload Format               |      |

| 8-1          | Downstream I/O Address and Upstream I/O Address         |      |

|              | Registers                                               | 8–5  |

| 8-2          | Downstream I/O Data and Upstream I/O Data Registers     |      |

| 8-3          | I/O Own Bits Registers                                  |      |

| 8-4          | I/O Control and Status Register                         |      |

| 8-5          | Lookup Table Offset Register                            |      |

| 8-6          | Lookup Table Data Register                              |      |

| 8-7          | I2O Inbound Queue                                       |      |

| 8-8          | I2O Outbound Queue                                      |      |

| 8-9          | I2O Outbound Post_List Status                           |      |

| 8-10         | I2O Outbound Post_List Interrupt Mask                   |      |

| 8-11         | I2O Inbound Post_List Status                            |      |

| 8-12         | I2O Inbound Post_List Interrupt Mask                    |      |

| 8-13         | I2O Inbound Free List Head Pointer                      |      |

| 8-14         | I2O Inbound Post List Tail Pointer                      |      |

| 8-15         | I2O Outbound Free_List Tail Pointer                     |      |

| 8-16         | I2O Outbound Post List Head Pointer                     |      |

| 8-17         | <del>-</del>                                            |      |

| 8-1 <i>1</i> | I2O Inbound Post_List Counter                           |      |

|              | I2O Inbound Free_List Counter                           |      |

| 8-19         | I2O Outbound Post_List Counter                          |      |

| 8-20         | I2O Outbound Free_List Counter                          |      |

| 8-21         | Upstream Memory 2 Lookup Table                          |      |

| 8-22         | Primary Clear IRQ and Secondary Clear IRQ Registers     |      |

| 8-23         | Primary Set IRQ and Secondary Set IRQ Registers         | 8−15 |

| 8-24 | Primary Clear IRQ Mask and Secondary Clear IRQ |      |

|------|------------------------------------------------|------|

|      | Mask Registers                                 | 8–16 |

| 8-25 | Primary Set IRQ Mask and Secondary Set IRQ     |      |

|      | Mask Registers                                 |      |

| 8-26 | Chip Status CSR                                |      |

| 8-27 | Chip Set IRQ Mask Register                     |      |

| 8-28 | Chip Clear IRQ Mask Register                   |      |

| 8-29 | Upstream Page Boundary IRQ 0 Register          |      |

| 8-30 | Upstream Page Boundary IRQ 1 Register          | 8–19 |

| 8-31 | Upstream Page Boundary IRQ Mask 0 Register     | 8–19 |

| 8-32 | Upstream Page Boundary IRQ Mask 1 Register     | 8–19 |

| 8-33 | ROM Setup Register                             | 8–20 |

| 8-34 | ROM Data Register                              | 8–20 |

| 8-35 | ROM Address Register                           | 8–21 |

| 8-36 | ROM Control Registe                            | 8–22 |

| 8-37 | Scratchpad 0 Through Scratchpad 7 Registers    | 8–23 |

| 11-1 | Parallel ROM Interface Signals                 | 11–1 |

| 12-1 | Serial ROM Interface Signals                   | 12–1 |

| 14-1 | Parity Error Responses                         | 14–1 |

| 16-1 | Reset Mechanisms                               | 17–2 |

| 16-2 | Power Management Actions                       | 17–6 |

| 16-3 | Hot-Swap Insertion from 21554 Viewpoint        | 17–8 |

| 16-4 | Add-In Card Removal from 21554 Viewpoint       | 17–9 |

| 17-1 | JTAG Signal Pins                               | 17–1 |

| 17-2 | JTAG Instruction Register Options              |      |

| 20-1 | Serial Preload Sequence                        |      |

| 20-2 | Configuration Register Summary                 |      |

| 20-3 | CSR Summary                                    |      |

|      |                                                |      |

int<sub>el</sub><sub>®</sub>

Preface

This manual provides a detailed functional and register description of the 21554 PCI-to-PCI bridge device for embedded applications. For pinouts, mechanical specifications, and electrical specifications for this device, please refer to the 21554 PCI-to-PCI Bridge for Embedded Applications Data Sheet.

#### 1.1 **Manual Organization**

This manual contains the following chapters and an appendix:

Chapter 2, "Introduction", provides an overview of the 21554 functionality and architecture.

Chapter 3, "Signal Pins", describes the signal pins grouped by function.

Chapter 4, "PCI Bus Operation", PCI transactions, transaction forwarding, and transaction termination.

Chapter 5, "Address Decoding", contains details about how addresses are decoded.

Chapter 6, "Configuration Accesses", explains how 21554 responds to Type 0 configuration accesses.

Chapter 7, "Configuration Space Registers", describes the 21554 configuration registers.

Chapter 8, "Control and Status Registers", describes the 21554 CSRs.

Chapter 9, "I2O Support", explains how the 21554 implements an I<sub>2</sub>O messaging unit.

Chapter 10, "Interrupt and Scratchpad Registers", describes interrupt support and scratchpad registers.

Chapter 11, "Parallel ROM Interface", describes the 21554 parallel ROM interface.

Chapter 12, "Serial ROM Interface", describes the 21554 serial ROM interface.

Chapter 13, "Arbitration", explains how 21554 implements primary and secondary PCI bus arbitration.

Chapter 14, "Error Handling", describes parity error responses and system error reporting.

Chapter 15, "Clocking", describes clocking support in the 21554.

Chapter 16, "Initialization Requirements", reset operation and initialization requirements for the 21554.

Chapter 17, "Diagnostic Mechanisms", explains the implementation of the 21554's JTAG test port.

Chapter 18, "VPD Support", 21554 Vital Product Data (VPD) support through serial ROM interface.

Chapter 19, "Special Applications", describes primary and secondary bus VGA support.

Chapter 20, "Serial ROM and Register Reset Summary", SROM preload sequence and register reset and access.

Appendix A, "Support, Products, and Documentation", technical support and ordering information.

# 1.2 Conventions and Terminology

This section describes the terminology and conventions used in this manual.

#### **1.2.1** Caution

Cautions provide information to prevent damage to equipment or loss of data.

#### 1.2.2 Data Units

This manual uses the following data-unit terminology.

| Term     | Words | Bytes | Bits |

|----------|-------|-------|------|

| Byte     | 1/2   | 1     | 8    |

| Word     | 1     | 2     | 16   |

| Dword    | 2     | 4     | 32   |

| Quadword | 4     | 8     | 64   |

## 1.2.3 Note

Notes emphasize particularly important information.

# 1.2.4 Numbering

All numbers are decimal or hexadecimal unless otherwise indicated. In cases of ambiguity, a subscript indicates the radix of nondecimal numbers. For example, 19 is decimal, but 19h and 19A are hexadecimal.

# 1.2.5 Signal Names

Signal names are printed in lowercase type.

Signal names indicate whether a signal is low-asserted (the signal is active, or asserted, when it is at a low voltage level) or high-asserted (the signal is asserted when it is at a high voltage level). The names of low-asserted signals carry the suffix \_l; the names of high-asserted signals have no suffix. For example, p\_idsel is a high-asserted signal, and p\_frame\_l is a low-asserted signal.

The prefix p\_ denotes a primary bus signal; the prefix s\_ denotes a secondary bus signal. For example, p\_ad is the primary interface address/data bus, and s\_ad is the secondary interface address/data bus.

# **1.2.6 SIGNAME#**

PCI signals that can be on either the primary interface or the secondary interface are printed in uppercase, normal type. The names of low-asserted signals are followed by #. For example, "asserting FRAME#" can refer to the assertion of the p\_frame\_l signal if the transaction is occurring on the primary bus, or the assertion of the s\_frame\_l signal if the transaction is occurring on the secondary bus.

intel®

Introduction

Intel's 21554 is a PCI peripheral device that performs PCI bridging functions for embedded and intelligent I/O applications. The 21554 has a 64-bit primary interface, a 64-bit secondary interface, and 33-MHz capability.

The 21554 is a "nontransparent" PCI-to-PCI bridge that acts as a gateway to an intelligent subsystem. It allows a local processor to independently configure and control the local subsystem. The 21554 implements an I<sub>2</sub>O message unit that enables any local processor to function as an intelligent I/O processor (IOP) in an I<sub>2</sub>O-capable system. Because the 21554 is architecture independent, it works with any host and local processors that support a PCI bus. This architecture independence enables vendors to leverage existing investments while moving products to PCI technology.

Unlike a transparent PCI-to-PCI bridge, the 21554 is specifically designed to bridge between two processor domains. The processor domain on the primary interface of the 21554 is also referred to as the host domain, and its processor is the host processor. The secondary bus interfaces to the local domain and the local processor. Special features include support of independent primary and secondary PCI clocks, independent primary and secondary address spaces, and address translation between the primary (host) and secondary (local) domains.

The 21554 enables add-in card vendors to present to the host system a higher level of abstraction than is possible with a transparent PCI-to-PCI bridge. The 21554 uses a Type 0 configuration header, which presents the entire subsystem as a single "device" to the host processor. This allows loading of a single device driver for the entire subsystem, and independent local processor initialization and control of the subsystem devices. Because the 21554 uses a Type 0 configuration header, it does not require hierarchical PCI-to-PCI bridge configuration code.

The 21554 forwards transactions between the primary and secondary PCI buses as does a transparent PCI-to-PCI bridge. In contrast to a transparent PCI-to-PCI bridge, however, the 21554 can translate the address of a forwarded transaction from a system address to a local address, or vice versa. This mechanism allows the 21554 to hide subsystem resources from the host processor and to resolve any resource conflicts that may exist between the host and local subsystems.

The 21554 operates at 3.3 V, but is also 5.0-V I/O tolerant. Adapter cards designed using the 21554 can be keyed as universal, thus permitting use in either a 5-V or 3-V slot.

#### 2.1 **Features**

The 21554 also supports the following features:

#### **PCI** Interfaces

- Full compliance with the PCI Local Bus Specification, Revision 2.1, plus:

- Vital Product Data (VPD) support

- Compact PCI Distributed Hot-Swap support

- 3.3-V operation with 5.0-V tolerant I/O

- Selectable asynchronous or synchronous primary and secondary interface clocks

· Concurrent primary and secondary bus operation

#### PCI Power Management

- Fully compliant with the Advanced Configuration Power Interface (ACPI) specification

- Fully compliant with the PCI Bus Power Management Specification

#### **Buffer Architecture**

- Queuing of multiple transactions in either direction

- 256 bytes of posted write (data and address) buffering in each direction:

- For forwarding of memory write (MW) and memory write and invalidate (MWI) transactions

- 256 bytes of read data buffering in each direction

- Four delayed transaction entries in each direction:

- For forwarding of I/O write and all read transactions

- For configuration and I/O transaction generation

- Two dedicated I<sub>2</sub>O delayed transaction entries

#### Configuration Registers and CSRs

- Two sets of standard PCI configuration registers corresponding to the primary and secondary interface; each set is accessible from either the primary or secondary interface

- Four 32-bit base address configuration registers mapping the 21554 control and status registers (CSRs):

- One for memory mapping of registers from the primary interface

- One for I/O mapping of registers from the primary interface

- One for memory mapping of registers from the secondary interface

- One for I/O mapping of registers from the secondary interface

#### Transaction Forwarding

- Four primary interface base address configuration registers for downstream forwarding, with size and prefetchability programmable for all four address ranges:

- One programmable for forwarding of either I/O or memory transactions

- Three for forwarding of memory transactions:

- \*One shared with primary CSR memory mapping.

- \*One is configurable as a 64-bit address base address register (BAR) for downstream dual-address cycles (DACs).

- Direct offset address translation for downstream memory and I/O transactions

- Three secondary interface address configuration registers specifying local address ranges for upstream forwarding, with size and prefetchability programmable for all three address ranges:

- One programmable for forwarding of either I/O or memory transactions using direct offset address translation

- One for forwarding memory transactions using direct offset address translation

- One for forwarding memory transactions using lookup table (LUT) based address translation

- Inverse decoding above the 4GB address boundary for upstream DACs

- Ability to generate Type 0 and Type 1 configuration commands on the primary or secondary interface via configuration or I/O CSR accesses

- Ability to generate I/O commands on the primary or secondary interface via I/O CSR accesses

#### Intelligent I/O Support

- I2O message unit

- Standard I<sub>2</sub>O registers at 40h and 44h, with queue-not-empty interrupts

- Queue size selectable between 256 and 32K entries, by powers of 2

- Hardware support for all primary (host-side) queue pointers

- Hardware support for queue-not-empty detection

- Doorbell registers for software generation of primary and secondary bus interrupts, 16 bits per interface

- Eight Dwords of scratchpad registers

#### **ROM Interfaces**

- Parallel flash ROM interface with primary bus expansion ROM base address register

- Read- and write-accessible by CSR access

- Programmable expansion ROM window size from 4KB to 16MB

- Programmable access times

- Serial ROM interface

- Read and write accessible through CSR access

- Enables preloading of selected configuration register fields to application-specific values

- \* Subsystem ID, subsystem vendor ID, and class code

- \* Numbers, sizes, and types of base address registers

- \* MIN\_GNT and MAX\_LAT for both interfaces

- \* Device-specific control bits

#### Miscellaneous Functions

- Secondary bus arbiter support for up to nine external devices (in addition to the 21554)

- Programmable two-level, rotating-priority arbiter

- Hardware disable control for internal arbiter to allow use of an external arbiter

- Secondary bus clock output for synchronous operation

- May be buffered externally to support any number of secondary bus devices

- \* Buffered version is fed back to the 21554 secondary clock input

- Hardware and software disable control

- Hardware enable for secondary bus central functions

- Driving s\_ad[31:0], s\_cbe\_1[3:0], and s\_par during reset

- Asserting s\_req64\_l during reset

- IEEE Standard 1149.1 boundary-scan JTAG interface

# 2.2 Comparing 21554 and Standard PCI-to-PCI Bridge

The 21554 is functionally similar to a standard PCI-to-PCI bridge (PPB) in that both provide a connection path between devices attached to two independent PCI buses. A 21554 and a PPB allow the electrical loading of devices on one PCI bus to be isolated from the other bus while permitting concurrent operation on both buses. Because the *PCI Local Bus Specification* restricts PCI option cards to a single electrical load, the ability of PPBs and the 21554 to spawn PCI buses enables the design of multidevice PCI option cards. The key difference between a PPB and the 21554 is that the presence of a PPB in a connection path between the host processor and a device is transparent to devices and device drivers, while the presence of the 21554 is not. This difference enables the 21554 to provide features that better support the use of intelligent controllers in the subsystem.

It was a primary goal of the PCI-to-PCI bridge architecture that a PPB be transparent to devices and device drivers. For example, no changes are needed to a device driver when a PCI peripheral is located behind a PPB. Once configured during system initialization, a PPB operates without the aid of a device driver. A PPB does not require a device driver of its own since it does not have any resources that must be managed by software during run-time. This requirement for transparency forced the usage of a flat addressing model across PCI-to-PCI bridges. This means that a given physical address exists at only one location in the PCI bus hierarchy and that this location may be accessed by any device attached at any point in the PCI bus hierarchy. As a consequence, it is not possible for a PPB to isolate devices or address ranges from access by devices on the opposite interface of a PPB. The PPB architecture assumes that the resources of any device in a PCI system are configured and managed by the host processor.

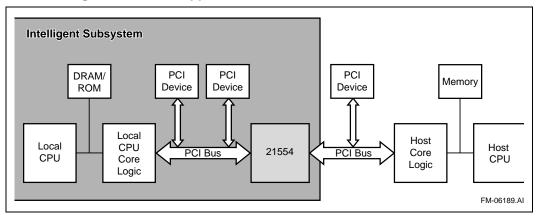

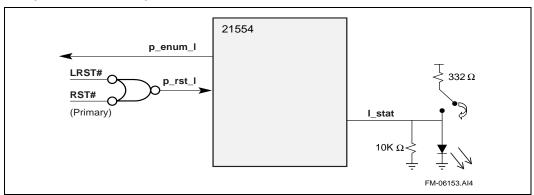

However, there are applications where the transparency of a PCI-to-PCI bridge is not desired. For example, Figure 2-1 shows a hypothetical PCI add-in card used for an intelligent subsystem application.

Figure 2-1. 21554 Intelligent Controller Application

Assume that the local processor on the add-in card is used to manage the resources of the devices attached to the add-in card's local PCI bus. Assume also that it is desirable to restrict access to these same resources from other PCI bus masters in the system and from the host processor. In

addition, there is a need to resolve address conflicts that may exist between the host system and the local processor. The nontransparency of the 21554 is perfectly suited to this kind of configuration, where a transparent PCI-to-PCI bridge would be problematic.

Because the 21554 is not transparent, the device driver for the add-in card must be aware of the presence of the 21554 and manage its resources appropriately. The 21554 allows the entire subsystem to appear as a single virtual device to the host. This enables configuration software to identify the appropriate driver for the subsystem.

With a transparent PCI-to-PCI bridge, a driver does not need to know about the presence of the bridge and manage its resources. The subsystem appears to the host system as individual PCI devices on a secondary PCI bus, not as a single virtual device.

Table 2-1 shows a comparison between a 21554 and a standard transparent PCI-to-PCI bridge.

Table 2-1. 21554 and PPB Feature Comparison

| Feature                         | 21554                                                                                                                               | PCI-to-PCI Bridge                                                                                                                                           |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transaction forwarding          | Adheres to PPB ordering rules.                                                                                                      | Adheres to PPB ordering rules.                                                                                                                              |

|                                 | Uses posted writes and delayed transactions.                                                                                        | Uses posted writes and delayed transactions.                                                                                                                |

|                                 | Adheres to PPB transaction error and parity error guidelines, although some errors may be reported differently.                     | Adheres to PPB transaction error and parity error guidelines.                                                                                               |

| Address decoding                | Base address registers are used to define independent downstream and upstream forwarding windows.                                   | PPB base and limit address registers are used to define downstream forwarding windows.                                                                      |

|                                 | Inverse decoding is only used for upstream transactions above the 4GB boundary.                                                     | Inverse decoding for all I/O and memory upstream forwarding.                                                                                                |

| Address<br>translation          | Supported for both memory and I/O transactions.                                                                                     | None. Flat address model is assumed.                                                                                                                        |

|                                 | Downstream devices are not visible to host.                                                                                         | Downstream devices are visible to host.                                                                                                                     |

|                                 | Does not require hierarchical configuration code (Type 0 configuration header).                                                     | Requires hierarchical configuration code (Type 1 configuration header).                                                                                     |

| Configuration                   | Does not respond to Type 1 configuration transactions.                                                                              | Forwards and converts Type 1 configuration transactions.                                                                                                    |

|                                 | Supports configuration access from the secondary bus. Implements separate set of                                                    | Does not support configuration access from the secondary bus. Same set of configuration registers is used to control both primary and secondary interfaces. |

|                                 | configuration registers for the secondary interface.                                                                                | primary and secondary interfaces.                                                                                                                           |

| Run-time resources              | Includes features such as doorbell interrupts, I <sub>2</sub> O message unit, and so on, that must be managed by the device driver. | Typically has only configuration registers; no device driver is required.                                                                                   |

| Cleake                          | Generates secondary bus clock output.                                                                                               | Generates one or more secondary bus clock outputs.                                                                                                          |

| Clocks                          | Asynchronous secondary clock input is also supported.                                                                               |                                                                                                                                                             |

| Secondary bus central functions | Implements secondary bus arbiter. This function can be disabled.                                                                    | Implements secondary bus arbiter. This function can be disabled.                                                                                            |

|                                 | Drives secondary bus AD,<br>C/BE#, and PAR during reset. This<br>function can be disabled.                                          | Drives secondary bus AD, C/BE#, and PAR during reset.                                                                                                       |

## 2.3 Architectural Overview

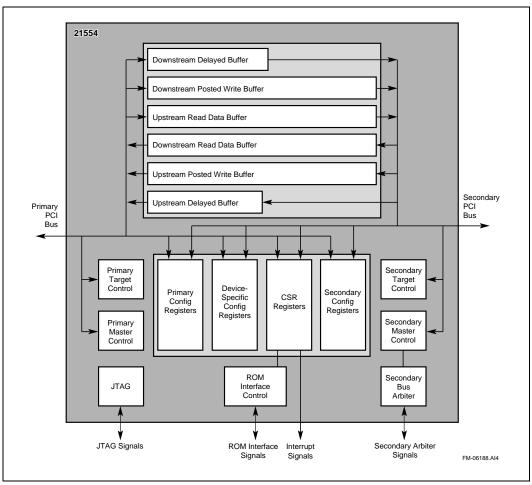

The 21554 consists of the following function blocks:

#### **Data Buffers**

Data buffers include the buffers along with the associated data path control logic. Delayed transaction buffers contain the compare functionality for completing delayed transactions. The blocks also contain the watchdog timers associated with the buffers. The data buffers are as follows:

- Four-entry downstream delayed transaction buffer

- · Four-entry upstream delayed transaction buffer

- 256-byte downstream posted write buffer

- 256-byte upstream posted write buffer

- 256-byte downstream read data buffer

- 256-byte upstream read data buffer

- Two downstream I<sub>2</sub>O delayed transaction entries

#### **Registers**

The following register blocks also contain address decode and translation logic, I<sub>2</sub>O message unit, and interrupt control logic:

- Primary interface header Type 0 configuration registers

- Secondary interface header Type 0 configuration registers

- Device-specific configuration registers

- Memory and I/O mapped control and status registers

#### **Control Logic**

The 21554 has the following control logic:

- Primary PCI target control logic

- Primary PCI master control logic

- Secondary PCI target control logic

- Secondary PCI master control logic

- ROM interface control logic for both serial and parallel ROM connections (interfaces between the ROM registers and ROM signals)

- Secondary PCI bus arbiter interface to secondary bus device request and grant lines, as well as the 21554 secondary master control logic

- JTAG control logic

Figure 2-2 shows the 21554 microarchitecture.

Figure 2-2. 21554 Microarchitecture

# int<sub>ط</sub>® Signal Pins

This chapter provides detailed descriptions of the 21554 signal pins, grouped by function. Table 3-1 describes these signal pin functional groups.

#### **Table 3-1. Signal Pin Functional Groups**

| Function                                                     | Description                                                                                                           |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Primary PCI bus interface signal pins                        | All PCI pins required by the PCI Local Bus Specification, Revision 2.1.                                               |

| Primary PCI bus<br>interface 64-bit<br>extension signal pins | All PCI 64-bit extension pins required by the PCI Local Bus Specification, Revision 2.1.                              |

| Secondary PCI bus interface signal pins                      | All PCI pins required by the PCI Local Bus Specification, Revision 2.1.                                               |

| Secondary PCI bus interface 64-bit extension signal pins     | All PCI 64-bit extension pins required by the PCI Local Bus Specification, Revision 2.1.                              |

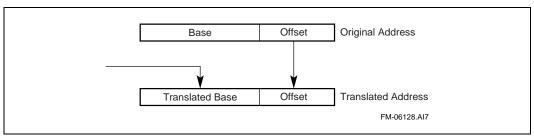

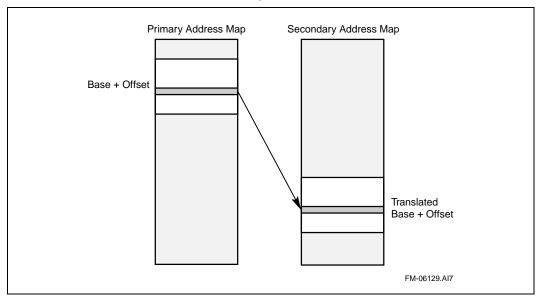

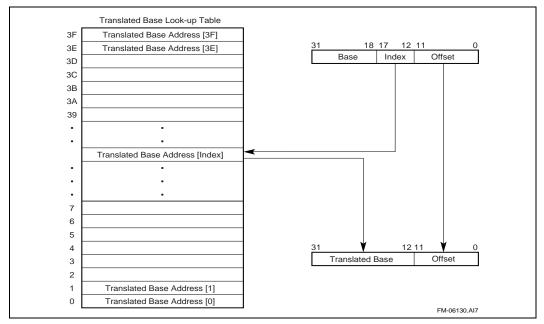

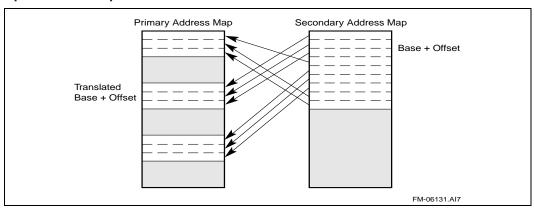

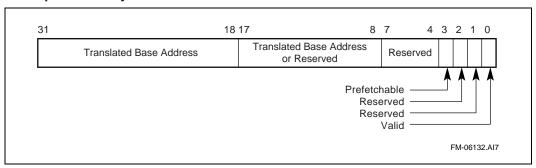

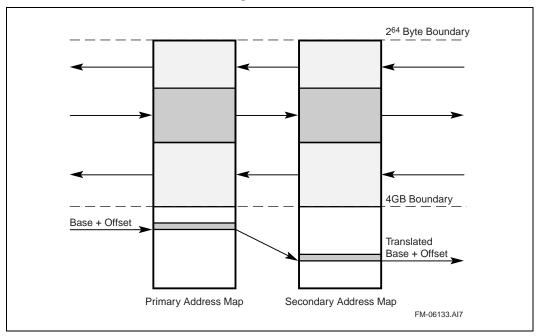

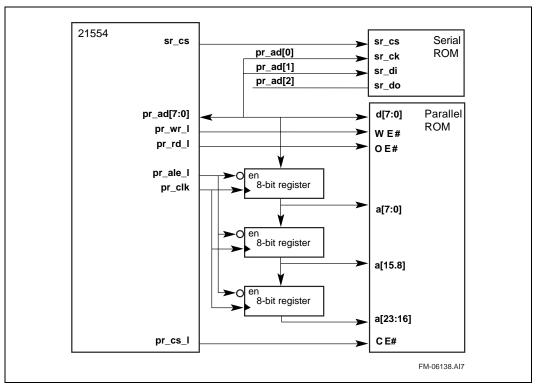

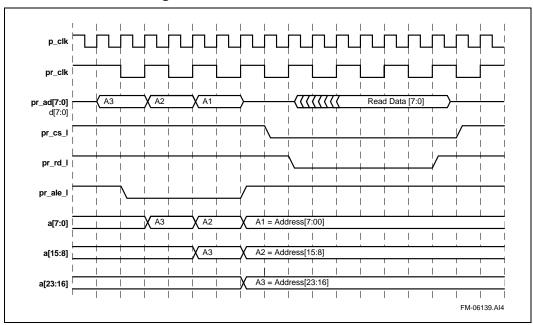

| Secondary PCI bus arbitration signal pins                    | Nine request/grant pairs of pins for the secondary PCI bus.                                                           |