# GAL® Data Book

In 1984, Lattice Semiconductor Corporation designed the world's first electrically erasable CMOS PLD, the GAL16V8. Five years later, Lattice is the largest volume supplier of CMOS Programmable Logic Devices.

Today, the GAL concept is being embraced by the largest PLD manufacturers in the world. These companies have recognized the benefits of GAL devices and are producing E<sup>2</sup>CMOS PLDs based on the GAL technology that Lattice pioneered. We welcome these companies into the high-speed CMOS marketplace. Their acceptance of Lattice's technology is a powerful endorsement of our efforts to develop what we believe is the best PLD.

In the future, Lattice will continue to supply our customers with the fastest, most innovative CMOS PLDs on the market. In 1989, we introduced the GAL16V8A-10 (10ns  $t_{\rm PD}$ , 62.5 MHz) and the GAL22V10 (15ns  $t_{\rm PD}$ , 50 MHz). These high-speed CMOS devices are in full production and provide the speed, power savings, and quality levels that our customers demand.

Thanks to you, and the companies that have chosen to second source GAL devices, Lattice's E<sup>2</sup>CMOS technology has become the new standard in the PLD marketplace. We look forward to helping you solve your system performance requirements and hope you find the 1989 GAL Data Book informative.

Cyrus Tsui

Chief Executive Officer

Lattice Semiconductor Corporation

# GAL® Data Book

1989

Copyright © 1989 Lattice Semiconductor Corporation

E²CMOS and Generic Array Logic are trademarks of Lattice Semiconductor Corporation. ispGAL, GAL, and UltraMOS are registered trademarks of Lattice Semiconductor Corporation.

PAL is a registered trademark of Advanced Micro Devices, Inc.

Products discussed in this literature are covered by U.S. Patents No. 4,761,768 and No. 4,766,569 issued to Lattice Semiconductor Corporation, and by U.S. and foreign patents pending.

LATTICE SEMICONDUCTOR CORP.

P.O. Box 2500 Portland, OR 97208-2500 Tel.: (503) 681-0116 FAX: (503) 681-3037

TELEX 277338 LSC UR

| Section 1: Introduction to Generic Array Logic <sup>TM</sup>                                                    | Page No.                            |   |

|-----------------------------------------------------------------------------------------------------------------|-------------------------------------|---|

| GAL Product Index Introduction to Generic Array Logic                                                           | 4<br>5                              |   |

| Section 2: GAL Datasheets                                                                                       | Page No.                            | 2 |

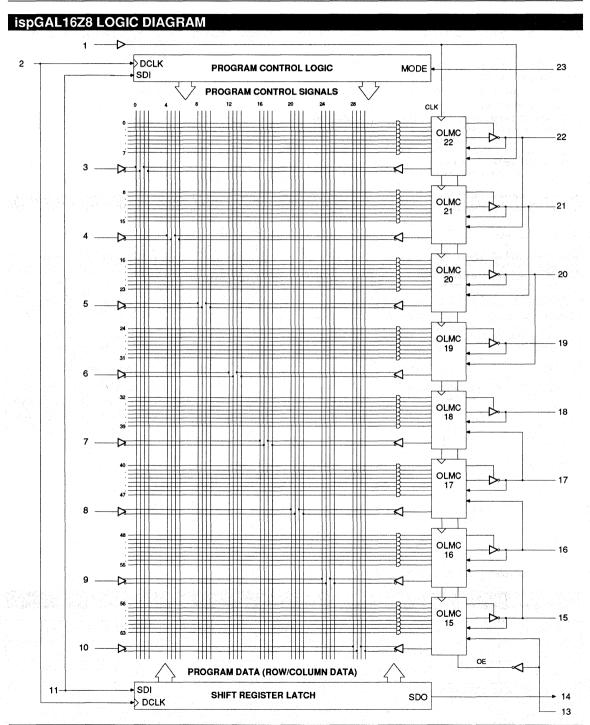

| Definition of Datasheet Levels GAL16V8A GAL16V8 GAL20V8A GAL20V8 GAL22V10 GAL6001 ispGAL16Z8                    | 8<br>9<br>41<br>9<br>41<br>59<br>77 |   |

| Section 3: GAL Applications Notes                                                                               | Page No.                            | 3 |

| Designing with High-Speed CMOS GAL Metastability Report                                                         | 111<br>119                          |   |

| Section 4: General Information                                                                                  | Page No.                            | 4 |

| Copying PAL Patterns into GAL Devices GAL Development Tools Package Diagrams Ordering Information Sales Offices | 135<br>137<br>138<br>142<br>143     |   |

### **GAL PRODUCT INDEX**

| DEVICE     | PINS | t <sub>PD</sub> (ns) | I <sub>cc</sub> (mA) | DESCRIPTION                                    | PAGE |

|------------|------|----------------------|----------------------|------------------------------------------------|------|

| GAL16V8A   | 20   | 10, 12, 15, 25       | 55, 115              | E <sup>2</sup> CMOS Generic PLD                | 9    |

| GAL16V8    | 20   | 15, 20, 25           | 45, 90               | E <sup>2</sup> CMOS Generic PLD                | 41   |

| GAL20V8A   | 24   | 10, 12, 15, 25       | 55, 115              | E²CMOS Generic PLD                             | 9    |

| GAL20V8    | 24   | 15, 20, 25           | 45, 90               | E <sup>2</sup> CMOS Generic PLD                | 41   |

| GAL22V10   | 24   | 15, 25               | 130                  | E <sup>2</sup> CMOS Generic PLD                | 59   |

| GAL6001    | 24   | 30                   | 150                  | E <sup>2</sup> CMOS FPLA                       | 77   |

| ispGAL16Z8 | 24   | 20, 25               | 90                   | E <sup>2</sup> CMOS In-System-Programmable PLD | 91   |

Note: Specifications ( $t_{PD}$  and  $I_{CC}$ ) listed above are for Commercial temperature range devices. See datasheets for Military and Industrial temperature range device specifications.

# Introduction to Generic Array Logic

### INTRODUCTION

Lattice Semiconductor, located in Hillsboro, Oregon, was founded in 1983 to design, develop and manufacture high-performance semiconductor components. It is a firm belief at Lattice that technological evolution can be accelerated through the continued development of higher-speed and architecturally superior products. This belief led to a decision to enter the programmable logic marketplace by developing the ideal product line: the GAL® (Generic Array Logic) family of devices.

GAL devices are ideal for four important reasons:

- 1. GAL devices are fabricated using very high-speed Electrically Erasable CMOS (E²CMOS™), which offers the highest degree of testability and quality of any process technology, as well as instant erasability, making GAL devices ideal for prototyping and manufacturing.

- GAL devices can directly replace PAL devices in nearly every application.

- 3. GAL devices have the low power consumption of CMOS, one-fourth to one-half that of bipolar devices.

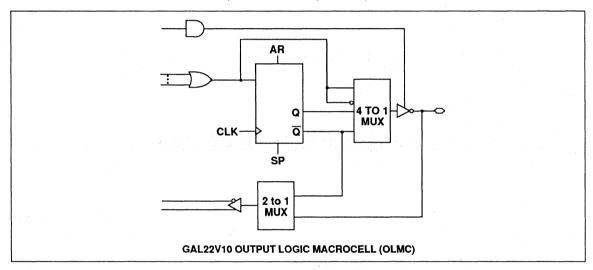

- GAL devices utilize Output Logic Macrocells (OLMCs), which allow the user to configure outputs as needed.

By melding all these features into a single product line, the GAL family is ideally targeted to replace TTL/74HC random logic, low-density gate arrays, and all other programmable logic. The GAL family offers the benefits of reduced system cost, product size and power requirements, as well as higher reliability and greatly simplified system design.

### THE GAL CONCEPT

### E2CMOS — The Ideal Technology

Of the three major technology approaches available E<sup>2</sup>CMOS,UVCMOS, and bipolar, the technology of choice is clearly E<sup>2</sup>CMOS—for many reasons, including: testability, quality, high speed, low power, and instant erasure for prototyping and error recovery.

### **Testability**

The biggest advantage of E²CMOS over competing technologies is its inherent testability. Capitalizing on very fast (50ms) erase times, Lattice is able to pattern and erase all devices many times during manufacture, and to directly test all characteristics including AC, DC and functionality. The result is guaranteed 100% programming and functional yields to the customer—and no further board rework. Competing technologies suffer serious test constraints, as discussed below.

### **Low Power**

Another advantage of this technology is the low power consumption of CMOS. This provides users the immediate benefit of decreased system power requirements allowing for higher-reliability, cooler-running systems, while maintaining high performance. The low power consumption of CMOS also permits circuit designs of much higher functional density, because of lower junction temperatures and power requirements on chip. The user will benefit because higher functional density means further reduction of chip count and smaller boards in the system.

### **High Speed**

Also advantageous is the very high speed attainable with Lattice's state-of-the-art E²CMOS process — speeds that are at least as fast as any device using any technology, with the exception of ECL circuits.

### Prototyping and Error Recovery

Finally, E²CMOS gives the user instant erasability, with no additional handling, or special packages necessary. This provides ideal products for prototyping because designs can be altered instantly, with no waste and no waiting. On the manufacturing floor, instant erasability can also be a big advantage for dealing with pattern changes or error recovery. If a GAL device is accidentally programmed to the wrong pattern, the recovery process is simple, again with no waiting or waste. Parts are simply put back into a device programmer and repatterned. No other technology can offer this.

### A LOOK AT OTHER TECHNOLOGIES

Here, the technologies that compete with E<sup>2</sup>CMOS—bipolar and UVCMOS—are compared and contrasted with the E<sup>2</sup>CMOS approach.

### **Bipolar**

Bipolar fuse-link technology was the first available for programmable logic devices. Although it offers high speed, it is saddled with high power dissipation. This not only significantly increases system power supply and cooling requirements it also limits the ability of high functional density.

Another weakness of this technology is the one-time-programmable fuses. Complete testing is impossible and manufacturers must rely on complex schemes using test rows and columns to simulate and correlate their device's performance, since the fuse array cannot be tested prior to programming. The result is programming failures at the customer location, due to incomplète testing. Also, because these devices can only be programmed once, no reuse in the event of mistakes during prototyping or errors on the production floor are possible and any misprogrammed devices must be discarded.

### **UVCMOS**

UVCMOS addresses many of the weaknesses of the bipolar approach, but introduces many shortcomings of its own. This technology requires much lower power and, while it has the capability to erase, this comes at the expense of slower speeds.

Testability is increased over bipolar since the "fuse" array can be programmed and tested by the manufacturer. The problem here is the long (20 minutes) erase times of this technology, coupled with the requirement of exposing the devices to ultraviolet light for erasing. This becomes a very expensive step in the manufacturing process. Because of the time involved, patterning and erasing is performed only once—a compromised, rather than complete functional test.

Additionally, the devices must be housed in expensive windowed packages to allow users to erase them. Again, this erase is coupled with the time-consuming and cumbersome task of shining ultraviolet light on the parts to erase them. As a cost-cutting measure, UVCMOS PLD manufacturers offer their devices in windowless packages, which cannot be completely tested after packaging, since they cannot be erased. Of course, the user cannot erase them either. These factors significantly detract from the desirability of this technology.

### THE GAL ADVANTAGE

GAL devices are ideal programmable logic devices because, as the name implies, they are architecturally generic. Lattice has employed the macrocell approach, which allows users to define the architecture and functionality of each output. The key benefit to the user is the freedom from being tied to any specific architecture. This is advantageous at the manufacturing level, as well as the design level.

### **Design Advantages**

Early programmable logic devices gave the user the ability to specify a function, but limited them to specific, predetermined output architectures. Comparing the GAL device with fixed-architecture programmable logic devices is much like comparing these same fixed PLDs with SSI/MSI. The GAL family is the next generation in simplified system design. The user need not bother searching for the architecture that best suits a particular design. Instead, the GAL family's generic architecture lets him configure as he goes.

### Manufacturing Advantages

The one-device-does-all approach greatly simplifies manufacturing flow. Inventorying one generic-architecture GAL device type versus having to monitor and maintain many different device types, each with its own architecture, will not only save money but will minimize the paperwork and headaches associated with the latter approach. Manufacturing flow is much smoother, too, because the handling process is greatly simplified. A generic-architecture GAL device also reduces the risk of running out of inventory and halting production, which can be a very expensive nightmare. Reduced chance of obsolete inventory and also easier QA tracking are additional benefits of the generic architecture.

### THE IDEAL PACKAGE

Programmable logic devices are ideal for designing today's systems. Lattice Semiconductor believes that the ideal design approach should be supported with the ideal products. It was on this premise that GAL devices were invented. The ideal device—with a generic architecture—fabricated with the ideal process technology, E²CMOS.

Lattice will continue to develop and expand its line of E<sup>2</sup>CMOS programmable logic devices, bringing higher speeds, more flexibility, and exciting new capabilities such as in-system programmability with our ispGAL® family. This is the Lattice Commitment to programmable logic and to you, our customer.

| Section 1: Introduction to Generic Array Logic™ | Page No |

|-------------------------------------------------|---------|

| GAL Product Index                               | 4       |

| Introduction to Generic Array Logic             | 5       |

| Section 2: GAL Datasheets                       | Page No |

| Definition of Datasheet Levels                  | 8       |

| GAL16V8A                                        | 9       |

| GAL16V8                                         | 41      |

| GAL20V8A                                        | 9       |

| GAL20V8                                         | 41      |

| GAL22V10                                        | 59      |

| GAL6001                                         | 77      |

| ispGAL16Z8                                      | 91      |

| Section 3: GAL Applications Notes               | Page No |

| Designing with High-Speed CMOS                  | 111     |

| GAL Metastability Report                        | 119     |

| Section 4: General Information                  | Page No |

| Copying PAL Patterns into GAL Devices           | 135     |

| GAL Development Tools                           | 137     |

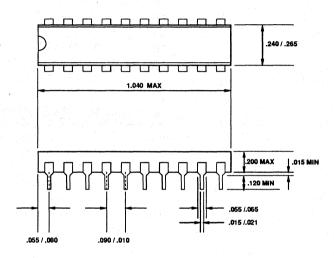

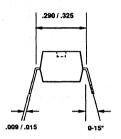

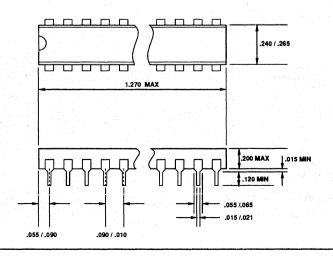

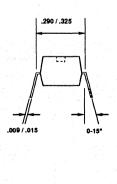

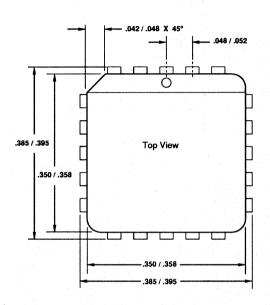

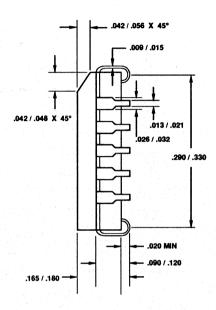

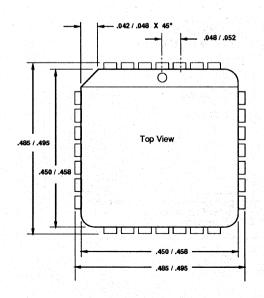

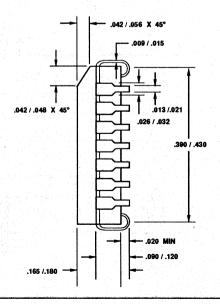

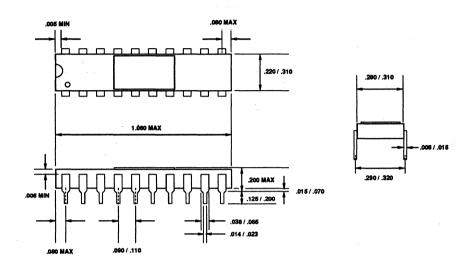

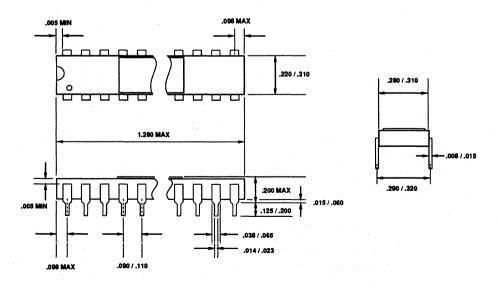

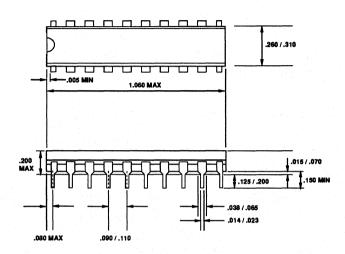

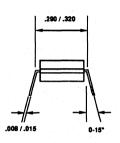

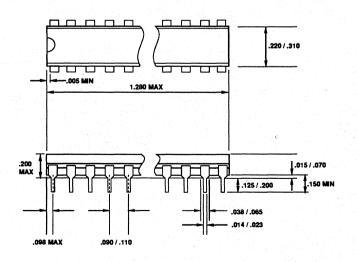

| Package Diagrams                                | 138     |

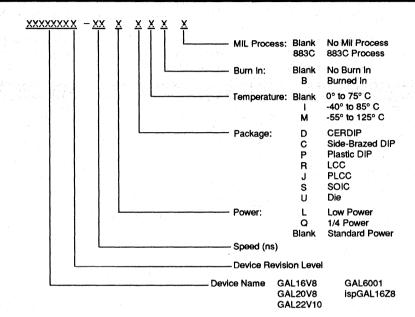

| Ordering Information                            | 142     |

| Sales Offices                                   | 143     |

A tasis, and

### **Definition of Datasheet Levels**

### **DEFINITION OF DATASHEET LEVELS**

| Datasheet Identification | Product Status                | Definition                                                                                                                                                                |

|--------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced                 | In Design                     | This datasheet contains advance information and specifications are subject to change without notice.                                                                      |

| Preliminary              | Sampling or<br>Pre-Production | This datasheet contains preliminary data and supplementary data will be published at a later date. Lattice reserves the right to make changes at any time without notice. |

| No Identification        | Full Production               | This datasheet contains final specifications. Lattice reserves the right to make changes at any time without notice.                                                      |

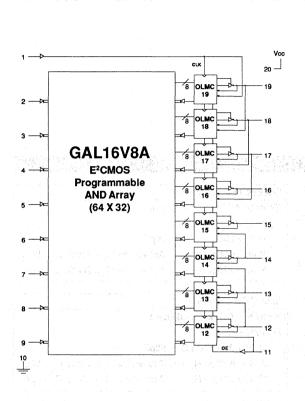

## GAL®16V8A GAL®20V8A

Generic Array Logic™

U.S. Patents 4.761.768 and 4.766.569

### **FEATURES**

- HIGH PERFORMANCE E<sup>2</sup>CMOS™ TECHNOLOGY

- 10 ns Maximum Propagation Delay

- Fmax = 62.5 MHz

- 8 ns Maximum from Clock Input to Data Output

- TTL Compatible 24 mA Outputs

- UltraMOS® III Advanced CMOS Technology

- 50% REDUCTION IN POWER

- 75mA Typ I<sub>cc</sub>

- E<sup>2</sup> CELL TECHNOLOGY

- Reconfigurable Logic

- Reprogrammable Cells

- 100% Tested/Guaranteed 100% Yields

- High Speed Electrical Erasure (<50ms)

- 20 Year Data Retention

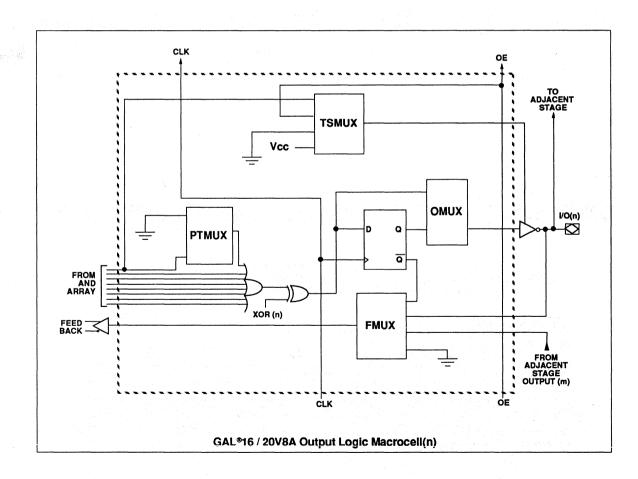

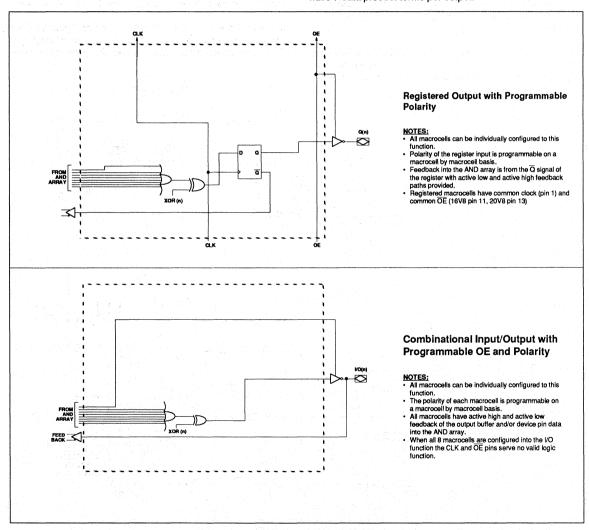

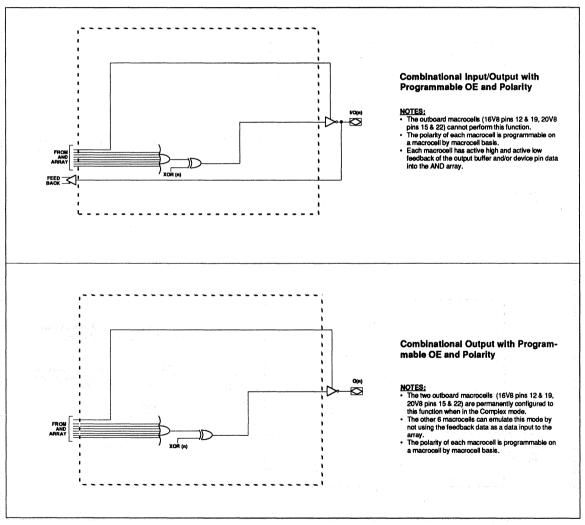

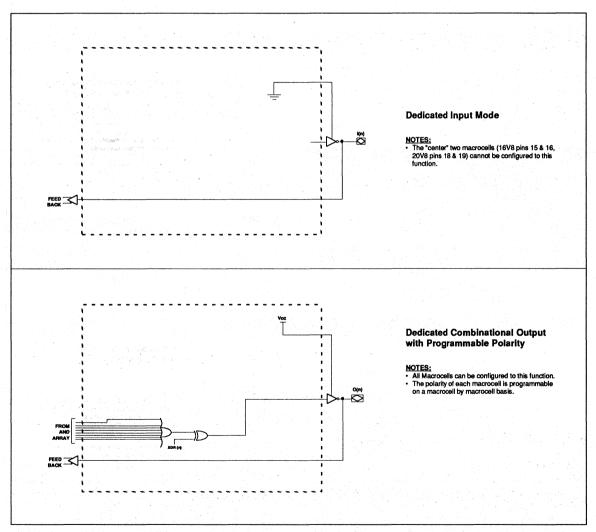

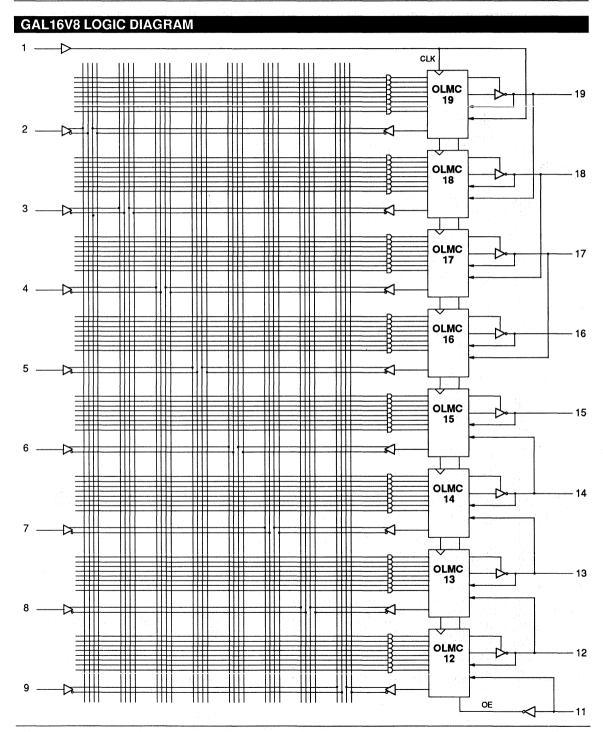

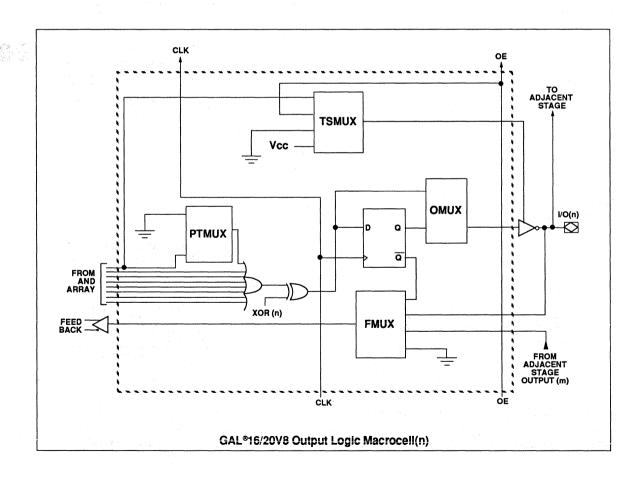

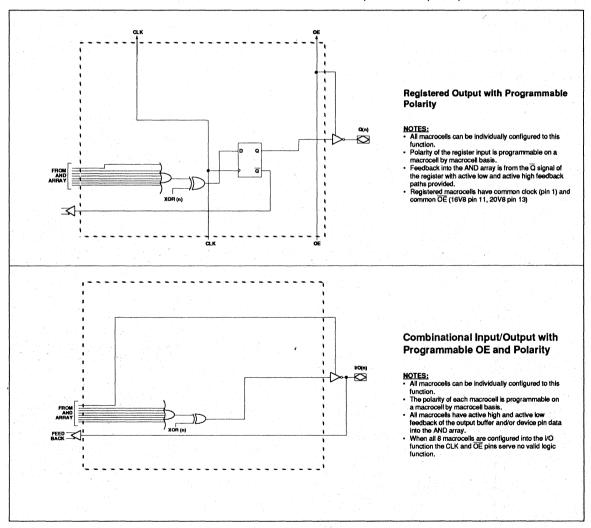

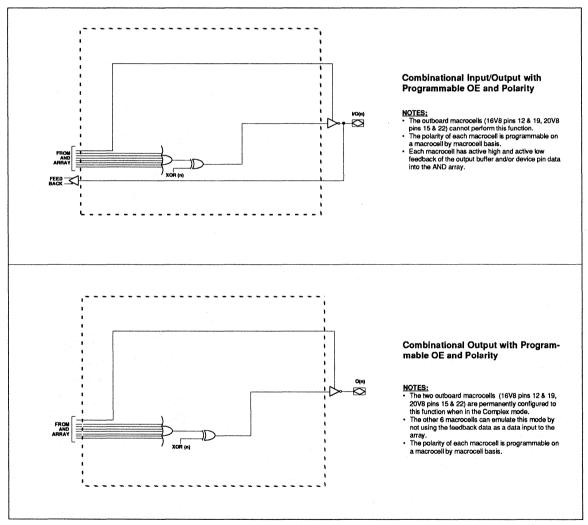

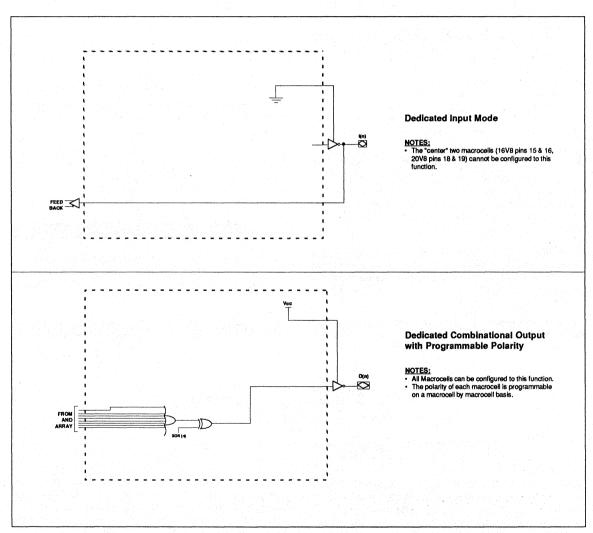

- EIGHT OUTPUT LOGIC MACROCELLS

- Maximum Flexibility for Complex Logic Designs

- Programmable Output Polarity

- GAL16V8A Emulates 20-pin PAL® Devices with Full Function/Fuse Map/Parametric Compatibility

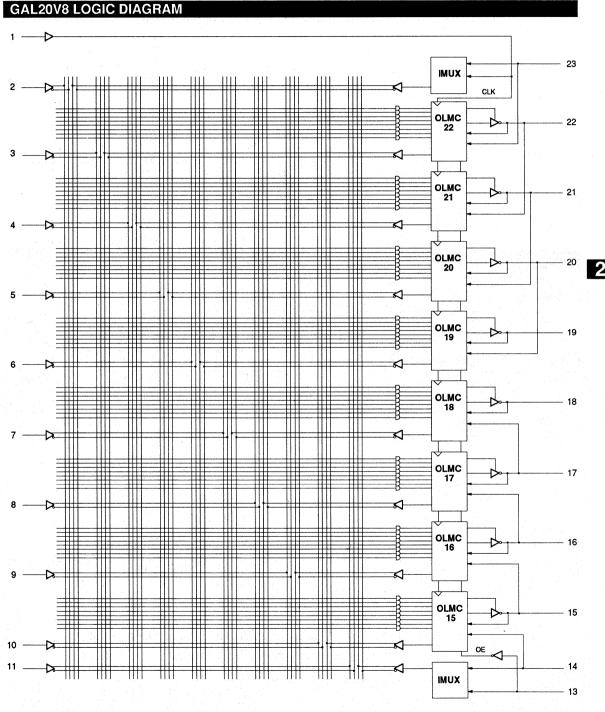

- GAL20V8A Emulates 24-pin PAL® Devices with Full Function/Fuse Map/Parametric Compatibility

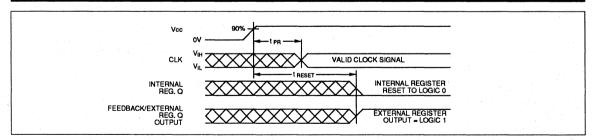

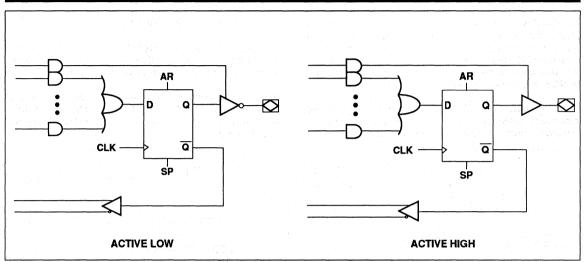

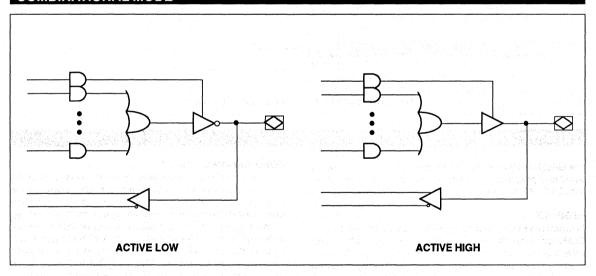

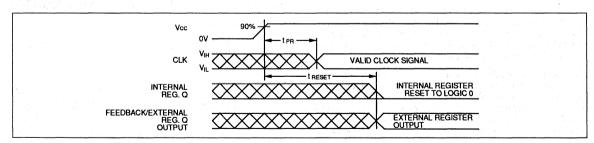

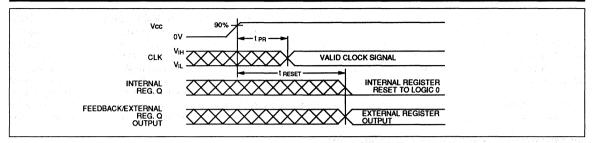

- PRELOAD AND POWER-ON RESET OF ALL REGISTERS 100% Functional Testability

- ELECTRONIC SIGNATURE FOR IDENTIFICATION

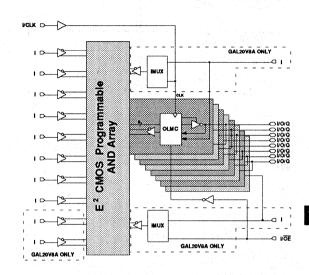

### DESCRIPTION

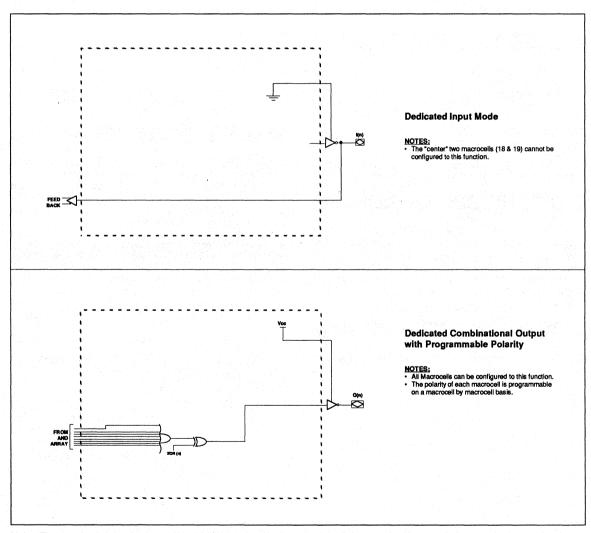

The GAL16V8A and GAL20V8A, at 10 ns maximum propagation delay time, combine a high performance CMOS process with Electrically Erasable (E²) floating gate technology to provide the highest speed performance available in the PLD market. CMOS circuitry allows the GAL16V8A and GAL20V8A to consume just 75mA typical I<sub>cc</sub> which represents a 50% savings in power when compared to their bipolar counterparts. The E² technology offers high speed (50ms) erase times, providing the ability to reprogram or reconfigure the devices quickly and efficiently.

The generic architecture provides maximum design flexibility by allowing the Output Logic Macrocell (OLMC) to be configured by the user. The GAL16V8A and GAL20V8A are capable of emulating standard 20 and 24-pin PAL® devices. The GAL16V8A is capable of emulating standard 20-pin PAL architectures with full function/fuse map/parametric compatibility. The GAL20V8A is capable of emulating standard 24-pin PAL architectures with full function/fuse map/parametric compatibility. On the right is a table listing the PAL architectures that the GAL16V8A and GAL20V8A can replace.

Unique test circuitry and reprogrammable cells allow complete AC, DC, and functional testing during manufacture. Therefore, Lattice guarantees 100% field programmability and functionality of all GAL products. Lattice also guarantees 100 erase/rewrite cycles and that data retention exceeds 20 years.

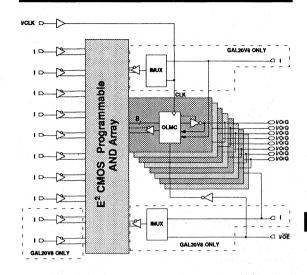

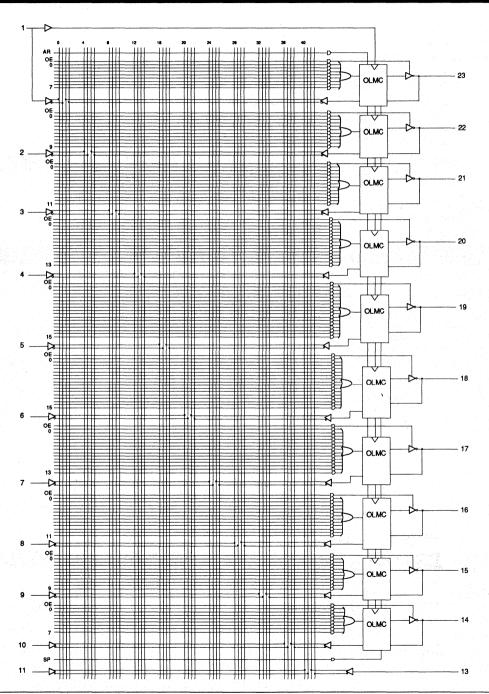

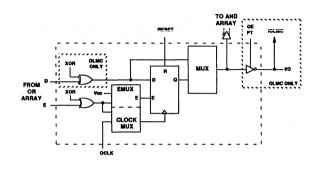

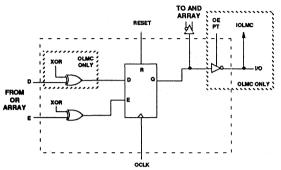

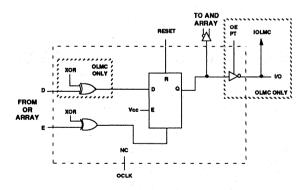

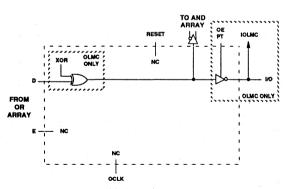

### GAL16V8A / GAL20V8A BLOCK DIAGRAM

### GAL16V8A / GAL20V8A ARCHITECTURE EMULATION

| GAL20V8A<br>PAL Architecture<br>Emulation | GAL16V8A<br>PAL Architecture<br>Emulation |

|-------------------------------------------|-------------------------------------------|

| 20L8                                      | 16L8                                      |

| 20H8                                      | 16H8                                      |

| 20R8                                      | 16R8                                      |

| 20R6                                      | 16R6                                      |

| 20R4                                      | 16R4                                      |

| 20P8                                      | 16P8                                      |

| 20RP8                                     | 16RP8                                     |

| 20RP6                                     | 16RP6                                     |

| 20RP4                                     | 16RP4                                     |

| 14L8                                      | 10L8                                      |

| 16L6                                      | 12L6                                      |

| 18L4                                      | 14L4                                      |

| 20L2                                      | 16L2                                      |

| 14H8                                      | 10H8                                      |

| 16H6                                      | 12H6                                      |

| 18H4                                      | 14H4                                      |

| 20H2                                      | 16H2                                      |

| 14P8                                      | 10P8                                      |

| 16P6                                      | 12P6                                      |

| 18P4                                      | 14P4                                      |

| 20P2                                      | 16P2                                      |

Copyright ©1989 Lattice Semiconductor Corp. GAL and UltraMOS are registered trademarks of Lattice Semiconductor Corp. Generic Array Logic and E°CMOS are trademarks of Lattice Semiconductor Corp. PAL is a registered trademark of Advanced Micro Devices, Inc. The specifications and information herein are subject to change without notice.

### ABSOLUTE MAXIMUM RATINGS(1)

| Supply voltage V <sub>cc</sub> |                                   |

|--------------------------------|-----------------------------------|

|                                | 2.5 to V <sub>cc</sub> +1.0V      |

| Off-state output voltage ap    | plied2.5 to V <sub>cc</sub> +1.0V |

| Storage Temperature            | -65 to 125°C                      |

Stresses above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress only ratings and functional operation of the device at these or at any other conditions above those indicated in the operational sections of this specification is not implied (while programming, follow the programming specifications).

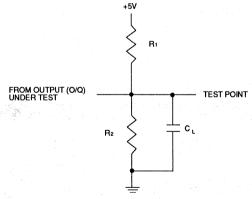

### **SWITCHING TEST CONDITIONS**

| <del></del>                    |               |

|--------------------------------|---------------|

| Input Pulse Levels             | GND to 3.0V   |

| Input Rise and Fall Times      | 3ns 10% – 90% |

| Input Timing Reference Levels  | 1.5V          |

| Output Timing Reference Levels | 1,5V          |

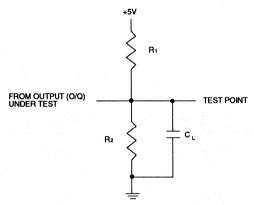

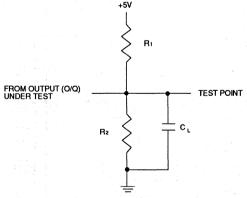

| Output Load                    | See Figure    |

Tri-state levels are measured 0.5V from steady-state active level.

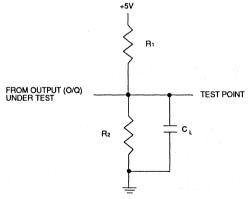

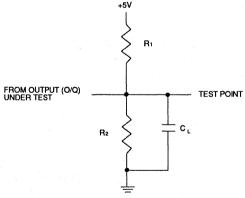

CL INCLUDES JIG AND PROBE TOTAL CAPACITANCE

### COMMERCIAL DEVICES

### **Refer to AC Test Conditions:**

$R_a = 390\Omega$

- 1) R<sub>1</sub> = 200Ω and C<sub>1</sub> = 50pF

- 2) Active High  $R_1 = \infty$ ; Active Low  $R_1 = 200\Omega$   $C_1 = 50pF$

- 3) Active High R<sub>1</sub> =  $\infty$ ; Active Low R<sub>2</sub> = 200 $\Omega$  C<sub>1</sub> = 5pF

### **MILITARY DEVICES**

### **Refer to AC Test Conditions:**

$R_a = 750\Omega$

- 1)  $R_1 = 390\Omega$  and  $C_1 = 50pF$

- 2) Active High  $R_1 = \infty$ ; Active Low  $R_1 = 390\Omega$   $C_1 = 50pF$

- 3) Active High  $R_1 = \infty$ ; Active Low  $R_1 = 390\Omega$   $C_L = 5pF$

### CAPACITANCE $(T_A = 25^{\circ}C, f = 1.0 \text{ MHz})$

| SYMBOL             | PARAMETER         | MAXIMUM* | UNITS | TEST CONDITIONS                   |

|--------------------|-------------------|----------|-------|-----------------------------------|

| C <sub>I</sub>     | Input Capacitance | 8        | pF    | $V_{cc} = 5.0V, V_{i} = 2.0V$     |

| C <sub>1/0/Q</sub> | I/O/Q Capacitance | 10       | pF    | $V_{cc} = 5.0V, V_{I/O/Q} = 2.0V$ |

<sup>\*</sup>Guaranteed but not 100% tested.

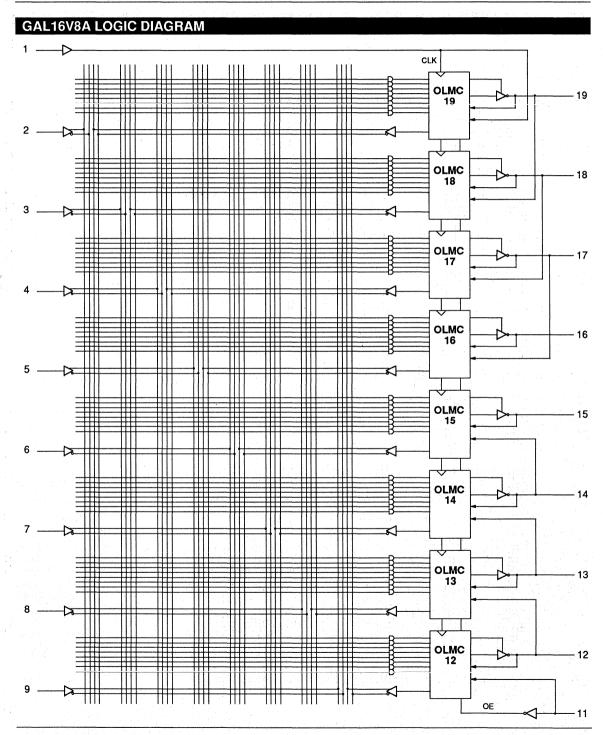

### **GAL16V8A BLOCK DIAGRAM**

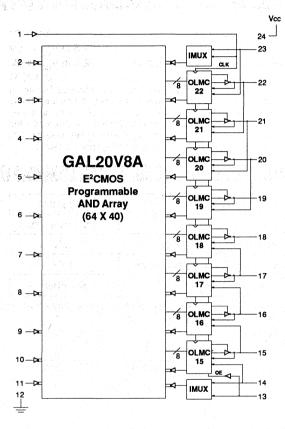

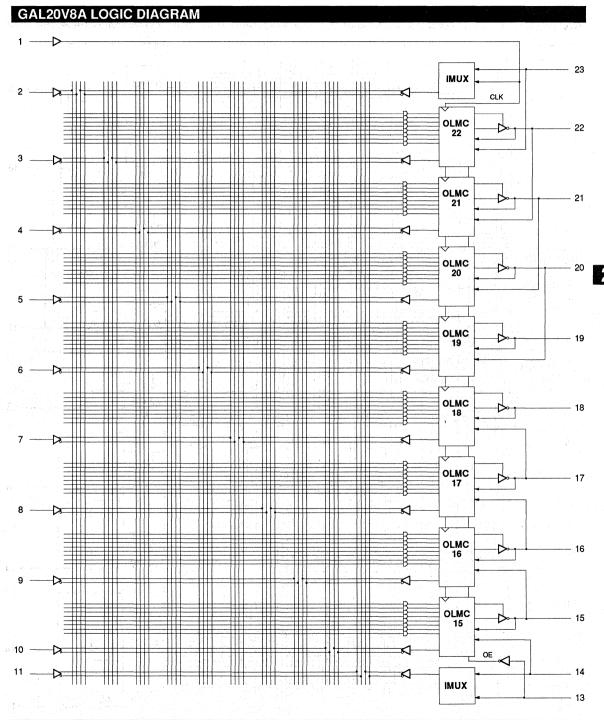

### GAL20V8A BLOCK DIAGRAM

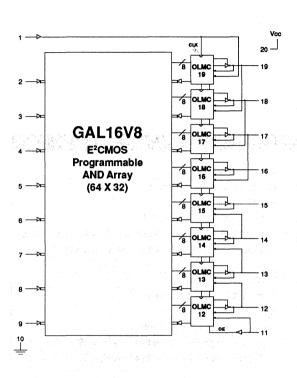

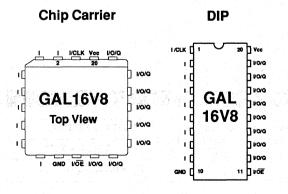

### **GAL16V8A PIN CONFIGURATION**

### **Chip Carrier** DIP I/CLK [ 1000 I/O/Q D VO/Q | I/O/Q GAL GAL16V8A VO/Q 1/0/0 16V8A ) vore Top View 1/0/0 1 vora i νονα סיסיו דו GND I/OE I/O/Q I/O/Q

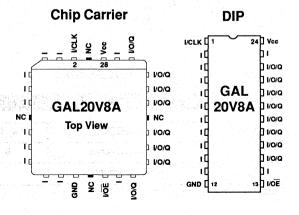

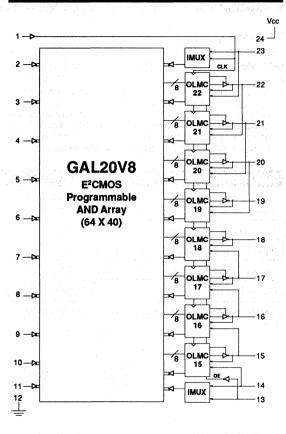

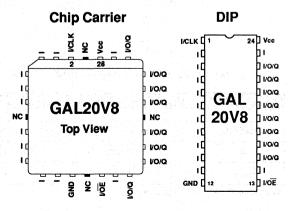

### **GAL20V8A PIN CONFIGURATION**

### **ELECTRICAL CHARACTERISTICS**

### GAL16 / 20V8A-10L Commercial

Over Recommended Operating Conditions (Unless Otherwise Specified)

| SYMBOL   | PARAMETER                         | CONDITION                                                                                                      | MIN. | TYP.         | MAX. | UNITS |

|----------|-----------------------------------|----------------------------------------------------------------------------------------------------------------|------|--------------|------|-------|

| Vol      | Output Low Voltage                | erato formativa e de la composición de |      | _            | 0.5  | V     |

| Vон      | Output High Voltage               |                                                                                                                | 2.4  | <del>-</del> |      | ٧     |

| lıL, lıH | Input Leakage Current             |                                                                                                                | _    |              | ±10  | μА    |

| 11/0/0   | Bidirectional Pin Leakage Current |                                                                                                                |      | _            | ±10  | μА    |

| los¹     | Output Short Circuit Current      | Vcc = 5V Vout = Gnd                                                                                            | -30  | _            | -150 | mA    |

| Icc      | Operating Power Supply Current    | VIL = 0.5V VIH = 3.0V ftoggle = 25MHz                                                                          | _    | 75           | 115  | mA    |

<sup>1)</sup> One output at a time for a maximum duration of one second.

### DC RECOMMENDED OPERATING CONDITIONS GAL16 / 20V8A-10L Commercial

| SYMBOL | PARAMETER                 |              |                                          | MIN.      | MAX.  | UNITS |

|--------|---------------------------|--------------|------------------------------------------|-----------|-------|-------|

| Та     | Ambient Temperature       | e Mary de la | - N. 1                                   | 0         | 75    | °C    |

| Vcc    | Supply Voltage            |              |                                          | 4.75      | 5.25  | V     |

| VIL    | Input Low Voltage         |              | 1000                                     | Vss - 0.5 | 0.8   | , V   |

| ViH    | Input High Voltage        |              | + \$ 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 2.0       | Vcc+1 | V     |

| lol    | Low Level Output Current  |              | Add to the Control                       | -         | 24    | mA    |

| Юн     | High Level Output Current |              |                                          | _         | -3.2  | mA    |

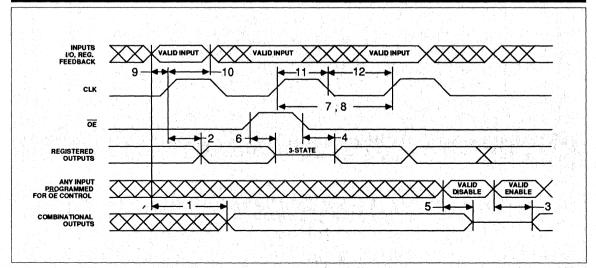

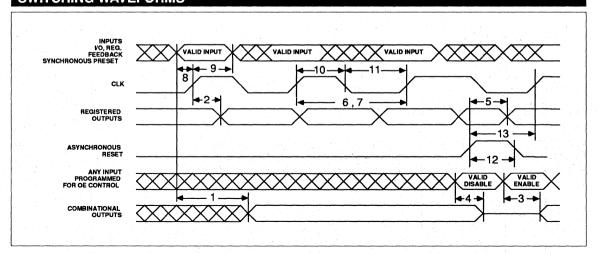

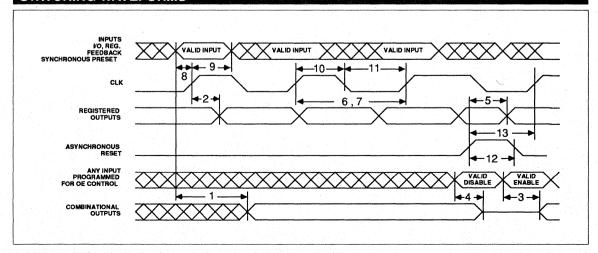

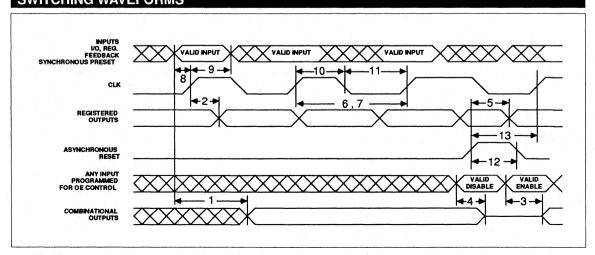

### **SWITCHING CHARACTERISTICS**

### GAL16 / 20V8A-10L Commercial

### **Over Recommended Operating Conditions**

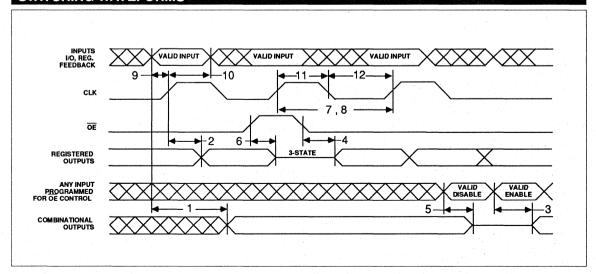

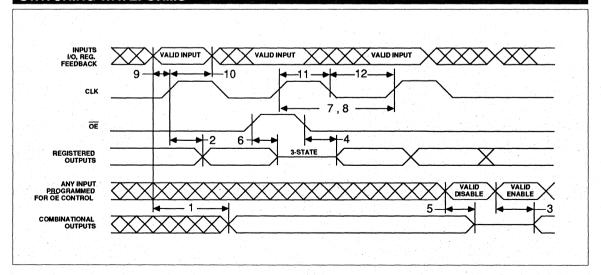

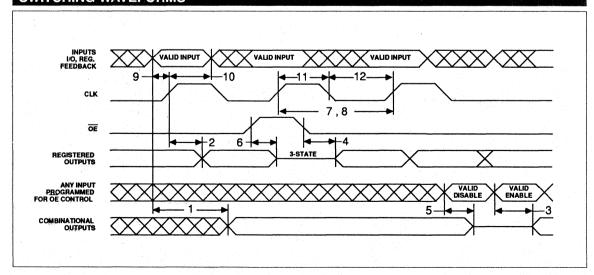

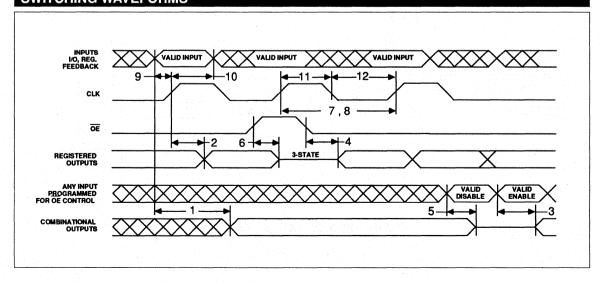

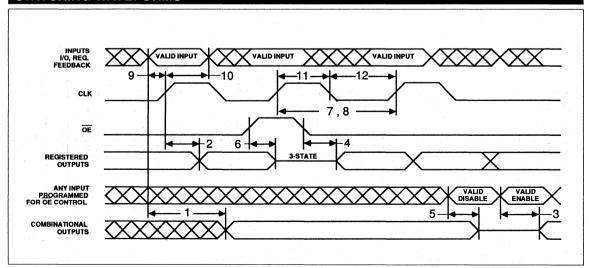

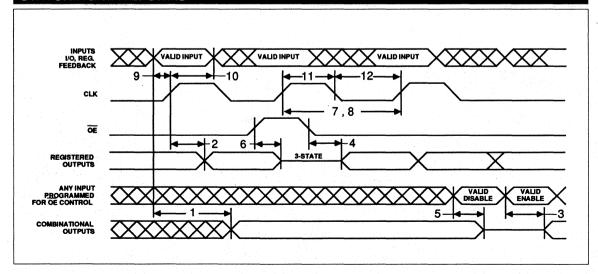

| PARAMETER    | # | FROM   | то  | DESCRIPTION                                | TEST<br>COND.1 | MIN. | мах. | UNITS |

|--------------|---|--------|-----|--------------------------------------------|----------------|------|------|-------|

| <b>t</b> pd  | 1 | I, I/O | 0   | Combinational Propagation Delay            | 1              | 3    | 10   | ns    |

| 400          | 2 | CLK    | Q   | Clock to Output Delay                      | 1              | 2    | 8    | ns    |

| ten          | 3 | I, I/O | 0   | Output Enable, Z → O                       | 2              |      | 10   | ns    |

| <b>.</b>     | 4 | ŌĒ     | Q   | Output Register Enable, $Z \rightarrow Q$  | 2              | _    | 10   | ns    |

| <b>t</b> dis | 5 | I, I/O | 0   | Output Disable, O → Z                      | 3              | _    | 10   | ns    |

| \$           | 6 | ŌĒ     | Q 1 | Output Register Disable, $Q \rightarrow Z$ | 3              | _    | 10   | ns    |

<sup>1)</sup> Refer to Switching Test Conditions section.

### AC RECOMMENDED OPERATING CONDITIONS GAL16 / 20V8A-10L Commercial

| PARAMETER    | #  | DESCRIPTION                                | TEST<br>COND. | MIN. | MAX.         | UNITS |

|--------------|----|--------------------------------------------|---------------|------|--------------|-------|

| <b>f</b> _n  | 7  | Clock Frequency without Feedback           | 1             | 0    | 62.5         | MHz   |

| <b>t</b> clk | 8  | Clock Frequency with Feedback              | 1             | 0    | 55.5         | MHz   |

| <b>t</b> su  | 9  | Setup Time, Input or Feedback, before CLK↑ |               | 10   | <del>-</del> | ns    |

| th           | 10 | Hold Time, Input or Feedback, after CLK↑   |               | 0    | _            | ns    |

|              | 11 | Clock Pulse Duration, High                 | _             | 8    |              | ns    |

| tw           | 12 | Clock Pulse Duration, Low                  | -             | 8    |              | ns    |

### **ELECTRICAL CHARACTERISTICS**

### GAL16 / 20V8A-12L Commercial

Over Recommended Operating Conditions (Unless Otherwise Specified)

| SYMBOL   | PARAMETER                         | CONDITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MIN. | TYP. | MAX. | UNITS |

|----------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Vol      | Output Low Voltage                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _    | _    | 0.5  | V     |

| Voн      | Output High Voltage               | was a second of the second of | 2.4  | _    |      | ٧     |

| IIL, IIH | Input Leakage Current             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -    |      | ±10  | μА    |

| 11/0/0   | Bidirectional Pin Leakage Current |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |      | ±10  | μА    |

| los¹     | Output Short Circuit Current      | Vcc = 5V Vout = Gnd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -30  | _    | -150 | mA    |

| Icc      | Operating Power Supply Current    | VIL = 0.5V VIH = 3.0V ftoggle = 25MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _    | 75   | 115  | mA    |

<sup>1)</sup> One output at a time for a maximum duration of one second.

### DC RECOMMENDED OPERATING CONDITIONS GAL16 / 20V8A-12L Commercial

| SYMBOL | PARAMETER                 | MIN.      | MAX.  | UNITS |

|--------|---------------------------|-----------|-------|-------|

| TA     | Ambient Temperature       | 0         | 75    | °C    |

| Vcc    | Supply Voltage            | 4.75      | 5.25  | ٧     |

| VIL    | Input Low Voltage         | Vss - 0.5 | 0.8   | ٧     |

| VIH    | Input High Voltage        | 2.0       | Vcc+1 | ٧     |

| loL    | Low Level Output Current  |           | 24    | mA    |

| Юн     | High Level Output Current | _         | -3.2  | mA    |

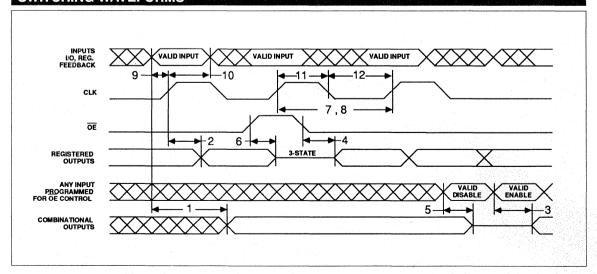

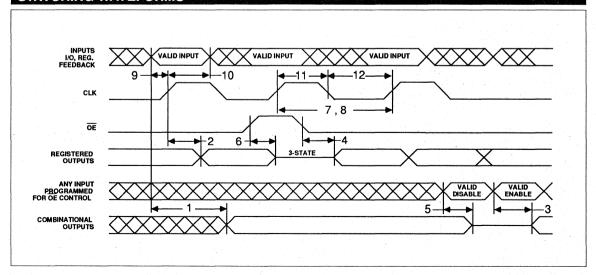

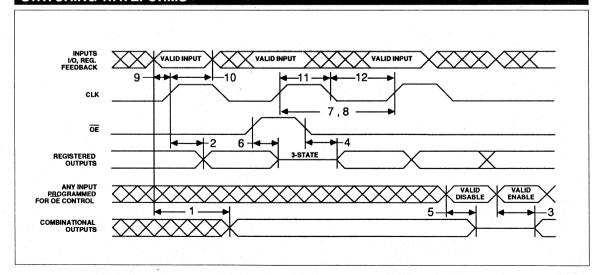

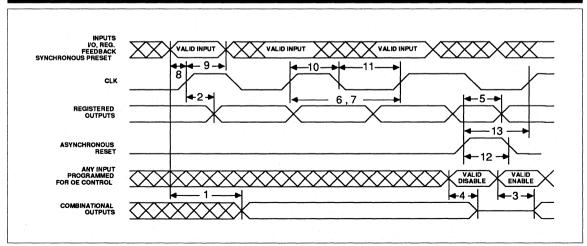

### **SWITCHING CHARACTERISTICS**

### GAL16 / 20V8A-12L Commercial

**Over Recommended Operating Conditions**

| PARAMETER    | # | FROM   | то | DESCRIPTION                     | TEST<br>COND.1 | MIN. | MAX. | UNITS |

|--------------|---|--------|----|---------------------------------|----------------|------|------|-------|

| tpd          | 1 | I, I/O | 0  | Combinational Propagation Delay | 1              | 3    | 12   | ns    |

|              | 2 | CLK    | Q  | Clock to Output Delay           | 1              | 2    | 10   | ns    |

| <b>t</b> en  | 3 | I, I/O | 0  | Output Enable, Z → O            | 2              | -    | 12   | ns    |

|              | 4 | ŌĒ     | Q  | Output Register Enable, Z → Q   | 2              |      | 10   | ns    |

| <b>t</b> dis | 5 | I, I/O | 0  | Output Disable, O → Z           | 3              | -    | 12   | ns    |

| 4.5 1 4.5    | 6 | ŌĒ     | Q  | Output Register Disable, Q → Z  | 3              |      | 10   | ns    |

<sup>1)</sup> Refer to Switching Test Conditions section.

### AC RECOMMENDED OPERATING CONDITIONS GAL16 / 20V8A-12L Commercial

| PARAMETER    | #  | DESCRIPTION                                | TEST<br>COND. | MIN. | MAX. | UNITS |

|--------------|----|--------------------------------------------|---------------|------|------|-------|

| f "          | 7  | Clock Frequency without Feedback           | 1             | 0    | 62.5 | MHz   |

| <b>T</b> clk | 8  | Clock Frequency with Feedback              | 1             | 0    | 50   | MHz   |

| tsu          | 9  | Setup Time, Input or Feedback, before CLK↑ | -             | 10   | _    | ns    |

| th           | 10 | Hold Time, Input or Feedback, after CLK↑   |               | 0    |      | ns    |

| Veril 1      | 11 | Clock Pulse Duration, High                 | <u></u>       | 8    | _    | ns    |

| [w           | 12 | Clock Pulse Duration, Low                  |               | 8    | _    | ns    |

### **ELECTRICAL CHARACTERISTICS**

### GAL16 / 20V8A-15L Commercial

Over Recommended Operating Conditions (Unless Otherwise Specified)

| SYMBOL   | PARAMETER                         | CONDITION                             | MIN.          | TYP. | MAX. | UNITS |

|----------|-----------------------------------|---------------------------------------|---------------|------|------|-------|

| Vol      | Output Low Voltage                |                                       | _             |      | 0.5  | v     |

| Vон      | Output High Voltage               |                                       | 2.4           | _    | _    | ٧     |

| lıL, lıH | Input Leakage Current             |                                       |               | _    | ±10  | μА    |

| lı/o/q   | Bidirectional Pin Leakage Current |                                       |               |      | ±10  | μА    |

| los¹     | Output Short Circuit Current      | Vcc = 5V Vout = Gnd                   | -30           | _    | -150 | mA    |

| Icc      | Operating Power Supply Current    | VIL = 0.5V VIH = 3.0V ftoggle = 25MHz | <del></del> . | 75   | 115  | mA    |

<sup>1)</sup> One output at a time for a maximum duration of one second.

### DC RECOMMENDED OPERATING CONDITIONS GAL16 / 20V8A-15L Commercial

| SYMBOL | PARAMETER                 | MIN.      | MAX.  | UNITS |

|--------|---------------------------|-----------|-------|-------|

| Та     | Ambient Temperature       | 0         | 75    | °C    |

| Vcc    | Supply Voltage            | 4.75      | 5.25  | V     |

| VIL    | Input Low Voltage         | Vss - 0.5 | 0.8   | V     |

| ViH    | Input High Voltage        | 2.0       | Vcc+1 | ٧     |

| loL    | Low Level Output Current  | _         | 24    | mA    |

| Юн     | High Level Output Current |           | -3.2  | mA    |

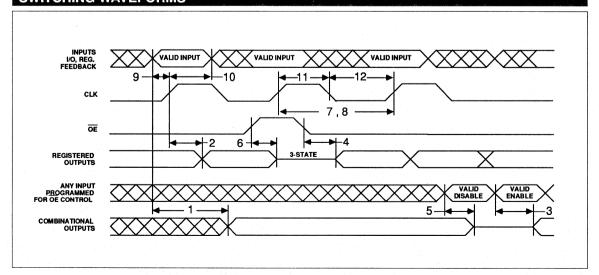

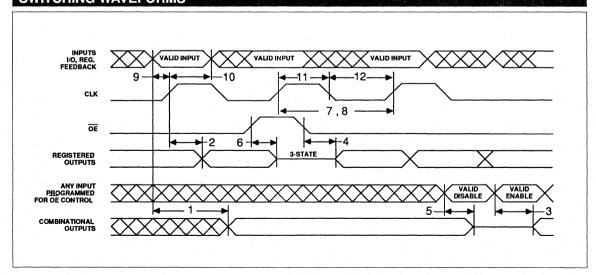

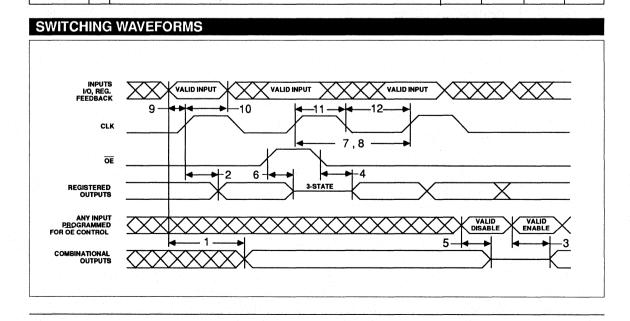

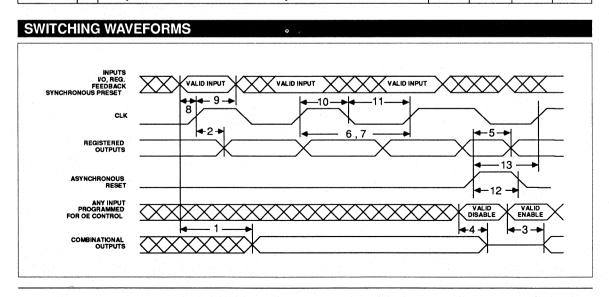

### **SWITCHING CHARACTERISTICS**

### GAL16 / 20V8A-15L Commercial

**Over Recommended Operating Conditions**

| PARAMETER   | # | FROM   | то  | DESCRIPTION                               | TEST<br>COND.1   | MIN.            | MAX. | UNITS |

|-------------|---|--------|-----|-------------------------------------------|------------------|-----------------|------|-------|

| <b>t</b> pd | 1 | I, I/O | 0   | Combinational Propagation Delay           | 1                | 3               | 15   | ns    |

| <b>493</b>  | 2 | CLK    | Q   | Clock to Output Delay                     | 1,               | 2               | 12   | ns    |

| ten         | 3 | I, I/O | 0   | Output Enable, Z → O                      | 2                | 4 4             | 15   | ns    |

|             | 4 | ŌĒ     | Q   | Output Register Enable, $Z \rightarrow Q$ | 2                | 14 <del>4</del> | 15   | ns    |

| tdis        | 5 | I, I/O | 0   | Output Disable, $O \rightarrow Z$         | 3                | ev <u>e</u> :   | 15   | ns    |

| 40          | 6 | ŌĒ     | i Q | Output Register Disable, Q → Z            | a a 1 <b>3</b> % |                 | 15   | ns    |

<sup>1)</sup> Refer to Switching Test Conditions section.

### AC RECOMMENDED OPERATING CONDITIONS GAL16 / 20V8A-15L Commercial **TEST** UNITS PARAMETER DESCRIPTION MIN. MAX. COND. 7 Clock Frequency without Feedback 1 0 50 MHz fclk 8 Clock Frequency with Feedback 1 0 41.6 MHz tsu 9 Setup Time, Input or Feedback, before CLK ↑ 12 ns th 10 Hold Time, Input or Feedback, after CLK↑ Ó ns 11 Clock Pulse Duration, High 10 ns tw 12 Clock Pulse Duration, Low 10 ns

### **ELECTRICAL CHARACTERISTICS**

### GAL16 / 20V8A-15Q Commercial

Over Recommended Operating Conditions (Unless Otherwise Specified)

| SYMBOL      | PARAMETER                         | CONDITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | JAN.  | TYP. | MAX. | UNITS |

|-------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------|

| VoL         | Output Low Voltage Wild findings  | On Commissional Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ) —   |      | 0.5  | ٧     |

| Vон         | Output High Voltage               | COLEGE OF THE CO | 2.4   | , —  | _    | ٧     |

| odit, lin o | Input Leakage Current             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | _    | ±10  | μА    |

| li/o/Q      | Bidirectional Pin Leakage Current | Milli                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - , ' | _    | ±10  | μА    |

| los¹        | Output Short Circuit Current      | Vcc = 5V Vov = and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -30   | _    | -150 | mA    |

| Icc         | Operating Power Supply Current    | VIL = 0.5 V (IH) 3.0V ftoggle = 15MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | 45   | 55   | mA    |

<sup>1)</sup> One output at a time for a maximum duration of one second.

| DC RECOMMENDED OPERATING CONDITIONS      | GAL16 / 20V8A-15Q Commercia  |

|------------------------------------------|------------------------------|

| De liecommended of EliAlina Co. Billions | CALID / ZUVOA-13 & Commercia |

| SYMBOL            | PARAMETE                  | MIN.     | MAX.  | UNITS |

|-------------------|---------------------------|----------|-------|-------|

| Ta                | Ambient Temperature       | 0        | 75    | °C    |

| Vcc               | Supply Voltage            | 4.75     | 5.25  | ٧     |

| VIL               | Input Low Tolkage         | Vss - 0. | 0.8   | ٧     |

| ViH               | Input Hip Voltage         | 2.0      | Vcc+1 | ٧     |

| , lo <sub>L</sub> | Low Level Output Current  |          | 24    | mA    |

| Юн                | High Level Output Current |          | -3.2  | mA    |

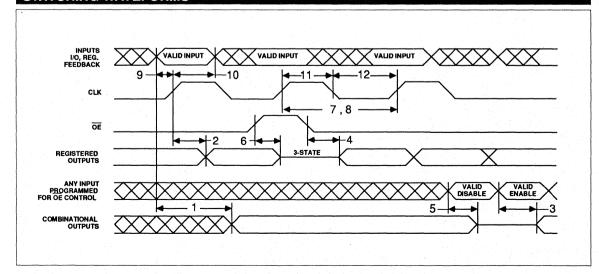

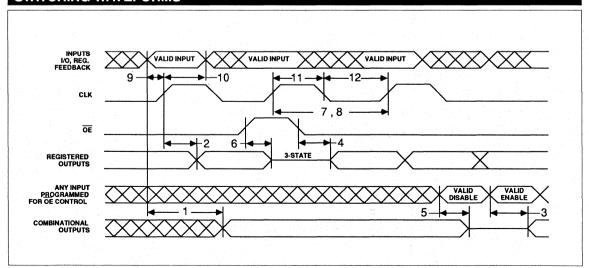

### **SWITCHING CHARACTERISTICS**

### GAL16 / 20V8A-15Q Commercial

### **Over Recommended Operating Conditions**

| PARAMETER    | # | FROM   | то | DESCRIPTION                     | TEST<br>COND.1 | MIN. | MAX. | UNITS |

|--------------|---|--------|----|---------------------------------|----------------|------|------|-------|

| tpd          | 1 | I, I/O | 0  | Combinational Propagation Delay | 1              | 3    | 15   | ns    |

| <b></b>      | 2 | CLK    | a  | Clock to Output Delay           | 1              | 2    | 12   | ns    |

| <b>t</b> en  | 3 | I, I/O | 0  | Output Enable, Z → O            | 2              | ,    | 15   | ns    |

|              | 4 | ŌĒ     | Q  | Output Register Enable          | 2              | _    | 15   | ns    |

| <b>t</b> dis | 5 | I, I/O | 0  | Output Disable, O               | 3              | -    | 15   | ns    |

| 1010         | 6 | ŌĒ     | Q  | Output Register Disaple, Q → Z  | 3              |      | 15   | ns    |

1) Refer to Switching Test Conditions section.

### AC RECOMMENDED OPERATING CONDITIONS

### GAL16 / 20V8A-15Q Commercial

| PARAMETER   | #  | DESCRIPTION                               | TEST<br>COND. | MIN. | MAX. | UNITS |

|-------------|----|-------------------------------------------|---------------|------|------|-------|

| <b>f</b> "  | 7  | Clock Frequency without Feedback          | 1             | 0    | 50   | MHz   |

| Tclk        | 8  | Clock Frequency with Feedback             | 1             | 0    | 41.6 | MHz   |

| <b>t</b> su | 9  | Setup Time Input or Feedback, before CLK↑ |               | 15   |      | ns    |

| th          | 10 | Hole Tinge, Input or Feedback, after CLK↑ | -             | 0    |      | ns    |

|             | 11 | West Pulse Duration, High                 |               | 10   |      | ns    |

| tw          | 12 | Clock Pulse Duration, Low                 |               | 10   |      | ns    |

### **ELECTRICAL CHARACTERISTICS**

GAL16 / 20V8A-25L Commercial

Over Recommended Operating Conditions (Unless Otherwise Specified)

| SYMBOL   | PARAMETER                         | CONDITION                             | MIN. | TYP. | MAX. | UNITS |

|----------|-----------------------------------|---------------------------------------|------|------|------|-------|

| Vol      | Output Low Voltage                |                                       | _    | _    | 0.5  | V     |

| Vон      | Output High Voltage               |                                       | 2.4  | _    | _    | V     |

| lı∟, lıн | Input Leakage Current             |                                       |      | _    | ±10  | μА    |

| li/o/Q   | Bidirectional Pin Leakage Current |                                       | _    | _    | ±10  | μА    |

| los¹     | Output Short Circuit Current      | Vcc = 5V Vout = Gnd                   | -30  |      | -150 | mA    |

| Icc      | Operating Power Supply Current    | VIL = 0.5V VIH = 3.0V ftoggle = 15MHz | _    | 75   | 90   | . mA  |

<sup>1)</sup> One output at a time for a maximum duration of one second.

### DC RECOMMENDED OPERATING CONDITIONS GAL16 / 20V8A-25L Commercial

| SYMBOL | PARAMETER                 | The second secon | MIN.      | MAX.  | UNITS |

|--------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-------|

| TA     | Ambient Temperature       | entra divolpera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0         | 75    | °C    |

| Vcc    | Supply Voltage            | The second of the second of the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.75      | 5.25  | V     |

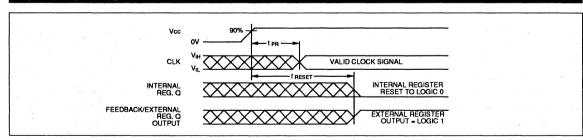

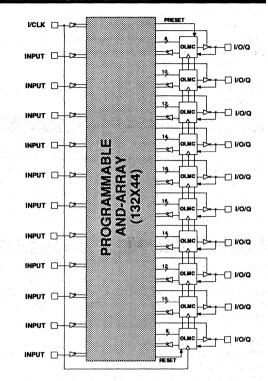

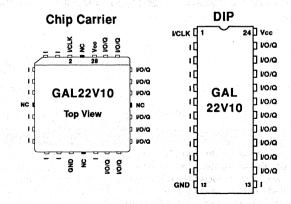

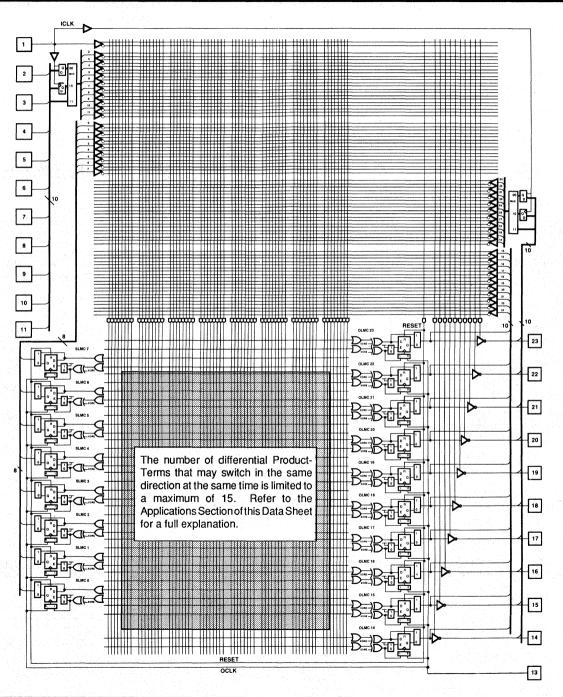

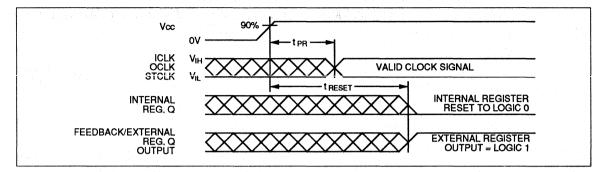

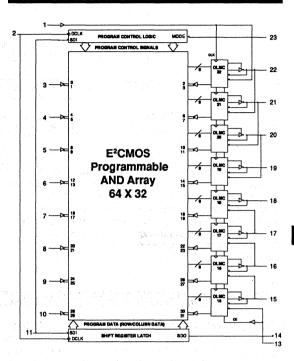

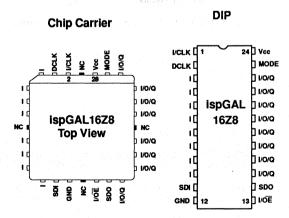

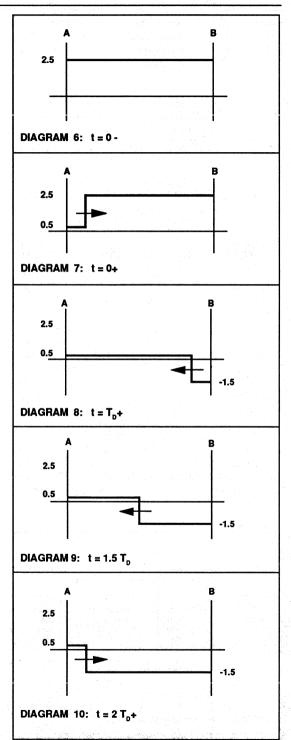

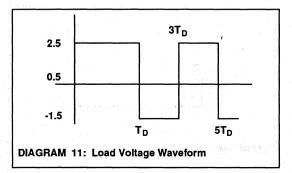

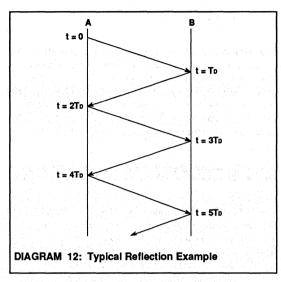

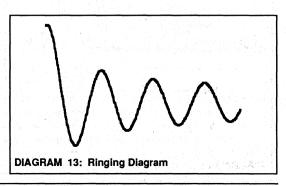

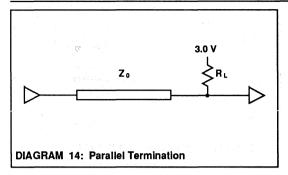

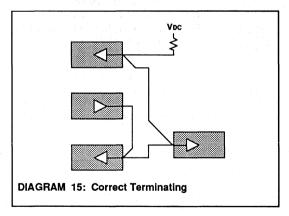

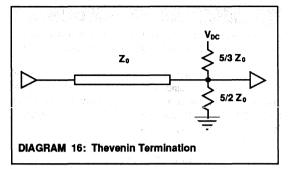

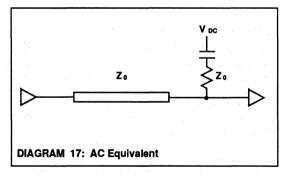

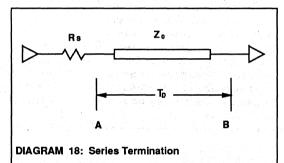

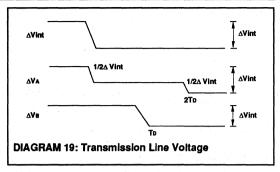

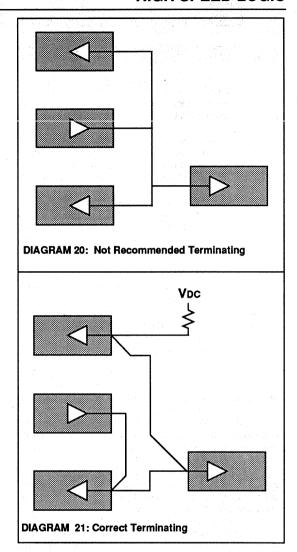

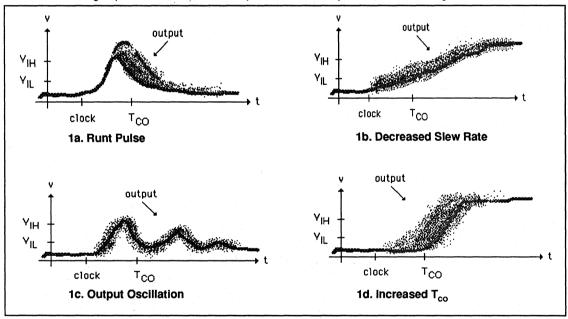

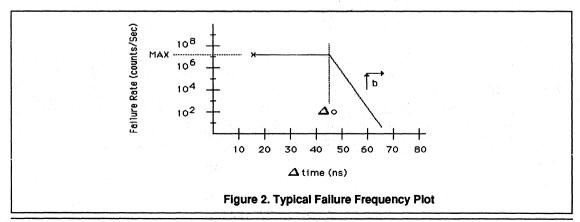

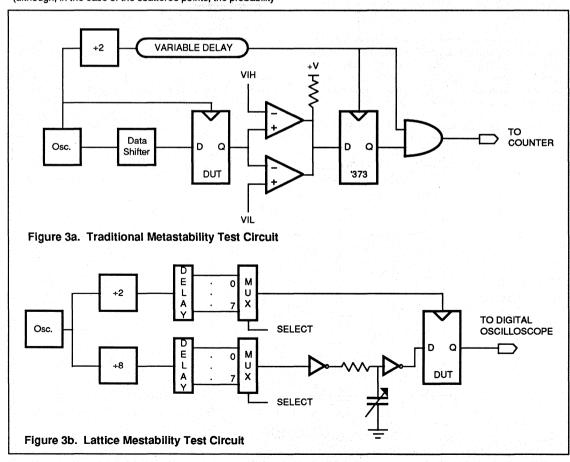

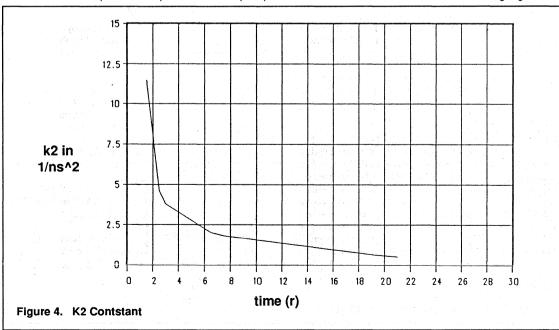

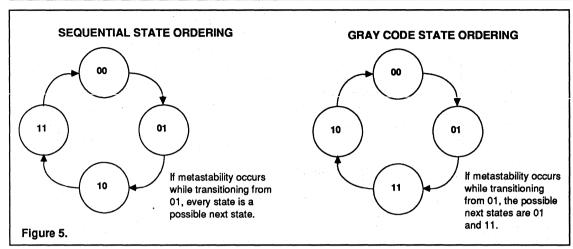

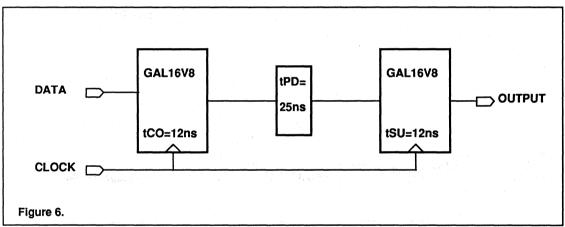

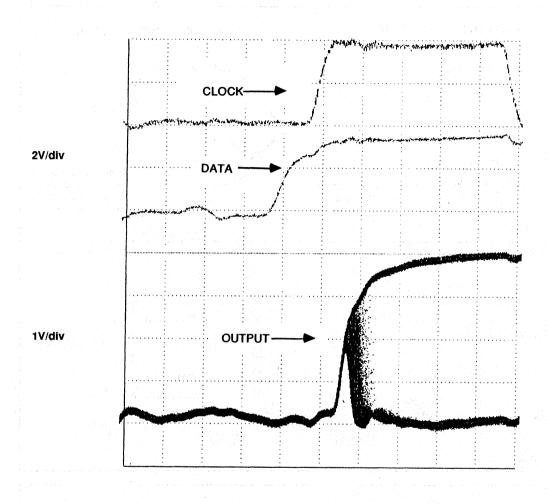

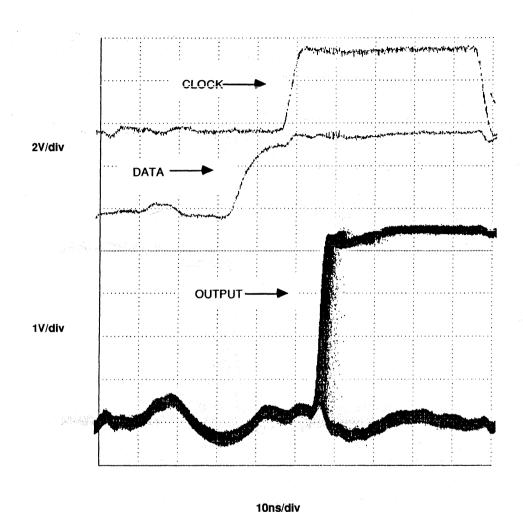

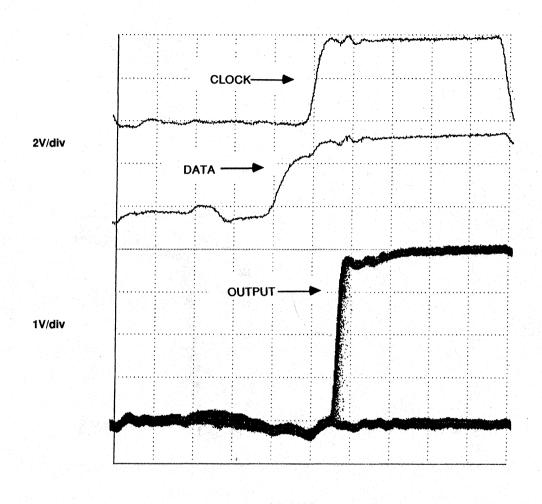

| VIL    | Input Low Voltage         | Asset a market second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Vss - 0.5 | 0.8   | V     |