## 7470 Series

# USER'S MANUAL

#### **FOREWORD**

This users manual describes the hardware function of the CMOS 8-bit single-chip microcomputers, 7470 series. The contents of this manual are Overview, Functional description, Electrical characteristics, Built-in PROM version microcomputers description, Emulator MCU description, and Applications. Please use the "Series MELPS 740 Software Manual" about their instruction set.

#### **CONTENTS**

| 1. | OVERVIEW                                                 | 1    |   |

|----|----------------------------------------------------------|------|---|

|    | 1.1 Overview                                             | 2    |   |

|    | 1.2 7470 series                                          | 3    | į |

|    | 1.3 Functional descriptions                              | 4    | , |

|    | 1.4 Pin configuration                                    | 6    | į |

|    | 1.5 Pin description                                      |      |   |

|    | 1.6 Block diagram                                        |      |   |

| 2. | FUNCTIONAL DESCRIPTION                                   |      |   |

|    | 2.1 Central processing unit (CPU)                        |      |   |

|    | 2.1.1 Accumulator (A)                                    |      |   |

|    | 2.1.2 Index register X (X), index register Y (Y)         |      |   |

|    | 2.1.3 Stack pointer (S)                                  |      |   |

|    | 2.1.4 Program counter (PC)                               | 16   |   |

|    | 2.1.5 Processor status register (PS)                     |      |   |

|    | 2.2 Access area                                          |      |   |

|    |                                                          |      |   |

|    | 2.2.1 Zero page                                          |      |   |

|    | 2.2.2 Special page                                       |      |   |

|    | 2.3 Memory map                                           |      |   |

|    | 2.4 Input/Output ports                                   |      |   |

|    | 2.4.2 Pin description                                    |      |   |

|    | 2.4.2 Fill description 2.5 Interrupts                    |      |   |

|    | 2.5 Interrupts 2.5.1 Interrupt causes                    |      |   |

|    |                                                          |      |   |

|    | 2.5.2 Interrupt control                                  |      |   |

|    |                                                          |      |   |

|    | 2.5.4 Timing after interrupt                             |      |   |

|    | 2.6 Timers                                               |      |   |

|    | 2.6.1 Timer 1, timer 2, timer 3 and timer 4              |      |   |

|    |                                                          |      |   |

|    | 2.6.3 Input latch function                               |      |   |

|    | 2.7 Serial I/O                                           |      |   |

|    | 2.7.1 Structure of serial I/O section                    |      |   |

|    | 2.7.2 Serial I/O data receive                            |      |   |

|    | 2.7.3 Serial I/O data transmit                           |      |   |

|    | 2.7.4 Byte specification mode                            |      |   |

|    | 2.7.5 SRDY signal and SARDY signal                       |      |   |

|    | 2.8 A-D converter                                        |      |   |

|    | 2.8.1 Block description                                  |      |   |

|    | 2.8.2 Method of use                                      |      |   |

|    | 2.8.3 Operation                                          |      |   |

|    | 2.8.4 Definition of A-D conversion precision             |      |   |

|    | 2.9 Key on wake up                                       |      |   |

|    | 2.10 Reset circuit                                       |      |   |

|    | 2.10.1 Reset operation                                   |      |   |

|    | 2.10.2 Internal status of microcomputer at reset release | .74  |   |

|    | 2.11 Oscillation circuit                                 |      |   |

|    | 2.11.1 Oscillation circuit                               |      |   |

|    | 2.11.2 Oscillating circuit for clock-function clock      |      |   |

|    | 2.12 Low power consumption modes                         |      |   |

|    | 2.12.1 Stop mode                                         | .78  | i |

|    | 2.12.2 Wait mode                                         | . 79 |   |

|    | 2.13 Status transitions                                  | .80  | į |

|    |                                                          |      |   |

| 3.ELECTRIC CHARACTERISTICS                                                                  | 83   |

|---------------------------------------------------------------------------------------------|------|

| 3.1 Electric characteristics of M37470M2-XXXSP, M37470M4-XXXSP, and M37470M8-XXXSP          | 84   |

| 3.2 Electric characteristics of M37471M2-XXXSP/FP, M37471M4-XXXSP/FP, and M37471M8-XXXSP/FP | 87   |

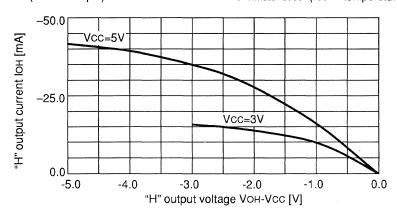

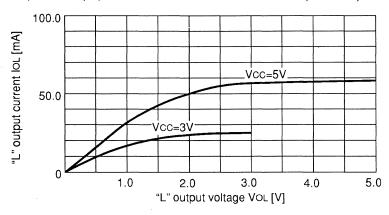

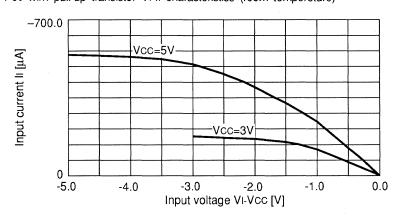

| 3.3 Standard characteristics                                                                |      |

| 4.BUILT-IN PROGRAMMABLE ROM VERSION                                                         | 91   |

| 4.1 Overview                                                                                | 92   |

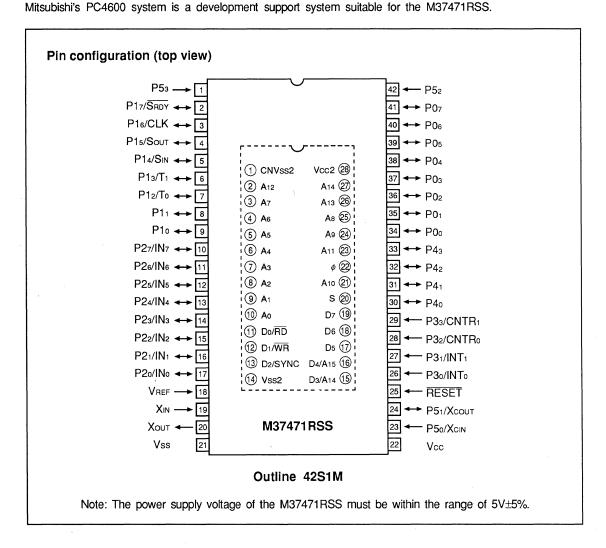

| 4.2 Pin configuration                                                                       | 93   |

| 4.3 Block diagram                                                                           | 95   |

| 4.4 EPROM mode                                                                              | 98   |

| 4.4.1 EPROM mode                                                                            | 98   |

| 4.4.2 Pin description                                                                       |      |

| 4.4.3 Reading, writing, and erasure of built-in PROM                                        | .102 |

| 4.4.4 Notes on handling                                                                     | .103 |

| 4.5 Electric Characteristics                                                                |      |

| 4.5.1 Electric characteristics of M37470E4-XXXSP and M37470E8-XXXSP                         |      |

| 4.5.2 Electric characteristics of M37471E4-XXXSP/FP, M37471E8-XXXSP/FP and M37471E8SS       |      |

| APPENDIX                                                                                    |      |

| Appendix 1 Handling of unused pins                                                          |      |

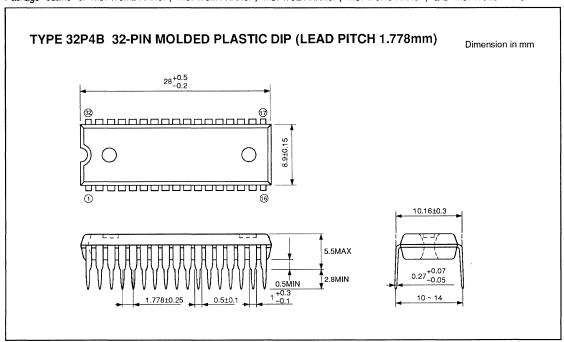

| Appendix 2 Package outline                                                                  |      |

| Appendix 3 Notes for usage                                                                  |      |

| Appendix 4 7470 series memory map                                                           |      |

| Appendix 5 SFR memory map                                                                   |      |

| Appendix 6 Control registers                                                                |      |

| Appendix 7 Machine language instruction table                                               |      |

| Appendix 8 Instruction code table                                                           |      |

| Appendix 9 Mask ROM ordering method                                                         |      |

| Appendix 10 Emulator MCU M37471RSS                                                          |      |

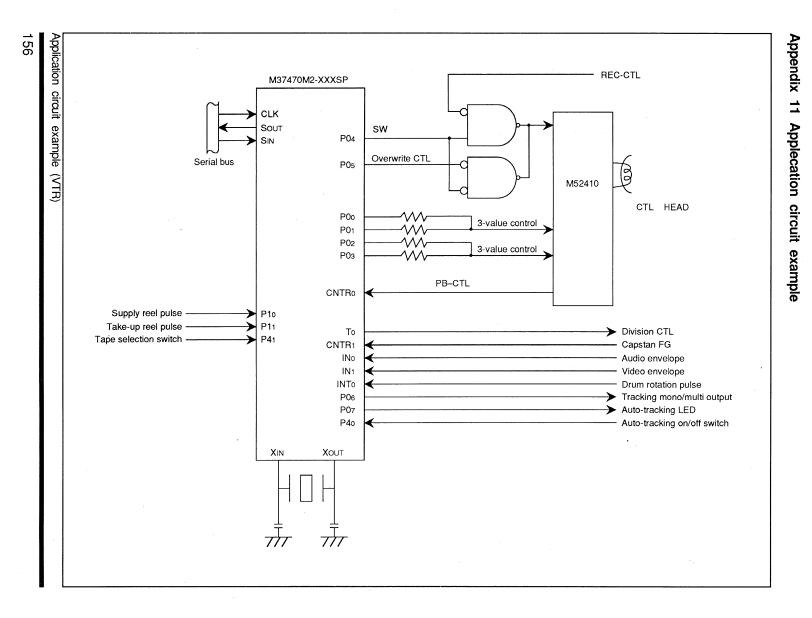

| Appendix 11 Applecation circuit example                                                     | .156 |

#### **FIGURES**

| Fig.1.4.1  | Pin configuration (M37470M2-XXXSP, M37470M4-XXXSP, and M37470M8-XXXSP)                |    |

|------------|---------------------------------------------------------------------------------------|----|

| Fig.1.4.2  | Pin configuration (M37471M2-XXXSP, M37471M4-XXXSP, and M37471M8-XXXSP)                | 7  |

| Fig.1.4.3  | Pin configuration (M37471M2-XXXFP, M37471M4-XXXFP, and M37471M8-XXXFP)                |    |

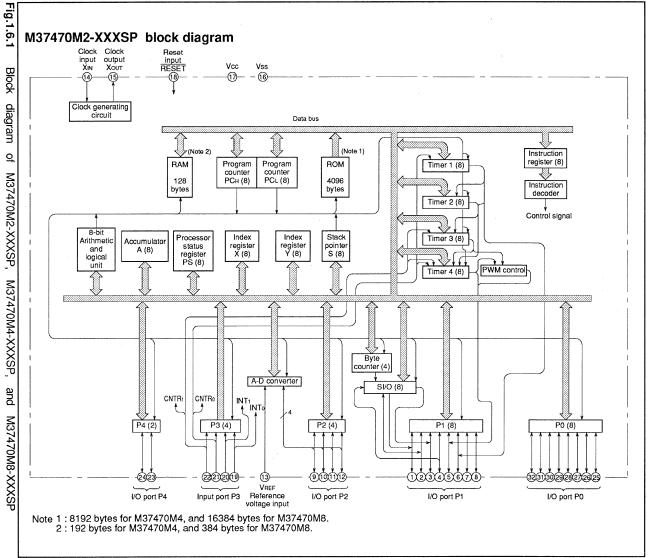

| Fig.1.6.1  | Block diagram of M37470M2-XXXSP, M37470M4-XXXSP, and M37470M8-XXXSP                   |    |

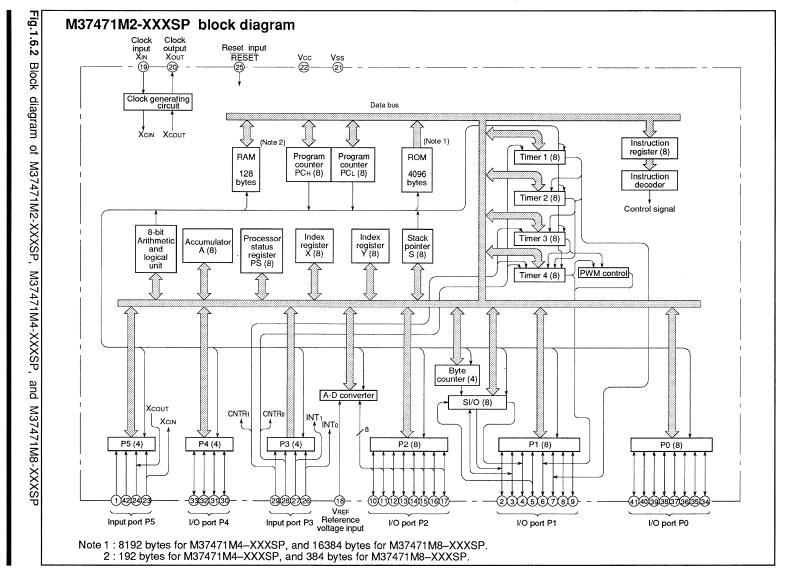

| Fig.1.6.2  | Block diagram of M37471M2-XXXSP, M37471M4-XXXSP, and M37471M8-XXXSP                   |    |

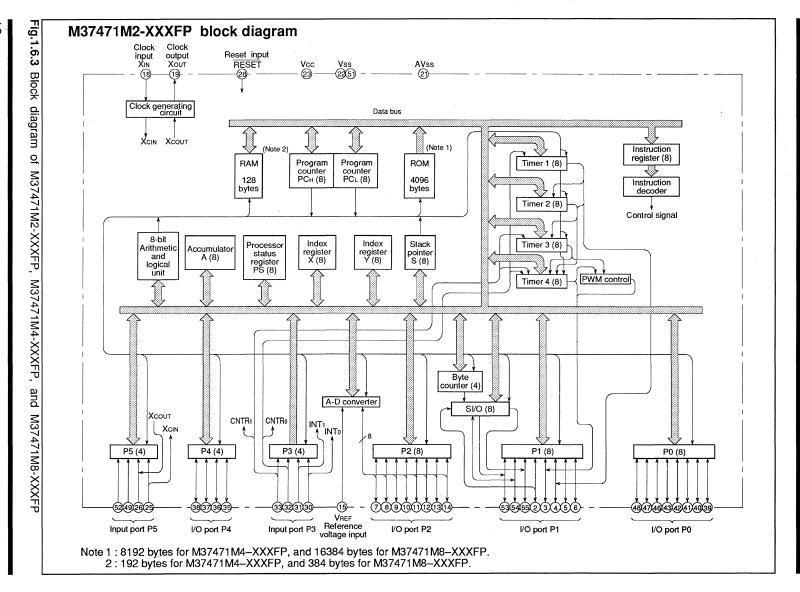

| Fig.1.6.3  | Block diagram of M37471M2-XXXFP, M37471M4-XXXFP, and M37471M8-XXXFP                   | 12 |

| Fig.2.1.1  | Register structure                                                                    |    |

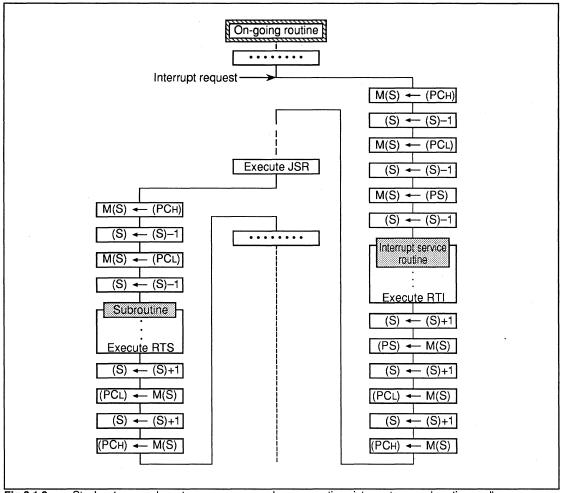

| Fig.2.1.2  | Stack store and restore sequence when executing interrupt or subroutine calls         | 16 |

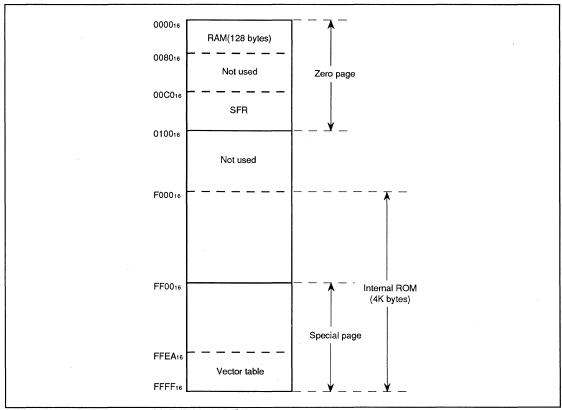

| Fig.2.2.1  | Access area (M37470M2-XXXSP)                                                          |    |

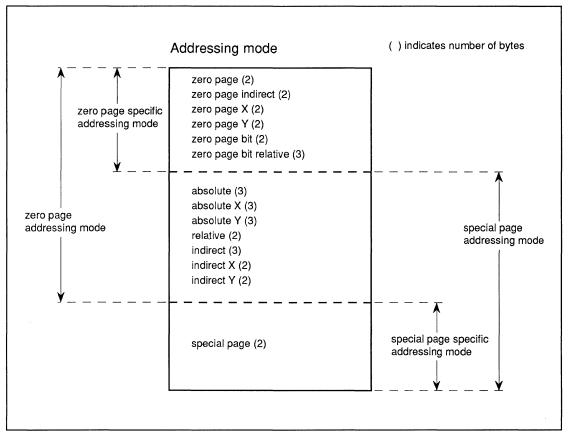

| Fig.2.2.2  | Zero page and special page addressing mode                                            | 19 |

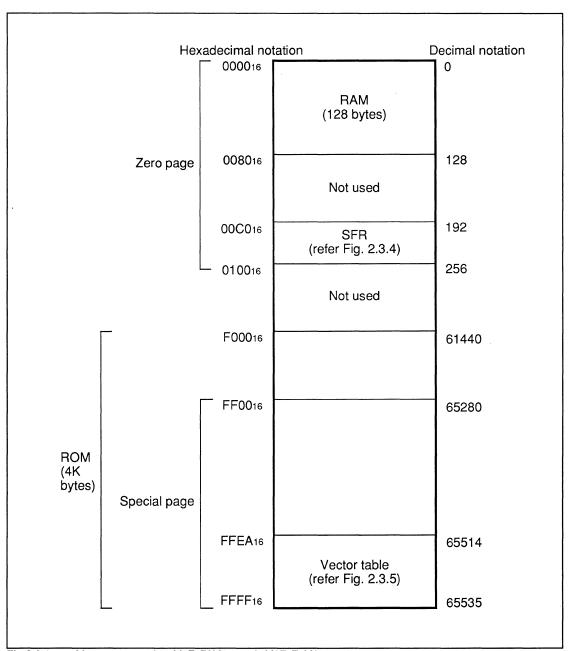

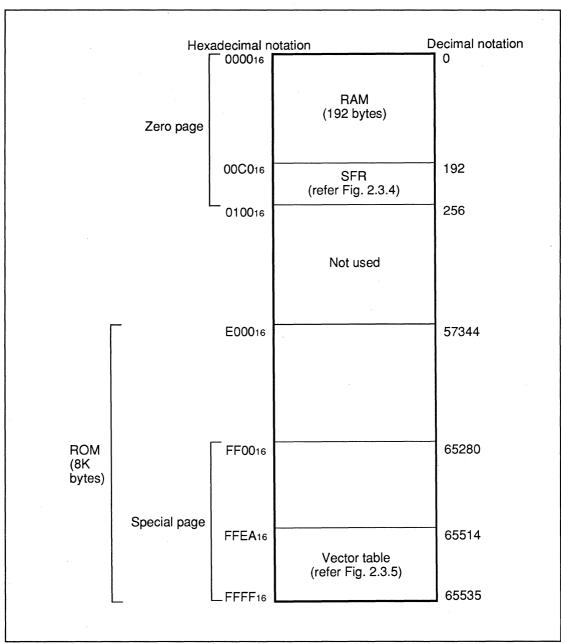

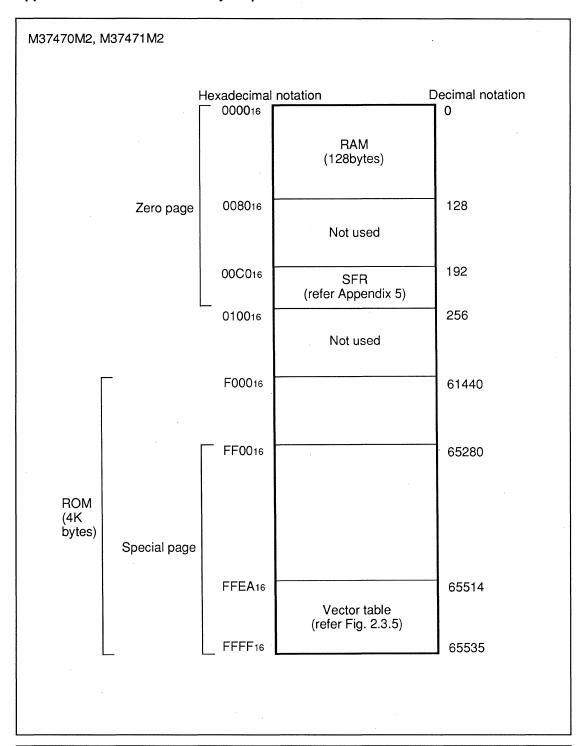

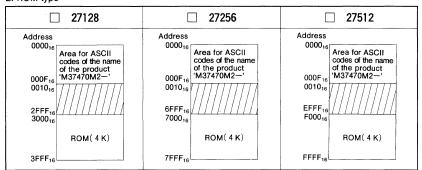

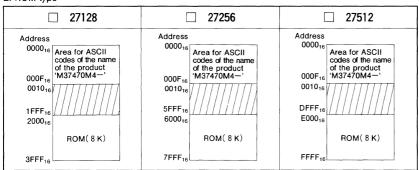

| Fig.2.3.1  | Memory map for M37470M2, and M37471M2                                                 | 21 |

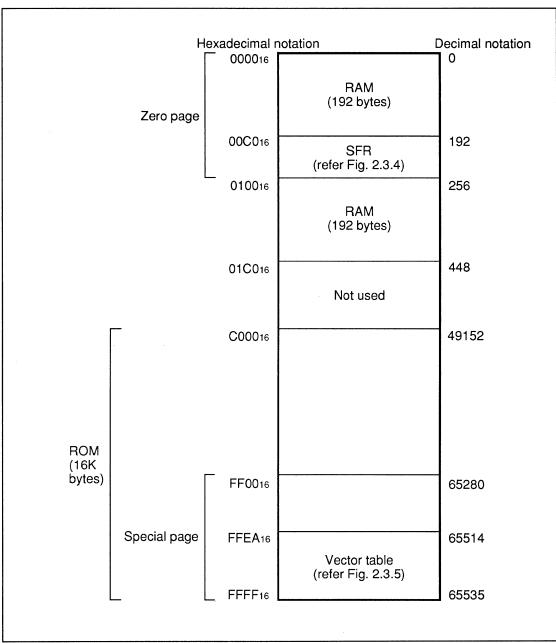

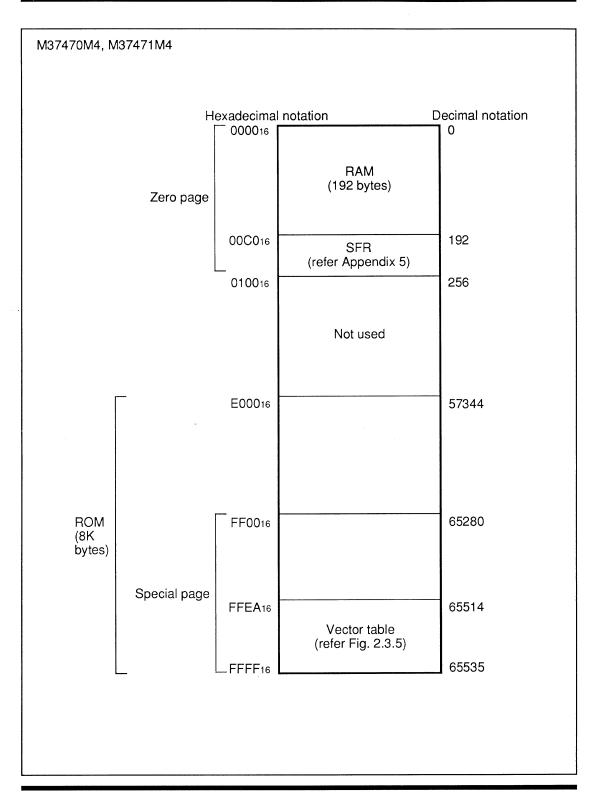

| Fig.2.3.2  | Memory map for M37470M4, and M37471M4                                                 |    |

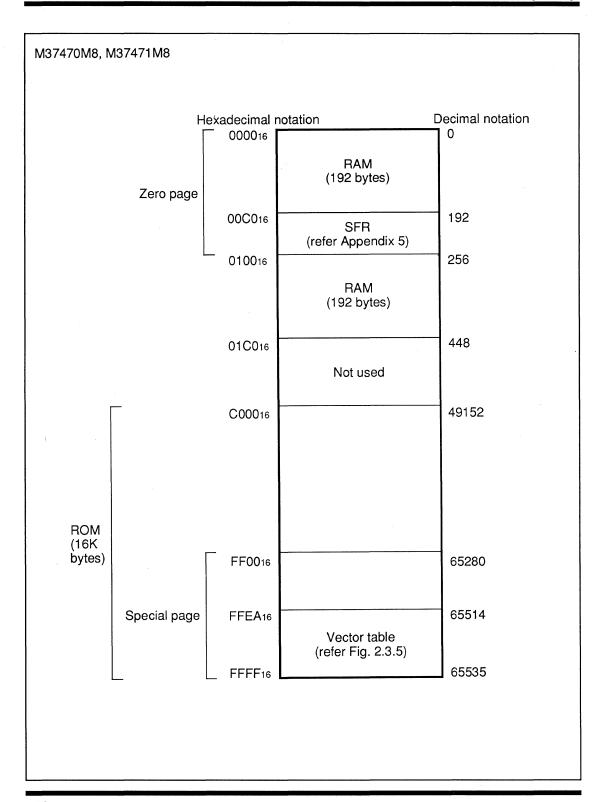

| Fig.2.3.3  | Memory map for M37470M8, and M37471M8                                                 |    |

| Fig.2.3.4  | SFR memory map                                                                        | 24 |

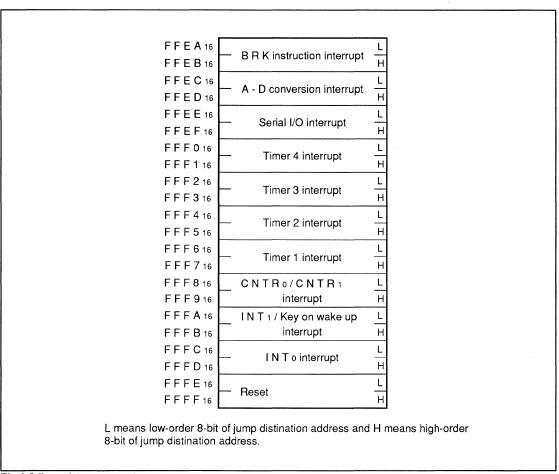

| Fig.2.3.5  | Interrupt vector area memory map                                                      |    |

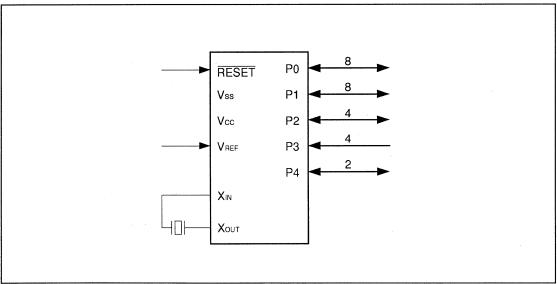

| Fig.2.4.1  | I/O ports of M37470M2, M37470M4, and M37470M8                                         | 26 |

| Fig.2.4.2  | I/O ports of M37471M2, M37471M4, and M37471M8                                         | 26 |

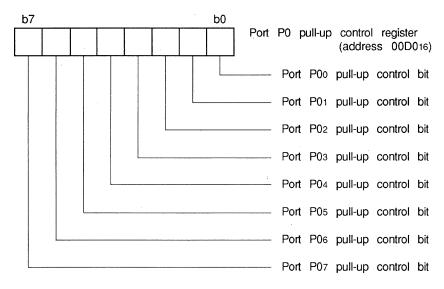

| Fig.2.4.3  | Structure of port P0 pull-up control register                                         |    |

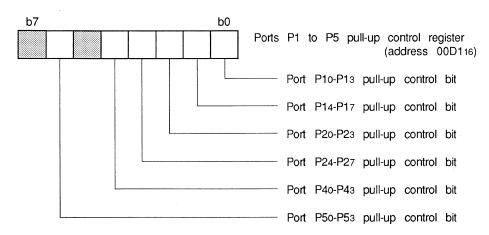

| Fig.2.4.4  | Structure of ports P1 to P5 pull-up control register                                  | 28 |

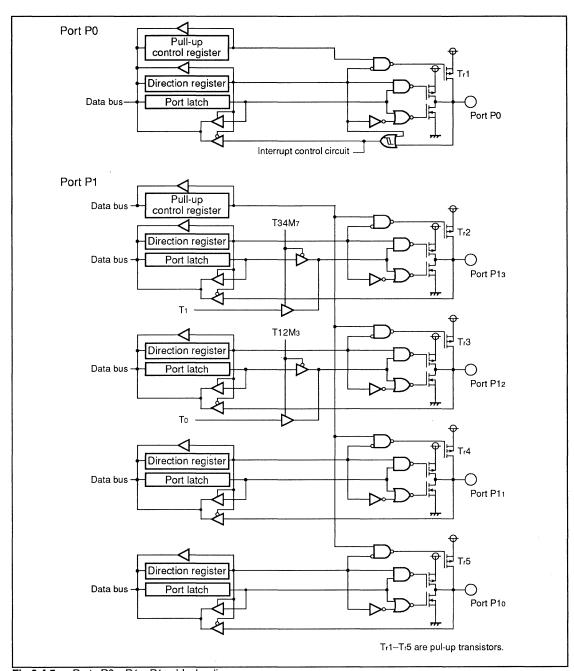

| Fig.2.4.5  | Port P0, P10-P13 block diagram                                                        | 31 |

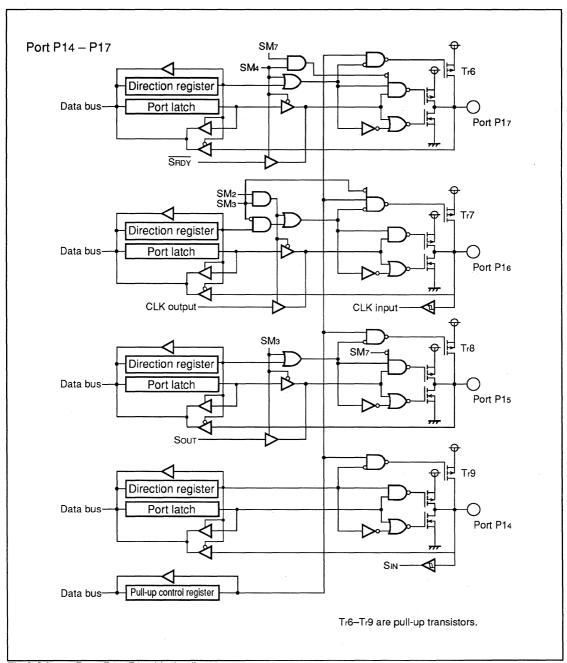

| Fig.2.4.6  | Port P14-P17 block diagram                                                            | 32 |

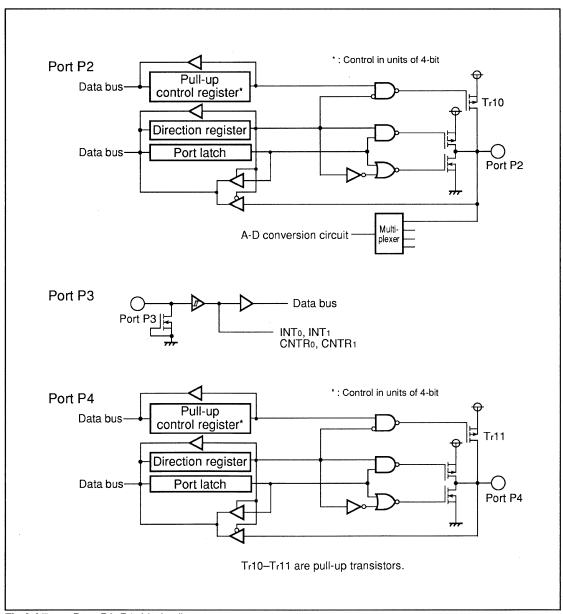

| Fig.2.4.7  | Port P2-P4 block diagram                                                              | 33 |

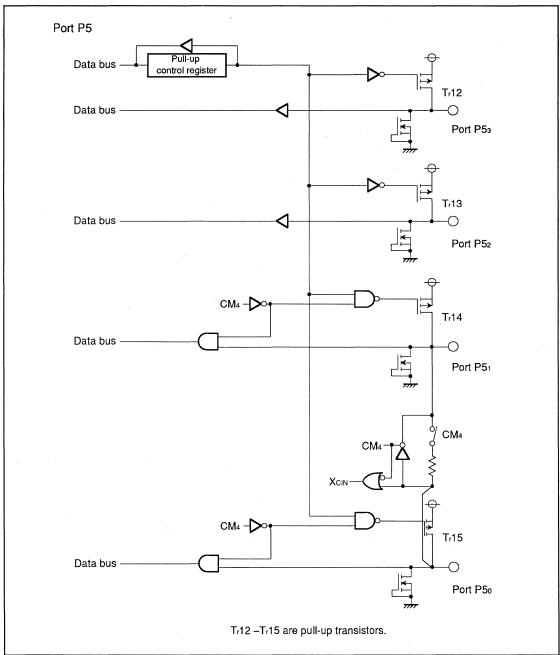

| Fig.2.4.8  | Port P5 block diagram                                                                 | 34 |

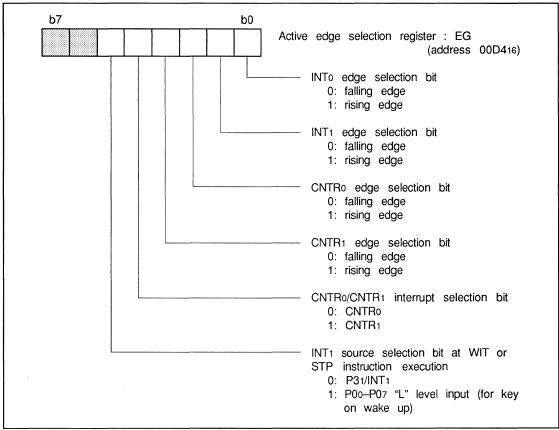

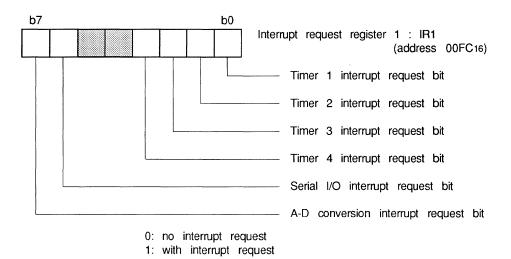

| Fig.2.5.1  | Structure of interrupt related registers (1)                                          | 37 |

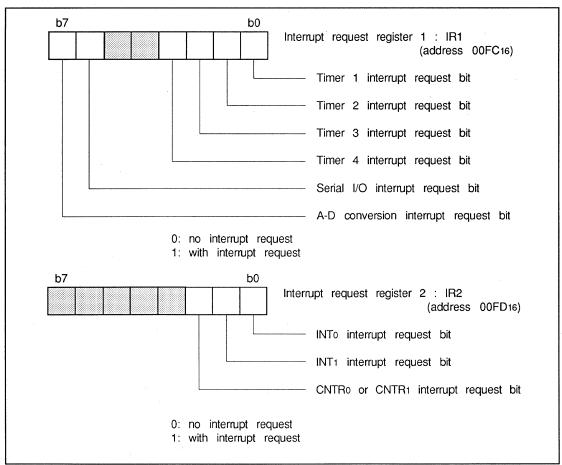

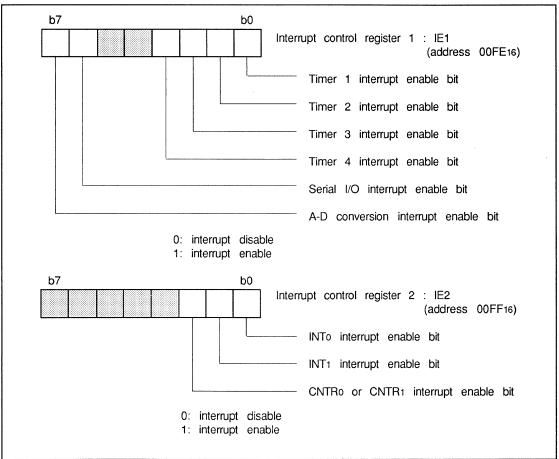

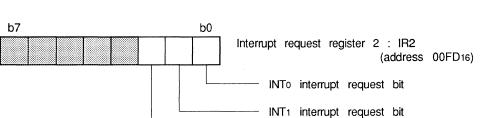

| Fig.2.5.2  | Structure of interrupt related registers (2)                                          | 38 |

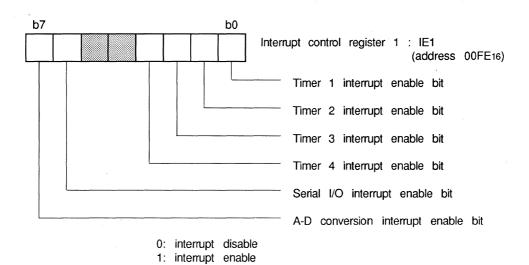

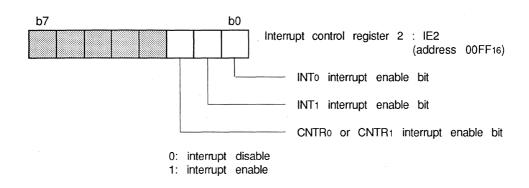

| Fig.2.5.3  | Structure of interrupt related registers (3)                                          | 39 |

| Fig.2.5.4  | Interrupt control                                                                     | 40 |

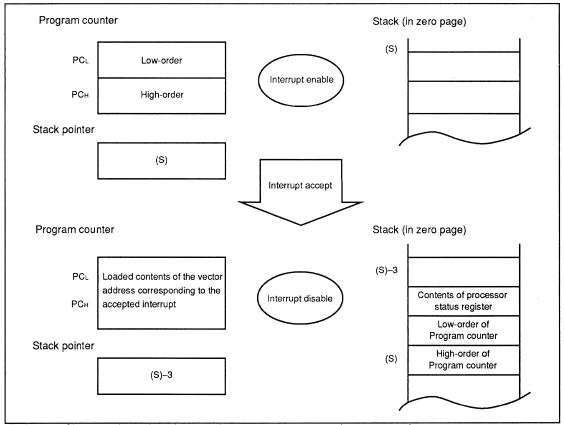

| Fig.2.5.5  | Change of stack pointer and program counter at interrupt receive                      | 41 |

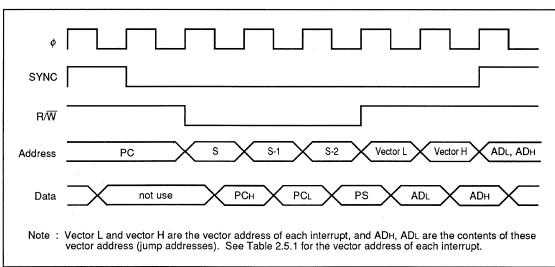

| Fig.2.5.6  | Timing chart after interrupt                                                          |    |

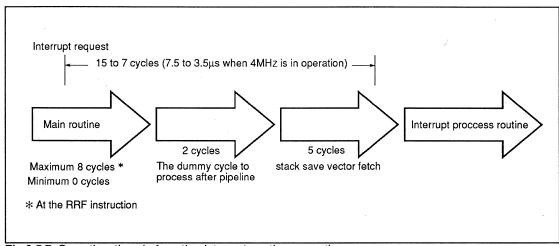

| Fig.2.5.7  | Operation time before the interrupt routine execution                                 | 42 |

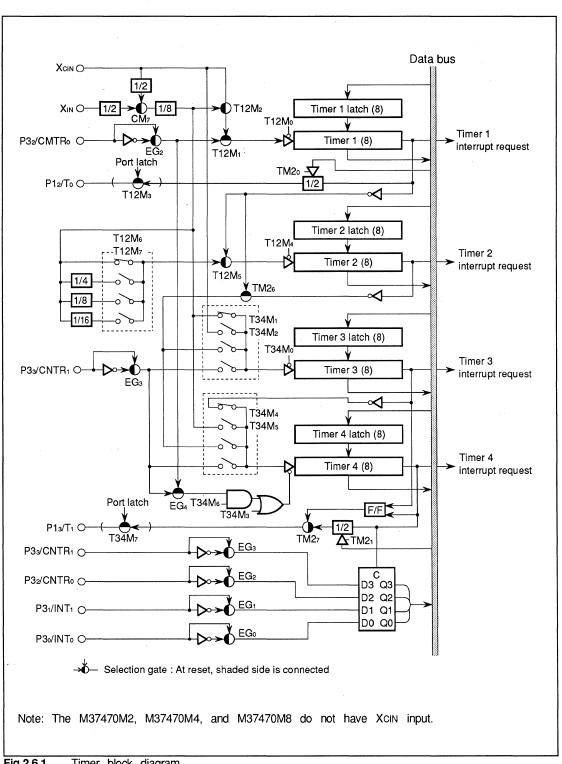

| Fig.2.6.1  | Timer block diagram                                                                   | 44 |

| Fig.2.6.2  | Timer count timing                                                                    | 45 |

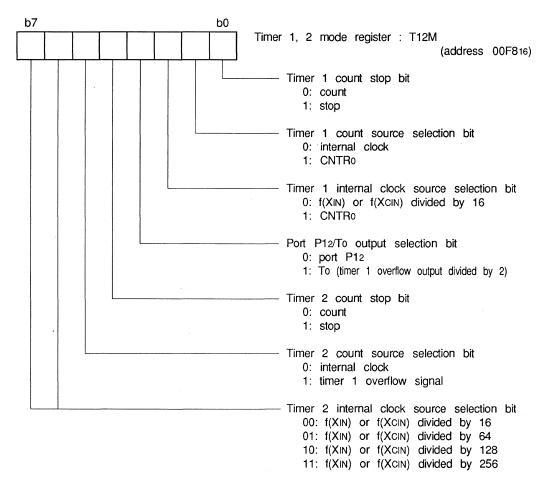

| Fig.2.6.3  | Structure of timer 1, 2 mode register                                                 | 46 |

| Fig.2.6.4  | Timing chart for timer 2 when its count source is timer 1 overflow signal             | 47 |

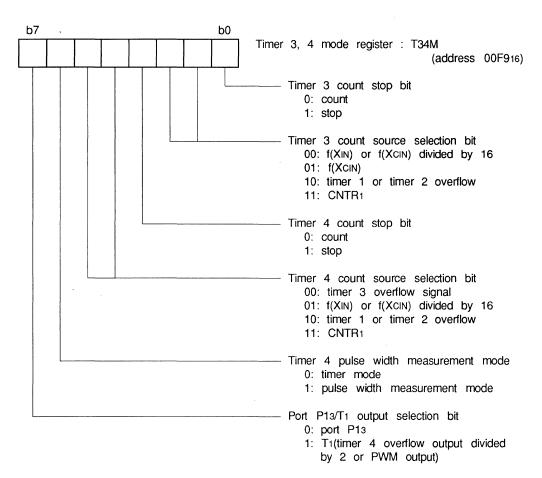

| Fig.2.6.5  | Structure of timer 3, 4 mode register                                                 | 49 |

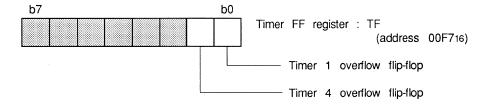

| Fig.2.6.6  | Structure of timer FF register                                                        | 49 |

| Fig.2.6.7  | PWM waveform                                                                          | 51 |

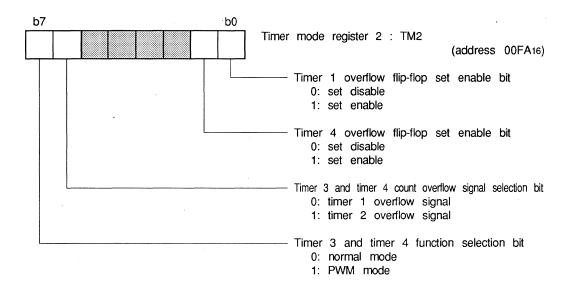

| Fig.2.6.8  | Structure of timer mode register 2                                                    | 51 |

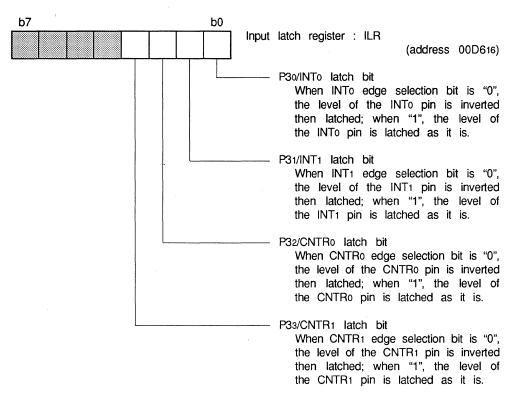

| Fig.2.6.9  | Structure of input latch register                                                     | 52 |

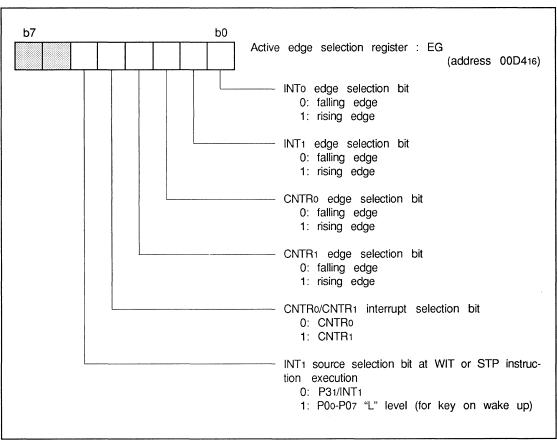

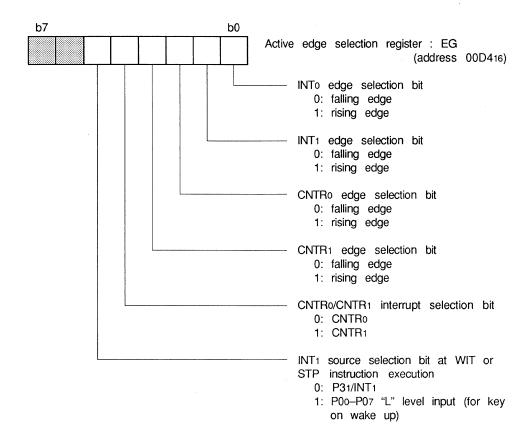

| Fig.2.6.10 | Structure of active edge selection register                                           | 53 |

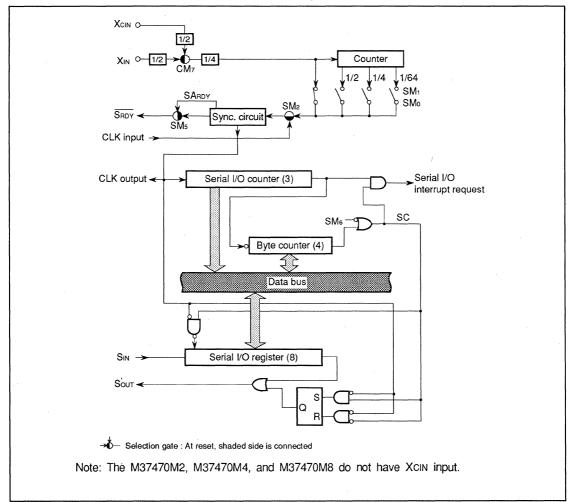

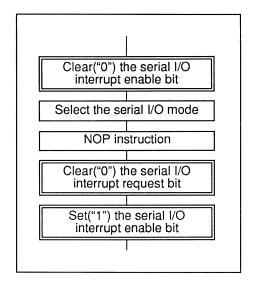

| Fig.2.7.1  | Serial I/O block diagram                                                              | 54 |

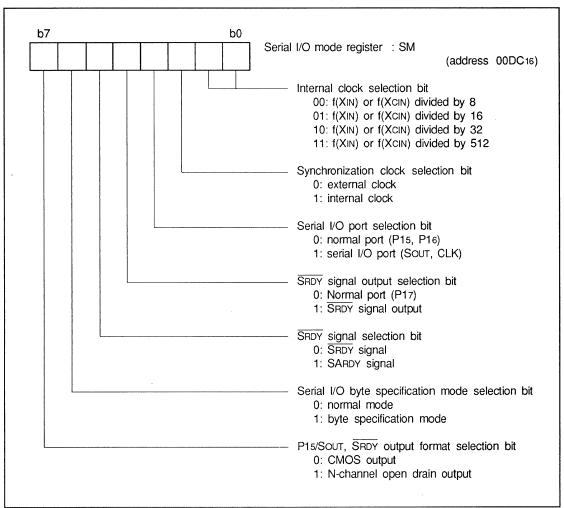

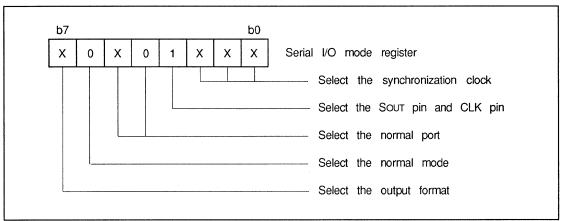

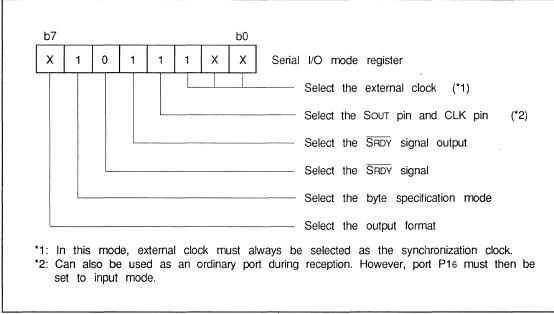

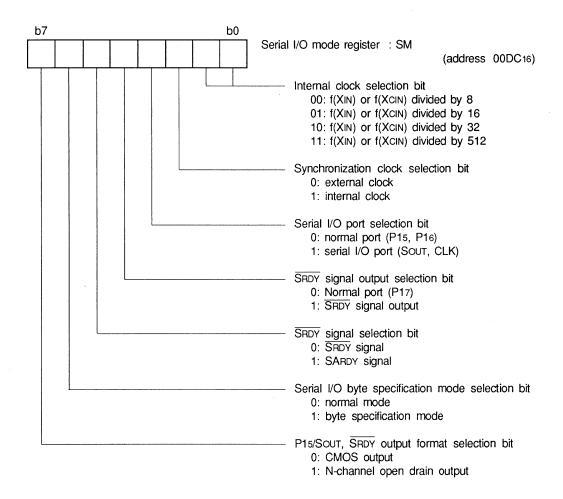

| Fig.2.7.2  | Structure of serial I/O mode register                                                 | 55 |

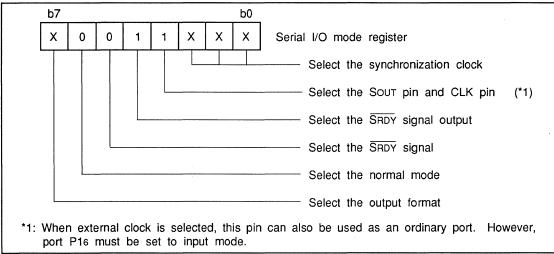

| Fig.2.7.3  | Example of the serial I/O mode register setting (data receive)                        | 56 |

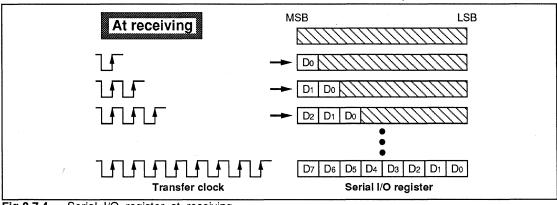

| Fig.2.7.4  | Serial I/O register at receiving                                                      | 56 |

| Fig.2.7.5  | Example of the serial I/O mode register setting (data transmit)                       | 57 |

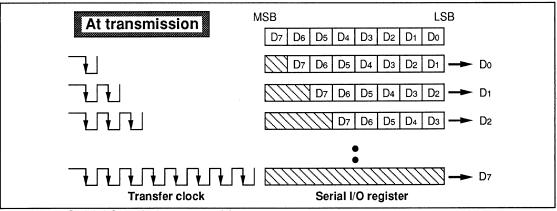

| Fig.2.7.6  | Serial I/O register at transmitting                                                   | 57 |

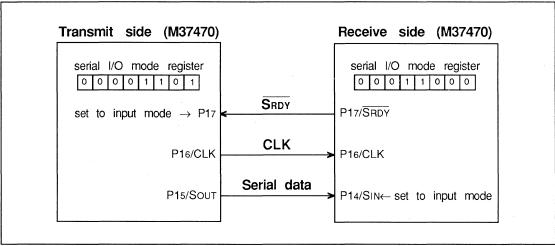

| Fig.2.7.7  | Connection example of serial I/O transfer (normal mode)                               | 58 |

| Fig.2.7.8  | Serial I/O data transfer operation sequence (normal mode)                             | 59 |

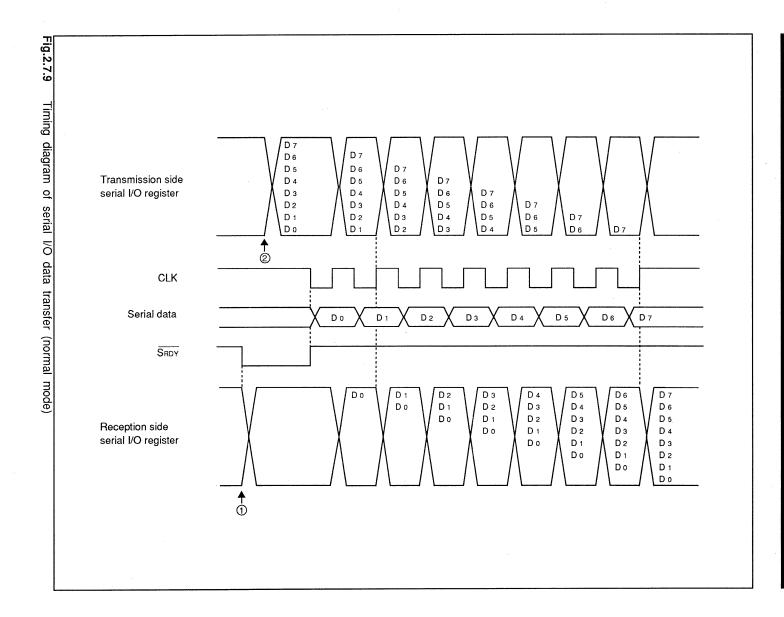

| Fig.2.7.9  | Timing diagram of serial I/O data transfer (normal mode)                              | 60 |

| Fig.2.7.10 | Example of the serial I/O mode register setting (byte specification mode)             |    |

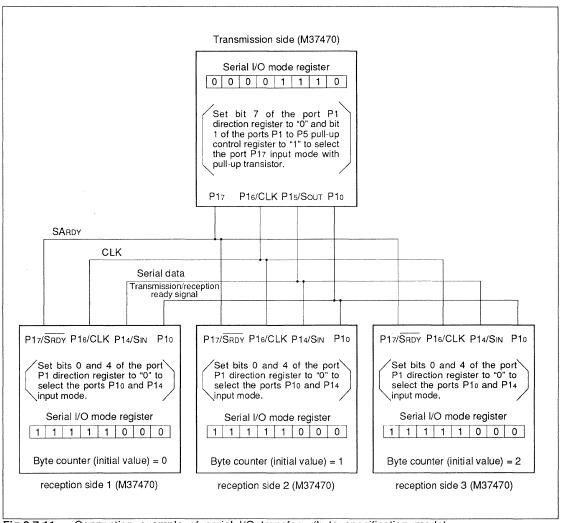

| Fig.2.7.11 | Connection example of serial I/O transfer (byte specification mode)                   | 63 |

| Fig.2.7.12 | Serial I/O data transfer operation sequence (byte specification mode)                 | 64 |

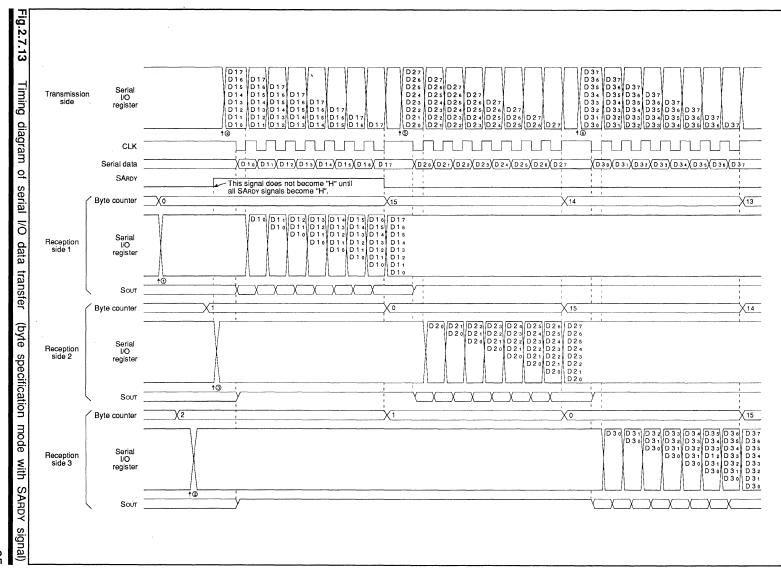

| Fig.2.7.13 | Timing diagram of serial I/O data transfer(byte specification mode with SARDY signal) | 65 |

|            |                                                                                       |    |

#### **CONTENTS**

#### **FIGURES**

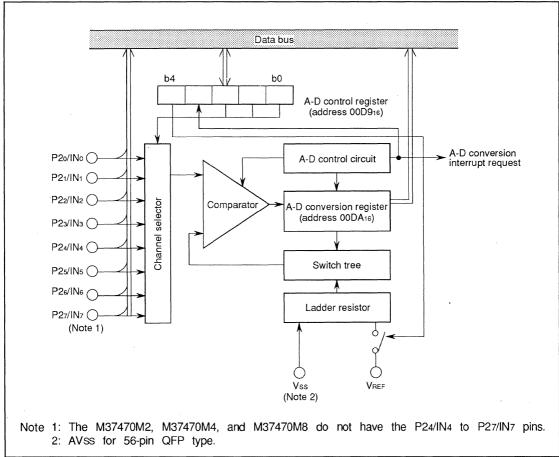

| Fig.2.8.1  | A-D converter block diagram                                                | 66  |

|------------|----------------------------------------------------------------------------|-----|

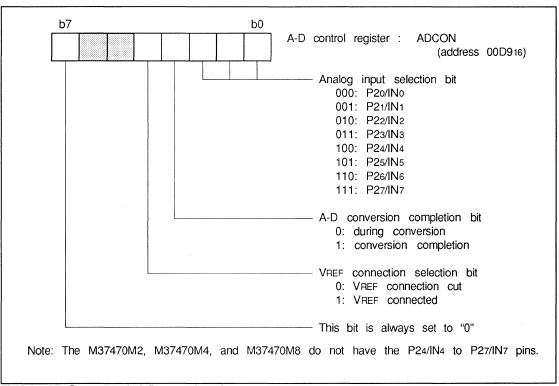

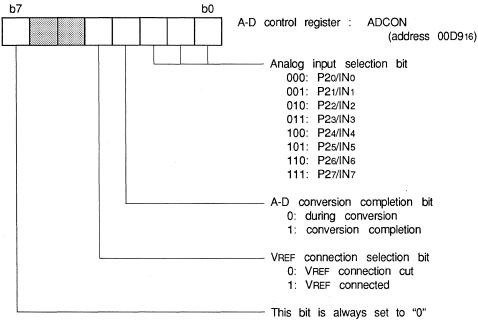

| Fig.2.8.2  | Structure of A-D control register                                          | 67  |

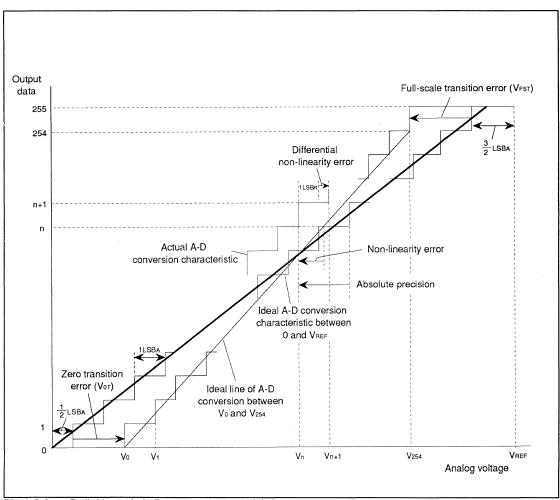

| Fig.2.8.3  | Definition of A–D conversion precision                                     | 71  |

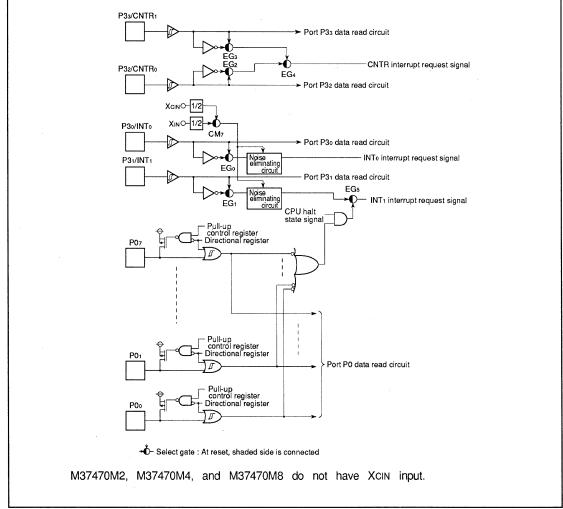

| Fig.2.9.1  | Block diagram of interrupt input and key on wake up circuit                | 72  |

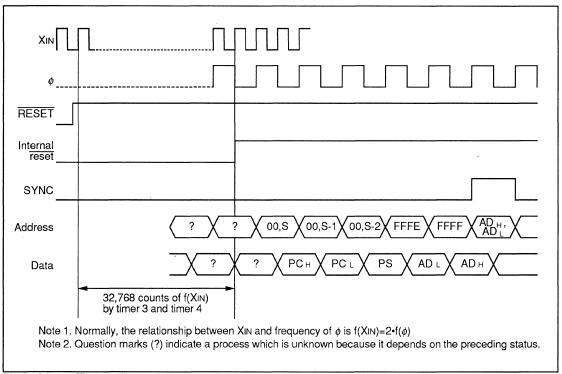

| Fig.2.10.1 | Timing diagram at reset                                                    |     |

| Fig.2.10.2 | Internal status of microcomputer at reset release                          |     |

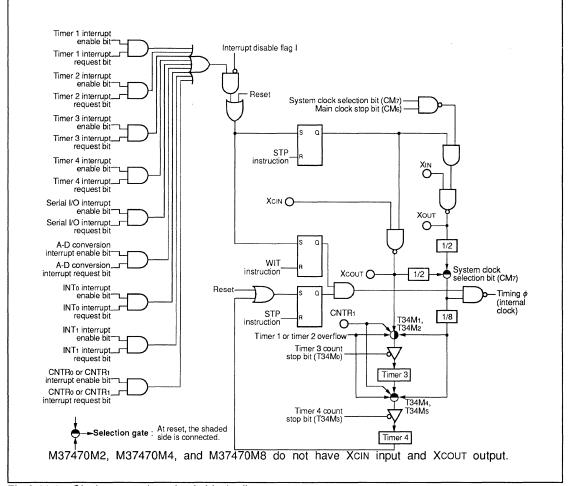

| Fig.2.11.1 | Clock generation circuit block diagram                                     | 75  |

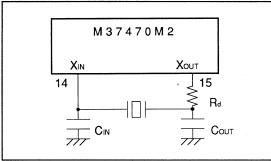

| Fig.2.11.2 | Oscillation circuit using ceramic resonator or crystal oscillator (M37470) | 76  |

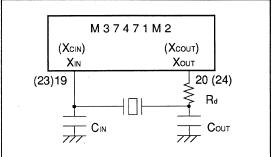

| Fig.2.11.3 | Oscillation circuit using ceramic resonator or crystal oscillator (M37471) |     |

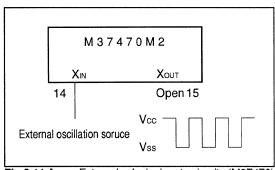

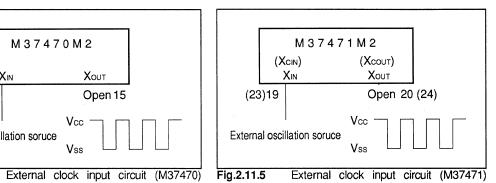

| Fig.2.11.4 | External clock input circuit (M37470)                                      | 76  |

| Fig.2.11.5 | External clock input circuit (M37471)                                      | 76  |

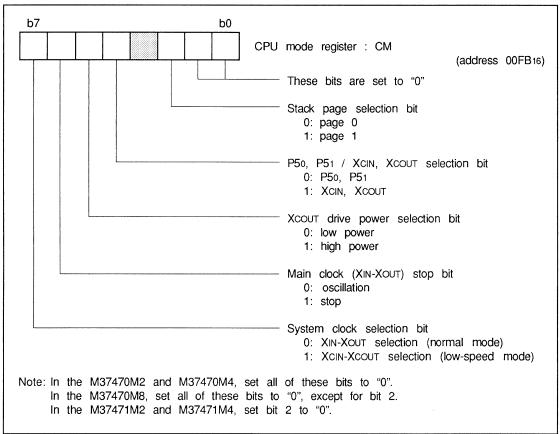

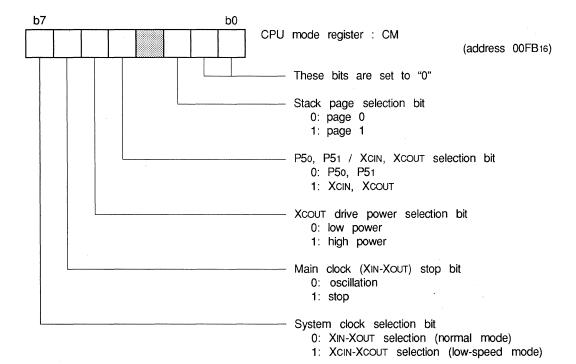

| Fig.2.11.6 | Structure of CPU mode register                                             | 76  |

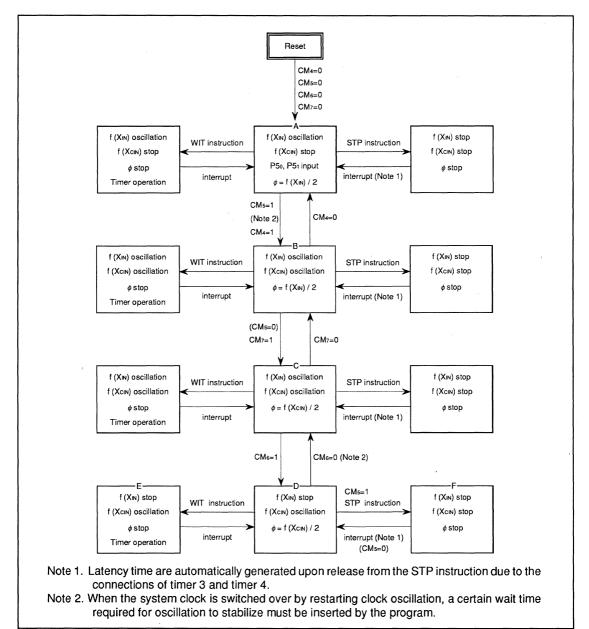

| Fig.2.13.1 | Status transitions                                                         | 80  |

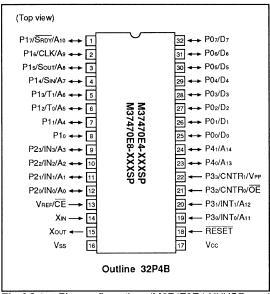

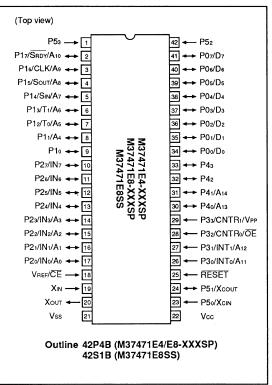

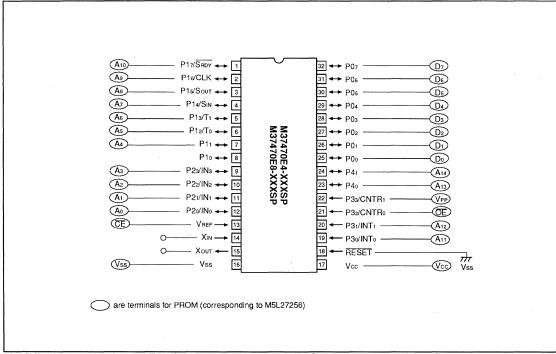

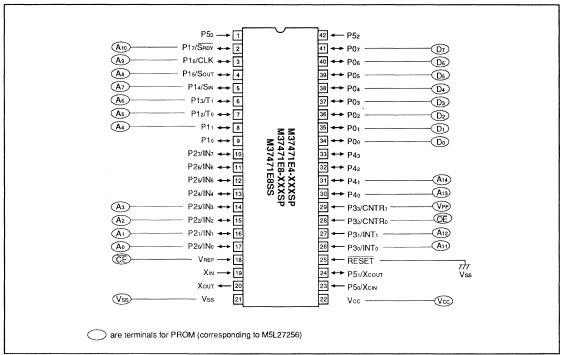

| Fig.4.2.1  | Pin configuration (M37470E4-XXXSP and M37470E8-XXXSP)                      | 93  |

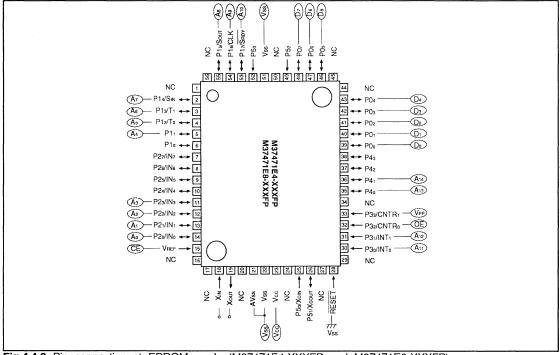

| Fig.4.2.2  | Pin configuration (M37471E4-XXXSP, M37471E8-XXXSP and M37471E8SS)          |     |

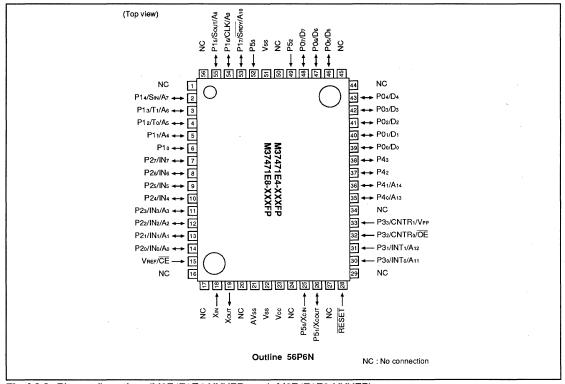

| Fig.4.2.3  | Pin configuration (M37471E4-XXXFP and M37471E8-XXXFP)                      |     |

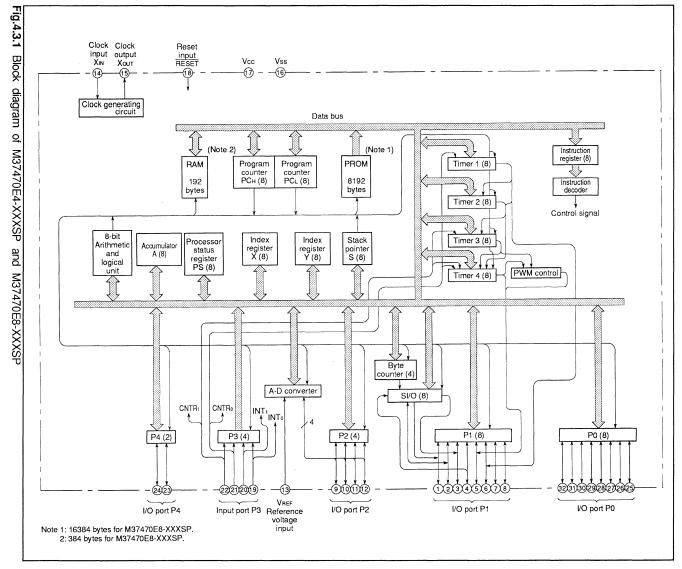

| Fig.4.3.1  | Block diagram of M37470E4-XXXSP and M37470E8-XXXSP                         |     |

| Fig.4.3.2  | Block diagram of M37471E4-XXXSP and M37471E8-XXXSP(M37471E8SS)             |     |

| Fig.4.3.3  | Block diagram of M37471E4-XXXFP and M37471E8-XXXFP                         |     |

| Fig.4.4.1  | Pin connection at EPROM mode (M37470E4-XXXSP and M37470E8-XXXSP)           |     |

| Fig.4.4.2  | Pin connection at EPROM mode (M37471E4-XXXSP, M37471E8-XXXSP and M37471E8  |     |

| Fig.4.4.3  | Pin connection at EPROM mode (M37471E4-XXXFP and M37471E8-XXXFP)           |     |

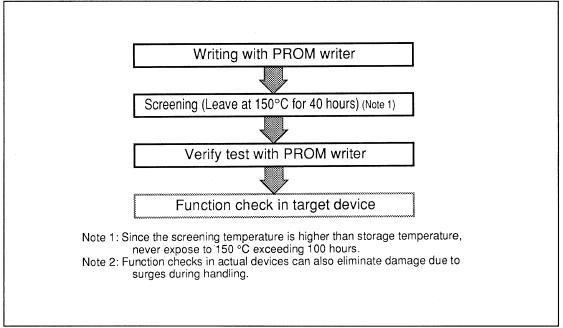

| Fig.4.4.4  | Writing and test for blank one-time programmable type                      | 103 |

#### **TABLES**

| Table | 1.2.1         | 7470 series                                                                    | 3    |

|-------|---------------|--------------------------------------------------------------------------------|------|

| Table | 1.3.1         | Functions of M37470M2-XXXSP, M37470M4-XXXSP, and M37470M8-XXXSP                | 4    |

| Table | 1.3.2         | Functions of M37471M2-XXXSP/FP, M37471M4-XXXSP/FP, and M37471M8-XXXSP/FP       | 5    |

| Table | 1.5.1         | Pin description                                                                | 9    |

| Table | 2.5.1         | Interrupt vector addresses and priority                                        | 35   |

| Table | 2.7.1         | Corresponding between serial I/O relation ports and serial I/O mode register   | 58   |

| Table | 2.8.1         | Change of A-D conversion register during A-D conversion                        | 69   |

| Table | 2.12.1        | Functions operating in stop mode                                               |      |

| Table | 2.12.2        | Functions operating in wait mode                                               | 79   |

| Table | 4.1. <b>1</b> | Functions of built-in PROM versions (M37470E4-XXXSP, M37470E8-XXXSP, M37471E4- |      |

|       | >             | (XXSP/FP, M37471E8-XXXSP/FP, and M37471E8SS)                                   | 92   |

| Table |               | Pin correspondence at the EPROM mode                                           |      |

| Table | 4.4.2         | Pin description                                                                | .100 |

| Table | 4.4.3         | Input/Output signal at each mode                                               | .102 |

# OVERVIEW

#### 1.1 Overview

The 7470 series are 8-bit single-chip microcomputers created by silicon gate CMOS processing. Built into these microcomputers are:

- MELPS 740 CPU core

- Four 8-bit timers

- Serial I/O function (with multi-connection compatibility)

- A-D converter (successive approximation comparison method)

- Key on wake up function

Designed as compact microcomputers for controlling household appliances and every-day electrical equipment, their reduced power dissipations enabled by the use of CMOS processing also make these microcomputers extremely suitable for applications using battery power.

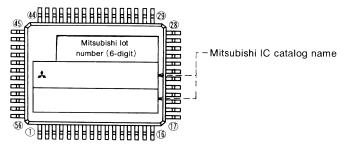

M37471M2-XXXSP chip

#### 1.2 7470 series

The 7470 series is an extended family consisting of the chips listed in Table 1.2.1, with the M37470M2-XXXSP being the base chip. These chips differ only in memory characteristics, memory size, and number of ports, to enable the user to select the chip best suited to the system. Throughout this manual, all of the 7470 series of microcomputers are referred to as the M37470, unless there is a real difference between models.

Table 1.2.1 7470 series

| Tuno           | ROM             | RAM    | I/O   | Input | Analog | Doolsono | Domorko |

|----------------|-----------------|--------|-------|-------|--------|----------|---------|

| Type           | (byte)          | (byte) | ports | ports | input  | Package  | Remarks |

| M37470M2-XXXSP | 4K              | 128    |       |       |        |          |         |

| M37470M4-XXXSP | 8K              | 192    |       |       |        |          | _       |

| M37470M8-XXXSP | 16K             | 384    | }     |       |        |          |         |

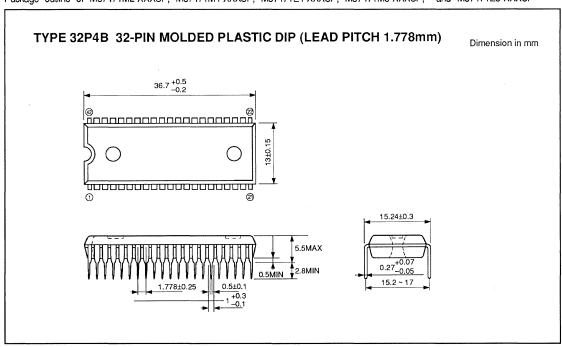

| M37470E4-XXXSP | 8K              | 192    | 22    | 4     | 4      | 32P4B    |         |

| M37470E8-XXXSP | 16K             | 384    | }     |       |        |          | *1      |

| M37470E4SP     | 8K              | 192    | ]     |       |        |          | '       |

| M37470E8SP     | 16K             | 384    |       |       |        |          |         |

| M37471M2-XXXSP | 4K              | 128    |       |       |        |          |         |

| M37471M4-XXXSP | 8K              | 192    |       |       |        | 42P4B    |         |

| M37471M8-XXXSP | 16K             | 384    |       |       |        |          |         |

| M37471M2-XXXFP | 4K              | 128    |       |       |        |          |         |

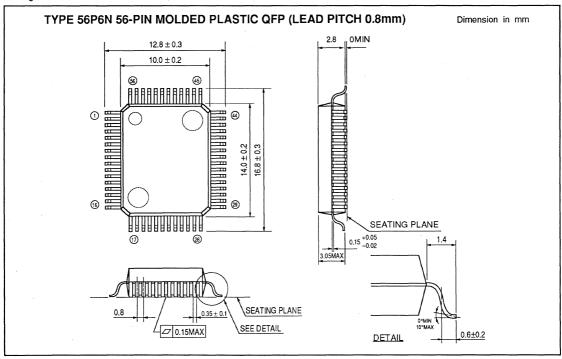

| M37471M4-XXXFP | 8K              | 192    |       |       |        | 56P6N    |         |

| M37471M8-XXXFP | 16K             | 384    |       |       |        |          |         |

| M37471E4-XXXSP | 8K              | 192    |       |       |        | 42P4B    |         |

| M37471E8-XXXSP | 16K             | 384    | 28    | 8     | 8      | 42540    |         |

| M37471E4-XXXFP | 8K              | 192    | ] 20  | 0     | 0      | 56P6N    |         |

| M37471E8-XXXFP | 16K             | 384    |       |       |        | SOFON    | *1      |

| M37471E4SP     | 8K              | 192    |       |       |        | 42P4B    |         |

| M37471E8SP     | 16K             | 384    |       |       |        | 42740    |         |

| M37471E4FP     | 8K              | 192    |       |       |        | 56P6N    |         |

| M37471E8FP     | 16K             | 384    |       |       |        | SOFOIN   |         |

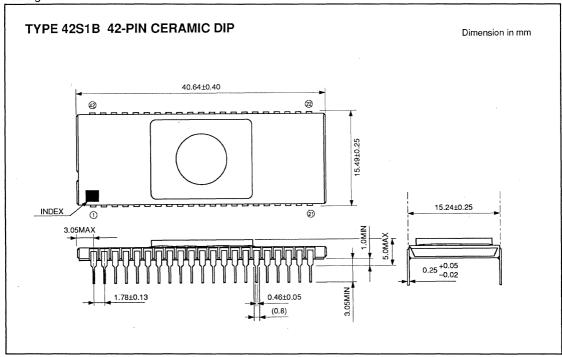

| M37471E8SS     | 16K             | 384    |       |       |        | 42S1B    | *2      |

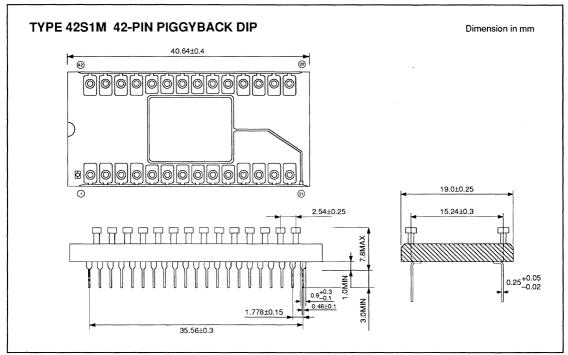

| M37471RSS      | 63.5K<br>(Note) | 384    |       |       |        | 42S1M    | *3      |

- \*1: One-time programmable version

- \*2: Window-type EPROM version

- \*3: Dedicated emulator MCU

Note: Address space that can be used as ROM area

#### (1) One-time programmable version

Non-erasable programs can be written into the internal PROM of this one-time programmable micro-computer. For details of the functions of this version, see Chapter 4, "Built-in programmable ROM version".

#### (2) Window-type EPROM version

Erasable programs can be written into the built-in EPROM of this built-in EPROM microcomputer. For details of the functions of this version, see Chapter 4, "Built-in programmable ROM version".

#### (3) Dedicated MCU for emulator

This dedicated MCU for emulator version is designed for program development—since it makes it easy for the user to develop programs, it is most suitable as an element in the trial manufacture of systems. For details of the functions of this version, see Appendix 11, "Dedicated MCU for emulator M37471RSS".

#### 1.3 Functional descriptions

Table 1.3.1 shows the functional descriptions of M37470M2-XXXSP, M37470M4-XXXSP, and M37470M8-XXXSP. Same as this, the functional description of M37471M2-XXXSP/FP, M37471M4-XXXSP/FP, and M37471M8-XXXSP/FP are shown in Table 1.3.2.

Table 1.3.1 Functions of M37470M2-XXXSP, M37470M4-XXXSP, and M37470M8-XXXSP

| Parame                                              | ter     |                                       | Functions                                                  |  |  |

|-----------------------------------------------------|---------|---------------------------------------|------------------------------------------------------------|--|--|

| Basic instructions                                  |         |                                       | 69                                                         |  |  |

| Instruction execution time                          |         |                                       | 1.0μs (minimum instructions, at 4MHz)                      |  |  |

| Clock frequency                                     |         |                                       | 4MHz                                                       |  |  |

| Memory size                                         | ROM     | M37470M2                              | 4096 bytes                                                 |  |  |

|                                                     |         | M37470M4                              | 8192 bytes                                                 |  |  |

|                                                     |         | M37470M8                              | 16384 bytes                                                |  |  |

|                                                     | RAM     | M37470M2                              | 128 bytes                                                  |  |  |

|                                                     |         | M37470M4                              | 192 bytes                                                  |  |  |

|                                                     |         | M37470M8                              | 384 bytes                                                  |  |  |

| Input/Output ports                                  | P0,P1   | 1/0                                   | 8-bit × 2                                                  |  |  |

|                                                     | P2      | 1/0                                   | 4-bit × 1                                                  |  |  |

|                                                     | P3      | Input                                 | 4-bit × 1                                                  |  |  |

|                                                     | P4      | 1/0                                   | 2-bit × 1                                                  |  |  |

| Serial I/O                                          |         |                                       | 8-bit × 1                                                  |  |  |

| Timers                                              |         |                                       | 8-bit × 4 (with 8-bit latch)                               |  |  |

| A-D converter (successive approximation comparison) |         |                                       | 8-bit × 1 (4-channel)                                      |  |  |

| Interrupts                                          |         |                                       | External 5, internal 6 and software 1                      |  |  |

| Subroutine nesting                                  | M37470  | OM2                                   | 64                                                         |  |  |

|                                                     | M3747   | 0M4                                   | 96                                                         |  |  |

|                                                     | M37470  | 8MC                                   | 192                                                        |  |  |

| Clock generating circuit (Note                      | 1)      |                                       | Built-in with internal feedback resistor                   |  |  |

|                                                     |         |                                       | (connect an external ceramic or quartz crystal oscillator) |  |  |

| Power supply                                        |         |                                       | 2.7 to 5.5V                                                |  |  |

| Power dissipation (typ.)                            |         |                                       | 17.5mW (at 4MHz)                                           |  |  |

| Input/Output characteristics                        | Input/O | utput voltage                         | 5V                                                         |  |  |

|                                                     | Output  | current                               | -5 to 10mA (P0, P1, P2 and P4: CMOS 3-state)               |  |  |

| Operating temperature range                         |         | · · · · · · · · · · · · · · · · · · · | −20 to 85°C                                                |  |  |

| Device structure                                    |         |                                       | CMOS silicon gate                                          |  |  |

| Package                                             |         |                                       | 32-pin shrink plastic molded DIP                           |  |  |

Note 1: Clock generating circuit for clock function is not built-in.

Table 1.3.2 Functions of M37471M2-XXXSP/FP, M37471M4-XXXSP/FP, and M37471M8-XXXSP/FP

| Two built-in with internal feedback resistor (connect an external ceramic or quartz crystal oscillator)                                                   |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3101)                                                                                                                                                     |  |  |

|                                                                                                                                                           |  |  |

|                                                                                                                                                           |  |  |

| state)                                                                                                                                                    |  |  |

| <u>siaic</u>                                                                                                                                              |  |  |

|                                                                                                                                                           |  |  |

|                                                                                                                                                           |  |  |

|                                                                                                                                                           |  |  |

|                                                                                                                                                           |  |  |

|                                                                                                                                                           |  |  |

|                                                                                                                                                           |  |  |

|                                                                                                                                                           |  |  |

| 17.5mW (at 4MHz) 5V -5 to 10mA (P0, P1, P2 and P4: CMOS 3-state) -20 to 85°C CMOS silicon gate 42-pin shrink plastic molded DIP 56-pin plastic molded QFP |  |  |

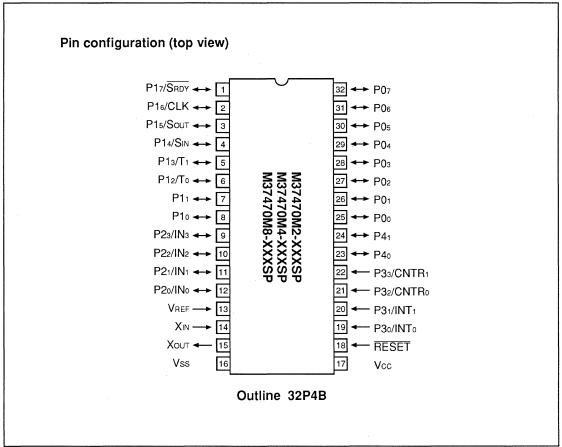

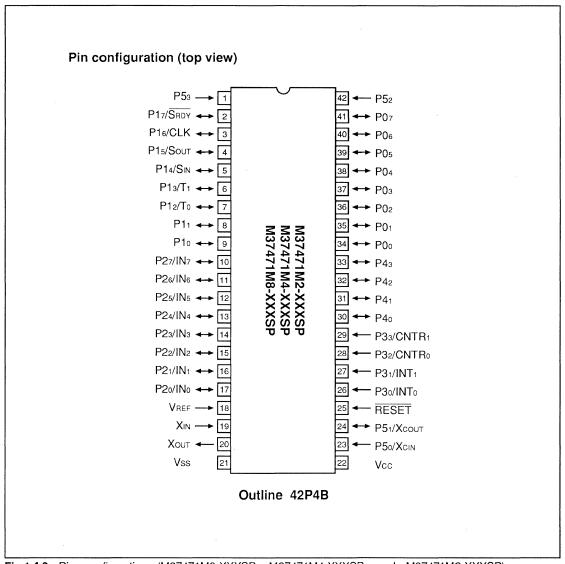

#### 1.4 Pin configuration

Figure 1.4.1 shows the pin configuration of M37470M2-XXXSP, M37470M4-XXXSP, and M37470M8-XXXSP. And the pin configuration of M37471M2-XXXSP, M37471M4-XXXSP, and M37471M8-XXXSP are shown in Figure 1.4.2, and the pin configuration of M37471M2-XXXFP, M37471M4-XXXFP, and M37471M8-XXXFP are shown in Figure 1.4.3.

Fig.1.4.1 Pin configuration (M37470M2-XXXSP, M37470M4-XXXSP, and M37470M8-XXXSP)

Fig.1.4.2 Pin configuration (M37471M2-XXXSP, M37471M4-XXXSP, and M37471M8-XXXSP)

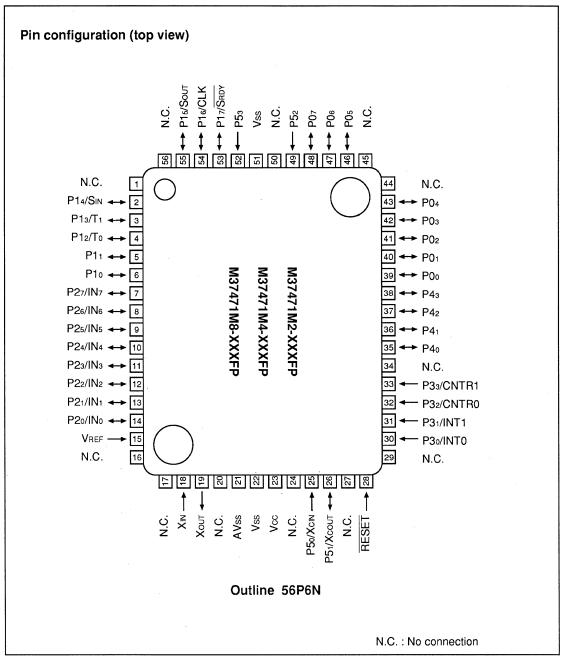

Fig.1.4.3 Pin configuration (M37471M2-XXXFP, M37471M4-XXXFP, and M37471M8-XXXFP)

#### 1.5 Pin description

Pin description is shown in Table 1.5.1

Table 1.5.1 Pin description

| Pin      | Name           | Input/<br>Output | Function                                                                        |

|----------|----------------|------------------|---------------------------------------------------------------------------------|

| Vcc, Vss | Supply voltage |                  | Supply 2.7 to 5.5V to Vcc, and 0V to Vss.                                       |

| AVss     | Analog         |                  | Acts as ground level input pin for A-D converter.                               |

|          | power supply   |                  | Same voltage as Vss is applied. (Note 1)                                        |

| VREF     | Reference      | Input            | Acts as reference voltage input pin for the A-D converter.                      |

|          | voltage input  |                  |                                                                                 |

| RESET    | Reset input    | Input            | Specifies reset when held at "L" for at least 2µs.                              |

| XIN      | Clock input    | Input            | Acts as input and output pins interfacing with the internal clock generating    |

|          |                |                  | circuit. Connect a ceramic resonator or crystal oscillator between the XIN      |

| Xout     | Clock output   | Output           | and XOUT pins to set the oscillator frequency. An internal feedback resistor    |

|          |                |                  | is connected between the XIN and XOUT pins.                                     |

|          |                |                  | If an external clock is used, connect the clock source to the XIN pin and leave |

|          |                |                  | the Xout pin open.                                                              |

| P00-P07  | I/O port P0    | 1/0              | Acts as 8-bit I/O port with CMOS output format. When input port is selected,    |

|          |                |                  | these pins can be connected individually to pull-up transistors. A key on       |

|          |                |                  | wake up function is also provided.                                              |

| P10-P17  | I/O port P1    | 1/0              | Acts as 8-bit I/O port with CMOS output format. When input port is selected,    |

|          |                |                  | these pins can be connected in groups of four to pull-up transistors. P12 and   |

|          |                |                  | P13 can also be used as timer outputs To and T1, and P14, P15, P16, and         |

|          |                |                  | P17 can also be used as SIN, SOUT, CLK, and SRDY of the serial I/O function.    |

|          |                |                  | SOUT and SRDY outputs can be set to N-channel open drain output.                |

| P20-P27  | I/O port P2    | 1/0              | Acts as 8-bit I/O port with CMOS output format. When input port is selected,    |

| (Note 2) |                |                  | these pins can be connected in groups of four to pull-up transistors. These     |

|          |                |                  | pins can also be used as analog inputs INo to IN7.                              |

| P30-P33  | Input port P3  | Input            | Acts as 4-bit input port. P3o and P31 can also be used as external interrupt    |

|          |                |                  | input pins INTo and INT1, and P32 and P33 can also be used as timer input       |

|          |                |                  | pins CNTRo and CNTR1.                                                           |

| P40-P43  | I/O port P4    | 1/0              | Acts as 4-bit I/O port with CMOS output format. When input port is selected,    |

| (Note 3) |                |                  | these pins can be connected in groups of four to pull-up transistors.           |

| P50-P53  | Input port P5  | Input            | Acts as 4-bit input port that can be connected as a group of four pins to pull- |

| (Note 4) |                |                  | up transistors. P50 and P51 can also be used as the XCIN and XCOUT pins         |

| •        |                |                  | for the clock-function clock generating circuit. When using these pins as       |

|          |                |                  | XCIN and XCOUT pins, an internal feedback resistor is connected between         |

|          |                |                  | them. To enable external clock input, connect the clock source to the XCIN      |

|          |                |                  | pin and leave the XCOUT pin open.                                               |

Note 1: For 56-pin QFP type only.

<sup>2:</sup> Only P20-P23 (IN0-IN3) 4-bit for M37470M2, M37470M4, and M37470M8. 3: Only P40 and P41 2-bit for M37470M2, M37470M4, and M37470M8.

<sup>4:</sup> This port is not included in M37470M2, M37470M4, and M37470M8.

# 1.6 Block diagram

Figure 1. And the Figure shown 1.6.2, 1.6.1 shows the block diagram and the Figure 1.6.3. block block diagram of M37470M2-XXXSP, M37470M4-XXXSP, and M37470M8-XXXSP of M37471M2-XXXSP, M37471M4-XXXSP, and M37471M8-XXXSP are shown in block diagram of M37471M2-XXXFP, M37471M4-XXXFP, and M37471M8-XXXFP

## OBARANDRA 2

### FUNCTIONAL DESCRIPTION

#### 2.1 Central processing unit (CPU)

The central processing unit (CPU) of the M37470 has six internal registers. Five of these registers (the accumulator (A), index register X (X), index register Y (Y), stack pointer (S), and processor status register (PS)) have an 8-bit configuration, but the program counter (PC) has a 16-bit configuration consisting of two 8-bit registers (PCH and PCL).

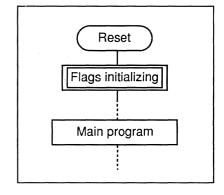

After a reset, the I flag of the processor status register is set to "1", the contents of address FFFF16 are placed in the high-order 8 bits of the program counter, and the contents of address FFFE16 are placed in the low-order 8 bits of the program counter. The contents of the rest of the PS and the other registers are undefined, so initialization may be necessary for some programs.

The register structure of the M37470 is shown in Figure 2.1.1.

Fig.2.1.1 Register structure

#### **FUNCTIONAL DESCRIPTION**

#### 2.1 Central processing unit (CPU)

#### 2.1.1 Accumulator (A)

The accumulator is the central register of the microcomputer, and it has an 8-bit configuration. This is the most frequently used general-purpose register—it is used for arithmetic operations, data transfer, temporary storage, and condition judgements.

#### 2.1.2 Index register X (X), index register Y (Y)

Both index register X and index register Y have 8-bit configurations. In addressing modes that use these index registers, the contents of these registers are added to the contents of the specified address to give the actual address to be used. These addressing modes are useful for referencing subroutine tables and memory tables.

These index registers also have increment, decrement, comparison, and data transfer functions, so they can be used as accumulators.

When the T flag of the processor status register (described below) is "1", the contents of index register X are used as they are as an operand address.

#### 2.1.3 Stack pointer (S)

The stack pointer is an 8-bit register used during subroutine calls and interrupts.

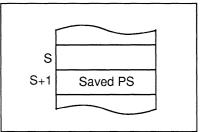

When processing branches from the currently executing routine to a subroutine or interrupt processing routine, the return address must be saved. This return address is usually stored in the internal RAM, in an area called the stack area. The contents of the stack pointer indicate the storage location of stack data in the stack area. The operations of pushing register contents onto the stack and popping them from the stack are shown in Figure 2.1.2. These operations are performed automatically when an interrupt is received or a subroutine is called.

The contents of registers other than the program counter and processor status register are not automatically pushed onto the stack, and at subroutine call only the contents of the program counter are pushed. If pushing is necessary, specify it in the program: use the PHA and PLA instructions to push and pop the contents of the accumulator, and the PHP and PLP instructions to push and pop the contents of the processor status register.

RAM in the zero page is usually used as the stack area for this storage, but 1 page (addresses 010016 to 01FF16) can also be used as a stack area by setting bit 2 of the CPU mode register (address 00FB16) to "1" (M37470M8 and M37471M8 only). The M37470M2, M37470M4, M37471M2, and M37471M4 do not have 1 page in RAM, so always set this bit to "0" in these microcomputers.

Fig.2.1.2 Stack store and restore sequence when executing interrupt or subroutine calls

#### 2.1.4 Program counter (PC)

The program counter is a 16-bit counter consisting of two 8-bit registers: PCH and PCL. It contains the address of the next instruction to be executed.

#### 2.1.5 Processor status register (PS)

The processor status register is an 8-bit register consisting of various flags such as those holding the status after an arithmetic operation.

After reset, the I flag is set to "1", but all other flags are undefined. Since the T and D flags directly affect arithmetic operations, always initialize them before such an operation.

The bits of the processor status register are described below.

#### **FUNCTIONAL DESCRIPTION**

#### 2.1 Central processing unit (CPU)

#### (1) Carry flag (C)

The C flag stores a carry or borrow sent from the arithmetic and logic unit after an arithmetic operation. It is also changed by a shift or rotate instruction.

The C flag can be set by the SEC instruction and cleared by the CLC instruction.

#### (2) Zero flag (Z)

The Z flag is set if the result of an arithmetic operation or a data transfer is "0", or cleared if the result is anything other than "0".

The Z flag is not valid in decimal mode.

#### (3) Interrupt disable flag (I)

The I flag disables all interrupts except for the interrupt generated by the BRK instruction. Interrupts are disabled when the I flag is "1". It is automatically set to "1" when an interrupt is received, preventing multiple interrupts.

The I flag can be set by the SEI instruction and cleared by the CLI instruction.

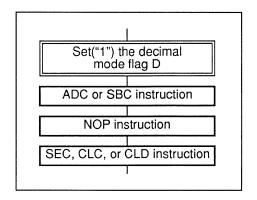

#### (4) Decimal mode flag (D)

The D flag determines whether additions and subtractions are performed in binary or decimal notation. Ordinary binary arithmetic is performed when the D flag is "0"; decimal arithmetic with two digits per word is performed when it is "1". Decimal correction is automatic in decimal mode, but only the ADC and SBC instructions can be used for decimal arithmetic.

The D flag can be set by the SED instruction and cleared by the CLD instruction. Once the D flag has been set, it is valid until it is cleared by the CLD instruction or other cause. Since the D flag directly affects calculations, always initialize it after a reset.

#### (5) Break flag (B)

The BRK instruction can be used during program debugging to give the same effect as an interrupt. The B flag determines whether an interrupt was generated by executing the BRK instruction. It is set to "1" if an interrupt was generated by the BRK instruction; or cleared to "0" and pushed onto the stack if any other interrupt was generated.

#### (6) Index X mode flag (T)

When the T flag is "0", arithmetic operations are performed between accumulator and memory; when it is "1", direct arithmetic operations and direct data transfers are enabled between memory and memory, memory and I/O, and I/O, and I/O, without using the accumulator. In this case, the result of an arithmetic operation performed on data in memory location 1 and memory location 2 is stored in memory location 1. The address of memory location 1 is specified by the index register X, and that of memory location 2 is specified by the normal addressing mode.

The T flag can be set by the SET instruction and cleared by the CLT instruction.

Since the T flag directly affects calculations, always initialize it after a reset.

#### (7) Overflow flag (V)

The V flag is valid during the addition or subtraction of binary, one-word signed data. It is set if the result is outside the range of +127 to -128. It is also used after the BIT instruction is executed, to contain the value in bit 6 of the memory location operated on by the BIT instruction.

The V flag can be cleared by the CLV instruction, but it cannot be set by an instruction.

The V flag is not valid in decimal mode.

#### (8) Negative flag (N)

The N flag is set if the result of an arithmetic operation or data transfer is negative (bit 7 is "1"). It is also used after the BIT instruction is executed, to contain the value in bit 7 of the memory location operated on by the BIT instruction.

The N flag cannot be set or cleared directly by any instruction.

The N flag is not valid in decimal mode.

#### 2.2 Access area

In the M37470, all the ROM, RAM, I/O functions, and control registers are located in the same memory area. This means that there is no need for programs to distinguish between memory and I/O operations—the same instructions can both transfer data and operate on data.

The program counter of the M37470 has a 16-bit configuration, and 64K bytes of memory area (from addresses 000016 to FFFF16) can be accessed. Of this 64K-byte memory area, the first 256 bytes are called the zero page area which holds frequently used memory functions such as internal RAM, I/O ports, and timers. The last 256 bytes of the 64K-byte memory area are called the special page area. The zero page and special page areas can be accessed in 2-byte units by using special addressing modes.

Fig.2.2.1 Access area (M37470M2-XXXSP)

#### **2.2.1 Zero page** (addresses 000016 to 00FF16)

The 256 bytes from address 000016 to address 00FF16 are called the zero page area. RAM, access flags, and the special function register (SFR) are allocated to this area. Use the zero page addressing mode shown in Figure 2.2.2 to specify memory and registers in the zero page area. This dedicated zero page addressing mode is particularly useful because it enables access to this area with even shorter instruction cycles.

#### 2.2.2 Special page (addresses FF0016 to FFFF16)

The 256 bytes from address FF0016 to address FFFF16 are called the special page area. Use the special page addressing mode shown in Figure 2.2.2 to specify memory in the special page area. This dedicated special page addressing mode is particularly useful because it enables access to this area with even shorter instruction cycles.

Frequently used subroutines are normally stored in this area.

Fig.2.2.2 Zero page and special page addressing mode

#### 2.3 Memory map

The memory map of the 7470 series is shown in Figures 2.3.1 to 2.3.3. Memory, I/O, and other functions allocated to the address spaces are described below.

●RAM

000016 to 007F16: M37470M2, and M37471M2

000016 to 00BF16: M37470M4, and M37471M4

000016 to 00BF16

and

010016 to 01BF16: M37470M8, and M37471M8

In the M37470M2, and M37471M2, static RAM with a capacity of  $128 \times 8$  bits is allocated to addresses 000016 to 007F16.

In the M37470M4, and M37471M4, static RAM with a capacity of  $192 \times 8$  bits is allocated to addresses 000016 to 00BF16.

In the M37470M8, and M37471M8, static RAM with a capacity of  $384 \times 8$  bits is allocated to addresses 000016 to 00BF16 and 010016 to 01BF16.

Internal RAM is used for data storage as well as a stack area for subroutine call and interrupt generation. Therefore, when using RAM as a stack area, be careful that subroutine nesting and interrupt levels do not become too complex, to ensure that data stored in that RAM area is not destroyed.

#### **OSFR**

The area from address 00C016 to address 00FF16 is allocated to the special function register (SFR), with the memory map shown in Figure 2.3.4. The SFR contains registers relating to functions such as I/O ports, timers, serial I/O, A-D converter, and interrupts.

●ROM

F00016 to FFFF16: M37470M2, and M37471M2 E00016 to FFFF16: M37470M4, and M37471M4 C00016 to FFFF16: M37470M8, and M37471M8

In the M37470M2, and M37471M2, mask ROM with a capacity of  $4K \times 8$  bits is allocated to addresses F00016 to FFFF16.

In the M37470M4, and M37471M4, mask ROM with a capacity of 8K  $\times$  8 bits is allocated to addresses E00016 to FFFF16.

In the M37470M8, and M37471M8, mask ROM with a capacity of  $16K \times 8$  bits is allocated to addresses C00016 to FFFF16.

Addresses FFEA16 to FFFF16 in internal ROM are allocated as a vector area for storing jump destination addresses used at reset or when an interrupt is generated. A memory map of this vector area is shown in Figure 2.3.5.

Fig.2.3.1 Memory map for M37470M2, and M37471M2

Fig.2.3.2 Memory map for M37470M4, and M37471M4

Fig.2.3.3 Memory map for M37470M8, and M37471M8

| 00C016         | Port P0                                 | 00 <b>E</b> 016             |                              |

|----------------|-----------------------------------------|-----------------------------|------------------------------|

| 00C116         | Port P0 direction register              | 00 <b>E</b> 1 <sub>16</sub> |                              |

| 00C216         | Port P1                                 | 00E216                      |                              |

| 0C316          | Port P1 direction register              | 00E316                      |                              |

| 0C416          | Port P2                                 | 00 <b>E4</b> 16             |                              |

| 0C516          | Port P2 direction register              | 00 <b>E</b> 516             |                              |

| 0C616          | Port P3                                 | 00 <b>E</b> 616             |                              |

| 0C716          |                                         | 00E716                      |                              |

| 0C816          | Port P4                                 | 00E816                      |                              |

| 0C916          | Port P4 direction register              | 00 <b>E</b> 916             |                              |

| 0CA16          | Port P5 (Note 1)                        | 00 <b>EA</b> 16             |                              |

| 0CB16          |                                         | 00EB16                      |                              |

| 0CC16          |                                         | 00EC16                      |                              |

| 0CD16          |                                         | 00ED16                      |                              |

| 0CE16          |                                         | 00EE16                      |                              |

| 0CF16          |                                         | 00EF16                      |                              |

| 0D016          | Port P0 pull-up control register        | 00F016                      | Timer 1                      |

| 0D116          | Ports P1 to P5 pull-up control register | 00F116                      | Timer 2                      |

| 0D216          |                                         | 00F216                      | Timer 3                      |

| 0D316          |                                         | 00F316                      | Timer 4                      |

| 0D416          | Edge polarity selection register        | 00F416                      |                              |

| 0D516          |                                         | 00F516                      |                              |

| 0D616          | Input latch register                    | 00F616                      |                              |

| 0D716          |                                         | 00F716                      | Timer FF register            |

| 0D816          |                                         | 00F816                      | Timer 12 mode register       |

| 0D916          | A-D control register                    | 00F916                      | Timer 34 mode register       |

| 0 <b>DA</b> 16 | A-D conversion register                 | 00FA16                      | Timer mode register 2        |

| 0DB16          |                                         | 00FB <sub>16</sub>          | CPU mode register            |

| 0DC16          | Serial I/O mode register                | 00FC <sub>16</sub>          | Interrupt request register 1 |

| 0DD16          | Serial I/O register                     | 00FD16                      | Interrupt request register 2 |

| 0DE16          | Serial I/O counter Byte counter         | 00FE <sub>16</sub>          | Interrupt control register 1 |

| 0DF16          |                                         | 00FF16                      | Interrupt control register 2 |

Fig.2.3.4 SFR memory map

Fig.2.3.5 Interrupt vector area memory map

#### 2.4 Input/Output ports

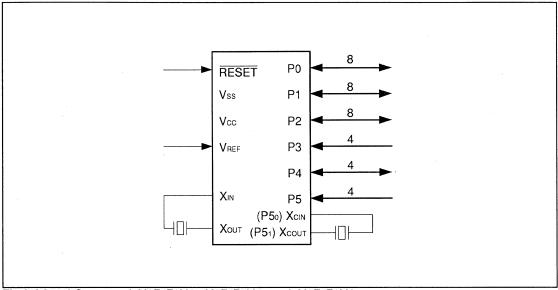

Figure 2.4.1 shows I/O ports of M37470M2-XXXSP, M37470M4-XXXSP, and M37470M8-XXXSP. And I/O ports of M37471M2-XXXSP/FP, M37471M4-XXXSP/FP, and M37471M8-XXXSP/FP are shown in Figure 2.4.2.

Fig.2.4.1 I/O ports of M37470M2, M37470M4, and M37470M8

Fig.2.4.2 I/O ports of M37471M2, M37471M4, and M37471M8

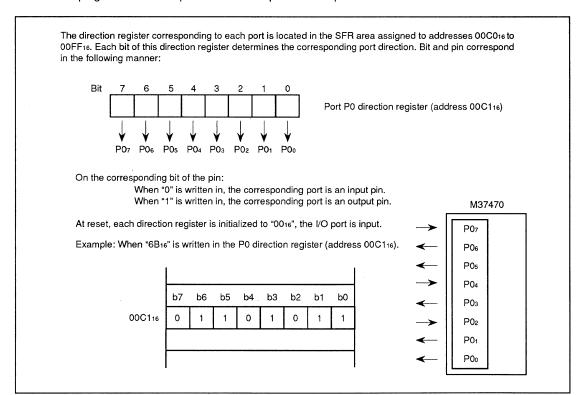

#### 2.4.1 Input/Output port

#### (1) Port P0

Port P0 is an 8-bit input/output port. Output is in CMOS output format. Port P0 is handled as memory at address 00C016 in the zero page. It has a direction registers (address 00C116) whose bits can be individually programmed to set each of the pins of port P0 to either input or output. If a bit of direction register is set by program to "1", the corresponding pin is set to be an output pin; if the bit of direction register is set to "0"; the pin is set to be an input pin. Data written to a pin that has been programmed as an output pin is written to a port latch, then it is output without change to the output pin. When data is read from a pin that has been programmed as an output pin, the contents of the output pin itself are not read; the contents of the port latch are read instead. This ensures that the previously output value is read correctly, even if some cause such as an external load has driven an output "H" voltage down or a "L" voltage up. A pin programmed to be an input pin is floating, and its status can always be read. When data is written to such a pin, it is written only to the port latch, so the pin itself stays floating.

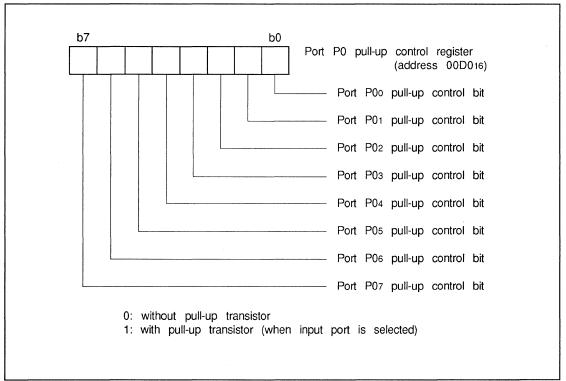

At reset, all the pins of port P0 are set to input. When the port is set to input, individual pins can be connected to pull-up transistors (see Figure 2.4.3).

If a key matrix is created for input to port P0, the M37470 can be returned from wait or stop mode to normal operating mode by simply pressing a key. This generates an interrupt by applying an "L" level voltage to port P0.

Fig.2.4.3 Structure of port P0 pull-up control register

- (2) Port P1

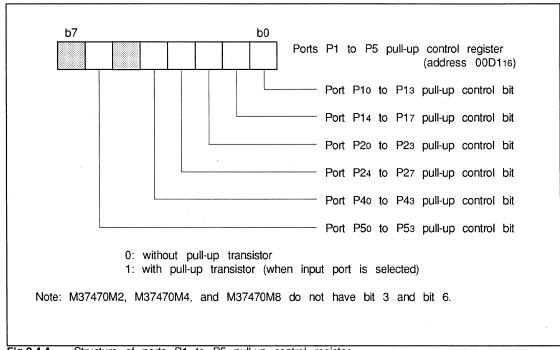

- Port P1 has the same functions as port P0. Pins P12 to P17 have double functions—their functions can be selected by program. When port P1 is selected to be an input port, its pins can be connected in groups of four to pull-up transistors (see Figure 2.4.4).

- (3) Port P2

Port P2 is an 8-bit I/O port with the same functions as port P0. In the M37470M2, M37470M4, and M37470M8, this port is P20 to P23, a 4-bit I/O port. This port can also be used as an analog voltage input pin. When port P2 is selected to be an input port, its pins can be connected in groups of four to pull-up transistors (see Figure 2.4.4).

(4) Port P3

Port P3 is a 4-bit input port. Its pins can also be used as external interrupt input pins and timer input pins.

(5) Port P4

Port P4 is an 4-bit I/O port with the same functions as port P0. In the M37470M2, M37470M4, and M37470M8, this port is P40 and P41, a 2-bit I/O port. When port P4 is selected to be an input port, its pins can be connected in groups of four to pull-up transistors (see Figure 2.4.4).

(6) Port P5

Port P5 is a 4-bit input port that can be connected as a group of four pins to a pull-up transistor (see Figure 2.4.4). Pins P50 and P51 can also be used as I/O pins for the clock-function clock generating circuit. Note that the M37470M2, M37470M4, and M37470M8 do not have this port.

Fig.2.4.4 Structure of ports P1 to P5 pull-up control register

Switch the programmable I/O ports between input and output as shown below.

### 2.4.2 Pin description

The functions of the other I/O pins of the M37470 are described below.

### (1) XIN and XOUT pins

The XIN and XOUT pins are clock I/O pins. The M37470 has a built-in clock generating circuit whose oscillation frequency can be set by a ceramic resonator or a crystal oscillator. A feedback resistor is built in between the XIN and XOUT pins.

When using an external clock, connect the clock oscillation source to the XIN pin, and leave the XOUT pin open.

### (2) RESET pin

The system is reset when the RESET pin is held at "L" for at least 2 µs.

### (3) Vss and Vcc pins

The Vss and Vcc pins supply power to the chip.

### (4) INTo pin (P3o/INTo)

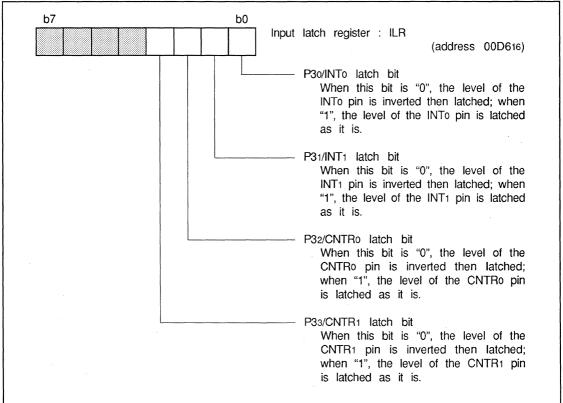

The interrupt input pin INTo can also be used as port P3o. When either a rising edge or a falling edge is input to this pin, the INTo interrupt request bit (bit 0 of address 00FD16) is set to "1".

### (5) INT1 pin (P31/INT1)

The interrupt input pin INT1 can also be used as port P31. When either a rising edge or a falling edge is input to this pin, the INT1 interrupt request bit (bit 1 of address 00FD16) is set to "1".

### (6) CNTRo pin (P32/CNTRo)

The timer input pin CNTRo can also be used as port P32.

#### (7) CNTR1 pin (P33/CNTR1)

The timer input pin CNTR1 can also be used as port P33.

### (8) To pin (P12/To)

The timer output pin To can also be used as port P12.

### (9) T1 pin (P13/T1)

The timer output pin T1 can also be used as port P13.

### (10) INo to IN7 pins (P20/IN0 to P27/IN7)

The analog input pins INo to IN7 can also be used as port P20 to P27. M37470M2, M37470M2A, M37470M4, and M37470M8 do not have IN4-IN7 pins.

#### (11) VREF pin

The VREF pin is a reference voltage input pin for the A-D converter.

### (12) XCIN and XCOUT pins (P50/XCIN and P51/XCOUT)

The XCIN and XCOUT pins are clock I/O pins for the clock function, but they can also be used as ports P50 and P51. A feedback resistor is built in between the XCIN and XCOUT pins, but it is disconnected when these pins are used as ordinary ports. The M37470M2, M37470M4, and M37470M8 do not have these pins.

## (13) AVss pin

The AVss pin is a ground level input pin for A-D converter. Same voltage as Vss is applied. This pin is for 56-pin QFP type only.

Fig.2.4.5 Port P0, P10-P13 block diagram

Fig.2.4.6 Port P14-P17 block diagram

Fig.2.4.7 Port P2-P4 block diagram

Fig.2.4.8 Port P5 block diagram

# 2.5 Interrupts

Interrupts are used in the following cases:

•When processing that is more important that the currently executing processing routine is requested. •When processing must be executed at a specific timing.

The M37470 can be interrupted by 12 causes. These interrupts are vector interrupts with a fixed priority sequence. Interrupt causes, jump destination addresses, and interrupt priorities are listed in Table 2.5.1.

Table 2.5.1 Interrupt vector addresses and priority

| Priority | Interrupt cases               | Jump destination addresses |        | Remarks                         |  |  |

|----------|-------------------------------|----------------------------|--------|---------------------------------|--|--|

| FHORITY  | interrupt cases               | Higher                     | Lower  |                                 |  |  |

| 1        | Reset (note)                  | FFFF16                     | FFFE16 | Non-maskable                    |  |  |

| 2        | INTo interrupt                | FFFD16                     | FFFC16 | Polarity programmable           |  |  |

| 3        | INT1/Key on wake up interrupt | FFFB16                     | FFFA16 | Polarity programmable (INT1)    |  |  |

| 4        | CNTRo/CNTR1 interrupt         | FFF916                     | FFF816 | Polarity programmable           |  |  |

| 5        | Timer 1 interrupt             | FFF716                     | FFF616 |                                 |  |  |

| 6        | Timer 2 interrupt             | FFF516                     | FFF416 |                                 |  |  |

| 7        | Timer 3 interrupt             | FFF316                     | FFF216 |                                 |  |  |

| 8        | Timer 4 interrupt             | FFF116                     | FFF016 |                                 |  |  |

| 9        | Serial I/O interrupt          | FFEF16                     | FFEE16 |                                 |  |  |

| 10       | A-D conversion interrupt      | FFED16                     | FFEC16 |                                 |  |  |

| 11       | BRK instruction interrupt     | FFEB16                     | FFEA16 | Non-maskable software interrupt |  |  |

Note: Reset is included in this table because it operates in the same way as an interrupt.

These 12 interrupts have the priorities listed in Table 2.5.1 (but note that a reset input has a higher priority than all these interrupts). If two or more interrupts are requested in the same sampling period, the interrupt with the highest priority is the only one that is accepted. The priority sequence is determined by the hardware, but a variety of interrupt processing options can also be set by software, using the interrupt control flags (the interrupt enable bits and the interrupt disable flag).

### 2.5.1 Interrupt causes

The various interrupt causes are described below.

### (1) INTo, INT1 and key on wake up interrupts

An interrupt request is generated when either a rising edge or a falling edge is detected in the level of the INTo pin or the INTo pin. The active edge that is detected in this way can be selected by setting bit 0 or bit 1 of the active edge selection register (address 00D416).

The INTo and INT1 pins can also be used as the P30 and P31 pins; the levels at ports P30 and P31 are always detected.

The active edge selection register is cleared to "0016" by a reset, so requests for INTo and INT1 interrupts are generated when falling edges are subsequently detected at those pins.

After a low power consumption mode has been set by the STP instruction or the WIT instruction, interrupts are key on wake up interrupts if bit 5 of the active edge selection register is "1", or INT1 interrupts if it is "0". If key on wake up interrupts are validated, an interrupt request is generated whenever an "L" level voltage is applied to any of the pins of port P0 that have been set to input mode.

When a non low power consumption mode is set, both key on wake up and INT1 interrupts are invalid if bit 5 of the active edge selection register is set to "1".

### (2) CNTRo and CNTR1 interrupts

An interrupt request is generated when either a rising edge or a falling edge is detected in the level of the CNTRo pin or the CNTR1 pin. Use bit 4 of the active edge selection register to determine whether the CNTRo pin or the CNTR1 pin is the interrupt input pin. The active edge can be selected for each pin by setting bits 2 and 3 of the active edge selection register.

- (3) Timer 1, timer 2, timer 3, and timer 4 interrupts An interrupt request is generated when the timer overflows.

- (4) Serial I/O interrupt An interrupt request is generated when serial I/O transmit or receive is completed.

- (5) A-D conversion interrupt An interrupt request is generated when A-D conversion is completed.

#### (6) BRK instruction interrupt

The BRK instruction interrupt has the lowest priority of software interrupts; it does not have a corresponding interrupt enable bit and the interrupt disable flag has no effect on it (it is non-maskable).

Fig.2.5.1 Structure of interrupt related registers (1)

Fig.2.5.2 Structure of interrupt related registers (2)

Fig.2.5.3 Structure of interrupt related registers (3)

For further details of the various interrupts, see the sections on the corresponding functions. **2.5.2 Interrupt control**

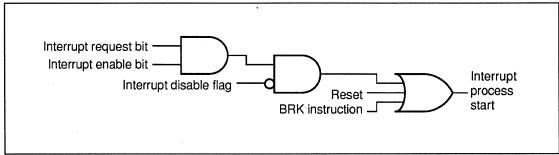

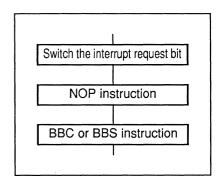

Each of the M37470's interrupts is controlled by two bits and one flag: its interrupt request bit, its interrupt enable bit, and the interrupt disable flag, as shown in Figure 2.5.4, except for the software interrupt set by the BRK instruction. These control bits and control flag are described below.

- (1) Interrupt request bits

- When an interrupt request is generated, the corresponding request bit is set to "1". The interrupt request bit remains set until the interrupt is accepted; it is cleared at the same time that the interrupt is accepted. These bits can be cleared by a program, but they cannot be set.

- (2) Interrupt enable bits

The interrupt enable bits control the acceptance of interrupts. When the bit corresponding to an interrupt is "0", the acceptance of that interrupt is disabled; when the bit is "1", the corresponding interrupt is enabled.

- (3) Interrupt disable flag (I)

- The I flag is allocated to bit 2 of the processor status register. This flag disables all interrupts except the BRK instruction interrupt. When the interrupt disable flag is set to "1", interrupts are disabled; when it is cleared to "0", interrupts are enabled. Use the SEI instruction to set the interrupt disable flag, and the CLI instruction to clear it.

- Once an interrupt service routine has started, the I flag is automatically set to disable multiple interrupts. To enable multiple interrupts, specify the CLI instruction within the interrupt service routine to clear the I flag.

The above control bits and control flag are independent; they do not have any effect on each other. An interrupt is generated when the corresponding interrupt request and enable bits are "1" and the

interrupt disable flag is "0".

### 2.5.3 Processing at interrupt acceptance

When an interrupt is accepted, the currently executing processing is temporarily halted and the appropriate interrupt service routine is executed. After the interrupt service routine ends, the program flow must be such that the previous processing continues.

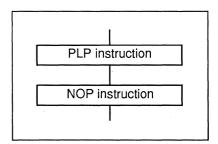

When the M37470 accepts an interrupt, it automatically pushes the contents of the program counter and the processor status register onto the stack. At the same time, it takes the contents of the vector corresponding to the accepted interrupt (the start address of the interrupt service routine) from the interrupt vector table and puts them into the program counter, then it executes the interrupt service routine.

When the interrupt service routine starts, the request bit corresponding to that interrupt is cleared to "0", and the interrupt disable flag becomes "1" to disable multiple interrupts. (To enable multiple interrupts, specify the CLI instruction within the interrupt service routine to clear the I flag.)

Before an interrupt service routine can be executed, a jump destination address must be set in the vector table to correspond to each interrupt. The jump destination addresses of all the interrupts are listed in Table 2.5.1.

Changes in the stack pointer and program counter when an interrupt is accepted are shown in Figure 2.5.5.

Fig.2.5.5 Change of stack pointer and program counter at interrupt receive

### 2.5.4 Timing after interrupt

Figure 2.5.6 shows the timing chart of stack save and interrupt routine start at the interrupt occurrence. Figure 2.5.7 shows the operation time before interrupt routine execution.

Fig.2.5.6 Timing chart after interrupt

The interrupt service routine will start after the completion of the instruction being executed when the request occurs. The two conditions that allow for the interrupt to be accepted is the interrupt disable flag must be "0" and the interrupt enable bit must be "1" (with the exception of the BRK instruction interrupt).

Fig.2.5.7 Operation time before the interrupt routine execution

### 2.6 Timers

The M37470 has four 8-bit built-in timers, each with an 8-bit timer latch: timer 1, timer 2, timer 3, and timer 4. The timers are all of the count-down type—when the counter of a timer reaches "FF16", the contents of the timer latch decremented by 1 at the next count pulse, is reloaded into the timer, and an interrupt request is generated. The divide ratio of a timer is given by 1/(n + 1), where n is the contents of the latch (n = 0 to 255).

Timers can be set by software, and they can be selected in the following modes:

- Timer mode

- Event count mode

- Pulse output mode

- Pulse width measuring mode

- PWM mode

A block diagram of the timers is shown in Figure 2.6.1.

Timer block diagram Fig.2.6.1

### 2.6.1 Timer 1, timer 2, timer 3 and timer 4

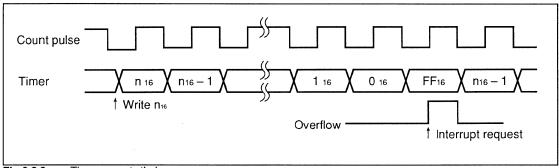

Each of timer 1, timer 2, timer 3, and timer 4 is an 8-bit timer with an 8-bit timer latch. If a timer is specified for a write, the corresponding timer latch is also specified at the same time. Therefore, if the value set in the timer is assumed to be n16, the value of the timer latch is also n16. When the timer starts to count, the timer's value decrements at the fall of each count pulse, in the sequence: n16  $\rightarrow$  (n16-1)  $\rightarrow$  (n16-2) $\rightarrow$  .....116  $\rightarrow$  016  $\rightarrow$  FF16. At the fall of the next count pulse after the timer reaches "FF16", the value (n16-1) obtained by subtracting one from the reload latch value is set (reloaded) into the timer, and the count resumes. At the rise of the next count pulse after the timer reaches "FF16", an overflow occurs, and an interrupt request is generated. Timer count timing is shown in Figure 2.6.2.

Fig.2.6.2 Timer count timing

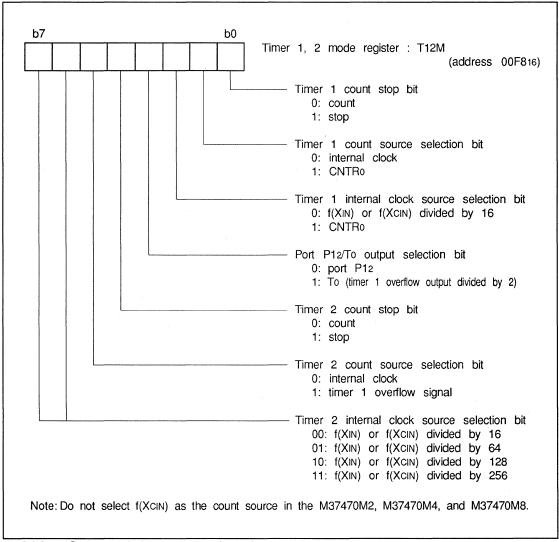

#### (1) Timer 1

Timer 1 can be used in three modes: timer mode, event count mode, and pulse output mode. Start the count of timer 1 by setting bit 0 of the timer 1, 2 mode register (address 00F816) to "0". In timer mode, an interrupt is generated at constant time intervals. The count source can be selected by setting bits 1 and 2 of the timer 1, 2 mode register to specify any one of: the clock oscillation frequency f(XIN) or the clock-function clock oscillation frequency f(XCIN) divided by 16, the clock-function clock oscillation frequency f(XCIN), or an external clock input through the CNTRo pin. Use bit 7 of the CPU mode register to select f(XIN) or f(XCIN). Do not select f(XCIN) as the count source in the M37470M2, M37470M4, and M37470M8.

In event count mode, the operation is the same as in timer mode, except that count source is an external clock input through the CNTRo pin. The active edge of input pulses can be selected by changing bit 2 of the active edge selection register (address 00D416). When this bit is "0", pulses input through the CNTRo pin are inverted to become count pulses; when this bit is "1", pulses input through the CNTRo pin are used unchanged as count pulses.

In pulse output mode, if bit 3 of the timer 1, 2 mode register (address 00F816) is set to "1", port P12 becomes the timer output To, and a signal that is the timer 1 overflow signal divided by two is output. To activate pulse output mode, set the P12 direction register to output mode. In this case, the initial output value can be set by writing to bit 0 of the timer FF register (address 00F716) while bit 0 of the timer mode register 2 (address 00FA16) is "1" (setting enabled).

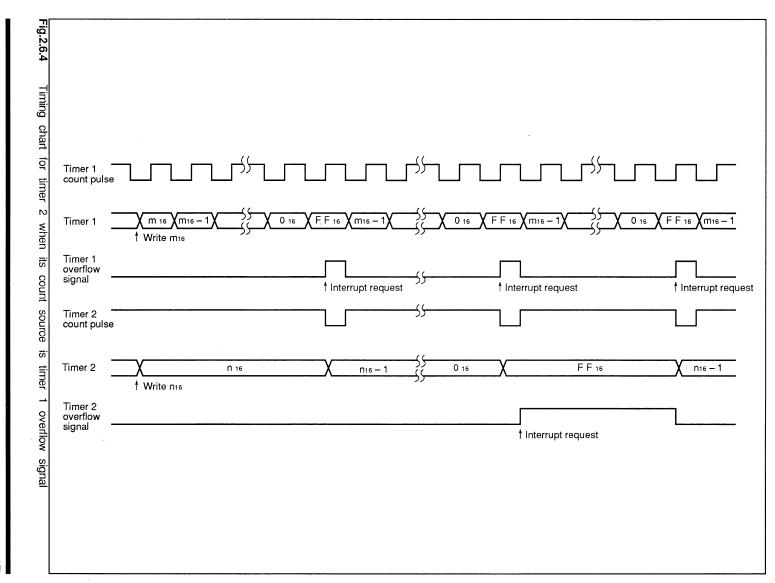

### (2) Timer 2

Timer 2 can be used in timer mode. Start the count of timer 2 by setting bit 4 of the timer 1, 2 mode register (address 00F816) to "0". The count source can be selected by setting bits 5, 6, and 7 of the timer 1, 2 mode register to specify any one of: the clock oscillation frequency f(XIN) or the clock-function clock oscillation frequency f(XCIN) divided by 16, 64, 128 or 256; or the timer 1 overflow signal.

Use bit 7 of the CPU mode register to select f(XIN) or f(XCIN). Do not select f(XCIN) as the count source in the M37470M2, M37470M4, and M37470M8.

Fig.2.6.3 Structure of timer 1, 2 mode register

### (3) Timer 3

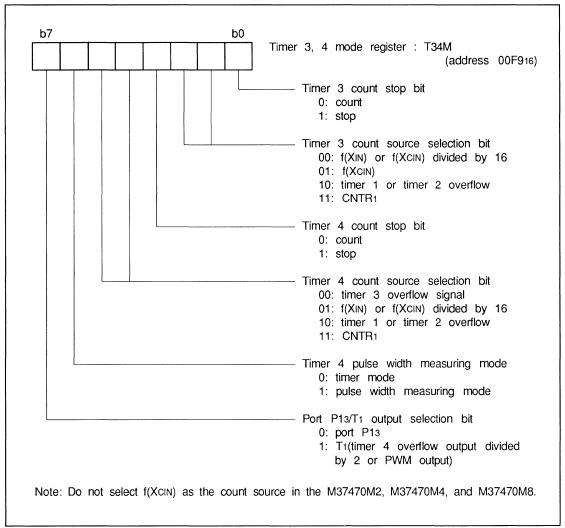

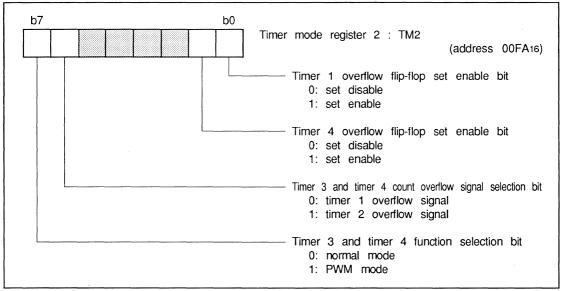

Timer 3 can be used in three modes: timer mode, event count mode, and PWM mode. Start the count of timer 3 by setting bit 0 of the timer 3, 4 mode register (address 00F916) to "0".

In timer mode, an interrupt is generated at constant time intervals. The count source can be selected by setting bits 1 and 2 of the timer 3, 4 mode register and bit 6 of the timer mode register 2 (address 00FA16) to specify any one of: the clock oscillation frequency f(XIN) or the clock-function clock oscillation frequency f(XCIN) divided by 16, the clock-function clock oscillation frequency f(XCIN), the timer 1 overflow signal, the timer 2 overflow signal, or an external clock input through the CNTR1 pin.

Use bit 7 of the CPU mode register to select f(XiN) or f(XciN). Do not select f(XciN) as the count source in the M37470M2, M37470M4, and M37470M8.

Note that, if bits 2 and 1 of the timer 3, 4 mode register are [10] and the timer 1 overflow signal is selected as the count source of timer 2, this timer 1 overflow signal is also the count source of timer 3, regardless of the value of bit 6 of the timer mode register 2.

In event count mode, the operation is the same as in timer mode, except that count source is an external clock input through the CNTR1 pin. The active edge of input pulses can be selected by changing bit 3 of the active edge selection register (address 00D416). When this bit is "0", pulses input through the CNTR1 pin are inverted to become count pulses; when this bit is "1", pulses input through the CNTR1 pin are used unchanged as count pulses.

For details of PWM mode, see "2.6.2 PWM mode".

For details of the operation when control returns from a low power consumption mode, see "2.12 Low power consumption modes".

Fig.2.6.5 Structure of timer 3, 4 mode register

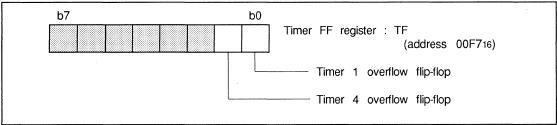

Fig.2.6.6 Structure of timer FF register

### (4) Timer 4

Timer 4 can be used in five modes: timer mode, event count mode, pulse output mode, external pulse width measuring mode, and PWM mode. Start the count of timer 4 by setting bit 3 of the timer 3, 4 mode register (address 00F916) to "0" when bit 6 of the same register is "0". Set bit 6 of the timer 3, 4 mode register to "1" to activate pulse width measurement mode, and set bit 3 to "1" to stop timer 4. Timer 4 also has an input latch function whereby the level of an external input pin can be latched in the input latch register when timer 4 overflows.

In timer mode, an interrupt is generated at constant time intervals. The count source can be selected by setting bits 4 and 5 of the timer 3, 4 mode register and bit 6 of the timer mode register 2 to specify any one of: the timer 3 overflow signal, the clock oscillation frequency f(XIN) or the clock-function clock oscillation frequency f(XCIN) divided by 16, the timer 1 overflow signal, the timer 2 overflow signal, or an external clock input through the CNTR1 pin.

Use bit 7 of the CPU mode register to select f(XIN) or f(XCIN). Do not select f(XCIN) as the count source in the M37470M2, M37470M4, and M37470M8.

Note that, if bits 5 and 4 of the timer 3, 4 mode register are [10] and the timer 1 overflow signal is selected as the count source of timer 2, this timer 1 overflow signal is also the count source of timer 4, regardless of the value of bit 6 of the timer mode register 2.

In event count mode, the operation is the same as in timer mode, except that count source is an external clock input through the CNTR1 pin. The active edge of input pulses can be selected by changing bit 3 of the active edge selection register (address 00D416). When this bit is "0", pulses input through the CNTR1 pin are inverted to become count pulses; when this bit is "1", pulses input through the CNTR1 pin are used unchanged as count pulses.

In pulse output mode, if bit 7 of the timer 3, 4 mode register is set to "1", port P13 becomes the timer output T1, and a signal that is the timer 4 overflow signal divided by two is output. To activate rectangular waveform mode, set the P13 to output mode. In this case, the initial output value can be set by writing to bit 1 of the timer FF register (address 00F716) while bit 1 of the timer mode register 2 (address 00FA16) is "1" (setting enabled).

In pulse width measuring mode, the "H" level width or the "L" level width of the signal input to either the CNTRo pin or the CNTR1 pin can be measured. To activate external pulse width measuring mode, set bit 6 of the timer 3, 4 mode register to "1". Select the count source with bits 4 and 5 of the timer 3, 4 mode register, then set bit 3 to "0" to count the number of timer 4 pulses generated while the signal at the CNTRo pin or the CNTR1 pin are either "H" or "L".

Select either the CNTRo pin or the CNTR1 pin by bit 4 of the active edge selection register (address 00D416), and select either the count during the "H" interval or the count during the "L" interval by bit 2 or bit 3 of the same register. When the edge selection bit is "0" (falling edge), pulses generated during the "H" interval are counted; when the edge selection bit is "1" (rising edge), pulses generated during the "L" interval are counted.

For details of PWM mode and the input latch function, see the appropriate sections.

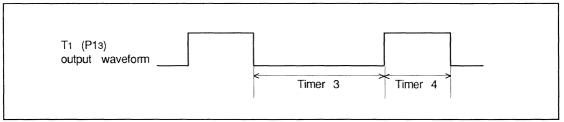

#### 2.6.2 PWM mode

The M37470 can output PWM waveforms from the T1 pin, using timer 3 and timer 4.