# 4-BIT EXPANDABLE BIPOLAR MICROCONTROLLER

|      | MILITARY | COMMERCIAL |

|------|----------|------------|

| 5701 | X        |            |

| 6701 |          | X          |

#### **PRODUCT FEATURES**

- Complete 4-Bit Bipolar LSI Processor Slice on a Single Chip.

- Replaces 25 TTL MSI Packages and Saves 5.5 Watts.

- 1000 Gate Complexity Schottky LSI Single Layer Metal.

- 36 Instructions Arithmetic, Logic, and Shifting Capability with Overflow Detection. Active High or Active Low Logic.

- 16 Directly Addressable, Two-port, General Purpose Accumulators Full 2 Address Capability, Some 3 Register Operations.

- A Separate Q-Register Useful as a Scratchpad or Accumulator Extension. Direct Data in and Accumulator Operations.

- Separate Low Fan in Input Bus and 3 State Output Bus.

- Expandable to handle N Bit Words with Full Carry Look-ahead.

- 200 ns Cycle (6701) which can Perform Multiple Nanoinstructions such as Subtract, Shift, and Store in One Cycle.

#### **APPLICATIONS**

- The Ideal Product for Upgrading or Replacing Existing

Central Processing Units and Maintaining the Existing Software.

The 5701/6701 can be Microprogrammed to Efficiently

Emulate (Simulate) Most Machines.

- Hard Wired Controllers Tape and Disk Controllers Data Concentrators.

- Point of Sale Terminals, Special Purpose Processors.

- Process and Machine Control.

- Word Processing and Navigation Systems.

- Intelligent Terminals and Game Machines.

- Traffic Control and Communications Systems.

- Upgrade Systems using the 74181, 9340, 9341, 74S281 Arithmetic Logic Units.

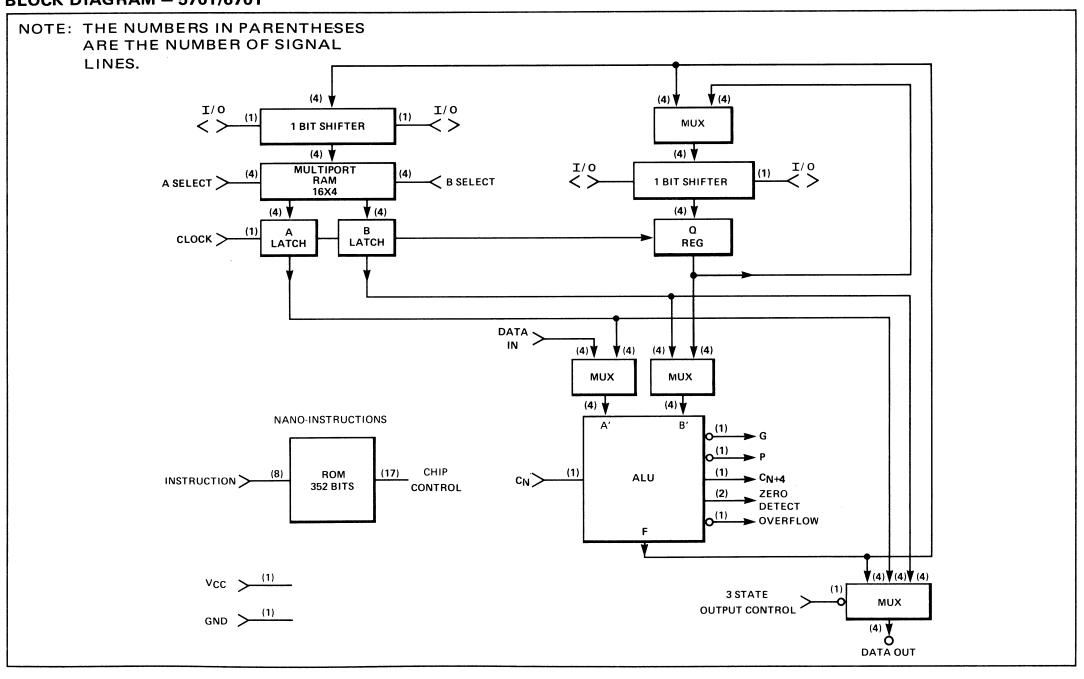

#### **BLOCK DIAGRAM - 5701/6701**

# **Monolithic Memories**

INCORPORATED

1165 East Arques Avenue/Sunnyvale, California 94086 (408) 739-3535 TWX 910-339-9229

#### I. INTRODUCTION

#### A) GENERAL DESCRIPTION

The microcontroller is designed to be used as a 4-bit processor slice of a conventional central processing unit (C.P.U) It can also be used in peripheral controllers, (tape, disk, etc.,) or as the heart of a microprocessor, terminal, or computer. It is a single chip 1000 gate complexity bipolar LSI device.

The two address capability (ability to work on two accumulators at once) and the powerful nano-instructions permit design of sub 1 microsecond cycle time hard wired C.P.U.'s or efficient emulation (imitation) of conventional machines using off chip ROMs for microprogramming.

The microcontroller will handle the data flow section of most computers since it is expandable to handle any word length in increments of 4 bits without significant speed degradation (look-ahead outputs are available). The 16 on-chip general purpose accumulators give the microcontroller the type of C.P.U. usually found only in high performance top of the line 16-bit minicomputers or 24 or 32-bit computers. It can be thought of as a general purpose 4-bit register and arithmetic logic unit with a separate A operand, B operand, data-in, and data-out ports. Additional accumulators or registers if required can be added with off chip packages tied to the microcontrollers data in pins.

#### B) TTL EQUIVALENT

The microcontroller is similar in function to the 25 TTL MSI packages listed below. It saves 375 I/O pins, 5.6 watts and 30 square inches of board area.

| Function                             | TTL#   | #14 Pin<br>or<br>#16 Pin<br>Pkgs. | #24 Pin<br>Pkgs. | Advertised<br>Gate Complexity<br>(Each Pkg.) | Gate<br>Complexity<br>Total | Typical<br>Power<br>Each (Watts) | Total<br>Power<br>(Watts) |

|--------------------------------------|--------|-----------------------------------|------------------|----------------------------------------------|-----------------------------|----------------------------------|---------------------------|

| 32 x 9 & 8 x 8 ROMs                  | 7488   | 3                                 |                  | 70                                           | 210                         | .50                              | 1.50                      |

| 16 x 4 Multiport RAM                 | 74172  |                                   | 4                | 150*                                         | 450                         | .56                              | 2.24                      |

| Arithmetic Logic Unit                | 74181  |                                   | 1                | <b>7</b> 5                                   | <b>7</b> 5                  | .55                              | .55                       |

| Storage Latches                      | 7475   | 2                                 |                  | 28                                           | 56                          | .16                              | .32                       |

| J-K Flip Flop (Q Reg)                | 74107  | 2                                 |                  | 22                                           | 44                          | .10                              | .20                       |

| 4 to 1 MUX                           | 74153  | 6                                 |                  | 16                                           | 96                          | .20                              | 1.20                      |

| O/I True Complement                  | 74H87  | 2                                 |                  | 18                                           | 36                          | .27                              | .54                       |

| Dual 4 Bit Select                    | 74157  | 2                                 |                  | 15                                           | 30                          | .15                              | .30                       |

| Quad 2 to 1 MUX with 3 State Outputs | 74S257 | 2                                 |                  | 15                                           | 30                          | .30                              | .60                       |

| 3 State Buffer                       | DM8094 | 1                                 |                  | 5                                            | 5                           | .18                              | .18                       |

| Totals                               |        | 20                                | 5                |                                              | 1032                        |                                  | 6.63                      |

<sup>\*</sup>NOTE: The 74172 is advertised at 201 gate complexity but we are using only 2 of the 3 address capability, hence we have counted it as 150 gates.

#### TABLE 1

#### C) PROCESS AND PACKAGING

The microcontroller is manufactured by an advanced Schottky bipolar single layer metal process. The chip requires only 5 volts and ground and all inputs and outputs are totally TTL compatible. The chip is packaged in a standard 40-pin dual in-line ceramic package.

#### D) POWER

The chip is designed to dissipate maximum power at low temperature. The power is minimum at high temperature. This feature permits full military range parts and easier power supply design.

#### E) PERFORMANCE

The microcontroller can execute one instruction every 200ns (250ns for the 5701). The instructions are more complex than normal micro-instructions permitting multiple operations in one cycle without timing problems.

#### II. OPERATION

#### A) BLOCK DIAGRAM

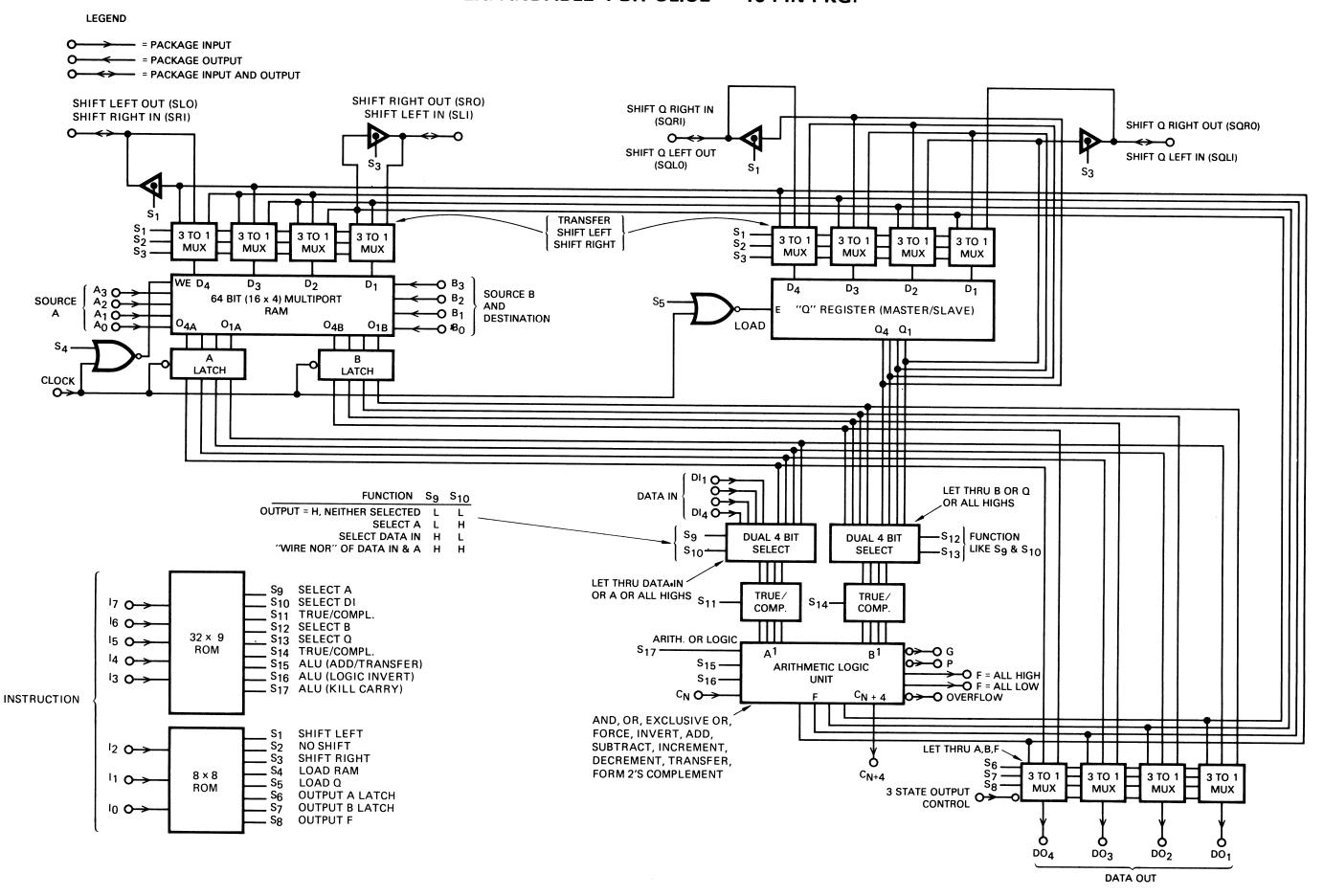

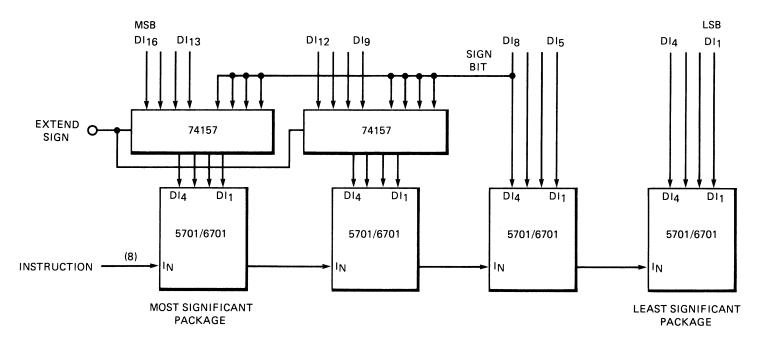

A detailed block diagram of the chip is shown in Figure 1. Note the legend used in the upper left hand corner for package inputs and outputs. The logic and control lines are shown as they are implemented on the chip even though fewer control inputs might be required by discrete logic devices. The dual 4-bit selects, at the input to the arithmetic logic unit, for example, have two "S" input control lines rather than the 74157 TTL equivalent which has one control line for letting through the left four bits or the right four bits on the output 4 bits.

#### B) ROM (LOWER LEFT CORNER)

Two on chip ROMs (352 bits total) are used to translate the eight (8) instruction lines I<sub>O</sub> to I<sub>7</sub> into 17 on chip control lines (labeled S<sub>1</sub> through S<sub>17</sub>) which open and close data paths required to execute an instruction.

The microcontroller is offered with a standard instruction set but the on chip ROM's can be custom coded for special customer requirements. (Contact factory for details.)

#### C) MULTIPORT RAM (UPPER LEFT CORNER)

A 16 word by 4 bit multiple port memory is used to fetch two operands at the same time since the RAM is double decoded (4 A address pins and 4B address pins). We could, for example, read from 0101 on the A address (file #5) and read from 0001 on the B address (file #1) at the same time. The B side of the RAM can be read out or written into independent of the address on the A side. The A side can only be read. The RAM must be loaded via the B side. The RAM if it is enabled is loaded when the clock is low. The duration of time the clock is low is the write enable pulse width required to switch the RAM.

#### D) LATCHES (CENTER LEFT)

The latches on the RAM outputs are the zero delay type (like 7475) which let the data into the latches appear on the latch outputs until the clock goes low and then hold the data. The latches permit parallel accessing of the RAM and ROM without two delays (one for the ROM and one for the RAM), since the access time of the ROM is masked by the delay through the RAM. The latches eliminate race conditions when the RAM data is fetched and updated in one cycle.

#### E) ARITHMETIC LOGIC UNIT (LOWER CENTER)

Input multiplexers into the arithmetic logic unit (A.L.U.) under ROM control permit the entry of data in or the A channel of the RAM into the A port of the ALU, and the B channel of the RAM or the Q register into the B port of the ALU.

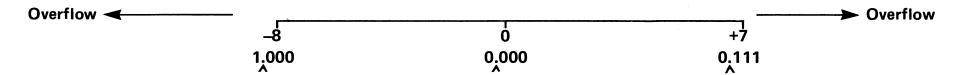

The ALU is of the conventional type except 0/1 true complement elements have been put in the input ports permitting the realization of a totally symmetrical ALU (i.e., A minus B or B minus A). Overflow detection and two zero detect pin (one for positive and one for negative logic) are also included.

#### F) OUTPUT MULTIPLEXERS (LOWER RIGHT HAND CORNER)

The 3 to 1 output multiplexers under ROM control let through the ALU output, the A latch output, the B latch output on the data out pins. The output multiplexers are three-state outputs controlled by the three-state output control pin. The three-state outputs permit processing to be performed in the microcontroller without tying up the data out bus.

#### G) SHIFT MULTIPLEXERS (UPPER LEFT AND UPPER RIGHT)

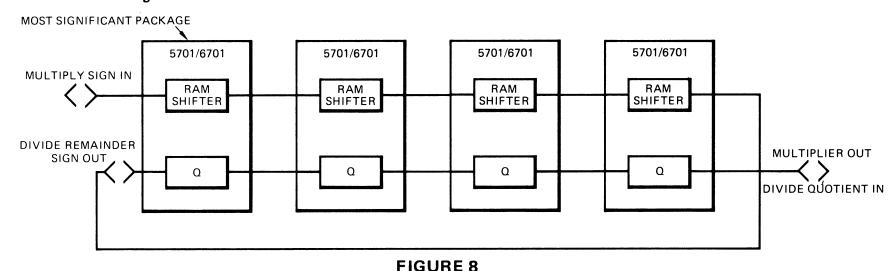

The four 3 to 1 mux's on top of the Q register permit the ALU output bus F to transfer straight through into the Q register or be shifted 1 bit left or right before being entered into the Q register. The four 3 to 1 multiplexer above the RAM function in the same manner. Both the RAM shifter and the Q shifter employ bi-directional shift in/shift out pins to permit expansion to more than 4 bits.

#### H) Q REGISTER (UPPER RIGHT)

The Q register can function as an accumulator extension register. It would normally be used to hold the least significant half of the double length product of a multiplication or as a storage register to catch the bits shifted off the beginning or end of a word during left or right shifting. In this mode of operation, the shift out pin of the least significant bit of the RAM shifter would be tied to the shift in pin of the most significant bit of the Q register. The Q register can shift on itself and be loaded from the ALU bus while any instruction is being executed. Its shift control pins, are in common with RAM shift controls permitting RAM shifting into Q and vice versa in one cycle. It can also be used as a program counter or scratchpad.

The Q register is a master slave flip-flop. Data is loaded into the master when the clock goes low (assuming it is enabled by the ROM) and transferred from the master to the slave when the clock goes high.

#### **EXPANDABLE 4 BIT SLICE — 40 PIN PKG.**

FIGURE 1

#### III. STATE OF THE ART ALU'S

A comparsion of the 6701 with commercially available ALU's is shown in table 2.

**TABLE 2 - 4 BIT ARITHMETIC UNITS**

|                                                                                                                                            | Arithmetic Logic Unit 74S181 | Monolithic Accumulator 74S281                                                      | Microcontroller<br>6701                   |

|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------|-------------------------------------------|

| Year Introduced                                                                                                                            | 1972                         | 1973                                                                               | 1974                                      |

| Gate Complexity                                                                                                                            | 75                           | 125                                                                                | 1000                                      |

| Package Size                                                                                                                               | 16 Pin                       | 24 Pin                                                                             | 40 Pin                                    |

| Number of Accumulators                                                                                                                     | 0                            | 1                                                                                  | 16                                        |

| Multiport Accumulators                                                                                                                     | No                           | No                                                                                 | Yes                                       |

| Number of Useful Arithmetic Instructions                                                                                                   | 4                            | 11                                                                                 | 21                                        |

| Number of Useful Logic Instructions                                                                                                        | 10                           | 11                                                                                 | 15                                        |

| One Bit Bidirectional Shift Capability                                                                                                     | No                           | Yes                                                                                | Yes                                       |

| Interface to 74S182 Look Ahead Carry Generator                                                                                             | Yes                          | Yes                                                                                | Yes                                       |

| Simultaneous Entry of Two Operands                                                                                                         | Yes                          | No                                                                                 | Yes                                       |

| Three State Outputs                                                                                                                        | No                           | No                                                                                 | Yes                                       |

| Zero Detect                                                                                                                                | Yes                          | No                                                                                 | Yes                                       |

| Overflow Detection                                                                                                                         | No                           | No                                                                                 | Yes                                       |

| Accumulator Extension Register                                                                                                             | No                           | No                                                                                 | Yes                                       |

| Accumulator Extension Register One Bit Shift Capability                                                                                    | No                           | No                                                                                 | Yes                                       |

| Operate on 3 Registers in One Cycle                                                                                                        | NA                           | No                                                                                 | Yes                                       |

| Symmetrical ALU (i.e. A minus B and B minus A)                                                                                             | No                           | Yes                                                                                | Yes                                       |

| Number of ALU input ports                                                                                                                  | 2                            | 2                                                                                  | 4                                         |

| Number of ALU output ports                                                                                                                 | 1                            | 1                                                                                  | 3                                         |

| Power Dissipation (TYP)                                                                                                                    | 600 mW                       | 750 mW                                                                             | 900 mW                                    |

| Power (mW) per Gate                                                                                                                        | 8                            | 6                                                                                  | .9                                        |

| ALU Time Required to Add Two 4 Bit Operands and Store the Result in an Accumulator Inside the ALU. A CPU with 3 to 16 Registers is Assumed | NA                           | 205 ns<br>(Max @ 5.0 V, 25°C)<br>Requires Off Chip<br>35 ns 64 Bit<br>(16 x 4) RAM | 200 ns<br>(Max @ 5.0 V ± 5%<br>0 to 75°C) |

| Number of Microcycles Required to Add Two 4 Bit Operands, Store the Result in an Accumulator and Look at the Result                        | NA                           | 4                                                                                  | 1                                         |

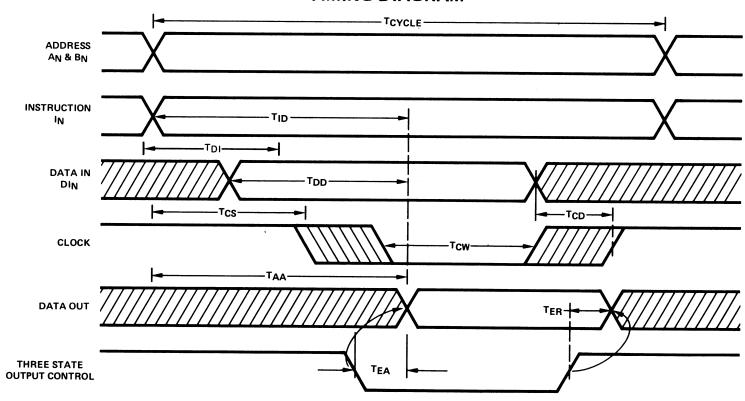

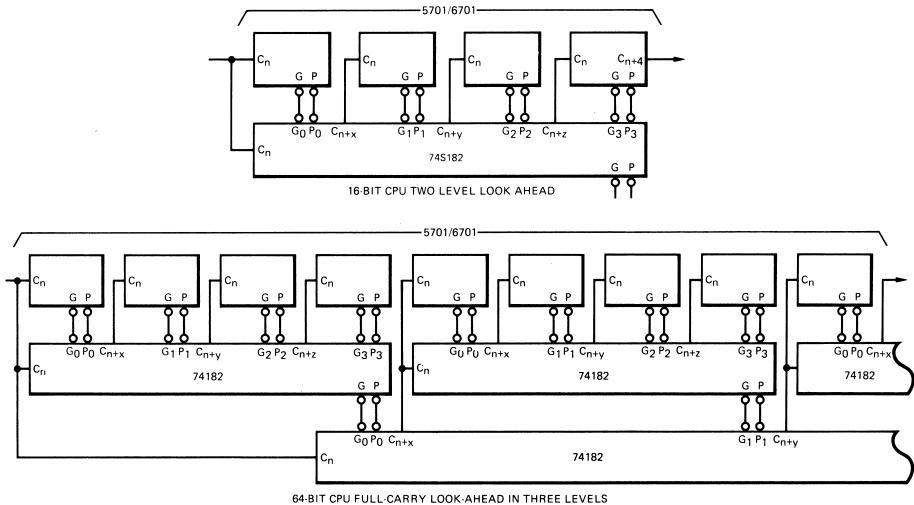

#### IV. CPU'S LARGER THAN 4 BITS

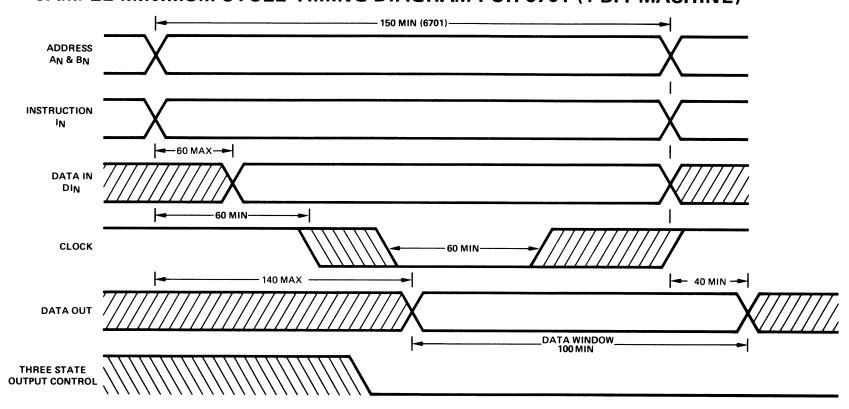

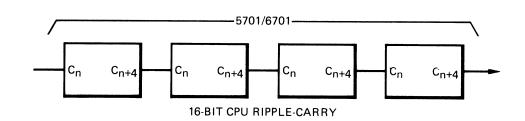

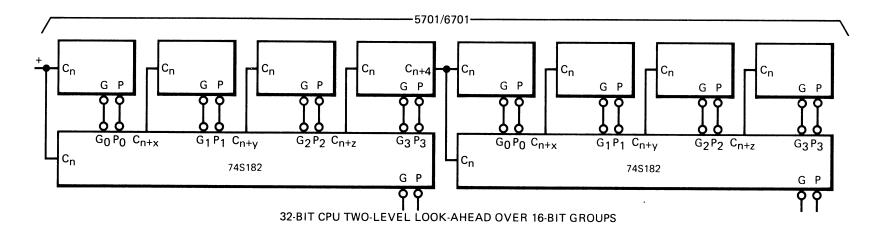

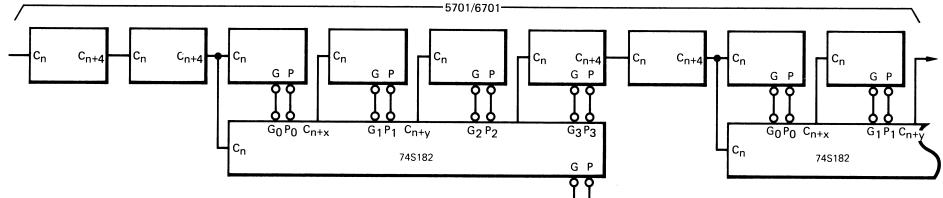

CPU's larger than 4 bits will have to wait for the carry generated by an off chip look ahead 74S182 or the ripple carry generated by the lower order package's  $C_{N+4}$ . As a result the minimum cycle time of the 5701/6701 will increase. When drawing timing diagram for these CPU's the amount of time the clock is high ( $T_{CS}$  of Figure 5) should be increased to permit a longer time for the ALU to stabilize based on the carry from lower order packages before bringing the clock low and writing into the RAM. The required clock low time ( $T_{CW}$  of Figure 5) does not have to be increased for CPU's larger than 4 bits. Page 14 shows the minimum cycles for larger machines.

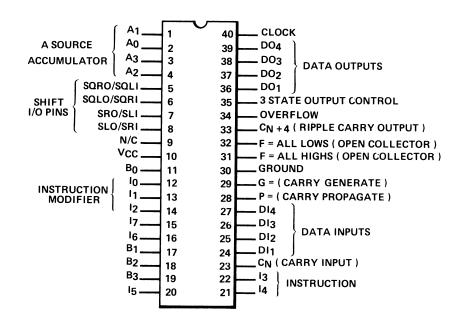

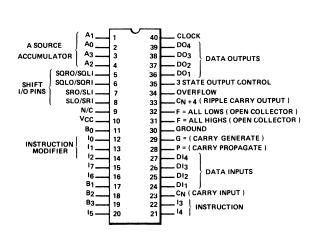

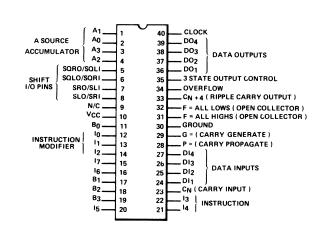

#### IV. PACKAGE PINS

Figure 2 shows a listing of the 40 pin I/O. The microcontroller will use a standard 40 lead ceramic dip approximately 2.00 inches long and .60 inches wide. See Figure 3 for the package details. NOTE THAT V<sub>CC</sub> AND GROUND ARE NOT ON THE CONVENTIONAL END PINS. This was necessary because the package current would produce too high a voltage drop in the package lead resistance out to the end pins to meet the V<sub>OL</sub> requirements.

#### **PIN CONFIGURATION**

Figure 2.

#### **PACKAGE OUTLINE** 2.000 ± .030 40 Pin Ceramic (Side Braze) $\Theta_{JA}$ (thermal resistance from junction to ambient soldered to a printed circuit board in still air) $\approx 35^{\circ}$ C/watt .580 ± .015 $\Theta_{\mbox{\scriptsize JC}}$ (thermal resistance from junction to case with freon as a heat sink) $\approx 20^{\circ}$ C/watt SHOULDER WIDTH .055 ± .015 .100 TYPICAL SEATED HEIGHT .230 MAX. .020 MAX LID THICKNESS .010 ± .003, .125 MIN **PLANE** .018 ± .004 -015. ± 600. .015 MIN (19 PLCS)

Figure 3.

#### **BURN-IN CIRCUIT**

The circuit in Figure 4 below puts the device in an instruction where the state of all outputs is known. Any other set of levels on the inputs may result in undefined output states and possible damage to the device under burn-in conditions. The other instructions involve the use of internal register whose initial conditions, after power-up, are undefined. The burn-in circuit shown comes closest to the usual reverse burn-in circuits of logic devices. The unit is in the force LLLL mode with the shift I/O pins disabled, the data outputs disabled, and with a single accumulator always selected.

VCC **BURN IN CIRCUIT >** R1 5701/6701 39 38 37 36 35 34 33 32 31 30 29 27 26 15 25 24 17 23 18 22 21 20

Figure 4.

# **ELECTRICAL PARAMETERS**

#### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage, V<sub>CC</sub>

Input Voltage

Output Current

-0.5 to 7 V

-1.0 to 5.5 V

Input Current -20 to 5 mA Stresses above or extended time at Absolute Maximum Rat-Storage Temperature -65 to +150°C ings may cause permanent damage or affect device reliability.

D. C. CHARACTERISTICS Unless otherwise indicated, all limits for the 6701 are guaranteed for 5 V  $\pm 5\%$  in a free air temperature of 0 to  $75^{\circ}$ C; all limits for the 5701 are guaranteed for 5 V  $\pm 10\%$  in a free air temperature of -55 to  $125^{\circ}$ C.

| P. 4            | DAMETER                            | DEVICE                                                                                 | CONDITIONS                                                                                     |      | 5701        |       |          | 6701              |       | UNITS |

|-----------------|------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|-------------|-------|----------|-------------------|-------|-------|

| PA              | RAMETER                            | PINS                                                                                   | CONDITIONS                                                                                     | MIN. | TYP.1       | MAX.  | MIN.     | TYP. <sup>1</sup> | MAX   |       |

| l F             | Input Load                         |                                                                                        |                                                                                                |      | ;<br>;<br>; |       |          |                   |       |       |

| •               | Current                            | Any A, B, or I                                                                         | $V_{CC}$ = Max, $V_F$ = .45 $V$                                                                |      |             | -250  |          |                   | -250  | μΑ    |

|                 |                                    | Clock or 3 State                                                                       | "                                                                                              |      |             |       |          |                   |       | _     |

|                 |                                    | Control                                                                                |                                                                                                |      |             | -250  |          |                   | -250  | μΑ    |

|                 |                                    | Shift I/O & Data In                                                                    | ,,                                                                                             |      |             | -0.80 |          |                   | -0.80 | mA    |

|                 |                                    | $c_N$                                                                                  | "                                                                                              |      |             | -4.80 |          |                   | -4.80 | mA    |

| R               | Input Leakage                      |                                                                                        |                                                                                                |      |             |       |          |                   |       |       |

| ••              | Current                            | Any A, B, or I                                                                         | $V_{CC}$ = Max, $V_R$ = 2.40 V                                                                 |      |             | 40    |          |                   | 25    | μΑ    |

|                 | ·                                  | Clock or 3 State                                                                       | ••                                                                                             |      |             |       |          |                   |       |       |

|                 |                                    | Control                                                                                |                                                                                                |      | ļ           | 40    |          |                   | 25    | μΑ    |

|                 |                                    | Shift I/O                                                                              | Used as an Input                                                                               |      |             | 100   |          |                   | 100   | μΑ    |

|                 |                                    | Data Inputs                                                                            | ,,                                                                                             |      |             | 20    |          |                   | 20    | μΑ    |

|                 |                                    | CN                                                                                     | "                                                                                              |      |             | 120   |          |                   | 120   |       |

| RB              | Input Leakage                      |                                                                                        |                                                                                                |      |             |       |          |                   | _     |       |

|                 | Current                            | Any A, B, or I                                                                         | $V_{CC}$ = Max, $V_{RB}$ = 5.50 V                                                              |      |             | 1.0   |          |                   | 1.0   | mA    |

|                 |                                    | Clock or 3 State                                                                       | "                                                                                              |      |             |       |          |                   |       |       |

|                 |                                    | Control                                                                                |                                                                                                |      |             | 1.0   |          |                   | 1.0   | mA    |

|                 |                                    | Shift I/O                                                                              | "                                                                                              |      |             | 1.0   |          | <u> </u>          | 1.0   | mA    |

|                 |                                    | Data Input                                                                             | "                                                                                              |      |             | 1.0   |          |                   | 1.0   | mA    |

|                 |                                    | C <sub>N</sub>                                                                         | "                                                                                              |      |             | 1.0   |          |                   | 1.0   | mA    |

| V <sub>OL</sub> | Low Level Out-<br>put Voltage      |                                                                                        | V <sub>CC</sub> = Min, I <sub>OL</sub> = 16 mA                                                 |      | .35         | 0.50  |          | .35               | 0.50  | V     |

|                 |                                    | F = All Low                                                                            |                                                                                                |      |             |       | <u> </u> |                   | 0.50  | .,    |

|                 |                                    | P, Overflow                                                                            | V <sub>CC</sub> = Min, I <sub>OL</sub> = 10 mA                                                 |      | .35         | 0.50  |          | .35               | 0.50  |       |

|                 |                                    | Shift I/O                                                                              | V <sub>CC</sub> = Min, I <sub>OL</sub> = 6 mA<br>Used as an Output                             |      | .35         | 0.50  |          | .35               | 0.50  | V     |

| Icc             | Power Supply<br>Current            | V <sub>CC</sub> , Grd                                                                  | All inputs ground (worst case), All Outputs Open, Shift I/O Open VCC = 5.00 V and Temp = Max   |      | 215         | 250   |          | 215               | 280   | mA    |

|                 |                                    |                                                                                        | All Inputs ground (worst case), All Outputs Open, Shift I/O Open VCC = 5.00 V and Temp = Min   |      | 230         | 280   |          | 230               | 250   | mA    |

| VIL             | Low Level<br>Input Voltage         | All Inputs and<br>Shift I/O                                                            | V <sub>CC</sub> = 5.00 V                                                                       |      |             | 0.80  |          |                   | 0.80  | V     |

| VIH             | High Level<br>Input Voltage        | All Inputs and<br>Shift I/O                                                            | V <sub>CC</sub> = 5.00 V                                                                       | 2.0  |             |       | 2.0      |                   |       | V     |

| VIC             | Input Clamp<br>Voltage             | All Inputs and<br>Shift I/O                                                            | V <sub>CC</sub> = Min, I <sub>IC</sub> = -5.0 mA                                               |      | -1.0        | -1.5  |          | -1.0              | -1.5  | V     |

| CEX             | Output Leakage<br>Current          | All Outputs and Shift I/O                                                              | V <sub>CC</sub> = Max, V <sub>CEX</sub> = 2.40 V,<br>High Stored or Disabled                   |      |             | 100   |          |                   | 100   | μΑ    |

|                 |                                    |                                                                                        | V <sub>CC</sub> = Max, V <sub>CEX</sub> = 0.45 V<br>Disabled                                   |      |             | -100  |          |                   | -100  | μΑ    |

| CEXB            | Output Leak-<br>age Current        | All Outputs and<br>Shift I/O                                                           | V <sub>CC</sub> = Max = V <sub>CEXB</sub> High Stored or Disabled                              |      |             | 1     |          |                   | 1     | mA    |

| SC              | Output Short<br>Circuit<br>Current | DO <sub>1</sub> , DO <sub>2</sub> , DO <sub>3</sub> ,<br>DO <sub>4</sub> , G, P, OVFL, | V <sub>OUT</sub> = OV, V <sub>CC</sub> = 5 V<br>Only one Output at a time<br>should be Shorted | 20   | 50          | 90    | 20       | 50                | 90    | mA    |

|                 |                                    | Shift I/O                                                                              | V <sub>OUT</sub> = OV, V <sub>CC</sub> = 5 V<br>Only one Output at a time<br>should be Shorted | 5    | 15          | 50    | 5        | 15                | 50    | mA    |

# **ELECTRICAL PARAMETERS (Cont'd)**

#### D.C. CHARACTERISTICS (Cont'd)

|     |                       | DEVICE                                                                                         | CONDITIONS                                                                 |      | 5701  |      | 6701 |       |     | UNITS |

|-----|-----------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------|-------|------|------|-------|-----|-------|

| P   | ARAMETER              | PINS                                                                                           | CONDITIONS                                                                 | MIN. | TYP.1 | MAX. | MIN. | TYP.1 | MAX | UNITS |

| VOH | Output Voltage "High" | DO <sub>1</sub> , DO <sub>2</sub> , DO <sub>3</sub> ,<br>DO <sub>4</sub> , G, C <sub>N+4</sub> | I <sub>O</sub> = -3.2 mA, V <sub>CC</sub> = Min<br>High Stored             | 2.4  |       |      | 2.4  |       |     | V     |

|     |                       | Shift I/O, P, OVFL                                                                             | $I_O = -500 \mu A V_{CC} = Min$<br>High Stored                             | 2.4  | 3.5   |      | 2.4  | 3.5   |     | V     |

| Cl  | Input<br>Capacitance  | All Inputs                                                                                     | $V_{CC} = 5.0 \text{ V}, V_{I} = 2.0 \text{ V}, 25^{\circ}\text{C},$ 1 MHz |      | 8     |      |      | 8     |     | pF    |

| co  | Output<br>Capacitance | All Outputs                                                                                    | V <sub>CC</sub> = 5.0 V, V <sub>O</sub> = 2.0 V,<br>25°C, 1 MHz            |      | 8     |      |      | 8     |     | pF    |

<sup>1.</sup> Typical values are measured at 5.0 V and 25°C.

A. C. CHARACTERISTICS The maximum or minimum of all possible input and output conditions is specified with outputs sinking maximum current and driving a 30pF load (15pF on Shift I/O).

| PARAMETER                                                 | SYMBOL/CONDITIONS                                                           |          | 5 V ± 10%<br>5 TO 125<br>5701 |        |             | 5 V ± 5%<br><u>0 TO 75°</u><br>6701 |        |       |

|-----------------------------------------------------------|-----------------------------------------------------------------------------|----------|-------------------------------|--------|-------------|-------------------------------------|--------|-------|

|                                                           | SEE FIGURE 5                                                                | MIN.     | TYP. <sup>1</sup>             |        |             | TYP.1                               | MAX.   | UNITS |

| Microinstruction Clock Cycle (Time Between Instructions)  | TCYCLE                                                                      | 250      | 152                           | ∞      | MIN.<br>200 | 152                                 | ∞      | ns    |

| Accumulator Address to Data Out Delay Thru ALU/Bypass ALU | ТАА                                                                         | 40/20    | 110/60                        | 170/90 | 40/20       | 110/60                              | 140/85 | ns    |

| Instruction to Data Out Delay                             | T <sub>ID</sub>                                                             | 40       | 110                           | 175    | 40          | 110                                 | 140    | ns    |

| Clock Pulse Width                                         | T <sub>CW</sub>                                                             | 80       | 42                            |        | 60          | 42                                  |        | ns    |

| Clock Set-up Time                                         | T <sub>CS</sub>                                                             | 115      | 80                            |        | 80          | 70                                  |        | ns    |

| 3 State Enable to Data Out Enable                         | TEA                                                                         | 10       | 25                            | 40     | 10          | 25                                  | 37     | ns    |

| 3 State Disable to Output Disable                         | TER                                                                         | 5        | 14                            | 25     | 5           | 14                                  | 20     | ns    |

| C <sub>N</sub> to C <sub>N+4</sub>                        |                                                                             |          | 20                            | 30     |             | 20                                  | 30     | ns    |

| Accumulator Address to CN+4                               | Clock High                                                                  |          | 65                            | 95     |             | 65                                  | 90     | ns    |

| Data In to C <sub>N+4</sub>                               |                                                                             |          | 28                            | 42     |             | 28                                  | 40     | ns    |

| Instruction to C <sub>N+4</sub>                           | Clock High                                                                  |          | 54                            | 81     |             | 54                                  | 78     | ns    |

| Accumulator Address to G                                  | Clock High                                                                  |          | 60                            | 90     |             | 60                                  | 85     | ns    |

| Data In to G                                              |                                                                             |          | 36                            | 54     |             | 36                                  | 50     | ns    |

| Instruction to G or P                                     | Clock High                                                                  |          | 52                            | 78     |             | 52                                  | 75     | ns    |

| Accumulator Address to P                                  | Clock High                                                                  |          | 60                            | 90     |             | 60                                  | 85     | ns    |

| Data In to P                                              |                                                                             |          | 25                            | 40     |             | 25                                  | 37     | ns    |

| Accumulator Address to F = All Highs                      | Clock High                                                                  |          | 64                            | 96     |             | 64                                  | 90     | ns    |

| Data In to F = All Highs                                  |                                                                             |          | 60                            | 90     |             | 60                                  | 86     | ns    |

| Instruction to F = All Highs                              | Clock High                                                                  |          | 76                            | 110    |             | 76                                  | 100    | ns    |

| Accumulator Address to F = All Lows                       | Clock High                                                                  |          | 64                            | 96     |             | 64                                  | 90     | ns    |

| Data In to F = All Lows                                   |                                                                             | <u> </u> | 40                            | 60     |             | 40                                  | 57     | ns    |

| Instruction to F = All Lows                               | Clock High                                                                  |          | 60                            | 90     |             | 60                                  | 85     | ns    |

| Accumulator Address to SLO/SRI or SRO/SLI                 | Clock High                                                                  |          | × 95                          | 140    |             | 95                                  | 130    | ns    |

| Data In to SLO/SRI or SRO/SLI                             |                                                                             |          | 40                            | 60     |             | 40                                  | 55     | ns    |

| Instruction to SLO/SRI or SRO/SLI                         | Clock High                                                                  |          | 75                            | 110    |             | 75                                  | 105    | ns    |

| Instruction to SQRI/SQLO or SQRO/SQLI                     | Clock High                                                                  |          | 25                            | 40     |             | 25                                  | 37     | ns    |

| Clock to Data Out Delay                                   | A <sub>N</sub> , B <sub>N</sub> , C <sub>N</sub> , D <sub>N</sub><br>Stable | 40       | 110                           | 175    | 40          | 110                                 | 140    | ns    |

#### A.C. CHARACTERISTICS (Cont'd)

| PARAMETER                             | SYMBOL/CONDITIONS  SEE FIGURE 5                                      | 5 V ± 10%<br>-55 TO 125°C<br>5701<br>MIN. TYP. <sup>1</sup> MAX. |     |     | 5 V ± 5%<br>0 TO 75°C<br>6701<br>MIN. TYP. 1 MAX. |     |     | UNITS |

|---------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------|-----|-----|---------------------------------------------------|-----|-----|-------|

| Data In to Data Out Delay             | T <sub>DD</sub> Clock High                                           | 20                                                               | 60  | 90  | 20                                                | 60  | 85  | ns    |

| Clock to Data In Hold Time            | T <sub>CD</sub> Clock Low to High<br>Transition                      |                                                                  | -20 | -10 |                                                   | -20 | -10 | ns    |

| Latest Possible Arrival of<br>Data In | T <sub>DI</sub> Measure Relative to A <sub>N</sub> or I <sub>N</sub> |                                                                  |     | 60  |                                                   |     | 60  | ns    |

| Q Register to SQLO/SQRI or SQRO/SQRI  | Measured From Low to<br>High Transition of Clock                     |                                                                  | 36  | 54  |                                                   | 36  | 50  | ns    |

| Accumulator Address to Overflow       | Clock High                                                           |                                                                  | 90  | 135 |                                                   | 90  | 125 | ns    |

| Data In to Overflow                   |                                                                      |                                                                  | 36  | 54  |                                                   | 36  | 50  | ns    |

| Instruction to Overflow               | Clock High                                                           |                                                                  | 56  | 84  |                                                   | 56  | 80  | ns    |

| C <sub>N</sub> to Overflow            |                                                                      |                                                                  | 25  | 38  |                                                   | 25  | 35  | ns    |

| C <sub>N</sub> to Data Out            | Three State Low                                                      | 5                                                                | 36  | 54  | 5                                                 | 36  | 50  | ns    |

1. Typical values are measured at 5.0 V, 25°C

#### **TIMING DIAGRAM**

# SAMPLE MINIMUM CYCLE TIMING DIAGRAM FOR 6701 (4 BIT MACHINE)

LEGEND: Shaded areas indicate don't care conditions or permitted timing tolerances.

Indicates that one pulse edge causes the other and that the two edges track.

FIGURE 5

### INSTRUCTIONS LOCATED IN THE ON CHIP ROMS

#### **SYMBOL DEFINITIONS**

$A_{I}$  = Any of the 16 four bit registers in the multiport RAM (I = 0 to 15)

$B_{.J} =$ (J = 0 to 15)

$A_I + B_J = A_I plus B_J$  (arithmetic addition)

$A_1 \forall B_J = A_1 \text{ exclusive OR'ed with } B_J$

$A_I \vee B_J = A_I \text{ or } B_J \text{ (logic inclusive or)}$

$A_I \wedge B_J = A_I \text{ and } B_J \text{ (logic and)}$

$\overline{A_I}$  = The complement of  $A_I$

$A_1 \longrightarrow Q = Transfer A_1 to Q, A_1 saved, Old Q is lost$

$A_1 \longrightarrow OUT = Transfer A_1$  to the output pins,  $A_1$  is saved

$\overline{A_1}$  =  $A_1$  shifted right one bit

$\overline{A_I}$  = A<sub>I</sub> shifted left one bit B<sub>J</sub> - A<sub>I</sub> = B<sub>J</sub> minus A<sub>I</sub> = B<sub>J</sub> +  $\overline{A_I}$  + C<sub>N</sub> = B<sub>J</sub> + 2's compl. of A<sub>I</sub>

#### POSITIVE (ACTIVE HIGH) VS. NEGATIVE (ACTIVE LOW) LOGIC

The Microcontroller will work with either positive or negative logic. Positive logic defines a TTL High Level (≈ 3V) to be a "I" and a Low TTL Level (≈ GRD) to be a "O". Negative logic defines a TTL High to be A "O" and a TTL Low to be a "I". Consider a

a classical "AND" function in TTL Logic OUTPUT INPUTS

| OUIPUI | INP | 012 |

|--------|-----|-----|

|        | В   | Α   |

| L      | L   | ٦   |

| L      | L   | Н   |

| L      | Н   | L   |

| Н      | н   | Н   |

| OUTPUT | PUT INPL |     |  |  |  |

|--------|----------|-----|--|--|--|

|        | В        | Α   |  |  |  |

| 0      | 0        | 0   |  |  |  |

| 0      | 0        | - 1 |  |  |  |

| 0      | 1        | 0   |  |  |  |

| 1      | 1        | - 1 |  |  |  |

In negative logic the "AND" becomes an "OR" function since:

| OUTPUT     | INPUTS |     |  |  |  |

|------------|--------|-----|--|--|--|

|            | В      | Α   |  |  |  |

| 1          | ı      | 1   |  |  |  |

| → <b>1</b> | ı      | 0   |  |  |  |

| 1          | 0      | - 1 |  |  |  |

| 0          | 0      | 0   |  |  |  |

in positive logic this becomes

Thus an "AND" in positive logic is an "OR" in negative logic. Similar reasoning yields the following transformations.

#### **POSITIVE LOGIC NEGATIVE LOGIC** AND OR OR AND **EXCLUSIVE OR EXCLUSIVE NOR EXCLUSIVE NOR EXCLUSIVE OR TRANSFER** DECREMENT **DECREMENT TRANSFER INCREMENT** TRANSFER **TRANSFER INCREMENT**

#### CARRY IN (CN)

The carry in pin is high when a carry is desired in positive logic, and a low when a carry is desired in negative logic.

#### **TWO ROMS**

All of the instructions in the 32 x 9 ROM can be modified in 8 different ways by the 8 x 8 ROM. Any instruction for example can be shifted left or right with the data out pins showing A, B, or F and the shifted result stored in the RAM or Q Register or both. If the clock is gated OFF by external logic it will be impossible to load the RAM or Q Register, and the controlled use of CN in many instructions further raises the instruction count.

# INSTRUCTIONS IN THE 32 x 9 ROM — POSITIVE LOGIC (1 = H ≈ 3 V) INTERPRETATION

|          |    |    |    |                |                 |       | ALU Instruction                                   | ALU O                                  | UTPUT                                  | TYPICAL                      |                                 |  |

|----------|----|----|----|----------------|-----------------|-------|---------------------------------------------------|----------------------------------------|----------------------------------------|------------------------------|---------------------------------|--|

|          | 16 | 15 | Γ. | I <sub>3</sub> | VORD<br>Decimal | Octal | (See Pg. 8 for Symbology)                         | No Carry In<br>(C <sub>N</sub> = L)    | With Carry In<br>(C <sub>N</sub> = H)  | USES                         |                                 |  |

| L        | L  | L  | L  | L              | 0               | 00    | LLLL + HHHH + C <sub>N</sub>                      | Force 1111                             | Force 0000                             | Initialization (Force 1's or | O's)                            |  |

| L        | L  | L  | L  | Н              | 1               | 01    | AND A <sub>I</sub> & B <sub>i</sub>               | A <sub>I</sub> ΛB <sub>i</sub>         | A <sub>I</sub> ΛB <sub>j</sub>         | AND                          | A <sub>1</sub> & B <sub>j</sub> |  |

| L        | L  | L  | Н  | L              | 2               | 02    | AND D <sub>1</sub> & B <sub>j</sub>               | D <sub>I</sub> ∧ B <sub>j</sub>        | D <sub>I</sub> Λ B <sub>j</sub>        | "                            | D <sub>I</sub> & B <sub>j</sub> |  |

| L        | L  | L  | Н  | Н              | 3               | 03    | OR A <sub>I</sub> & B <sub>j</sub>                | A <sub>I</sub> V B <sub>j</sub>        | A <sub>I</sub> V B <sub>j</sub>        | OR                           | A <sub>I</sub> & B <sub>j</sub> |  |

| L        | L  | Н  | L  | L              | 4               | 04    | OR D <sub>I</sub> & B <sub>j</sub>                | D <sub>I</sub> V B <sub>j</sub>        | D <sub>I</sub> V B <sub>j</sub>        | "                            | D <sub>I</sub> & B <sub>j</sub> |  |

| L        | L  | Н  | L  | Н              | 5               | 05    | Exclusive OR A <sub>1</sub> & B <sub>j</sub>      | A <sub>I</sub> ★ B <sub>j</sub>        | A <sub>I</sub> ₩ B <sub>j</sub>        | Exclusive Or                 | A <sub>I</sub> & B <sub>j</sub> |  |

| L        | L  | Н  | Н  | L              | 6               | 06    | Exclusive OR D <sub>I</sub> & B <sub>j</sub>      | D <sub>I</sub> ₩ B <sub>j</sub>        | D <sub>I</sub> ₩ B <sub>j</sub>        | "                            | D <sub>I</sub> & B <sub>j</sub> |  |

| L        | L  | Н  | Н  | Н              | 7               | 07    | A <sub>I</sub> + HHHH + C <sub>N</sub>            | A <sub>I</sub> + 1111                  | Aı                                     | Invert                       | Al                              |  |

| L        | Н  | L  | L  | L              | 8               | 10    | D <sub>I</sub> + HHHH + C <sub>N</sub>            | D <sub>I</sub> + 1111                  | DI                                     | 11                           | D <sub>I</sub>                  |  |

| L        | Н  | L  | L  | Η.             | 9               | 11    | <del>В</del> <sub>ј</sub> + нннн + С <sub>N</sub> | B <sub>j</sub> + 1111                  | Bj                                     |                              | Вј                              |  |

|          | Н  | L  | Н  | L              | 10              | 12    | <u>Q</u> + HHHH + C <sub>N</sub>                  | Q + 1111                               | ā                                      | "                            | Q                               |  |

| L        | Н  | L  | Н  | Н              | 11              | 13    | A <sub>I</sub> + LLLL + C <sub>N</sub>            | Aı                                     | A <sub>I</sub> + 0001                  | 2's Complement Of            | Al                              |  |

| L        | Н  | Ĥ  | L  | L              | 12              | 14    | D <sub>I</sub> + LLLL + C <sub>N</sub>            | DI                                     | D <sub>I</sub> + 0001                  | "                            | D <sub>I</sub>                  |  |

| L        | I  | Н  | L  | Н              | 13              | 15    | B <sub>j</sub> + LLLL + C <sub>N</sub>            | Bj                                     | B <sub>j</sub> + 0001                  | ,,                           | Bj                              |  |

| L        | Н  | Н  | Н  | L              | 14              | 16    | Q + LLLL + C <sub>N</sub>                         | ā                                      | Q + 0001                               | ;;                           | Q                               |  |

| L        | Н  | Н  | H  | Н              | 15              | 17    | A <sub>I</sub> + LLLL + C <sub>N</sub>            | A <sub>I</sub>                         | A <sub>I</sub> + 0001                  | Transfer Or Increment        | A <sub>I</sub>                  |  |

| Н        | L  | L  | L  | L              | 16              | 20    | D <sub>I</sub> + LLLL + C <sub>N</sub>            | D <sub>I</sub>                         | D <sub>I</sub> + 0001                  | "                            | DI                              |  |

| Н        | L  | L  | L  | Н              | 17              | 21    | B <sub>j</sub> + LLLL + C <sub>N</sub>            | Вј                                     | B <sub>j</sub> + 0001                  | "                            | Вј                              |  |

| Н        | L  | L  | Н  | L              | 18              | 22    | Q + LLLL + C <sub>N</sub>                         | Q                                      | Q + 0001                               | "                            | <u>Q</u>                        |  |

| Н        | L  | L  | Н  | Н              | 19              | 23    | A <sub>I</sub> + HHHH + C <sub>N</sub>            | A <sub>I</sub> + 1111                  | Α <sub>I</sub>                         | Decrement Or Transfer        | A <sub>I</sub>                  |  |

| <u>H</u> | L  | Н  | L  | L              | 20              | 24    | D <sub>I</sub> + HHHH + C <sub>N</sub>            | D <sub>I</sub> + 1111                  | D <sub>I</sub>                         | "                            | DI                              |  |

| _H       | L  | Н  | L  | Н              | 21              | 25    | B <sub>j</sub> + HHHH + C <sub>N</sub>            | B <sub>j</sub> + 1111                  | Вј                                     | "                            | Bj                              |  |

| <u>H</u> | L  | H  | Н  | L              | 22              | 26    | Q + HHHH + C <sub>N</sub>                         | Q + 1111                               | <u>Q</u>                               | "                            | <u>Q</u>                        |  |

| Н        | L  | Н  | Н  | Н              | 23              | 27    | $A_I + B_j + C_N$                                 | A <sub>I</sub> + B <sub>j</sub>        | A <sub>I</sub> + B <sub>j</sub> + 0001 | Add                          | A <sub>1</sub> & B <sub>j</sub> |  |

| Н        | Η  | L  | L  | L              | 24              | 30    | $D_l + B_j + C_N$                                 | D <sub>I</sub> + B <sub>j</sub>        | D <sub>I</sub> + Q + 0001              | ′′                           | D <sub>1</sub> & Q              |  |

| Н        | I  | L  | L  | Н              | 25              | 31    | $A_I + Q + C_N$                                   | A <sub>1</sub> + Q                     | D <sub>I</sub> + Q + 0001              | "                            | Α <sub>Ι</sub> & Ω              |  |

| Н        | Н  | L  | Н  | L              | 26              | 32    | D <sub>I</sub> + Q + C <sub>N</sub>               | D <sub>I</sub> + Q                     | D <sub>I</sub> + Q + 0001              | "                            | D <sub>1</sub> & Q              |  |

| Н        | Н  | L  | Н  | Н              | 27              | 33    | $A_1 + \overline{B_j} + C_N$                      | A <sub>I</sub> - B <sub>j</sub> - 0001 | A <sub>I</sub> - B <sub>j</sub>        | Subtract                     | A <sub>I</sub> & B <sub>j</sub> |  |

| Н        | Н  | Н  | L  | L              | 28              | 34    | <u> </u>                                          | B <sub>j</sub> - A <sub>I</sub> - 0001 | B <sub>j</sub> - A <sub>l</sub>        | "                            | Bj & Al                         |  |

| Н        | Н  | Н  | L  | Н              | 29              | 35    | $D_1 + \overline{B_i} + C_N$                      | D <sub>I</sub> - B <sub>i</sub> - 0001 | D <sub>I</sub> - B <sub>i</sub>        | "                            | D <sub>I</sub> & B <sub>j</sub> |  |

| Н        | Н  | Н  | Н  | L              | 30              | 36    |                                                   | B <sub>j</sub> – D <sub>l</sub> – 0001 | B <sub>j</sub> - D <sub>l</sub>        | 11                           | B <sub>j</sub> & D <sub>l</sub> |  |

| Н        | Н  | Н  | Н  | Н              | 31              | 37    | $D_1 + \overline{\Omega} + C_N$                   | D <sub>I</sub> - Q - 0001              | D <sub>I</sub> - Q                     | "                            | D <sub>I</sub> & Q              |  |

# INSTRUCTION MODIFIERS IN THE 8 x 8 ROM - POSITIVE LOGIC (1 = H $\approx$ 3 V) INTERPRETATION

| Roi | Rom Word |    | Rom Word | Load Con                | Shift Control |       |       | Data Out Control |       |       |          |

|-----|----------|----|----------|-------------------------|---------------|-------|-------|------------------|-------|-------|----------|

| 1-  |          |    | Decimal  | Load Ram B <sub>i</sub> | Load Q        | Shift | Shift | Don't            | Α     | В     | ALU      |

| 12  | '1       | 10 | Decimal  | Load Raili B            | Load Q        | Left  | Right | Shift            | Latch | Latch | Output F |

| L   | L        | L  | 0        | X                       |               |       |       | Х                |       |       | X        |

| L   | L        | Н  | 1        | X                       |               |       |       | Χ                | X     |       |          |

| L   | Н        | L  | 2        | X                       |               |       |       | X                |       | X     |          |

| L   | Н        | Н  | 3        | X                       |               | Х     |       |                  |       |       | X        |

| Н   | L        | L  | 4        | X                       |               |       | Х     |                  |       |       | Х        |

| Н   | L        | Н  | 5        | X                       | X             | Х     |       |                  |       |       | X        |

| Н   | Н        | L  | 6        | X                       | X             |       | Х     |                  |       |       | X        |

| Н   | Н        | Н  | 7        |                         | X             |       |       | Х                |       |       | X        |

#### PIN CONFIGURATION

# INSTRUCTIONS IN THE 32 x 9 ROM — NEGATIVE LOGIC (1 = L $\approx$ 0 V) INTERPRETATION

| ROM WORD |    |    |   |    |         |       | ALU Instruction                                   | ALU OUTPUT                             |                                         | TYPICAL                      |                                 |

|----------|----|----|---|----|---------|-------|---------------------------------------------------|----------------------------------------|-----------------------------------------|------------------------------|---------------------------------|

| 17       | 16 | 15 |   | Γ. | Decimal | Octal | (See Pg. 8 for Symbology)                         | No Carry In<br>(C <sub>N</sub> = H)    | With Carry In<br>(C <sub>N</sub> = L)   | USES                         |                                 |

| L        | L  | L  | L | L  | 31      | 37    | LLLL + HHHH + C <sub>N</sub>                      | Force 1111                             | Force 0000                              | Initialization (Force 1's or | O's)                            |

| L        | L  | L  | L | Н  | 30      | 37    | OR A <sub>I</sub> & B <sub>j</sub>                | A <sub>I</sub> V B <sub>j</sub>        | A <sub>I</sub> V B <sub>i</sub>         | OR                           | A <sub>I</sub> & B <sub>i</sub> |

| L        | L  | L  | Н | L  | 29      | 35    | OR D <sub>1</sub> & B <sub>j</sub>                | D <sub>I</sub> V B <sub>j</sub>        | D <sub>I</sub> V B <sub>j</sub>         | "                            | D <sub>I</sub> & B <sub>i</sub> |

| L        | L  | L  | Н | Н  | 28      | 34    | AND A <sub>I</sub> & B <sub>j</sub>               | A <sub>I</sub> ∧ B <sub>j</sub>        | A <sub>I</sub> Λ B <sub>i</sub>         | AND                          | A <sub>I</sub> & B <sub>i</sub> |

| L        | L  | Н  | L | L  | 27      | 33    | AND D <sub>I</sub> & B <sub>j</sub>               | D <sub>I</sub> ∧ B <sub>j</sub>        | D <sub>I</sub> $\Lambda$ B <sub>i</sub> | "                            | D <sub>I</sub> & B <sub>i</sub> |

| L        | L  | Н  | L | H  | 26      | 32    | Exclusive OR A <sub>1</sub> & B <sub>1</sub>      | A <sub>I</sub> ¥ B <sub>j</sub>        | A <sub>I</sub> ₩ B <sub>i</sub>         | Exclusive Nor                | A <sub>I</sub> & B <sub>i</sub> |

| L        | L  | Н  | Н | L  | 25      | 31    | Exclusive OR D <sub>I</sub> & B <sub>j</sub>      | D <sub>I</sub> ¥ B <sub>j</sub>        | D <sub>I</sub> ¥ B <sub>i</sub>         | "                            | D <sub>I</sub> & B <sub>i</sub> |

| L        | L  | Н  | Η | Н  | 24      | 30    | A <sub>I</sub> + HHHH + C <sub>N</sub>            | Āī                                     | A <sub>1</sub> + 0001                   | 2's Complement Of            | Αl                              |

| L        | Н  | L  | L | L  | 23      | 27    | D <sub>I</sub> + HHHH + C <sub>N</sub>            | Di                                     | D <sub>I</sub> + 0001                   | "                            | DI                              |

| L        | Н  | L  | L | Н  | 22      | 26    | <del>В</del> <sub>ј</sub> + НННН + С <sub>N</sub> | Bj                                     | B <sub>i</sub> + 0001                   | "                            | Вј                              |

| L        | Н  | L  | Η | L  | 21      | 25    | <u> </u>                                          | ā                                      | Q + 0001                                | "                            | Q                               |

| L        | Н  | L  | Н | Н  | 20      | 24    | A <sub>I</sub> + LLLL + C <sub>N</sub>            | A <sub>I</sub> + 1111                  | Aı                                      | Invert                       | Aı                              |

| L        | Н  | Н  | L | L  | 19      | 23    | DI + LLLL + CN                                    | D <sub>I</sub> + 1111                  | DI                                      | "                            | DI                              |

| L        | Н  | Н  | L | Н  | 18      | 22    | B <sub>i</sub> + LLLL + C <sub>N</sub>            | B <sub>i</sub> + 1111                  | Bj                                      | **                           | Bj                              |

| L        | Н  | Н  | Н | L  | 17      | 21    | Q + LLLL + CN                                     | Q + 1111                               | <u> </u>                                | ",                           | Q                               |

| L        | Н  | Н  | Н | Н  | 16      | 20    | A <sub>I</sub> + LLLL + C <sub>N</sub>            | A <sub>I</sub> + 1111                  | Aı                                      | Decrement Or Transfer        | A <sub>I</sub>                  |

| Н        | L  | L  | L | L  | 15      | 17    | D <sub>I</sub> + LLLL + C <sub>N</sub>            | D <sub>I</sub> + 1111                  | DI                                      | "                            | DI                              |

| Н        | L  | L  | L | Н  | 14      | 16    | B <sub>j</sub> + LLLL + C <sub>N</sub>            | B <sub>i</sub> + 1111                  | B <sub>i</sub>                          | • "                          | Bj                              |

| Н        | L  | L  | Н | L  | 13      | 15    | Q + LLLL. + CN                                    | Q + 1111                               | Q                                       | ,,                           | Q                               |

| Н        | L  | Г  | Η | Н  | 12      | 14    | A <sub>I</sub> + HHHH + C <sub>N</sub>            | Aı                                     | A <sub>I</sub> + 0001                   | Transfer Or Increment        | Aı                              |

| Н        | Г  | Н  | L | L  | 11      | 13    | D <sub>I</sub> + HHHH + C <sub>N</sub>            | Di                                     | D <sub>1</sub> + 0001                   | "                            | DI                              |

| Н        | L  | Н  | L | Н  | 10      | 12    | В <sub>ј</sub> + НННН + С <sub>N</sub>            | Bj                                     | B <sub>i</sub> + 0001                   | ,,                           | Bj                              |

| H        | L  | Н  | Н | L  | 9       | 11    | Q + HHHH + C <sub>N</sub>                         | Q                                      | Q + 0001                                | 7                            | Q                               |

| Н        | L  | Н  | Н | Н  | 8       | 10    | $A_I + B_j + C_N$                                 | A <sub>I</sub> + B <sub>j</sub>        | A <sub>I</sub> + B <sub>j</sub> + 0001  | Add                          | A <sub>I</sub> & B <sub>j</sub> |

| Н        | Н  | L  | L | L  | 7       | 07    | $D_l + B_j + C_N$                                 | D <sub>I</sub> + B <sub>j</sub>        | D <sub>I</sub> + Q + 0001               | "                            | D <sub>I</sub> & Q              |

| Н        | Н  | L  | L | Н  | 6       | 06    | A <sub>1</sub> + Q + C <sub>N</sub>               | A <sub>1</sub> + Q                     | D <sub>I</sub> + Q + 0001               | "                            | A <sub>1</sub> & Q              |

| Н        | Н  | L  | Н | L  | 5       | 05    | D <sub>I</sub> + Q + C <sub>N</sub>               | D <sub>I</sub> + Q                     | D <sub>I</sub> + Q + 0001               | 11                           | D <sub>I</sub> & Q              |

| Н        | Н  | L  | Н | Н  | 4       | 04    | $A_I + B_j + C_N$                                 | A <sub>I</sub> - B <sub>j</sub> - 0001 | A <sub>I</sub> - B <sub>j</sub>         | Subtract                     | A <sub>I</sub> & B <sub>i</sub> |

| Н        | Н  | Н  | L | L  | 3       | 03    | $B_j + A_l + C_N$                                 | B <sub>j</sub> - A <sub>I</sub> - 0001 | B <sub>i</sub> - A <sub>I</sub>         | "                            | B <sub>i</sub> & A <sub>I</sub> |

| Н        | Н  | Н  | L | Н  | 2       | 02    | D <sub>I</sub> + B <sub>i</sub> + C <sub>N</sub>  | D <sub>I</sub> - B <sub>i</sub> - 0001 | D <sub>I</sub> - B <sub>i</sub>         | "                            | D <sub>I</sub> & B <sub>i</sub> |

| H        | H  | H  | Н | L  | 1       | 01    | ,                                                 | B <sub>j</sub> - D <sub>I</sub> - 0001 | B <sub>j</sub> - D <sub>l</sub>         | "                            | B <sub>j</sub> & D <sub>l</sub> |

| Н        | Н  | Н  | Н | Н  | 0       | 00    | $D_I + Q + C_N$                                   | D <sub>I</sub> - Q - 0001              | D <sub>I</sub> - Q                      | •                            | D <sub>I</sub> & Q              |

# INSTRUCTION MODIFIERS IN THE 8 x 8 ROM - NEGATIVE LOGIC (1 = L $\approx$ 0 V) INTERPRETATION

| Roi | Rom Word |    | Rom Word | Load Control |        | Shift Control |       |       | Data Out Control |       |          |

|-----|----------|----|----------|--------------|--------|---------------|-------|-------|------------------|-------|----------|

| 12  | 11       | 10 | Decimal  | Load Ram Bi  | Load Q | Shift         | Shift | Don't | Α                | В     | ALU      |

|     |          | .0 | 200      | Load Hall Dj | Load Q | Left          | Right | Shift | Latch            | Latch | Output F |

| L   | L        | L  | 7        | X            |        |               |       | X     |                  |       | X        |

| L   | L        | Н  | 6        | X            |        |               |       | ×     | X                |       |          |

| L   | Н        | L  | 5        | X            |        |               |       | ×     |                  | X     |          |

| L   | Н        | Н  | 4        | X            |        | Х             |       |       |                  |       | Х        |

| Н   | L        | L  | 3        | X            |        |               | Х     |       |                  |       | Х        |

| Н   | L        | Н  | 2        | X            | X      | Х             |       |       |                  |       | X        |

| Н   | Н        | L  | 1        | X            | X      |               | Х     |       |                  |       | X        |

| Н   | I        | I  | 0        |              | X      |               |       | Х     |                  |       | X        |

#### PIN CONFIGURATION

#### **APPLICATION TRICKS WITH SOME INSTRUCTIONS**

- 1)  $A_{\parallel} \wedge B_{\parallel}$  or  $A_{\parallel} \vee B_{\parallel}$  can be used as a no operation if  $A_{\parallel} = B_{\parallel}$  and only the RAM is loaded since we are loading a register with itself.

- 2)  $A_1 \forall B_J$  can be used to load LLLL if  $A_1 = B_J$  regardless of the state of  $C_N$ .

- 3)  $A_1 + B_2 + C_N$  gives  $A_1 + A_1 + C_N$  if  $A_1 = B_2$ , forming twice "A" or twice  $(A_1 + B_2) + C_N$  is shifted left with  $A_1 = B_2$ , we get a double left shift since adding a number to itself is a multiply by 2 which in binary is a shift left.

- 4) Q can be shifted and stored back in Q during any instruction involving HLH or HHL on I<sub>2</sub>, I<sub>1</sub>, I<sub>0</sub> permitting simultaneous RAM and Q shifting. Operations involving 3 registers (A, B, and Q) are also possible since we can perform A + B Q.

- 5)  $B_J + LLLL + C_N \longrightarrow B_J$  can be used as a NO OP if there is no carry

- 6)  $B_J + LLLL + C_N \longrightarrow B_J$ ,  $A_I \longrightarrow OUT$  $B_J + HHHH + C_N \longrightarrow B_J$ ,  $A_I \longrightarrow OUT$

Permits use of one of the B<sub>J</sub> for a program counter (P.C) while looking at one of the A<sub>I</sub> which might be an accumulator on the output pins. If there is a carry,  $B_O + OOOI \longrightarrow B_O$  (Increment P.C)

$$A_I \longrightarrow OUT (Old P.C \longrightarrow OUT)$$

Might be used to increment the program counter while having the old value of the program counter addressing memory (via the data out pins) in one microcontroller cycle.

#### CARRY GENERATE (G) AND CARRY PROPAGATE (P)

#### A) THEORY

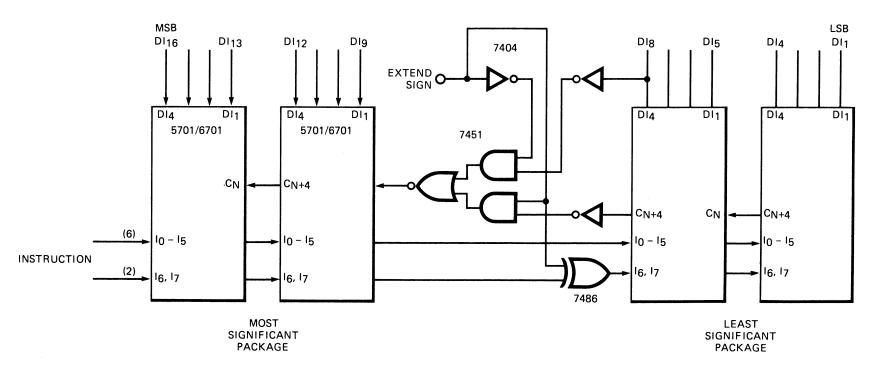

The G and P pins of the microcontroller are designed to be used with the TTL 54182/74182 look-ahead carry generator. The look-ahead techniques predict whether or not there will be a carry generated from the microcontroller and whether the input carry (C<sub>N</sub>) will be propagated through the microcontroller, based on the input operands rather than waiting for the carry to ripple through each internal stage of the microcontroller. The add times of larger word length machines are significantly faster with these techniques.

#### B) ACTIVE HIGH AND ACTIVE LOW LOGIC

G and P are sometimes called X and Y in active HIGH (Positive) logic terminology since the generate and propagate terminology are pertinent only to active LOW (Negative) logic. The microcontroller and look-ahead carry generator will produce the correct results in both active HIGH and active LOW logic. Figure 6 shows how to hook-up the look-ahead carry generator (74182 or 74S182).

#### C) LOGIC EQUATION

In logic symbology where J is a logic "AND" and + is a logic "OR" and where the subscript L means a low TTL logic level; P can be expressed as follows:

$$Y = P_L = (A'_{3H} + B'_{3H}) \cdot (A'_{2H} + B'_{2H}) \cdot (A'_{1H} + B'_{1H}) \cdot (A'_{0H} + B'_{0H})$$

This equation is interpreted to mean that propagate is a low level if  $A'_3$  or  $B'_3$  is high and  $A'_2$  or  $B'_2$  is high, and  $A'_1$  or  $B'_1$  is high, and  $A'_0$  or  $B'_0$  is high.  $A'_3$ ,  $A'_2$ ,  $A'_1$ ,  $A'_0$ , and  $B'_3$ ,  $B'_2$ ,  $B'_1$ ,  $B'_0$  refer to the four bit number applied at the input  $A'_1$  and  $B'_2$  of the microcontroller ALU.

In the same symbology:

$$X = G_{L} = (A'_{3H} \cdot B'_{3H}) + (A'_{3H} + B'_{3H}) \cdot (A'_{2H} \cdot B'_{2H}) + (A'_{3H} + B'_{3H}) \cdot (A'_{2H} + B'_{2H}) \cdot (A'_{3H} + B'_{3H}) \cdot (A'_{2H} + B'_{3H}) \cdot (A'_{3H} + B'_{3H}) \cdot (A'_{3H$$

#### RIPPLE CARRY (CN+4)

In systems not requiring the speed of look-ahead addition the 74S182 look-ahead carry generator can be eliminated and the ripple carry  $C_{N+4}$  can be used instead. Simply tie the ripple carry output  $C_{N+4}$  of the least significant microcontroller package to the carry input  $C_N$  of the more significant microcontroller package. Figure 7 shows some examples of ripple carry and combined ripple and look-ahead carry.

The ripple carry output will be a TTL high level when a carry out occurs in the active HIGH (Positive) logic convention. The ripple carry output will be a TTL low level when a carry out occurs in the active LOW (Negative) logic convention.

COMBINED TWO-LEVEL LOOK-AHEAD AND RIPPLE-CARRY

#### FIGURE 7

# WORST CASE MINIMUM CYCLE TIMES OVER THE V<sub>CC</sub> AND TEMPERATURE RANGE FOR CPU'S LARGER THAN 4 BITS

|                    | Minimum<br>Cycle<br>With | 6701                    |                       |                          | 5701  Minimum Cycle* With  Look Ahead |                       |  |

|--------------------|--------------------------|-------------------------|-----------------------|--------------------------|---------------------------------------|-----------------------|--|

| CPU<br>Word Length |                          | Minimum Cy<br>Look A    |                       | Minimum<br>Cycle<br>With |                                       |                       |  |