RANDY BIELEFELDT Field Sales Engineer

MOSTEK Corporation/1762 Technology Drive, Suite 126 San Jose, CA. 95110-1384/408-287-5138/TWX-910-338-2219

MDX-CPU3

DATA SHEET

PRELIMINARY

GARY KOTTERMAN

Fleid Applications Engineer

1762 Technology Dr./Sulte 128 San Jose, CA 95110

Telephone (408) 287-5080/TWX: 910-338-2219

## . 1: PEATURES

# PRELIMINARY

- [] Utilizes the powerful Z80A Microprocessor.

- [] A single 28 Pin socket which may be strapped to accept any of the following industry-standard memory devices.

| EPROM    |         | ROM     |           |

|----------|---------|---------|-----------|

| MK2716 ( | 2K × 8) | MK34000 | (2K x 8)  |

| 2732 (   | 4K x 8) |         |           |

| 2764 (   | 8K x 8) | MK37000 | (8K x 8)  |

|          |         | MK38000 | (32K × 8) |

- [] 64K x 8 of dynamic memory capacity.

- [] 2K to 32K of ROM memory capacity.

- [] Flexible memory decoding of ROM memory on any 2k boundary.

- [] Phantom ROM capability.

- [] Bidirectional address, data and control busses to permit external DNA.

- [] 8 bit output port with handshake for interfacing to a Centronics printer.

- [] Full handshake serial RS232 I/O Port.

- [] Software programable baud rate.

- [] Power on reset logic.

- [] STD-Z80 BUS compatible.

- [] 2 timer channel outputs.

- [] Fully buffered signals for system expandability.

- [] Bidirectional reset which allows operation with the MDX-PFD.

- [] Supports multiple memory banks for multiple operating systems.

- [] Supports MEMEX capability

PRELIMINARY

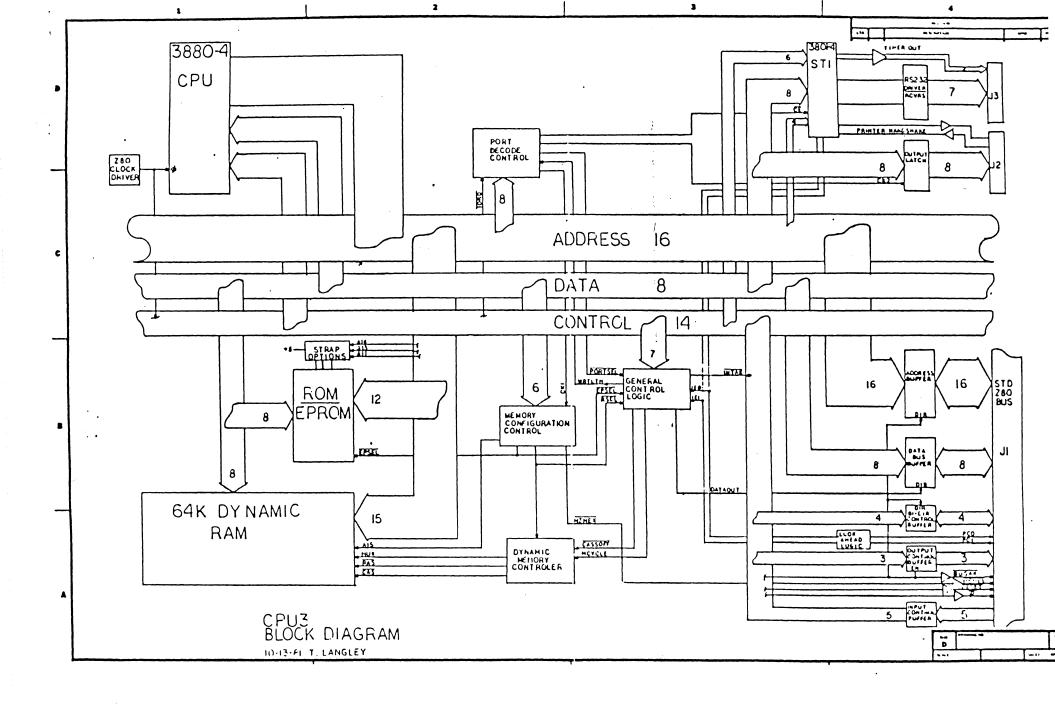

## 2. MDX-CPU3 DESCRIPTION

The MDX-CPU3 features a RS232 serial port, an 8 bit output with handshake for connection to a printer, 64K of dynamic Ram, and 2K to 32K of ROM/EPROM. The CPU3 supports a very flexible memory map configuration by the use of a memory configuration PROM (U24). This allows the user to map this ROM anywhere on 2K boundaries in the 64K memory map. This PROM also allows up to 16 different configurations selectable from software. If desired, the user may, by programming this PROM, be configured to support multiple pages of memory. Address, data and control busses have been made bidirectional to allow external masters to directly access CPU memory.

The 8 bit parallel output port with handshake lines have been configured to easily accommodate direct connection to a centronics type printer interface.

The RS232 serial port has been configured to accomodate full handshake cpapbilites.

## 3. I/O CAPACITY

The MDX-CPU3 utilizes 18 of the possible 256 port addresses leaving 238 port addresses avaliable to the user for expansion.

### 4. MEMORY REFRESH

The MDX-CPU3 generates all address and control signals necessary to refresh external dynamic RAM modules.

### 5. I/O ADDRESSING

The onboard ports are programmed to the following port addresses:

| Device                | Port Address (Hex) |

|-----------------------|--------------------|

|                       |                    |

| MK3801 STI            | B0 - BF            |

| PARALLEL OUTPUT LATCH | D0                 |

| MEMORY CONFIGURATION  | FF                 |

### 6. INTERUPTS

The MDX-CPU3 will process interupts in any of the three different Z80-CPU interrupt modes.

# 7. CONNECTORS AND HEADERS

# 7.1. BDS CONNECTOR

J1 SIGNAL DEFINITIONS

| BUS PIN                                                                                      | MNEMONIC                                                                                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 2                                                                                          | +5V<br>+5V                                                                                           | +5V DC LOGIC POWER<br>+5V DC LOGIC POWER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3<br>4                                                                                       | GND<br>GND                                                                                           | DIGITAL SYSTEM GROUND DIGITAL SYSTEM GROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5<br>6                                                                                       | -5V<br>-5V                                                                                           | Logic Bias Voltage (-5vdc) NOT USED<br>Logic Bias Voltage (-5vdc) NOT USED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7<br>8.<br>9<br>10<br>11<br>12<br>13<br>14                                                   | D3<br>D7<br>D2<br>D6<br>D1<br>D5<br>D0                                                               | The data bus is an 8-bit, bidirectional, 3-state bus. (Bidirectional means signals may flow either into or out of any card on the bus.) Direction of data is normally controlled by the processor card with the control bus. The data direction is normally affected by such signals as (RD), (WR), and interrupt acknowledge (INTAK). The data bus uses high-active logic. All cards are required to release the bus to high-impedance state when not in use. The processor card releases the data bus in response to bus request (BUSRQ) input from an alternate system controller as in DMA transfers.                                                                                                                                                                                                                                                              |

| 15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30 | A7<br>A15<br>A6<br>A14<br>A5<br>A13<br>- A4<br>A12<br>A3<br>A11<br>A2<br>A10<br>A1<br>A9<br>A0<br>A8 | The address bus is a 16-bit, 3-state, high-level active bus. Normally, the address originates at the processor card. The card releases the address bus in response to a BUSRQ input from and alternate controller. The address bus provides 16 address lines for decoding by either memory or I/O. Memory request (MEMRQ) and I/O request (IORQ) control lines distinguish between the two operations. The 16-bit Z8O address is applied directly to the 16 STD BUS address lines. The address bus provides a 16-bit memory address, an 8-bit I/O address or a 7-bit refresh address. I/O addressing uses the lower 8 address bits of the 16-bit address bus, and occurs during I/O instruction execution. Refresh addressing for dynamic RAMs uses the lower 7 address bus lines. The refresh address occurs during the T3 and T4 time states of an M1 machine cycle. |

| 31                                                                                           | /WR                                                                                                  | This signal indicates that the BUS holds valid data to be written in the addressed memory or output device. WR is the clock pulse, which writes data to memory or output port latches. The signal originates from the processor, which also provides the output data on the BUS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

32 This signal indicates that the CPU wants memory or /RD an I/O device to place data on the BUS. RD is the clock pulse, which causes memory or I/O device to gate data outward onto the data bus. The signal originates from the processor, which is the receiver of the data on the BUS. 33 /IORQ This signal indicates that the lower half of the address bus holds a valid I/O address for an I/O read or write operation. The IORQ signal is also generated with an Ml signal when an interrupt is being acknowledged to indicate that an interrupt response vector can be placed on the data bus. Interrupt Acknowledge operations occur during Ml time, while I/O operations never occur during Nl time. 34 /MEMRQ This signal indicates that the address bus holds a valid address for a memory read or memory write operation. 35 IOEXP Not supported on this card. 36 MEMEX This signal indicates to external memory cards that secondary memory should be allowed access by the CPU. 37 /REFRESH This signal indicates that the lower seven (7) bits of the address bus contain a refresh address for dynamic memories and the MEMRQ signal should be used to perform a refresh cycle for all dynamic RAMs in the system. During the refresh cycle an eighth bit which is the R registers most significant bit is program-settable in the high or low state. 38 Not supported on this card. /MCSYNC 39 /STATUS1 This signal indicates that the current machine cycle is in the op code fetch cycle of an instruction or is performing an interrupt acknowledge cycle (Ml is ANDed with IORQ internally to produce INTAK). Note that the Z80 has both one and two byte opcodes (2byte opcodes are identified by a first byte equal to CB, DD, ED, or FD hexadecimal). Accordingly, the processor asserts Ml in each opcode byte, or twice per instruction cycle for these instructions. 40 /STATUSO Not supported on this card. 41 /BUSAK This signal is used to indicate to the requesting device that the CPU address bus, data bus, and control bus signals have been set to their high impedance state and the external device can now control the bus.

| 42         | /BUSRQ    | This signal is used to request the CPU address bus, data bus, and control signal bus to go to a high impedance state so that other devices can control those buses. When BUSRQ is asserted the CPU will set these buses to a high impedance state as soon as the current CPU machine cycle is terminated and the BUSAK signal will be asserted.                                                                                                                                                                           |

|------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43         | /INTAK    | This signal is used to indicate that an interrupt acknowledge cycle is in progress, and the interrupting device should place its response vector on the data bus. The INTAK signal is equivalent to an IORQ during an Ml cycle.                                                                                                                                                                                                                                                                                           |

|            | /INTRQ    | This signal is generated by an I/O device. A request will be honored at the end of the current instruction if the internal software controlled interrupt enable flip flop (IFF) is enabled and if the BUSRQ signal is not active. When the CPU accepts the interrupt, an interrupt acknowledge signal INTAK (IORQ during an Ml) is sent out at the beginning of the next instructions.                                                                                                                                    |

| <b>4</b> 5 | /WAITRQ   | This input signal to the processor indicates that the addressed memory or I/O device is not ready for a data transfer and therefore the CPU should maintain a valid address for extra cycles as long as WAITRQ remains valid. This signal allows memory or I/O devices of any speed to be synchronized to the CPU. Use of this signal postpones refresh as long as it is held active.                                                                                                                                     |

| 46         | /NMIRQ    | This signal is a processor-card interrupt input of the highest priority. The NMIRQ automatically forces the CPU to restart to location 0066h. The program counter is automatically saved in the external stack so that the user can return to the program that was interrupted. Note that continuous WAIT cycles can prevent the current instruction from ending, and that a /BUSRQ will override a /NMIRQ.                                                                                                               |

| 47         | /SYSRESET | This signal is an output from the system reset circuit, which is triggered by power-on detection, or by the push-button reset. The system reset bus line should be applied to all bus cards that have latch circuits requiring initialization. A system reset will force the CPU program counter to zero, disable interrupts, set the I register to 00h, set the r register to 00h, and set Interrupt Mode 0. Mostek MD CPU boards also support this signal in an input mode for use with a power fail detect controller. |

48

/PBRESET This signal is an input line to the system reset

| circuit which will generate a debounced system reset. This input will support 15 74LS loads or a push-button switch input. |

|----------------------------------------------------------------------------------------------------------------------------|

| This signal is a buffered, processor clock signal                                                                          |

| 49 | /CLOCK  | This signal is a buffered, processor clock signal, for use in system synchronization or as a general clock source.                                                                                                                                                         |

|----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50 | /CNTRL  | Not supported on this card.                                                                                                                                                                                                                                                |

| 51 | PCO     | This signal is sent to the PCI input of the next<br>lower card in priority. A card that needs priority<br>should hold PCO low. A high level on this pin<br>indicates that no other devices of higher priority<br>are being serviced by a CPU interrupt service<br>routine. |

|    | PCI     | This signal is provided directly from the PCO of the next higher card in priority. A card that needs priority should hold PCO low. A high level on this pin indicate that no other devices of higher priority are being serviced by a CPU interrupt service routine.       |

| 53 | AUX GND | Auxiliary Power Return Bus (not used)                                                                                                                                                                                                                                      |

| 54 | AUX GND | Auxiliary Power Return Bus (not used)                                                                                                                                                                                                                                      |

| 55 | +12V    | Positive DC System Supply Power (+12vdc)                                                                                                                                                                                                                                   |

## 7.2. PRINTER CONNECTOR

-12V

56

J2 The printer port data and control signals are brought out to a 26 pin connector as shown:

Negative DC System Supply Power (-12vdc)

| SIGNAL NAME | PIN | J2<br>++                  | PIN         | SIGNAL NAME |

|-------------|-----|---------------------------|-------------|-------------|

| /STB        | 1   | ix xi                     | 14          | GND         |

| Dl          | 2   | ix xi                     | 15          | GND         |

| D2          | 3   | X XI                      | 16          | NC          |

| <b>D</b> 3  | 4   | X X                       | 17          | NC          |

| D4          | 5   | [X X]                     | 18          | NC          |

| D5          | 6   | IX XI                     | 19          | NC          |

| D6          | 7   | [X X]                     | <b>2</b> 0  | NC          |

| <b>D7</b>   | 8   | X X                       | 21          | NC          |

| <b>D</b> 8  | 9   | X X                       | 22          | NC          |

| NC          | 10  | $[X \ X]$                 | 23          | NC          |

| BUSY        | 11  | $ \mathbf{x} \mathbf{x} $ | 24          | NC          |

| PE          | 12  | [X X]                     | . 25        | NC          |

| NC          | 13  | X X                       | <b>26</b> . | NC          |

|             |     | 4                         |             |             |

## 7.3. SERIAL CONNECTOR

J3 The serial communication signals and handshake to perform an RS232 type interface are buffered and brought out to a 26 pin connector as shown:

| SIGNAL NAME | PIN | <b>J</b> 3                | PIN        | SIGNAL NAME |

|-------------|-----|---------------------------|------------|-------------|

|             |     | ++                        |            |             |

| GND         | 1   | IX XI                     | 14         | NC          |

| RX          | 2   | $ \mathbf{x} \mathbf{x} $ | 15         | NC          |

| TX          | 3   | [X X]                     | 16         | NC          |

| RTS         | · 4 | IX XI                     | 17         | NC          |

| CTS         | 5   | $ \mathbf{x} \mathbf{x} $ | 18         | TAO         |

| DSR         | 6   | $ \mathbf{x} \mathbf{x} $ | 19         | NC          |

| GND         | 7   | $ \mathbf{x} \mathbf{x} $ | 20         | DTR         |

| RSLD        | 8   | [X X]                     | 21         | NC          |

| NC          | 9   | IX XI                     | 22         | NC          |

| NC          | 10  | [X X]                     | 23         | NC          |

| TCO         | 11  | X X                       | 24         | NC          |

| NC          | 12  | $ \mathbf{x} \mathbf{x} $ | <b>2</b> 5 | NC          |

| NC          | 13  | $ \mathbf{x} \mathbf{x} $ | <b>2</b> 6 | ' NC        |

|             |     | 4                         |            |             |

Note aslo that the timer outputs are buffered and brought out this connector on pins 18 and 11.

### 7.4. ROH/EPROM STRAPPING

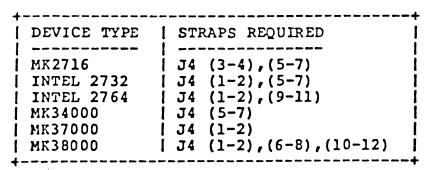

J4 This header allows the ROM/EPROM socket U22 to be configured to accept various type devices. The following table shows the strapping needed for each device.

| <b>J4</b>  |        |    |    |    |    |     |     |    |

|------------|--------|----|----|----|----|-----|-----|----|

|            |        | 1  | +  | +  | 2  |     |     |    |

| U22        | pin 23 |    | 10 | Q١ |    | All |     |    |

|            | •      |    | 10 | 01 |    | +5V | CC  |    |

|            | +5Vcc  |    | 10 | 01 |    | Al3 |     |    |

| <b>U22</b> | pin 26 |    | 10 | 01 |    | U22 | pin | 26 |

|            | +5Vcc  |    | 10 | 01 |    | Al4 |     |    |

| <b>U22</b> | pin 1  |    | 10 | 01 |    | U22 | pin | 1  |

|            | _      | 11 | +  |    | 12 |     | -   |    |

Fig. 7-1: Memory strapping

## 7.5. TEST CONNECTOR

**J**5 This header is used for testing purposes only and is strapped at the factory. DO NOT REMOVE

#### 8. ELECTRICAL SPECIFICATINS

STD BUS COMPATIBLE

SYSTEM INTERUPT UNITS: 1 SIU

SYSTEM CLOCK: 3.6864Mhz ±0.05%

OPERATING TEMPERATURE: OoC to 60oC

POWER SUPPLY REQUIREMENTS +5V ±5% @ 2.3A max +12V ±5% @ 25ma max -12V ±5% @ -23ma max

## 9. SOFTWARE PROGRAMING GUIDELINES

The CPU3 can support a phantom ROM type of operation where the ROM has just enough code to bring a larger operating system into RAM, then by switching to another memory map, dynamically disables the ROM and begins operation in a purely RAM configuration. A very simple method to do this is to have memory map 0 in the configuration PROM which will allow the Prom to appear at both 0000H and E000H addresses. Then the following procedure is followed:

- Perform a jump to Bootstrap at E003H. This sets the CPU program counter to point to the second image area of the RON.

- B. Perform a self copy of the ROM code into the RAM at the same address range as the ROM.

- Switch maps by outputling a mew map number to the Nemory C. Configuration port.

- D. Execution of the program will continue at the next instruction now in RAM.

An example of the programing required to accomplish this procedure is shown below:

```

3 *

PHANTON BOOT

BOOTSP

EQU

$

3

JP

BOOTSO

SET ADDRESS IN CPU

BOOTSO:

LD

HL, BOOTSP

GET START OF BOOTSTRAP PGM

LD

D, H

MOVE TO DESTINATION

LD

E,L

: ADDRESS

LD

BC, BOOTEND-BOOTSP GET # OF BYTES

LDIR

:TRANSFER DATA

BOOTS1:

LD

A, MAP1

GET MAPI BYTE

OUT

(MAPPRT), A

OUTPUT TO MAP PORT

```

At this point the program will begin execution out of RAM.

## 10. PROM PROGRAMING GUIDELINES

The following is an example of how to define the code necessary to custom program a memory map into the Memory Configuration PROM.

## STEP 1.

Define the areas where RAM, ROM, or Blank areas should be located.

## STEP 2.

Determine which of the Maps is desired to be used. The following chart shows the boundaries of each Map.

| MAP NO. | WORD NO. | MAP NO. | WORD NO. |

|---------|----------|---------|----------|

|         |          |         |          |

| 0       | 000-01F  | 8       | 100-11F  |

| 1       | 020-03F  | 9       | 120-13F  |

| 2       | 040-05F  | 10      | 140-15F  |

| 3       | 060-07F  | 11      | 160-17F  |

| 4       | 080-09F  | 12      | 180-19F  |

| 5       | 0A0-0BF  | 13      | 1A0-1BF  |

| 6       | 0C0-0DF  | 14      | 1C0-1DF  |

| 7       | 0E0-0FF  | 15      | 1E0-1FF  |

#### STEP 3.

Using the following bit definition chart select the proper bits for each word necessary to support the desired Map.

OUTPUT BIT DEPINITIONS . ACTIVE STATE Ol - SELECT EPROM LOW

O2 - A15 ADDRESS LINE OUTPUT SEE A15 ADDRESS CHART O3 - SELECT RAM O4 - MEMORY EXPAND OUTPUT LOW

LOW

SELECT EPRON This bit generates the signal which enables the ROM/EPROM for reading.

- Al5 ADDRESS LINE OUTPUT This bit generates the 2. uppermost address line to the onboard RAM memory. This allows the interchanging of the upper and lower 32K halves of RAM. Normally this line is programed to give a true image of Al5.

- 3. SELECT RAM This bit generates the signal which enables the RAM.

- MEMORY EXPAND OUTPUT This bit generates a signal which is defined by the STD-Bus specification for the MEMEX signal. In most single board configurations this bit is programmed high.

#### Al5 ADDRESS CHART

| WORD NO. | Al5 STATE | WORD NO. | Al5 STATEO |

|----------|-----------|----------|------------|

|          |           |          |            |

| XX 0     | 0         | XX8      | 1          |

| XXl      | 0         | XX9      | 1          |

| XX2      | 0         | XXA      | 1          |

| XX3      | 0 .       | XXB      | 1          |

| XX4      | 0         | XXC      | 1          |

| XX5      | 0         | XXD      | 1          |

| XX6      | 0         | XXE .    | 1          |

| XX7      | 0         | XXF      | 1          |

| This | is | an | example | of the | above | procedure: |

|------|----|----|---------|--------|-------|------------|

|------|----|----|---------|--------|-------|------------|

| MEMORY<br>ADDRESS | MAP NO. | PROM LISTING WORD NUMBER | BIT NO.<br>1 2 3 4                                     | HEX VAL    |

|-------------------|---------|--------------------------|--------------------------------------------------------|------------|

| FPFF              | RAM     |                          |                                                        |            |

|                   |         | 00                       | 0 0 1 1                                                | (C)        |

| <b>F</b> 000      | ROM     | 01                       | 1001                                                   | (9)        |

|                   |         | 02                       | 1 0 0 1                                                | (9)        |

| <b>E</b> 000      | RAM I   | 1 03<br>1 04             | 1 0 0 1 1 0 0 1                                        | (9)<br>(9) |

| D000              |         | 1 05                     | 1001                                                   | (9)        |

| D000              | 1 1     | 1 06                     | 1 0 0 1                                                | (9)        |

| C000              | i i     | 07                       | 1 0 0 1                                                | (9)        |

| Cooo              | i i     | 08                       | 1 1 0 1                                                | (B)        |

| B000              | i i     | 09                       | 1 1 0 1                                                | (B)        |

|                   | i i     | AO I                     | 1 1 0 1                                                | (B)        |

| A000              | 1 !     | 0 B                      | 1 1 0 1                                                | (B)        |

|                   | [ [     | I OC                     | 1.1 0 1                                                | (B)        |

| 9000              | ] !     | ! 0D                     | 1 1 0 1                                                | (B)        |

| 0000              |         | 0E<br>  0F               | $\begin{smallmatrix}0&1&0&1\\1&1&0&1\end{smallmatrix}$ | (A)<br>(B) |

| 8000              | RAM     | 1 10                     | 0 0 1 1                                                | (C)        |

| 7000              |         | 1 11                     | 1 0 0 1                                                | (9)        |

| 7000              | i       | 1 12                     | 1 0 0 1                                                | (9)        |

| 6000              | i i     | 1 13                     | 1 0 0 1                                                | (9)        |

|                   | i i     | 1 14                     | 1 0 0 1                                                | (9)        |

| 5000              | 1       | 1 15                     | 1 0 0 1                                                | (9)        |

| •                 | į į     | 16                       | 1001                                                   | (9)        |

| 4000              | !!!     | 1 17                     | 1 0 0 1 1 1 0 1                                        | (9)        |

| 2000              | !!!     | 1 18                     | 1 1 0 1 1 1 0 1                                        | (B)<br>(B) |

| 3000              |         | 19<br>  1A               | 1 1 0 1                                                | (B)        |

| 2000              | RAM     | I IB                     | 1 1 0 1                                                | (B)        |

| 2000              | I WHIT  | 1 1C                     | 1 1 0 1                                                | (B)        |

| 1000              | i       | i iD                     | 1 1 0 1                                                | (B)        |

| 2000              |         | 1E                       | 0 1 0 1                                                | (A)        |

| 0000              | ROH     | i 1F                     | 1101                                                   | (B)        |

## 11. MECHANICAL SPECIFICATINS

## CARD DIMENSIONS

4.50 in. (11.43 cm.) wide by 6.50 in. (16.51 cm.) long

0.675 in. (1.71 cm.) maximum profile thickness 0.062 in. (0.16 cm.) printed circuit board thickness

## STD BUS EDGE CONNECTOR

56 Pin Dual Readout; 0.125 In. centers

## · 12. ORDERING INFORMATION

**DESIGNATOR** MDX-CPU3

DESCRIPTION

PART NO. MK77857

3.6864Mhz CPU3 module with Operations Manual (less EPROM and mating connectors)

## 13. WARRANTY INFORMATION

To be supplied later.

APPLICATION BRIEF

THE

MOSTEK MDX-CPU3

SINGLE BOARD MICROCOMPUTER

...a power-packed, compact, cost-effective single board microcomputer...

THE

MOSTEK MDX-CPU3

SINGLE BOARD MICROCOMPUTER...

the STD-Z80 BUS compatible CPU (Central Processor Unit)

- [] is a complete Z80 microprocessor system on one  $4.5 \times 6.5$  inch circuit board.

- [] has 64K bytes of dynamic memory on-board. (no other memory cards are required, but can be used if necessary.)

- [] has a RS232C serial I/O port (with modem control) for two-way flow of data between the computer and a user terminal or other computer equipment.

- [] has an 8-Bit parallel printer port that is Centronics interface compatible.

- [] has a red light emitting diode (LED) that is user program-mable. (could be used as a diagnostic test indicator, CPU run light etc.)

- [] provides phantom capability for the single 28-pin socket for a total RAM operating mode.

#### HIGHLIGHTS

- [] Allows the user to build a more compact system. (single board system)

- [] Permits the user to use existing 8080A software without modifications. (The Z80 processor includes all of the 8080A instructions as a subset; adds Bit, Relative, and Indexed addressing modes; powerful data block search and move instructions; and a duplicate set of internal registers for quick execution time in many applications.)

- [] Permits easy maintanance...only one board to replace.

- [] Eliminates the need for large inventory requirements.

- [] Has ability to perform a user defined diagnostics of the system and indicate the results by the onboard red LED.

## FEATURES

- [] The MDX-CPU3 is STD BUS compatible which will permit it to work with other STD boards if so required.

- [] The MDX-CPU3 board has a single 28-Pin socket which may be strapped to accept any of the following industry-standard memory devices.

|   |        | EPRO | 1 |    |   |         | ROM  |   |    |   |

|---|--------|------|---|----|---|---------|------|---|----|---|

| 1 | MK2716 | (2K  | x | 8) | 1 | MK34000 | (2K  | x | 8) | 1 |

| 1 | 2732   | (4K  | X | 8) | 1 |         |      |   |    | 1 |

| 1 | 2764   | (8K  | X | 8) | ١ | MK37000 | (8K  | X | 8) | 1 |

| 1 |        |      |   |    | 1 | MK38000 | (32K | x | 8) | I |

|   |        |      |   |    | : |         |      |   |    |   |

- [] Phantom ROM capability is provided and desired if the user wishes to maximize the transient program RAM area of memory.

- [] Bidirectional address, data, and control busses to permit external Direct Memory Access (DMA).

- [] Software programmable baud rate. (minimal configuring straps required during manufacturing phase of your product)

- [] Printer port pinout is configured for direct connection to Centronics interface using mass terminated connectors and flat ribbon cabling. (no scrambling or use of discrete wire is required.)

- [] Supports multiple memory banks for multiple operating systems.

- [] User programmable LED indicator to signal faulty or other condition.

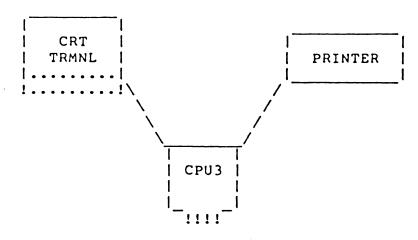

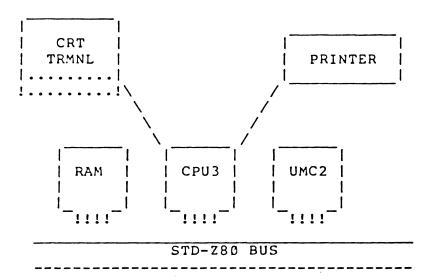

Figure 1. Constitution of the

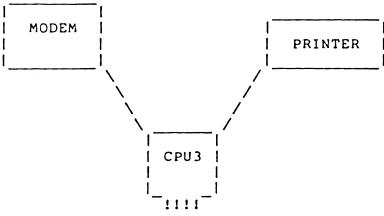

## MOSTEK MDX-CPU3 CONFIGURATIONS

## Single Board System

## Multi-board System

| MODEM | | \_\_\_\_\_|

Remote Stand Alone System

#### APPLICATIONS

The MDX-CPU3 board is a versatile single board microcomputer system. Its use spans a wide range of applications. An attempt is made to catagorize its uses below:

-Manufacturing

-Business Data Processing

-Product Development

Within these broad catagories, the MDX-CPU3 can be used specifically in the following applications.

## Manufacturing

- \* Test Equipment

- \* Process Control

- \* Instrumentation

- \* Data Logging

- \* Quality Control

- \* Process Monitoring

- \* Remote Machine Control

## Business Data Processing

- \* Word Processing

- \* Report Generation

- \* Executive Work Stations

- \* Small Business Accounting

- \* Inventory Control

- \* Point of Sale Processing

- \* Hotel Phone Call Accounting

- \* Communication Control

## Product Development

- \* Software Development

- \* Software Evaluation

- \* PC Design Support

- \* Microcomputer Board Development

- \* Target System Emulation

Part months Est

## TECHNICAL INFORMATION

I/O CAPACITY

The MDX-CPU3 utilizes 18 of the possible 256 port addresses available to the user for expansion.

#### MEMORY REFRESH

The MDX-CPU3 generates all address and control signals necessary to refresh external dynamic RAM modules.

#### I/O ADDRESSING

The on-board ports are programmed to the following addresses:

| Device                | Port | Нех | Address |

|-----------------------|------|-----|---------|

| MK3801 STI            | B0 - | BF  |         |

| Parallel Output Latch | DØ   |     |         |

| Memory Configuration  | FF   |     |         |

#### INTERRUPTS

The MDX-CPU3 will process interrupts in any of the three different Z80 Modes.

### CONNECTORS & HEADERS

## J1 STD BUS CONNECTOR

### J2 PARALLEL PORT CONNECTOR

The printer port data and control signals are brought out to a 26-Pin connector as shown below.

| /STB 1                                                                                                                                                                                             | SIGNAL NAME | PIN | <u>J2</u> | PIN | SIGNAL NAME |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|-----------|-----|-------------|

| D2 3   0 0   16 NC D3 4   0 0   17 NC D4 5   0 0   18 NC D5 6   0 0   19 NC D6 7   0 0   20 NC D7 8   0 0   21 NC D8 9   0 0   22 NC NC 10   0 0   23 NC BUSY 11   0 0   24 NC PE 12   0 0   25 NC | /STB        | 1   | 1001      | 14  | GND         |

| D3 4   0 0   17 NC D4 5   0 0   18 NC D5 6   0 0   19 NC D6 7   0 0   20 NC D7 8   0 0   21 NC D8 9   0 0   22 NC NC 10   0 0   23 NC BUSY 11   0 0   24 NC PE 12   0 0   25 NC                    | Dl          | 2   | 10 01     | 15  | GND         |

| D4 5   0 0   18 NC D5 6   0 0   19 NC D6 7   0 0   20 NC D7 8   0 0   21 NC D8 9   0 0   22 NC NC 10   0 0   23 NC BUSY 11   0 0   24 NC PE 12   0 0   25 NC                                       | D2          | 3   | 10 01     | 16  | NC          |

| D5 6   0 0   19 NC   D6 7   0 0   20 NC   D7 8   0 0   21 NC   D8 9   0 0   22 NC   NC 10   0 0   23 NC   BUSY 11   0 0   24 NC   PE 12   0 0   25 NC                                              | D3          | 4   | 10 01     | 17  | NC          |

| D6 7   0 0   20 NC D7 8   0 0   21 NC D8 9   0 0   22 NC NC 10   0 0   23 NC BUSY 11   0 0   24 NC PE 12   0 0   25 NC                                                                             | D4          | 5   | 10 01     | 18  | NC          |

| D7 8   0 0   21 NC D8 9   0 0   22 NC NC 10   0 0   23 NC BUSY 11   0 0   24 NC PE 12   0 0   25 NC                                                                                                | D5          | 6   | 10 01     | 19  | NC          |

| D8 9   0 0   22 NC NC NC 10   0 0   23 NC NC NC PE 12   0 0   24 NC                                                                                            | D6          | 7   | 10 01     | 20  | NC          |

| NC 10   0 0   23 NC BUSY 11   0 0   24 NC PE 12   0 0   25 NC                                                                                                                                      | D7          | 8   | 10 01     | 21  | NC          |

| BUSY 11   0 0   24 NC PE 12   0 0   25 NC                                                                                                                                                          | D8          | 9   | 10 01     | 22  | NC          |

| PE 12  0 0   25 NC                                                                                                                                                                                 | NC          | 10  | 10 01     | 23  | NC          |

|                                                                                                                                                                                                    | BUSY        | 11  | 10 01     | 24  | NC          |

| NC 13 lool 26 NC                                                                                                                                                                                   | PE          | 12  | 10 01     | 25  | NC          |

|                                                                                                                                                                                                    | NC          | 13  | 10 01     | 26  | NC          |

## J3 SERIAL PORT CONNECTOR

The serial communication signals and control lines to perform an RS232C type interface are buffered and brought out to a 26 pin connector as shown. Note that timer outputs are brought out as well.

| SIGNAL NA | ME PIN | <u>J3</u> | PIN | SIGNAL NAME |

|-----------|--------|-----------|-----|-------------|

|           | GND 1  | 10 01     | 14  | NC          |

| RX        | 2      | 10 01     | 15  | NC          |

| TX        | 3      | 10 01     | 16  | NC          |

| RTS       | 4      | 10 01     | 17  | NC          |

| CTS       | 5      | 10 01     | 18  | TAO         |

| DSR       | 6      | 10 01     | 19  | NC          |

| GND       | 7      | 10 01     | 20  | DTR         |

| RSLD      | 8      | 10 01     | 21  | NC          |

| NC        | 9      | 10 01     | 22  | NC          |

| NC        | 1 Ø    | 10 01     | 23  | NC          |

| TCØ       | 11     | 10 01     | 24  | NC          |

| NC        | 12     | 10 01     | 25  | NC          |

| NC        | 13     | 10 01     | 26  | NC          |

#### ROM/EPROM STRAPPING

The J4 header allows the ROM/EPROM socket U22 to be configured to accept various type devices. See table below.

| :  | =========   |                                         |  |

|----|-------------|-----------------------------------------|--|

| ١  | DEVICE TYPE | J4 STRAPS REQUIRED                      |  |

| 1: | ==========  | ======================================= |  |

| İ  | MK2716      | 3-4, 5-7                                |  |

| 1  | INTEL 2732  | 1-2, 5-7                                |  |

| 1  | INTEL 2764  | 1-2, 9-11                               |  |

| ١  | MK34000     | 5-7                                     |  |

| 1  | MK37000     | 1-2                                     |  |

| 1  | MK38000     | 1-2, 6-8, 10-12                         |  |

| :  |             |                                         |  |

#### TEST CONNECTOR

The J5 connector is used for testing purposes only and is strapped at the factory. Do not remove this strap.

#### ELECTRICAL SPECIFICATIONS

STD BUS COMPATIBLE

SYSTEM INTERRUPT UNITS: 1 SIU

SYSTEM CLOCK: 3.6864 MHz + 0.05 %

OPERATING TEMPERATURE: 0°C to 50°C

POWER SUPPLY REQUIREMENTS: + 5 VDC +5 0 2.3A max +12 VDC +5 0 25ma max -12 VDC +5 0 23ma max

Free Land Control

#### MECHANICAL SPECIFICATIONS

#### CARD DIMENSIONS:

4.50 in. (11.43 cm) wide by 6.50 in. (16.51 cm) long.

0.675 in. (1.71 cm) maximum profile thickness.

0.052 in. (0.16 cm) printed circuit board thickness.

#### STD BUS CARD EDGE CONNECTOR J1:

56 Pin Dual Readout; 0.125 in. centers

## MATING CONNECTORS: (User provided)

for J1: VIKING 3VH28/1CE5 (printed circuit type)

VIKING 3VH28/1CND5 (wire-wrap type) VIKING 3VH28/1CN5 (solder lug type)

for J2 & J3:

Mass terminated:

T & B Ansley #609-2601M

Winchester Electronics #51-1126-01

3M #3399-6926

Discrete wires:

Winchester Electronics

Housing: #PGB-13-A

Contacts: Crimp #100-72020S (20-24 AWG)

#100-72025S (25-30 AWG)

PART NO.

MK77857

#### ORDERING INFORMATION:

. .

DESIGNATOR DESCRIPTION

MDX-CPU3 3.6854 MHz CPU3 module with

Data Sheet (less EPROM and

mating connectors)