MD SERIES™ MICROCOMPUTER MODULES

## **Operations Manual**

# EPROM/UART MODULE MDX-EPROM/UART

MDX-EPROM/UART

OPERATION MANUAL

|  |  | , |  |

|--|--|---|--|

|  |  |   |  |

|  |  |   |  |

## TABLE OF CONTENTS

| SECTION | PARAGRAPH |                                     | PAGE   |

|---------|-----------|-------------------------------------|--------|

| NUMBER  | NUMBER    | TITLE                               | NUMBER |

| 1       |           | GENERAL INFORMATION                 |        |

|         | 1.1       | INTRODUCTION                        | 1-1    |

|         | 1.2       | GENERAL DESCRIPTION                 | 1-1    |

|         | 1.3       | STD-Z80 BUS PIN-OUT AND DESCRIPTION | 1-4    |

| 2       |           | FUNCTIONAL DESCRIPTION              |        |

|         | 2.1       | INTRODUCTION                        | 2-1    |

|         | 2.2       | MEMORY ARRAY                        | 2-1    |

|         | 2.3       | MEMORY SELECTION LOGIC              | 2-1    |

|         | 2.4       | PORT SELECTION LOGIC                | 2-1    |

|         | 2.5       | UART                                | 2-1    |

|         | 2.6       | RS-232 and 20mA BUFFERS             | 2–1    |

| 3       |           | UTILIZATION                         |        |

|         | 3.1       | INTRODUCTION                        | 3-1    |

|         | 3.2       | MEMORY INTERFACE                    | 3-1    |

|         | 3.3       | EPROM DECODING JUMPERS              | 3-1    |

|         | 3.4       | SERIAL INTERFACE                    | 3-1    |

|         | 3.5       | I/O PORT DECODING JUMPERS           | 3-1    |

|         | 3.6       | BAUD RATE SELECTION                 | 3-3    |

|         | 3.7       | PROGRAMMING THE UART                | 3-3    |

|         | 3.8       | SERIAL I/O CONNECTOR AND CABLE      | 3-3    |

|         | 3.9       | RS-232 INTERFACE                    | 3-3    |

|         | 3.10      | TELETYPE AND READER STEP INTERFACE  | 3-4    |

## TABLE OF CONTENTS (contd.)

| SECTION  | PARAGRAPH |                                       | PAGE   |

|----------|-----------|---------------------------------------|--------|

| NUMBER   | NUMBER    | TITLE                                 | NUMBER |

| APPENDIX | A         | SPECIFICATIONS                        |        |

|          | A.1       | ELECTRICAL SPECIFICATIONS             | A-1    |

|          | A.2       | MECHANICAL SPECIFICATIONS             | A-2    |

|          | A.3       | STD-Z80 ELECTRICAL BUS SPECIFICATIONS | A-3    |

## LIST OF FIGURES

| FIGURE |                                    | PAGE   |

|--------|------------------------------------|--------|

| NUMBER | TITLE                              | NUMBER |

|        |                                    |        |

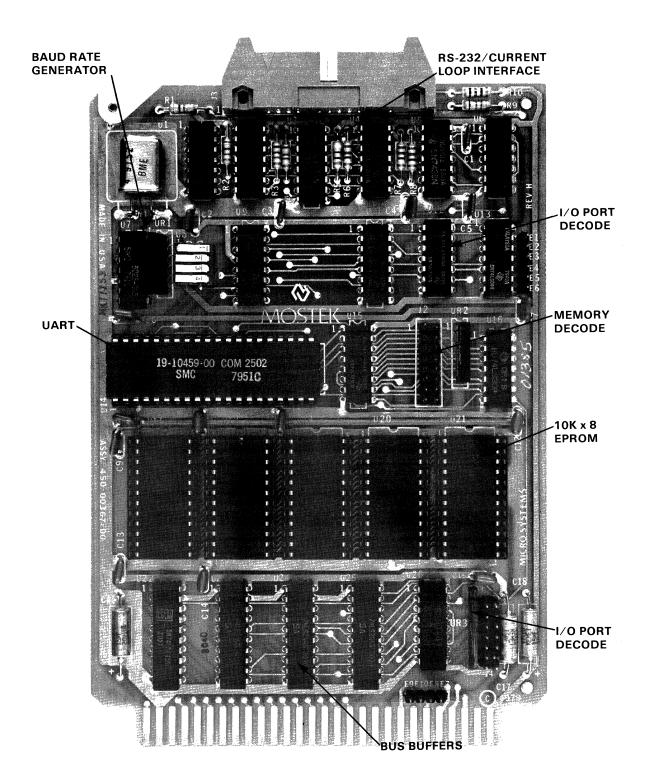

| 1-1    | BOARD PHOTO WITH OVERLAY           | 1-3    |

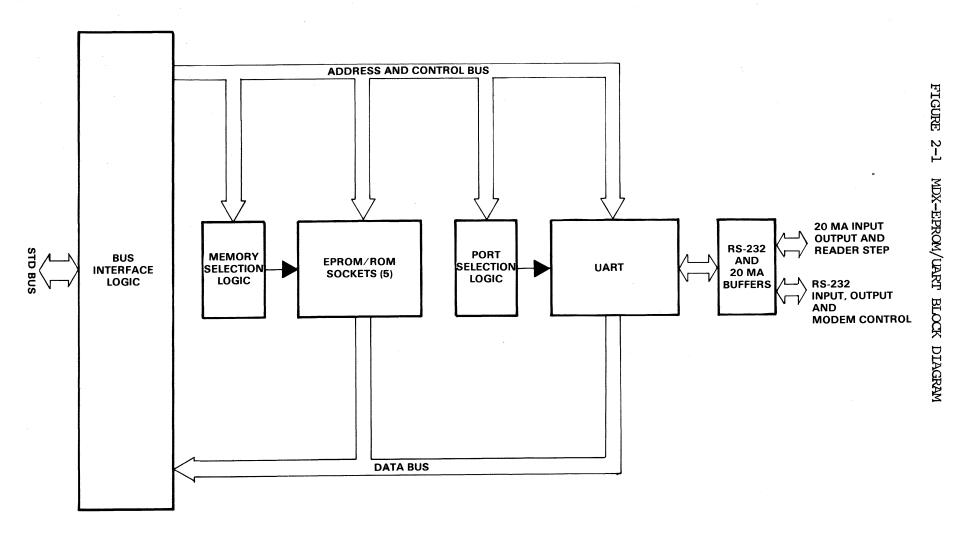

| 2-1    | MDX-EPROM BLOCK DIAGRAM            | 2-2    |

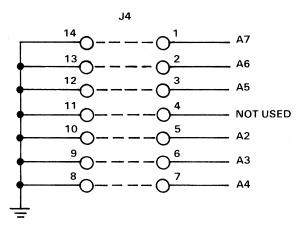

| 3-1    | I/O CHANNELS                       | 3-1    |

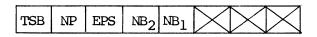

| 3-2    | PROGRAMMING THE UART               | 3–9    |

| 3-3    | TIY CONNECTION WITHOUT READER STEP | 3–13   |

## LIST OF TABLES

| TABLE  |                                  | PAGE   |

|--------|----------------------------------|--------|

| NUMBER | TITLE                            | NUMBER |

| 3-1    | MEMORY DECODING JUMPER SELECTION | 3–6    |

| 3-2    | BAUD RATE SWITCH SELECTION       | 3–8    |

| 3-3    | SERIAL PORT TO RS-232 CONNECTOR  | 3-12   |

## SECTION 1 GENERAL INFORMATION

#### 1.1 INTRODUCTION

- 1.1.1 The MD series and the STD BUS were designed to satisfy the need for low cost OEM Microcomputer modules. The STD BUS uses a mother board interconnect system concept and is designed to handle any MD series card type in any slot. The modules for the STD BUS are a compact 4.5 x 6.5 inches which provide for system partitioning by function (RAM,EPROM,I/O). This smaller module size makes system packaging easier while increasing MOS-LSI densities provide high functionality per module.

- 1.1.2 The MD series of OEM microcomputer boards and the STD BUS offer the most cost-effective system configuration available to the OEM system designer.

## 1.2 GENERAL DESCRIPTION

- 1.2.1 The MDX-EPROM/UART is one of MOSTEK's complete line of STD BUS compatible Z80 microcomputer modules.

- 1.2.2 Designed as a universal EPROM add-on module for the STD BUS, the MDX-EPROM/UART provides the system designer with sockets to contain up to  $10K \times 8$  of EPROM memory (5-2716's) as shown in the Block Diagram, figure 2-1.

- 1.2.3 The EPROM memories can be positioned to start on any 2K boundary within a 16K block of memory via a strapping option provided on the MDX-EPROM/UART.

- 1.2.4 Included on-board the MDX-EPROM/UART is a fully buffered asynchronous I/O port with a Teletype reader step control. A full duplex UART is used to receive and transmit data at the serial port. Operation and UART options are under software control. Once the unit has been programmed, no further changes are

necessary unless there is a modification of the serial data format. Features of the UART include:

Full duplex operation

Start bit verification

Data word size variable from 5 to 8 bits

One or two stop bits may be selected

Odd, even, or no parity option

One word buffering on both transmit and receive

FIGURE 1-1 BOARD PHOTO WITH OVERLAY

## 1.3 STD-Z80 BUS PIN-OUT AND DESCRIPTION

| BUS |                 |                                                            |

|-----|-----------------|------------------------------------------------------------|

| PIN | MNEMONIC        | DESCRIPTION                                                |

|     |                 |                                                            |

| 1   | +5V             | +5Vdc system power                                         |

| 2   | <b>+</b> 5∇     | +5Vdc system power                                         |

| 3   | GND             | Ground - System signal ground and dc return                |

| 4   | GND             | Ground - System signal ground and dc return                |

|     |                 |                                                            |

| 5 * | <b>-</b> 5V     | -5Vdc system power                                         |

| 6 * | <del>-</del> 5V | -5Vdc system power                                         |

|     |                 |                                                            |

| 7   | D3              |                                                            |

| 8   | D <b>7</b>      |                                                            |

| 9   | D2              | Data Bus (Tri-state, input/output active high). D0-D7      |

| 10  | D6              | constitute an 8-bit bidirectional data bus. The data bus   |

| 11  | Dl              | is used for data exchange with memory and I/O devices.     |

| 12  | D5              |                                                            |

| 13  | DØ              |                                                            |

| 14  | D4              |                                                            |

|     |                 |                                                            |

| 15  | D <b>7</b>      |                                                            |

| 16  | A15             |                                                            |

| 17  | A6              |                                                            |

| 18  | Al4             |                                                            |

| 19  | A5              |                                                            |

| 20  | A13             | Address Bus (Tri-state, output, active high). $A_0-A_{15}$ |

| 21  | A4              | make up a 16-bit address bus. The address bus provides     |

| 22  | A12             | the address for memory (up to 65K bytes) data exchanges    |

| 23  | A3              | and for I/O device data exchanges. I/O addressing uses     |

| 24 | All             | the lower 8 address bits to allow the user to directly                   |

|----|-----------------|--------------------------------------------------------------------------|

| 25 | A2              | select up to 256 input or 256 output ports. $A_0$ is                     |

| 26 | AlØ             | the least significant address bit. During refresh                        |

| 27 | Al              | time, the lower 7 bits contain a valid refresh address                   |

| 28 | A9              | for dynamic memories in the system.                                      |

| 29 | AØ              |                                                                          |

| 30 | A8              |                                                                          |

|    |                 |                                                                          |

| 31 | WR              | Memory Write (Tri-state, output, active low). $\overline{\text{WR}}$     |

|    |                 | indicates that the CPU data bus holds valid data to be                   |

|    |                 | stored in the address memory or I/O device.                              |

|    |                 |                                                                          |

| 32 | $\overline{RD}$ | Memory Read (Tri-state, output, active low). $\overline{RD}$             |

|    |                 | indicates that the CPU wants to read data from memory                    |

|    |                 | or an I/O device. The addressed I/O device or memory                     |

|    |                 | should use this signal to gate data onto the CPU data                    |

|    |                 | bus.                                                                     |

|    |                 |                                                                          |

| 33 | IORQ            | Input/Output Request (Tri-state, output, active low).                    |

|    |                 | The IORQ signal indicates that the lower half of the                     |

|    |                 | address bus holds a valid I/O address for an I/O read                    |

|    |                 | or write operation. An $\overline{\text{IORQ}}$ signal is also generated |

|    |                 | with an $\overline{\mathrm{Ml}}$ signal when an interrupt is being       |

|    |                 | acknowledged to indicate that an interrupt response                      |

|    |                 | vector can be placed on the data bus. Interrupt                          |

|    |                 | Acknowledge operations occur during Ml time, while I/O                   |

|    |                 | operations never occur during Ml time.                                   |

| 34 | MEMRO           | Memory Request (Tri-State, output, active low). The                      |

|    | ~               | MEMRQ signal indicates that the address bus holds a                      |

|    |                 | valid address for a memory read or memory write oper-                    |

|    |                 |                                                                          |

ation.

| 35 * | TOEXP   | I/O expansion, not used on Mostek MDX cards.                                                                                                                                                                                                                                                                                                                       |

|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36 * | MEMEX   | Memory expansion, not used on Mostek MDX cards                                                                                                                                                                                                                                                                                                                     |

| 37 * | REFRESH | REFRESH (Tri-state, output, active low). REFRESH indicates that the lower 7 bits of the address bus contain a refresh address for dynamic memories and the MEMRQ signal should be used to perform a refresh cycle for all dynamic RAMs in the system. During the refresh cycle A7 is a logic zero and the upper 8 bits of the address bus contains the I register. |

| 38 * | DEBUG   | DEBUG (Input) used in conjunction with DDT-80 operating system and the MDX Single Step card for implementing a hardware single step. When pulled low, the DEBUG line will set a latch that will force the upper three address lines to a logic 1. To reset this latch, an I/O operation must be performed.                                                         |

| 39 * | MI      | Machine Cycle One (Tri-state, output, active low), $\overline{\text{MI}}$ indicates that the current machine cycle is in the op code fetch cycle of an instruction. Note that during the execution of 2-byte op-codes, $\overline{\text{MI}}$ will be generated                                                                                                    |

40 Status 0 Not used on Mostek MDX cards.

cycle.

Bus Acknowledge (Output, active low). Bus acknowledge is used to indicate to the requesting device that the CPU address bus, data bus, and control bus signals have been set to their high impedance state and the external device can now control the bus.

as each op code is fetched.

always begin with a CBH, DDH, EDH, or FDH.

occurs with IORQ to indicate an interrupt acknowledge

These two-byte op codes

42 \* <u>BUSRO</u>

Bus Request (Input, active low). The BUSRQ signal is used to request the CPU address bus, data bus, and control signal bus to go to a high impedance state so that other devices can control those buses. When BUSRQ is activated, the CPU will set these buses to a high impedance state as soon as the current CPU machine cycle is terminated, and the Bus Acknowledge (BUSAK) signal is activated.

43 \* <u>INTAK</u>

Interrupt Acknowledge (Tri-state output, active low). The  $\overline{\text{INTAK}}$  signal indicates that an interrupt acknowledge cycle is in progress, and the interrupt device should place its response vector on the data bus.

44 \* <u>INTRO</u>

Interrupt Request (Input, active low). The Interrupt Request Signal is generated by I/O devices. A request will be honored at the end of the current instruction if the internal software controlled interrupt enable flip-flop (IFF) is enabled and if the  $\overline{\text{BUSRQ}}$  signal is not active. When the CPU accepts the interrupt, an acknowledge signal ( $\overline{\text{IORQ}}$  during an  $\overline{\text{Ml}}$ ) is sent out at the beginning of the next instruction cycle.

45 WAITRO

WAIT REQUEST (Input, active low). Wait request indicates to the CPU that the addressed memory or I/O devices are not ready for a data transfer. The CPU continues to enter wait states for as long as this signal is active. This signal allows memory or I/O devices of any speed to be synchronized to the CPU.

46 \* NMIRQ

NonMaskable Interrupt Request (Input, negative edge triggered). The nonmaskable interrupt request line has a higher priority than  $\overline{\text{INTRQ}}$  and is always recognized at the end of the current instruction, independent of the status of the interrupt enable flip-flop.  $\overline{\text{NMIRQ}}$  automatically forces the CPU to restart to location  $0066_{\text{H}}$ . The program counter is automatically saved in the external stack so that the user can return to the program that was interrupted. Note that continuous wall cycles can prevent the current instruction from ending, and that a  $\overline{\text{BUSRQ}}$  will override a  $\overline{\text{NMIRO}}$ .

47

SYSRESET

System Reset (Output, active low). The System Reset line indicates that a reset has been generated from either an external reset or the power on reset circuit. The system reset will occur only once per reset request and will be approximately 2 microseconds in duration. A system reset will also force the CPU program counter to zero, disable interrupts, set the I register to  $\emptyset \emptyset_H$ , set the R register to  $\emptyset \emptyset_H$ , and set Interrupt Mode  $\emptyset$ .

48 \*

PBRESET

Push Button Reset (Input, active low). The push button reset will generate a debounced system reset.

49

**CLOCK**

Processor Clock (Output, active low). Single phase

system clock.

50 \*

CNTRL

Auxiliary Timing

51

PCO Priority Chain Output (Output, active high). This signal is used to form a priority interrupt daisy

chain when more than one interrupt driven device is being used. A high level on this pin indicates that no other devices of higher priority are being serviced by a CPU interrupt service routine.

| 52 | PCI | Priority Chain In (Input, active high). This signal is  |

|----|-----|---------------------------------------------------------|

|    |     | used to form a priority interrupt daisy chain when more |

|    |     | than one interrupt driven device is being used. A high  |

|    |     | level on this pin indicates that no other devices of    |

|    |     | higher priority are being serviced by a CPU interrupt   |

|    |     | service routine.                                        |

|      |         | ,                         |

|------|---------|---------------------------|

| 53 * | AUX GND | Auxiliary Ground (Bussed) |

| 54 * | AUX GND | Auxiliary Ground (Bussed) |

|      |         |                           |

| 55   | +12V    | +12Vdc system power       |

|      |         |                           |

| 56   | -12V    | -12Vdc system power       |

### NOTES:

- (1) The input/output designations of the STD-Z80 Bus are made with respect to the MDX-CPU card.

- (2) The following signals have pull-up resistors:  $\overline{WR}$ ,  $\overline{RD}$ ,  $\overline{IROQ}$ ,  $\overline{MEMRQ}$ ,  $\overline{RE}$ - $\overline{FRESH}$ ,  $\overline{DEBUG}$ ,  $\overline{M1}$ ,  $\overline{BUSRQ}$ ,  $\overline{INTAK}$ ,  $\overline{INTRQ}$ ,  $\overline{WAITRQ}$ ,  $\overline{NMIRQ}$ ,  $\overline{SYSRESET}$ ,  $\overline{PBRESET}$  and  $\overline{CLOCK}$ .

- (3) Pins indicated by \* are not connected on the MDX-EPROM/UART.

#### SECTION 2

#### FUNCTIONAL DESCRIPTION

#### 2.1 INTRODUCTION

2.1.1 The MDX-EPROM/UART shown in Figure 1-1 provides a low cost way to expand EPROM and SERIAL I/O for the MDX system. The major functions of the MDX-EPROM/UART are shown in Figure 2-1 and will be explained below.

#### 2.2 MEMORY ARRAY

2.2.1 The memory array consists of up to 5 MK2716's (2K  $\times$  8, +5V only EPROM). The total storage of the MDX-EPROM/UART board is 10,240 bytes.

#### 2.3 MEMORY SELECTION LOGIC

2.3.1 The memory selection logic is responsible for decoding the selected address and enabling the selected EPROM onto the data bus through the data bus buffer.

#### 2.4 PORT SELECTION LOGIC

2.4.1 The port selection logic is used to allow read and write operations to the Serial I/O port (UART).

#### 2.5 UART

2.5.1 The UART on the MDX-EPROM/UART board is used to convert parallel data from the CPU into serial data for use with a serial terminal. The UART is also used to convert serial data from the data terminal into parallel data for the CPU.

#### 2.6 RS-232 AND 20mA BUFFERS

2.6.1 The RS-232 and 20mA buffers are used to convert TTL voltage levels used by the MDX logic to the RS-232 voltage levels and 20mA current loop for use with data communications equipment.

#### SECTION 3

#### UTILIZATION

### 3.1 INTRODUCTION

3.1.1 This section will describe the various jumper options for the MDX-EPROM/UART board.

### 3.2 MEMORY INTERFACE

#### 3.3 EPROM DECODING JUMPERS

3.3.1 The MDX-EPROM/UART can be populated with up to  $10K \times 8$  of EPROM. (5-2716's). The decoding for the EPROM's is on 2K boundaries within a 16K block. Jumper options for the EPROM decoding is shown in Table 3-1.

## 3.4 SERIAL INTERFACE

### 3.5 I/O PORT DECODING JUMPERS

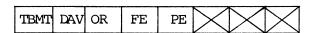

3.5.1 The port decoding for the EPROM/UART board is jumper programmable to allow multiple EPROM/UART boards within a MDX system. The EPROM/UART board uses three read ports and three write ports to interface to the serial port. Figure 3.1 shows the format for strapping the I/O decoder.

FIGURE 3-1 I/O CHANNELS

|                |                |                |                |                |                |       |                 | I/O       | I/O                  |

|----------------|----------------|----------------|----------------|----------------|----------------|-------|-----------------|-----------|----------------------|

| A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | $A_1$ | $A_{\emptyset}$ | READ      | WRITE                |

| Х              | Х              | X              | X              | X              | Х              | Ø     | Ø               | Data from | Data to UART         |

|                |                |                |                |                |                |       |                 | UART      |                      |

| Х              | Х              | Х              | X              | X              | X              | Ø     | 1               | Status    | Control word to UART |

|                |                |                |                |                |                |       |                 | from UART |                      |

| х              | X              | X              | X              | X              | Х              | 1     | Ø               | Read MODE | Write to MODEM LINES |

|                |                |                |                |                |                |       |                 | Lines     |                      |

STRAP = Logic Ø

No STRAP = Logic 1

## EXAMPLE:

STRAP J4 so that the EPROM/UART serial ports will respond to I/O ports DCH, DDH, and DEH:

This strapping will cause the I/O decoder to respond in this way.

| A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | Aø | READ/WRITE PORTS |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|------------------|

| 1              | 1              | Ø              | 1              | 1              | 1              | Ø              | Ø  | DCH              |

| 1              | 1              | Ø              | 1              | 1              | 1              | Ø              | 1  | DDH              |

| 1              | 1              | Ø              | 1              | 1              | 1              | 1              | Ø  | DEH              |

Selected by J4

The strapping of J4 shown in this example is required for use with DDT-80 or the MDX-DEBUG board.

#### 3.6 BAUD RATE SELECTION

3.6.1 The baud rate for the serial interface is generated by the baud rate chip U7. The baud rate is selected by DIP switch U8. Table 3.2 shows DIP switch setting versus baud rates.

#### 3.7 PROGRAMMING THE UART

3.7.1 A full duplex UART is used to receive and transmit data at the serial port. Operation and UART options are under software control. Once the unit has been programmed, no further changes are necessary unless there is a modification of the serial format. Transmit and receive clock rates (baud clock rate) must be 16 times the desired baud rate. A programming model for the UART is shown in Figure 3-2.

## 3.8 SERIAL I/O CONNECTOR AND CABLE

- 3.8.1 All serial interface lines are brought out to a 26-pin connector J3.

- 3.8.2 The serial cable is constructed of the following parts:

- 1) 26-pin connector (Ansley No. 609-2600M)

- 2) 26 wire flat cable (Ansley No. 171-26)

- 3) 25-pin standard EIA-RS232 connector (Ansley No. 609-25P)

- 3.8.3 Table 3-3 shows the interconnection between the 26-pin connector and the 25-pin RS-232 connector.

#### 3.9 RS-232 INTERFACE

3.9.1 Because the MDX-EPROM/UART was designed to communicate with RS-232 terminals (as opposed to other types of communication peripherals), the serial interface looks like a receiving modem or computer port rather than a transmitting

terminal port (such as a Silent 700). The effect of this is to scramble three pairs of signals.

## 3.9.2 For example:

1) <u>Transmitted Data (RS-232) from Terminal</u> (Pin 3) is an out direction signal at the terminal but is shown as an in-direction signal at the serial port.

Receive Data (RS-232) at Terminal (Pin 5) is an in-direction signal at the terminal but is shown as an out-direction signal at the serial port.

2) Request To Send (Pin 7) is an out-direction signal at the terminal but is shown as an in-direction signal at the serial port.

Clear To Send (Pin 9) is an in-direction signal at the terminal but is shown as an out-direction signal at the serial port.

3) <u>Data Terminal Ready</u> (Pin 14) is an out-direction signal at the terminal but is shown as an in-direction signal at the serial port.

Data Set Ready (Pin 11) is an in-direction signal at the terminal but it is shown as an out-direction at the serial port.

3.9.3 To change the "sense" of this port i.e., to make it look like a transmitting terminal (as might be required in some OEM applications), the two signals in each pair above need to be interchanged.

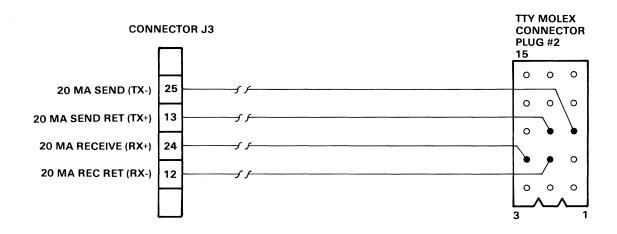

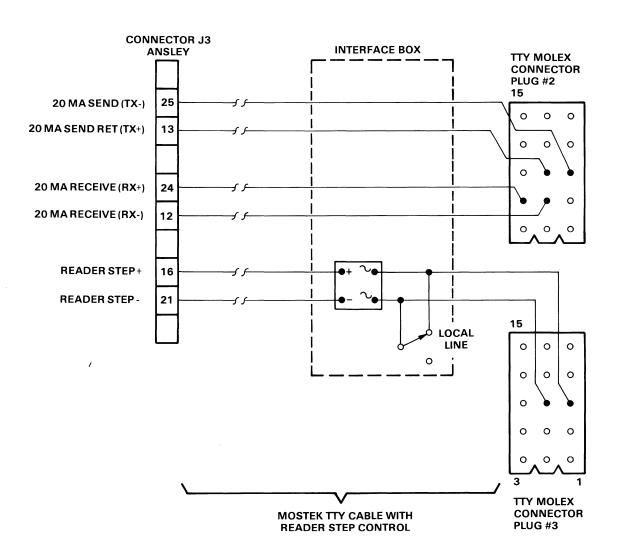

#### 3.10 TELETYPE AND READER STEP INTERFACE

3.10.1 Figure 3-3 shows how the MDX-EPROM/UART can be interfaced to an ASR-33 Teletype with and without reader step. The reader step function is controlled by lines RS+ and RS-. These lines control an optically isolated solid state relay

which controls the 115VAC teletype reader. The MDX-DEBUG board is designed to interface directly to the MOSTEK TTY cable with reader step control. The Reader Step lines can control up to 40mA of current.

## NOTES:

Under no circumstances should 110VAC ever be applied to the MDX-EPROM/UART or MDX-DEBUG cards.

TABLE 3-1

MEMORY DECODING JUMPER SELECTION

| J2 JUMPERS                                                                              |                                               |                                               |                                               |                                               |                                               | JUMPERS<br>El - E6          |

|-----------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------|

| DECODED<br>ADDRESS                                                                      | EPROM<br>U17                                  | EPROM<br>U18                                  | EPROM<br>U19                                  | EPROM<br>U2Ø                                  | EPROM<br>U21                                  |                             |

| 0000-07FF                                                                               | J2<br>Pin to Pin<br>16 1                      | J2<br>Pin to Pin<br>15 1                      | J2<br>Pin to Pin<br>14                        | J2 Pin to Pin 13 1                            | J2<br>Pin to Pin<br>12 1                      | <b>A</b>                    |

| 0800-0FFF<br>1000-17FF<br>1800-1FFF<br>2000-27FF<br>2800-2FFF<br>3000-37FF<br>3800-3FFF | " 2<br>" 3<br>" 4<br>" 5<br>" 6<br>" 7        | El to E6<br>and<br>E4 to E5 |

| 4000-47FF<br>4800-4FFF<br>5000-57FF<br>5800-5FFF<br>6000-67FF<br>6800-6FFF<br>7000-77FF | " 1<br>" 2<br>" 3<br>" 4<br>" 5<br>" 6<br>" 7 | " 1 2 3 4 4 5 6 7 8                           | " 1<br>" 2<br>" 3<br>" 4<br>" 5<br>" 6<br>" 7 | " 1<br>" 2<br>" 3<br>" 4<br>" 5<br>" 6<br>" 7 | " 1<br>" 2<br>" 3<br>" 4<br>" 5<br>" 6<br>" 7 | El to E6<br>and<br>E3 to E5 |

| 8000-87FF<br>8800-8FFF<br>9000-97FF<br>9800-9FFF<br>A000-A7FF<br>A800-AFFF<br>B000-B7FF | " 1<br>" 2<br>" 3<br>" 4<br>" 5<br>" 6<br>" 7 | " 1<br>" 2<br>" 3<br>" 4<br>" 5<br>" 6<br>" 7 | " 1<br>" 2<br>" 3<br>" 4<br>" 5<br>" 6<br>" 7 | " 1<br>" 2<br>" 3<br>" 4<br>" 5<br>" 6<br>" 7 | " 1<br>" 2<br>" 3<br>" 4<br>" 5<br>" 6<br>" 7 | E2 to E6<br>and<br>E4 to E5 |

| CØØØ-C7FF<br>C8ØØ-CFFF<br>DØØØ-D7FF<br>D8ØØ-DFFF<br>EØØØ-E7FF<br>E8ØØ-EFFF<br>FØØØ-F7FF | " 1<br>" 2<br>" 3<br>" 4<br>" 5<br>" 6<br>" 7 | " 1<br>" 2<br>" 3<br>" 4<br>" 5<br>" 6<br>" 7 | " 1<br>" 2<br>" 3<br>" 4<br>" 5<br>" 6<br>" 7 | " 1<br>" 2<br>" 3<br>" 4<br>" 5<br>" 6<br>" 7 | " 1<br>" 2<br>" 3<br>" 4<br>" 5<br>" 6<br>" 7 | E2 to E6<br>and<br>E3 to E5 |

NOTE: The MDX-DEBUG board is a specialized version of the MDX-EPROM/UART board. The difference between the boards is the installation of the ASMB-80/DDT-80 ROM firmware package. The MDX-DEBUG board will come from the factory with J2 jumpered for addresses C000-E7FF. However, the ROMs may be removed and EPROMs inserted for customer applications. In that case the table shown above should be used to select the appropriate jumper options.

TABLE 3-2

BAUD RATE SWITCH SELECTION

|   | U8 SWITCH |   |   |   |       |        |

|---|-----------|---|---|---|-------|--------|

|   | POSITION  |   |   |   | X16   | BAUD   |

|   | 4         | 3 | 2 | 1 | CLOCK | RATE   |

| _ |           |   |   |   |       |        |

|   | Ø         | Ø | Ø | Ø | •8KHZ | 5Ø     |

| 1 | Ø         | Ø | Ø | 1 | 1.2   | 75     |

|   | Ø         | Ø | 1 | Ø | 1.76  | 110    |

|   | Ø         | Ø | 1 | 1 | 2.152 | 134.5  |

|   | Ø         | 1 | Ø | Ø | 2.4   | 150    |

|   | Ø         | 1 | Ø | 1 | 4.8   | 300    |

|   | Ø         | 1 | 1 | Ø | 9.6   | 600    |

|   | Ø         | 1 | 1 | 1 | 19.2  | 1200   |

|   | 1         | Ø | Ø | Ø | 28.8  | 1800   |

|   | 1         | Ø | Ø | 1 | 32.0  | 2000   |

|   | 1         | Ø | 1 | Ø | 38.4  | 2400   |

|   | 1         | Ø | 1 | 1 | 57.6  | 3600   |

|   | 1         | 1 | Ø | Ø | 76.8  | 4800   |

|   | 1         | 1 | Ø | 1 | 115.2 | 7200   |

|   | 1         | 1 | 1 | Ø | 153.6 | 9600   |

|   | 1         | 1 | 1 | 1 | 307.2 | 19,200 |

1 = OPEN

$\emptyset$  = CLOSED

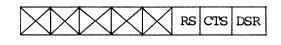

#### FIGURE 3-2 PROGRAMMING THE WART

1. UART DATA PORT DCH Write to Port DCH

DATA TO SERIAL DEVICE

Read from UART

DATA FROM SERIAL DEVICE

2. UART CONTROL PORT  ${\rm DD}_{\rm H}$  Write to UART

Read from UART

3. System Control Port  $\underline{\text{DE}_H}$  Write to Port  $\underline{\text{DE}_H}$

Read from Port DEH

Number Stop Bits (TSB)

This bit will select the number of stop bits, 1 or 2, to be appended immediately after the parity bit. A logic "0" will insert 1 stop bit and a logic "1" will insert 2 stop bits.

No Parity (NP)

A logic "1" on this lead will eliminate the parity bit from the transmitted and received character (no PE indication). The stop bit(s) will immediately follow the last data bit.

Odd/Even Parity Select (EPS)

The logic level on this pin selects the type of parity which will be appended immediately after the data bits. It also determines the parity that will be checked by the receiver. A logic "Ø" will insert odd parity and a logic "l" will insert even parity.

#### FIGURE 3-2 (cont)

Number of Bits/Character

(NB2, NB1)

These two bits will be internally decoded to select either 5,6,7 or 8 data bits/character.

| NB2 | NB1 | Bits/Character |

|-----|-----|----------------|

| Ø   | Ø   | 5              |

| Ø   | 1   | 6              |

| 1   | Ø   | 7              |

| 1   | 1   | 8              |

Transmitter Buffer Empty

(TBMT)

The transmitter buffer empty flag goes to a logic "1" when the data buffer holding register may be loaded with another character.

Data Available (DAV)

This bit goes to a logic "1" when an entire character has been received and transferred to the receiver holding register.

Over-Run (OR)

This bit goes to a logic "1" if the previously received character is not read (DAV line not reset) before the present character is transferred to the receiver holding register.

Framing Error (FE)

This bit goes to a logic "1" if the received character has no valid stop bit.

Parity Error (PE)

This bit goes to a logic "1" if the received character parity does not agree with the selected parity.

Reader Step (RS)

A logic 1 on this bit will activate the reader step current loop driver.

## FIGURE 3-2 (cont)

Clear to Send (CTS)

A logic 1 on this bit will set the CTS output to a +V RS-232 level.

Data Set Ready (DSR)

A logic 1 on this bit will set the DSR output to a +V RS-232 level

Request to Send (RTS)

This bit goes to a logic 1 when the RS-232 RTS is in its active state.

Data Terminal Ready (DTR) This bit goes to a logical 1 when the RS-232 DTR is in its active state.

Serial IN (SI) This port line inputs the serial data stream from the EIA or teletype terminal that is required by DDT-80.

NOTE: DDT-80 was written to automatically calculate and generate the baud rate for the UART using a CTC. However, the MDX-EPROM/UART and MDX-DEBUG cards do not use this feature. The baud rate for the MDX-EPROM/UART and MDX-DEBUG cards is generated by a switch selectable baud rate generator.

TABLE 3-3

SERIAL PORT TO RS-232 CONNECTOR

| SIGNAL                 | J3 CONNECTOR | RS-232 CONNECTOR              |

|------------------------|--------------|-------------------------------|

| NAME                   | Pin Number   | Pin Number                    |

|                        |              |                               |

| Chassis GND            | 1            | 1                             |

|                        | 14           | 14                            |

| Transmitted data       | 2            | 2                             |

| (RS-232) from terminal | 15           | 15                            |

| Receive data (RS-232)  | 3            | 3                             |

| at terminal            |              |                               |

| Reader step +          | 16           | 16                            |

| Request to send        | 4            | 4                             |

|                        | .17          | 17                            |

| Clear to send          | 5            | 5                             |

|                        | 18           | 18                            |

| Data set ready         | 6            | 6                             |

|                        | 19           | 19                            |

| GND                    | 7            | 7                             |

| Data terminal ready    | 2Ø           | 2Ø                            |

| Carrier detect         | 8            | 8                             |

| Reader step -          | 21           | 21                            |

|                        | 9            | 9                             |

|                        | 22           | 22                            |

|                        | 1Ø           | 100                           |

|                        | 23           | 23                            |

|                        | 11           | 11                            |

| 20mA Receive (RX+)     | 24           | 24                            |

| 20mA Receive RET(RX-)  | 12           | 12                            |

| 20mA Send (TX-)        | 25           | 25                            |

| 20mA Send RET (TX+)    | 13           | 13                            |

|                        | 26           | Wire remove from 26 wire flat |

|                        |              | cable                         |

FIGURE 3-3 TTY CONNECTION WITHOUT READER STEP

|  |  |  |  | • |  |

|--|--|--|--|---|--|

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

APPENDIX A

SPECIFICATIONS

#### SPECIFICATIONS

### A.1 ELECTRICAL SPECIFICATIONS

WORD SIZE

8 bits for PROM

5 to 8 bits for Serial I/O.

MEMORY ADDRESSING

ROM/EPROM

$2\mbox{K}$  blocks jumper selectable for any  $2\mbox{K}$  boundary within a given  $16\mbox{K}$  boundary of  $28\mbox{Ø}$  memory map.

MEMORY CAPACITY

10K bytes of 2716 memory. (2716's not included)

MEMORY SPEED REQUIRED

MEMORY ACCESS TIME

2716\* 450ns

\*Single 5 Volt type required

## I/O TRANSFER RATE

| X16 BAUD RATE CLOCK | BAUD RATE (Hz) |

|---------------------|----------------|

| 1760                | 110            |

| 4800                | 300            |

| 9600                | 600            |

| 19200               | 1200           |

| 38400               | 2400           |

| 76800               | 4800           |

| 153600              | 9600           |

| 307200              | 19200          |

#### SERIAL COMMUNICATIONS CHARACTERISTICS

## Asynchronous

Full duplex operation

Start bit verification

Data word size variable from 5 to 8 bits

One or two stop bits

Odd, even, or no parity

One word buffering on both transmit and receive.

## I/O ADDRESSING

On-board fully programmable

## SYSTEM CLOCK

MIN.

MAX.

MDX-EPROM/UART

250 KHz

2.5 MHz

MDX-EPROM/UART-4

250 KHz

4.0 MHz

#### POWER SUPPLY REQUIREMENTS

+12 Volts + 5% at 50 mA max.

-12 Volts + 5% at 35 mA max.

+5 Volts + 5% at 1.2 A max.

#### OPERATING TEMPERATURE RANGE

00 to +600C

#### A.2 MECHANICAL SPECIFICATIONS

#### CARD DIMENSIONS

4.5 in. (11.43cm) high by 6.50 in. (16.51 cm) long

0.48 in. (1.22 cm) maximum profile thickness

0.062 in. (0.16 cm) printed circuit board thickness

## CONNECTORS

| FUNCTION   | CONFIGURATION                    | MATING CONNECTOR                                                                                          |

|------------|----------------------------------|-----------------------------------------------------------------------------------------------------------|

| STD BUS    | 56 pin dual<br>0.125 in. centers | Printed Circuit Viking 3VH28/1CE5 Wire Wrap                                                               |

|            |                                  | 3VH28/1CND5 Solder Lug Viking 3VH28/1CN5                                                                  |

| Serial I/O | 26 pin dual<br>0.100 in. grid    | Flat Ribbon Ansley 609-2600M Discrete Wires Winchester PGB26A (housing) Winchester 100- 70020S (contacts) |

## A.3 STD-Z80 ELECTRICAL BUS SPECIFICATIONS

Bus Receivers

One 74LS load max.

### Bus Drivers

Logical Low: 0.5V max at 24mA Logical High: 2.4V min at -2.6mA

Recommended Bus Drivers and Receivers

Bus Drivers - 74LS240, 74LS2241, 74LS373, 74LS374, 74LS244

Bus Receivers - 74LS240, 74LS241, 74LS244

Bus Transceivers - 74LS245, 74LS242, 74LS243

|   | - |  |

|---|---|--|

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

| • |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   | • |  |

|   |   |  |

|   |   |  |

1215 W. Crosby Rd. • Carrollton, Texas 75006 • 214/323-6000 In Europe, Contact: MOSTEK Brussels 150 Chaussee de la Hulpe, B1170, Belgium; Telephone: 660.69.24

Mostek reserves the right to make changes in specifications at any time and without notice. The information furnished by Mostek in this publication is believed to be accurate and reliable. However, no responsibility is assumed by Mostek for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Mostek.