# Interfacing Serial EEPROM To DSP563xx

by

Ilan Naslavsky Leonid Smolyansky

Motorola, Incorporated Semiconductor Products Sector 6501 William Cannon Drive West Austin, TX 78735-8598

Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

# **CONTENTS**

| 1     | Introduction                                  |

|-------|-----------------------------------------------|

| 1.1   | Scope                                         |

| 1.2   | Serial EEPROM Versus Parallel EEPROM          |

| 1.3   | Application Example                           |

| 1.4   | Serial EEPROM / DSP Clock Ratio               |

| 2     | Physical Connection                           |

| 2.1   | Serial EEPROM Pinout                          |

| 2.2   | ESSI Pin Connections                          |

| 2.3   | SCI Pin Connections                           |

| 2.4   | Chip Select (CS)                              |

| 2.5   | HOLD And WP Lines                             |

| 3     | System Implementation                         |

| 3.1   | Block Diagram                                 |

| 3.2   | High-Level Functions                          |

| 3.3   | Application Program Interface                 |

| 3.3.1 | WRITE_BLOCK Function                          |

| 3.3.2 | READ BLOCK Function                           |

| 3.3.3 | PROTECT Function                              |

| 3.3.4 | UNPROTECT Function                            |

| 3.3.5 | PROTECT_ALL Function                          |

| 3.3.6 | UNPROTECT_ALL Function                        |

| 3.4   | Serial EEPROM Functions                       |

| 3.4.1 | WRITE_ENABLE and WRITE_DISABLE Functions 3-23 |

| 3.4.2 | READ_STATUS_REG Function                      |

| 3.4.3 | WRITE_STATUS_REG Function                     |

| 3.4.4 | WRITE Function                                |

| 3.4.5 | READ Function                                 |

| 3.5   | Auxiliary Routines                            |

| 3.5.1 | Serial Interface Reset                        |

| 3.5.2 | Synchronize Serial Interface                  |

| 3.5.3 | Poll Status Register3-36                      |

| 3.5.4 | Read Modify Write Operation3-37               |

| 3.6   | ESSI Timing Considerations                    |

| 4     | ESSI and SCI Configuration                         |

|-------|----------------------------------------------------|

| 4.1   | ESSI Configuration                                 |

| 4.1.1 | ESSI Control Register A                            |

| 4.2.1 | ESSI Control Register B                            |

| 4.3.1 | ESSI Port Control, Direction and Data Registers    |

| 4.4   | SCI Configuration                                  |

| 4.4.1 | SCI Control Register                               |

| 4.5.1 | SCI Clock Control Register                         |

| 4.6.1 | SCI Port Control, Direction, and Data Registers4-5 |

| 5     | Customization                                      |

| 5.1   | Code Optimization5-1                               |

| 5.2   | Larger-Capacity Serial EEPROM5-1                   |

| Apper | ndix A Assembly Equates                            |

| Apper | ndix B Assembly Equates                            |

# **Figures**

| Figure 1-1  | Application Example                        | 1-2  |

|-------------|--------------------------------------------|------|

| Figure 2-1  | DSP - Serial EEPROM Connection to the ESSI | 2-2  |

| Figure 2-2  | DSP - Serial EEPROM Connection with SCI    | 2-3  |

| Figure 3-1  | System Implementation                      | 3-1  |

| Figure 3-2  | WRITE_BLOCK Flow-Chart                     | 3-4  |

| Figure 3-3  | WRITE_BLOCK Timing for One Page            | 3-5  |

| Figure 3-4  | WRITE_BLOCK Timing                         | 3-5  |

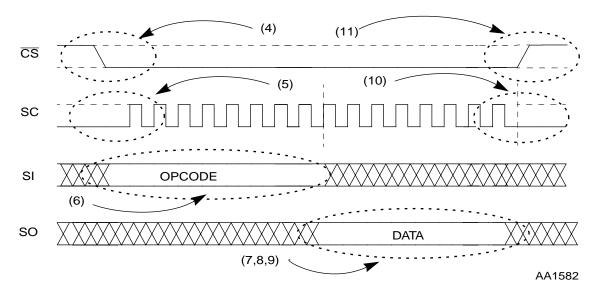

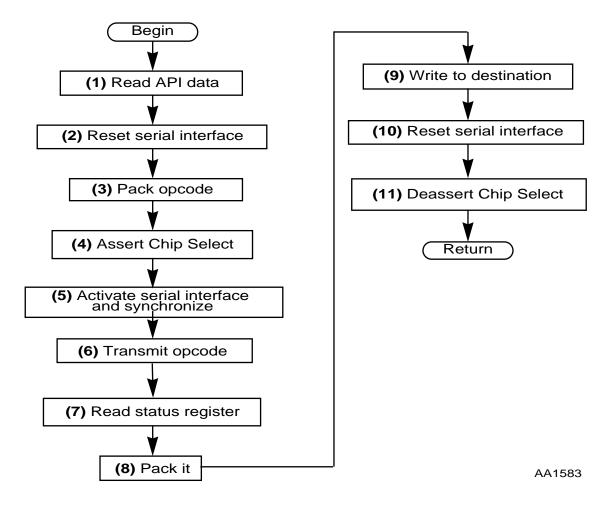

| Figure 3-5  | READ_BLOCK Flow Chart 3                    | 3-12 |

| Figure 3-6  | READ_BLOCK Timing 3                        | 3-13 |

| Figure 3-7  | PROTECT/UNPROTECT Flow-Chart               | 3-17 |

| Figure 3-8  | WRITE_ENABLE/WRITE_DISABLE Flowchart 3     | 3-23 |

| Figure 3-9  | READ_STATUS_REG Timing                     | 3-26 |

| Figure 3-10 | READ_STATUS_REG Flow-Chart                 | 3-26 |

| Figure 3-11 | WRITE_STATUS_REG Timing                    | 3-30 |

| Figure 3-12 | WRITE_STATUS_REG Flow-Chart 3              | 3-31 |

| Figure 3-13 | ESSI Enabling Synchronization              | 3-39 |

| Figure 3-14 | ESSI Disabling Synchronization             | 3-39 |

| Figure 4-2  | Control Register A                         | 4-1  |

| Figure 4-3  | Control Register B                         | 4-2  |

| Figure 4-5  | SCI Control Register                       | 4-4  |

| Figure 4-6  | SCI Clock Control Register                 | 4-5  |

# **Tables**

| Table 2-1 | Serial EEPROM Pins2-1          |

|-----------|--------------------------------|

| Table 3-1 | High-Level Functions           |

| Table 3-2 | WRITE_BLOCK Parameters         |

| Table 3-3 | READ_BLOCK Parameters3-13      |

| Table 3-4 | PROTECT Parameters             |

| Table 3-5 | UNPROTECT Parameters           |

| Table 3-6 | Serial EEPROM Functions        |

| Table 3-7 | READ_STATUS_REG Parameters     |

| Table 3-8 | WRITE_STATUS_REG Parameters    |

| Table 4-1 | PCRC, PRRC and PDRC Values 4-3 |

| Table 4-1 | PCRE PRRE and PDRE Values 4-6  |

viii

# **Examples**

| Example 3-1  | API Access Code                                  |

|--------------|--------------------------------------------------|

| Example 3-2  | WRITE_BLOCK Routine Assembly Code                |

| Example 3-3  | A WRITE_BLOCK Call                               |

| Example 3-4  | READ_BLOCK Assembly Code                         |

| Example 3-5  | A READ_BLOCK Call                                |

| Example 3-6  | PROTECT Function Assembly Code                   |

| Example 3-7  | A PROTECT Call                                   |

| Example 3-8  | UNPROTECT Function Assembly Code                 |

| Example 3-9  | An UNPROTECT Call                                |

| Example 3-10 | The PROTECT_ALL Function                         |

| Example 3-11 | A PROTECT_ALL Call                               |

| Example 3-12 | The UNPROTECT_ALL Function                       |

| Example 3-13 | An UNPROTECT_ALL Call                            |

| Example 3-14 | WRITE_ENABLE/_DISABLE Routine Assembly Code 3-24 |

| Example 3-15 | WRITE_ENABLE/_DISABLE Calls                      |

| Example 3-16 | READ_STATUS_REG Routine Assembly Code            |

| Example 3-17 | READ_STATUS_REG Call                             |

| Example 3-18 | WRITE_STATUS_REG Assembly Code                   |

| Example 3-19 | A WRITE_STATUS_REG Call                          |

| Example 3-20 | Single Byte WRITE Call                           |

| Example 3-21 | Single Page WRITE Call                           |

| Example 3-22 | One-Byte SEEPROM READ Call                       |

| Example 3-23 | SERIAL_INTERFACE_RESET Code                      |

| Example 3-24 | SYNCHRONIZE Code            | 3 |

|--------------|-----------------------------|---|

| Example 3-25 | POLL_SR Code                | 7 |

| Example 3-26 | READ_MODIFY_WRITE Operation | 7 |

# 1 Introduction

This application report describes how to interface Serial Electrically Erasable Programmable Memory (SEEPROM) devices with DSP56300 Family chips through either the Enhanced Synchronous Serial Interface (ESSI) or the Synchronous Communication Interface (SCI) of the DSP563xx chip. The ESSI and SCI are available in several derivatives of the DSP56300 family of microprocessors. See **Appendix B**.

The DSP56300 Family's ESSI and SCI are fully capable of interfacing to SEEPROM devices through a Serial Peripheral Interface (SPI) bus using the following family features:

- SPI industry-standard bus connection support through ESSI or SCI

- Application Program Interface (API) support for:

- Read data dlock

- Write data block

- Write protection management

- Full serial clock rate support (up to 2MHz)

# 1.1 Scope

This application report describes the connection of DSP56300 Family devices to industry standard SPI-compatible SEEPROMs, such as SGS-THOMSON's ST95010/020/040 or National's NM25C020. It is recommended for the developer who has previous knowledge of Motorola's DSP56300 family, as well as the specification of the selected Serial EEPROM.

**Section 2** describes the physical connection between the serial interface, ESSI or SCI, and a SEEPROM. **Section 3** details the implemented system conception. **Section 4** explains the configuration of ESSI and SCI registers; **Section 5** makes recommendations on system and code customization.

**Appendix A** lists the application's assembly equates; **Appendix B** lists relevant reference information.

#### 1.2 Serial EEPROM Versus Parallel EEPROM

In comparison to Parallel EEPROMs, Serial EEPROMs have several advantages:

- Serial EEPROMs are cheaper.

- Serial EEPROMs are smaller and take up less area on the application board.

- Serial EEPROMs require fewer connection lines.

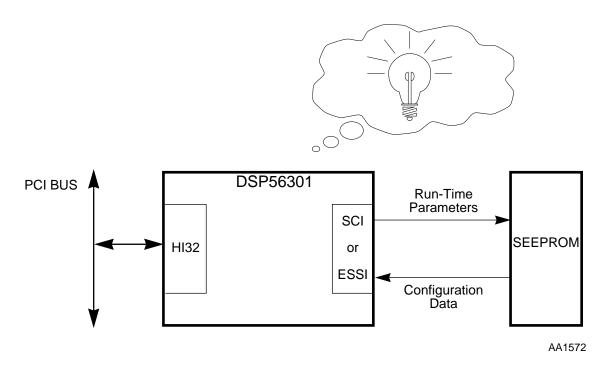

# 1.3 Application Example

**Figure 1-1**illustrates the use of SEEPROMs with DSP56300 Family devices. Here, a DSP56301 chip connects to a Peripheral Component Interconnect (PCI) bus through the HI32 Host Interface and to a SEEPROM through ESSI or SCI. The SEEPROM is used for downloading configuration data for HI32 and for storing run-time parameters that should be saved on non-volatile storage.

Figure 1-1 Application Example

# 1.4 Serial EEPROM / DSP Clock Ratio

Due to ESSI timing considerations, as explained in **Section 3.6**, the ratio between the Serial EEPROM Clock and DSP internal clock is limited to a minimum of 40:1.

For the SCI, the ratio is limited by specification to a minimum of 8:1.

Serial EEPROM / DSP Clock Ratio

# 2 Physical Connection

This section describes the physical connection between the ESSI or SCI and a generic Serial EEPROM. The DSP563xx/Serial EEPROM connection suggested in this application report uses three ESSI pins or three SCI pins and one Port A Address Attribute pin, AAx, to provide all the data and control functions available in marketed Serial EEPROMs.

#### 2.1 Serial EEPROM Pinout

Most SPI-compatible Serial EEPROMs present the user with eight pins: four for the serial interface, two for auxiliary control, and two for supply voltage and ground.

This report refers to an imaginary device with just such a configuration; we use general pin names, not necessarily those used in real devices.

On most Serial EEPROMs, pins with different names can have the same function. **Table 2-1** briefly describes each pin function and the corresponding connection on the application board or DSP.

ESSI SCI Pin **Description** Version Version AAx (DSP Port A)<sup>1</sup>  $\overline{\mathrm{CS}}$ Chip Select SISerial Data Input STDxTXD (SCI)  $(ESSIx)^2$ SO Serial Data Output SRDx RXD (SCI)  $(ESSIx)^2$ Serial Clock, provided by DSP (ESSIx<sup>2</sup> or SCI) SCSCKx SCLK (SCI)  $(ESSIx)^2$ WP Write Protect, disables memory programming if asserted pulled-up HOLD Halts Serial Communication if set pulled-up VCC Power Supply board supplied **GND** Ground board supplied

Table 2-1 Serial EEPROM Pins

#### **ESSI Pin Connections**

**Notes:**

- 1. The application discussed here uses pin AA1. Any of the AAx pins (AA0-AA3) could be used.  $\overline{\text{CS}}$  can also be achieved via any GPIO pin, as explained in **Section 2.3**.

- **2.** This application addresses ESSI0, although it can run on ESSI1 with the appropriate register name changes.

ESSI/SCI and Port A act as the serial interface for the DSP while the two additional control pins ( $\overline{HOLD}$  and  $\overline{WP}$ ) are pulled-up. Power Supply and ground are provided by the board. All these lines should connect on the EEPROM according to the corresponding specification.

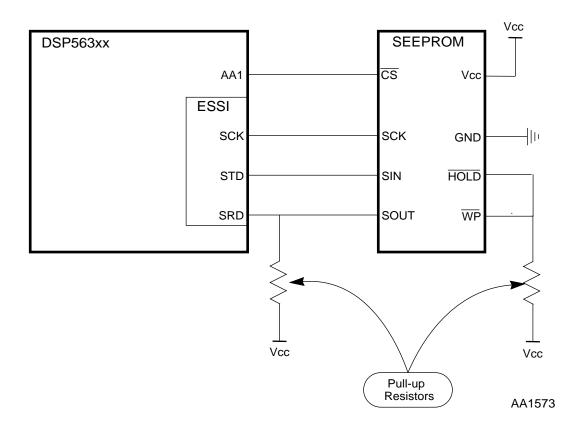

#### 2.2 ESSI Pin Connections

**Figure 2-1** outlines a DSP-Serial EEPROM connection using ESSI. The ESSI supplies the serial clock to the EEPROM through its Serial Clock (SCK) Pin, once the Port C P3 Pin is configured as ESSI. The Serial Data Input (SI) line is provided at the Port C P5 Pin once this pin is configured as the ESSI TX0 Serial Transmitter Output (STD) Pin.

Figure 2-1 DSP - Serial EEPROM Connection to the ESSI

The Serial Data Output (SO) line is supplied by the Serial EEPROM, driving the Port C P4 Pin once it is configured as the ESSI Serial Receive Data (SRD) Pin. In read operations, most Serial EEPROMs keep this line tri-stated until the address byte is received. Since the ESSI works in synchronous mode reading dummy bytes during this period, we recommend pulling up this line to minimize power consumption.

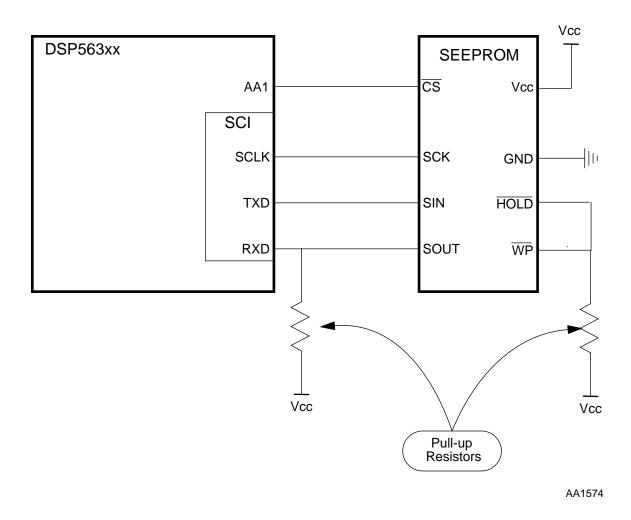

#### 2.3 SCI Pin Connections

**Figure 2-2** outlines a DSP-Serial EEPROM connection using SCI.

Figure 2-2 DSP - Serial EEPROM Connection with SCI

#### **Chip Select (CS)**

The SCI supplies the serial clock to the EEPROM through its Serial Clock (SCLK) Pin once the Port E P2 Pin is configured as SCI. A Serial Data Input (SI) line is provided at the Port E P1 Pin once it is configured as the SCI Transmit Data (TXD) Pin.

The Serial Data Output (SO) line is supplied by the Serial EEPROM, driving the Port E P0 Pin, configured as the SCI Receive Data (RXD) Pin. In read operations, most Serial EEPROMs keep this line tri-stated until the address byte is received. Since SCI works in synchronous mode reading dummy bytes during this period, we recommend pulling up this line to minimize power consumption.

# 2.4 Chip Select (CS)

The Serial EEPROM receives a Chip Select  $(\overline{CS})$  signal from the DSP. Any General-Purpose I/O (GPIO) pin can be used to implement Chip Select for the Serial EEPROM, as long as the pin is kept deasserted any time the EEPROM is not in use. Here,  $\overline{CS}$  is driven at the Port A Address Attribute or Row Address Strobe Pin (AA1/ $\overline{RAS}$ 1), configured as Address Attribute. Any activity on serial interface pins while  $\overline{CS}$  is deasserted has no effect on the Serial EEPROM.

The  $\overline{\text{CS}}$  line is asserted and deasserted by changing the pin polarity, with no relation to the Port A Address Attribute mechanism. This pin cannot be used with *real* Address Attribute functionality in applications implementing the currently-described connection. This procedure permits usage of the ESSI or SCI for other connections besides Serial EEPROM in the same application.

To configure the AA1/ $\overline{\text{RAS}}$ 1 ( $\overline{\text{CS}}$ ) Pin as an Address Attribute, DRAM access should not be defined for the external access type through the External Access Type and Pin Definition Bits (BAT(1:0) = 10), at the corresponding Address Attribute Register (AAR1). The pin polarity is determined in AAR1, through the AA Pin Polarity (BAAP) Bit. Since AA1 is not used for external access, the AA1 pin always reflects an inactive status. A set BAAP bit gives an active high pin, so the AA1 ( $\overline{\text{CS}}$ ) Pin is low and Chip Select is asserted. The default after reset is a cleared BAAP that provides an active low pin, or the deassertion of the Chip Select Pin (AA1 -  $\overline{\text{CS}}$ ). If BAAP is set, the AA1 ( $\overline{\text{CS}}$ ) pin is active high and  $\overline{\text{CS}}$  is asserted.

#### 2.5 HOLD And WP Lines

Asserting the  $\overline{\text{HOLD}}$  pin halts serial communication without resetting the current sequence. This option is not implemented in this application report. This line is hard-wired deasserted through a pull-up resistor.

The WP pin disallows write operations to memory when it is asserted. The application discussed here provides writing functions, so this pin is kept deasserted by a pull-up resistor. Write protection can be achieved by software through a proper call to one of the write protection handling functions.

Active usage of these lines can be achieved by GPIO pins, but such usage is beyond the scope of this application.

**HOLD And WP Lines**

# 3 System Implementation

This section presents a set of assembly routines that accomplish high-level functions for transparent access to the Serial EEPROM. These functions allow any application running on the DSP563xx to interact with the Serial EEPROM by subroutine calls with memory-mapped arguments. Along with the high-level functions, auxiliary lower-level routines compose a kernel to perform the Serial EEPROM tasks employed by the functions. These kernel functions are also available for direct call by any application.

# 3.1 Block Diagram

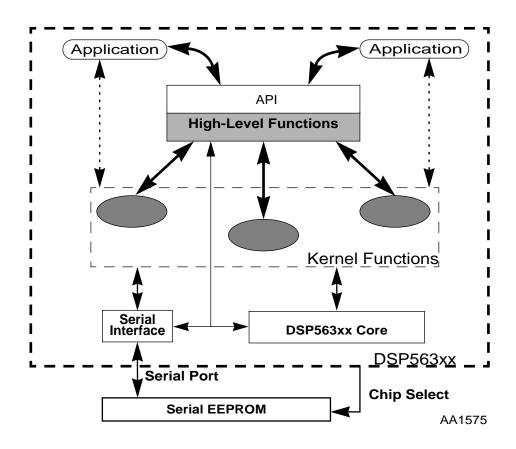

**Figure 3-1** shows a block diagram of a general application that interacts with a Serial EEPROM. As **Section 2** shows, any application running on a DSP563xx can access an external Serial EEPROM connected to a serial interface, ESSI, or SCI. All interaction occurs through an Application Program Interface (API). No additional code is needed. Optionally, the application can call lower-level routines (kernel routines) for a direct interaction with the Serial EEPROM.

Figure 3-1 System Implementation

# 3.2 High-Level Functions

The high-level Serial EEPROM functions perform write to SEEPROM, read from SEEPROM and SEEPROM write protection control. **Table 3-1** summarizes these functions.

**Function** Description WRITE BLOCK Copies a block of N x M-byte words from any DSP memory space to Serial EEPROM READ BLOCK Copies a block of N x M-byte words from Serial EEPROM to any DSP memory space **PROTECT** Write-protects Serial EEPROM above any given address PROTECT ALL Write-protects all Serial EEPROM UNPROTECT Write-unprotects Serial EEPROM below any given address UNPROTECT\_ALL Write-unprotects all Serial EEPROM

**Table 3-1** High-Level Functions

# 3.3 Application Program Interface

A straightforward Application Program Interface (API) is provided for interaction with Serial EEPROM. The basic procedure consists of two steps:

- 1. Data Feed: transferring arguments to data memory through a set of **move** instructions, DMA transfers, or previous Serial EEPROM download

- 2. Subroutine Call: any flow control instructions (**jumps** and **branches** to a correspondent subroutine)

**Notes:** 1. PROTECT\_ALL and UNPROTECT\_ALL functions do not require step 1.

2. Memory protection handling is performed by the user's application through a suitable call to any of the write protection handling functions. The API does execute a call of WRITE\_BLOCK to a protected address, although SEEPROM does not complete the write cycle because of the protection.

The following example shows the code for general accesses to the API:

Example 3-1 API Access Code

```

; MACRO definition

API

MACRO ARGUMENT, VALUE

move

#(VALUE),r0

r0,x:ARGUMENT

move

ENDM

; call <FUNCTION> with parameters: PARAMETER_0,PARAMETER_1,...,PARAMETER_n

<PARAMETER 0>, <VALUE FOR PARAMETER 0>

API

API

<PARAMETER_1>,<VALUE_FOR_PARAMETER_1>

<PARAMETER_2>,<VALUE_FOR_PARAMETER_2>

APT

API

<PARAMETER_n>, <VALUE_FOR_PARAMETER_n>

<FUNCTION>

; call <FUNCTION> without parameters

bsr

<FUNCTION>

```

The sections that follow completely describe all the functions and respective parameters. Each description includes the function's flowchart, timing diagrams, and the routine's code. Major steps in the routine are indexed and referenced both in the flowchart and the timing diagrams. Functions that require calling parameters, are summarized in a table for each function. Descriptions conclude with an example function call.

The code provided is the same for both the ESSI and SCI versions. Particular portions corresponding to one peripheral or the other (ESSI or SCI) are selected during assembling through the equate SERIAL\_INTERFACE. This equate is defined in **Appendix A**. To assemble the code for ESSI, SERIAL\_INTERFACE should be equal to 'ESSI'. Similarly, to assemble the code for SCI, SERIAL\_INTERFACE equate must be 'SCI'.

# 3.3.1 WRITE\_BLOCK Function

The WRITE\_BLOCK function permits the application to copy a block of words from DSP memory to the Serial EEPROM. The function performs Serial EEPROM page

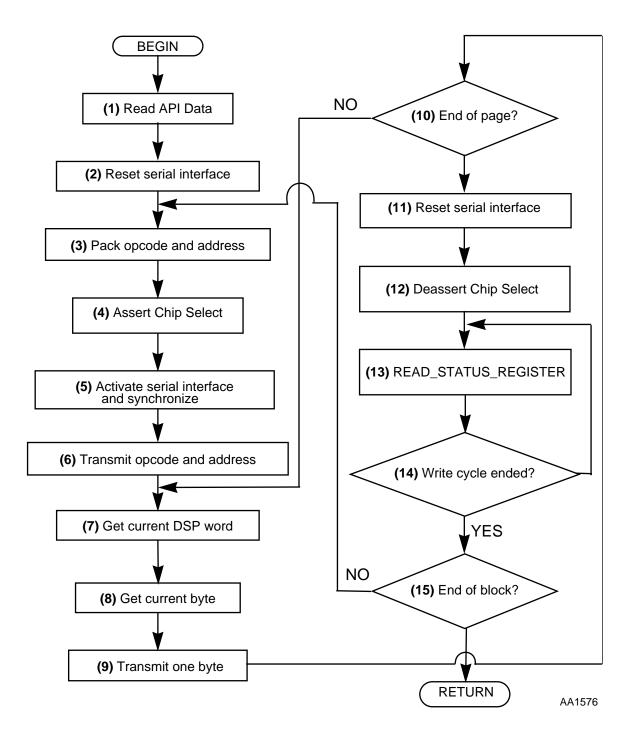

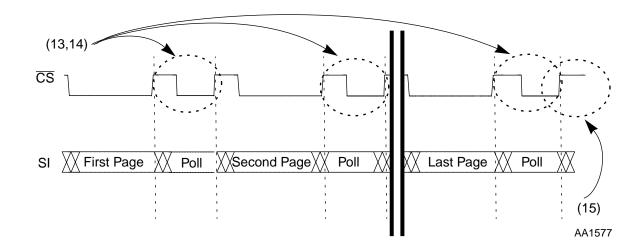

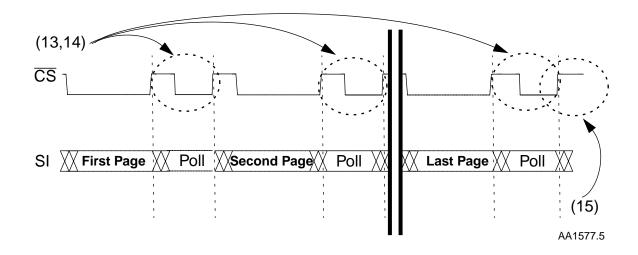

management in a transparent way. **Figure 3-2** displays the WRITE\_BLOCK function flowchart; **Figure 3-3** and **Figure 3-4** show the function's timing scheme.

Figure 3-2 WRITE\_BLOCK Flow-Chart

Figure 3-3 WRITE\_BLOCK Timing for One Page

Figure 3-4 WRITE\_BLOCK Timing

**Table 3-2** depicts WRITE\_BLOCK parameters.

Table 3-2

WRITE\_BLOCK Parameters

| Parameter      | Description                                    | Range                                                 | API (1) |

|----------------|------------------------------------------------|-------------------------------------------------------|---------|

| WR_N_SRC_N     | number of words to be written to SEEPROM       | 1 to 16M-words (24 bits)                              | x:\$8   |

| WR_N_SRC_SPC   | block source memory space                      | X,Y or P, case insensitive                            | x:\$9   |

| WR_N_SRC_ADD   | block source base address                      | any mapped DSP memory address                         | x:\$A   |

| WR_N_DEST_ADD  | Serial EEPROM address for<br>LSB of first word | \$00 to \$FF (8 bits)                                 | x:\$B   |

| WR_N_PAGE_SIZE | Serial EEPROM page size minus 1                | Device dependent, must be a power of 2 (-1)           | x:\$C   |

| WR_N_WRD_SZ    | word size in bytes                             | 1 for byte, 2 for 16-bit words,<br>3 for 24-bit words | x:\$D   |

| WR_N_STAT_REG  | internal use                                   |                                                       | x:\$E   |

| WR_N_COUNTER   | internal use                                   |                                                       | x:\$F   |

Note:

These addresses are determined by the assembler equates. The values correspond to those in **Appendix A** and can be changed by modifying the equates appropriately, with no additional change needed in the code.

# **Example 3-2** presents the assembly code for the WRITE\_BLOCK routine.

### Example 3-2 WRITE\_BLOCK Routine Assembly Code

```

WRITE_BLOCK

; (1) READ API DATA

#$0,r0

move

r0,x:WR_N_COUNTER ; clear counter

move

x:WR_N_SRC_ADD,r0

move

x:WR_N_DEST_ADD,b

move

x:WR_N_PAGE_SIZE,m2

#$1,r3

move

x:WR_N_WRD_SZ,m3

x:WR_N_DEST_ADD,r4

move

m2,x0

move

x0,b

and

clr

move

b,r2

; loop WRITE_PAGE until all DSP words have been transmitted

WRITE_PAGE

; Write Enable

WRITE_ENABLE

; (2) RESET SERIAL INTERFACE

SERIAL_INTERFACE_RESET

; (3) PACK OPCODE and ADDRESS

r4,a2

move

#24,a,a

#WRITE_OPCODE,a2

#8,a,a

; now we have WR N DEST ADD i

; AO and WRITE_OPCODE in Al

; (4) ASSERT CHIP SELECT

\#$4,x:M\_AAR1; set AA1 low

; (5) ACTIVATE SERIAL INTERFACE and SYNCHRONIZE

SYNCHRONIZE

bsr

```

# **Example 3-2** WRITE\_BLOCK Routine Assembly Code (Continued)

```

; (6) TRANSMIT OPCODE and ADDRESS

;-----

IF SERIAL INTERFACE=='ESSI'

; load 2nd valid byte to be

a0,x:M_TX00

movep

; TXed (address, B2)

brclr

#M RDF,x:M SSISR0,*

; wait until byte is TXed

; (opcode, B1)

movep

x:M RX0,n5

; clear RDF bit

ELSE

IF SERIAL_INTERFACE=='SCI'

#M TDRE,x:M SSR,*

; wait until byte is TXed

; (opcode, B0)

; load 2nd valid byte to be TXed

movep

a0,x:M STXH

; (address, B1)

; clean receiver

brclr

#M_RDRF,x:M_SSR,*

x:M SRXH,a1

movep

; pipeline delay

nop

ENDIF

ENDIF

; which space?

b

clr

x:WR N COUNTER, b0

а

#>$20,x0

move

x:WR_N_SRC_SPC,a

move

; is it lowercase?

cmp

#$70,a

x0,a ifge

; capitalize

sub

x:WR_N_SRC_N,x0

move

#'X',a

cmp

\#(xin_word_end+1),r5

move

_xin_word

beq

#'Y',a

cmp

\#(yin_word_end+1),r5

move

bea

yin word

move

#(_pin_word-_end+1),r5

; transmit page

; (7) GET CURRENT DSP WORD

_pin_word

p:(r0),a1

move

; case P

bra

_cont

yin word

y:(r0),a1

move

; case Y

_cont

bra

_xin_word

x:(r0),a1

move

; case X

cont

```

# **Example 3-2** WRITE\_BLOCK Routine Assembly Code (Continued)

```

; (8) GET CURRENT BYTE

r3,_cut1byte

asr

#$8,a,a

_cut1byte

(r3)+

; updates byte pointer in

move

; current DSP word

; (9) TRANSMIT ONE BYTE

IF SERIAL INTERFACE=='ESSI'

a0,x:M TX00

; load Nth valid byte to be TXed

movep

; (data, B.n)

brclr

#M RDF,x:M SSISRO,*

; wait until byte is TXed

; (address/data, B.n-1)

x:M_RX0,n5

; clear RDF bit

movep

; pipeline delay

nop

; pipeline delay

nop

IF SERIAL INTERFACE=='SCI'

brclr

#M_TDRE,x:M_SSR,*

; wait until byte is TXed

; load Nth valid byte to be TXed

movep

a0,x:M STXH

; (data, B.n)

brclr

#M RDRF,x:M SSR,*

; clean receiver

x:M SRXH,a1

movep

ENDIF

ENDIF

move

r3,a

move

(r4)+

tst

a

; current DSP word finished?

bne

_upd

; resets r3 to 1 (byte pointer)

move

(r3)+

move

(r0)+

; points to next DSP word

inc

x0,a0

move

; compare number of TXed words

a,b

cmp

; to number of DSP words

; end transaction in case all

beq

end

; DSP word have been TX

upd

(r2)+

move

; points to next in-page address

move

r2,a

tst

r5

; continues until END OF PAGE

bne

end

nop

```

# **Example 3-2** WRITE\_BLOCK Routine Assembly Code (Continued)

```

; (10) END OF PAGE

;-----

IF SERIAL INTERFACE=='ESSI'

#M_RDF,x:M_SSISR0,*

; wait until last byte is TXed

brclr

x:M_RX0,n5

; clear RDF bit

movep

b0,x:WR_N_COUNTER

; save number of TXed words

move

IF SERIAL INTERFACE=='SCI'

; wait until byte is TXed

brclr #M_TDRE,x:M_SSR,*

; (address, B1)

brclr

#M RDRF,x:M SSR,*

; clean receiver

x:M SRXH,a1

movep

; save number of TXed words

b0,x:WR N COUNTER

move

ENDIF

ENDIF

; (11) RESET SERIAL INTERFACE

SERIAL_INTERFACE_RESET

;-----

; (12) DEASSERT CHIP SELECT

;-----

#M_BAAP,x:M_AAR1

; set AA1 high

; (13) READ_STATUS_REGISTER

POLL_SR

; (14) WRITE CYCLE ENDED?

b

a

clr

x:WR_N_SRC_N,x0

clr

x:WR_N_COUNTER,b0

x0,a0

move

nop

; (15) END OF BLOCK?

cmp

a,b

; compare number of transmitted

; words to number of DSP words

WRITE PAGE

bne

nop

; RETURN

;-----

rts

```

**Example 3-3** shows a call to WRITE\_BLOCK for copying a 24-word block of 24-bit words (3-byte words) from DSP X memory, address \$204, to address \$0 of an 8-byte page Serial EEPROM.

Example 3-3 A WRITE\_BLOCK Call

```

; a WRITE BLOCK call

WR_N_SRC_N,$18

API

; 24 words

WR_N_SRC_SPC,"'x'"

API

; from X memory

API

WR_N_SRC_ADD,$204

; Block begins on address $204

API

WR_N_DEST_ADD,$0

; Block is written to address $0

API

WR_N_PAGE_SIZE,$7

; SEEPROM's page size is 8 bytes

API

WR_N_WRD_SZ,$3

; word size is 3 bytes = 24 bits

WRITE_BLOCK

; branch to WRITE_BLOCK subroutine

bsr

```

# 3.3.2 READ\_BLOCK Function

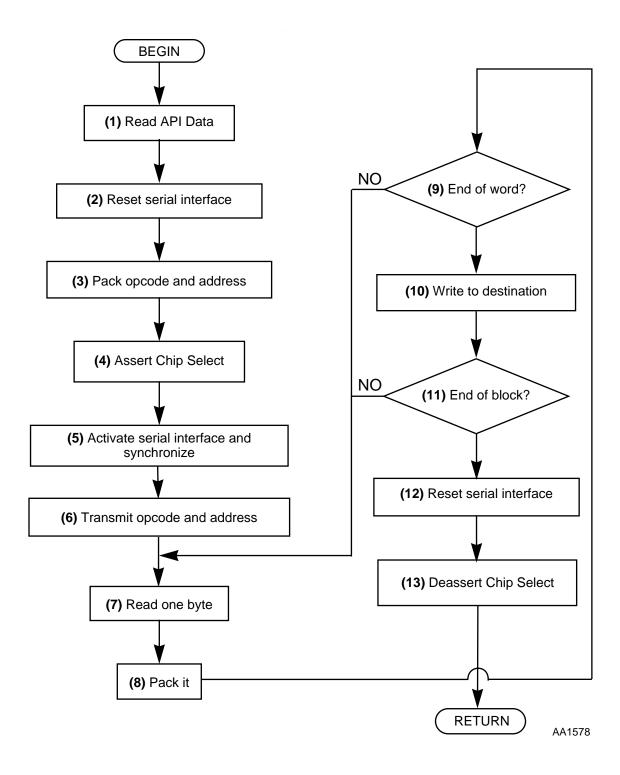

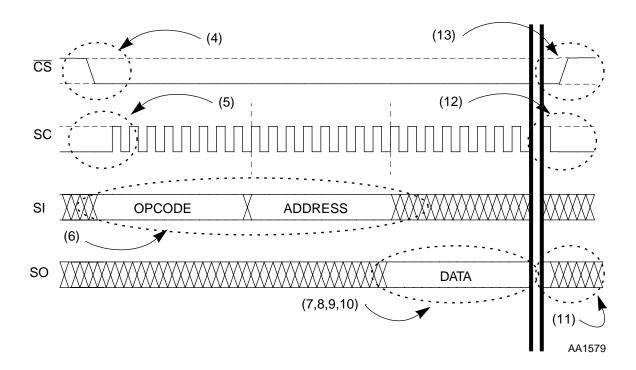

A call to READ\_BLOCK reads a block of words from Serial EEPROM to DSP memory. **Figure 3-5** shows the READ\_BLOCK function flowchart; **Figure 3-6** shows the function's timing scheme. **Figure 3-3** displays READ\_BLOCK parameters.

Figure 3-5 READ\_BLOCK Flow Chart

Figure 3-6 READ\_BLOCK Timing

Table 3-3

READ\_BLOCK Parameters

| Parameter     | Description                                      | Range                                              | API (1) |

|---------------|--------------------------------------------------|----------------------------------------------------|---------|

| RD_N_SRC_N    | Number of words to be read<br>from Serial EEPROM | 1 to 16M-words (24 bits)                           | x:\$0   |

| RD_N_SRC_ADD  | Serial EEPROM address for<br>LSB of first word   | \$00 to \$FF (8 bits)                              | x:\$1   |

| RD_N_DEST_SPC | Block destination memory space                   | X,Y or P, case insensitive                         | x:\$2   |

| RD_N_DEST_ADD | Block destination base address                   | Any mapped DSP<br>memory address                   | x:\$3   |

| RD_N_WRD_SZ   | Word size in bytes                               | 1 for byte, 2 for 16-bit words, 3 for 24-bit words | x:\$4   |

**Note:** These addresses are determined by assembler equates. The values correspond to those in **Appendix A** and can be changed by modifying the equates appropriately, with no additional change needed in the code.

**Example 3-4** shows the assembly code for the READ\_BLOCK routine.

### **Example 3-4** READ\_BLOCK Assembly Code

```

READ BLOCK

; (1) READ API DATA

clr

move

#>$20,x0

x:RD_N_SRC_ADD,a2

move

x:RD_N_DEST_ADD,r0

move

x:RD_N_DEST_SPC,b

x:RD_N_WRD_SZ,x1

; is it lowercase?

cmp

#$70,b

sub

x0,b

; capitalize

ifge

x:RD_N_SRC_N,x0

move

; (2) RESET SERIAL INTERFACE

SERIAL_INTERFACE_RESET

; (3) PACK OPCODE and ADDRESS

#24,a,a

#READ_OPCODE,a2

#8,a,a

; now we have RD N SRC ADD in A0

; and READ_OPCODE in A1

; (4) ASSERT CHIP SELECT

#$4,x:M_AAR1

; change AA1 low

; (5) ACTIVATE SERIAL INTERFACE and SYNCHRONIZE

bsr

SYNCHRONIZE

; (6) TRANSMIT OPCODE and ADDRESS

IF SERIAL_INTERFACE=='ESSI'

a0,x:M_TX00

; load 2nd valid byte to be

movep

; TXed (address, B2)

#M_RDF,x:M_SSISR0,*

brclr

; wait until byte is TXed

; (opcode, B1)

x:M_RX0,n5

; clear RDF bit

movep

#M_RDF,x:M_SSISR0,*

; wait until byte is TXed

brclr

; (address, B2)

movep x:M_RX0,n5

; clear RDF bit

```

### **Example 3-4** READ\_BLOCK Assembly Code (Continued)

```

ELSE

IF SERIAL INTERFACE=='SCI'

brclr

#M TDRE,x:M SSR,*

; wait until byte is TXed

; (opcode, B0)

; load 2nd valid byte to be

movep

a0,x:M\_STXH

; TXed (address, B1)

brclr

#M RDRF,x:M SSR,*

; clean receiver

movep

x:M SRXH,a1

nop

; pipeline delay

;-----

#M TDRE,x:M SSR,*

; wait until byte is TXed

brclr

; (address, B1)

movep

#$ff0000,x:M STXH

; keep transmitting to maintain

; clock

brclr

#M_RDRF,x:M_SSR,*

; clean receiver

x:M_SRXH,a1

movep

ENDIF

ENDIF

; which space?

;-----

#'X',b

cmp

move

\#(x-p+1),r5

_sp_end

beq

#'Y',b

cmp

move

\#(_y-_p+1),r5

_sp_end

beq

move

#$1,r5

_sp_end

; read words and write to DSP memory

do

x0, rd_n ws

; read N words

x1,_rd_bytes

; read bytes

IF SERIAL INTERFACE=='ESSI'

brclr

#M_RDF,x:M_SSISR0,*

; wait until ESSIO's receiver is

; full

; (7) READ ONE BYTE

movep

x:M_RX0,a1

ELSE.

IF SERIAL INTERFACE=='SCI'

brclr

#M TDRE,x:M SSR,*

; wait until byte is TXed

; keep transmitting to maintain

#$ff0000,x:M_STXH

movep

; clock

```

# **Example 3-4** READ\_BLOCK Assembly Code (Continued)

```

; (7) READ ONE BYTE

#M_RDRF,x:M_SSR,*

; read received byte

brclr

x:M SRXH,a1

movep

ENDIF

ENDIF

; (8) PACK IT

#16,a

#8,a,a

_rd_bytes

; (9) END OF WORD?

x1

#8,a,a

; (10) WRITE TO DESTINATION

_p

al,p:(r0)+

move

bra

_rd_end

_x

move a1,x:(r0)+

bra

_rd_end

al,y:(r0)+

move

_rd_end

nop

_rd_n_ws

; (11) END OF BLOCK?

;-----

; (12) RESET SERIAL INTERFACE

SERIAL INTERFACE RESET

; (13) DEASSERT CHIP SELECT

;-----

#M BAAP,x:M AAR1

; set AA1 high

; RETURN

```

**Example 3-5** shows a call to the READ\_BLOCK function for copying a 6-word block of 8-bit words (1-byte words) from address \$0 of a Serial EEPROM to DSP X memory, address \$104. This example actually reads the first two 24-bit words written to the Serial EEPROM in **Example 3-3** as six independent bytes that are each written on a different DSP X memory address. The LSB of the first 24-bit word written to the Serial EEPROM is read to the LSB of X:\$104, and so on.

Example 3-5 A READ\_BLOCK Call

```

; a READ BLOCK call

API

RD_N_SRC_N,$6

; 6-word block

APT

RD_N_SRC_ADD,$0

; from SEEPROM's address $0

RD N DEST SPC,"'x'"

API

; to DSP X memory

API

RD_N_DEST_ADD,$100

; at address $100

API

RD N WRD SZ,$1

; 1-byte words

bsr

READ BLOCK

```

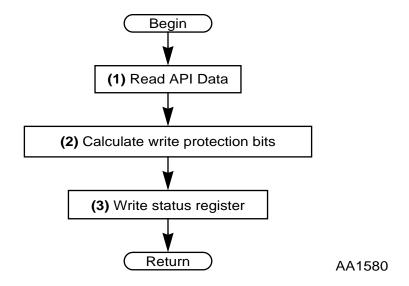

### 3.3.3 PROTECT Function

The PROTECT function protects the Serial EEPROM from writing from a given address' section to the top of the memory. A Serial EEPROM's section corresponds to one fourth of its address range. An address' section is the one to which the address to be protected belongs. **Figure 3-7** displays the PROTECT function flowchart; **Table 3-4** shows the function's parameters.

Figure 3-7 PROTECT/UNPROTECT Flow-Chart

## **Application Program Interface**

Table 3-4

PROTECT Parameters

| Parameter    | Description                               | Range                          | API (1) |

|--------------|-------------------------------------------|--------------------------------|---------|

| PRF_BASE_ADD | Serial EEPROM base address for protection | One byte, \$00 to \$FF         | x:\$10  |

| PRF_MEM_SZ   | Serial EEPROM's size in Kbits             | 1 for 1K-bits or 2 for 2K-bits | x:\$11  |

Note:

These addresses are determined by assembler equates. The values correspond to those in **Appendix A** and can be changed by modifying the equates, with no additional change needed on the code.

**Example 3-6** shows the assembly code for the PROTECT routine.

**Example 3-6** PROTECT Function Assembly Code

| 1     |                                   |

|-------|-----------------------------------|

| ;     |                                   |

| , ,   | ) READ API DATA                   |

| •     |                                   |

| clr   | a<br>b                            |

|       | #>1,y0                            |

| move  | #>\$40,a1                         |

| move  | #>\$60,a0                         |

| move  | x:PRF_MEM_SZ,b                    |

| dec   | h                                 |

| asl   |                                   |

| move  | al,xl                             |

| move  | a0,x0                             |

| clr   | a                                 |

| move  | x:PRF_BASE_ADD,al                 |

| clr   | b                                 |

| move  | #>\$3,b                           |

| ;     |                                   |

|       | ) CALCULATE WRITE PROTECTION BITS |

| =     |                                   |

|       | x1,a                              |

|       | y0,b ifge                         |

| -     | x0,a                              |

|       | y0,b ifge                         |

|       | #2,b<br>                          |

| ,     | ) WRITE STATUS REGISTER           |

|       |                                   |

|       | b1,r0                             |

|       | rO,x:WRSR DATA                    |

|       | WRITE_STATUS_REG                  |

| nop   |                                   |

| ;     |                                   |

| ; RET | IURN                              |

| ;     |                                   |

| rts   |                                   |

The following example calls the PROTECT function in order to write-protect all addresses above address \$d0 on a 2K-bit SEEPROM. The routine protects all addresses above \$d0 location's section, including the section itself—that is, all addresses above \$c0.

Example 3-7 A PROTECT Call

| ; a PROTECT call |                   |

|------------------|-------------------|

| API              | PRF_BASE_ADD,\$d0 |

| API              | PRF_MEM_SZ,\$2    |

| bsr              | PROTECT           |

### 3.3.4 UNPROTECT Function

Calling the UNPROTECT function cancels write protection for the Serial EEPROM from memory's bottom address to a given address' section. The UNPROTECT function flowchart is the same as for PROTECT, shown in **Figure 3-7**. **Table 3-5** displays the parameters of the UNPROTECT function.

Table 3-5

UNPROTECT Parameters

| Parameter     | Description                               | Range                             | API <sup>(1)</sup> |

|---------------|-------------------------------------------|-----------------------------------|--------------------|

| UPRF_BASE_ADD | Serial EEPROM base address for protection | One byte, \$00 to \$FF            | x:\$12             |

| UPRF_MEM_SZ   | Serial EEPROM's size in Kbits             | 1 for 1K-bits or<br>2 for 2K-bits | x:\$13             |

Note:

These addresses are determined by assembler equates. The values correspond to those in **Appendix A.** These values can be changed by modifying the equates appropriately, with no additional change needed in the code.

### **Application Program Interface**

**Example 3-8** shows the assembly code for the UNPROTECT routine.

## **Example 3-8** UNPROTECT Function Assembly Code

```

UNPROTECT

; (1) READ API DATA

clr

clr

b

#>1,y0

move

#>$40,a1

move

move

#>$60,a0

move

x:UPRF_MEM_SZ,b

dec

asl

b1,a,a

al,xl

move

a0,x0

move

clr

x:UPRF_BASE_ADD,a1

clr

b

#$0,b

move

; (2) CALCULATE WRITE PROTECTION BITS

x0,a

cmp

y0,b

add

iflt

cmp

x1,a

add

y0,b

iflt

lsl

#2,b

; (3) WRITE STATUS REGISTER

bl,r0

move

r0,x:WRSR_DATA

move

WRITE_STATUS_REG

bsr

; RETURN

rts

```

**Example 3-9** calls for UNPROTECT enabling a 2K-bit Serial EEPROM to be written on all addresses below address \$b0. The routine unprotects all addresses below the \$d0 location's section as well, including the section itself, that is, all addresses below \$c0.

Example 3-9 An UNPROTECT Call

```

; a UNPROTECT call

; API UPRF_BASE_ADD,$b0

API UPRF_MEM_SZ,$2

bsr UNPROTECT

```

## 3.3.5 PROTECT\_ALL Function

Calling the PROTECT\_ALL function protects the whole Serial EEPROM from being written. No parameters are needed. The function writes an adequate value to the SEEPROM Status Register, as shown in the following code.

**Example 3-10** The PROTECT\_ALL Function

```

protect_ALL

;

-----

; call WRSR with this correspondent data

;

------

move #$c,r0

move r0,x:WRSR_DATA

bsr WRITE_STATUS_REG

nop

;

; return

; rets

```

To call PROTECT\_ALL it is enough to branch to the subroutine, as **Example 3-11** shows.

Example 3-11 A PROTECT\_ALL Call

```

; a PROTECT_ALL call

; bsr PROTECT_ALL

```

## 3.3.6 UNPROTECT\_ALL Function

Calling the UNPROTECT\_ALL function cancels write protection for the whole Serial EEPROM. No parameters are needed. The function writes an adequate value to the SEEPROM Status Register, as the following code shows.

**Example 3-12** The UNPROTECT\_ALL Function

```

UNPROTECT_ALL

;-----

; call WRSR with this correspondent data

;------

move #$0,r0

move r0,x:WRSR_DATA

bsr WRITE_STATUS_REG

nop

;------

; RETURN

;-------

```

To call UNPROTECT\_ALL it is enough to branch to the subroutine, as **Example 3-13** shows.

### Example 3-13 An UNPROTECT\_ALL Call

```

;-----;

; a UNPROTECT_ALL call

;------bsr UNPROTECT_ALL

```

### 3.4 Serial EEPROM Functions

Serial EEPROMs accept one-byte serial opcodes delivering the memory basic functionality. The general Serial EEPROM complete instruction set is implemented in this application report. Part of the instruction set is achieved as a sub-set of the high-level functions described in **Section 3.2** and **Section 3.3**. Other instructions accomplished by kernel routines that serve those high-level functions are similarly available for direct call by any application.

**Table 3-6** summarizes these low-level functions and the way they work. The following paragraphs describe them. These functions are called in much the same way as the high-level functions described in **Section 3.3**, some with parameters and some without.

| Function | Description                              | Implementation           |

|----------|------------------------------------------|--------------------------|

| WREN     | Enables Serial EEPROM for writing        | Kernel: WRITE_ENABLE     |

| WRDI     | Disables Serial EEPROM for writing       | Kernel: WRITE_DISABLE    |

| RDSR     | Reads Serial EEPROM's Status<br>Register | Kernel: READ_STATUS_REG  |

| WRSR     | Programs Serial EEPROM's Status Register | Kernel: WRITE_STATUS_REG |

| WRITE    | Writes to Serial EEPROM                  | Sub-set of WRITE_BLOCK   |

| READ     | Reads from Serial EEPROM                 | Sub-set of READ_BLOCK    |

**Table 3-6** Serial EEPROM Functions

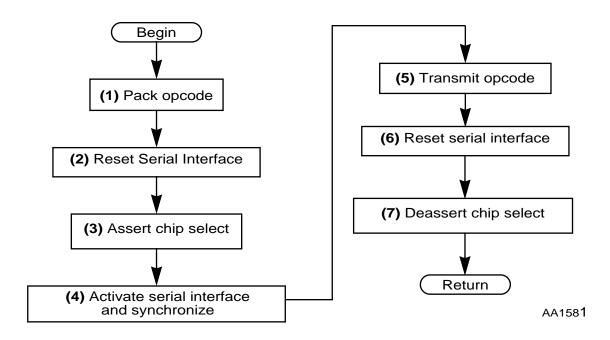

## 3.4.1 WRITE\_ENABLE and WRITE\_DISABLE Functions

The WRITE\_ENABLE and WRITE\_DISABLE functions do not require parameters. WRITE\_ENABLE prepares the Serial EEPROM for writing. It is called by higher-level functions before any programming task, data writing, or status register writing. WRITE\_DISABLE disables the Serial EEPROM for writing and is not called by any high-level function. The same routine executes both functions, as **Figure 3-8** shows.

Figure 3-8 WRITE\_ENABLE/WRITE\_DISABLE Flowchart

### **Serial EEPROM Functions**

**Example 3-14** shows the complete assembly code for the WRITE\_ENABLE/WRITE DISABLE routine.

Example 3-14 WRITE\_ENABLE/\_DISABLE Routine Assembly Code

```

WRITE ENABLE

; (1) PACK OPCODE and ADDRESS

#$0,a2

#24,a,a

move

#WREN OPCODE, a2

asr

#8,a,a

; now we have WREN OPCODE in Al

bra

endis

WRITE_DISABLE

; (1) PACK OPCODE and ADDRESS

#$0,a2

move

#24,a,a

asr

#WRDI_OPCODE,a2

move

#8,a,a

; now we have WRDI_OPCODE in Al

endis

; (2) RESET SERIAL INTERFACE

SERIAL_INTERFACE_RESET

bsr

; (3) ASSERT CHIP SELECT

#$4,x:M_AAR1

movep

; set AA1 low

; (4) ACTIVATE SERIAL INTERFACE and SYNCHRONIZE

SYNCHRONIZE

; (5) TRANSMIT OPCODE

IF SERIAL_INTERFACE=='ESSI'

jclr

#M_RDF,x:M_SSISR0,*

; wait until byte is TXed

; (opcode, B1)

movep

x:M_RX0,n5

; clear RDF bit

ELSE.

IF SERIAL_INTERFACE=='SCI'

brclr

#M TDRE,x:M SSR,*

; wait until byte is TXed

; (opcode, B0)

#$ff0000,x:M_STXH

; keep transmitting to maintain

movep

; clock

#M_RDRF,x:M_SSR,*

brclr

; clean receiver

x:M_SRXH,a1

movep

```

**Example 3-14** WRITE\_ENABLE/\_DISABLE Routine Assembly Code (Continued)

The WRITE\_ENABLE and WRITE\_DISABLE functions can be called by branching to the subroutine, with no need for parameters.

**Example 3-15** WRITE\_ENABLE/\_DISABLE Calls

```

; a WRITE_ENABLE call

; bsr WRITE_ENABLE

; a WRITE_DISABLE call

; bsr WRITE_DISABLE

```

## 3.4.2 READ\_STATUS\_REG Function

The READ\_STATUS\_REG function reads the SEEPROM Status Register and writes it on the Least Significant Byte of a given address in a given DSP memory space. **Figure 3-9** shows the READ\_STATUS\_REG function timing scheme; **Figure 3-10** displays the function's flowchart; **Table 3-7** lists the parameters of READ\_STATUS\_REG.

### **Serial EEPROM Functions**

Figure 3-9 READ\_STATUS\_REG Timing

Figure 3-10 READ\_STATUS\_REG Flow-Chart

Table 3-7

READ\_STATUS\_REG Parameters

| Parameter     | Description              | Range                         | Address <sup>1</sup> |

|---------------|--------------------------|-------------------------------|----------------------|

| RDSR_DEST_SPC | destination memory space | X,Y or P                      | x:\$5                |

| RDSR_DEST_ADD | destination address      | any mapped DSP memory address | x:\$6                |

**Note:** These addresses are determined by assembler equates. The values correspond to those in **Appendix A**. These values can be changed by modifying the equates appropriately, with no additional change needed on the code.

**Example 3-16** shows the complete assembly code for the READ\_STATUS\_REG routine.

Example 3-16 READ\_STATUS\_REG Routine Assembly Code

```

READ STATUS REG

; (1) READ API DATA

;-----

#>$20,x0

x:RDSR_DEST_ADD,r1

move

move

x:RDSR_DEST_SPC,b

move

#$70,b

; is it lowercase?

cmp

x0,b

; capitalize

; (2) RESET SERIAL INTERFACE

SERIAL_INTERFACE_RESET

; (3) PACK OPCODE

move

#RDSR OPCODE,a2

asr

#8,a,a

; now we have READ OPCODE in Al

; (4) ASSERT CHIP SELECT

#$4,x:M_AAR1

; set AA1 low

; (5) ACTIVATE SERIAL INTERFACE and SYNCHRONIZE

SYNCHRONIZE

;-----

; (6) TRANSMIT OPCODE

;______

```

### **Serial EEPROM Functions**

### Example 3-16 READ\_STATUS\_REG Routine Assembly Code (Continued)

```

IF SERIAL_INTERFACE=='ESSI'

brclr

#M RDF,x:M SSISRO,*

; wait until byte is TXed

; (opcode, B1)

x:M RX0,n5

; clear RDF bit

movep

ELSE

IF SERIAL_INTERFACE=='SCI'

brclr

#M TDRE,x:M SSR,*

; wait until byte is TXed

; (opcode, BO)

#$ff0000,x:M_STXH

; keep transmitting to maintain

movep

; clock

#M RDRF,x:M SSR,*

; clean receiver

brclr

x:M SRXH,a1

movep

; pipeline delay

nop

ENDIF

ENDIF

; which space?

#'X',b

cmp

move

#(_x-_p+1),r5

beq

_sp_end

#'Y',b

move

\#(_y-_p+1),r5

sp end

bea

#$1,r5

move

_sp_end

; read SR and write to DSP memory

; (7) READ STATUS REGISTER

IF SERIAL_INTERFACE=='ESSI'

brclr

#M RDF,x:M SSISRO,*

; wait until ESSIO's receiver is

; full

movep

x:M RX0,a1

ELSE

IF SERIAL_INTERFACE=='SCI'

brclr

#M RDRF,x:M SSR,*

; read received byte

x:M SRXH,a1

movep

ENDIF

ENDIF

```

## **Example 3-16** READ\_STATUS\_REG Routine Assembly Code (Continued)

```

; (8) PACK IT

; (9) WRITE TO DESTINATION

bra

_p

al,p:(r1)+

move

_rd_end

bra

_x

move

a1,x:(r1)+

_rd_end

bra

_У

a1,y:(r1)+

move

rd end

; (10) RESET SERIAL INTERFACE

SERIAL INTERFACE RESET

; (11) DEASSERT CHIP SELECT

\#M_BAAP,x:M_AAR1

; set AA1 polarity high

rts

```

**Example 3-17** shows an example of a READ\_STATUS\_REG call. The call reads the SEEPROM's Status Register and writes its value to DSP X data memory at address \$300.

## Example 3-17 READ\_STATUS\_REG Call

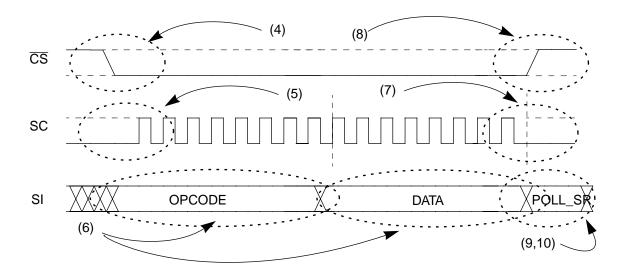

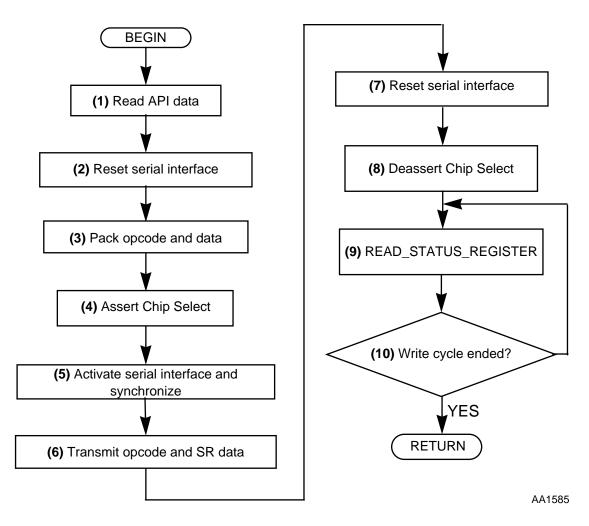

## 3.4.3 WRITE\_STATUS\_REG Function

The WRITE\_STATUS\_REG function programs the SEEPROM Status Register with a given value. **Figure 3-11** displays the WRITE\_STATUS\_REG timing scheme; **Figure 3-12** shows the flowchart; **Table 3-8** lists the parameters of WRITE\_STATUS\_REG.

Table 3-8

WRITE\_STATUS\_REG Parameters

| Parameter | Description                                         | Range                                   | API   |

|-----------|-----------------------------------------------------|-----------------------------------------|-------|

| WRSR_DATA | Data to be written into the SEEPROM Status Register | One byte, at LSB of DSP memory location | x:\$7 |

**Note:** These addresses are determined by assembler equates. The values correspond to those in **Appendix A** and can be changed by modifying the equates appropriately, with no additional change needed on the code.

Figure 3-11 WRITE\_STATUS\_REG Timing

Figure 3-12 WRITE\_STATUS\_REG Flow-Chart

### **Serial EEPROM Functions**

**Example 3-18** presents the assembly code for the WRITE\_STATUS\_REG routine.

### **Example 3-18** WRITE\_STATUS\_REG Assembly Code

```

WRITE_STATUS_REG

; Write Enable

WRITE ENABLE

; (1) READ API DATA

clr

clr a move x:WRSR_DATA,al

; (2) RESET SERIAL INTERFACE

SERIAL_INTERFACE_RESET

; (3) PACK OPCODE and DATA

move #WRSR_OPCODE,a2

#8,a,a

; now we have WRSR_DATA in A0

asr

; and WRSR_OPCODE in A1

; (4) ASSERT CHIP SELECT

#$4,x:M_AAR1

; change AA1 polarity, in order

movep

; to set it low

; (5) ACTIVATE SERIAL INTERFACE and SYNCHRONIZE

bsr

SYNCHRONIZE

; (6) TRANSMIT OPCODE and SR DATA

IF SERIAL_INTERFACE=='ESSI'

; load 2nd valid byte to be

movep

a0,x:M TX00

; TXed (SR data, B2)

brclr

#M_RDF,x:M_SSISR0,*

; wait until byte is TXed

; (opcode, B1)

movep

x:M_RX0,n5

; clear RDF bit

brclr

#M_RDF,x:M_SSISR0,*

; wait until byte is TXed

;(SR data, B2)

x:M_RX0,n5

; clear RDF bit

movep

```

## Example 3-18 WRITE\_STATUS\_REG Assembly Code (Continued)

```

ELSE

IF SERIAL INTERFACE=='SCI'

brclr

#M TDRE,x:M SSR,*

; wait until byte is TXed; (opcode, B0)

movep

a0,x:M STXH

; load 2nd valid byte to be TXed

; (data, B1)

#M_RDRF,x:M_SSR,*

brclr

; clean receiver

x:M_SRXH,a1

movep

; pipeline delay

nop

#M_TDRE,x:M_SSR,*

brclr

; wait until byte is TXed

; (data, B1)

brclr

#M RDRF,x:M SSR,*

; clean receiver

movep

x:M_SRXH,a1

ENDIF

ENDIF

; (7) RESET SERIAL INTERFACE

SERIAL_INTERFACE_RESET

; (8) DEASSERT CHIP SELECT

#M_BAAP,x:M_AAR1

; change AA1 polarity, in order

; to set it high

; (9) READ STATUS REGISTER

POLL_SR

; (10) WRITE CYCLE ENDED?

rts

```

**Example 3-19** shows an example of a WRITE\_STATUS\_REG call, which writes a value of \$f2 to the SEEPROM Status Register.

## Example 3-19 A WRITE\_STATUS\_REG Call

### 3.4.4 WRITE Function

The typical Serial EEPROM presents a WRITE function that enables writing to the SEEPROM from one byte up to one memory page. The WRITE function is thus a subset of the WRITE\_BLOCK function described in **Section 3.3.1 WRITE\_BLOCK Function** on page 3-3. With appropriate calls to WRITE\_BLOCK, you can run any WRITE function. For example, the following call writes one byte to address \$10 in the Serial EEPROM.

**Example 3-20** Single Byte WRITE Call

| API | WR N SRC N,\$1     |                                       |

|-----|--------------------|---------------------------------------|

|     |                    | ; The data to be written is           |

| API | WR_N_SRC_SPC,"'x'" |                                       |

| API | WR_N_SRC_ADD,\$200 | ; taken from DSP memory x:\$200       |

| API | WR_N_DEST_ADD,\$10 |                                       |

| API | WR_N_PAGE_SIZE,\$3 | ; The used SEEPROM has a 4-byte; page |

| API | WR_N_WRD_SZ,\$1    |                                       |

| bsr | WRITE_BLOCK        |                                       |

For writing a page, the call is as follows:

**Example 3-21** Single Page WRITE Call

```

API

WR_N_SRC_N,$4

; The page is 4-byte long

WR N SRC SPC, "'x'"

API

WR N SRC ADD, $200

APT

API

WR N DEST ADD, $10

; $10 is base address of a page

API

WR_N_PAGE_SIZE,$3

APT

WR_N_WRD_SZ,$1

bsr

WRITE_BLOCK

```

### 3.4.5 READ Function

As with the WRITE function, a READ function is available on the typical Serial EEPROM, and it permits reading of any number of bytes from the SEEPROM. Calling the READ\_BLOCK function as detailed in **Section 3.3.2** runs the READ function. Since READ\_BLOCK can read 8-,16- and 24-bit words, the Serial EEPROM READ function is a subset of READ\_BLOCK. A one-byte SEEPROM READ access is performed, for example, with the following call:

**Example 3-22** One-Byte SEEPROM READ Call

| API | RD_N_SRC_N,\$1      | ; read one byte               |

|-----|---------------------|-------------------------------|

| API | RD_N_SRC_ADD,\$0    | ; from SEEPROM address \$0    |

| API | RD_N_DEST_SPC,"'y'" | ; write to DSP memory y:\$100 |

| API | RD_N_DEST_ADD,\$100 |                               |

| API | RD_N_WRD_SZ,\$1     | ; read byte mode              |

| bsr | READ_BLOCK          |                               |

|     |                     |                               |

## 3.5 Auxiliary Routines

Other available auxiliary routines are SERIAL\_INTERFACE\_RESET, SYNCHRONIZE, and POLL\_SR.

### 3.5.1 Serial Interface Reset

The SERIAL\_INTERFACE\_RESET routine puts the serial interface, either ESSI or SCI, in the Personal Reset state while programming the relevant control registers to initial values. See **Example 3-23**:

**Example 3-23** SERIAL\_INTERFACE\_RESET Code

```

SERIAL_INTERFACE_RESET

IF SERIAL_INTERFACE=='ESSI'

#DEFAULT_PCR,x:M_PCRC

#DEFAULT PDR,x:M PDRC

movep

#DEFAULT_PRR,x:M_PRRC

movep

#DEFAULT_CRA,x:M_CRA0

movep

#DEFAULT_CRB,x:M_CRB0

movep

ELSE

IF SERIAL INTERFACE=='SCI'

#DEFAULT_PCRE,x:M_PCRE

movep

movep #DEFAULT_PDRE,x:M_PDRE

movep #DEFAULT_PRRE,x:M_PRRE

movep

#DEFAULT_SCR,x:M_SCR

#DEFAULT SCCR,x:M SCCR

movep

#ACTV_PCRE_1,x:M_PCRE

; avoid initial 1 DSP clock

movep

; spike at SCLK

ENDIF

ENDIF

rts

```

### **Auxiliary Routines**

## 3.5.2 Synchronize Serial Interface

The SYNCHRONIZE routine activates the serial interface in a synchronized way in order to guarantee timing constraints of the SPI protocol. **Example 3-24** shows the routine's assembly listing:

Example 3-24 SYNCHRONIZE Code

```

SYNCHRONIZE

IF SERIAL INTERFACE=='ESSI'

#$ffffff,x:M TX00

; load first byte to be TXed (dummy, B0)

movep

movep

#ACTV_PCR_1,x:M_PCRC

; enable ESSI

#ACTV CRB,x:M CRB0

; activate ESSI's TX and RX

movep

#M TFS,x:M SSISRO,*

; wait until frame status bit occurs

brclr

a1,x:M TX00

; load 1st valid byte to be TXed

movep

; (opcode, B1)

#M_RDF,x:M_SSISR0,*

; wait until byte is TXed; (dummy, B0)

brclr

; clear RDF bit

x:M_RX0,n5

movep

#(CLOCK RATIO/2)

rep

nop

; enable SCK and STD

movep

#ACTV PCR 2,x:M PCRC

FLSE

IF SERIAL_INTERFACE=='SCI'

movep

#ACTV PCRE 2,x:M PCRE

; enable SCI

; load 1st valid byte to be TXed

movep

al,x:M STXH

; (opcode, B0)

; activate SCI's TX and RX

#ACTV SCR,x:M SCR

movep

ENDIF

ENDIF

rts

```

# 3.5.3 Poll Status Register

The POLL\_SR routine polls the SEEPROM Status Register's READY bit to determine the end of a Serial EEPROM write cycle. The routine is called by the WRITE\_BLOCK routine at the end of each page write of the Serial EEPROM. It is also called by the WRITE\_STATUS\_REGISTER routine after it writes to the SEEPROM Status Register. **Example 3-25** shows the routine's assembly listing.

### Example 3-25 POLL\_SR Code

| POLL_SR |      |                     |

|---------|------|---------------------|

|         | move | #>WR_N_STAT_REG,a   |

|         | move | a,x:RDSR_DEST_ADD   |

|         | move | #>'X',a             |

|         | move | a,x:RDSR_DEST_SPC   |

|         | jsr  | READ_STATUS_REG     |

|         | move | #WR_N_STAT_REG,r1   |

|         | jset | #\$0,x:(r1),POLL_SR |

|         | rts  |                     |

|         |      |                     |

## 3.5.4 Read Modify Write Operation

The following example performs a READ\_MODIFY\_WRITE operation on a 10-word block in a 1K-bit SEEPROM, followed by write protection of the block. The modification part of the operation switches the first word and the second, the third and the fourth, and so on until the ninth and tenth words.

Example 3-26 READ\_MODIFY\_WRITE Operation

```

; Read the block from SEEPROM address $00 to Y memory, address $100

API

RD_N_SRC_N,$a

RD_N_SRC_ADD,$d0

API

; from SEEPROM address $c0

; write to DSP memory y:$100

API

RD_N_DEST_SPC,"'y'"

API

RD N DEST ADD, $100

API

RD_N_WRD_SZ,$3

; read 3-byte words

bsr

READ BLOCK

; Modify the block

move #$100,r0

#$5,_end_modify

do

y:(r0)+,a0

move

y:(r0)-,a1

a1,y:(r0)+

move

move

a0,y:(r0)+

_end_modify

; Write-unprotect the block

UPRF_BASE_ADD,$d0

UPRF MEM SZ,$1

bsr

UNPROTECT

```

### **ESSI Timing Considerations**

**Example 3-26** READ\_MODIFY\_WRITE Operation (Continued)

```

; Write back the block

API WR_N_SRC_N,$a

API WR_N_SRC_SPC,"'y'"

API WR_N_SRC_ADD,$100

WR_N_DEST_ADD,$d0

API

WR N PAGE SIZE,$3

API

API

WR N WRD SZ,$3

WRITE_BLOCK

; Write-protect the block

API

PRF BASE ADD,$d0

API

PRF MEM SZ,$1

PROTECT

bsr

; stop

nop

nop

nop

stop

nop

nop

nop

```

# 3.6 ESSI Timing Considerations

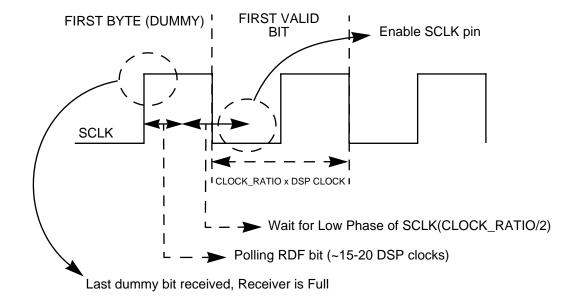

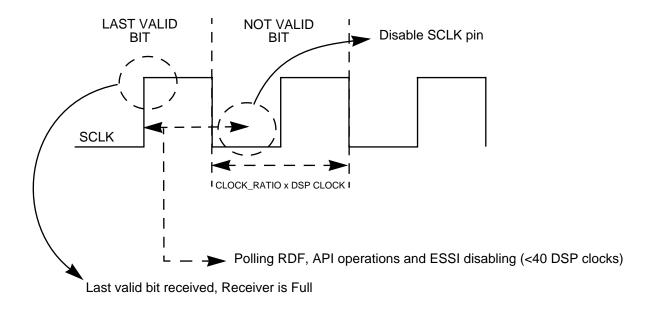

A set of polling routines synchronize ESSI SCLK, enabling with the first valid bit of Serial Data Out, emulating a gated clock. **Figure 3-13** and **Figure 3-14** show Synchronization events for enabling and disabling the ESSI in the worst case (a READ BLOCK call).

To guarantee this synchronization scheme, the ratio between the SEEPROM period and DSP period should be greater than 40, which guarantees the gated clock when the ESSI SCLK is enabled, while avoiding extra forbidden clocks after the last valid bit on the ESSI SCLK is disabled.

NOTE: Diagram out of scale

AA1586

Figure 3-13 ESSI Enabling Synchronization

NOTE: Diagram out of scale

AA1587

Figure 3-14 ESSI Disabling Synchronization

**ESSI Timing Considerations**

# 4 ESSI and SCI Configuration

This section details how the serial interface, whether ESSI or SCI, is configured.

## 4.1 ESSI Configuration

The following paragraphs describe ESSI programming.

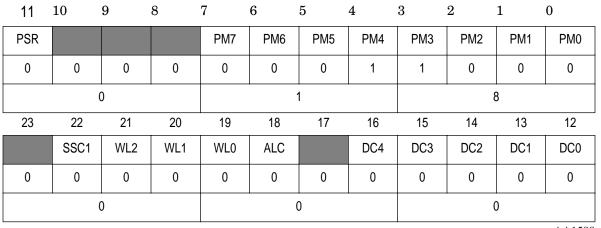

## 4.1.1 ESSI Control Register A

ESSI Control Register A (CRA) is initialized with a value of **\$000018**, corresponding to the following configuration

AA1588

Figure 4-2 Control Register A

- PM7-PM0 and PSR: Prescale Modulus Select and Prescale Range bits are configured so that a 1MHz serial clock is generated for a 400 MHz chip.

- DC4-DC0: Frame Rate Divider Control bits are cleared providing continuous data transfer in Normal mode.

- ALC: the Alignment Control bit is cleared, so that transmitted and received bytes would be aligned to bit 23 in the corresponding data registers.

- WL2-WL0: Word Length Control bits are programmed for 8-bit words.

- SSC1: this bit is irrelevant to the application discussed in this report.

## 4.2.1 ESSI Control Register B

ESSI Control Register B (CRB) is initialized with a value of \$001920. A value of a value of \$031920 activates the ESSI.

| 11   | 10   | 9    | 8    | 7    | 6    | 5      | 4      | 3    | 2    | 1   | 0   |

|------|------|------|------|------|------|--------|--------|------|------|-----|-----|

| CKP  | FSP  | FSR  | FSL1 | FSL0 | SHFD | SCKD   | SCD2   | SCD1 | SCD0 | OF1 | OF0 |

| 1    | 0    | 0    | 1    | 0    | 0    | 1      | 0      | 0    | 0    | 0   | 0   |

|      | 9    |      |      | 2    |      |        | 0      |      |      |     |     |

| 23   | 22   | 21   | 20   | 19   | 18   | 17     | 16     | 15   | 14   | 13  | 12  |

| REIE | TEIE | RLIE | TLIE | RIE  | TIE  | RE     | TE0    | TE1  | TE2  | MOD | SYN |

| 0    | 0    | 0    | 0    | 0    | 0    | 0 -> 1 | 0 -> 1 | 0    | 0    | 0   | 1   |

|      | 0    |      |      |      | 0 -  | > 3    |        |      |      | 1   |     |

AA1589

Figure 4-3 Control Register B

These values correspond to the following configurations:

- OF0 and OF1: Output Flags bits are not used in this implementation.

- SCD2-SCD0: Serial Control Direction bits are irrelevant for this application.

- SCKD: The internal clock is used, so the Clock Source Direction bit is set.

- SHFD: Data is shifted in and out MSB first, so the Shift Direction bit is cleared.

- FSL1-FSL0: Frame Sync Length bits are set to 10 (bit-length) according to the ESSI specification for continuous periodic data transfers.

- FSR and FSP: Frame Sync Relative Timing and Frame Sync Polarity bits are irrelevant for the current implementation.

- CKP: The Clock Polarity bit is set so that data is clocked out on the falling edge of bit clock and latched in on its rising edge.

- SYN: ESSI works in its synchronous mode, so the Synchronous/Asynchronous bit is set.

- MOD: Clearing the ESSI Mode Select bit selects Normal mode for the application.

- TE2 and TE1: Transmitters 2 and 1 are not used, so corresponding Transmit Enable bits are zeroed.

- TE0: the Transmit 0 Enable bit is set whenever transmitter 0 is to be used.

- RE: the Receive Enable bit is set whenever the ESSI receiver is to be used.

- REIE, TEIE, RLIE, TLIE, RIE and TIE: No interrupt is used on the application, so all the interrupt enabling bits are cleared.

## 4.3.1 ESSI Port Control, Direction and Data Registers

The ESSI Port Control Register (PCRC), Port Direction Register (PRRC) and Port Data Register (PDRC) mirror the pin functionality, direction, and state required in every task performed throughout the application.

**Table 4-1** condenses all the combinations used.

Table 4-1 PCRC, PRRC and PDRC Values

|                            | Pin Number                                  | P5     | P4     | <b>P3</b> | P2     | P1     | P0     | H<br>E |

|----------------------------|---------------------------------------------|--------|--------|-----------|--------|--------|--------|--------|

|                            | ESSI<br>Function                            | STD    | SRD    | SCK       | SC2    | SC1    | SC0    | X<br>A |

| D<br>E                     | Function (PCRC)                             | GPIO   | GPIO   | GPIO      | GPIO   | GPIO   | GPIO   | 00     |

| F<br>A<br>U                | Direction (PRRC)                            | OUTPUT | OUTPUT | OUTPUT    | OUTPUT | OUTPUT | OUTPUT | 3F     |

| L<br>T                     | Data<br>(PDRC)                              | 1      | 1      | 0         | 1      | 1      | 1      | 37     |

| A<br>C<br>T<br>I<br>V<br>E | Function<br>(PCRC)<br>Enable ESSI           | GPIO   | ESSI   | GPIO      | GPIO   | GPIO   | GPIO   | 20     |

|                            | Function<br>(PCRC)<br>Enable SCK<br>and STD | ESSI   | ESSI   | ESSI      | GPIO   | GPIO   | GPIO   | 38     |

## 4.4 SCI Configuration

The following paragraphs describe SCI programming.

## 4.4.1 SCI Control Register

The SCI Control Register (SCR) is initialized with a value of **\$008008**. A value of **\$008308** simultaneously enables both the receiver and transmitter 1.

AA1591

Figure 4-5 SCI Control Register

These values correspond to the following configuration:

- REIE, STIR, TMIE, TIE, RIE and ILIE: no interrupt is used in this implementation, so these bits are programmed with zero.

- SCKP: Negative Clock Polarity is used, so this bit is set to one.

- TE: the enable bit is set when the SCI transmitter is to be used.

- RE: the Receive Enable bit is set when the SCI receiver is to be used.

- WOMS, RWU, WAKE and SBK: These bits are irrelevant in the current application.

- SSFTD: the Most Significant Bit is shifted first, so this bit should be set to one.

- WDS2-WDS0: the Word Select Bits are all zeroed, configuring SCI to its Synchronous Mode (Mode 0).

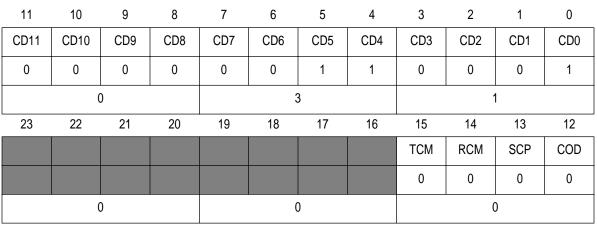

# 4.5.1 SCI Clock Control Register

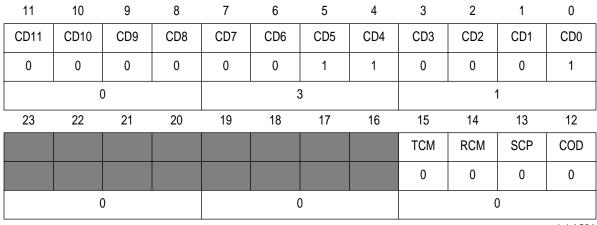

A value of \$000031 initializes the SCI Clock Control Register (SCCR).

AA1591

Figure 4-6 SCI Clock Control Register

This value corresponds to the following configuration:

- TCM and RCM: An internal clock is used, so the Transmitter Clock Mode and Receiver Clock Mode bits are zeroed.

- SCP: SCI Clock Prescaler divides by one, so this bit is set to zero.

- COD: this bit is irrelevant in Synchronous mode, since the output divider is fixed at divide by 2.

- CD11-CD0: the Clock Divider bits are programmed to **\$31**, providing a 1/400 ratio between the serial clock and the DSP clock.

# 4.6.1 SCI Port Control, Direction, and Data Registers

The SCI Port Control Register (PCRE), Port Direction Register (PRRE), and Port Data Register (PDRE) mirror the pin functionality, direction, and state required in every task performed throughout the application.

# **SCI Configuration**

Table 4-1 condenses all the combinations used.

Table 4-1

PCRE PRRE and PDRE Values

|                                 | Pin Number                                | P2     | P1     | P0     | HEXA |  |

|---------------------------------|-------------------------------------------|--------|--------|--------|------|--|

|                                 | ESSI Function                             | SCLK   | TXD    | RXD    |      |  |

| D<br>E<br>F<br>A<br>U<br>L<br>T | Function (PCRE)                           | GPIO   | GPIO   | GPIO   | 0    |  |

|                                 | Direction (PRRE)                          | OUTPUT | OUTPUT | OUTPUT | 7    |  |

|                                 | Data<br>(PDRE)                            | 0      | 1      | 1      | 3    |  |

| A<br>C<br>T                     | Function<br>(PCRE)<br>Enable SCI          | GPIO   | GPIO   | SCI    | 1    |  |

| I<br>V<br>E                     | Function<br>(PCRE)<br>Enable SCLK and TXD | SCI    | SCI    | SCI    | 7    |  |

## 5 Customization

This section explains how to customize the routines provided in the earlier sections.

## 5.1 Code Optimization

Much of the assembly code provided in Section 3 is consumed in processing API parameters and in running API routines. This includes DSP memory space selection, Serial EEPROM page management, word packing, and so on. Although it gives great transparency and flexibility, the code needed for performing these features consumes DSP cycles and program memory, which can be optimized by customizing all the API functions for the specific user's application. Below is a list of some features that can be customized to reduce DSP memory and processing cycles. The numbers in parentheses address to correspondent steps on the WRITE\_BLOCK routine where the applicable changes should be made. Refer to the function code in **Section 3.3.1**.

- Using a fixed DSP memory space permits the DSP memory space processing from any function to be cut (1,6-7).

- Using a fixed word size or/and fixed SEEPROM addresses permits reduce packing routines (1,3,8,9).

- Isolated use of some functions may permit you to avoid branching to common routines (1-2,5,11,13).

- If you do not need to write large blocks, the page management mechanism can be extracted (1,7,8,10,14,15).

- In case some functions that are called one after another, SERIAL\_INTERFACE\_RESET can be ignored at the beginning of any function after the second one (2).

## 5.2 Larger-Capacity Serial EEPROM

The application discussed in this report provides a one-byte addressing mechanism that covers any Serial EEPROM up to 2K-bit density. Serial EEPROMs of greater density use an additional address line for accessing memory locations higher than \$FF. This additional address bit is usually one of the unused bits of the one-byte opcode and is device-dependent. If your application needs to access larger-density Serial EEPROMs, you should modify some code in order to fit the present addressing routines to the selected device. We suggest modifying the code on its highest level, at the API subroutines call, with minor low-level routine changes for opcode and address determination.

Larger-Capacity Serial EEPROM

# **Appendix A** Assembly Equates

This Appendix presents the assembly code and defined equates for this application.

### A.1 EQUATES

In addition to the I/O and Interrupt Equates of the respective DSP56300 derivatives, the AC-link application assembly code uses the equates defined below.

## A.1.1 General Equates

```

; General

; General

; Main Program Starting Address

CLOCK_RATIO equ $190 ; ratio (EEPROM period / DSP

; period = 1/400)

SERIAL_INTERFACE equ "ESSI" ; This equate should determine

; which Serial Interface will

; be used on the connection. Set

; it to "SCI" in case it is

; intended to be used as Serial

; Interface

```

# A.1.2 ESSI Configuration Equates

| ;           |              |          |                        |

|-------------|--------------|----------|------------------------|

| ;           | ESSI EQUATES |          |                        |

| ;           |              |          |                        |

| DEFAULT_PCR | equ          | \$000000 |                        |

| DEFAULT_PRR | equ          | \$00003F |                        |

| DEFAULT_PDR | equ          | \$000037 |                        |

| DEFAULT_CRA | equ          | \$000018 |                        |

| DEFAULT_CRB | equ          | \$001920 |                        |

| ;           |              |          |                        |

| ACTV_CRB    | equ          | \$031920 | ; TX & RX enabled      |

| ACTV_PCR_1  | equ          | \$000020 | ; ESSI activation      |

| ACTV_PCR_2  | equ          | \$000038 | ; SCK and STD enabling |

# A.1.3 SCI Configuration Equates

| ;                |        |          |                             |

|------------------|--------|----------|-----------------------------|

| ; SCI E          | QUATES |          |                             |

| ;                |        |          |                             |

| DEFAULT_PCRE     | equ    | \$000000 |                             |

| DEFAULT_PRRE equ |        | \$000007 |                             |

| DEFAULT_PDRE     | equ    | \$000003 |                             |

| DEFAULT_SCR      | equ    | \$008008 |                             |

| DEFAULT_SCCR     | equ    | \$000031 | ; 400MHz (400 : 8 : 1 : 50) |

|                  |        |          | i = 1MHz                    |

| ;                |        |          |                             |

| ACTV_SCR         | equ    | \$008308 | ; TX & RX enabled           |

| ACTV_PCRE _1 equ |        | \$000001 |                             |

| ACTV_PCRE _2 equ |        | \$000007 |                             |

# A.1.4 SEEPROM Opcodes

| ;           |                |      |

|-------------|----------------|------|

| ;           | EEPROM OPCODES |      |

| ;           |                |      |

| WRSR_OPCODE | equ            | \$01 |

| WRITE_OPCOD | E equ          | \$02 |

| READ_OPCODE | equ            | \$03 |

| WRDI_OPCODE | equ            | \$04 |

| WREN_OPCODE | equ            | \$06 |

| RDSR_OPCODE | equ            | \$05 |

# A.1.5 API

| ;                                          |                                          |              |                   |                                  |               |  |  |

|--------------------------------------------|------------------------------------------|--------------|-------------------|----------------------------------|---------------|--|--|

|                                            | API                                      |              |                   |                                  |               |  |  |

| ,                                          |                                          |              | <br>DOM           |                                  |               |  |  |

|                                            | ; RD_N: Read N words from EEPROM         |              |                   |                                  |               |  |  |

| RD_N_SRC_N                                 | $\epsilon$                               | equ          | \$0               | ; number of words                | to be read    |  |  |

|                                            |                                          |              |                   | ; from SEEPROM                   |               |  |  |

| RD_N_SRC_ADD                               | €                                        | equ          | \$1               | ; SEEPROM address                | for MSB byte  |  |  |

|                                            |                                          |              |                   | ; of first word                  |               |  |  |

| RD_N_DEST_SP                               | С ∈                                      | -            | \$2               | ; Destination mem                | ory space     |  |  |

| RD_N_DEST_AD                               | D e                                      | e <b>q</b> u | \$3               | ; Destination mem                | ory address   |  |  |

| RD_N_WRD_SZ                                | e                                        | equ          | \$4               | ; word size em by                | tes           |  |  |

| ;; RDSR : Read STATUS REGISTER from EEPROM |                                          |              |                   |                                  |               |  |  |

| RDSR_DEST_SP                               |                                          | equ          |                   |                                  |               |  |  |

| RDSR_DEST_AD                               | D e                                      | equ          | \$6               |                                  |               |  |  |

| ; WRSR :                                   | ;; Wrsr: Write STATUS REGISTER to EEPROM |              |                   |                                  |               |  |  |