Order this data sheet by MC6805S2/D

Advance Information

# 8-Bit Microcomputers

MC6805S2 MC6805S3 MC68705S3

This document contains information on a new product. Specifications and information herein are subject to change without notice.

| Introduction                                                   | 1  |

|----------------------------------------------------------------|----|

| Signal Description,<br>Memory, CPU, and Registers              | 2  |

| Timers                                                         | 3  |

| Serial Peripheral Interface                                    | 4  |

| Self-Check, Resets, Clock<br>Generator Options, and Interrupts | 5  |

| Input/Output Ports and<br>Analog-to-Digital Converter          | 6  |

| Software and<br>Instruction Set                                | 7  |

| Electrical Specifications                                      | 8  |

| Ordering Information                                           | 9  |

| Mechanical Data                                                | 10 |

| MC6805S3                                                       | Α  |

| MC68705S3                                                      | В  |

| MC6805S2/MC6805S3 Emulation                                    | С  |

| 1           | Introduction                                                   |

|-------------|----------------------------------------------------------------|

| 2           | Signal Description,<br>Memory, CPU, and Registers              |

| 3           | Timers                                                         |

| 4           | Serial Peripheral Interface                                    |

| 5           | Self-Check, Resets, Clock<br>Generator Options, and Interrupts |

| 6           | Input/Output Ports and Analog-to-Digital Converter             |

| 7           | Software and Instruction Set                                   |

| 8           | Electrical Specifications                                      |

| 9           | Ordering Information                                           |

| <b>%</b> 10 | Mechanical Data                                                |

| <b>7</b> A  | MC6805S3                                                       |

| <b>о</b> в  | MC68705S3                                                      |

| С           | MC6805S2/MC6805S3 Emulation                                    |

#### **PREFACE**

This document describes the MC6805S2, MC6805S3, and MC68705S3 Microcomputer Unit (MCU) devices which are part of the M6805 Family of MCU devices. This preface provides a brief overview of the three devices. In addition to the overview descriptions, a quick comparison summary of the overall block diagrams, and memory map diagrams unique to the individual MCU device are provided on foldout sheets located at the rear of this document.

The organization of this document is such that the MC6805S2 MCU device is described throughout **Sections 1 through 10**. Information common to all three devices are also contained in these sections. The appendices contain unique/specific information applicable to the MC6805S3 MCU and MCC68705S3 EPROM MCU devices.

#### **DEVICE DESCRIPTIONS**

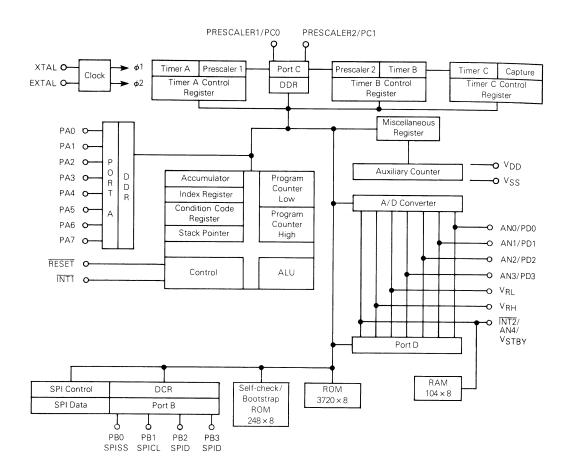

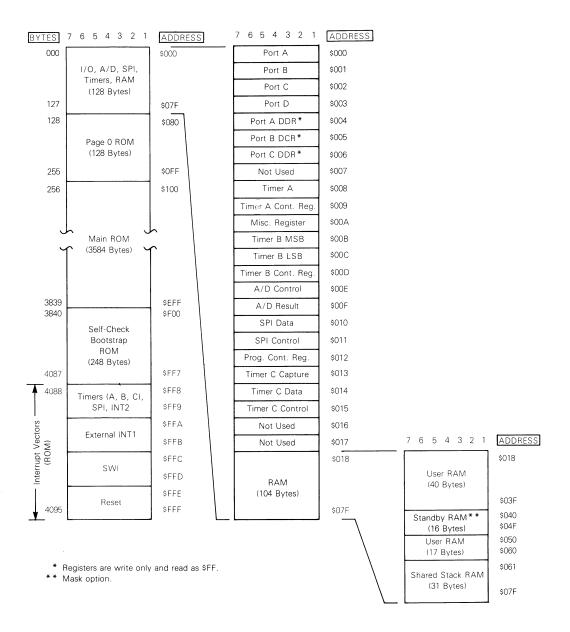

The MC6805S3 MCU device is available for users who require the features of the MC6805S2, but read additional ROM, RAM, and timer. The MC6805S3 device is similar to the MC6805S2 device with several exceptions. These exceptions include 3720 user ROM bytes (3712 user bytes and eight inverrupt vector bytes), 104 RAM bytes, and an additional timer. Information throughout this occument pertaining to the MC6805S2 MCU is also applicable to the MC6805S3 MCU. Difference information applicable to the MC6805S3 MCU is provided in **Appendix A** of this document.

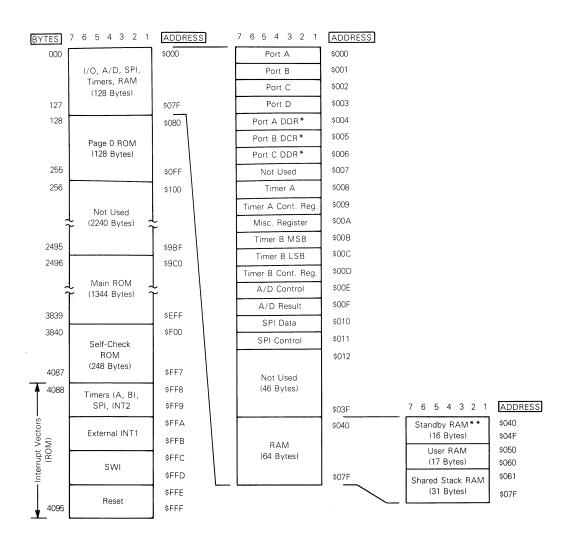

▶ e MC68705S3 EPROM MCU device is an erasable programmable read-only memory (EPROM) Persion of the MC6805S2/MC6805S3 MCU devices and is used to emulate either of these devices in low volume applications. The MC68705S3 device is similar to the MC6805S2 device with several exceptions. These exceptions include 3752 user EPROM bytes (3744 user bytes and eight interrupt victor bytes), 104 RAM bytes, 216 bytes of bootstrap ROM firmware for EPROM programming, and an additional timer circuitry. Information throughout this document pertaining to the MC6805S2 NICU is also applicable to the MC68705S3 EPROM MCU. Difference information applicable to the MC68705S3 EPROM MCU is provided in Appendix B of this document. Emulation information is provided in Appendix C of this document.

### **OVERALL SUMMARY OF DEVICES**

The following paragraphs provide an overall summary of the unique features (differences) between the MC6805S2, MC6805S3, and MC68705S3 devices. These features vary slightly between devices and are as follows:

| <u>FEATURES</u>   | MC6805S2 | MC6805S3 | MC68705S3 |

|-------------------|----------|----------|-----------|

| (EP)ROM bytes     | 1480     | 3720     | 3752      |

| RAM bytes         | 64       | 104      | 104       |

| Standby RAM bytes | 16*      | 16*      | 16        |

| Timers            | 3        | 4        | 4         |

<sup>\*</sup> Denotes standby RAM mask option.

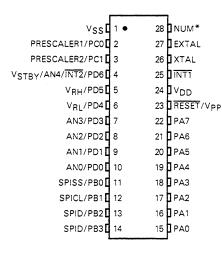

The above differences are shown in the block and memory map summary (comparison) diagrams which are located on foldout pages at the end of this document. All three MCU devices are 28-pin devices with similar pin assignments. The only pin assignment exception pertains to the MC68705S3 RESET/Vpp pin (pin 23) which is used for both resetting and inputting the Vpp programming voltage. The corresponding pin on the other two devices is used strictly for resetting purposes.

The electrical characteristics of the  $\overline{RESET}/VPP$  (pin 23) and  $VSTBY/AN4/\overline{INT2}/PD6$  (pin 4) pins of the MC68705S3 are different than those of the MC6805S2/MC6805S3. Users should refer to the emulation limitations described in Appendix C for a detailed explanation of the electrical characteristic differences before emulating either MC6805S2 or MC6805S3 devices with the MC68705S3 device.

### TABLE OF CONTENTS

| Paragraph<br>Number                                                                                                                                                                                       | Title                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|

|                                                                                                                                                                                                           | Section 1                                                                                                                                                                                                                                                                                                                                                                                                                           |                                         |  |  |  |

|                                                                                                                                                                                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         |  |  |  |

| 1.1<br>1.2<br>1.3<br>1.4                                                                                                                                                                                  | General Hardware Features Software Features User Selectable Options                                                                                                                                                                                                                                                                                                                                                                 | 1-1<br>1-2<br>1-3<br>1-3                |  |  |  |

| 0                                                                                                                                                                                                         | Section 2                                                                                                                                                                                                                                                                                                                                                                                                                           |                                         |  |  |  |

|                                                                                                                                                                                                           | Signal Description, Memory, CPU, and Registers                                                                                                                                                                                                                                                                                                                                                                                      |                                         |  |  |  |

| 2.1<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.2<br>2.3<br>2.4<br>2.4.1<br>2.4.2<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>1<br>2.4.5.1<br>2.4.5.2<br>2.4.5.3<br>2.4.5.4<br>2.4.5.5 | Signal Description  VCC and VSS. INT1 and INT2  XTAL and EXTAL.  PRESCALER 1/PC0 and PRESCALER 2/PC1  RESET.  Input/Output Lines (PA0-PA7, PB0-PB3, PC0-PC1, and PD0-PD6).  NUM (Non User Mode)  Memory  Central Processing Unit  Registers.  Accumulator (A)  Index Register (X).  Program Counter (PC)  Stack Pointer (SP)  Condition Code Register (CC)  Half Carry (H)  Interrupt (I)  Negative (N)  Zero (Z)  Carry/Borrow (C) | 2-1 2-1 2-1 2-1 2-1 2-1 2-2 2-2 2-2 2-2 |  |  |  |

| 0                                                                                                                                                                                                         | Section 3                                                                                                                                                                                                                                                                                                                                                                                                                           |                                         |  |  |  |

| -                                                                                                                                                                                                         | Timers                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         |  |  |  |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2<br>3.3                                                                                                                                                              | Timer A  Direct Loading  Asynchronous External Event Loading  Auto-Loading  Timer A Control Register  Timer B                                                                                                                                                                                                                                                                                                                       | 3-2<br>3-3<br>3-3<br>3-3<br>3-5         |  |  |  |

vii

# TABLE OF CONTENTS (Continued)

| Paragraph<br>Number | Title                                                        | Page<br>Number |  |  |

|---------------------|--------------------------------------------------------------|----------------|--|--|

| 3.4                 | Timer B Control and Status Register                          | 3-7            |  |  |

| 3.5                 | Prescaler 1                                                  | 3-8            |  |  |

| 3.6                 | Prescaler 2                                                  | 3-8            |  |  |

| 3.7                 | Auxiliary Counter                                            | 3-8            |  |  |

|                     | Section 4                                                    |                |  |  |

|                     | Serial Peripheral Interface (SPI)                            |                |  |  |

| 4.1                 | Introduction                                                 |                |  |  |

| 4.2                 | SPI Terminology                                              |                |  |  |

| 4.2.1               | Clock Mastership                                             | . 4-4          |  |  |

| 4.2.2               | Data Mastership                                              |                |  |  |

| 4.2.3               | SPI Transaction Mode                                         |                |  |  |

| 4.2.4               | SPI Deselect Mode                                            |                |  |  |

| 4.2.5               | SPI Active Mode                                              |                |  |  |

| 4.2.6               | SPI Idle Mode                                                | . 4-4          |  |  |

| 4.3                 | SPI Control and Status Register                              |                |  |  |

| 4.4                 | SPI Data Register                                            |                |  |  |

| 4.5                 | SPI Divide-by-Eight Counter                                  | . 4-9          |  |  |

| 4.6                 | SPI Operation                                                |                |  |  |

| 4.7                 | Start Bit Operation                                          | 4-12           |  |  |

| 4.8                 | Address and Data Field Separation                            | 4-14           |  |  |

| 4.9                 | Data Field Only Operation                                    | 4-14           |  |  |

| 4.10                | Data Arbitration                                             |                |  |  |

| 4.11                | Clock Arbitration                                            | 4-17           |  |  |

| 4.11.1              | Clock Arbitration via Slave Select Input Line                |                |  |  |

| 4.11.2              | Clock Arbitration via Serial Peripheral Interface Clock Line | 4-17           |  |  |

| 4.12                | Slave Select Input Operation                                 | 4-19           |  |  |

| 4.12.1              | Slave Select Input Actions During Master Mode                | 4-19           |  |  |

| 4.12.2              | Slave Select Input Actions During Slave Mode                 |                |  |  |

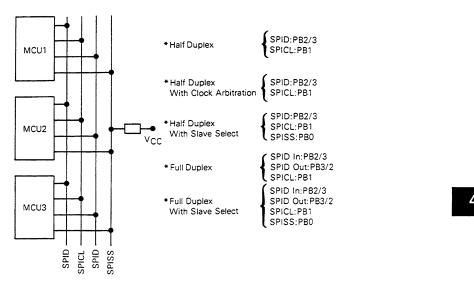

| 4.13                | SPI Operating Modes                                          |                |  |  |

| 4.13.1              | One-Wire — Autoclocked Mode                                  |                |  |  |

| 4.13.2              | Two-Wire Half-Duplex Mode                                    | 4-23           |  |  |

| 4.13.3              | Two-Wire Half-Duplex Mode with Clock Arbitration             | 4-23           |  |  |

| 4.13.4              | Three-Wire Half-Duplex Mode with Slave Select Input          | 4-23           |  |  |

| 4.13.5              | Three-Wire Full-Duplex Mode                                  | 4-24           |  |  |

| 4.13.6              | Three-Wire Full-Duplex Mode with Clock Arbitration           | 4-24           |  |  |

| 4.13.7              | Four-Wire Full-Duplex Mode with Slave-Select Input           | 4-24           |  |  |

|                     | Section 5                                                    |                |  |  |

|                     | Self-Check, Resets, Clock Generator Options, and Interrupts  |                |  |  |

| 5.1                 | Self-Check                                                   | 5-1            |  |  |

| 5 1 1               | RAM Self-Check Subroutine                                    | 5-2            |  |  |

viii

# TABLE OF CONTENTS (Continued)

| Paragraph<br>Number | Title                                              |                    |  |  |

|---------------------|----------------------------------------------------|--------------------|--|--|

| 5.1.2               | ROM Checksum Subroutine                            | 5-2<br>5-2         |  |  |

| 5.1.3<br>5.1.4      | Timer Self-Check Subroutine                        | 5-2<br>5-2         |  |  |

| 5.1.4               | Resets                                             | 5-3                |  |  |

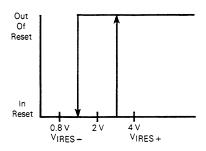

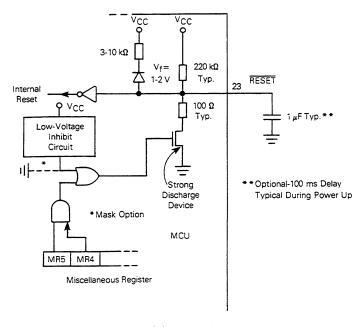

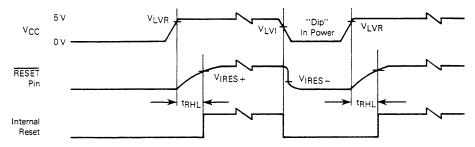

| 5.2.1               | Power-On Reset (POR)                               | 5-4                |  |  |

| 5.2.2               | External Reset Input                               | 5-4                |  |  |

| 5.2.3               | Low Voltage Inhibit (LVI)                          | 5-4                |  |  |

| 5.2.4               | Forced Reset                                       | 5-5                |  |  |

| 5.2.5               | Reset Initialization                               | 5-5                |  |  |

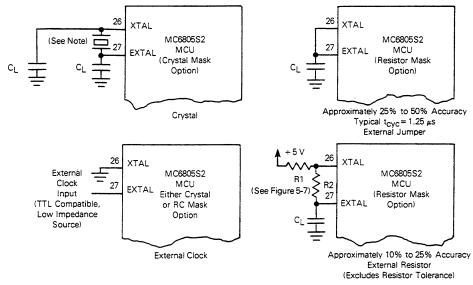

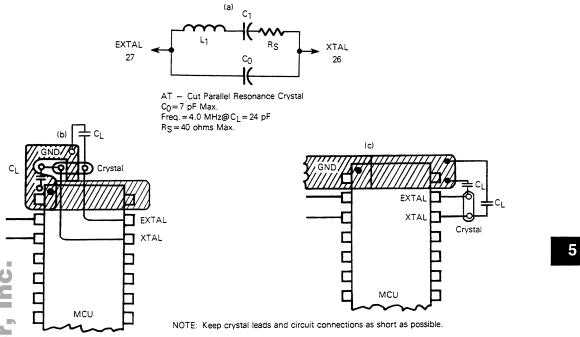

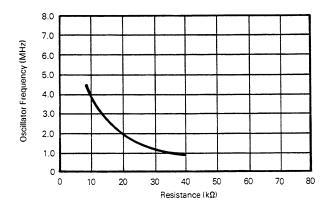

| 5.3                 | Internal Clock Generator Options                   | 5-5                |  |  |

| 5. <b>4</b>         | Interrupts                                         |                    |  |  |

|                     | Section 6                                          |                    |  |  |

|                     | Input/Output Ports and Analog-to-Digital Converter | 0.1                |  |  |

| 6.1                 | Input/Output                                       | 6-1                |  |  |

| <del></del>         | Port B Toggle Capability                           |                    |  |  |

| 6.3<br>6.4<br>6.5   | Port B Data Control Register                       |                    |  |  |

| 5.4                 | Port A and C Data Direction Registers              |                    |  |  |

| <b>5</b> 5          | Miscellaneous Register                             | -                  |  |  |

| ô                   | Analog-to-Digital Converter (A/D)                  | 0-0                |  |  |

|                     | Section 7                                          |                    |  |  |

| 0                   | Software and Instruction Set                       |                    |  |  |

| <b>2</b> 1          | Software                                           | 7-1                |  |  |

| 1.1                 | Bit Manipulation                                   |                    |  |  |

| 1.2                 | Addressing Modes                                   |                    |  |  |

| 7.1.2.1             | Immediate                                          | 7-2                |  |  |

| 1.2.2               | Direct                                             |                    |  |  |

| 7.1.2.3             | Extended                                           |                    |  |  |

| 7.1.2.4             | Relative                                           |                    |  |  |

| 1.2.5               | Indexed, No Offset                                 |                    |  |  |

| 71.2.6              | Indexed, 8-Bit Offset                              |                    |  |  |

| 71.2.7              | Indexed, 16-Bit Offset                             |                    |  |  |

| 7,1.2.8             | Bit Set/Clear                                      |                    |  |  |

| 7.1.2.9             | Bit Test and Branch                                |                    |  |  |

| 7,1.2.10            | Inherent                                           |                    |  |  |

| 7 2                 | Instruction Set                                    |                    |  |  |

| 7.2.1               | Register/Memory Instructions                       |                    |  |  |

| 7.2.2               | Read-Modify-Write Instructions                     |                    |  |  |

| 7.2.3               | Branch Instructions                                |                    |  |  |

| 7.2.4               | ·                                                  |                    |  |  |

| 7.2.5               | Control Instructions                               | . / <del>-</del> / |  |  |

# TABLE OF CONTENTS (Continued)

| Paragraph<br>Number                           | Title                                                                                                                                                                             |                                 |  |  |  |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|--|

| 7.2.6<br>7.2.7                                | Alphabetical Listing                                                                                                                                                              |                                 |  |  |  |

|                                               | Section 8                                                                                                                                                                         |                                 |  |  |  |

|                                               | Electrical Specifications                                                                                                                                                         |                                 |  |  |  |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7 | Maximum Ratings Thermal Characteristics Power Considerations Electrical Characteristics Switching Characteristics. A/D Converter Characteristics. Port Electrical Characteristics | 8-1<br>8-2<br>8-2<br>8-3<br>8-3 |  |  |  |

|                                               | Section 9                                                                                                                                                                         |                                 |  |  |  |

|                                               | Ordering Information                                                                                                                                                              |                                 |  |  |  |

| 9.1<br>9.2<br>9.3<br>9.4<br>9.5               | Flexible Disks  EPROMs  Verification Media  ROM Verification Units (RVUs)  Ordering Information                                                                                   | 9-1<br>9-2<br>9-2               |  |  |  |

|                                               | Section 10                                                                                                                                                                        |                                 |  |  |  |

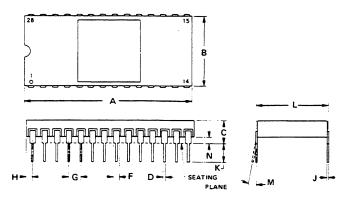

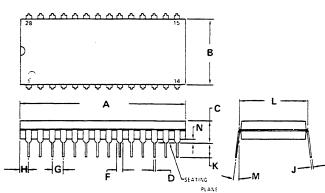

|                                               | Mechanical Data                                                                                                                                                                   |                                 |  |  |  |

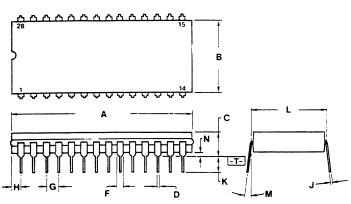

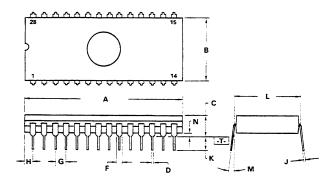

| 10.1                                          | Pin Assignment                                                                                                                                                                    | 10-1                            |  |  |  |

| 10.2                                          | Package Dimensions                                                                                                                                                                | 10-2                            |  |  |  |

|                                               | Appendix A                                                                                                                                                                        |                                 |  |  |  |

|                                               | MC6805S3                                                                                                                                                                          |                                 |  |  |  |

| A.1                                           | Introduction                                                                                                                                                                      |                                 |  |  |  |

| A.1.1                                         | Features                                                                                                                                                                          |                                 |  |  |  |

| A.1.2<br>A.2                                  | Block Diagram                                                                                                                                                                     |                                 |  |  |  |

| A.2<br>A.2.1                                  | Signal Description, Memory, CPU, and Registers                                                                                                                                    |                                 |  |  |  |

| A.2.1<br>A.2.2                                | PRESCALER1/PC0 and PRESCALER2/PC1                                                                                                                                                 | A-3                             |  |  |  |

| A.2.2<br>A.3                                  | Memory                                                                                                                                                                            | A-3<br>A-3                      |  |  |  |

| A.3.1                                         | Timer C.                                                                                                                                                                          | A-3<br>A-3                      |  |  |  |

| A.3.1.1                                       | Control Register.                                                                                                                                                                 | A-3<br>A-6                      |  |  |  |

| A.3.1.2                                       | Clock Source                                                                                                                                                                      |                                 |  |  |  |

| A.3.1.3                                       | Capture Latch                                                                                                                                                                     | A-8                             |  |  |  |

| A.3.1.4                                       | Timer Interrupt                                                                                                                                                                   | A-8                             |  |  |  |

| A.3.1.5                                       | Capture Interrupt                                                                                                                                                                 |                                 |  |  |  |

| A.3.1.6                                       | Capture Edge Control                                                                                                                                                              |                                 |  |  |  |

# TABLE OF CONTENTS (Concluded)

| <sup>a</sup> ragraph<br>Number                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|--|--|

| A.3.1.7<br>A.3.2<br>A.3.3<br>A.3.4<br>A.4<br>A.4.1<br>A.4.2<br>A.4.3                                                                     | Capture Source Port B Toggle Source Port B Toggle Capability Interrupts  Self-Check ROM Checksum Subroutine. Analog-to Digital Converter Self-Check Timer Self-Check Subroutine                                                                                                                                                                                               | A-8<br>A-8<br>A-8<br>A-10<br>A-10<br>A-10<br>A-10                                |  |  |  |  |

|                                                                                                                                          | Appendix B<br>MC68705S3                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |  |  |  |  |

| B.1<br>B.1<br>B.2<br>B.2<br>B.2<br>B.2<br>B.2<br>B.2<br>B.3<br>B.2<br>B.3<br>B.3<br>B.3<br>B.3<br>B.3<br>B.3<br>B.3<br>B.3<br>B.3<br>B.3 | Introduction Features Block Diagram  Signal Description, Memory, CPU, and Registers PRESCALER1/PC0 and PRESCALER2/PC1 RESET/VPP VSTBY/AN4/INT2/PD6 Memory.  Timers Mask Option Register Programming Control Register Electrical Specifications Electrical Characteristics Programming Operation Electrical Characteristics Mechanical Data Pin Assignments Package Dimensions | B-1<br>B-3<br>B-3<br>B-3<br>B-3<br>B-5<br>B-5<br>B-6<br>B-7<br>B-7<br>B-8<br>B-8 |  |  |  |  |

| S                                                                                                                                        | Appendix C                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |  |  |  |  |

|                                                                                                                                          | MC6805S2 and MC6805S3 Emulation Introduction                                                                                                                                                                                                                                                                                                                                  | C-1<br>C-2<br>C-2<br>C-3<br>C-3<br>C-4                                           |  |  |  |  |

### LIST OF ILLUSTRATIONS

| Figure<br>Number                                                                                                    | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page<br>Number                                                                                            |

|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 1-1                                                                                                                 | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-2                                                                                                       |

| 2-1<br>2-2<br>2-3                                                                                                   | MC6805S2 Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-4                                                                                                       |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7                                                                       | Timer A and B Block Diagram. Timer A . Timer A Control Register. Timer A Operation. Timer B . Timer B Control Register. Auxiliary Counter Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-2<br>3-2<br>3-4<br>3-6<br>3-6                                                                           |

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11<br>4-12<br>4-13<br>4-14<br>4-15<br>4-16 | Serial Peripheral Interface (SPI).  SPI Operation (Example: Clock Slave Mode)  SPI Clock (Active Transaction)  SPI Control Register Operation  SPI Clock Idle Level Definition  SPI Start Bit Definition  SPI Stop Bit Definition  SPI Address and Data Field Separation (Reception)  SPI Data Arbitration Timing Diagram  Clock Arbitration via Clock Line Timing  Clock Arbitration via Slave Select Input — Master Mode  Clock Arbitration via Slave Select Input — Slave Mode  SPI NRZ Operation (Transmit) Timing  SPI NRZ Operation (Receive) Timing  Daisy Chain/Cascade Organization  SPI Operation Bus Organization | 4-5<br>4-6<br>4-7<br>4-12<br>4-13<br>4-13<br>4-15<br>4-16<br>4-18<br>4-20<br>4-21<br>4-22<br>4-22<br>4-24 |

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7                                                                       | Self-Check Connections.  Typical Reset Schmitt Trigger Hysteresis Reset Circuit.  Power and Reset Timing.  Power-Up Reset Delay Circuit.  Clock Generator Options.  Crystal Motional Arm Parameters and Suggested PC Board Layout.                                                                                                                                                                                                                                                                                                                                                                                           | 5-3<br>5-3<br>5-4<br>5-4<br>5-6                                                                           |

# LIST OF ILLUSTRATIONS (Continued)

| Figure<br>Number                               | Title                                                                                                                                                                                                                                                        | Page<br>Number                   |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

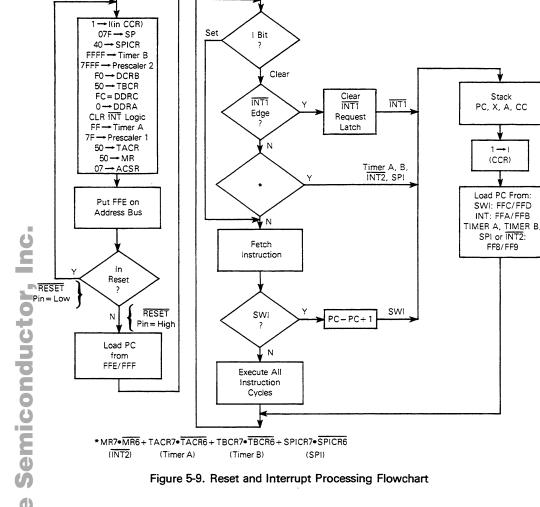

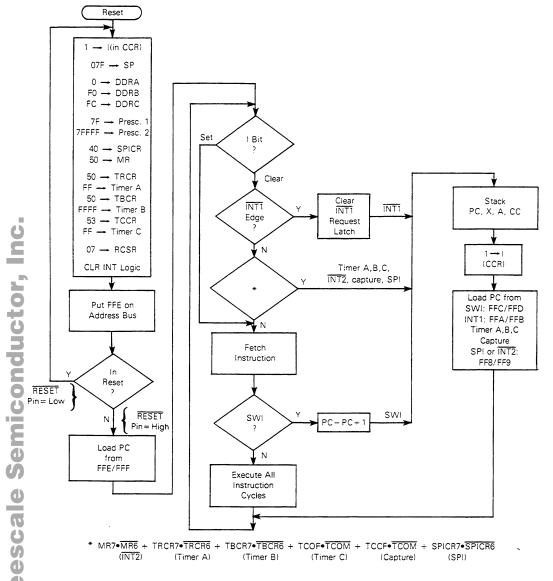

| 5-8<br>5-9<br>5-10<br>5-11                     | Typical Frequency Selection for Resistor Oscillator Option  Reset and Interrupt Processing Flowchart  Interrupt Timing                                                                                                                                       | 5-9<br>5-10                      |

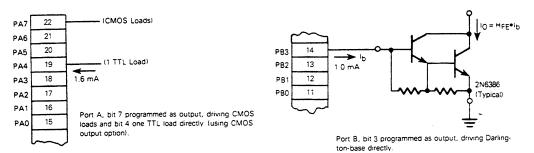

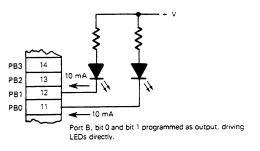

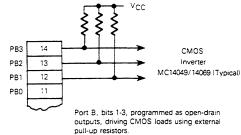

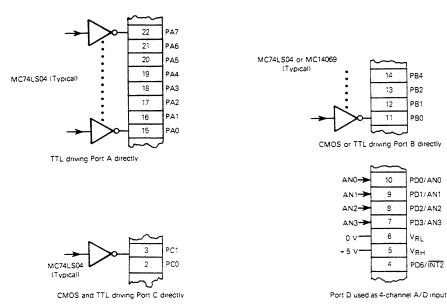

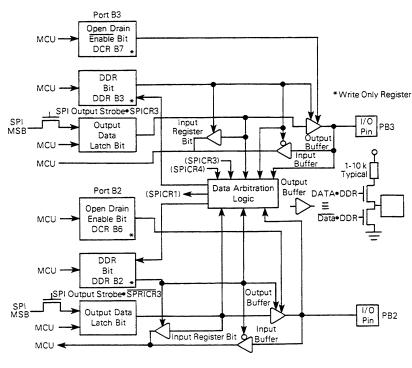

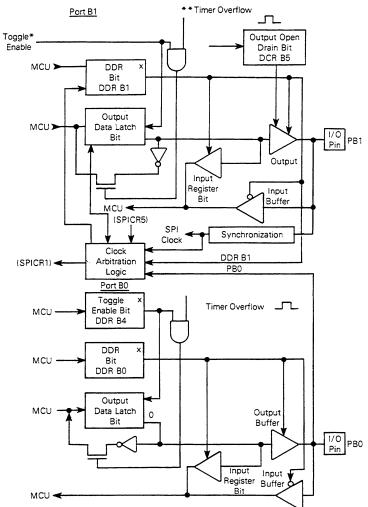

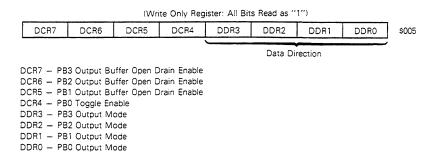

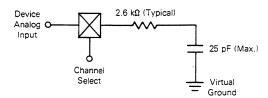

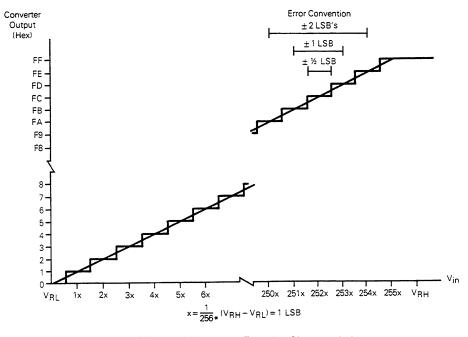

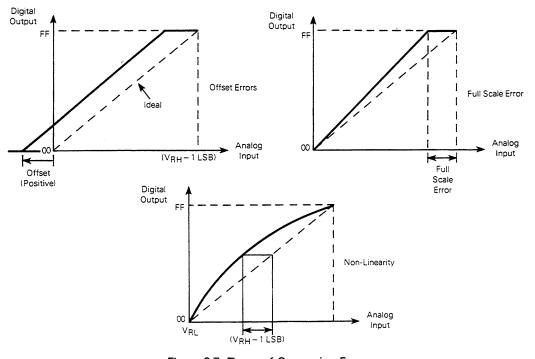

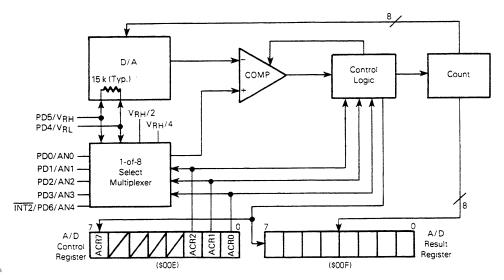

| 6-1<br>6-2<br>6-3<br>6-4<br>5-5<br>\$-6<br>5-7 | Typical Port I/O Circuitry.  Typical Port Connections.  Port B Configuration  Port B Data Control Register.  Effective Analog Input Impedance (During Sampling Only)  Ideal Converter Transfer Characteristic  Types of Conversion Errors  A/D Block Diagram | 6-3<br>6-4<br>6-6<br>6-9<br>6-10 |

| 7-1                                            | Bit Manipulation Example                                                                                                                                                                                                                                     | 7-1                              |

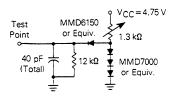

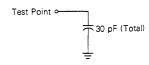

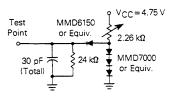

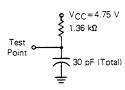

| 3-1<br>3-2<br>3-3<br>3-4                       | TTL Equivalent Test Load (Port B)  CMOS Equivalent Test Load (Port A)  TTL Equivalent Test Load (Ports A and C)  Open-Drain Equivalent Test Load (PB1, PB2, and PB3)                                                                                         | 8-5<br>8-5                       |

| A-1<br>A-2<br>A-3<br>A-4                       | MC6805S3 Microcomputer Block Diagram  MC6805S3 Memory Map  Timer A, B, and C Block Diagram  Reset and Interrupt Processing Operation                                                                                                                         | A-4<br>A-5                       |

| B-1<br>B-2                                     | MC68705S3 Microcomputer Block Diagram                                                                                                                                                                                                                        |                                  |

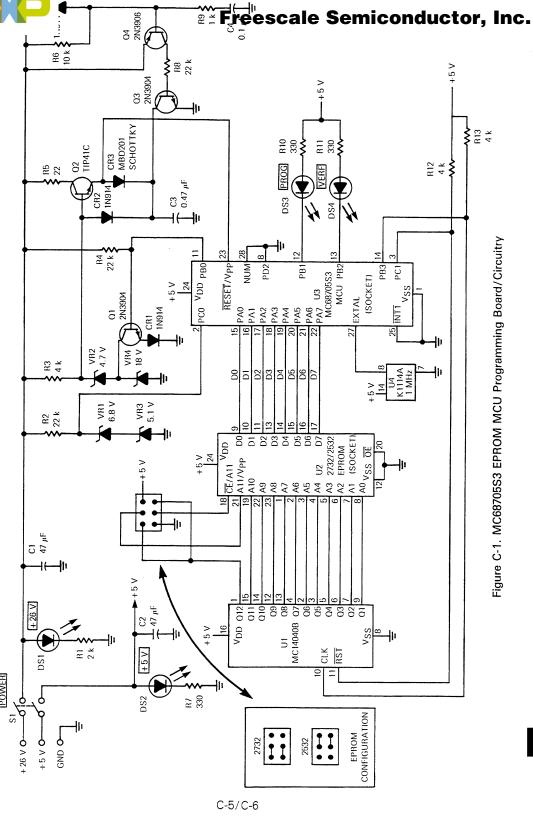

| C-1                                            | MC68705S3 MCU EPROM Programming Board/Circuitry                                                                                                                                                                                                              | C-5                              |

### LIST OF TABLES

| Table<br>Number                        | Title                                                                                                                                              | Page<br>Number           |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 4-1<br>4-2                             | SPI Operation                                                                                                                                      | _                        |

| 5-1                                    | Interrupt Priorities                                                                                                                               | 5-8                      |

| 6-1<br>6-2                             | Digital Input/Output Ports                                                                                                                         |                          |

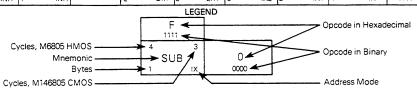

| 7-1<br>7-2<br>7-3<br>7-4<br>7-5<br>7-6 | Register/Memory Instructions Read-Modify-Write Instructions Branch Instructions Bit Manipulation Instructions Control Instructions Instruction Set | 7-5<br>7-6<br>7-7<br>7-7 |

| 7-7                                    | M6805 Family Instruction Set Opcode Map                                                                                                            |                          |

K

# SECTION 1 INTRODUCTION

This document describes the MC6805S2, MC6805S3, and MC68705S3 Microcomputer Unit (MCU) devices which are part of the M6805 Family of 8-bit MCU devices. The organization of this document is such that the MC6805S2 MCU device is described throughout sections 1 through 10. Information common to all three devices are also contained in these sections. The appendices contain unique/specific information applicable to the MC6805S3 MCU and MC68705S3 EPROM MCU devices.

### 1.1\_GENERAL

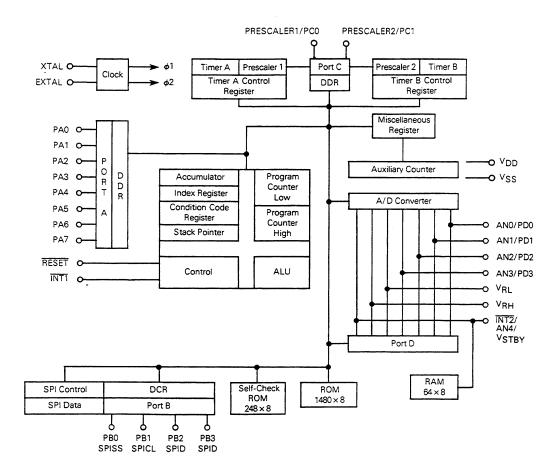

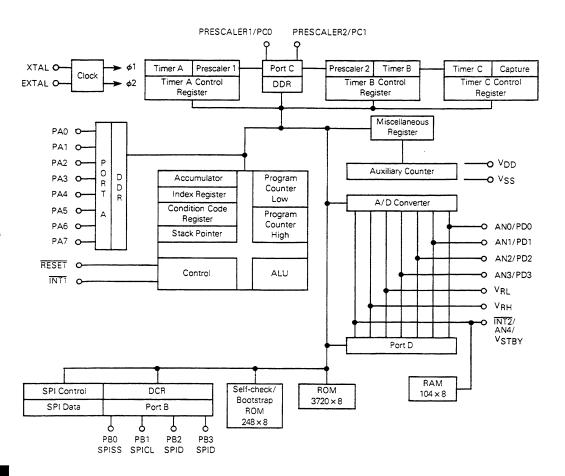

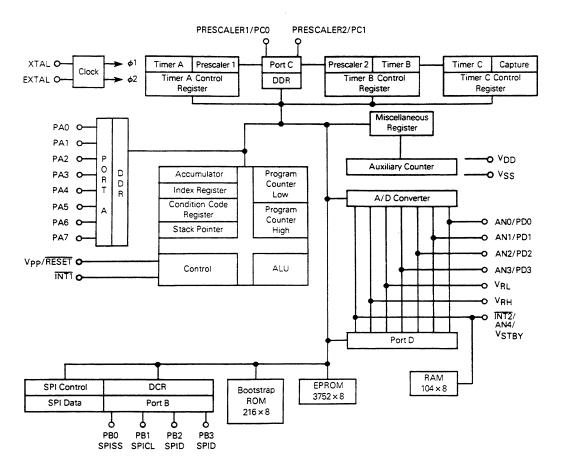

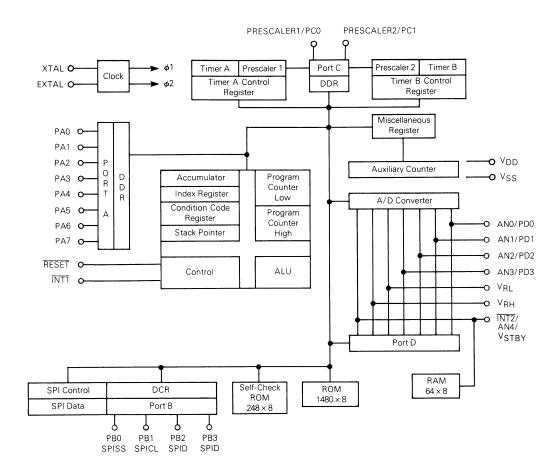

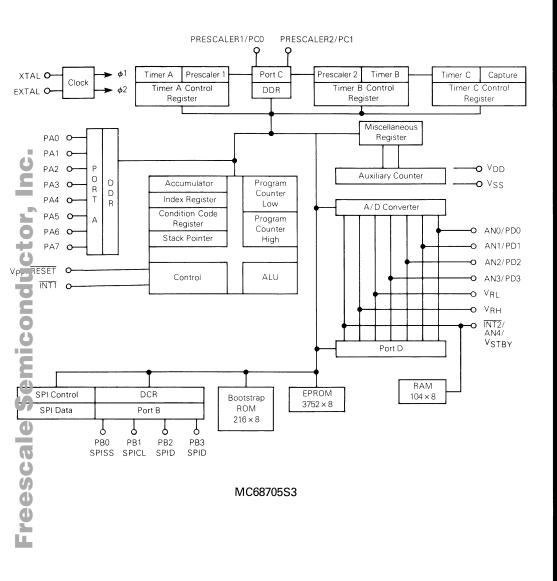

The MC6805S2 MCU device (shown in Figure 1-1) contains a CPU, on-chip clock, ROM, RAM, I/ 4-channel 8-bit analog-to-digital (A/D) converter, three timers, two programmable prescalers, and a serial peripheral interface. It is designed for the user who needs an economical microcomputer with the proven capabilities of the M6800-based instruction set.

Tr. MC6805S3 MCU device is available for users who require the features of the MC6805S2, but need additional ROM, RAM, and timer. The MC6805S3 device is similar to the MC6805S2 device with several exceptions. These exceptions include 3720 user ROM bytes (3712 user bytes and eight incurrupt vector bytes), 104 RAM bytes, and an additional timer. Information throughout this document pertaining to the MC6805S2 MCU is also applicable to the MC6805S3 MCU. Difference in ormation applicable to the MC6805S3 MCU is provided in Appendix A of this document.

The MC68705S3 EPROM MCU device is an erasable programmable read-only memory (EPROM) value of the MC6805S2/MC6805S3 MCU devices and is used to emulate either of these devices in 'two volume applications. The MC68705S3 device is similar to the MC6805S2 device with several exceptions. These exceptions include 3752 user EPROM bytes (3744 user bytes and eight interrupt veltor bytes), 104 RAM bytes, 216 bytes of bootstrap ROM firmware for EPROM programming, and an additional timer circuitry. Information throughout this document pertaining to the MC6805S2 MCU is also applicable to the MC68705S3 EPROM MCU. Difference information applicable to the MC68705S3 EPROM MCU. Bytes of this document. Emulation information is provided in Appendix C of this document.

Figure 1-1. MC6805S2 Microcomputer Block Diagram

### 1.2 HARDWARE FEATURES

The following are some of the hardware features of the MC6805S2 MCU.

A/D Converter

8-Bit Conversion, Monotonic

Four Multiplexed Analog Inputs

Ratiometric Conversion

- 21 TTL Including Eight TTL/CMOS Compatible I/O Lines

14 Bidirectional (Four Lines are LED Compatible)

7 Input-Only

- 1480 Bytes of User ROM

- 64 Bytes of RAM

- Self-Check Mode

- Serial Peripheral Interface (SPI)

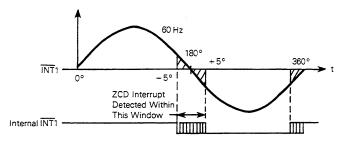

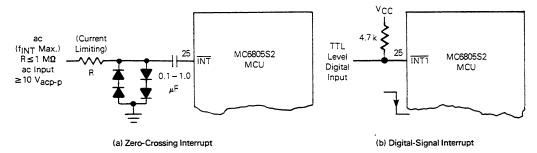

- Zero-Crossing Detect/Interrupt

- One 8-Bit and One 16-Bit Timer

- One 7-Bit and One 15-Bit Software Programmable Prescaler

- Three Bidirectional I/O Lines with TTL or Open-Drain Interface (Software Programmable)

- Auxiliary Counter with "Watchdog" Reset Feature

- 5-Volt Single Supply

### 1 SOFTWARE FEATURES

True following are some of the software features of the MC6805S2 MCU.

- 10 Powerful Addressing Modes

- 📑 Byte Efficient Instruction Set with True Bit Manipulation, Bit Test, and Branch Instructions

- Single Instruction Memory Examine/Change

- Powerful Indexed Addressing for Tables

- Full Set of Conditional Branches

- Memory Usable as Register/Flags

- User Callable Self-Check Subroutines

- Complete Development System Support on EXORciser, EXORset, and HDS-200 Available Now

#### 1 USER SELECTABLE OPTIONS

- The following are user selectable options of the MC6805S2 MCU.

- ♠ Eight Bidirectional I/O Lines with TTL or TTL/CMOS Interface Option

- Crystal or Low-Cost Resistor Oscillator Option

- Low Voltage Inhibit Option

- Vectored Interrupts: Timer/SPI, Software, and External

- 16-Bytes Standby RAM Option

- Fifth A/D Channel Option

EXORciser® is a registered trademark of Motorola Inc. EXORset and HDS-200 are trademarks of Motorola Inc.

1-3/1-4

2

# SECTION 2 SIGNAL DESCRIPTION, MEMORY, CPU, AND REGISTERS

This section provides a description of the signals, memory spaces, the central processing unit (CPU), and the various registers.

#### 2.1 SIGNAL DESCRIPTION

The following paragraphs provide a brief description of the signals and a reference (if applicable) to other paragraphs that contain more detail about the function being performed.

### 2.111 VCC and VSS

P-ver is supplied to the MCU using these two pins. VCC is power and VSS is the ground connection.

### 2.02 INT1 and INT2

These pins provide the capability for asynchronously applying an external interrupt to the MCU. Rever to **5.4 INTERRUPTS** for additional information.

### 2.1.3 XTAL and EXTAL

These pins provide control input for the on-chip clock oscillator circuit. A crystal, a resistor, or an external signal, depending on the user selected manufacturing mask option, can be connected to those pins to provide a system clock source with various stability/cost tradeoffs. Lead length and stay capacitance on these two pins should be minimized. Refer to 5.3 INTERNAL CLOCK GENERATOR OPTIONS for recommendations about these inputs.

### 2.1.4 PRESCALER1/PC0 and PRESCALER2/PC1

These pins allow an external input to be used to decrement the internal timer circuitry. Refer to SCITION 3 TIMERS for additional information about the timer circuitry.

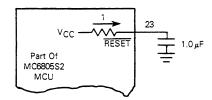

### 2.405 RESET

This pin allows resetting of the MCU at times other than the automatic resetting capability already in the MCU. The MCU can be reset by pulling RESET low. Refer to **5.2 RESETS** for additional information.

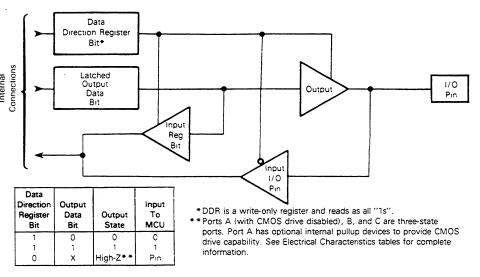

### 2.1.6 Input/Output Lines (PA0-PA7, PB0-PB3, PC0-PC1, and PD0-PD6)

Ports A, B, and C are programmable as either inputs or outputs under software control of the data direction registers (DDRs). Port D has up to four analog inputs or five via mask option, plus two voltage reference inputs when the analog-to-digital (A/D) converter is used (PD5/VRH, PD4/VRL, and an  $\overline{\text{INT2}}$  input). If any analog input is used, then the voltage reference pins (PD5/VRH, PD4/VRL) must be used in the analog mode. Refer to **6.1 INPUT/OUTPUT**, **6.6 ANALOG-TO-DIGITAL CONVERTER (A/D)**, and **5.4 INTERRUPTS** for additional information. Port D can also be used as a 7-bit digital input-only port.

### 2.1.7 NUM (Non User Mode)

This pin is reserved for factory use only, and should be tied to VSS (GND/ground).

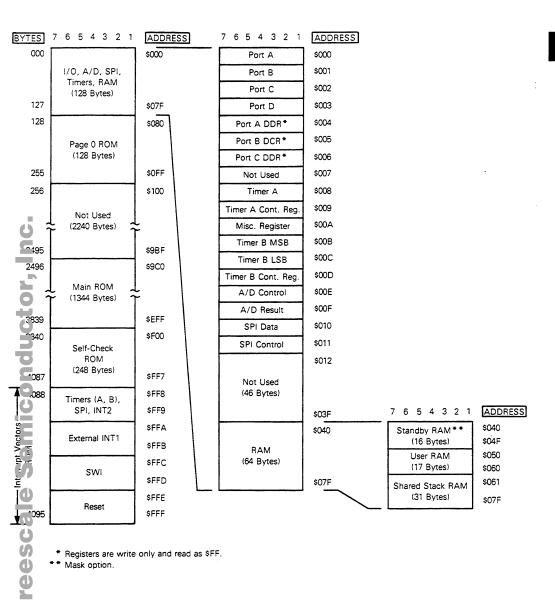

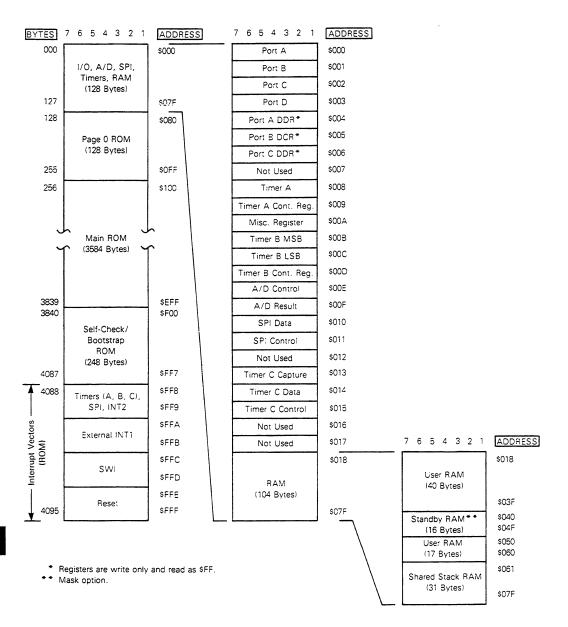

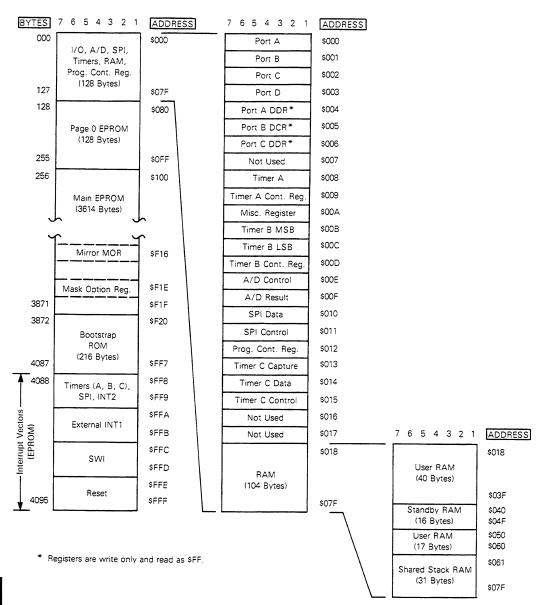

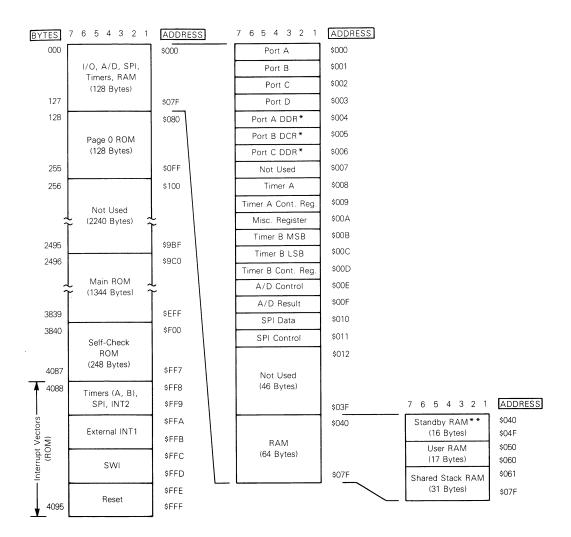

#### 2.2. MEMORY

As shown in Figure 2-1, the MCU is capable of addressing 4096 bytes of memory and I/O registers with its program counter. The MC6805S2 MCU has implemented 1802 of these locations. This consists of: 1480 bytes of user ROM including eight interrupt vectors, 248 bytes of self-check ROM, 64 bytes of user RAM, seven bytes of port I/O, five timer registers, two A/D registers, a miscellaneous register, and two serial peripheral interface (SPI) registers. The user ROM has been split into three areas. The first area is memory locations \$080 to \$0FF, and allows the user to access these ROM locations utilizing the direct and table look-up indexed addressing modes. The main user ROM area is from \$9C0 to \$EFF. The last eight user ROM locations at the top of memory are for the interrupt vectors.

The MCU reserves the first 18 memory locations for I/O features, of which 17 have been implemented. These locations are used for the ports, the port DDRs, the timers, the miscellaneous register, the SPI, and the A/D. Of the 64 RAM bytes, 31 are shared with the stack area, from \$061 through \$07F. The stack must be used with care when data shares the stack area. The lower 16 bytes of RAM, between \$40 and \$4F, may be powered through the  $\overline{\text{INT2}}/\text{PD6}$  pin via a user-defined mask option. Selection of this option does not exclude any of the available functions of the  $\overline{\text{INT2}}/\text{PD6}$  input.

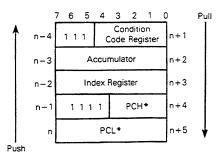

The shared stack area is used during the processing of an interrupt or subroutine calls to save the contents of the CPU state. The register contents are pushed onto the stack in the order shown in Figure 2-2. Since the stack pointer decrements during pushes, the low order byte (PCL) of the program counter is stacked first; then the high order four bits (PCH) are stacked. This ensures that the program counter is loaded correctly during pulls from the stack, since the stack pointer increments when it pulls data from the stack. A subroutine call results in only the program counter (PCL, PCH) contents being pushed onto the stack; the remaining CPU registers are not pushed.

### 2.3 CENTRAL PROCESSING UNIT

The CPU of the M6805 Family is implemented independently from the I/O or memory configuration. Consequently, it can be treated as an independent central processor communicating with I/O and memory via internal address, data, and control buses.

\* Registers are write only and read as \$FF.

\*\* Mask option.

Figure 2-1. MC6805S2 Memory Map

<sup>\*</sup>For subroutine calls, only PCH and PCL are stacked.

Figure 2-2. Interrupt Stacking Order

### 2.4 REGISTERS

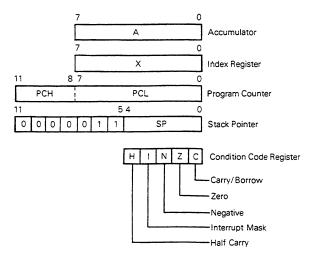

The M6805 Family CPU has five registers available to the programmer. They are shown in Figure 2-3 and are explained in the following paragraphs.

Figure 2-3. Programming Model

### 2.4.1 Accumulator (A)

The accumulator is a general purpose 8-bit register used to hold operands and results of arithmetic calculations or data manipulations.

### 2.4.2 Index Register (X)

The index register is an 8-bit register used for the indexed addressing mode. It contains an 8-bit value that may be added to an instruction value to create an effective address. The index register can also be used for data manipulations using the read-modify-write instructions and as a temporary storage area.

### 2.4.3 Program Counter (PC)

The program counter is a 12-bit register that contains the address of the next instruction to be executed.

#### 2.4.4 Stack Pointer (SP)

-

The stack pointer is a 12-bit register that contains the address of the next free location on the stack. During an MCU reset or the reset stack pointer (RSP) instruction, the stack pointer is set to location \$07F. The stack pointer is then decremented as data is pushed onto the stack and incremented as data is pulled from the stack. The seven most significant bits of the stack pointer are permanently configured to 0000011. Subroutines and interrupts may be nested down to location \$03 (31 bytes maximum) which allows the programmer to use up to 15 levels of subroutine calls (lex if interrupts are allowed).

#### 2.4.5 Condition Code Register (CC)

The condition code register is a 5-bit register in which four bits are used to indicate the results of the ir. Luction just executed. These bits can be individually tested by a program and specific action taken as a result of their state. Each bit is explained in the following paragraphs. For more information concerning the condition code register refer to the M6805 HMOS/M146805 CMOS Family U. S. Manual.

- **2.**  $\circ$  **.1** HALF CARRY (H) Set during ADD and ADC operations to indicate that a carry occurred be i re bits 3 and 4.

- 2. 5.2 INTERRUPT (I) When set, this bit masks (disables) the timer (both A and B), external  $(\overline{IN11}]$  and  $\overline{INT2}$ , and the serial peripheral interface interrupts. If an interrupt occurs while this bit is \$1, the interrupt is latched and is processed as soon as the interrupt bit is cleared.

- **2.4.5.3 NEGATIVE (N)** When set, this bit indicates that the result of the last arithmetic, logical, or vata manipulation was negative (bit 7 in the result is a logic one).

- 2.45.4 ZERO (Z) When set, this bit indicates that the result of the last arithmetic, logic, or data midipulation was zero.

- 2 + 5.5 CARRY/BORROW (C) When set, this bit indicates that a carry or borrow out of the animetic logic unit (ALU) occurred during the last arithmetic operation. This bit is also affected during bit test and branch instructions plus shifts and rotates.

2-5/2-6

# SECTION 3 TIMERS

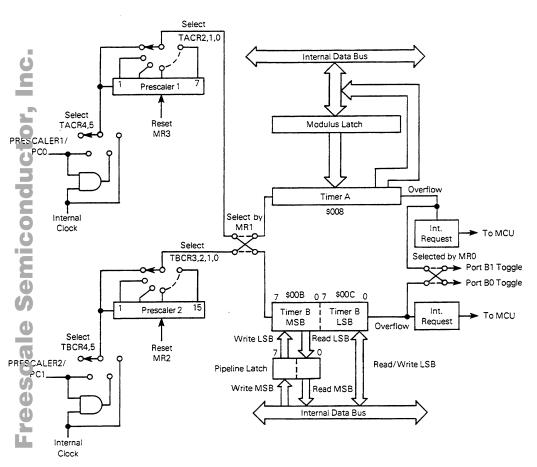

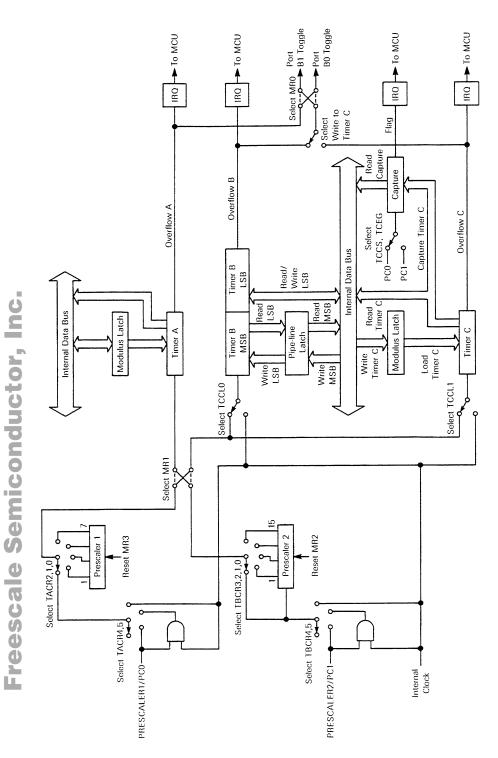

The MC6805S2 has three timers and two programmable prescalers (see Figure 3-1) which are described in this section.

3

Figure 3-1. Timer A and B Block Diagram

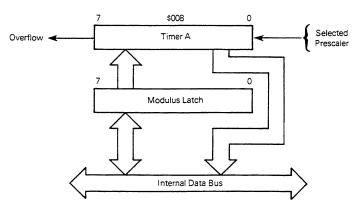

### 3.1 TIMER A

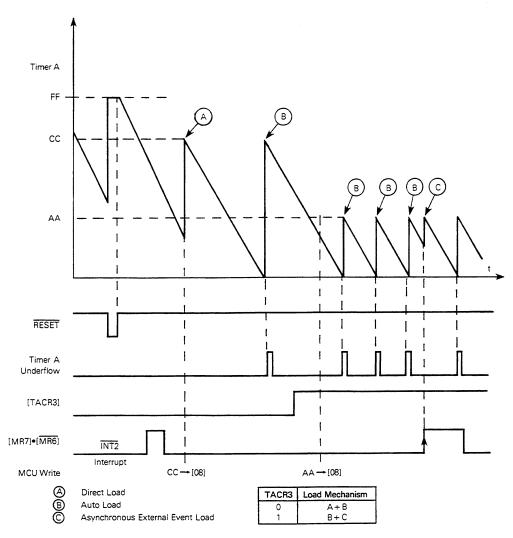

Timer A is an 8-bit programmable down counter, which may be loaded under program control (see Figures 3-2 and 3-3). Included in this timer is a modulus latch which allows the timer to be "auto reloaded." Address \$08 is the location of TIMER A's data register. Upon every clock input received, timer A decrements toward \$00. Upon reaching this value, bit 7 in the timer A control register (TACR located at \$09) is set, signifying a timer interrupt has been generated. At the same time, the timer is reloaded with the contents of the modulus latch. In addition to setting the interrupt bit, the transition to state \$00 also generates an overflow condition which can be used to toggle bit 0 or bit 1 of port B directly, under the control of the miscellaneous register bit 0 (MR0), the serial peripheral interface control register, and the port B data direction register. The bit selected depends upon the state of bit 0 of the miscellaneous register. The timer interrupt may be masked by setting bit 6 of the TACR. Of course, the I bit in the condition code register will also prevent a timer interrupt from being processed. The timer interrupt vector locations are \$FF8 and \$FF9. The timer interrupt request bit *MUST* be cleared by software.

Figure 3-2. Timer A

| TACR7                                                       | TACR6                                                  | TACR5                                      | TACR4     | TACR3 | TACR2 | TACR1 | TACR0 | \$009 |

|-------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------|-----------|-------|-------|-------|-------|-------|

| TACR7 = TACR6 = TACR5 = ETACR4 = ETACR3 = TACR2 TACR1 TACR0 | Fimer A In<br>External/In<br>External Er<br>Fimer A Lo | terrupt Re<br>iternal<br>nable<br>nad Mode | quest Mas |       |       |       |       |       |

|                                                             |                                                        |                                            |           |       |       |       |       |       |

| TACR5 | TACR4 | Prescaler 1 Clock         |  |  |

|-------|-------|---------------------------|--|--|

| 0     | 0     | Internal Clock            |  |  |

| 0     | 1     | AND of Internal Clock PC0 |  |  |

| 1     | 0     | Clock Disabled            |  |  |

| 1     | 1     | PC0 Positive Transition   |  |  |

Figure 3-3. Timer A Control Register

3-2

There are three ways of loading data from the modulus latch into timer A as described in the following paragraphs (refer to Figure 3-4).

#### 3.1.1 Direct Loading

When the MCU writes to the timer A data register, the data is latched by the modulus latch, and forced into the timer. For this operation, TACR bit 3 must be clear.

### 3.1.2 Asynchronous External Event Loading

When TACR bit 3 is a logic one, the contents of the modulus latch are transferred to the timer at the rising edge of the  $\overline{\text{INT2}}$  interrupt request bit (MR7) gated with interrupt request mask bit (MR6).

### NOTE

If this feature is used, then care must be taken in programming as it will start an interrupt service routine if the I bit in condition code register (CC) is clear.

Loading \$00 to timer A allows a countdown of 256 clocks before next \$00 state is reached.

### 3 3 Auto-Loading

Auto-loading of the modulus latch occurs whenever the timer reaches the \$00 state. This mode is invependent of the status of bit 3 in TACR.

### NOTE

Loading modes 1 and 2 are mutually exclusive, and auto-loading occurs in both modes 1 and 2.

Timer A may be read at any time without disturbing the countdown mechanism of the timer. At recet, both the timer and modulus latch contents are set to \$FF.

#### NOTE

Loading \$01 to timer A should be avoided when operating with a divide-by-one prescaler. Doing so will inhibit timer A auto-loading, interrupt generation, and port B toggle mechanisms.

### 3.2 TIMER A CONTROL REGISTER

Timer A control register (TACR) occupies memory location \$09 (see Figure 3-3). Five bits are al coated to timer A and three bits are used to control prescaler 1.

R

Figure 3-4. Timer A Operation

TACR7 Timer A Interrupt Request Flag

Set at the transition of timer A to \$00 state. Cleared by software or at reset.

Timer A Interrupt Request Mask TACR6

> Set at reset or under program control. When set, timer A interrupt requests to the processor are inhibited. Cleared under program control.

TACR5 External or Internal Bit

> Set under program control. When set, selects the input clock source for prescaler 1 to be the PRESCALER1/PC0 input, otherwise the internal clock (fosc divided by four) is

the input clock source. Cleared at reset or under program control.

TACR4 External Enable Bit

Control bit used to enable the external timer pin (PRESCALER1/PC0).

| TACR5 | TACR4 | Prescaler 1 Clock Source                  |

|-------|-------|-------------------------------------------|

| 0     | 0     | Internal Clock                            |

| 0     | 1     | AND of Internal Clock and PRESCALER1/PC0* |

| 1     | 0     | Inputs Disabled                           |

| 1     | 1     | PRESCALER1/PC0* Low-to-High Transition    |

CR3 Timer A Load Mode Control

Set under program control. When set, allows asynchronous external event loading of timer A (INT2 driven loading is enabled). Cleared under program control or at reset. When clear, allows direct loading of timer A. Auto-loading takes place independent of TACR3 status. Cleared by reset or by program control.

Prescaler 1 Division Ratio Control Bits

Set or cleared under program control, also cleared at reset. When set, these bits select

|            | one of the eight possible outputs on prescaler 1. |       |       |                                   |  |  |  |

|------------|---------------------------------------------------|-------|-------|-----------------------------------|--|--|--|

| 00         | TACR2                                             | TACR1 | TACR0 | Prescaler 1 <u>Division Ratio</u> |  |  |  |

|            | 0                                                 | 0     | 0     | 1                                 |  |  |  |

|            | 0                                                 | 0     | 1     | 2                                 |  |  |  |

| <b>O</b>   | 0                                                 | 1     | 0     | 4                                 |  |  |  |

| S          | 0                                                 | 1     | 1     | 8                                 |  |  |  |

| 40         | 1                                                 | 0     | 0     | 16                                |  |  |  |

| <u> </u>   | 1                                                 | 0     | 1     | 32                                |  |  |  |

| <b>6</b> 5 | 1                                                 | 1     | 0     | 64                                |  |  |  |

|            | 1                                                 | 1     | 1     | 128                               |  |  |  |

|            |                                                   |       |       |                                   |  |  |  |

### 3<sub>13</sub> TIMER B

T=CR2

T.CR1

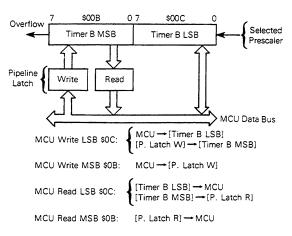

Tiber B is a 16-bit timer which is accessed via two registers at \$0B for the most-significant byte (MSB) and \$0C for the least-significant byte (LSB) (refer to Figure 3-5). Included within the MSB of ....er B is a "pipeline" latch, which allows a "snap shot" value of the entire 16 bits to be read.

<sup>\*</sup>The status of PRESCALER1/PC0 depends upon the data direction status of PRESCALER1/PC0. If PRESCALER1/PC0 is an output, then the clock source is equal to the port data register content, independent of the port electrical loading. If an input, then the clock source is the logic level of PRESCALER1/PCO.

Figure 3-5. Timer B

Read/write operations to the LSB are direct. Reading the LSB can occur at any time without disturbing the count. At the time of the LSB read, the contents of the MSB are loaded into the pipeline latch, so when the MPU reads the MSB, it actually reads the latch.

Writing to the LSB of timer B may occur at any time, and the contents are immediately entered into the timer. At the same time the contents of the pipeline latch are forced into the MSB of the timer. Hence, a 16-bit word may be placed into the entire timer data register during a LSB write operation.

In order to manipulate a 16-bit word in timer B during a read, it is recommended that a read of the LSB be done first, then the MSB. A 16-bit write should be done in the opposite order. (First, write the MSB and then the LSB.) After reset, timer B contains \$FFFF.

Like timer A, timer B decrements toward zero upon every clock input received and during the transition to state \$00 TBCR7 in the timer B control register is set (TBCR is located at \$0D).

The timer interrupt can be masked by setting the timer interrupt mask bit (TBCR6) (Figure 3-6). The I bit in the condition code register will also prevent a timer interrupt from being processed. The MCU responds to a timer interrupt by saving the current MCU state in the stack, fetching the vector from \$FF8 and \$FF9, and executing the interrupt routine. The timer interrupt routine bit *MUST* be cleared by software.

| TBCR7 | TBCR6                      | TBCR5     | TBCR4      | TCBR3 | TBCR2 | TBCR1 | TBCR0 | \$00D  |                                                   |

|-------|----------------------------|-----------|------------|-------|-------|-------|-------|--------|---------------------------------------------------|

|       | Timer B In<br>Timer B In   |           |            |       |       | ТВ    | CR5   | TBCR4  | Prescaler 2 Clock                                 |

|       | External/In<br>External En |           |            |       |       | 1     | 0     | 0      | Internal AND of Internal Clock  PC1 PC1           |

| TBCR1 | Prescaler 2                | Divide Ra | tio Select |       |       |       | 1     | 0<br>1 | Clock Disabled PRESCALER2/PC1 Positive Transition |

Figure 3-6. Timer B Control Register

The transition to \$00 generates an underflow pulse which may be used to force a port B data register toggle under the control of the miscellaneous register bit 3 (MR3), the SPI control register, and the port B data direction register. (See 6.5 MISCELLANEOUS REGISTER and 4.3 SERIAL PERIPHERAL INTERFACE CONTROL AND STATUS REGISTER.)

#### 3.4 TIMER B CONTROL AND STATUS REGISTER

Timer B control and status register (TBCR) occupies memory location \$0D (see Figure 3-6). Four bits are allocated to timer B and four bits are used to control prescaler 2.

TBCR7 Timer B Interrupt Request Flag

Set at the transition of timer B to \$00. Cleared by software or at reset.

TBCR6 Timer B Interrupt Request Mask

Set at reset or under program control. When set, inhibits timer B interrupt requests to the

processor. Cleared under program control.

TB\_CR5 External or Internal Bit

> Set under program control. When set, selects the input clock source for prescaler 2 to be the PRESCALER2/PC1 input, otherwise the internal clock (fosc divided by four) is the input clock source. Cleared at reset or under program control.

External Enable Bit

Set under program control or at reset. When set, this bit enables the external timer pin (PRESCALER2/PC1). Cleared under program control.

| TBCR5 | TBCR4 | Prescaler 2 Clock Source                 |  |  |  |  |

|-------|-------|------------------------------------------|--|--|--|--|

| 0     | 0     | Internal Clock                           |  |  |  |  |

| 0     | 1     | AND of Internal Clock and PRESCALER2/PC1 |  |  |  |  |

| 1     | 0     | Inputs Disabled                          |  |  |  |  |

| 1     | 1     | PRESCALER2/PC1* Low-to-High Transition   |  |  |  |  |

Prescaler 2 Division Ratio Control Bits

Set or cleared under program control. When set, these bits select one of the 16 possible outputs on prescaler 2. All bits are cleared at reset.

TECR3

TOCR2 TSCR1

3-7

<sup>\*</sup>PRESCALER2/PC1 status depends on the data direction status of PRESCALER2/PC1. If PRESCALER2/PC1 is an output, then the clock source is equal to the port data register content, independent of the port electrical loading. If an input then the clock source is the logic level on PRESCALER2/PC1.

| TBCR3 | TBCR2 | TBCR1 | TBCR0 | Division Ratio |

|-------|-------|-------|-------|----------------|

| 0     | 0     | 0     | 0     | 1              |

| 0     | 0     | 0     | 1     | 2              |

| 0     | 0     | 1     | 0     | 4              |

| 0     | 0     | 1     | 1     | 8              |

| 0     | 1     | 0     | 0     | 16             |

| 0     | 1     | 0     | 1     | 32             |

| 0     | 1     | 1     | 0     | 64             |

| 0     | 1     | 1     | 1     | 128            |

| 1     | 0     | 0     | 0     | 256            |

| 1     | 0     | 0     | 1     | 512            |

| 1     | 0     | 1     | 0     | 1024           |

| 1     | 0     | 1     | 1     | 2048           |

| 1     | 1     | 0     | 0     | 4096           |

| 1     | 1     | 0     | 1     | 8192           |

| 1     | 1     | 1     | 0     | 16384          |

| 1     | 1     | 1     | 1     | 32768          |

#### 3.5 PRESCALER 1

Prescaler 1 is a 7-bit binary down counter whose value is selected by TACR2, TACR1, and TACR0. The selected output is used as the clock input to either timer A or timer B, depending upon the status of the prescaler cross-couple bit (MR1). The type of clock source to prescaler 1 may be selected by TACR5 and TACR4 (see **3.1 TIMER A**).

Prescaler 1 is set to \$7F at reset or under program control when a one is written to prescaler 1 clear bit (MR3).

### NOTE

When changing outputs on the prescaler, a prescaler clear should be done first to avoid truncation errors.

### 3.6 PRESCALER 2

Prescaler 2 is a 15-bit down counter whose value is selected by TBCR3, TBCR2, TBCR1, and TBCR0. The selected output is used as the clock input to either timer A or timer B, depending upon the status of MR1. The type of clock source to prescaler 2 can be selected by TBCR5 and TBCR4 (see 3.3 TIMER B).

Prescaler 2 is preset to \$7FFF at reset, under program control when a logic one is written to prescaler 2 clear bit (MR2).

#### NOTE

When changing outputs on the prescaler, a prescaler clear should be done first to avoid truncation errors.

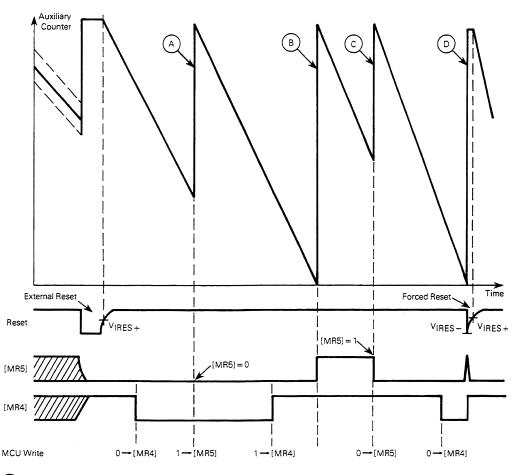

### 3.7 AUXILIARY COUNTER

The third timer register in the MC6805S2 is the auxiliary counter, or "watchdog" timer. It is a fixed counter which is clocked by the internal clock (fosc divided by four). The total count period is 4095

cycles. The MCU communicates with this counter via the miscellaneous register bits 5 and 4 (MR5, MR4). Upon underflow, the auxiliary counter control/status bit in the miscellaneous register (MR5) is set. Countdown may be aborted at any time under program control, which also will reset the counter to 4095. To do this, the MCU must write to MR5 the inverse of what is read from MR5.

At reset, the counter is preset to its maximum count of 4095, and MR5 is cleared. The value of the counter is not accessible to the MCU; however, the possibility of detecting an underflow and presetting it at any time under program control allows it to be used as a fixed rate polled timer in applications requiring lengthy time out periods.

When the auxiliary counter reset mask bit in the miscellaneous register (MR4) is clear and the MR5 is set as a result of counter time out, the reset pin is internally pulled to ground (VSS). This feature is useful in many applications, e.g., automotive, where the MCU operates in a noisy environment. Due to high energy spikes on the power supply and I/O lines, the MCU may lose control of the program and execute through non-valid memory space. The "watchdog" timer will bring the MCU back to reset. MR4 is automatically set at reset or under program control.

To return from a catastropic system runaway, the reset line is pulsed, which will restart the entire program. This program should regularly preset the auxiliary counter at a rate higher than the counter time out so as not to allow a forced reset. If program runaway does occur, it is likely that regular presetting of the auxiliary counter will not take place, and an underflow will force the MCU to regain control. (See Figure 3-7.)

K

- A Counter Preset by Writing "1"

- B Underflow: MR5 1; No Forced Reset

- C Counter Reset by Writing "0"

- (D) Underflow MR5 → 1 Forced Reset

Figure 3-7. Auxiliary Counter Operation

# SECTION 4 SERIAL PERIPHERAL INTERFACE (SPI)

This section describes the operation of the serial peripheral interface (SPI) on the MC6805S2.

### 4.1 INTRODUCTION

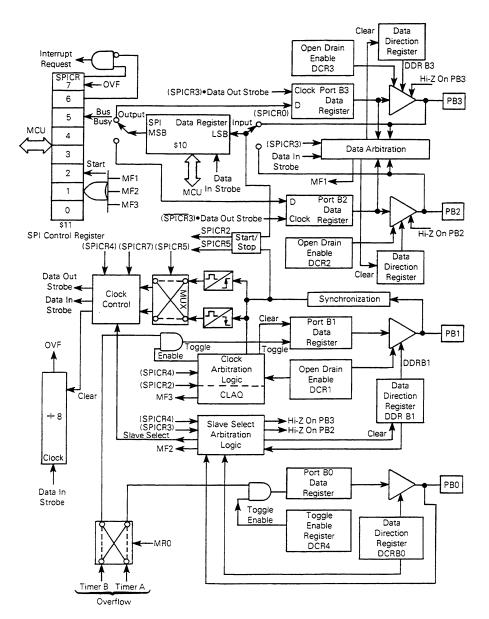

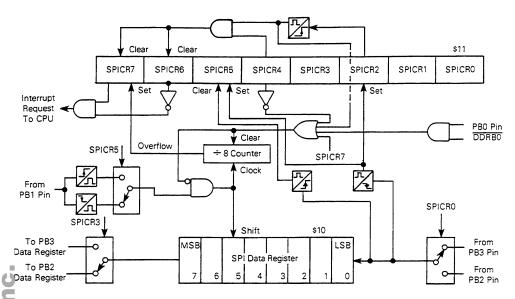

The serial peripheral interface (SPI) on the MC6805S2 has several versatile operating modes. Arbitration on data and clock lines is provided. The SPI communicates with the MCU via data and control registers located at memory addresses \$10 and \$11, respectively. Operation of the SPI occurs via port B (see Figure 4-1).

The SPI consists of:

an 8-bit shift register (MSB out first; MSB in first) which may also be used as an SPI data register,

) a divide-by-eight counter,

Slave select/arbitration logic,

(d) an SPI control register, and

start and stop bit detection capability.

Unike the I/O port operation, the SPI data and clock inputs are always taken from their respective I/O port pins, regardless of the status of the data direction register relative to that port. This makes it easy to do data and clock arbitration.

Suial peripheral interface operation is enabled when the SPI enable bit (SPICR4) is set. When embled, the SPI is capable of operating in the following modes:

🧐 one wire – auto clocked (e.g., NRZ),

(1) two wire - half duplex,

two wire - half duplex with clock arbitration,

three wire - half duplex with slave select/busy line,

three wire - full duplex,

three wire - full duplex with clock arbitration, and

four wire - full duplex with slave select/busy line.

### 4. SPI TERMINOLOGY

The following explanations are provided to facilitate user understanding of the various operating the des of the serial peripheral interface (see Table 4-1).

4

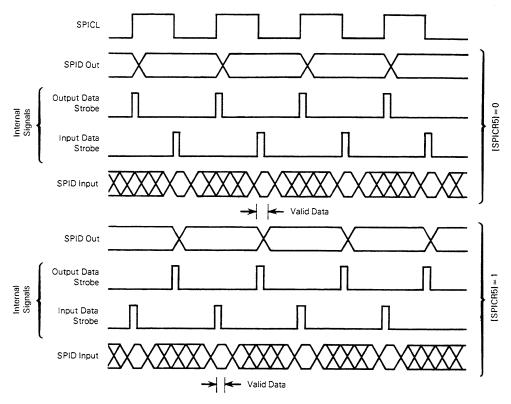

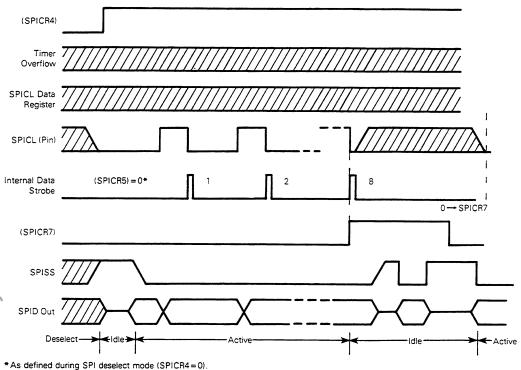

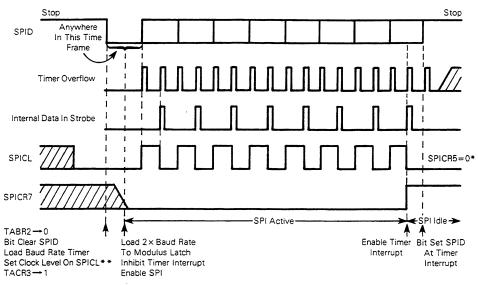

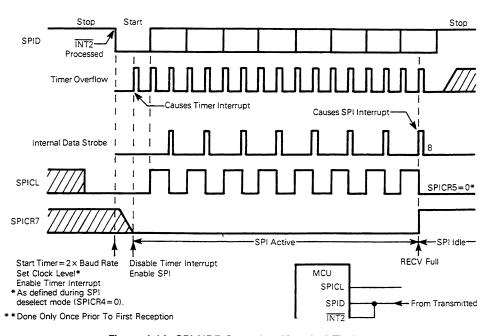

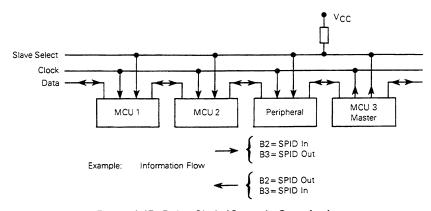

Figure 4-1. Serial Peripheral Interface (SPI)

Table 4-1. SPI Operation

DEFINTIONS

Transmitter — Data Master: DDRB2 or 3=1

Receiver — Data Slave: DDRB2 or 3=0

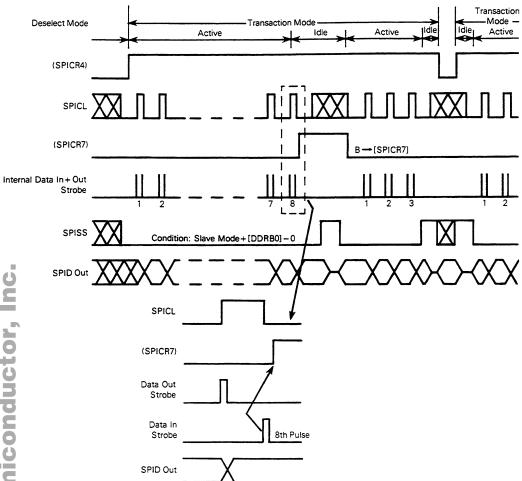

Clock Master: DDRB1 = 1 Clock Slave: DDRB1 = 0 Transaction Mode: SPICR4 = 1

1) Active: \$\frac{\text{SPICR7}\(\text{ODRB0}\circ \text{PB0} + \text{DDRB0}\) of DDRB1=0 (clock slave mode) or \frac{\text{SPICR7}\(\text{ODRB0}\circ \text{PB0} + \text{DDRB0}\) if DDRB1=1 (clock master mode)

Clock pulses allowed, data shifted

2) Idle: SPICR7+DDRB0•PB0 if DDRB1=0 (clock slave mode)

Clock pulses blocked, data output line in high-impedance state

Deselect Mode: SPICR4=0-No SPI Operations

SLAVE SELECT INPUT

Slave Select Input: SPISS - PB0

If DDRB0=0 then no SPISS action on MCU

1) Master Mode: SPISS = 1 DDRB1 = 1

SPISS 1 — 0: Switch to Slave Mode (DDRB1 1—0)

Set SPICR1 (Mode Fault Flag)

2) Slave Mode: SPISS=0 DDRB1=0

External clock is allowed to shift data in/out. If SPISS is pulled high, the external clock input pulses are inhibited; no data shift; divide-by-eight counter cleared; SPID (PB2 or PB3) switched to high-impedance state.

Used as Chip-Select Input

### DATA ARBITRATION

Data master loses data mastership when data collision occurs during internal data strobe time.

If SPID output port (PB2 or PB3) = 1 while actual pin level is pulled low externally — conflict detected at internal data strobe time.

Then SPICR1 (mode fault flag) is set; SPID output port DDR (B2 or B3) 1 - 0 (high-impedance state).

#### CLOCK ARBITRATION

MCU has clock mastership (DDRB1 = 1)

Via SPISS line (DDRB0=0). If SPISS is pulled low, then clock mastership lost; DDRB1 1→0 (high-impedance state); SPICR1 is set (mode fault flag).

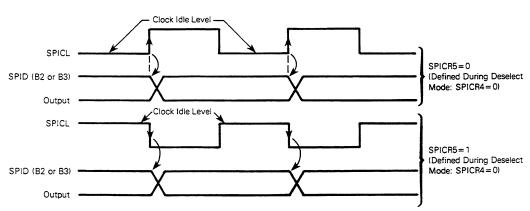

2) Via clock line SPICL (DDRB1 = 1 and DCRB5 = 0)

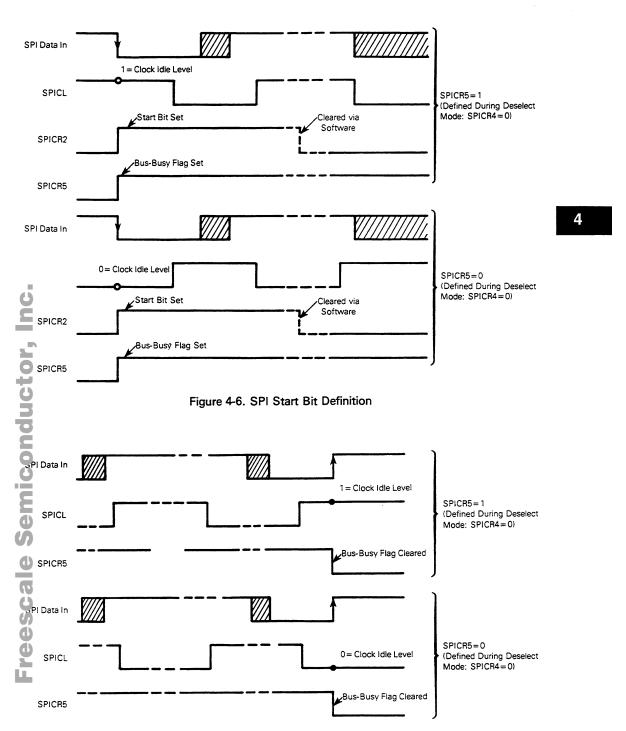

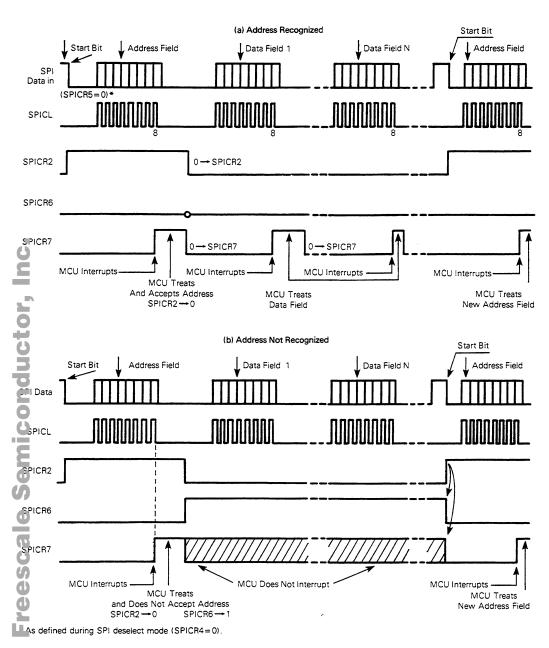

Condition: SPICL must have open-drain output (DCRB5=0)