Order this document by AN432/D

# **AN432**

**ARCHIVED 200**

## 128-Kbyte Addressing with the M68HC11

By Ross Mitchell

MCU Applications Engineering

Motorola Ltd.

East Kilbride, Scotland

#### Overview

#### Freescale Semiconductor. Inc

The maximum direct addressing capability of the M68HC11 device is 64 Kbytes, but this can be insufficient for some applications.

This application note describes two methods of memory paging that allow the MCU to fully address a single 1 megabit EPROM (128 Kbytes) by manipulation of the address lines.

The two methods illustrate the concept of paging and the inherent compromises. The technique may be expanded to allow addressing of several EPROM, RAM, or EEPROM memories, or several smaller memories by using both address lines and chip enables.

2

## **Paging Scheme**

The M68HC11 8-bit MCU is capable of addressing up to 64 Kbytes of contiguous address space. Addressing greater than 64 Kbytes requires that a section of the memory be replaced with another block of memory at the same address range. This technique of swapping memory is known as paging and is simply a method of overlaying blocks of data over each other such that only one of the blocks or pages is visible to the CPU at a given time.

In a system requiring more than 64 Kbytes of user code and tables, it is possible to use the port lines to extend the memory addressing range of the M68HC11 device. This has certain restrictions, but these can be minimized by careful consideration of the user code implementation.

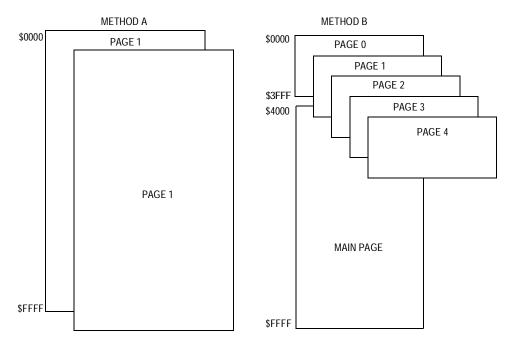

There are two basic configurations:

- Method A uses only software plus a single port line to control the high address bit A16.

- Method B is a combination of a small amount of hardware and software controlling the top three address bits — A14, A15, and A16.

In the examples that follow, the MC68HC11G5 device is used to demonstrate the paging techniques, since this device has a non-multiplexed data and address bus. Any M68HC11 device may be used in a similar way.

Method A has the advantage of no additional hardware and very few limitations in the software. The user code main loop can be up to 64 Kbytes long and remain in the same page, but this is at the expense of longer interrupt latency. The vector table and a small amount of code must be present in both pages of memory to allow correct swapping of the pages.

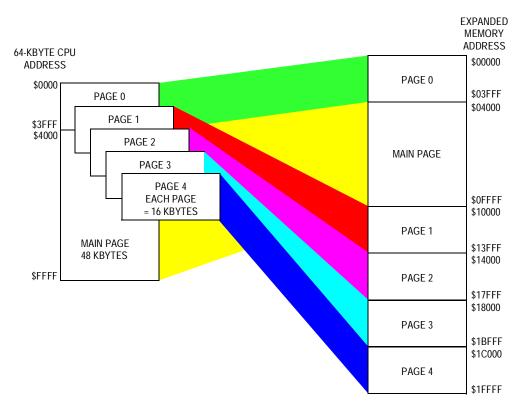

Method B has the advantage of not affecting the interrupt latency and has just one copy of the vector table. The maximum length of the user code main loop in this example is 48 Kbytes with a further five paged areas of 16 Kbytes for subroutines and tables.

Application Note

Method A — Software Technique

## Method A — Software Technique

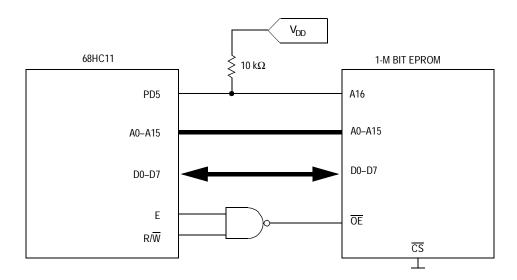

Address A16 of the EPROM is directly controlled by port D(5) of the M68HC11 as shown in **Figure 1**. This port is automatically configured to be in the input state following reset. It is vital that the state of the port line controlling address A16 is known following reset and so there is a  $10\text{-k}\Omega$  pullup resistor on this port line to force the A16 address bit to a logic high state following reset. This port bit is then made an output during the setup code execution, but care must be taken in ensuring that the data register is written to a logic 1 before the data direction register is written with a 1 to make the port line output a high state.

This port bit allows the M68HC11 to access the 128-Kbyte EPROM as two memories of 64 Kbytes each, which are paged by changing the state of the address A16 line on the EPROM. It is important to make sure that the port timing enables the port line to change state, at least the setup and hold time, before the address strobe (E clock rising edge on the MC68HC11G5), otherwise, there could be problems with address timing.

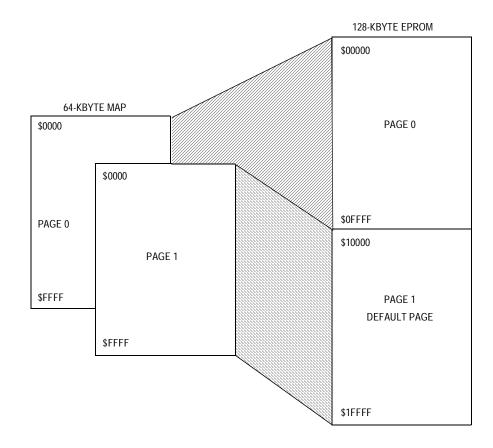

**Figure 2** shows a schematic representation of the paging technique for this method where there are two separate 64-Kbyte pages of memory which may be addressed only individually.

This paging scheme means that code cannot directly jump from one 64-Kbyte page to another without running some common area of code during the page switch. This may be accomplished in two basic ways:

- The user code could build a routine in RAM, which is common to both pages, since it is internal and, therefore, unaffected by the port D(5) line.

- The user code could have the same location in both pages devoted to a page change routine.

The example software listing in **Appendix A** — **Software Paging Scheme** uses the latter approach.

### **Application Note**

#### **Interrupt Routines**

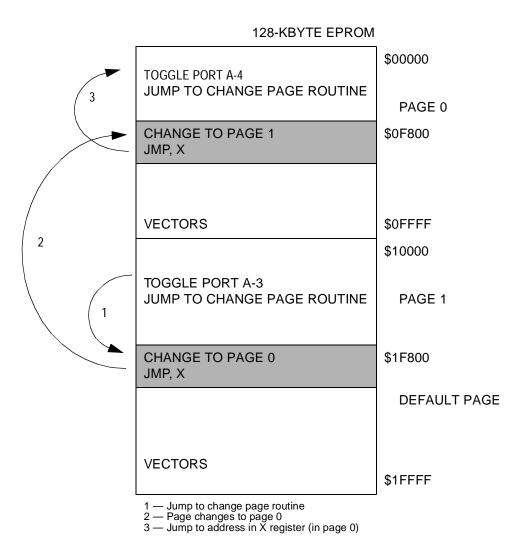

The change of page routine stores the current page before setting or clearing the port D(5) line and then has a jump command which must be at exactly the same address in both pages of memory. This is because the setting or clearing of the port D(5) line will immediately change the page of memory but the program counter will increment normally. Thus a change from page 0 to page 1 will result in the BSET PORTD command from page 0 followed by the JMP 0,X instruction from page 1 (the new page). To enable a jump to work, the X index register has been loaded with the address of the routine to be run in the new page.

Figure 3 shows the execution of code to perform a change of page from page 1 to page 0.

Returning from the interrupt routine requires the return-from-interrupt (RTI) command to be replaced with an RTI routine that checks the RAM location containing the memory page number prior to the interrupt routine execution. The routine then either performs an RTI command immediately, if it is to remain in the same page, or otherwise changes the state of the port D(5) line and then performs an RTI command in the correct page. Note that as with the JMP 0,X command, the RTI must be at the same address in both pages. It is important that the I bit in the condition code register (CCR) (interrupt inhibit) is set during this time for the example code to run correctly. Otherwise, the return page may be altered. This limitation can be overcome by using the stack to maintain a copy of the last page prior to the current interrupt.

The latency for an interrupt routine in a different page from the currently running user code is increased by 21 cycles on entering the interrupt routine and 18 cycles on leaving the interrupt routine. Any interrupt code that could not tolerate any such latency could be repeated in both pages of memory.

Application Note Method A — Software Technique

#### **Other Routines**

Jumping from one page to another may be done at any time by using the same change of page routine, but there is no need to store the current page in RAM, and so these two lines of code become redundant. In the example, the change page routine could be started at the BCLR or BSET command and save four cycles. This would, therefore, reduce the page change delay to 17 cycles. Note that it is not possible to perform a JSR command to move into the other page with the method shown in the example, since the RTS would not return to the original page. However, a modification to the return-from-interrupt routine would allow an equivalent function for a return from subroutine. In this case, the stack should be used to maintain the correct return page or the I bit in the CCR should be set to prevent interrupts.

# Important Conditions

The state of the port line controlling address A16 after reset is very important. In the example, port D(5) is used which is an input after reset and has a pullup resistor to force a logic high on A16. If an output-only port line was used, then it could be reset such that A16 is a logic 0 (no pullup resistor required), which has an important consequence. The initialization routine which sets up the ports must be in the default page dictated by the state of address A16 following reset; otherwise, the user code may not be able to correctly configure the ports and hence be unable to manipulate address A16. Similarly, a bidirectional port line could have a pull-down resistor to determine the address A16 line after reset with the same implications.

The assembler generates two blocks of code with identical address ranges used by the user code. This could not be programmed directly into an EPROM since the second page would simply attempt to overwrite the first page. The code must, therefore, be split into two blocks and programmed into the correct half of the EPROM. Some linkers may be capable of performing this function automatically.

Figure 2 illustrates the expansion of the pages into the 128-Kbyte EPROM memory.

The RAM and registers, and internal EEPROM if available and enabled, will all appear in the memory map in preference to external memory, so care must be taken to avoid these addresses or move the RAM or registers away to different addresses by writing to the INIT register.

Figure 1. Software Paging Schematic Diagram

Figure 2. Software Paging Representation

Application Note Method A — Software Technique

Figure 3. Flow of Program Changing from Page 1 to Page 0

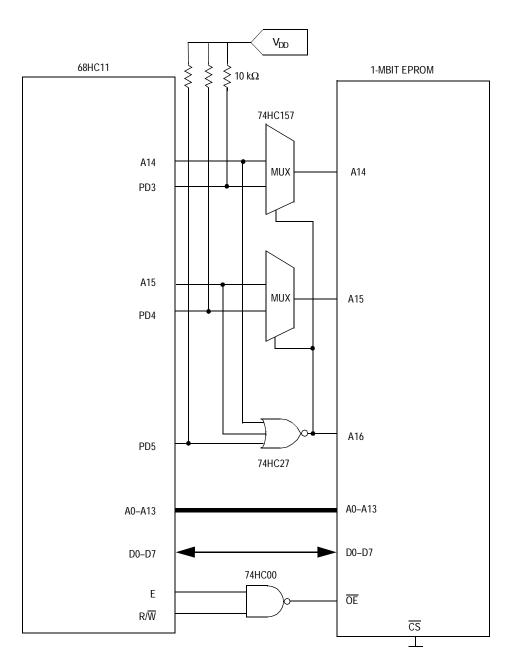

Figure 4. Hardware and Software Paging Schematic Diagram

Application Note Method B — Combined Hardware and Software Technique

#### Method B — Combined Hardware and Software Technique

The basic approach to this method is the same as in **Method A** — **Software Technique** except that hardware replaces some of the software. A port line together with M68HC11 addresses A14 and A15 are NORed to control the address A16 line of the EPROM. This signal is also used to select between the port line and address line for A15 and A15 (see **Figure 4**). The hardware between the port lines controlling the A14 and A15 addresses enables 64 Kbytes of user code to be addressed at all times with 48 Kbytes common to all the pages and then selecting one of five 16-Kbyte pages of EPROM memory.

In the example, port D(3) and address A14 are connected to the input of a 2-channel multiplexer such that port D(5), address A14, and address A14 control which of these two signals reaches the A14 pin of the EPROM. If addresses A14 or A15 are logic 1, the NOR gate outputs a logic 0 state, ensuring the A16 pin of the EPROM is a logic 0. In this case, address A14 controls the A14 pin of the EPROM and similarly A15 and port D(4) are selected such that address A15 controls the A15 pin of the EPROM. Thus the main 48-Kbyte portion of the EPROM memory may be addressed at all times at addresses \$4000 up to \$FFFF. With port D(5) and address A14 and A15 all at logic 0 (address range \$0000 to \$3FFF), the port lines port D(3) and port D(4) are selected in place of address lines A14 and A15. Page 0 is always selected whenever port D(5) is a logic 1. This makes it possible to have one of the five pages of 16 Kbytes paged into the 64-K addressing range of the HC11 while always maintaining the main 48 Kbytes of user code in the memory map.

There are few restrictions on the user code since the hardware provides the switching logic. Code can be made to run from one paged area to another by jumping to an intermediate routine in the main page. Port D is configured to be in the input state following reset which results in the main page plus page 0 of the paged memory in the 64-Kbyte address map since the port D lines each have a pullup resistor to maintain a logic high state after reset. A simple change memory map routine can then bring in the desired page at any time. Appendix B — Hardware and Software Paging Scheme shows the assembly code for a program that toggles different port pins in each of the five pages controlled from a

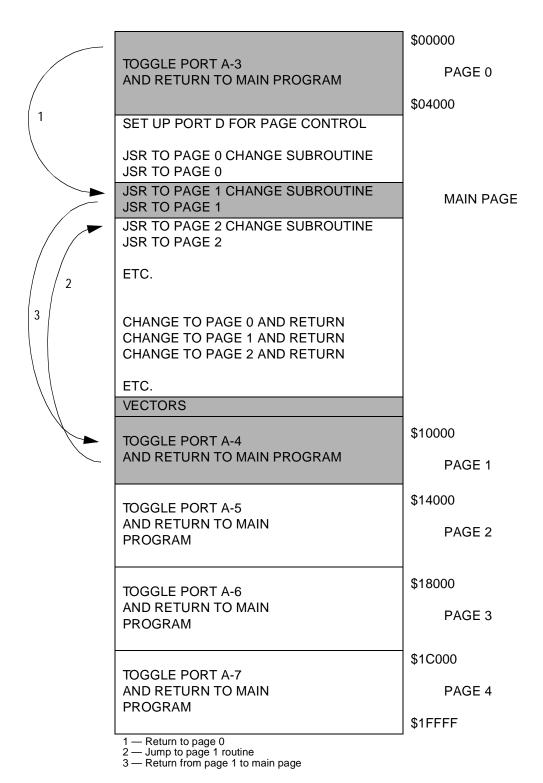

main routine in the main page. **Figure 5** shows the five overlaid pages expanded to a 128-K map with the flow of the program demonstrating a change from page 0 to page 1 by running the change page subroutine shown in bold type.

# Implementation in C Language

The demonstration code was originally written in assembly language, but it may also be implemented in C, as shown in

Appendix C — C Language Routines for Method B. The change of page routines were written in C with the first part an example of using inline code and the second part calling a function. The short example shows the assembly code on the left, generated by the C code on the right. This is very similar to the assembly code example in Appendix B — Hardware and Software Paging Scheme, and so it is possible to extend the memory addressing beyond 64-Kbytes with the C language just as with assembly language.

# Interrupt Conditions

The interrupt routines have normal latency when they reside in the main 48-Kbytes page since this is always visible to the CPU. The 25-cycle delay for changing pages may cause problems for interrupt routines in a paged area of memory.

# Important Conditions

There are few special conditions for this method. The vectors must point to the main page of memory where the page changing routine must also reside. Routines in a paged area can only move to another page via the main 48-Kbyte page unless the technique in method A is utilized (for example, page change routine duplicated at identical addresses in both pages).

As with method A, the RAM and registers and internal EEPROM, if available and enabled, will all appear in the memory map in preference to external memory, so care must be taken to avoid these addresses or move the RAM or registers away to different addresses.

Application Note Method B — Combined Hardware and Software Technique

The assembler generates five blocks of code with identical address ranges used by the user code plus the main 48-Kbyte section. This could not be programmed directly into an EPROM since the second and subsequent pages would simply attempt to overwrite the first page. The code must, therefore, be split into blocks and programmed into the correct part of the EPROM. Some linkers may be capable of performing this function automatically.

**Figure 6** illustrates the expansion of the pages into a single 128-Kbyte EPROM memory.

#### Customization

Clearly, the size of the paged areas may be made to suit the application with, for example, a 32-Kbyte main page and three 32 Kbytes of paged memory simply by not implementing control over the A14 address of the EPROM and not including port D(3) control. Similarly, by adding another port line to control address A13, the main program can be 56 Kbytes with nine pages of eight Kbytes each.

Figure 5. Illustration of Changing from Page 0 to Page 1

Application Note Method B — Combined Hardware and Software Technique

Figure 6. Hardware and Software Paging Representation

Figure 7. Comparison of Paging Schemes

### **Application Note**

#### In General

In both methods, the registers may be moved to more appropriate addresses. If the usage of RAM is not critical, the registers may be moved to address \$0000 by writing \$00 to the INIT register immediately after reset. For the MC68HC11G5, this means losing 128 bytes of RAM, but results in a clean memory map above \$1FF. In the examples, the registers and RAM remain at the default addresses and so care must be taken not to have user code from address \$0000 to \$01FF and \$1000 to \$107F for the MC68HC11G5. Note that the MC68HC11E9 and MC68HC11A8 have slightly different RAM and register address ranges plus the internal EEPROM which should be disabled if not used.

**Figure 7** demonstrates the differences between the paging techniques by showing the overlap of the pages. The number and size of the pages can easily be modified by small changes to the page change routines and hardware.

#### Beyond 128 Kbytes

Both techniques may be scaled up with several port lines controlling address lines beyond address A15 with the addition of further change page routines and enhancing the return-from-interrupt routine to allow a return to a specific page in method A or the addition of further multiplexing logic in method B.

#### In Conclusion

The two methods described in detail are the basis for many other ways of controlling paging on a single large EPROM memory device or several smaller EPROMs. It is a simple matter to scale up or modify the techniques to suit a particular application or EPROM.

The software approach is the cheapest and allows for a main program of up to the full size of the EPROM while the combined hardware and software approach has a maximum main program size of 48 Kbytes (in this example) and no additional interrupt latency.

Application Note Appendix A — Software Paging Scheme

## Appendix A — Software Paging Scheme

|                                    | * * TESTS EXTENDED MEMORY CONTROL                                                                                                                                                                                                                                |            |                        |                                                             |  |  |  |  |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------|-------------------------------------------------------------|--|--|--|--|

|                                    | *  * For a single 1M bit (128K byte) EPROM split into 2 x 64K byte pages  * Al6 is connected to Port D(5) which then selects which half of  * the EPROM is being accessed. PD5 = 1 after reset since it is in  * the input state with a pull-up resistor to Vdd. |            |                        |                                                             |  |  |  |  |

|                                    | * * This code is written for the 68HC11G5 MCU but can be easily modified * to run on any 68HC11 device. The 68HC11G5 has a non-multiplexed                                                                                                                       |            |                        |                                                             |  |  |  |  |

|                                    | * address and dat  *  *                                                                                                                                                                                                                                          | ta bus in  | expanded mode.         |                                                             |  |  |  |  |

|                                    |                                                                                                                                                                                                                                                                  | *****      | ******                 | **********                                                  |  |  |  |  |

| 00000000                           | *<br>PORTA EQU                                                                                                                                                                                                                                                   |            | \$00                   |                                                             |  |  |  |  |

| 0000001                            | DDRA EQU                                                                                                                                                                                                                                                         |            | \$01                   |                                                             |  |  |  |  |

| 00000004                           | PORTB EQU                                                                                                                                                                                                                                                        |            | \$04                   |                                                             |  |  |  |  |

| 00000006<br>00000007               | PORTC EQU<br>DDRC EQU                                                                                                                                                                                                                                            |            | \$06<br>\$07           |                                                             |  |  |  |  |

| 00000008                           | PORTD EQU                                                                                                                                                                                                                                                        |            | \$08                   |                                                             |  |  |  |  |

| 00000009                           | DDRD EQU                                                                                                                                                                                                                                                         |            | \$09                   |                                                             |  |  |  |  |

| 00000024                           | TMSK2 EQU                                                                                                                                                                                                                                                        |            | \$24                   |                                                             |  |  |  |  |

| 00000025<br>00000040               | TFLG2 EQU                                                                                                                                                                                                                                                        |            | \$25                   |                                                             |  |  |  |  |

| 00000040                           | RTII EQU<br>RTIF EQU                                                                                                                                                                                                                                             |            | \$40<br>\$40           |                                                             |  |  |  |  |

| 00000026                           | PACTL EQU                                                                                                                                                                                                                                                        |            | \$26                   |                                                             |  |  |  |  |

| 0800000                            | DDRA7 EQU                                                                                                                                                                                                                                                        |            | \$80                   |                                                             |  |  |  |  |

| 00001000                           | REGS EQU<br>*                                                                                                                                                                                                                                                    |            | \$1000                 |                                                             |  |  |  |  |

|                                    |                                                                                                                                                                                                                                                                  | ******     | ******                 | *********                                                   |  |  |  |  |

|                                    | *  * RAM definitions (from \$0000 to \$01FF)                                                                                                                                                                                                                     |            |                        |                                                             |  |  |  |  |

|                                    | * *************************************                                                                                                                                                                                                                          |            |                        |                                                             |  |  |  |  |

|                                    | ******                                                                                                                                                                                                                                                           | ORG        | ************<br>\$0000 | **********                                                  |  |  |  |  |

| 00000000                           | PAGE                                                                                                                                                                                                                                                             | RMB        | 1                      | page number prior to interrupt                              |  |  |  |  |

| 00000001                           | TIME                                                                                                                                                                                                                                                             | RMB        | 2                      | counter value for real time interrupt routi                 |  |  |  |  |

| 0000000                            | *                                                                                                                                                                                                                                                                | T011       | 400                    | DODE D. F                                                   |  |  |  |  |

| 00000020<br>00000200               | NPAGE<br>ROMBASE                                                                                                                                                                                                                                                 | EQU<br>EQU | \$20<br>\$0200         | PORT D-5 page control line<br>Avoid RAM (from \$0 to \$1FF) |  |  |  |  |

| 0000f800                           | CHANGE                                                                                                                                                                                                                                                           | EQU        | \$F800                 |                                                             |  |  |  |  |

| 0000ffcc                           | VECTORS<br>*                                                                                                                                                                                                                                                     | EQU        | \$FFCC                 |                                                             |  |  |  |  |

|                                    | ***************************************                                                                                                                                                                                                                          |            |                        |                                                             |  |  |  |  |

|                                    |                                                                                                                                                                                                                                                                  |            | AIN PROGRAM            | ++++++++++++++++++                                          |  |  |  |  |

|                                    | *                                                                                                                                                                                                                                                                | +++++++    | ++++++++++++           | +++++++++++++++++                                           |  |  |  |  |

|                                    |                                                                                                                                                                                                                                                                  | e 0 (1st ) | half of EPROM)         |                                                             |  |  |  |  |

|                                    | *                                                                                                                                                                                                                                                                |            |                        |                                                             |  |  |  |  |

|                                    | *++++++++++++                                                                                                                                                                                                                                                    | ++++++++   | ++++++++++++           | +++++++++++++++++++++++++++++++++++++++                     |  |  |  |  |

|                                    | org                                                                                                                                                                                                                                                              | RO         | MBASE                  |                                                             |  |  |  |  |

|                                    | ******                                                                                                                                                                                                                                                           | *****      | ******                 | ************                                                |  |  |  |  |

|                                    |                                                                                                                                                                                                                                                                  | irect res  | et vector to pa        | ge 1                                                        |  |  |  |  |

|                                    | *                                                                                                                                                                                                                                                                | IICCC ICD  | cc vector to pa        | gc 1                                                        |  |  |  |  |

|                                    |                                                                                                                                                                                                                                                                  |            |                        | **********                                                  |  |  |  |  |

| 00000200 ce0200<br>00000203 7ef800 | RESETO                                                                                                                                                                                                                                                           | LDX<br>JMP | #RESET<br>CHGPAGE0     |                                                             |  |  |  |  |

| 00000203 761000                    |                                                                                                                                                                                                                                                                  |            |                        |                                                             |  |  |  |  |

|                                    | **********                                                                                                                                                                                                                                                       | ******     | ******                 | *************                                               |  |  |  |  |

|                                    | * 2nd                                                                                                                                                                                                                                                            | half of    | page 0 loop run        | ning in page 1                                              |  |  |  |  |

|                                    | *                                                                                                                                                                                                                                                                | nair or    | page o roop run        | ning in page i                                              |  |  |  |  |

|                                    | ******                                                                                                                                                                                                                                                           | *****      | ******                 | ***********                                                 |  |  |  |  |

| 00000206 181c0010                  | LOOPP0                                                                                                                                                                                                                                                           | BSET       | PORTA,Y,#\$10          | Toggle bit 4                                                |  |  |  |  |

| 0000020a 181d0010                  |                                                                                                                                                                                                                                                                  | BCLR       | PORTA,Y,#\$10          | got woturn address in 1                                     |  |  |  |  |

| 0000020e ce0216<br>00000211 7ef800 |                                                                                                                                                                                                                                                                  | LDX<br>JMP | #LOOPP1<br>CHGPAGE0    | get return address in page 1 jump to change page routine    |  |  |  |  |

|                                    | *                                                                                                                                                                                                                                                                |            |                        |                                                             |  |  |  |  |

|                                    | **********                                                                                                                                                                                                                                                       | ******     | ******                 | **********                                                  |  |  |  |  |

|                                    | *                                                                                                                                                                                                                                                                | Dool :     | timo interrunt         | service routine                                             |  |  |  |  |

|                                    | *                                                                                                                                                                                                                                                                |            |                        |                                                             |  |  |  |  |

#### **Application Note**

```

00000214 181e254001 RTISRV

BRSET TFLG2, Y, #RTIF, RTISERV

return if not correct interrupt source

This is an RTI because interrupt vector

00000219 3b

82

RTT

84

only points here when in page 1

85

0000021a

RTISERV

87

0000021a 8640

T.DAA

#%01000000

page 0 interrupt starts here

clear RTI flag

0000021c 18a725

0000021f 9602

88

STAA

TFLG2,Y

get the time counter

00000221 4c

00000222 b71004

90

INCA

increment counter

91

STAA

PORTB+REGS

store time in port B

00000222 B7100

00000225 de01

00000227 08

00000228 fd01

93

TNX

and copy back into RAM jump to RTI routine

94

STX

TIME

0000022a 7ef80a

RETRTI0

96

97

98

99

100

CHANGE PAGE ROUTINE

* This code must be executed with the I-bit set to prevent interrupts * during the change if it is a jump for an interrupt routine. * Otherwise PAGE could be updated and then another interrupt could

102

103

104

occur before the PAGE was changed causing the first interrupt

105

routine to return to the wrong page

106

* The PAGE variable is not required for a normal jump and so it does * not require the I-bit to be set (only the BSET is important).

107

108

109

This code is repeated for the same position in both pages

110

111

112

jump routine

113

CHANGE

Address for this routine is fixed

ORG

cycles

114

115

0001800

CHGPAGE 0

116

0000f800 8600

LDAA

#0 2

PAGE 2

set current page number = 0

0000f802 9700

117

STAA

PAGE 2 store page page number

PORTD,Y,#NPAGE 8 change page by setting PD-5

0000f804 181c0820

118

BSET

119

0000f808 6e00

JMP

0.X

3

This code is the same in both pages

120

122

return from interrupt routine running in page 0

123

124

125

check if interrupt occurred while code was running in page 1 and return to page 1 before the RTI command is performed

126

127

128

129

cycles

0000f80a

RETRTIO

130

0000f80a 9600

0000f80c 8101

get page the interrupt occured in is it page 1 if yes then change page

131

TIDAA

PAGE

2

132

CMPA

0000f80e 2701

0000f810 3b

BEQ

133

RTIPAGE0 3

otherwise, return from interrupt

134

RTT

12

135

RTIPAGE 0

136

0000f811 181c0820

BSET

PORTD,Y, #NPAGE 8 change page and return from interrupt

This codes is the same in both pages

137

0000f815 3b

RTT

12

138

139

140

141

142

143

ORG

VECTORS

0000ffcc 0200

0000ffce 0200

EVENT 2

145

FDB

RESET0

RESET0

EVENT 1

146

FDB

147

0000ffd0 0200

RESET0

TIMER OVERFLOW 2

0000ffd2 0200

0000ffd4 0200

INPUT CAPTURE 6 / OUTPUT COMPARE 7

INPUT CAPTURE 5 / OUTPUT COMPARE 6

148

FDB

RESETO

RESET0

149

FDB

150

0000ffd6 0200

RESET0

PULSE ACC INPUT

PULSE ACC OVERFLOW

151

0000ffd8 0200

0000ffda 0200

FDB

RESETO

152

RESET0

FDB

153

0000ffdc 0200

RESET0

TIMER OVERFLOW 1

INPUT CAPTURE 4 / OUTPUT COMPARE 5

154

0000ffde 0200

FDB

RESETO

155

0000ffe0 0200

RESET0

FDB

OUTPUT COMPARE 4

OUTPUT COMPARE 3

OUTPUT COMPARE 2

156

0000ffe2 0200

RESETO

157

0000ffe4 0200

FDB

RSEETO

0000ffe6 0200

158

FDB

RESET0

OUTPUT COMPARE 1

INPUT CAPTURE 3

INPUT CAPTURE 2

159

0000ffe8 0200

FDB

RESET0

160

0000ffea 0200

FDB

RESETO

0000ffec 0200

RESET0

161

FDB

162

0000ffee 0200

FDB

RESETO

INPUT CAPTURE 1

163

0000fff0 0214

FDB

RTTSRV

REAL TIME INTERRUPT

0000fff2 0200

164

FDB

RESET0

IRQ

165

0000fff4 0200

FDB

RESET0

XIRO

0000fff6 0200

166

FDB

RESETO

SWT

0000fff8 0200

ILLEGAL OPCODE

```

Application Note Appendix A — Software Paging Scheme

| 168<br>169<br>170                      | 0000fffa 0200<br>0000fffc 0200<br>0000fffe 0200 |                                                                                                                                                    | FDB<br>FDB<br>FDB | RESETO<br>RESETO<br>RESETO | COP<br>CLOCK MONITOR<br>RESET                                           |  |  |  |

|----------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------|-------------------------------------------------------------------------|--|--|--|

| 171<br>172                             |                                                 | ***************************************                                                                                                            |                   |                            |                                                                         |  |  |  |

| 173<br>174                             |                                                 | *+++++++++++++++++                                                                                                                                 | ++++++            | +++++++++++++              | ***************************************                                 |  |  |  |

| 175<br>176<br>177<br>178<br>179<br>180 |                                                 | * page 1                                                                                                                                           | (2nd ha           | alf of EPROM)              |                                                                         |  |  |  |

|                                        |                                                 | *                                                                                                                                                  |                   |                            |                                                                         |  |  |  |

|                                        |                                                 | **  * MAIN ROUTINE NOT UNDER INTERRUPT CONTROL                                                                                                     |                   |                            |                                                                         |  |  |  |

| 182                                    |                                                 | * MAIN ROUTINE NOT UNDER INTERRUPT CONTROL *                                                                                                       |                   |                            |                                                                         |  |  |  |

| 183<br>184                             |                                                 | ******                                                                                                                                             | *****             | *****                      | ***********                                                             |  |  |  |

| 185<br>186                             | 00000200 8e01ff                                 | RESET                                                                                                                                              | ORG<br>LDS        | ROMBASE<br>#\$01FF         |                                                                         |  |  |  |

| 187                                    | 00000203 bd021b                                 |                                                                                                                                                    | JSR               | SETUP                      | initialize RTI interrupt and DDRs                                       |  |  |  |

| 188<br>189                             | 00000206 86ff<br>00000208 181c0008              | LOOP1<br>LOOP                                                                                                                                      | LDAA<br>BSET      | #\$FF<br>PORTA,Y,#\$08     | Toggle bit 3                                                            |  |  |  |

| 190<br>191                             | 0000020c 181d0008<br>00000210 ce0206            |                                                                                                                                                    | BCLR<br>LDX       | PORTA,Y,#\$08<br>#LOOPP0   | set up jump to other page                                               |  |  |  |

|                                        |                                                 | T 00 DD 1                                                                                                                                          | JMP               | CHGPAGE1                   | go to other page                                                        |  |  |  |

| 194                                    | 00000216 4a                                     | LOOPP1                                                                                                                                             | DECA              |                            | return point from other page                                            |  |  |  |

| 195<br>196                             | 00000217 26ef<br>00000219 20eb                  |                                                                                                                                                    | BNE<br>BRA        | LOOP<br>LOOP1              | toggle port A start loop again                                          |  |  |  |

| 197                                    |                                                 | *                                                                                                                                                  |                   |                            |                                                                         |  |  |  |

| 198<br>199                             |                                                 | *                                                                                                                                                  |                   | IZATION ROUTINE            |                                                                         |  |  |  |

| 200<br>201                             |                                                 | ************                                                                                                                                       | ******            | ******                     | **************                                                          |  |  |  |

| 202<br>203                             | 0000021b 0f<br>0000021c 18ce1000                | SETUP                                                                                                                                              | SEI<br>LDY        | #\$1000                    | Register address offset                                                 |  |  |  |

| 204                                    | 00000220 86ff                                   |                                                                                                                                                    | LDAA              | #\$FF                      | Register address offset                                                 |  |  |  |

| 205<br>206                             | 00000222 b71001<br>00000225 b71008              |                                                                                                                                                    | STAA<br>STAA      | DDRA+REGS<br>PORTD+REGS    | make port A all outputs make sure port D-5 is written a 1               |  |  |  |

| 207<br>208                             | 00000228 b71009<br>0000022b 8640                |                                                                                                                                                    | STAA<br>LDAA      | DDRD+REGS<br>#%01000000    | and only then make all outputs                                          |  |  |  |

| 209                                    | 0000022d b71025                                 |                                                                                                                                                    | STAA              | TFLG2+REGS                 | clear RTI flag                                                          |  |  |  |

| 210<br>211                             | 00000230 b71024<br>00000233 0e                  |                                                                                                                                                    | STAA<br>CLI       | TMSK2+REGS                 | enable RTI interrupt                                                    |  |  |  |

| 212<br>213                             | 00000234 39                                     | *****                                                                                                                                              | RTS               | *****                      | ***********                                                             |  |  |  |

| 214                                    |                                                 | *                                                                                                                                                  |                   |                            |                                                                         |  |  |  |

| 215<br>216<br>217                      |                                                 | * Redirect to the Real time interrupt service routine  * Page 1 routine for service routine located in page 0  *********************************** |                   |                            |                                                                         |  |  |  |

| 218                                    | 00000005 101 054001                             | *                                                                                                                                                  |                   |                            |                                                                         |  |  |  |

| 219<br>220                             | 00000235 181e254001<br>0000023a 3b              | INTRI                                                                                                                                              | BRSET<br>RTI      | TFLG2,Y,#RTIF,             | return if not correct interrupt source                                  |  |  |  |

| 221<br>222                             |                                                 | *                                                                                                                                                  |                   |                            | This is an RTI because interrupt vector only points here when in page 1 |  |  |  |

| 223                                    |                                                 | *                                                                                                                                                  |                   | 1                          | 111                                                                     |  |  |  |

| 224<br>225                             | 0000023b<br>0000023b ce021a<br>00000233 73f800  | GOODINT                                                                                                                                            | LDX               | cycles<br>#RTISERV 3       | get the interrupt entry point in page 0                                 |  |  |  |

| 226<br>227                             |                                                 | *                                                                                                                                                  | JMP               | CHPAGE! 3                  | jump to change page routine                                             |  |  |  |

| 228<br>229                             |                                                 | ******                                                                                                                                             | ******            | *****                      | ********                                                                |  |  |  |

| 230                                    |                                                 | *                                                                                                                                                  |                   |                            |                                                                         |  |  |  |

| 231<br>232                             |                                                 | * CHANGE PAGE ROUTINE *                                                                                                                            |                   |                            |                                                                         |  |  |  |

| 233<br>234                             |                                                 | * This code must be executed with the I-bit set to prevent interrupts                                                                              |                   |                            |                                                                         |  |  |  |

| 235                                    |                                                 | * during the change if it is a jump for an interrupt routine.  * Otherwise PAGE could be updated and then another interrupt could                  |                   |                            |                                                                         |  |  |  |

| 236<br>237                             |                                                 | * occur before the PAGE was changed causing the first interrupt * routine to return to the wrong page.                                             |                   |                            |                                                                         |  |  |  |

| 238<br>239                             |                                                 | * The PAGE variable is not required for a normal jump and so it does * not require the I-bit to be set (only the BCLR is important).               |                   |                            |                                                                         |  |  |  |

| 240<br>241                             |                                                 | * This code is repeated for the same position in both pages                                                                                        |                   |                            |                                                                         |  |  |  |

| 242<br>243                             |                                                 | * jump routine                                                                                                                                     |                   |                            |                                                                         |  |  |  |

| 244<br>245                             |                                                 | * ORG<br>*                                                                                                                                         | CHANGE            | cycles                     | Address for this routine is fixed                                       |  |  |  |

|                                        | 0000f800                                        | CHGPAGE1                                                                                                                                           | T D 3 3           |                            | got gurrent page number 1                                               |  |  |  |

| 248                                    | 0000f802 9700                                   |                                                                                                                                                    | LDAA<br>STAA      | #\$1 2<br>PAGE 2           | set current page number = 1 store page page number                      |  |  |  |

|                                        | 0000f804 181d0820<br>0000f808 6e00              |                                                                                                                                                    | BCLR<br>JMP       | PORTD,Y,#NPAGE<br>0,X 3    | 8 Change page by clearing PD-5 This code is the same in both pages      |  |  |  |

| 251                                    |                                                 | *                                                                                                                                                  |                   | •                          |                                                                         |  |  |  |

## **Application Note**

```

252

253

return from interrupt routine running in page 0

255

check if interrupt occurred while code was running in page 1 and return to page 0 before the RTI command is performed

256

258

*******************

259

cycles

261

0000f80a

RETRTT1

0000f80a 9600

get page the interrupt occured in

is it page 0

if yes then change page

262

LDAA

PAGE

2

0000f80c 8100

RTIPAGE1 3

264

0000f80e 2701

BEO

0000f810 3b

otherwise, return from interrupt

265

RTI

12

RTIPAGE1

0000f811 181d0820

BCLR

PORTD,Y, \# NPAGE - 8 change page and return from interrupt 12 This codes is the same in both pages

267

268

0000f815 3b

RTI

270

271

272

VECTORS

273

274

275

ORG

VECTORS

0000ffcc 0200

EVENT 2

276

FDB

RESET

277

0000ffce 0200

RESET

EVENT 1

FDB

278

0000ffd0 0200

RESET

TIMER OVERFLOW 2

INPUT CAPTURE 6 / OUTPUT COMPARE 7

INPUT CAPTURE 5 / OUTPUT COMPARE 6

279

0000ffd2 0200

FDB

RESET

280

0000ffd4 0200

FDB

RESET

SCI

SPI

281

0000ffd6 0200

RESET

282

0000ffd8 0200

FDB

RESET

SPI

PULSE ACC INPUT

PULSE ACC OVERFLOW

TIMER OVERFLOW 1

INPUT CAPTURE 4 / OUTPUT COMPARE 5

OUTPUT COMPARE 4

OUTPUT COMPARE 3

OUTPUT COMPARE 2

OUTPUT COMPARE 2

0000ffda 0200

283

FDB

RESET

284

285

0000ffdc 0200

FDB

RESET

0000ffde 0200

RESET

FDB

0000ffe0 0200

RESET

286

FDB

287

0000ffe2 0200

FDB

RESET

288

0000ffe4 0200

FDB

RESET

0000ffe6 0200

FDB

RESET

OUTPUT COMPARE 1

INPUT CAPTURE 3

INPUT CAPTURE 2

INPUT CAPTURE 1

290

0000ffe8 0200

FDB

RESET

291

0000ffea 0200

RESTE

FDB

0000ffec 0200

RESET

293

0000ffee 0200

FDB

RESET

294

0000fff0 0235

FDB

INTRI

REAL TIME INTRRUPT

295

0000fff2 0200

RESET

296

0000fff4 0200

FDB

RESET

XIRQ

297

0000fff6 0200

FDB

RESET

SWI

298

0000fff8 0200

RESET

ILLEGAL OPCODE

0000fffa 0200

0000fffc 0200

299

FDB

RESET

CLOCK MONITOR

300

FDB

RESET

RESET

302

```

## Appendix B — Hardware and Software Paging Scheme

| for a single 1M bit (12                            | ONTROL                                                            |                     |

|----------------------------------------------------|-------------------------------------------------------------------|---------------------|

|                                                    | 8K byte) EEPROM split i<br>48K COMMON PAGE<br>16K PAGES 0,1,2,3,4 | nto 48KB + 5 x 16KB |

| controlled by PD5 and A<br>This ensures that Addre |                                                                   | PD5+A14+A15)        |

| SOURCE CODE<br>ADDRESS                             |                                                                   | EPROM<br>ADDRESS    |

| 0000                                               | PAGE 0                                                            | - 00000             |

| 4000                                               | MAIN PAGE                                                         | - 04000             |

| 0000                                               | PAGE 1                                                            | - 10000             |

| 0000                                               | PAGE 2                                                            | - 14000             |

| 0000                                               | PAGE 3                                                            | 10000               |

| 0000                                               | PAGE 4                                                            | - 10000             |

| 3FFF                                               |                                                                   | -   1FFFF           |

| B<br>                                              | +                                                                 |                     |

|                                                    | +                                                                 | - A14               |

|                                                    |                                                                   |                     |

|                                                    |                                                                   |                     |

| A  <br>  MUX                                       | <br>                                                              | A15                 |

| PD4 MUX                                            | <br>  <br>                                                        | 1M BIT EPROM        |

| PD5                                                | <br> <br> <br>                                                    | 1M BIT              |

| PD5                                                |                                                                   | 1M BIT<br>EPROM     |

| PD5A                                               |                                                                   | 1M BIT<br>EPROM     |

# **Application Note**

| 81<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>90<br>91<br>92<br>93<br>95<br>97<br>99<br>101 | 00000000<br>00000001<br>00000004<br>00000007<br>00000008<br>00000009<br>00000024<br>00000025<br>00000040<br>00000040<br>00000026<br>00000080<br>00000080 | PORTA DDRA PORTB PORTC DDRC PORTD DDRD TMSK2 TFLG2 RTII RTIF PACTL DDRA7 REGS * ********************************** | *****                                                            | EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU | \$00<br>\$01<br>\$04<br>\$06<br>\$07<br>\$08<br>\$09<br>\$24<br>\$25<br>\$40<br>\$40<br>\$26<br>\$80<br>\$1000 | 68HC11G5 only 68HC11E9 only                                                                                                                                            |  |  |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 99                                                                                            |                                                                                                                                                          | * RAM definitions                                                                                                  |                                                                  |                                                                    |                                                                                                                |                                                                                                                                                                        |  |  |

| 100<br>101                                                                                    |                                                                                                                                                          | * ************************************                                                                             |                                                                  |                                                                    |                                                                                                                |                                                                                                                                                                        |  |  |

| 102<br>103                                                                                    | 0000000                                                                                                                                                  | *<br>TIME                                                                                                          | ORG                                                              | \$0000<br>RMB                                                      | 2                                                                                                              | Real time interrupt routine counter                                                                                                                                    |  |  |

| 104<br>105                                                                                    | 00000200                                                                                                                                                 | * ROMBASE 0                                                                                                        |                                                                  | EOU                                                                | \$0200                                                                                                         | Avoid RAM (from \$0 to \$1FF)                                                                                                                                          |  |  |

| 106<br>107<br>108                                                                             | 00000200<br>00000400<br>0000ffcc                                                                                                                         | ROMBASEU<br>ROMBASE1<br>VECTORS                                                                                    |                                                                  | EQU<br>EQU                                                         | \$0400<br>\$FFCC                                                                                               | AVOIG RAM (IIOM \$0 to \$1FF)                                                                                                                                          |  |  |

| 109                                                                                           |                                                                                                                                                          | *****                                                                                                              |                                                                  |                                                                    | ******                                                                                                         |                                                                                                                                                                        |  |  |

| 110<br>111<br>112<br>113<br>114<br>115<br>116                                                 |                                                                                                                                                          | * MAIN<br>* PAGE<br>* PAGE<br>* PAGE                                                                               | = \$04000 - 1<br>= \$10000 - 2<br>= \$14000 - 3<br>= \$18000 - 3 | \$0FFFF<br>\$13FFF<br>\$17FFF<br>\$1BFFF                           | (A16=0)<br>(A16=1,A15=0,A14<br>(A16=1,A15=0,A14<br>(A16=1,A15=1,A14                                            | <pre>l=0) =&gt; PAGE0=%00100000 =&gt; START=%001XX000 l=0) =&gt; PAGE1=%00000000 l=1) =&gt; PAGE2=%0001000 l=0) =&gt; PAGE3=%00010000 l=1) =&gt; PAGE4=%00011000</pre> |  |  |

| 117<br>118                                                                                    |                                                                                                                                                          | * PAGEn                                                                                                            | is added to D(4) and D(                                          |                                                                    | xxx to give the s                                                                                              | state of port                                                                                                                                                          |  |  |

| 119<br>120<br>121<br>122<br>123<br>124<br>125                                                 | 00000000<br>00000020<br>00000000<br>00000008<br>00000010<br>00000018                                                                                     | START PAGE0 PAGE1 PAGE2 PAGE3 PAGE4                                                                                |                                                                  | EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU                             | \$00<br>\$20<br>\$00<br>\$08<br>\$10<br>\$18                                                                   |                                                                                                                                                                        |  |  |

| 126<br>127<br>128<br>129                                                                      |                                                                                                                                                          | * ********  *+++++++++++++++++++++++++                                                                             | * * * * * * * * * * * * * * * * * * *                            | ***********                                                        | *************************************                                                                          |                                                                                                                                                                        |  |  |

| 130<br>131<br>132                                                                             |                                                                                                                                                          | *<br>*<br>*                                                                                                        | page 0 (1                                                        | st half                                                            | of EPROM)                                                                                                      |                                                                                                                                                                        |  |  |

| 133<br>134<br>135                                                                             | 00000200 181c0008<br>00000204 181d0008<br>00000208 7e4014                                                                                                | *                                                                                                                  | ++++++++++                                                       | ++++++<br>org<br>BSET                                              | ++++++++++++++++++++++++++++++++++++++                                                                         | +++++++++++++++++++++++++++++++++++++++                                                                                                                                |  |  |

| 136<br>137                                                                                    |                                                                                                                                                          |                                                                                                                    |                                                                  | BCLR<br>JMP                                                        | PORTA,Y,#\$08<br>MAINO                                                                                         | Toggle Port A-3 return to main page                                                                                                                                    |  |  |