# Programmable Timer

Fundamentals and Applications

MC6840

PERPHERALS

Doing more so your processor can do more

# MC6840 PROGRAMMABLE TIMER FUNDAMENTALS AND APPLICATIONS

Prepared by

NMOS Microcomputer Systems Applications

Austin, Texas

Motorola reserves the right to make changes to any products herein to improve reliability, function or design. Although the information in this document has been carefully reviewed for broad application, Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

Second Edition ©MOTOROLA INC. 1981 "All Rights Reserved"

## **TABLE OF CONTENTS**

| CHAPTE              | R 1 INTRODUCTION                                                                             | 1-1  |

|---------------------|----------------------------------------------------------------------------------------------|------|

| 1.0<br>1.1<br>1.1.1 | INTRODUCTION TO THE MC6840 PROGRAMMABLE TIMER MODULE (PTM) THE FOUR BASIC MODES OF OPERATION | 1-1  |

| 1.1.2               | Single Shot Mode                                                                             |      |

| 1.1.3               | Period Measurement Mode                                                                      | 1-2  |

| 1.1.4               | Pulse Width Measurement Mode                                                                 | 1-2  |

| CHAPTE              | R 2 INTERFACING THE PTM TO THE MPU                                                           | 2-1  |

| 2.0                 | INTERFACING THE PTM TO THE MC6800 OR MC6802                                                  | 2-1  |

| 2.1                 | INTERFACING THE MC6840 PTM TO A NON-MOTOROLA MPU                                             | 2-3  |

| 2.2                 | 8085 INTERFACE                                                                               | 2-3  |

| 2.3                 | MC68A40 SIGNAL DERIVATION                                                                    | 2-4  |

| 2.3.1               | Chip Selects CS1, $\overline{\text{CS0}}$ and R/ $\overline{\text{W}}$                       | 2-4  |

| 2.3.2               | Enable (E)                                                                                   |      |

| 2.3.3               | RESET (R)                                                                                    |      |

| 2.3.4               | IRQ                                                                                          |      |

| 2.3.5               | Read/Write Timing                                                                            |      |

| 2.3.6               | Summary                                                                                      |      |

| 2.4                 | 8080 INTERFACE                                                                               | 2-10 |

| CHAPTE              | R 3 SOFTWARE INITIALIZATION                                                                  | 3-1  |

| 3.0                 | INTRODUCTION                                                                                 | 3-1  |

| 3.1                 | RESETS                                                                                       |      |

| 3.1.1               | Hardware                                                                                     |      |

| 3.1.2               | Software                                                                                     |      |

| 3.2                 | COUNTER INITIALIZATION                                                                       |      |

| 3.3                 | COUNTER ENABLE                                                                               |      |

| 3.4                 | COUNTER LATCH INITIALIZATION                                                                 |      |

| 3.5                 | EXAMPLE COUNTER PROGRAMMING                                                                  |      |

| 3.5.1               | Writing to a Timer Latch                                                                     |      |

| 3.5.2               | Reading from a Timer Counter                                                                 |      |

| 3.6                 | CONTROL REGISTER PROGRAMMING                                                                 |      |

| 3.6.1               | Individual Bits                                                                              |      |

| 3.7                 | CONTINUOUS OPERATION MODE                                                                    |      |

| 3.7.1               | 16-Bit Operation                                                                             |      |

| 3.7.2               | Dual 8-Bit Operation                                                                         |      |

| 3.8                 |                                                                                              | 3-6  |

| 004                 | SINGLE SHOT MODE                                                                             |      |

| 3.8.1               | 16-Bit Operation                                                                             |      |

| 3.8.2               | 16-Bit Operation                                                                             | 3-7  |

| 3.8.2<br>3.9        | 16-Bit Operation                                                                             | 3-7  |

| 3.8.2               | 16-Bit Operation                                                                             | 3-7  |

| CHAPTER 4  | 4 SAMPLE SOFTWARE INITIALIZATION ROUTINE         | 4-1        |

|------------|--------------------------------------------------|------------|

| 4.0        | INTRODUCTION                                     | 4-1        |

| 4.1        | PTM INITIALIZATION                               |            |

| CHAPTER !  | 5 APPLICATIONS                                   | 5-1        |

| 5.0        | INTRODUCTION                                     |            |

| 5.1        | PROGRAMMING FOUR MODES ON THE PROGRAMMABLE TIMER | 5-1        |

| 5.1.1      | The 16-Bit Continuous Mode                       | 5-1        |

| 5.1.2      | The Single Shot Mode                             | 5-1        |

| 5.1.3      | Period Measurement Mode                          | 5-1        |

| 5.1.4      | Pulse Width Measurement Mode                     |            |

| 5.2        | PTM THERMOMETER                                  |            |

| 5.3        | MC6840 PTM CONTROLLED REAL-TIME TIMER            | 5-8        |

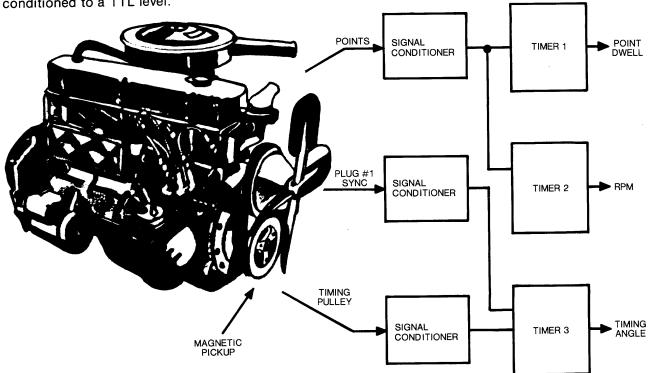

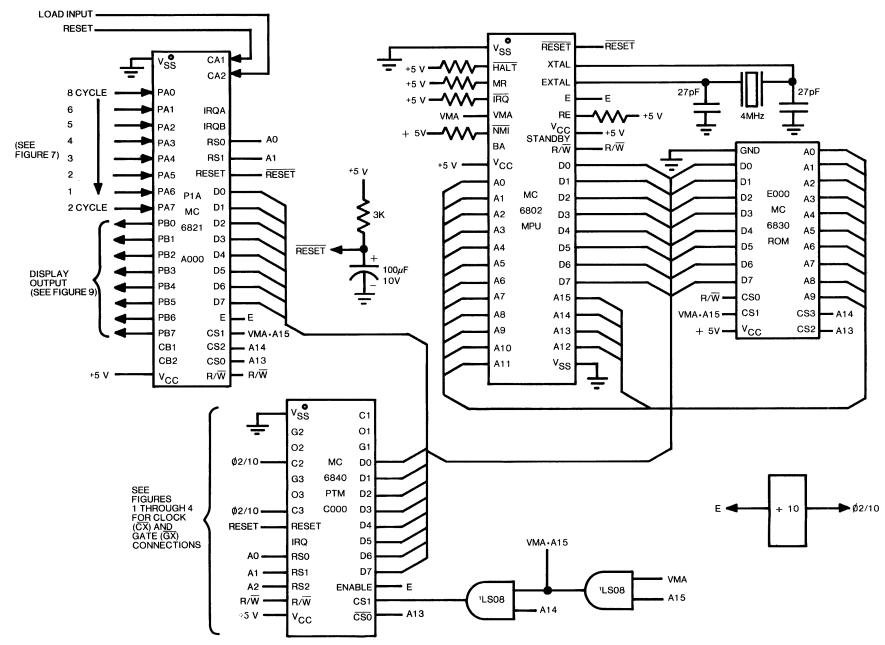

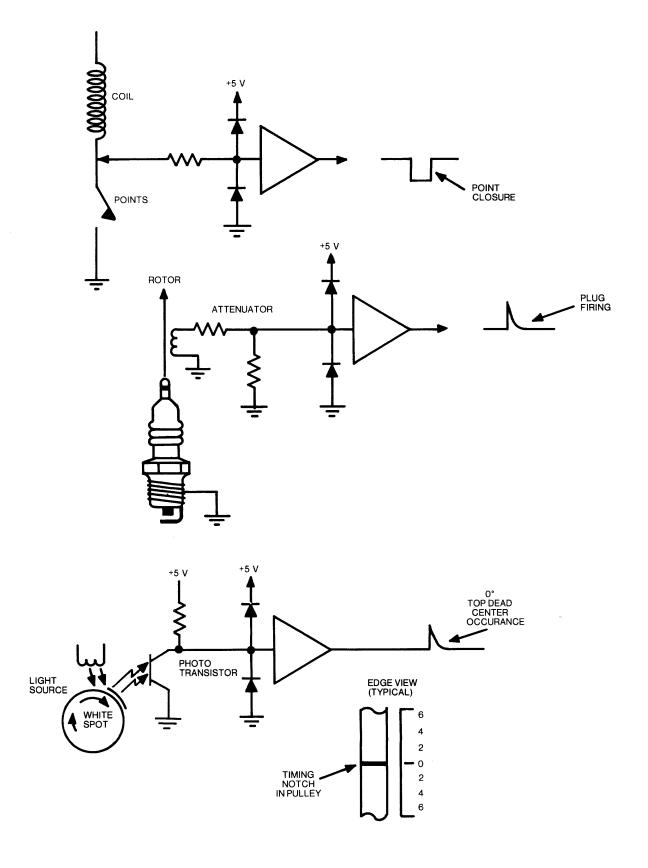

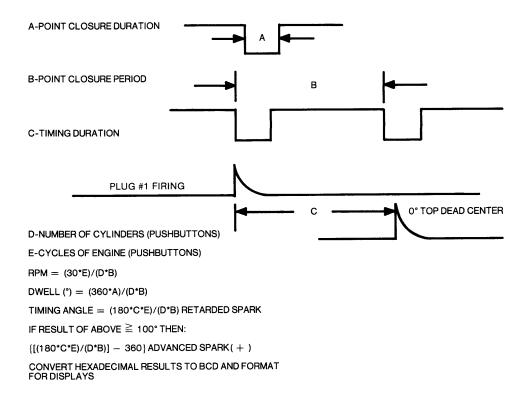

| 5.4        | MC6840/MC6802 MPU-PTM CONTROLLED ENGINE ANALYZER | 5-9        |

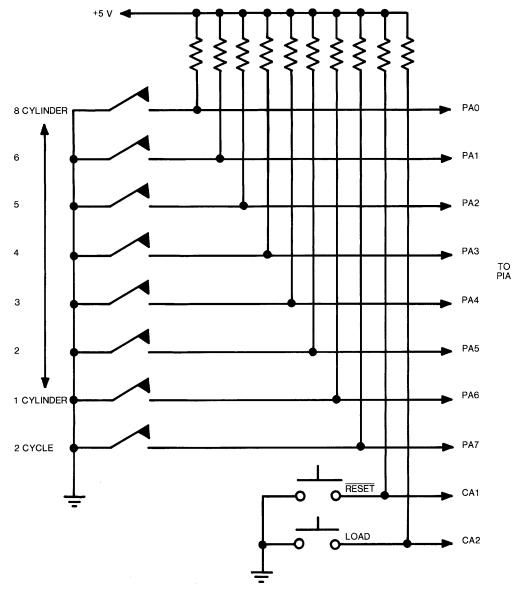

| 5.5        | ENGINE INPUT HARDWARE                            | 5-11       |

| 5.6        | MANUAL INPUT HARDWARE                            | 5-15       |

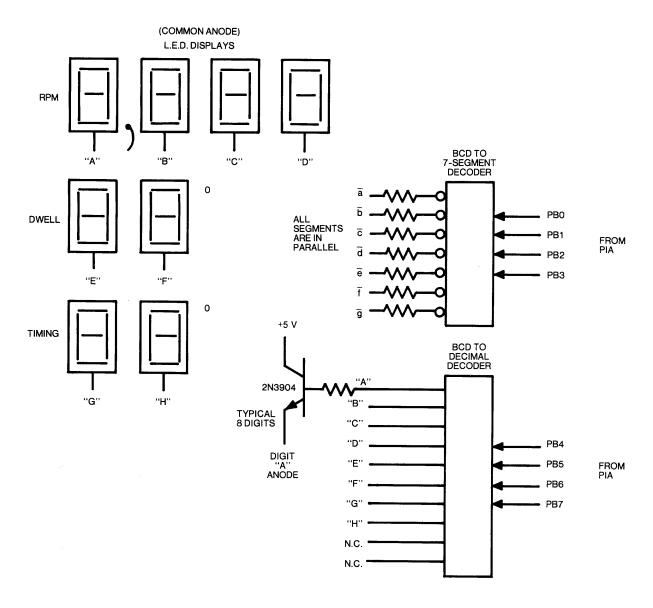

| 5.7        | DISPLAY HARDWARE                                 |            |

| 5.8        | MPU INTERCONNECTION                              | 5-17       |

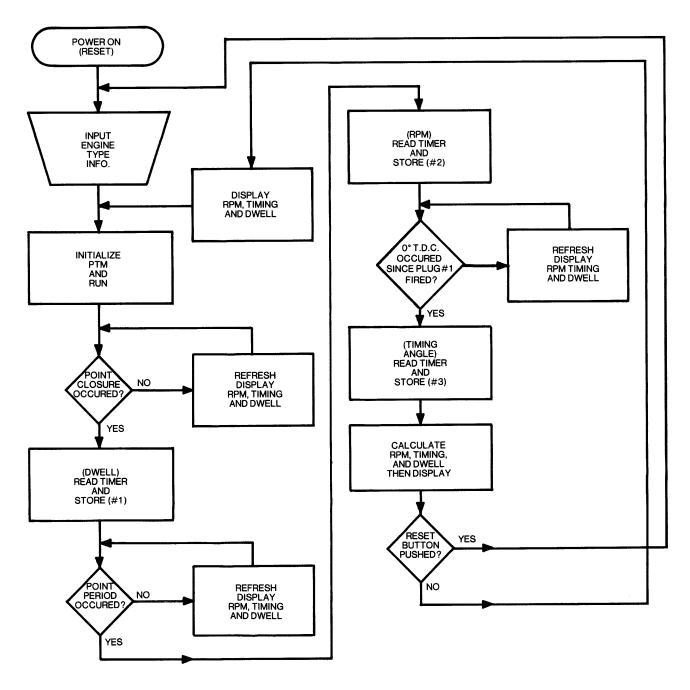

| 5.9        | OPERATION                                        |            |

| 5.9.1      | Power On Reset                                   | 5-18       |

| 5.9.2      | Input Engine Type Information                    | 5-18       |

| 5.9.3      | Initialize the PTM and Run                       | 5-19       |

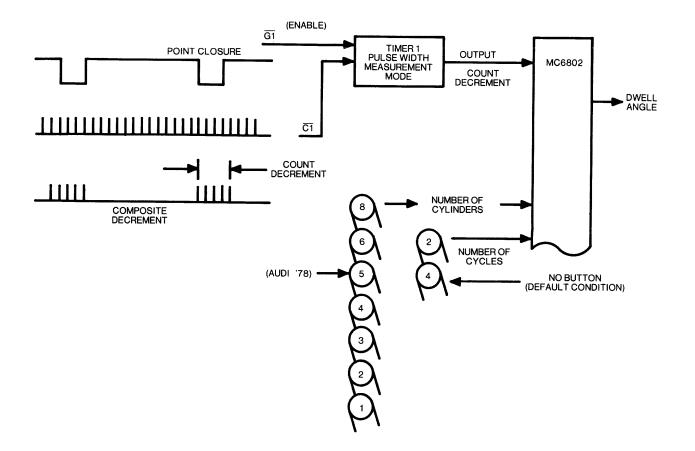

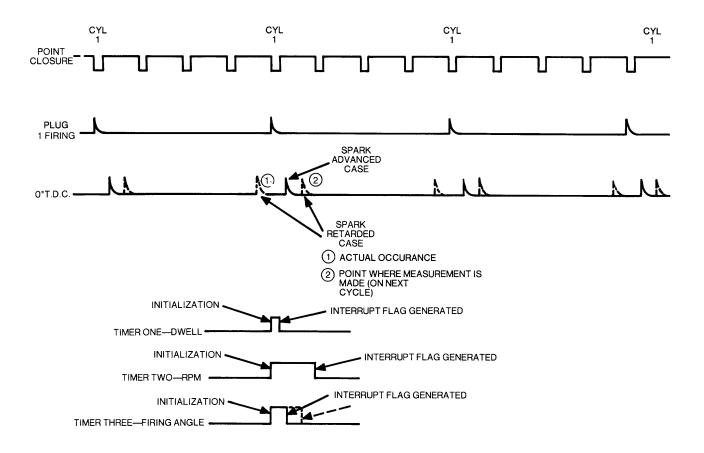

| 5.9.4      | Point Closure                                    |            |

| 5.9.5      | Read Timer and Store (Dwell)                     | 5-19       |

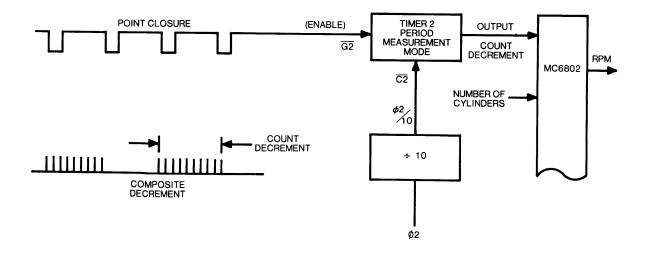

| 5.9.6      | Point Period                                     | 5-20       |

| 5.9.7      | Read Timer and Store (RPM)                       | 5-20       |

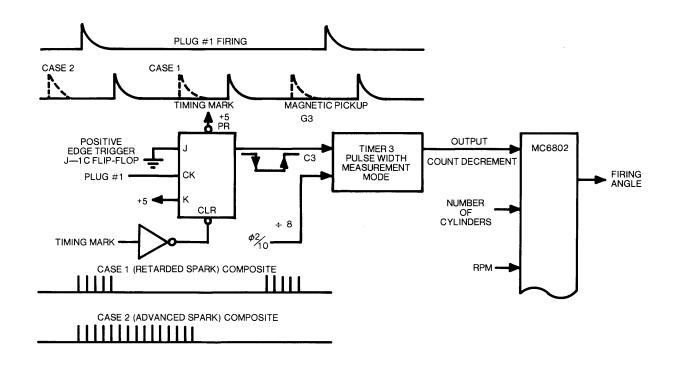

| 5.9.8      | 0º T.D.C. Occurred Since Plug #1 Fired?          | 5-20       |

| 5.9.9      | Read Timer and Store (Timing Angle)              | 5-20       |

| 5.9.10     | Calculate                                        | 5-20       |

| 5.9.11     | Reset Button Pushed?                             | 5-20       |

| 5.10       | POWER                                            |            |

| 5.11       | SUMMARY                                          | 5-20       |

| APPENDIX A | A ELECTRICAL AND MECHANICAL DATA                 | <b>A-1</b> |

| APPENDIX I | MC6800/02 MICROPROCESSOR INSTRUCTION SET         | B-1        |

## LIST OF FIGURES

| CHAPT | ER 2                                                |      |

|-------|-----------------------------------------------------|------|

| 2-1   | PTM INTERFACED TO THE MPU                           | 2-1  |

| 2-2   | PTM INTERFACED TO THE MEK6800D2                     | 2-2  |

| 2-3   | MEK6800D2 PATCH AREA BUILD-UP                       | 2-2  |

| 2-4   | 8085 IO MAPPED MC6840 PTM                           | 2-3  |

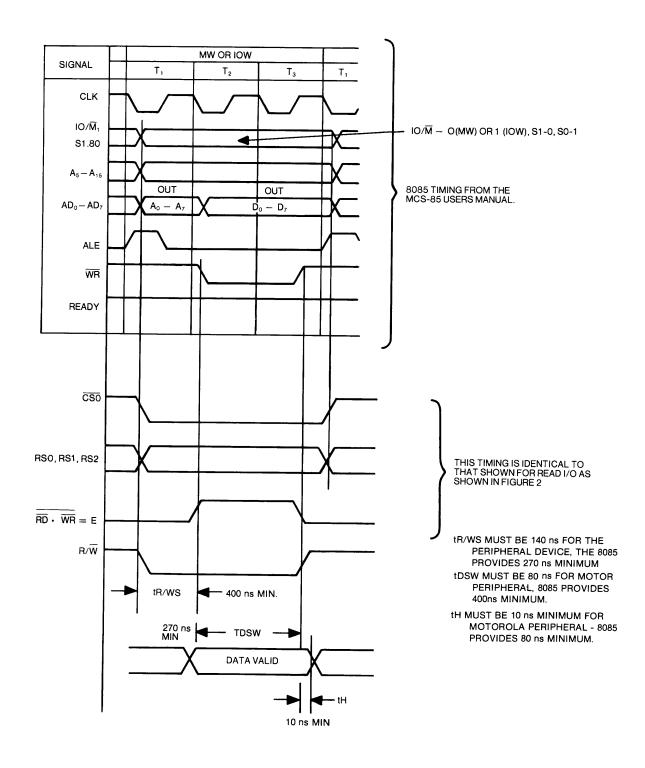

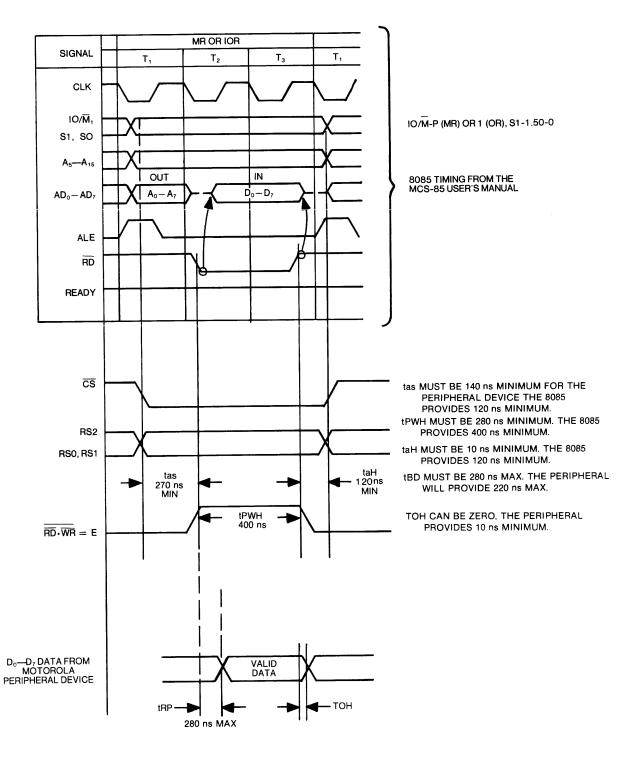

| 2-5   | 8085/MC68A40 I/O WRITE AND READ TIMING              | 2-5  |

| 2-6   | 8085 MEMORY MAPPED MC6840 PTM                       | 2-11 |

| 2-7   | 8080 MEMORY MAPPED MC6840 PTM                       | 2-12 |

| CHAPT | ER 4                                                |      |

| 4-1   | PTM CASCADED OPERATION                              | 4-1  |

| 4-2   | SAMPLE MC6840 PRINTOUT                              | 4-2  |

| 4-3   | MC6840 CONTROL REGISTER PROGRAMMING                 | 4-3  |

| CHAPT | ER 5                                                |      |

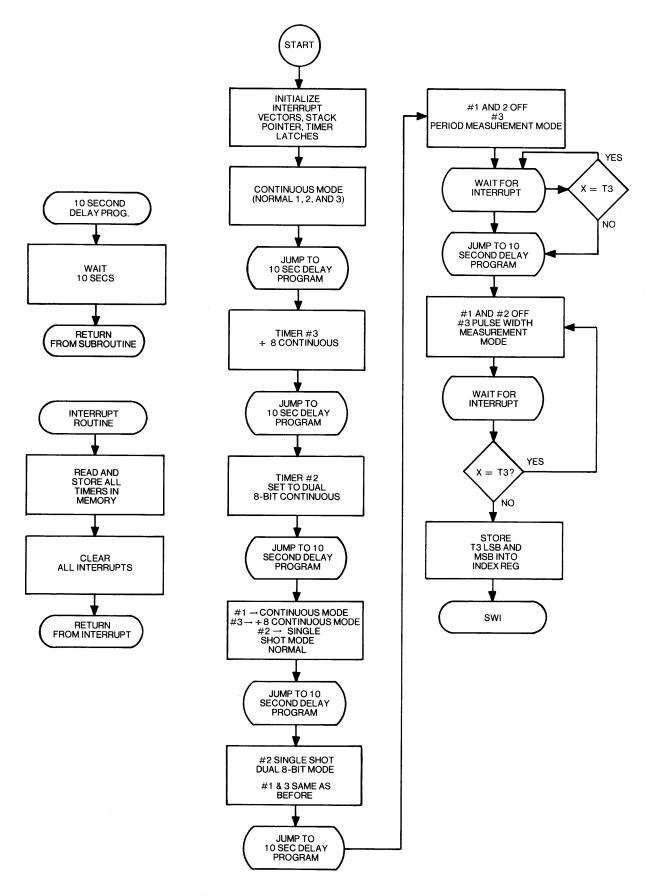

| 5-1   | PTM FOUR MODE PROGRAM FLOW CHART                    |      |

| 5-2   | PTM FOUR MODE PROGRAM ASSEMBLY LISTING              |      |

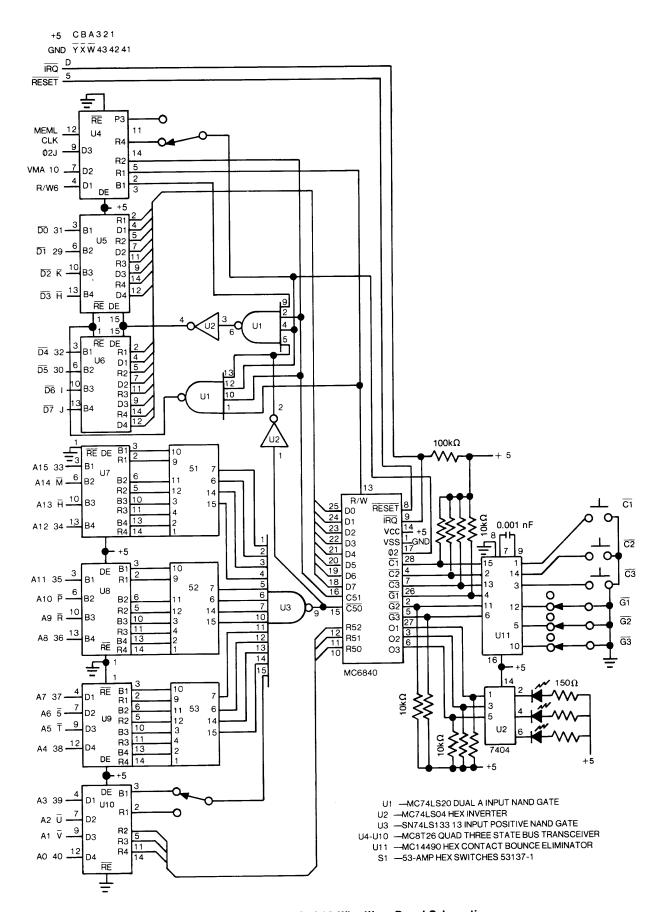

| 5-3   | PTM MC6840 WIRE WRAP BOARD SCHEMATIC                | 5-7  |

| 5-4   | TEMPERATURE MONITORING DEVICE                       |      |

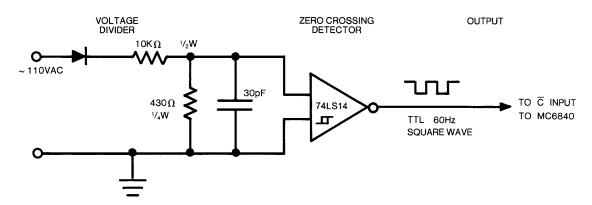

| 5-5   | HARDWARE SCHEMATIC OF TTL CONDITIONER               | 5-9  |

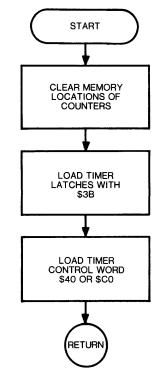

| 5-6   | FLOW CHART TO INITIALIZE TIMER                      |      |

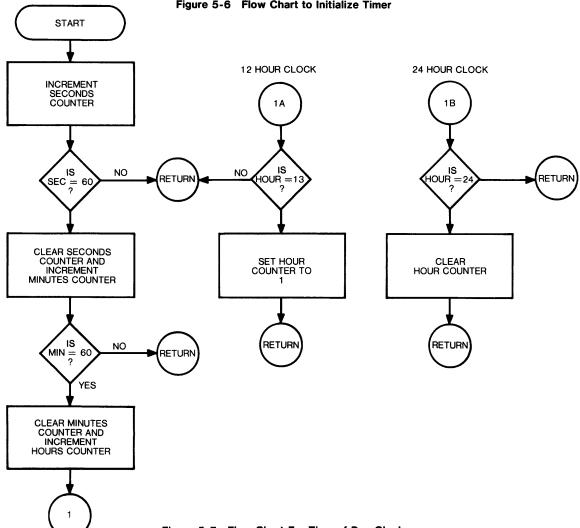

| 5-7   | FLOW CHART FOR TIME OF DAY CLOCK                    | 5-10 |

| 5-8   | DIGITAL ENGINE ANALYZER                             | 5-11 |

| 5-9   | DWELL ANGLE                                         | 5-12 |

| 5-10  | RPM                                                 | 5-12 |

| 5-11  | TIMING ANGLE                                        | 5-13 |

| 5-12  | 4 CYLINDER, 4 CYCLE ENGINE                          | 5-13 |

| 5-13  | ENGINE ANALYZER-SYSTEM INTERCONNECTION AND DECODING | 5-14 |

| 5-14  | INPUT CONTROLS                                      |      |

| 5-15  | SIGNAL CONDITIONERS                                 | 5-16 |

| 5-16  | DISPLAY SYSTEM                                      | 5-17 |

| 5-17  | ENGINE ANALYZER FLOW CHART                          | 5-18 |

| 5-18  | SOFTWARE CALCULATIONS                               | 5-21 |

## **LIST OF TABLES**

|   | u | Α | ~ |   | $\mathbf{p}$ | 2 |

|---|---|---|---|---|--------------|---|

| L | п | А | 1 | ᆮ | п            | Z |

| 2-1<br>2-2 | 8085/MC68A40 ADDRESSING                |     |

|------------|----------------------------------------|-----|

| СНАРТ      | ER 3                                   |     |

| 3-1        | REGISTER SELECTION                     | 3-1 |

| 3-2        | REGISTER SELECTION AS MEMORY LOCATIONS | 3-2 |

# CHAPTER 1 INTRODUCTION

#### 1.0 INTRODUCTION TO THE MC6840 PROGRAMMABLE TIMER MODULE (PTM)

The purpose of using the MC6840 PTM is to allow the MPU and its associated RAM to be free of the timing function task. The three timers in the PTM will not bother the MPU until they have a result of their pre-programmed task. This is especially valuable when long Time Outs are involved.

The MC6840 is a totally compatible member of the M6800 family of peripheral parts. The eight write only and seven read only registers of the PTM appear as eight memory locations to the MPU. The following chapters contain complete information in interfacing the PTM to the M6800 MPU family, interfacing the PTM to a non-Motorola MPU, software initialization, applications, and ordering information.

If the user is not familiar with the M6800 instructions used throughout this manual, refer to the M6800 Microprocessor Instruction Set Summary (Programming Card). This card is available through your local Motorola Sales Office.

When refering to an MPU address or data in this manual, hexadecimal numbers are used exclusively and are shown as \$XXXX. Earlier MC6840 data sheets referred to the Period Measurement Mode as the Frequency Comparison Mode, and the Pulse Width Measurement Mode as the Pulse Width Comparison Mode. The electrical function of these modes has not been altered. The mode names were changed in order to more accurately reflect the operation of the timers.

The PTM consists of three independent timers each capable of four basic modes of operation. Each mode, in turn, has several programmable variations that may be used to suit an individual application.

#### 1.1 THE FOUR BASIC MODES OF OPERATION

#### 1.1.1 Continuous Mode

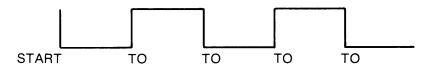

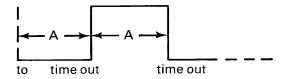

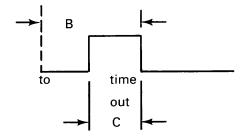

In this mode the timer counts down its initial programmed timer data word (16 bits) to zero. This is called a Time Out (TO) and may generate an interrupt if it is so programmed. The continuous output is:

The output is low for the first Time Out period, and changes state for each subsequent Time Out period. This produces a 50% duty cycle square twice the duration of the Time Out.

#### 1.1.2 Single-Shot Mode

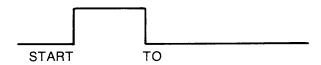

The Single-Shot Mode is similar to the continuous mode except that the output produces only one high pulse for the Time Out period.

In this mode a timer operates as a programmable, retriggerable one shot.

#### 1.1.3 Period Measurement Mode

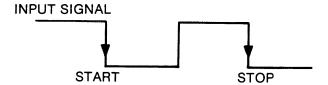

One operation performed in this mode is to measure the period (reciprocal of the frequency) of a given digital signal:

When the pulse goes low the first time, the timer starts counting down from its programmed number. When the signal goes low again, the timer stops counting down and generates an interrupt. The MPU can now determine the frequency easily (1/p = f).

#### 1.1.4 Pulse Width Measurement Mode

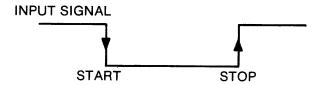

The width of a given pulse may be determined by using this mode. The "down-time" of a digital signal can be measured in the same manner as in the Period Measurement Mode:

In this mode the timer starts decrementing when the input pulse goes low and stops decrementing and generates an interrupt when the input pulse returns high.

There are many variations of operation using the four previously described modes. The three timers are independent, and each may be:

- 1. Cascaded with another timer.

- 2. Operated in any of three basic modes.

- 3. Programmed to use the internal clock or an external clock.

The initialization chapter fully explains all the points available to the user.

# CHAPTER 2 INTERFACING THE PTM TO THE MPU

#### 2.0 INTERFACING THE PTM TO THE MC6800 OR MC6802

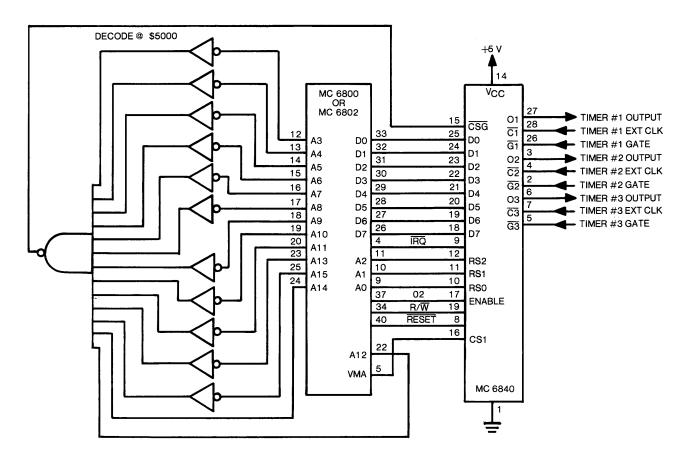

The Programmable Timer (MC6840), as with all Motorola 6800 family peripherals, interfaces easily to the Motorola MPU line. Figure 2-1 shows the PTM interfaced to either an MC6802 or MC6800. The base PTM address has been completely decoded for \*\$5000. The two hex inverters and a thirteen input NAND gate LS devices decode the address and minimize the loading on the address lines. Any valid base address desired from \*\$0010 through \*\$FFF8 may be completely decoded with a different configuration of the same hardware. If complete address decoding is not necessary, as in a minimum parts count system, two packs may be eliminated. This must be done with care to avoid addressing conflicts.

The three least significant bits of the 16-bit address lines are connected directly to the three register select (RSX) inputs. These three least significant bits, in conjunction with the state of the Read/Write line, select the seven Read Only and eight Write Only registers accessible to the MPU.

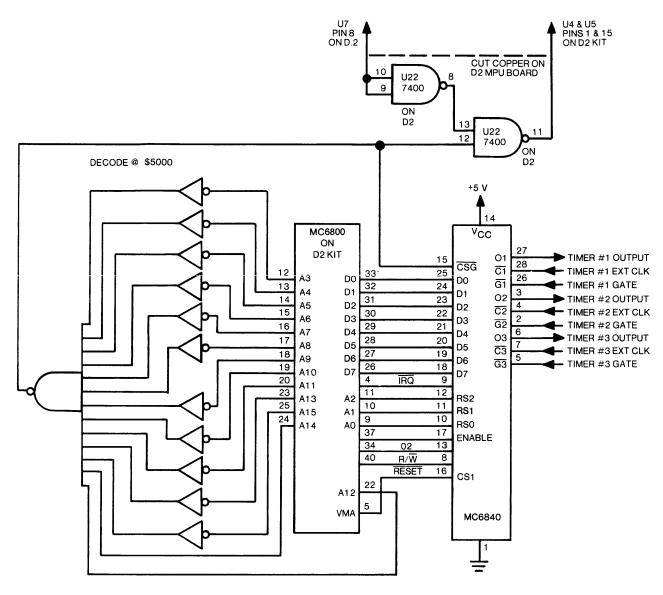

Figure 2-2 shows the PTM interfaced to the MEK6800D2 kit. It is identical to Figure 2-1 except for the two extra gates (available on the kit) which are used to disable the data bus extenders. Only addresses \*\$5000 thorugh \*\$5007 are disabled for kit expansion use. (See Motorola Application Note 771 — Expanding the MEK6800D2 kit).

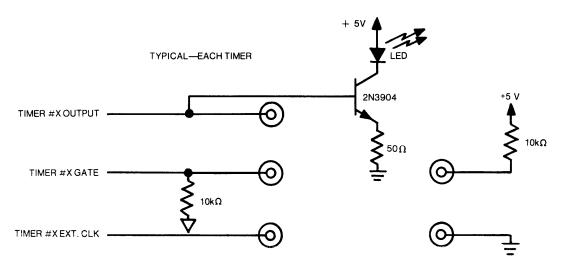

Figure 2-3 shows an additional manual patching area which may be built up in the MEK6800D2 wire wrap area. This has proven to be a valuable design and learning tool for the PTM. Software may be quickly implemented and any timer output configurations may be quickly implemented in hardware and tested. Each timer output is buffered to drive an L.E.D. so that the output state may be observed.

Figure 2-1 PTM Interfaced to the MPU

<sup>\*</sup> hexadecimal number

Figure 2-2 PTM Interfaced to MEK6800D2

Figure 2-3 MEK6800D2 Patch Area Build-up

In high frequency output applications, the L.E.D. will appear partially on if the high state duty cycle is greater than 20%. The hardware patch area permits cascading timers, external clocking and gating, and interfacing the results to additional hardware.

The MC6840, when interfaced to the M6800 family of parts, provides the user with an intelligent peripheral that is not software intensive. Once the PTM has been conditioned by the MPU, further MPU time is not required in most applications until the PTM generates an interrupt. This can be especially valuable in industrial controls where the timer controls several interval dependent production functions. During the timers intervals, the MPU can be accomplishing other tasks.

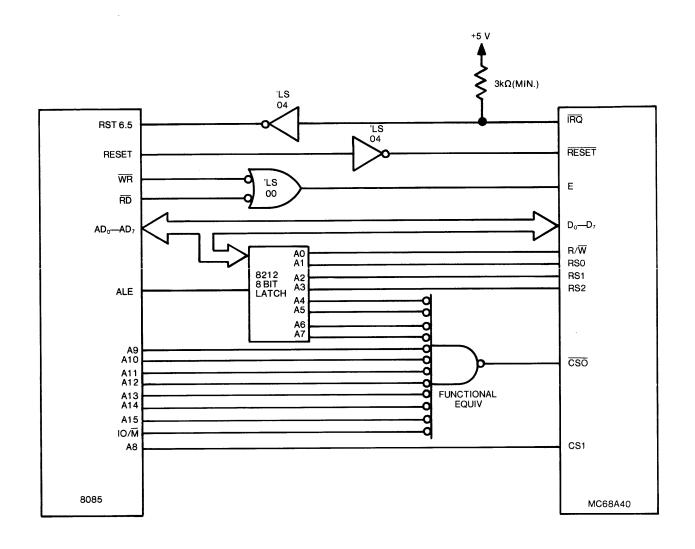

#### 2.1 INTERFACING THE MC6840 PTM TO A NON-MOTOROLA MPU

The user of a non-Motorola MPU who needs the superior capabilities of the MC68X40 PTM can be accommodated with minimal difficulty. This section deals with interfacing the Intel 8085 to the MC68A40 (1.5 MHz) PTM. MPU's similar to the Intel 8085 will interface to the Motorola PTM in a like manner, but care must be exercised in order to insure proper performance.

The user should have the MC6840 PTM Data Sheet, the Intel MCS-85 Users Manual and the Motorola M6800 MPU/Memory Data book on hand to ensure the proper use of both parts.

It should be noted that a 1.0 MHz PTM must not be used. Only the faster 1.5 MHz MC68A40 can be interfaced to the 8085. The method selected to provide for an E timing signal ( $\overline{WR} + \overline{RD} = E$ ) will result in an E pulse with a 400 ns pulse width. The MC6840 PTM requires a pulse width of 480 ns minimum. Also, some setup times given by the 8085 exclude the use of the MC6840 PTM.

#### **2.2 8085 INTERFACE**

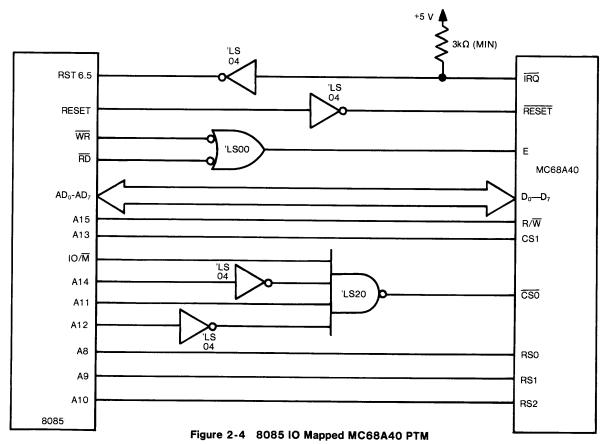

The hardware design is given in Figure 2-4 with the Motorola MC68A40 PTM shown connected to an 8085. Each signal input/output pin on the MC68A40 that must be connected to an 8085 pin is explained in succeeding paragraphs in the section titled, Derivation of the MC68A40 Signals.

The interface technique selected makes use of I/O mapped I/O. That is to say, the MC68A40 is addressed only by use of the INPUT or OUTPUT instructions in the 8085. Using the fact that the 8085 copies the I/O address (0-255) on to A8-A15 as well as A0-A7 during an INPUT or OUTPUT instruction, external latches are not required to store the I/O address. The address is valid on A8-A15 for a read or write cycle within an 8085 I/O instruction.

Using the  $\overline{\text{WR}}$  and  $\overline{\text{RD}}$  signals to produce the Enable (E) signal will result in an E pulse width of 400 ns. M6840 (1.0 MHz) parts need an E pulse width of 480 ns, minimum. MC68A40 (1.5 MHz) and MC68B40 (2.0 MHz) family parts have an E pulse width minimum down to 280 ns and 220 ns respectively.

Also note in Figure 2-4 that address bit 15 is used to provide the MC68A40 with its R/W signal. This was done to satisfy the timing requirements on the R/ $\overline{W}$  signal to the MC68A40 PTM. The use of A15 as a R/ $\overline{W}$  signal does limit the total number of I/O devices since there are now only 7 bits of address available for chip select decoding. This still leaves 128 device addresses that can be used for I/O, and for most requirements this number is more than sufficient. (NOTE: This means 128 device addresses and not 128 I/O lines. A device address can support many I/O lines). A15 was arbitrarily chosen to be used as R/ $\overline{W}$ . Any address bit within A15-A11 could have been used with the same results.

The use of  $\overline{RD}$  logically ORed with  $\overline{WR}$  to generate an Enable (E) pulse assumes that using the MC68A40 PTM, a maximum pulse width of 24 microseconds on the E signal must be observed. Wait and Halt states associated with 8085 instructions are much less than 25 microseconds during a read or write operation. There is also guaranteed to be several  $\overline{WR}$  or  $\overline{RD}$  signals in any instruction (each instruction must have one or more opcode fetches) so that the free running requirement on E is met. Since this E pulse does change frequency during operation the internal clock function will not have an accurate "real time" function.

#### 2.3 MC68A40 SIGNAL DERIVATION

Register Selects (RS0, RS1, RS2) — These three input pins control the selection of the control registers, counters, latches, or status register within the MC68A40. In Figure 2-4; A8, A9 and A10 are shown driving these input pins.

#### 2.3.1 Chip Selects (CS1), (CS0) and $R/\overline{W}$

The  $\overline{\text{CSO}}$  and CS1 inputs are decoded by the desired combination of 8085 address bits A11-A14. These four bits in conjunction with the register select bits, A8, A9 and A10, result in seven address bits to specify an I/O port address. The 8085 IO/M pin is also included in the address decode as the address bus will contain unwanted information during a memory read or write cycle.

As previously mentioned, address bit A15 is used as the R/ $\overline{W}$  input to the MC68A40. As shown in the write timing diagram of Figure 2-5, R/ $\overline{W}$  must be low for a minimum of 140 nanoseconds prior to the rising edge of the E pulse. Use of A15 will provide a low R/ $\overline{W}$  line at least 270 nanoseconds before the rising edge of E. A consequence of using A15 as the R/ $\overline{W}$  signal is that there must be separate addresses defined for read and write operations in software. The following example for MC68A40 PTM should be helpful.

Example 1: The 68A40 PTM eight write addresses and seven read addresses. RS0, RS1, RS2, A15 will select which addresses are to be accessed according to Table 2-1.

Now arbitrarily assigning values to A14-A11 of 0101 produces the complete address as shown in the column labeled as such in Table 2-1. In software, these addresses must be defined by using pseudo instructions (EQU):

Figure 2-5 8085/MC68A40 I/O Write Timing

Figure 2-5 8085/MC68A4 I/O Read Timing (continued)

#### COMPLETE ADDRESS

|                        |           |          |          | COMPLETE  | : ADDR | ESS |     |     |     |     |    |    | HEXIDECIMAL |

|------------------------|-----------|----------|----------|-----------|--------|-----|-----|-----|-----|-----|----|----|-------------|

|                        | RS2 = A10 | RS1 = A9 | RS0 = A8 | R/W = A15 | A15    | A14 | A13 | A12 | A11 | A10 | Α9 | A8 | NOTATION    |

| Unused                 | 0         | 0        | 0        | 1         | 1      | 0   | 1   | 0   | 1   | 0   | 0  | 0  | A8          |

| Write Reg. 1 or Reg. 3 | 0         | 0        | 0        | 0         | 0      | 0   | 1   | 0   | 1   | 0   | 0  | 0  | 28          |

| Read Status Register   | 0         | 0        | 1        | 1         | 1      | 0   | 1   | 0   | 1   | 0   | 0  | 1  | A9          |

| Write Register 2       | 0         | 0        | 1        | 0         | 0      | 0   | 1   | 0   | 1   | 0   | 0  | 1  | 29          |

| Read Timer             |           |          |          |           |        |     |     |     |     |     |    |    |             |

| #1 Counter             | 0         | 1        | 0        | 1         | 1      | 0   | 1   | 0   | 1   | 0   | 1  | 0  | AA          |

| Write MSB              |           |          |          |           |        |     |     |     |     |     |    |    |             |

| Buffer Reg.            | 0         | 1        | 0        | 0         | 0      | 0   | 1   | 0   | 1   | 0   | 1  | 0  | 2A          |

| Read LSB Buffer Reg.   | 0         | 1        | 1        | 1         | 1      | 0   | 1   | 0   | 1   | 0   | 1  | 1  | AB          |

| Write Timer            |           |          |          |           |        |     |     |     |     |     |    |    |             |

| #1 Latches             | 0         | 1        | 1        | 0         | 0      | 0   | 1   | 0   | 1   | 0   | 1  | 1  | 2B          |

| Read Timer             |           |          |          |           |        |     |     |     |     |     |    |    |             |

| #2 Counter             | 1         | 0        | 0        | 1         | 1      | 0   | 1   | 0   | 1   | 1   | 0  | 0  | AC          |

| Write MSB              |           |          |          |           |        |     |     |     |     |     |    |    |             |

| Buffer Reg.            | 1         | 0        | 0        | 0         | 0      | 0   | 1   | 0   | 1   | 1   | 0  | 0  | 2C          |

| Read LSB Buffer Reg.   | 1         | 0        | 1        | 1         | 1      | 0   | 1   | 0   | 1   | 1   | 0  | 1  | AD          |

| Write Timer            |           |          |          |           |        |     |     |     |     |     |    |    |             |

| #2 Latches             | 1         | 0        | 1        | 0         | 0      | 0   | 1   | 0   | 1   | 1   | 0  | 1  | 2D          |

| Read Timer             |           |          |          |           |        |     |     |     |     |     |    |    |             |

| #3 Counter             | 1         | 1        | 0        | 1         | 1      | 0   | 1   | 0   | 1   | 1   | 1  | 0  | AE          |

| Write MSB              |           |          |          |           |        |     |     |     |     |     |    |    |             |

| Buffer Reg.            | 1         | 1        | 0        | 0         | 0      | 0   | 1   | 0   | 1   | 1   | 1  | 0  | 2E          |

| Read LSB Buffer Reg.   | 1         | 1        | 1        | 1         | 1      | 0   | 1   | 0   | 1   | 1   | 1  | 1  | AF          |

| Write Timer            |           |          |          |           |        |     |     |     |     |     |    |    |             |

| #3 Latches             | 1         | 1        | 1        | 0         | 0      | 0   | 1   | 0   | 1   | 1   | 1  | 1  | 2F          |

Table 2-1 8085/MC68A40 Addressing

| LABEL FIELD | OP CODE FIELD | OPERAND FIELD | COMMENT FIELD         |

|-------------|---------------|---------------|-----------------------|

| RSTS        | EQU           | \$A9          | READ STATUS REG       |

| RCN1        | EQU           | \$AA          | READ TIMER ONE        |

| RLB1        | EQU           | \$AB          | READ LSB BUFFER       |

| RCN2        | EQU           | \$AC          | READ TIMER TWO        |

| RLB2        | EQU           | \$AD          | READ LSB BUFFER       |

| RCN3        | EQU           | \$AE          | READ TIMER THREE      |

| RLB3        | EQU           | \$AF          | READ LSB BUFFER       |

| WR13        | EQU           | \$28          | WRITE REG. 1 OR 3     |

| WRG2        | EQU           | \$29          | WRITE REG. 2          |

| WMB1        | EQU           | \$2A          | WRITE MSB BUFFER      |

| WLT1        | EQU           | \$2B          | WRITE TIMER 1 LATCHES |

| WMB2        | EQU           | \$2C          | WRITE MSB BUFFER      |

| WLT2        | EQU           | \$2D          | WRITE TIMER 2 LATCHES |

| WMB3        | EQU           | \$2E          | WRITE MSB BUFFER      |

| WLT3        | EQU           | \$2F          | WRITE TIMER 3 LATCHES |

Table 2-2 Pseudo Instructions

The pseudo instructions (Table 2-2) are easy to use, but care should be exercised to avoid confusing the 8085 IN and OUT instructions when reading from or writing to the MC68A40 PTM. OUT is only used with a write. In order to avoid a mismatch, the first character in the label field of the pseudo instruction tells the user if it is a read or write instruction:

```

IN RXXX (READ INSTRUCTION)

OUT WXXX (WRITE INSTRUCTION)

```

Further, when writing to a timer latch or reading from a timer counter (this is a 16-bit wide word) two consecutive pseudo instructions must be used in the order shown:

TO WRITE TO A TIMER:

OUT WMBX (WRITE MSB BUFFER)

OUT WLTX (WRITE TIMER X LATCHES)

TO READ OUT A TIMER:

IN RCNX (READ TIMER X)

IN RLBX (READ LSB BUFFER X)

To read the MC68A40 status register:

```

IN RSTS (READ STATUS REGISTER)

```

To write a word to control register 2 (write control register 2), an output instruction must be used: WRG2 OUT.

In the IN instruction, A15 will be high (R/ $\overline{W}$  = 1) for the read operation, while in the OUT instruction, A15 will be low (R/ $\overline{W}$  = 0) for the write operation. In both cases, the MC68A40 chip selects input will become active for A14 - A11 = 0101.

This technique costs nothing in firmware as EQU statements are pseudo instructions and are used in the assembly process only.

#### 2.3.2 Enable (E)

As pointed out earlier, the E pulse input to the MC68A40 is the logical OR of the 8085 outputs  $\overline{WR}$  and  $\overline{RD}$  (the logical OR here is done with a NAND gate performing a Low Level OR on  $\overline{WR}$  and  $\overline{RD}$ ). Referring to the timing diagrams of Figure 2-5, this will produce an E pulse with proper timing with relation to the address, data and  $R/\overline{W}$  signals.

#### 2.3.3 RESET (R)

This active low MC68A40 input is the inverse of the 8085 reset output.

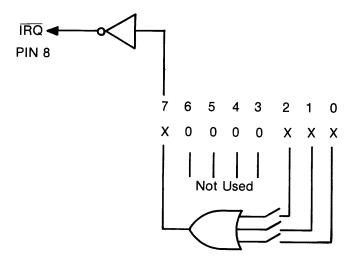

#### 2.3.4 IRQ

This active low output from the MC68A40 PTM must be inverted to drive a RESTART INTERRUPT INPUT such as RST 6.5 on an 8085. The  $\overline{IRQ}$  output is an open drain and should be pulled up to +5 volts.

The generation of an interrupt signal by the MC68A40 PTM should cause the 8085 to immediately branch to a service routine. At the end of the routine, a RET instruction should transfer control back to the original program. For this reason, the RESTART INTERRUPTS (RST 5.5, RST 6.5, RST 7.5, and TRAP) should be used and not the INTERRUPT REQUEST (INTR). The INTR input simply inhibits the Program Counter from incrementing and the INTERRUPT ACKNOWLEDGE signal (INTA) is given. At this time, it is the responsibility of the peripheral device to insert a CALL or RESTART instruction to jump to the service routine. This routine must also be responsible for preserving the return address located in the Program Counter. The MC68A40 PTM is not able to do such lengthy and complicated procedures so it must use one of the four RESTART INTERRTUPTS. An interrupt signal on any of these inputs causes the immediate execution of a RESTART instruction in which the contents of the Program Counter are placed on the Stack and a branch is executed to a RESTART address. The addresses for each of the interrupts are:

TRAP — 24 (Hex) RST 5.5 — 2C RST 6.5 — 34 RST 7.5 — 3C

These locations should contain the JUMP instruction to the service routine. At the end of ths routine a RET instruction will branch back to the original program. RST 5.5, RST 6.5, RST 7.5 are maskable interrupts of increasing priority (RST 5.5 lowest). TRAP is non-maskable and has the highest priority of all. RST 5.5 and RST 6.5 are high level-sensitive and RST 7.5 is rising edge-sensitive. All are sampled on the last clock cycle of each instruction.

### 2.3.5 Read/Write Timing

The read and write timings are shown in Figure 2-5. Below each are the necessary inputs to a MC68A40 PTM generated from the 8085 outputs.

#### 2.3.6 Summary

The interface between a Motorola MC68A40 PTM and the Intel 8085 microprocessors can be done with as little as two gates and two inverters.

When the technique of I/O mapped I/O is used, the IN/OUT instructions of the 8085 will result in the I/O address being copied onto the A15-A8 address bus of the 8085 for most of an I/O operation cycle. Therefore no external latches are required for address latching as would be the case if the I/O address were present on the multiplexed data/address bus AD0-AD7.

Because the MC68A40 PTM requires an E pulse width of 480 nanoseconds maximum and since the generation of E is done by logically ORing two 400 nanosecond pulses ( $\overline{RD}$  and  $\overline{WR}$ ), only 1.5 MHz and 2.0 MHz deviced (MC68A/B40) should be used.

Generation of the  $\overline{\text{CSO}}$  and CS1 signals to MC68A40 PTM is done by decoding 8085 address bits A14-A11 while a R/W signal is obtained from A15 directly. This means that separate write and read addresses must be defined in software. The IO/M signal output from the 8085 is used in the A14-A11 chip decoder.

The multiplexed data/address bus AD0-AD7 of the 8085 is connected directly to the data port D0-D7 of the MC68A40 PTM.

For systems requiring several peripheral devices, the hardware desing shown here will need to be expanded to include appropriate drivers.

Since the "E" input pulse may be used as an internal clock for any of the timers, it must be remembered that this line will vary in frequency. Precise real-time period measurements cannot be made using the internal clock. Accurate measurements can be made using the external clock, but care must be used to insure conformity to the PWL and PWH timing limits in the data sheet section.

The MC68A40 may also be connected as a memory mapped location, as shown in Figure 2-6. This approach uses the 8212 latch to separate the address and data lines for the PTM. Address line Ao is used in this case for the Read/Write line. Ao was selected for use as the R/W line in this case as a matter of convenience. This permits all odd addresses to be "Read" addresses and all even addresses to be "Write" addresses. The timing requirements are essentially the same as shown in Figure 2-5.

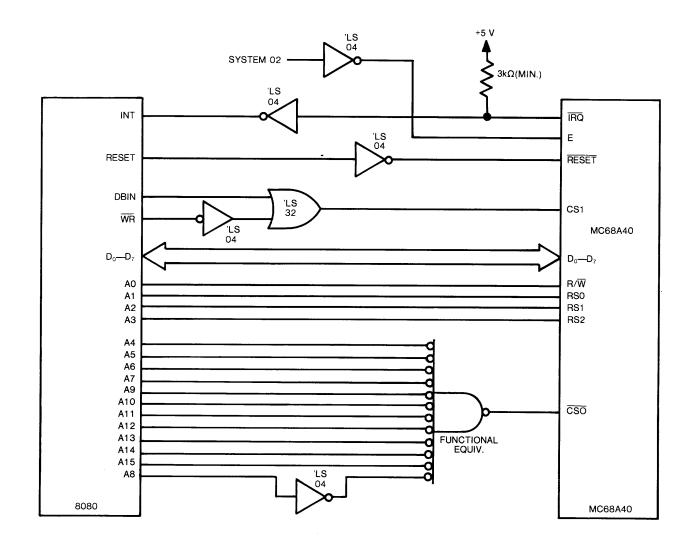

#### **2.4 8080 INTERFACE**

The MC6840 may be interfaced to the 8080 in a similar manner to that shown in the preceding chapter. Figure 2-7 shows the basic approach. Care must be exercised to ensure the  $\phi$ 2 clock input frequency does not exceed the specified maximum:

MC6840 — 1.0 MHz MC68A40 — 1.5 MHz MC68B40 — 2.0 MHz

The incoming  $\phi$ 2 signal may be divided by a flip-flop, but the proper timing relationships must be maintained.

BASE ADDRESS—\$0100

| \$   | r   |     |     |                                                                           |

|------|-----|-----|-----|---------------------------------------------------------------------------|

| ADDR | RS2 | RS1 | RS0 | $R/\overline{W} = 0$                                                      |

| 0100 | 0   | 0   | 0   | CR20 = 0 Write Control Register # 3<br>CR20 = 1 Write Control Register #1 |

| 0102 | 0   | 0   | 1   | Write Control Register #2                                                 |

| 0104 | 0   | 0   | 1   | Write MSB Buffer Register                                                 |

| 0106 | 0   | 1   | 1   | Write Timer #1 Latches                                                    |

| 0108 | 1   | ၁   | 0   | Write MSB Buffer Register                                                 |

| 010A | 1   | 0   | 1   | Write Timer #2 Latches                                                    |

| 010C | 1   | 1   | 0   | Write MSB Buffer Register                                                 |

| 101E | 1   | 1   | 1   | Write Timer #3 Latches                                                    |

|      |     |     |     | $R/\overline{W} = 1$                                                      |

| 0101 | 0   | 0   | 0   | No Operation                                                              |

| 0103 | 0   | 0   | 1   | Read Status Register                                                      |

| 0105 | 0   | 1   | 0   | Read Timer #1 Counter                                                     |

| 0107 | 0   | 1   | 1   | Read LSB Buffer Register                                                  |

| 0109 | 1   | 0   | 0   | Read Timer #2 Counter                                                     |

| 010B | 1   | 0   | 1   | Read LSB Buffer Register                                                  |

| 010D | 1   | 1   | 0   | Read Timer #3 Counter                                                     |

| 010F | 1   | 1   | 1   | Read LSB Buffer Register                                                  |

Figure 2-6 8085 Memory Mapped MC68A40 PTM

#### BASE ADDRESS-\$0100

| \$   |     |     |     |                                     |  |  |  |  |

|------|-----|-----|-----|-------------------------------------|--|--|--|--|

| ADDR | RS2 | RS1 | RS0 | $R/\overline{W} = 0$                |  |  |  |  |

| 0100 | 0   | 0   | 0   | CR20 = 0 Write Control Register # 3 |  |  |  |  |

| 0100 |     |     |     | CR20 = 1 Write Control Register #1  |  |  |  |  |

| 0102 | 0   | 0   | 1   | Write Control Register #2           |  |  |  |  |

| 0104 | 0   | 0   | 1   | Write MSB Buffer Register           |  |  |  |  |

| 0106 | 0   | 1   | 1   | Write Timer #1 Latches              |  |  |  |  |

| 0108 | 1   | 0   | 0   | Write MSB Buffer Register           |  |  |  |  |

| 010A | 1   | 0   | 1   | Write Timer #2 Latches              |  |  |  |  |

| 010C | 1   | 1   | 0   | Write MSB Buffer Register           |  |  |  |  |

| 101E | 1   | 1   | 1   | Write Timer #3 Latches              |  |  |  |  |

|      |     |     |     | $R/\overline{W} = 1$                |  |  |  |  |

| 0101 | 0   | 0   | 0   | No Operation                        |  |  |  |  |

| 0103 | 0   | 0   | 1   | Read Status Register                |  |  |  |  |

| 0105 | 0   | 1   | 0   | Read Timer #1 Counter               |  |  |  |  |

| 0107 | 0   | 1   | 1   | Read LSB Buffer Register            |  |  |  |  |

| 0109 | 1   | 0   | 0   | Read Timer #2 Counter               |  |  |  |  |

| 010B | 1   | 0   | 1   | Read LSB Buffer Register            |  |  |  |  |

| 010D | 1   | 1   | 0   | Read Timer #3 Counter               |  |  |  |  |

| 010F | 1   | 1   | 1   | Read LSB Buffer Register            |  |  |  |  |

|      |     |     |     |                                     |  |  |  |  |

Figure 2-7 8080 Memory Mapped MC68A40 PTM

# CHAPTER 3 SOFTWARE INITIALIZATION

#### 3.0 INTRODUCTION

Programming the PTM requires the user to have an understanding of the registers. The versatility of this part requires that each timer have its own 8-bit control register in order to select the modes and timer characteristics needed by the user. These registers will be thoroughly examined in this chapter along with the Interrupt Status Register and the registers used to read and write data from and to the counters.

Table 3-1 shows how the registers, latches and counters are selected using the Register Select input pins. Further in this chapter, register selection is discussed as it will probably be connected in most applications (to the three lowest order address lines).

This chapter describes and defines

RESETS

COUNTER INITIALIZATION

COUNTER ENBLE

COUNTER LATCH INITIALIZATION

EXAMPLE COUNTER PROGRAMMING

BIT BY BIT CONTROL REGISTER PROGRAMMING FOR ALL MODES

INTERRUPTS AND THE INTERRUPT STATUS REGISTER

| Register<br>Select Inputs |     |     | Operation                           | ns                       |

|---------------------------|-----|-----|-------------------------------------|--------------------------|

| RS2                       | RS1 | RS0 | R/W = 0                             | R/W = 1                  |

| 0                         | 0   | 0   | CR20 = 0 Write Control Register = 3 | No Operation             |

|                           |     |     | CR20 = 1 Write Control Register = 1 |                          |

| 0                         | 0   | 1   | Write Control Register #2           | Read Status Register     |

| 0                         | 1   | 0   | Write MSB Buffer Register           | Read Timer #1 Counter    |

| 0                         | 1   | 1   | Write Timer #1 Latches              | Read LSB Buffer Register |

| 1                         | 0   | 0   | Write MSB Buffer Register           | Read Timer #2 Counter    |

| 1                         | 0   | 1   | Write Timer #2 Latches              | Read LSB Buffer Register |

| 1                         | 1   | 0   | Write MSB Buffer Register           | Read Timer #3 Counter    |

| 1                         | 1   | 1   | Write Timer #3 Latches              | Read LSB Buffer Register |

**Table 3-1 Register Selection**

#### 3.1 RESETS

#### 3.1.1 Hardware

This pin on the PTM is normally tied to the system RESET, and is asserted during power up and whenever the system "Reset" button is pushed. This Reset causes the following conditions:

- All operations (clocks) in progress in the PTM's timers are stopped.

- All interrupt flags in the interrupt Status Register are cleared.

- All Counter latch data is set to hexadecimal FFFF (65,536).

- All Control Register bits are cleared (0) except bit 0 of Control Register #1 which is set (1). This is the software Internal Reset Bit.

#### 3.1.2 Software

The internal software Reset bit is set by a hardware Reset or being written high by the MPU. The software Reset being asserted causes the following conditions.

- All operations (clocks) in progress in the PTM's timers are stopped.

- All interrupt flags in the Interrupt Status Register are cleared.

- All Counter latches retain the data last written to them.

- All remaining Control Register bits are not changed.

#### 3.2 COUNTER INITIALIZATION

Counter Initialization is caused by various conditions in the different modes. The conditions will be discussed for each mode. Counter initialization causes:

- The data stored in the counter latch will be written to the counter.

- The interrupt associated with the timer being initialized will be cleared.

#### 3.3 COUNTER ENABLE

Counter Enable is the state where conditions allow the counter to operate. One condition is that all resets are always cleared. The other necessary conditions will be discussed in each mode. In order to operate a timer must be Initialized AND Enabled.

#### 3.4 COUNTER LATCH INITIALIZATION

Counter Latch Initialization is the transferal of a 16-bit data word (two 8-bit words) from the MPU to the counter latches. Counter Latch Initialization is fully explained in the following example. The M6800 Instruction Set Summary card may be used to interpret the mnemonics:

#### 3.5 EXAMPLE COUNTER PROGRAMMING

In Table 3-2 it is assumed that the register select lines have been connected to the three least significant address lines:

RS0 to A0 RS1 to A1 RS2 to A2

The MSB buffer register is a single, write only, 8-bit holding register with three separate addresses — \$XXX2, \$XXX4, \$XXX6.

The LSB buffer register is a single, read only 8-bit holding register with three separate addresses — \$XXX3, \$XXX5, \$XXX7.

| ADDR   | READ                | WRITE                     |

|--------|---------------------|---------------------------|

| \$XXX0 | NOP                 | CONTROL REGISTER #1 OR #3 |

| \$XXX1 | STATUS REGISTER     | CONTROL REGISTER #2       |

| \$XXX2 | TIMER #1 COUNTER    | MSB BUFFER REGISTER       |

| \$XXX3 | LSB BUFFER REGISTER | TIMER #1 LATCHES          |

| \$XXX4 | TIMER #2 COUNTER    | MSB BUFFER REGISTER       |

| \$XXX5 | LSB BUFFER RGISTER  | TIMER #2 LATCHES          |

| \$XXX6 | TIMER #3 COUNTER    | MSB BUFFER REGISTER       |

| \$XXX7 | LSB BUFFER REGISTER | TIMER #3 LATCHES          |

**Table 3-2 Register Selection As Memory Locations**

#### 3.5.1 Writing to a Timer Latch

Writing to a Timer Latch (typical for all three timers): LDX\* \$FDEC

(\*\$XXXX indicates an immediate addressing mode of a hexadecimal number; FDEC is used here as example data).

#### \$ - HEXADECIMAL NUMBER

STX \$XXX2

When writing to the LS byte of the timer latch (@ memory location \$XXX3), the contents of the MSB buffer is internally written to the MS byte of that latch. (16-bit wide word)

#### 3.5.2 Reading from a Timer Counter

When reading a timer counter (16-bits), the MS byte (8-bits) is read at \$XXX2 (M) and the LS byte is internally written to the LSB buffer register which may be read at the next memory location — \$XXX3 (M+1).

The STS & STX instructions automatically perform the 16-bit write.

The LDS & LDX instructions automatically perform the 16-bit read.

The contents of the MSB Buffer and LSB Buffer are changed only by two methods:

- Being written over OR

- A hardware Reset occurs

#### 3.6 CONTROL REGISTER PROGRAMMING:

#### 3.6.1 Individual Bits

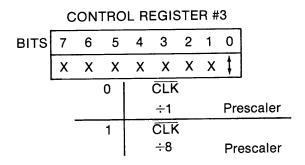

After initializing the counter latches, the next registers programmed are the control registers. Bits 1 through 7 perform the same function in all three control registers. Bit 0 performs a unique function in each control register. Control register three is located at address \$0000 after a RESET or power-up and is usually programmed first. Bit 0 in control register #3 is a clock prescalar and is available only in control register #3. The prescalar divides either the internal or external clock.

Bit 0 in control register #2 (@ \$0001) determines which control register may be written at location \$0000. This bit defaults to zero upon power up and a hardware reset.

#### **CONTROL REGISTER #2**

| 7 | 6 | 5   | 4    | 3  | 2   | 1    | 0        |     |

|---|---|-----|------|----|-----|------|----------|-----|

| Х | Х | Х   | Х    | Х  | Х   | Х    | <b>†</b> |     |

| 0 |   | REC | 3 #3 | MA | ΥE  | BE W | /RIT     | TEN |

| 1 |   | REC | 3 #1 | MA | Y E | BE W | /RIT     | TEN |

When bit zero in control register #2 is a "1", control register #1 may now be written at location \$0000. This bit allows all three timers to operate or holds all three timers in a preset condition.

#### **CONTROL REGISTER #1**

| 7 | 6 | 5    | 4   | 3    | 2    | 1   | 0   |

|---|---|------|-----|------|------|-----|-----|

| Х | Х | Х    | Х   | Χ    | Χ    | Χ   | ‡   |

| 0 | Å | ALL  | TIM | 1ER: | s o  | PER | ATE |

| 1 |   | Δ1.1 | TIM | IFR  | S PI | RES | ET  |

The remaining bits in the control registers perform the same operation in each register. The operation of each timer clock is completely independent on the other timers unless they are cascaded. Each timer has its own external clock pin or the internal enable clock may be used.

| 7 | 6 | 5   | 4  | 3    | 2   | 1        | 0   |                        |

|---|---|-----|----|------|-----|----------|-----|------------------------|

| Х | Χ | Χ   | Χ  | Χ    | Х   | <b>‡</b> | Х   | CONTROL REGISTER #X    |

| 0 | E | XTE | RN | AL ( | CLO | СК       | (CX | INPUT) (X= 1, 2, or 3) |

| 1 |   | NTE | RN | AL C | CLO | СК       | (EN | ABLE)                  |

Bit 6 will mask or enable the individual interrupt flag to cause a composite interrupt. The individual interrupt flag is not maskable. (See Status Register section).

| 7 | 6 | 5    | 4   | 3   | 2  | 1  | 0   |                     |

|---|---|------|-----|-----|----|----|-----|---------------------|

| Х | ‡ | Χ    | Х   | Х   | Х  | Χ  | Х   | CONTROL REGISTER #X |

| 0 |   | INTE | ERR | UP1 | FL | AG | MAS | SKED (IRQ)          |

| 1 |   | INTE | RR  | UP1 | FL | AG | ENA | ABLED (IRQ)         |

Bit 7 simply enables the timer's output on the individual timer's output pin. If the output is masked it will always be electrically "low."

| 7 | 6 | 5   | 4   | 3   | 2   | 1  | 0    |                     |

|---|---|-----|-----|-----|-----|----|------|---------------------|

| 1 | Х | Х   | Х   | Х   | Х   | Χ  | Х    | CONTROL REGISTER #X |

| 0 | T | IME | RC  | UT  | PUT | M  | ASKI | ED                  |

| 1 | Т | IME | R C | DUT | PUT | EN | IABL | ED                  |

#### 3.7 CONTINUOUS OPERATING MODE

In the examination of the PTMs operating modes the following terms will be used:

- Reset since a hardware Reset always causes a software Reset (which can also be programmed), and a software Reset cannot be cleared while a hardware Reset is present, the term "Reset" shall refer to the software Reset.

- Interrupt when an individual timer's interrupt flag is high.

- Write to Counter Latches Counter Latch Initialization.

- Gate the individual input control pin that is associated with each timer. This pin's state or transition controls the various timer functions is described below.

- Time Out occurance one count after the contents of a timer equals \$0000.

- "Condition" clear the named condition is not active.

- Counter Enable (as refers to all Continuous Mode conditions):

Reset clear

Gate pin is low

#### 3.7.1 16-Bit Operation

16-bit operation is considered the "usual" count down operation of the timers. It is probably the most frequently used. The timer's clock counts down the 16-bit latch data word to zero and then generates an interrupt and an output transition as shown below:

16-bit operation

A = the total 16-bit count in the latch +1, times the period of the clock.

The control register programming for the two cases of Counter Initialization in 16-bit operation is shown below:

Interrupt:

Occurs at each Time Out

Counter Initialization:

Reset OR

Gate pin goes low

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| X | Х | 0 | 0 | 0 | 0 | Х | Х |

#### **CONTROL REGISTER #X**

Interrupt:

Occurs at each Time Out

Counter Initialization:

Reset OR

Gate pin goes low OR

Write to the Counter Latches

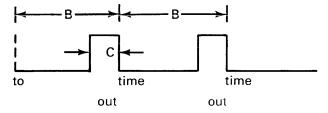

#### 3.7.2 Dual 8-Bit Operation

This latch count down option treats the 16-bit word in the latch as two separate 8-bit wide words. The output transition occurs **before** the time out occurs. The dual 8-bit operation is described below:

**Dual 8-bit operation**

B = The count in the LSB latch +1, times the count in the MSB latch +1, times the period of the clock.

C = The count in the LSB latch period.

The control register programming for the two cases of Counter Initialization in the Dual 8-bit Mode are shown below:

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| X | Х | 0 | 1 | 0 | 1 | Χ | Х |

**CONTROL REGISTER #X**

Interrupt:

Occurs at each Time Out

Counter Initialization:

Reset OR

Gate pin goes low

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| Х | Х | 0 | 0 | 0 | 1 | X | Х |

**CONTROL REGISTER #X**

Interrupt:

Occurs at each Time Out

Counter Initialization:

Reset OR

Gate pin goes low OR

Write to the Counter latches

#### 3.8 SINGLE SHOT MODE

Counter Enable (as refers to **all** Single Shot conditions)

Reset Clear

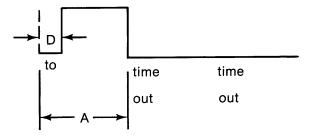

#### 3.8.1 16-Bit Operation

The count-down operation is the same as described in 3.7.1. The only differences are:

- The output is high during the first time out as shown below.

- The gate pin need not be held low to enable the timer, but a low transition (Counter Initialization) will cause a "Single Shot."

The 16-bit operation of the Single Shot Mode is shown below:

16-bit operation

A = The total 16-bit count in the latch +1, times the period of the clock

D = one count times the clock period

The control register programming for the two cases of Counter Initialization in 16-bit operation are shown below. Each initialization causes a single shot (even during a single shot) if the counter is enabled;

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 1 | Х | 1 | 1 | 0 | 0 | Х | X |

**CONTROL REGISTER #X**

Interrupt:

Occurs at each Time Out

Counter Initialization:

Reset OR

Gate pin goes low

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 1 | Х | 1 | 0 | 0 | 0 | X | Χ |

**CONTROL REGISTER #X**

Interrupt:

Occurs at each Time Out

CounterInitialization:

Reset OR

Gate pin goes low OR

Write to the Counter Latches

#### 3.8.2 Dual 8-Bit Operation

This count down option is the same as described in 3.7.1.

B = the counter in the LSB latch +1, times the count in the MSB latch +1, times the period of the clock. C = the count in the LSB latch times the period of the clock.

The control register programming for the two cases of Counter Initialization in Dual 8-bit operation are shown below:

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 1 | Χ | 1 | 1 | 0 | 1 | Χ | Χ |

**CONTROL REGISTER #X**

Interrupt:

Occurs at each Time Out Counter Initialization: Reset OR Gate pin goes low

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 1 | Х | 1 | 0 | 0 | 1 | X | Χ |

**CONTROL REGISTER #X**

Interrupt:

Occurs at each Time Out

Counter Initialization:

Reset OR

Gate pin goes low OR

Write to the Counter Latches

Bit 7, the output enable bit must be high in the Single Shot Mode. This enables the output for the "Single Shot." Internally, the count recycling is continuous as if in the Continuous Mode. Only one pulse is evident on the output pin for each Counter Initialization.

#### 3.9 PERIOD MEASUREMENT MODE

Counter Enable (refers to all Period Measurement Mode conditions).

The gate pin goes low AND No write to the Counter Latches AND Reset is cleared AND There is no individual interrupt flag asserted

This mode compares the period of a digital signal with the period generated by the word in the counter times the period of the clock (Time Out). The control register may be programmed to generate an interrupt if the period of the incoming signal is elss than or greater than that of the Time Out. The digital signal to be measured is applied to the individual gate pin that is assigned to each timer. The two cases of control register programming are shown below:

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | Х | 0 | 0 | 1 | Х | Χ | Χ |

**CONTROL REGISTER #X**

Interrupt Flag Set:

Interrupt will be generated if the \(\frac{\psi}{\psi}\) duration of the signal on the timer's gate pin is less than the Time Out

Counter Initialization:

The gate pin goes low AND

There is no individual interrupt flag asserted AND

\*(A Reset Counter Enable OR a Time Out has occurred) OR

<sup>\*</sup>This prevents initialization on the trailing edge of a previous period measurement.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | Х | 1 | 0 | 1 | Х | Х | X |

#### CONTROL REGISTER #X

Interrupt Flag Set:

Interrupt will be generated if the \(\frac{\psi}{\psi}\) duration of the signal on the timer's gate pin is greater the Time Out

Counter Initialization:

The gate pin goes low AND

There is no individual interrupt flag asserted OR

#### 3.10 PULSE WIDTH MEASUREMENT MODE

Counter Enable (refers to all Pulse Width Measurement Mode conditions)

The gate pin goes low AND

No write to the Counter Latches AND

Reset is cleared AND

There is no individual interrupt flag asserted

The Pulse Width Comparison Mode operates in the same manner as the Period Measurement Mode in 3.9, except the "down time" of the pulse is compared to the Time Out. The pulse on the gate pin is defined as the period from the negative transition causing initialization to the first positive transition of the gate. An interrupt may be generated if the period of the "down time" pulse is greater than or less than the Time Out. The two cases of control register programming are shown below:

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | Х | 0 | 1 | 1 | X | X | X |

CONTROL REGISTER #X

Interrupt Flag Set:

Interrupt will be generated if the \duration of the signal on the timer's gate pin is less than the Time Out.

Counter Initialization:

The gate pin goes low AND

There is no individual interrupt flag asserted OR

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | X | 1 | 1 | 1 | Х | X | Х |

Interrupt Flag Set:

Interrupt will be generated if the \dagger \tag{\tag{duration of the signal on the timer's gate pin is greater} than the Time Out.

Counter Initialization:

The gate pin goes low AND

There is no individual interrupt flag asserted OR

Reset.

NOTE: The output is usually not used in the Period or Pulse Width Comparison Modes. It is defined. If the output of the timer is enabled, the output will operate in the following manner:

- During the first Time Out the output will be low.

- If the first Time Out is completed, the output will go high at the Time Out completion.

- If further Time Outs are allowed to be completed, the output will change state at the completion of each Time Out.

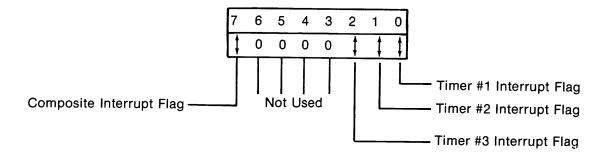

#### 3.11 STATUS REGISTER OPERATION

The Status Register is a read only register that contains the interrupt flags, the three timers and the Composite Interrupt.

The relationship between the individual interrupt flags, the composite interrupt and the  $\overline{\text{IRQ}}$  pin is shown below:

Bit 6 in each control register "closes" the switch in the above functional diagram when it is a logic "1". When "open" (bit 6 = 0) the functional OR gate input is low. The basic characteristics of the Status Register are:

- Individual timer interrupts cannot be masked.

- A composite interrupt is caused by a timer interrupt and that timer's interrupt flag enabled (CRX6 = 1).

- A composite interrupt causes IRQ to be asserted.

What clears interrupts:

Hardware reset (RESET = 0)

Software reset (CR10 = 1)

Read the status register (RS), then read the timer (RT) causing the interrupt. (An interrupt that occurs between RS and RT will **not** be cleared.)

Writing to the latches. (IF CR x 3 = 0 and CR x 4 = 0)

The gate (GX) goes low. (IF  $CR \times 3 = 0$ )

# CHAPTER 4 SAMPLE SOFTWARE INITIALIZATION ROUTINE

#### 4.0 INTRODUCTION

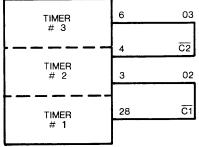

The attached sample initialization routine demonstrates the ease of initializing the PTM. The purpose of this routine is to set up the timer in the continuous mode. By cascading the outputs (shown on Figure 4-1) to the external clock inputs, interrupts of from a few microseconds to over 282 years can be achieved on timer one.

#### 4.1 PTM INITIALIZATION

The PTM is interfaced to the MPU as shown in Chapter 2, Figure 2-1. The external output and input pins of the PTM are connected as shown in Figure 4-1. The PTM may now be initialized. In order to achieve maximum software efficiency, the PTM should be initialized in the following sequence:

1. First write the latch data to the three counter latches —

LDX STX

If the latches are not written, they default to \$FFFF. The time out data may be loaded directly into the index register from two consecutive RAM memory locations. (e.g. This permits a routine to calculate a time out and leave it to be retrieved later for timer data.) The overall effect is a single instruction, 16 bit wide timer data word that is very software efficient. Since "writing to" or "reading from" a timer appears exactly like two successive memory locations to the MPU (M & M + 1), the index register and stack pointer operations handle the 16 bit timer data. The three timers occupy six consecutive locations and are totally independent.

2. Next, the control word is written to the three timer control registers. The three control registers differ only in their least significant bits. The three registers occupy two memory locations. Address "zero" (RS0 = 0, RS1 = 0, RS2 = 0) is in the location of both control register #1 and control register #3. The state of bit 0 of control register #2 selects which control register is selected at address "zero". (Bit 0 = 0 - control register #3 is selected; bit 0 = 1 - control register #1 is selected). Address "one" (RS0 = 1, RS1 = 0, RS2 = 0) contains only control register #2. Upon initialization (power up or hardware reset), bit 0 of control register #2 defaults to zero (control register #3 is selected address "zero").

The easiest method of loading the control words is the following order:

WRITE CONTROL REGISTER #3

WRITE CONTROL REGISTER #2

WRITE CONTROL REGISTER #1

The part powers up so Control Register #3 can be accessed directly at RS0 = RS1 = RS2 = 0. When writing control register #2, control register #1 is enabled by the user by writing bit 0 = 1. When writing register #1, bit 0 "turns on" all three timers.

The sample initialization routine, Figure 4-2, is a printout of an actual initialization of the PTM. Figure 4-3, MC6840 Control Register Programming, describes the function of the bits in each of the control registers.

Figure 4-1 PTM Cascaded Operation

```

PAGE

00 I

00001

*

SAMPLE INITIALIZATION ROUTINE

00002

*

MC6840 PROGRAMMABLE TIMER

00003

00004

00005

* THIS ROUTINE DEMONSTRATES THE CASCADING TIMEOUT

00006

* CAPABILITY OF THE MC6840 PTM. CONNECT 03 TO *C2

00007

* AND CONNECT O2 TO *CI (PTM BASE ADDRESS IS $5000

00008

00009

* FIRST, LORD THE TIMEOUT WORD INTO THE LATCHES

00010A 0000 CE 0010

LDX

Н

#$0010

17 X I MICROSECOND

00011A 0003 FF 5002

Ĥ

STX

$5002

COUNTER ONE

00012A 0006 CE 0100

Ĥ

LDX

#$0100

257 X COUNTER ONE

00013A 0009 FF 5004

Ĥ

5TX

$5004

COUNTER THO

00014A 000C CE 1000

Ĥ

LDX

#$1000

4097 X COUNTER TWO

00015A 000F FF 5006

COUNTER THREE

Ĥ

STX

$5666

* NEXT, PROGRAM THE CONTROL REGISTERS

00016

00017A 0012 86 82

Ĥ

LDAR

##82

CONTRUL MORD

00018H 0014 B7 5000

Ĥ

STAA

$500⊎

CONTROL REGISTER THREE

00019A 0017 86 81

Ĥ

LDAA

#$81

CONTROL WORD

00020A 0019 B7 5001

Ħ

STĤĤ.

$5001

CONTRUL REGISTER TWO

00021

* ADDRESS $5000 IS NOW CONTROL REGISTER ONE.

00022

* IT INITIALIZES AS CONTROL REGISTER THREE.

00023A 001C 86 40

Ĥ

LDAR

#$40

CONTROL NORD

00024A 001E B7 5000

STAA

CONTRUL REGISTER ONE & GO!

Ĥ

$5000

00025

* THE COMPOSITE INTERRUPT WILL OCCUR @ 71.599172

99926

* SECONDS: MAXIMUM TIMEOUT CAPABILITY, USING

00027

* ONLY THE I MHZ CLOCK, IS OVER 282 YEARS USING

00028

* THIS CASCADED OPERATION AND THE DIVIDE BY 8

00029

* FERTURE.

00030A 0021 3F

SWI

00031

END

TOTAL ERRORS 00000

```

Figure 4-2 Sample MC6840 Printout

|        |                                              |        |        |          |            |             |                                                                 | REGISTER                                                                                     | REGISTER 2                        | REGISTER      |  |  |  |  |

|--------|----------------------------------------------|--------|--------|----------|------------|-------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------|---------------|--|--|--|--|

| 7      | 6                                            | 5      | 4      | 3        | 2          | 1 0         | o                                                               | ALL TIMERS<br>OPERATE                                                                        | REG #3 MAY<br>BE WRITTEN          | T3            |  |  |  |  |

| X      | х                                            | Х      | ×      | х        | Х          | x ‡         | 1                                                               | ALL TIMERS<br>PRESET                                                                         | REG #1 MAY<br>BE WRITTEN          | T3 CLK<br>+ 8 |  |  |  |  |

| 7      | 6                                            | 5      | 4      | 3        | 2          | 1 0         | 0                                                               | EXTERNAL CLOCK                                                                               | (CX INPUT)                        |               |  |  |  |  |

| ×      | Х                                            | Х      | Х      | х        | Х          | ‡ x         | 1                                                               | INTERNAL CLOCK                                                                               | (ENABLE)                          |               |  |  |  |  |

|        | 7 6 5 4 3 2 1 0 0 NORMAL (16 BIT) COUNT MODE |        |        |          |            |             |                                                                 |                                                                                              |                                   |               |  |  |  |  |

| x      | X                                            | X      | 4<br>Х | X        | ‡          | x x         | 1                                                               |                                                                                              |                                   |               |  |  |  |  |

|        |                                              |        |        |          |            |             | 1                                                               | •                                                                                            |                                   |               |  |  |  |  |

| 7<br>X | 6<br>X                                       | 5      | 0      | 3        | 2<br>X     | 1 0<br>X X  | CON<br>TO L                                                     | CONTINUOUS OPERATING MODE: GATE ♦ OR WRITE TO LATCHES OR RESET CAUSES COUNTER INITIALIZATION |                                   |               |  |  |  |  |

|        |                                              | I      | l      |          |            | <u> </u>    | J                                                               |                                                                                              |                                   |               |  |  |  |  |

| 7<br>X | 6<br>X                                       | 5      | 4      | 3        | 2<br>X     | 1 0<br>X X  | FREC<br>IF G                                                    | QUENCY COMPARISON                                                                            | MODE: INTERRUPT<br>UNTER TIME OUT |               |  |  |  |  |

| L^     |                                              |        |        | <u> </u> |            | 1^1^        | J                                                               |                                                                                              |                                   |               |  |  |  |  |

| 7      | 6                                            | 5      | 4      | 3        | 2          | 1 0         | CON                                                             | CONTINUOUS OPERATING MODE: GATE ↓ OR RESET CAUSES COUNTER INITIALIZATION                     |                                   |               |  |  |  |  |

| X      | X                                            | 0      | 1      | 0        | Х          | X   X       | ]                                                               | TOAGGEO COGNIEN                                                                              | MATERIAL PARTIES                  |               |  |  |  |  |

| 7      | 6                                            | 5      | 4      | 3        | 2          | 1 0         |                                                                 | SE WIDTH COMPARISO                                                                           | N MODE: INTERRUPT                 |               |  |  |  |  |

| X      | Х                                            | 0      | 1      | 1        | х          | x x         | ] IF G                                                          | IF GATE ↓IS < COUNTER TIME OUT                                                               |                                   |               |  |  |  |  |

| 7      | 6                                            | 5      | 4      | 3        | 2          | 1 0         | SING                                                            | LE SHOT MODE: GATE                                                                           | F or write to                     |               |  |  |  |  |

| 1      | Х                                            | 1      | 0      | 0        | х          | x x         | LAT                                                             | CHES OR RESET CAUS                                                                           | ES COUNTER INITIAL                | IZATION       |  |  |  |  |

| 7      | 6                                            | 5      | 4      | 3        | 2          | 1 0         | FRE                                                             | DUENCY COMPARISON                                                                            | MODE: INTERRUPT                   |               |  |  |  |  |

| X      | x                                            | 1      | 0      | 1        | х          | x x         | iF G                                                            | QUENCY COMPARISON<br>ATE LIBS > COI                                                          | UNTER TIME OUT                    |               |  |  |  |  |

| 7      | 6                                            | 5      | 4      | 3        | 2          | 1 0         | 7                                                               | NE CHOT MODE: CAT                                                                            | E L OD DESET                      |               |  |  |  |  |

| 1      | X                                            | 1      | 1      | 0        | X          | x x         | SINGLE SHOT MODE: GATE ♦ OR RESET CAUSES COUNTER INITIALIZATION |                                                                                              |                                   |               |  |  |  |  |

|        |                                              | _      |        | _        | Ī <u>^</u> | -           | 7                                                               |                                                                                              |                                   |               |  |  |  |  |

| 7<br>X | 6<br>X                                       | 5<br>1 | 1      | 1        | 2<br>X     | 1 0<br>X X  | ן le ਰੋ                                                         | <u>SE</u> WIDTH COMPARISO<br>SATE ★ IS > COUNT                                               | ON MODE: INTERRUPT<br>ER TIME OUT |               |  |  |  |  |

|        |                                              | I      | 1      | I        | 1          | <del></del> | _                                                               | 1                                                                                            | <u> </u>                          |               |  |  |  |  |

| 7<br>X | 6                                            | 5<br>X | 4<br>X | 3<br>X   | 2<br>X     | 1 0         | $\frac{0}{1}$                                                   | INTERRUPT FLAG                                                                               |                                   |               |  |  |  |  |

|        | <b>」▼</b>                                    |        |        |          |            |             |                                                                 |                                                                                              |                                   |               |  |  |  |  |

| 7      | 6                                            | 5      | 4      | 3        | 2          | 1 0         |                                                                 | TIMER OUTPUT MA                                                                              |                                   |               |  |  |  |  |

| -      | X X X X X X X X X X 1 TIMER OUTPUT ENABLE    |        |        |          |            |             |                                                                 |                                                                                              |                                   |               |  |  |  |  |

NOTE: RESET IS HARDWARE OR SOFTWARE RESET (RESET = 0 OR CR10 = 1)

Figure 4-3 MC6840 Control Register Programming

## **CHAPTER 5**

#### 5.0 INSTRUCTION

This chapter describes four MC6840 Programmable Timer Module applications.

Programming Four Modes on the Programmable Timer Thermometer Real Time Timer Ignition Analyzer

The PTM has many other applications in pulse generation, interval and period measurement, industrial timing control and programmable one-shot uses. The four applications in this chapter attempt to demonstrate the MC6840 PTM's versatility in different applications.

#### 5.1 PROGRAMMING FOUR MODES ON THE PROGRAMMABLE TIMER

The purpose of this program is to bring a software tool into the hands of the user which demonstrates the four basic modes of the MC6840. The program flow chart is shown in Figure 5-1.

#### 5.1.1 The 16 Bit Continuous Mode

The first mode in the program (Figure 5-2) is the normal 16 bit continuous mode. In this mode any timer will output a 50% duty cycle wave form at various frequencies (the period is twice the value in the latches). The counter decrements through the latches once during which time the output is low, it decrements again and the output is high. The frequence and duty cycle is determined by the number in the latches; i.e. the larger the number (FFFF) the lower the frequency; the smaller the number (0000) the higher the frequency. In this case (0000) a divide by 2 counter is established. In this same mode, with the dual 8 bit configuration selected, the duty cycle is whatever the LSB contains and the period is the number in both the latches plus 2. Start the counter decrementing by the gate signal going low  $(\overline{G}\downarrow)$  and stop the counter at the gate signal going high  $(\overline{G}\uparrow)$ . The switches for  $\overline{G}$  and  $\overline{C}$  are connected as shown in the schematic in Figure 5-3.

#### 5.1.2 The Single Shot Mode

The second mode is a single shot mode where the pulse can be either the width of the number in the MSB and LSB (normal 16 bit) or it can be the width of the number in the LSB with a delay of whatever is in the MSB (dual 8 bit mode). The pulse starts when the gate signal goes low.

#### **5.1.3 The Period Measurement Mode**

In the third mode, the period measurement mode requires  $\overline{G}\downarrow$  before starting and another  $\overline{G}\downarrow$  before a Time Out to Interrupt the MPU. When an IRQ is present the program jumps down to the pulse width comparison mode.

#### 5.1.4 Pulse Width Measurement Mode

In the pulse width measurement mode, the fourth and last mode, the timers are activated by  $\overline{G} \downarrow$ , which decrements the latches until  $\overline{G} \uparrow$ . The  $\overline{IRQ}$  line goes low signaling the MPU that a pulse occurred. Then the "duration" can be checked by reading the timer counter.

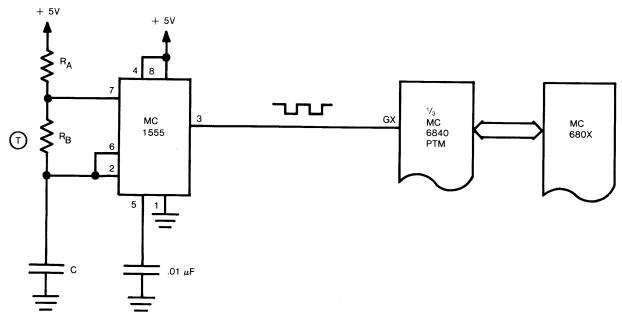

#### **5.2 PTM THERMOMETER**

The MC6840 can be used as a temperature monitoring device as shown in Figure 5-4. An MC1555 is used in the astable mode in order to generate a pulse train for the PTM to monitor. R<sub>B</sub> is a thermistor.

In the astable mode the timer is connected so that it will retrigger itself and cause the capacitor voltage to oscillate between 1/3  $V_{CC}$  and 2/3  $V_{CC}$ .

Figure 5-1 PTM Four Mode Program Flow Chart

```

PAGE 001

00001

NAM

PTM

00002

00003

******

THIS PROGRAM UTILIZES THE FOUR BASIC MODES

00004

*

00005

*

OF THE MC6840 PROGRAMMABLE TIMER.

00006

00007

00008

0000 AE0000

ORG

10000

00010A 0000

0002

A T1

RMR

2

00011A 0002

9992

Δ T2

PMR

2

00012A 0004

0002

A T3

RMB

THIS IS THE PTM'S DECODED ADDRESS

00013A 4000

ORG

$4000