# **Random Access Memory Databook**

- STATIC Rams

- TTL Rams

- TTL FIFOs

- ECL Rams

# Random Access Memory DATABOOK

Static RAMs

**TTL RAMs**

**TTL FIFOs**

**ECL RAMs**

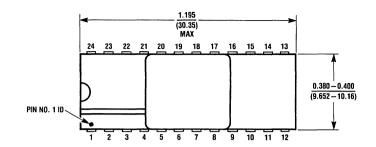

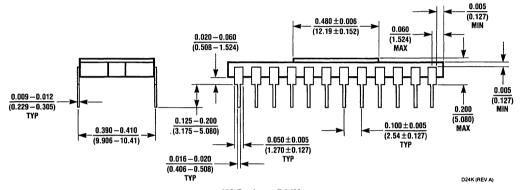

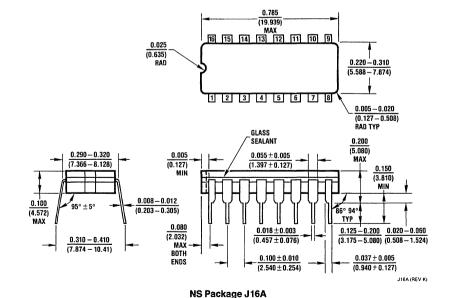

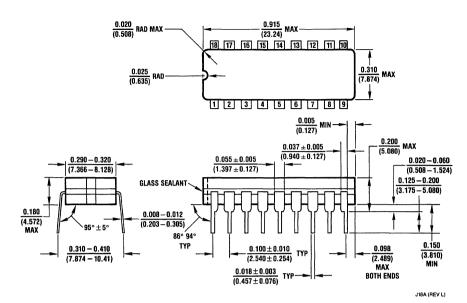

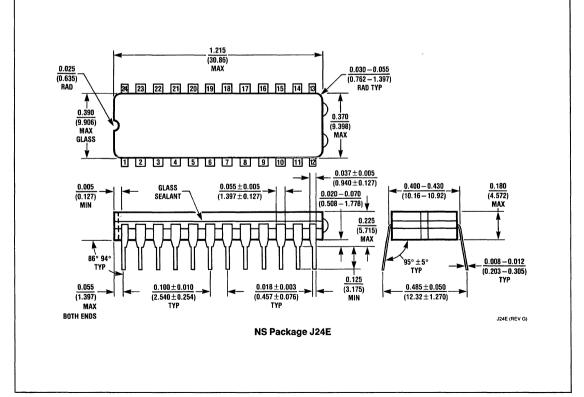

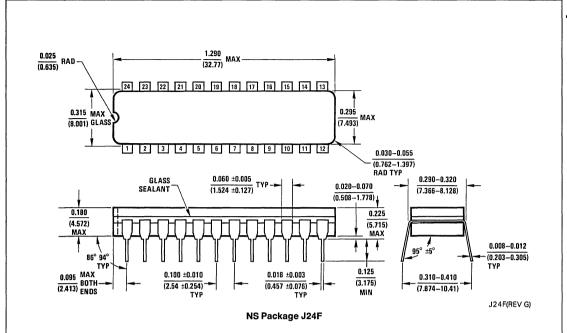

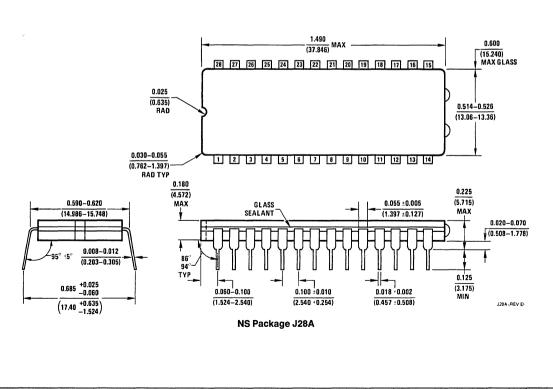

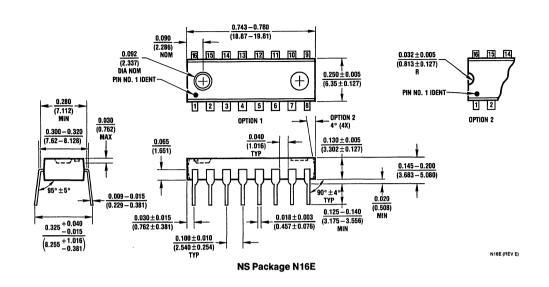

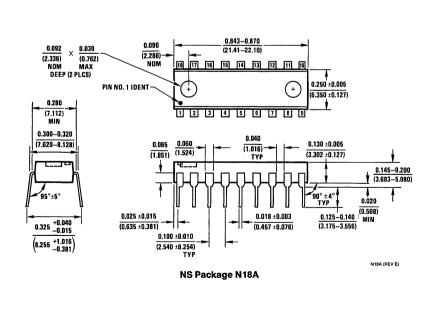

**Physical Dimensions**

#### **TRADEMARKS**

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

Abuseable™ E-Z-LINKTM Anadig™ 5-Star Service™ ANS-R-TRAN™ **GENIXTM** APPSTM **GNXTM** Auto-Chem Deflasher™ HEX 3000™ **BI-FETTM HPCTM ІСМ**ТМ BI-FET IITM BI-LINETM INFOCHEX™ **BIPLANTM** Integral ISETM **BLCTM** Intelisplay™ **BLXTM ISETM** Brite-Lite™ ISE/06TM BTI TM ISE/08™ CheckTrack™ ISE/16TM СІМТМ ISE32TM **CIMBUSTM** KeyScan™ Clock ✓ Chek™ LMCMOSTM. M2CMOSTM СОМВОТМ COMBO ITM Macrobus™ COMBO II™ Macrocomponent<sup>TM</sup> COPSTM microcontrollers Meat ✓ Chek™ Datachecker® Microbus™ data bus **DENSPAKTM** MICRO-DAC™ DIBTM µtalker™

NAX 800TM Nitride Plus™ Nitride Plus Oxide™ **NMLTM** NOBUSTM NSC800™ NSX-16™ NS-XC-16™ NURAM™ OXISSTM. P2CMOSTM Perfect Watch™ Pharma Chek™ **PLANTM** Polycraft™ POSitalker™ Power & Control™ QUAD3000™ QUIKLOOK™ **RATTM** RTX16™ **SABRTM**

Script Chek™

SERIES/800™

Series 3000™

Series 32000®

**SCXTM**

Naked-8™

National®

STARPLEX IITM SuperChip<sup>TM</sup> SuperScript<sup>TM</sup> SYS32TM TapePak<sup>TM</sup> **TDSTM** TeleGate™ The National Anthem® Time Chek™ TINATM TLCTM Trapezoidal<sup>TM</sup> TRI-CODE™ TRI-POLYTM TRI-SAFE™ TRI-STATE® TURBOTRANSCEIVER™ **VIPTM** VR32TM **XMOSTM XPUTM** Z STARTM 883B/RETSTM 883S/RETS™

Shelf Chek™

STARPLEXTM

SPIRETM

STARTM

Starlink<sup>TM</sup>

#### LIFE SUPPORT POLICY

Digitalker®

DISTILLTM

DNR™

DPVMTM

**ELSTAR™**

DISCERN™

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

Microtalker™

**MOLETM**

**MSTTM**

MICROWIRE™

MICROWIRE/PLUSTM

A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 (408) 721-5000 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

# Random Access Memory Databook Introduction

The Random Access Memory databook contains comprehensive technical information on National's volatile memory product lines. National offers a breadth of static-RAM products from high-speed, low-power MOS SRAMs to ultra-high-performance ECL RAMs.

# **Table of Contents**

| Section 1 Static RAMs                                                   |             |

|-------------------------------------------------------------------------|-------------|

| NMC2147H 4096 x 1 Static RAM                                            | 1-3         |

| NMC2148H 1024 x 4 Static RAM                                            | <b>-1-8</b> |

| NMC6164AN/NMC6164AN-L 8192 x 8-Bit Static RAM                           | 1-13        |

| NMC61256N/NMC61256N-L 32,768 x 8-Bit Static RAM                         | 1-18        |

| Section 2 TTL RAMs                                                      |             |

| TTL RAM Selection Guide                                                 | 2-3         |

| DM54S189/DM74S189 64-Bit (16 x 4) TRI-STATE® RAM, DM74S289 64-Bit Open- |             |

| Collector RAM, DM54S189A/DM74S189A High Speed 64-Bit TRI-STATE RAM      | 2-4         |

| DM85S06 Open-Collector, DM75S07/DM85S07 TRI-STATE, DM75S07A/DM85S07A    |             |

| High Speed TRI-STATE Non-Inverting, 64-Bit (16 x 4) RAMs                | 2-12        |

| DM75S68/DM85S68/DM75S68A/DM85S68A 16 x 4 Edge Triggered Registers       | 2-20        |

| IDM29705/29705A 16 Word by 4-Bit Two-Port RAM/Register File             | 2-24        |

| Section 3 TTL FIFOs                                                     |             |

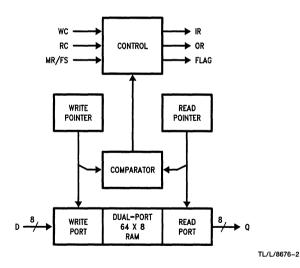

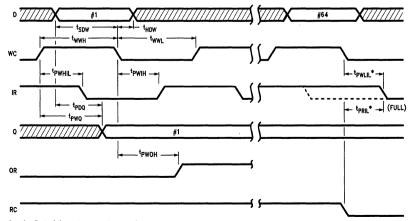

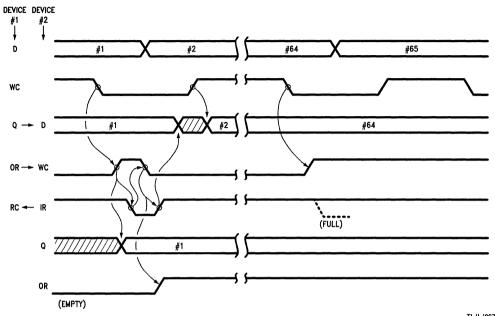

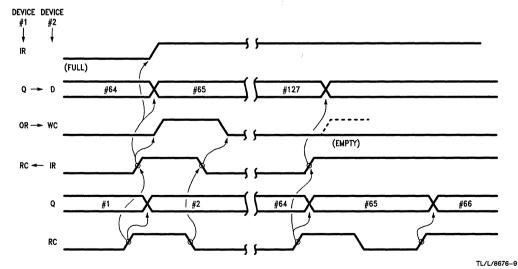

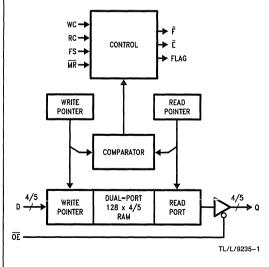

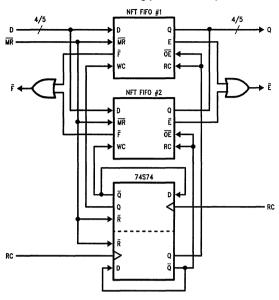

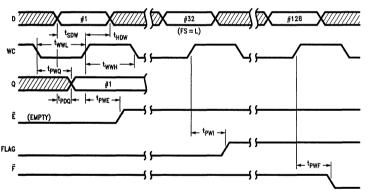

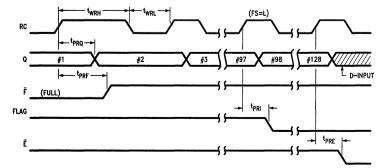

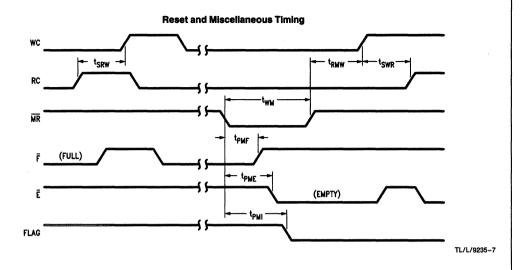

| DM75/85X431 64 x 8 No-Fall-Through FIFO Memory                          | 3-3         |

| DM75/85X432 128 x 4, DM75/85X433 128 x 5 No-Fall-Through FIFO Memories  | 3-9         |

| Section 4 ECL RAMs                                                      |             |

| DM10414/DM10414A 256 x 1 ECL Random Access Memory                       | 4-3         |

| DM10415/DM10415A 1024 x 1 ECL Random Access Memory                      | 4-8         |

| DM10422/DM10422A/DM10422A-7 1024-Bit (256 x 4) ECL RAM                  | 4-13        |

| DM10470/DM10470A 4096-Bit (4096 x 1) ECL RAMs                           | 4-19        |

| DM10474A/DM10474A-10/DM10474A-8 4096-Bit (1024 x 4) ECL RAMs            | 4-24        |

| DM100422/DM100422A 1024-Bit (256 x 4) ECL RAM                           | 4-30        |

| DM100470/DM100470A 4096-Bit (4096 x 1) ECL RAMs                         | 4-35        |

| DM100474A/DM100474A-10/DM100474A-8 4096-Bit (1024 x 4) ECL RAM          | 4-40        |

| Section 5 Physical Dimensions                                           |             |

# Alpha-Numeric Index

| DM10414 256 x 1 ECL Random Access Memory4-3                          |

|----------------------------------------------------------------------|

| DM10414A 256 x 1 ECL Random Access Memory4-3                         |

| DM10415 1024 x 1 ECL Random Access Memory                            |

| DM10415A 1024 x 1 ECL Random Access Memory4-8                        |

| DM10422 1024-Bit (256 x 4) ECL RAM4-13                               |

| DM10422A 1024-Bit (256 x 4) ECL RAM4-13                              |

| DM10422A-7 1024-Bit (256 x 4) ECL RAM4-13                            |

| DM10470 4096-Bit (4096 x 1) ECL RAM4-19                              |

| DM10470A 4096-Bit (4096 x 1) ECL RAM4-19                             |

| DM10474A 4096-Bit (1024 x 4) ECL RAM                                 |

| DM10474A-8 4096-Bit (1024 x 4) ECL RAM                               |

| DM10474A-10 4096-Bit (1024 x 4) ECL RAM                              |

| DM100422 1024-Bit (256 x 4) ECL RAM4-30                              |

| DM100422A 1024-Bit (256 x 4) ECL RAM                                 |

| DM100470 4096-Bit (4096 x 1) ECL RAM                                 |

| DM100470A 4096-Bit (4096 x 1) ECL RAM                                |

| DM100474A 4096-Bit (1024 x 4) ECL RAM                                |

| DM100474A-8 4096-Bit (1024 x 4) ECL RAM                              |

| DM100474A-10 4096-Bit (1024 x 4) ECL RAM4-40                         |

| DM54S189 64-Bit (16 x 4) TRI-STATE RAM2-4                            |

| DM54S189A High Speed 64-Bit TRI-STATE RAM2-4                         |

| DM74S189 64-Bit (16 x 4) TRI-STATE RAM2-4                            |

| DM74S189A High Speed 64-Bit TRI-STATE RAM2-4                         |

| DM74S289 64-Bit Open Collector RAM2-4                                |

| DM75S07 TRI-STATE Non-Inverting, 64-Bit (16 x 4) RAM2-12             |

| DM75S07A High Speed TRI-STATE Non-Inverting, 64-Bit (16 x 4) RAM2-12 |

| DM75S68 16 x 4 Edge Triggered Registers                              |

| DM75S68A 16 x 4 Edge Triggered Registers2-20                         |

| DM75/85X431 64 x 8, No-Fall Through FIFO Memory                      |

| DM75/85X432 128 x 4, No-Fall Through FIFO Memory3-9                  |

| DM75/85X433 128 x 5, No-Fall Through FIFO Memory                     |

| DM85S06 Open-Collector Non-Inverting, 64-Bit (16 x 4) RAM            |

| DM85S07 TRI-STATE Non-Inverting, 64-Bit (16 x 4) RAM2-12             |

| DM85S07A High Speed TRI-STATE Non-Inverting, 64-Bit (16 x 4) RAM2-12 |

| DM85S68 16 x 4 Edge Triggered Register                               |

| DM85S68A 16 x 4 Edge Triggered Register2-20                          |

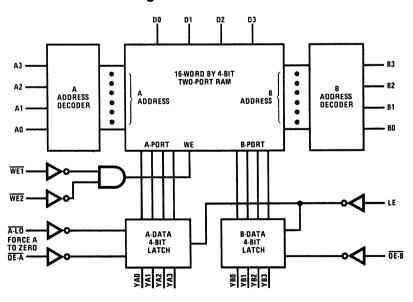

| IDM29705 16 Word By 4-Bit Two-Port RAM/Register File2-24             |

| IDM29705A 16 Word By 4-Bit Two-Port RAM/Register File2-24            |

| NMC2147H 4096 x 1 Static RAM                                         |

| NMC2148H 1024 x 4 Static RAM                                         |

| NMC6164AN 8192 x 8-Bit Static RAM1-13                                |

| NMC6164AN-L 8192 x 8-Bit Static RAM1-13                              |

| NMC61256N 32,768 x 8-Bit Static RAM1-18                              |

| NMC61256N-L 32,768 x 8-Bit Static RAM1-18                            |

|  |   | ( |   |  |

|--|---|---|---|--|

|  |   |   | I |  |

|  | , |   |   |  |

|  |   |   |   |  |

|  |   |   |   |  |

|  |   |   |   |  |

|  |   |   |   |  |

|  |   |   |   |  |

|  |   |   |   |  |

|  |   |   |   |  |

# Section 1 Static RAMs

Я

# **Section 1 Contents**

| DEVICE                 | DESCRIPTION               | PAGE<br>NUMBER |

|------------------------|---------------------------|----------------|

| NMC2147H               | 4096 x 1 Static RAM       | 1-3            |

| NMC2148H               | 1024 x 4 Static RAM       | 1-8            |

| NMC6164AN, NMC6164AN-L | 8192 x 8-Bit Static RAM   | 1-13           |

| NMC61256N, NMC61256N-L | 32,768 x 8-Bit Static RAM | 1-18           |

## NMC2147H 4096 x 1 Static RAM

#### **General Description**

The NMC2147H is a 4096-word by 1-bit static random access memory fabricated using N-channel silicon-gate technology. All internal circuits are fully static and therefore require no clocks or refreshing for operation. The data is read out nondestructively and has the same polarity as the input data.

The separate chip select input automatically switches the part to its low power standby mode when it goes high.

The output is held in a high impedance state during write to simplify common I/O applications.

#### **Features**

- All inputs and outputs directly TTL compatible

- Static operation-no clocks or refreshing required

- Automatic power-down

- High-speed-down to 35 ns access time

- TRI-STATE® output for bus interface

- Separate Data In and Data Out pins

- Single +5V supply

- Standard 18-pin dual-in-line package

- Available in MIL-STD-883 class B screening

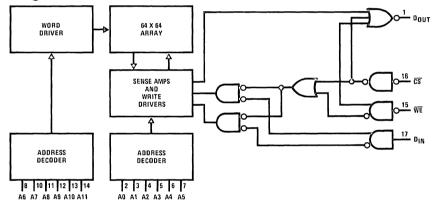

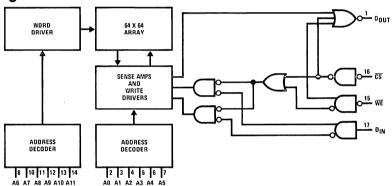

# MEMORY ARRAY ROW SELEC 1-0F-64 COLUMN I/O CIRCUITS O D<sub>OUT</sub> (0) COLUMN SELECT TL/D/5257-1

#### Pin Names\*

| A0-A11               | Address Input |

|----------------------|---------------|

| WE (W)               | Write Enable  |

| CS (S)               | Chip Select   |

| D <sub>IN</sub> (D)  | Data In       |

| D <sub>OUT</sub> (Q) | Data Out      |

| Vcc                  | Power (5V)    |

| Vss                  | Ground        |

Order Number NMC2147HJ-1. NMC2147HJ-2, NMC2147HJ-3, or NMC2147HJ-3L NS Package Number J18A Order Number NMC2147HN-1. NMC2147HN-2, NMC2147HN-3 or NMC2147HN-3L NS Package Number N18A

# Logic Symbol\*

# Connection Diagram\*

\*The symbols in parentheses are proposed industry standard.

### **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Voltage on Any Pin Relative to VSS -3.5V to +7VStorage Temperature Range -65°C to +150°C Power Dissipation 1.2W DC Output Current 20 mA

Bias Temperature Range -65°C to +135°C 300°C

Lead Temperature (Soldering, 10 sec.)

#### Truth Table\*

| CS<br>(S) | WE<br>(W) | DIN<br>(D) | DOUT<br>(Q) | Mode         | Power   |

|-----------|-----------|------------|-------------|--------------|---------|

| Н         | Х         | Х          | Hi-Z        | Not Selected | Standby |

| L         | L         | Н          | Hi-Z        | Write 1      | Active  |

| L         | L         | L          | Hi-Z        | Write 0      | Active  |

| L         | Н         | Х          | DOUT        | Read         | Active  |

## DC Electrical Characteristics TA = $0^{\circ}$ C to $+70^{\circ}$ C, VCC = 5V $\pm$ 10% (Notes 1 and 2)

| Symbol | Parameter                                                | Conditions                  | NMC2147H-3L |     | NMC2147H-1<br>NMC2147H-2<br>NMC2147H-3 |     | NMC2147H |     | Units |

|--------|----------------------------------------------------------|-----------------------------|-------------|-----|----------------------------------------|-----|----------|-----|-------|

|        |                                                          |                             | Min         | Max | Min                                    | Max | Min      | Max |       |

| ILI    | Input Load Current<br>(All Input Pins)                   | VIN = 0V to 5.5V, VCC = Max |             | 10  |                                        | 10  |          | 10  | μА    |

| ILO    | Output Leakage<br>Current                                |                             |             | 50  |                                        | 50  |          | 50  | μА    |

| VIL    | Input Low Voltage                                        | nput Low Voltage            |             | 0.8 | -3.0                                   | 0.8 | -3.0     | 0.8 | ٧     |

| VIH    | Input High Voltage                                       |                             | 2.0         | 6.0 | 2.0                                    | 6.0 | 2.0      | 6.0 | ٧     |

| VOL    | Output Low Voltage                                       | IOL = 8.0 mA                |             | 0.4 |                                        | 0.4 |          | 0.4 | ٧     |

| VOH    | Output High Voltage                                      | IOH = -4.0 mA               | 2.4         |     | 2.4                                    |     | 2.4      |     | ٧     |

| ICC    | ICC Power Supply VIN = 5.5V, TA = 0° Current Output Open |                             |             | 125 |                                        | 180 |          | 160 | mA    |

| ISB    | Standby Current                                          | VCC = Min to Max, CS = VIH  |             | 20  |                                        | 30  |          | 20  | mA    |

| IPO    | Peak Power-On                                            |                             |             | 30  |                                        | 40  |          | 30  | mA    |

#### Capacitance TA = 25°C, f = 1 MHz (Note 3)

| Symbol | Parameter                   | Conditions | Min | Max | Units |

|--------|-----------------------------|------------|-----|-----|-------|

| CIN    | Address/Control Capacitance | VIN = 0V   |     | 5   | pF    |

| COUT   | Output Capacitance          | VOUT = 0V  |     | 6   | pF    |

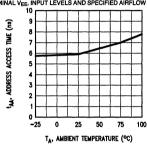

Note 1: The operating ambient temperature range is guaranteed with transverse air flow exceeding 400 linear feet per minute.

Note 2: These circuits require 500 µs time delay after VCC reaches the specified minimum limit to ensure proper orientation after power-on. This allows the internally generated substrate bias to reach its functional level.

Note 3: This parameter is guaranteed by periodic testing.

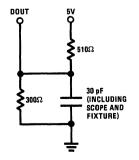

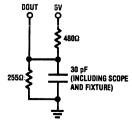

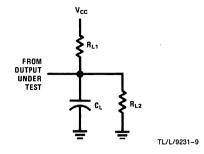

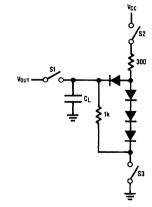

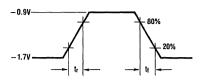

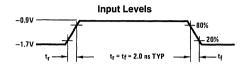

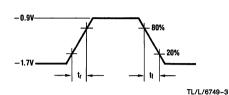

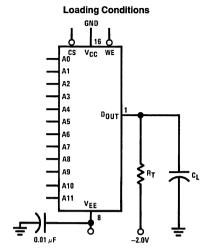

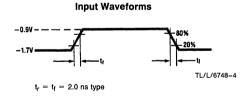

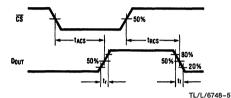

#### AC Test Conditions

Input Test Levels GND to 3.0V Input Rise and Fall Times 5 ns Input Timing Reference Level 1.5V Output Timing Reference Level (H-1) 1.5V Output Timing Reference Level 0.8V and 2.0V (H-2, H-3, H-3L) **Output Load** See Figure 1

TL/D/5257-4

FIGURE 1. Output Load

<sup>\*</sup>Symbols in parentheses are proposed industry standard.

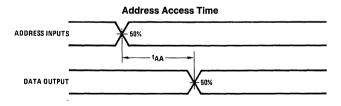

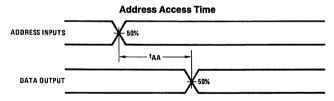

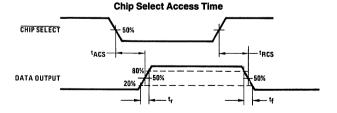

# Read Cycle AC Electrical Characteristics TA = 0°C to 70°C, VCC = 5V ±10% (Note 1)

| Symbol           |          | Parameter                                  | NMC21 | 47H-1 | NMC21 | 47H-2 |     | 147H-3<br>47H-3L | NMC2 | 147H | Units |

|------------------|----------|--------------------------------------------|-------|-------|-------|-------|-----|------------------|------|------|-------|

| Alternate        | Standard | raidilletei                                | Min   | Max   | Min   | Max   | Min | Max              | Min  | Max  | Onits |

| t <sub>RC</sub>  | TAVAV    | Read Cycle Time                            | 35    |       | 45    |       | 55  |                  | 70   |      | ns    |

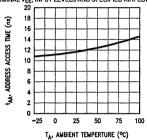

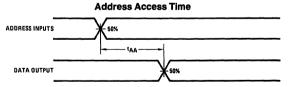

| t <sub>AA</sub>  | TAVQV    | Address Access Time                        |       | 35    |       | 45    |     | 55               |      | 70   | ns    |

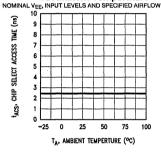

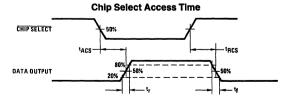

| t <sub>ACS</sub> | TSLQV    | Chip Select Access Time<br>(Notes 4)       |       | 35    |       | 45    |     | 55               |      | 70   | ns    |

| t <sub>LZ</sub>  | TSLQX    | Chip Select to Output Active (Note 5)      | 5     |       | 5     |       | 10  |                  | 10   |      | ns    |

| t <sub>HZ</sub>  | TSHQZ    | Chip Deselect to Output TRI-STATE (Note 5) | 0     | 30    | 0     | 30    | 0   | 30               | 0    | 30   | ns    |

| tон              | TAXQX    | Output Hold from Address<br>Change         | 5     |       | 5     |       | 5   |                  | 5    |      | ns    |

| t <sub>PU</sub>  | TSLIH    | Chip Select to Power-Up                    | 0     |       | 0     |       | 0   |                  | 0    |      | ns    |

| t <sub>PD</sub>  | TSHIL    | Chip Deselect to Power-Down                |       | 20    |       | 20    |     | 20               |      | 30   | ns    |

| Max Access/Current       | NMC2147H-1 | NMC2147H-2 | NMC2147H-3 | NMC2147H-3L | NMC2147H |

|--------------------------|------------|------------|------------|-------------|----------|

| Access (TAVQV—ns)        | 35         | 45         | 55         | 55          | 70       |

| Active Current (ICC—mA)  | 180        | 180        | 180        | 125         | 160      |

| Standby Current (ISB—mA) | 30         | 30         | 30         | 20          | 20       |

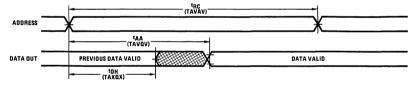

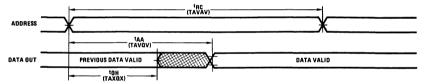

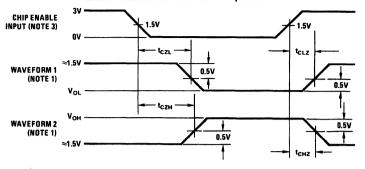

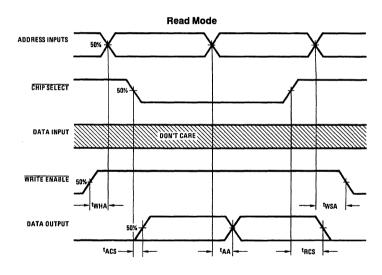

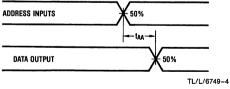

# **Read Cycle Waveforms\***

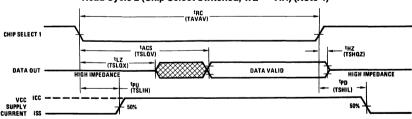

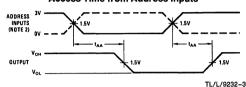

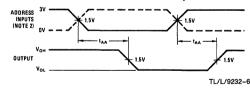

#### Read Cycle 1 (Continuous Selection $\overline{CS} = VIL$ , $\overline{WE} = VIH$ )

TL/D/5257-5

TL/D/5257-6

Note 4: Addresses must be valid coincident with or prior to the chip select transition from high to low.

Note 5: Measured ±50 mV from steady state voltage. This parameter is sampled and not 100% tested.

<sup>\*</sup>The symbols in parentheses are proposed industry standard.

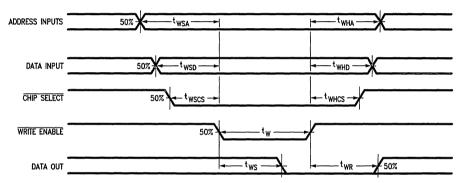

# Write Cycle AC Electrical Characteristics TA = 0°C to 70°C, VCC = 5V ± 10% (Note 1)

| Symbol          |                | Parameter                                    | NMC21 | 47H-1 | NMC21 | 147H-2 | NMC21 | 147H-3<br>47H-3L | NMC2 | 147H | Units |

|-----------------|----------------|----------------------------------------------|-------|-------|-------|--------|-------|------------------|------|------|-------|

| Alternate       | Standard       |                                              | Min   | Max   | Min   | Max    | Min   | Max              | Min  | Max  |       |

| twc             | TAVAV          | Write Cycle Time                             | 35    |       | 45    |        | 55    |                  | 70   |      | ns    |

| tcw             | TSLWH          | Chip Select to End of Write                  | 35    |       | 45    |        | 45    |                  | 55   |      | ns    |

| t <sub>AW</sub> | TAVWH          | Address Valid to End of Write                | 35    |       | 45    |        | 45    |                  | 55   |      | ns    |

| t <sub>AS</sub> | TAVSL<br>TAVWL | Address Set-Up Time                          | 0     |       | 0     |        | ; o   |                  | 0    |      | ns    |

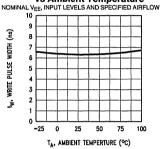

| twp             | TWLWH          | Write Pulse Width                            | 20    |       | 25    |        | 25    |                  | 40   |      | ns    |

| twR             | TWHAX          | Write Recovery Time                          | 0     |       | 0     |        | 10    |                  | 15   |      | ns    |

| t <sub>DW</sub> | TDVWH          | Data Set-Up Time                             | 20    |       | 25    |        | 25    |                  | 30   |      | ns    |

| t <sub>DH</sub> | TWHDX          | Data Hold Time                               | 10    |       | 10    |        | 10    |                  | 10   |      | ns    |

| twz             | TWLQZ          | Write Enable to Output<br>TRI-STATE (Note 5) | 0     | 20    | 0     | 25     | 0     | 25               | 0    | 35   | ns    |

| tow             | TWHQX          | Output Active from End of Write (Note 5)     | 0     |       | 0     |        | 0     |                  | 0    |      | ns    |

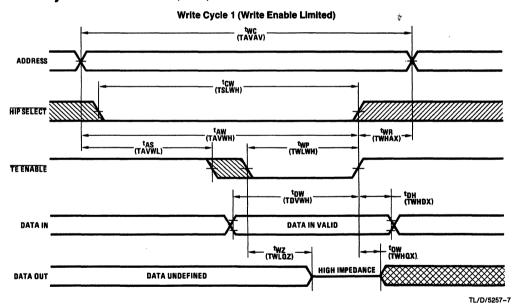

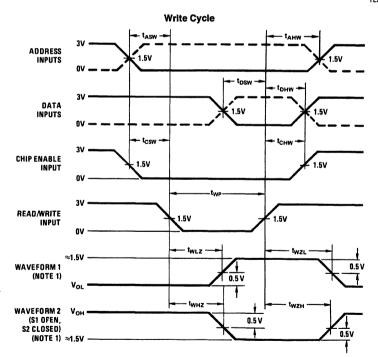

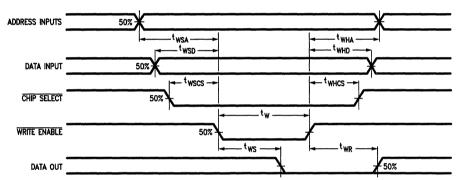

# Write Cycle Waveforms\* (Note 6)

TL/D/5257-8

Note 6: The output remains TRI-STATE if the  $\overline{\text{CS}}$  and  $\overline{\text{WE}}$  go high simultaneously.  $\overline{\text{WE}}$  or  $\overline{\text{CS}}$  or both must be high during the address transitions to prevent an erroneous write.

<sup>\*</sup>The symbols in parentheses are proposed industry standard.

August 1986

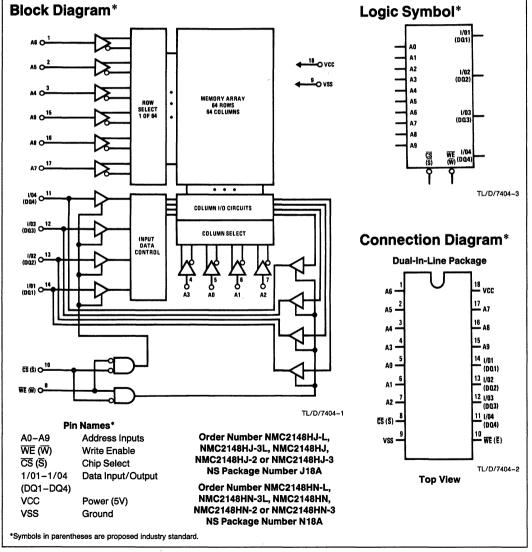

# NMC2148H 1024 x 4 Static RAM

### **General Description**

The NMC2148H is a 1024-word by 4-bit static random access memory fabricated using N-channel silicon-gate technology. All internal circuits are fully static and therefore require no clocks or refreshing for operation. The data is read out nondestructively and has the same polarity as the input data

The separate chip select input automatically switches the part to its low power standby mode when it goes high. Common input/output pins are provided.

#### **Features**

- All inputs and outputs directly TTL compatible

- Static operation—no clocks or refreshing required

- Automatic power-down

- High-speed—down to 45 ns access time

- TRI-STATE® output for bus interface

- Common data I/O pins

- Single +5V supply

- Standard 18-pin dual-in-line package

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Voltage at Any Pin with Respect to VSS

Storate Temperature

Temperature with Bias

DC Output Current

Power Dissipation

Lead Temperature (Soldering, 10 sec.)

-3.5V to +7V

-65°C to +150°C

-10°C to +85°C

20 mA

20 mA

300°C

#### **Truth Table**

| CS | WE | 1/0  | Mode    | Power   |

|----|----|------|---------|---------|

| н  | Х  | Hi-Z | Standby | Standby |

| L  | L  | Н    | Write 1 | Active  |

| L  | L  | L    | Write 0 | Active  |

| L  | Н  | DOUT | Read    | Active  |

#### DC Electrical Characteristics TA = 0°C to +70°C, VCC = 5V ± 10% (Notes 1 and 2)

| Symbol | Parameter                              | Conditions                                          | NMC2148H-L<br>NMC2148H-3L |     | NMC2148H<br>NMC2148H-2<br>NMC2148H-3 |     | Units |

|--------|----------------------------------------|-----------------------------------------------------|---------------------------|-----|--------------------------------------|-----|-------|

|        |                                        |                                                     | Min                       | Max | Min                                  | Max |       |

| ILI    | Input Load Current<br>(All Input Pins) | VIN = 0V to 5.5V,<br>VCC = Max                      |                           | 10  |                                      | 10  | μА    |

| ILO    | Output Leakage Current                 | CS = VIH, VOUT = GND to 4.5V,<br>VCC = Max          |                           | 50  |                                      | 50  | μА    |

| VIL    | Input Low Voltage                      |                                                     | -2.5                      | 0.8 | -2.5                                 | 0.8 | ٧     |

| VIH    | Input High Voltage                     |                                                     | 2.1                       | 6.0 | 2.1                                  | 6.0 | ٧     |

| VOL    | Output Low Voltage                     | IOL = 8.0 mA                                        |                           | 0.4 |                                      | 0.4 | ٧     |

| VOH    | Output High Voltage                    | IOH = −4.0 mA                                       | 2.4                       |     | 2.4                                  |     | ٧     |

| ICC    | Power Supply Current                   | VIN = 5.5V, TA = 0°C,<br>Output Open                |                           | 125 |                                      | 180 | mA    |

| ISB    | Standby Current                        | VCC = Min to Max, $\overline{\text{CS}}$ = VIH      |                           | 20  |                                      | 30  | mA    |

| IPO    | Peak Power-On Current                  | VCC = VSS to VCC Min,  CS = Lower of VCC or VIH Min |                           | 30  |                                      | 40  | mA    |

| IOS    | Output Short Circuit Current           | VOUT = GND to VCC                                   |                           | 250 |                                      | 250 | mA    |

## Capacitance TA = 25°C, f = 1.0 MHz (Note 3)

| Symbol | Parameter                   | Conditions | Min | Max | Units |

|--------|-----------------------------|------------|-----|-----|-------|

| CIN    | Address/Control Capacitance | VIN = 0V   |     | 5   | pF    |

| CI/O   | Input/Output Capacitance    | VI/O⊱ OV   |     | 7   | pF    |

Note 1: The operating ambient temperature range is guaranteed with transverse air flow exceeding 400 linear feet per minute.

Note 2: These circuits require 500 µs time delay after VCC reaches the specified minimum limit to ensure proper operation after power-on. This allows the internally generated substrate bias to reach its functional level.

Note 3: This parameter is guaranteed by periodic testing.

#### **AC Test Conditions**

Input Test Levels GND to 3.0V

Input Rise and Fall Times 5 ns

Input Timing Reference Level 1.5V

Output Timing Reference Levels 0.8V and 2.0V

Output Load See Figure 1

TL/D/7404-4

# Read Cycle AC Electrical Characteristics TA = $0^{\circ}$ C to $+70^{\circ}$ C, VCC = 5V $\pm 10^{\circ}$ (Note 1)

| Symbol            |          | Parameter                                  | NMC2148H-2 |     | NMC2148H-3<br>NMC2148H-3L |     | NMC2148H<br>NMC2148H-L |     | Units |

|-------------------|----------|--------------------------------------------|------------|-----|---------------------------|-----|------------------------|-----|-------|

| Alternate         | Standard |                                            | Min        | Max | Min                       | Max | Min                    | Max |       |

| t <sub>RC</sub>   | TAVAV    | Read Cycle Time                            | 45         |     | 55                        |     | 70                     |     | ns    |

| t <sub>AA</sub>   | TAVQV    | Address Access Time                        |            | 45  |                           | 55  |                        | 70  | ns    |

| t <sub>ACS1</sub> | TSLQV1   | Chip Select Access Time (Notes 4 and 5)    |            | 45  |                           | 55  |                        | 70  | ns    |

| t <sub>ACS2</sub> | TLSQV2   | Chip Select Access Time (Notes 4 and 6)    |            | 55  |                           | 65  |                        | 80  | ns    |

| $t_{LZ}$          | TSLQX    | Chip Select to Output Active (Note 7)      | 20         |     | 20                        |     | 20                     |     | ns    |

| t <sub>HZ</sub>   | TSHQZ    | Chip Deselect to Output TRI-STATE (Note 7) | 0          | 20  | 0                         | 20  | 0                      | 20  | ns    |

| tOH               | TAXQX    | Output Hold from Address Change            | 5          |     | 5                         |     | 5                      |     | ns    |

| t <sub>PU</sub>   | TSLIH    | Chip Select to Power-Up                    | 0          |     | 0                         |     | 0                      |     | ns    |

| t <sub>PD</sub>   | TSHIL    | Chip Deselect to Power-Down                |            | 30  |                           | 30  |                        | 30  | ns    |

| Max Access/Current       | NMC2148H-2 | NMC2148H-3 | NMC2148H | NMC2148H-3L | NMC2148H-L |

|--------------------------|------------|------------|----------|-------------|------------|

| Access (TAVQV—ns)        | 45         | 55         | 70       | 55          | 70         |

| Active Current (ICC—mA)  | 180        | 180        | 180      | 125         | 125        |

| Standby Current (ISB—mA) | 30         | 30         | 30       | 20          | 20         |

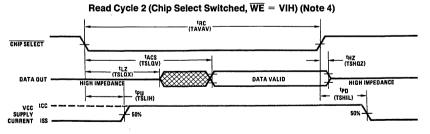

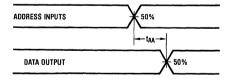

# **Read Cycle Waveforms\***

#### Read Cycle 1 (Continuous Selection $\overline{CS} = VIL$ , $\overline{WE} = VIH$ )

TL/D/7404-5

#### Read Cycle 2 (Chip Select Switched, $\overline{WE} = VIH$ ) (Note 4)

TL/D/7404-6

Note 4: Addresses must be valid coincident with or prior to the chip select transition from high to low.

Note 5: Chip deselected longer than 55 ns.

Note 6: Chip deselected less than 55 ns.

Note 7: Measured  $\pm 50$  mV from steady state voltage. This parameter is sampled and not 100% tested.

\*The symbols in parentheses are proposed industry standard.

# Write Cycle AC Electrical Characteristics TA = $0^{\circ}$ C to $+70^{\circ}$ C, VCC = $5V \pm 10\%$ (Note 1)

| Syn             | nbol           | Parameter                                 | NMC21 | 148H-2 | NMC21 |     | NMC2<br>NMC21 |     | Units |

|-----------------|----------------|-------------------------------------------|-------|--------|-------|-----|---------------|-----|-------|

| Alternate       | Standard       |                                           | Min   | Max    | Min   | Max | Min           | Max |       |

| twc             | TAVAV          | Write Cycle Time                          | 45    |        | 55    |     | 70            |     | ns    |

| tcw             | TSLWH          | Chip Select to End of Write               | 40    |        | 50    |     | 65            |     | ns    |

| t <sub>AW</sub> | TAVWH          | Address Valid to End of Write             | 40    |        | 50    |     | 65            |     | ns    |

| t <sub>AS</sub> | TAVSL<br>TAVWL | Address Set-Up Time                       | 0     |        | 0     |     | 0             |     | ns    |

| t <sub>WP</sub> | TWLWH          | Write Pulse Width                         | 35    |        | 40    |     | 50            |     | ns    |

| t <sub>WR</sub> | TWHAX          | Write Recovery Time                       | 5     |        | 5     |     | 5             |     | ns    |

| t <sub>DW</sub> | TDVWH          | Data Set-Up Time                          | 20    |        | 20    |     | 25            |     | ns    |

| t <sub>DH</sub> | TWHDX          | Data Hold Time                            | 0     |        | 0     |     | 0             |     | ns    |

| t <sub>WZ</sub> | TWLQZ          | Write Enable to Output TRI-STATE (Note 7) | 0     | 15     | 0     | 20  | 0             | 25  | ns    |

| tow             | TWHQX          | Output Active from End of Write (Note 7)  | 0     |        | 0     |     | 0             |     | ns    |

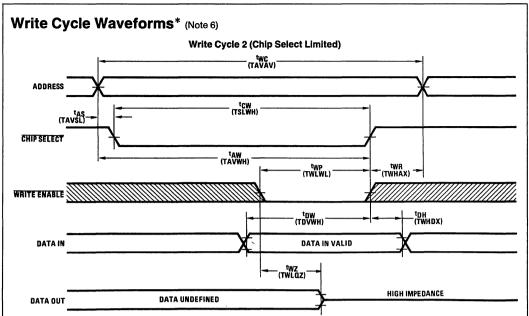

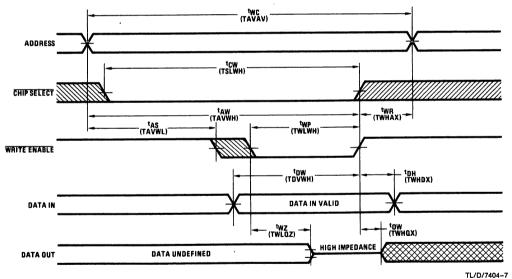

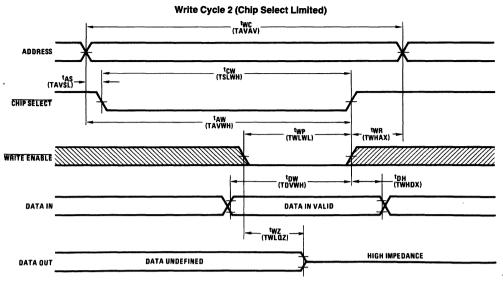

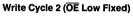

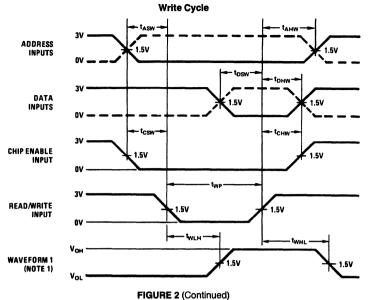

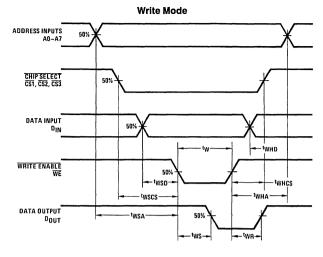

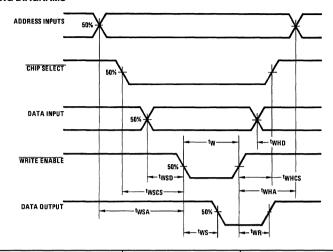

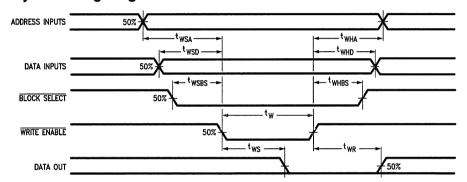

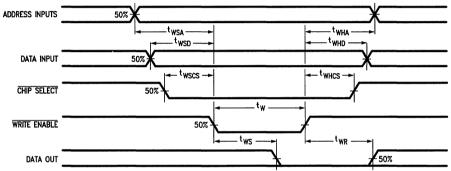

# Write Cycle Waveforms\* (Note 8)

#### Write Cycle 1 (Write Enable Limited)

# Write Cycle Waveforms\* (Note 8) (Continued)

TL/D/7404-8

Note 8: The output remains TRI-STATE if the  $\overline{CS}$  and  $\overline{WE}$  go high simulataneously.  $\overline{WE}$  or  $\overline{CS}$  or both must be high during the address transitions to prevent an erroneous write.

\*Symbols in parentheses are proposed industry standard.

# ADVANCED INFORMATION

## NMC6164AN/6164AN-L 8192 x 8-Bit Static RAM

March 1987

#### **General Description**

The NMC6164A/6164AN-L is an 8192 by 8-bit, new generation, static RAM. It is fabricated with National's proprietary microCMOS double-polysilicon technology which combines high performance and high density with low power consumption and excellent reliability.

The NMC6164A/6164AN-L operates with a single 5V power supply with  $\pm 10\%$  tolerance. Additional battery back-up operation is available (L version) for data retention down to 2V, with low standby current.

Packaging is available in standard 28-pin plastic DIP.

In addition to the inputs and outputs being TTL compatible, the outputs are also CMOS compatible, in that capacitive loads are driven to  $V_{CC}$  or  $V_{SS}$ .

#### **Features**

- Single power supply: 5V ±10%

- Fast access time 45 ns/55 ns/70 ns max

- Equal access and cycle times

- Completely static RAM: no clock or timing strobe required

- Low standby power and low power operation Standby: 10 µW, typical Operation: 10 mW/MHz, typical

- Battery back-up operation available (L version) with data retention supply voltage: 2V-5.5V

- Common data input and output, TRI-STATE® output

- TTL compatible: all inputs and outputs

- CMOS compatible: outputs drive capacitive loads to V<sub>CC</sub> or V<sub>SS</sub>

- Standard 28-pin package configuration

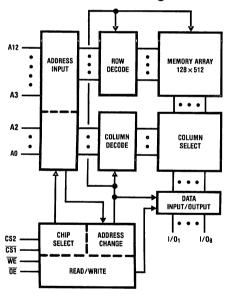

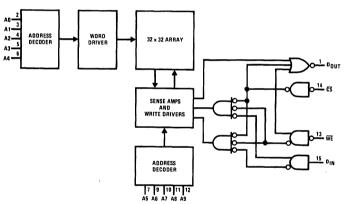

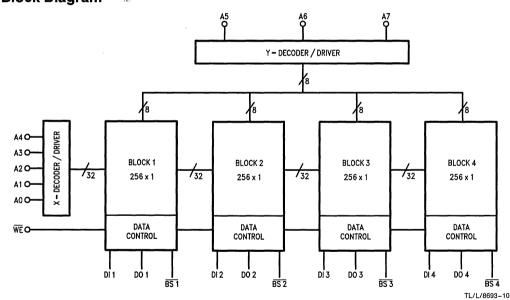

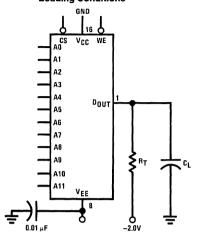

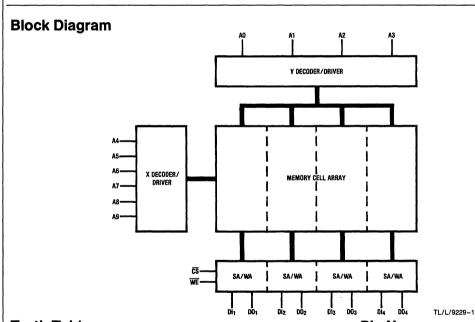

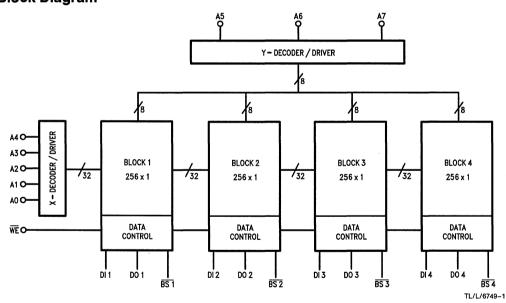

#### **Block and Connection Diagrams**

**CMOS**

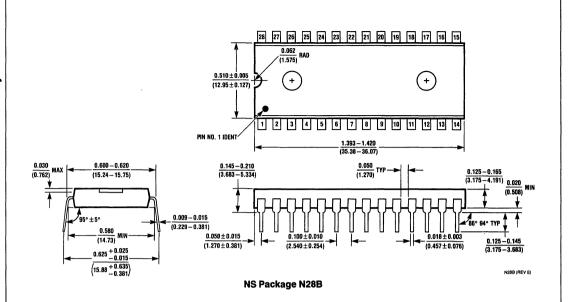

Order Number NMC6164AN or NMC6164AN-L See NS Package Number N28B

| Order Number             | NMC6164AN-45L | NMC6164AN-45 | NMC6164AN-55I | NMC6164AN-55    | NMC6164AN-70L    | NMC6164AN-70 |

|--------------------------|---------------|--------------|---------------|-----------------|------------------|--------------|

| Parameter                | NWC0104AN-45L | MMC6164AN-45 | NWC6164AN-55L | NIVICO 104AN-55 | NINCO 104AI4-70L | NWC6164AN-70 |

| Access<br>Time (ns)      | 45            | 45           | 55            | 55              | 70               | 70           |

| I <sub>CC</sub> Standby, | 100 μΑ        | 2 mA         | 100 μΑ        | 2 mA            | 100 μΑ           | 2 mA         |

TL/D/8808-1

#### **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

# Recommended DC Operating Conditions

| Min          | Max                                                      | Units                                                                               |

|--------------|----------------------------------------------------------|-------------------------------------------------------------------------------------|

| 4.5          | 5.5                                                      | ٧                                                                                   |

| 0            | 0                                                        | V                                                                                   |

|              |                                                          |                                                                                     |

| 2.2          | 6.0                                                      | V                                                                                   |

| $V_{CC}-0.2$ | $V_{CC} + 0.2$                                           | ٧                                                                                   |

|              |                                                          |                                                                                     |

| -0.3         | 0.8                                                      | ٧                                                                                   |

| -0.3         | 0.2                                                      | V                                                                                   |

| 0            | 70                                                       | °C                                                                                  |

|              | 4.5<br>0<br>2.2<br>V <sub>CC</sub> - 0.2<br>-0.3<br>-0.3 | 4.5 5.5 0 0 0 2.2 6.0 V <sub>CC</sub> - 0.2 V <sub>CC</sub> + 0.2 -0.3 0.8 -0.3 0.2 |

# DC Electrical Characteristics at recommended operating conditions

| Sym              | lodr | Parameter                       | Conditions                                                                                                                                                                                                           | Min                   | Max                   | Units |

|------------------|------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-------|

| ILI              |      | Input Leakage Current           | $V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                                                                                                        | -2                    | 2                     | μΑ    |

| lLO              |      | Output Leakage Current          | $\overline{\text{CS1}} = \text{V}_{\text{IH}} \text{ or CS2} = \text{V}_{\text{IL}} \text{ or } \overline{\text{OE}} = \text{V}_{\text{IH}}$ $\text{V}_{\text{I/O}} = \text{V}_{\text{SS}} \text{ to V}_{\text{CC}}$ | -2                    | 2                     | μΑ    |

| lcc              |      | Active Quiescent Current, TTL   | All Inputs at TTL Levels                                                                                                                                                                                             |                       | 25                    | mA    |

| lcc              | Std  | Active Quiescent Current, CMOS  | All Inputs at CMOS Levels                                                                                                                                                                                            |                       | 2                     | mA    |

|                  | L    |                                 |                                                                                                                                                                                                                      |                       | 100                   | μΑ    |

| ICC1             |      | Average Operating Current, TTL  | $\begin{array}{l} t_{RC} = t_{RC}  \text{Min} \\ \hline CS1 = V_{IL}  \text{TTL and CS2} = V_{IH}  \text{TTL} \\ I_{I/O} = 0  \text{mA} \\ \text{All Inputs at TTL Levels} \end{array}$                              |                       | 50                    | mA    |

|                  |      | Average Operating Current, CMOS | $\begin{array}{l} t_{RC} = t_{RC}  \text{Min} \\ \hline CS1 = V_{IL}  \text{CMOS and CS2} = V_{IH}  \text{CMOS} \\ I_{I/O} = 0  \text{mA} \\ \text{All Inputs at CMOS Levels} \end{array}$                           |                       | 30                    | mA    |

| ISB              | Std  | Standby Power Supply Current    | CS1 = V <sub>IH</sub> TTL or CS2 = V <sub>IL</sub> TTL                                                                                                                                                               |                       | 4                     | mA    |

|                  | L    |                                 |                                                                                                                                                                                                                      |                       | 2                     | mA    |

| I <sub>SB1</sub> | Std  | Standby Power Supply Current    | CS1 = V <sub>IH</sub> CMOS or CS2 = V <sub>IL</sub> CMOS                                                                                                                                                             |                       | 2                     | mA    |

|                  | L    |                                 |                                                                                                                                                                                                                      |                       | 100                   | μΑ    |

| V <sub>OL</sub>  |      | Output Low Voltage, TTL         | $I_{OL} = 8 \text{ mA}$                                                                                                                                                                                              |                       | 0.4                   | ٧     |

|                  |      | Output Low Voltage, CMOS        | $I_{OL} = \pm 10 \mu A$                                                                                                                                                                                              | -0.2                  | 0.2                   | ٧     |

| VoH              |      | Output High Voltage, TTL        | $I_{OH} = -4.0 \text{ mA}$                                                                                                                                                                                           | 2.4                   |                       | ٧     |

|                  |      | Output High Voltage, CMOS       | $I_{OH} = \pm 10 \mu A$                                                                                                                                                                                              | V <sub>CC</sub> - 0.2 | V <sub>CC</sub> + 0.2 | V     |

# Capacitance

| Symbol           | Parameter                | Conditions                     | Max | Units |

|------------------|--------------------------|--------------------------------|-----|-------|

| C <sub>IN</sub>  | Input Capacitance        | V <sub>IN</sub> = 0V (Note 5)  | 8   | pF    |

| C <sub>I/O</sub> | Input/Output Capacitance | V <sub>I/O</sub> = 0V (Note 5) | 10  | pF    |

#### **Truth Table**

| Mode            | WE | CS1 | CS2 | ŌĒ | I/O              | Current                            |

|-----------------|----|-----|-----|----|------------------|------------------------------------|

| Not Selected    | *  | Н   | *   | *  | Hi-Z             | I <sub>SB</sub> , I <sub>SB1</sub> |

| (Power Down)    | *  | *   | L   | *  | Hi-Z             | I <sub>SB</sub> , I <sub>SB1</sub> |

| Output Disabled | Н  | L   | Н   | Н  | Hi-Z             | Icc, Icc1                          |

| Read            | Н  | L   | Н   | L  | D <sub>OUT</sub> | Icc, Icc1                          |

| Write           | L  | L   | Н   | *  | D <sub>IN</sub>  | I <sub>CC</sub> , I <sub>CC1</sub> |

\*Don't Care (H or L) H = Logic HIGH Level L = Logic LOW Level

#### **AC Electrical Characteristics\*** (Note 1)

|                  |                                                          | NMC6164AN/6164AN-L |     |     |     |     |     |       |

|------------------|----------------------------------------------------------|--------------------|-----|-----|-----|-----|-----|-------|

| Symbol           | Parameter                                                |                    | 45  | -   | 55  | -   | 70  | Units |

|                  |                                                          | Min                | Max | Min | Max | Min | Max |       |

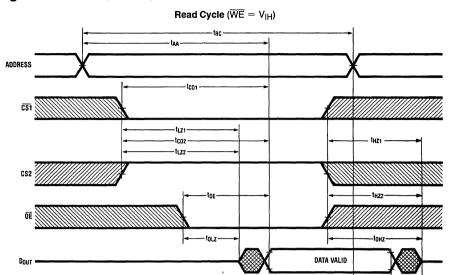

| READ CY          | CLE (Note 4)                                             |                    |     |     |     |     |     |       |

| t <sub>RC</sub>  | Read Cycle Time                                          | 45                 |     | 55  |     | 70  |     | ns    |

| t <sub>AA</sub>  | Address Access Time                                      |                    | 45  |     | 55  |     | 70  | ns    |

| t <sub>CO1</sub> | Chip Selection (CS1) to Output Valid                     |                    | 45  |     | 55  |     | 70  | ns    |

| t <sub>CO2</sub> | Chip Selection (CS2) to Output Valid                     |                    | 45  |     | 55  |     | 70  | ns    |

| tOE              | Output Enable (OE) to Output Valid                       |                    | 20  |     | 25  |     | 30  | ns    |

| t <sub>LZ1</sub> | Chip Selection (CS1) to Output Active (Note 12)          | 15                 |     | 15  |     | 15  |     | ns    |

| t <sub>LZ2</sub> | Chip Selection (CS2) to Output Active (Note 12)          | 15                 |     | 15  |     | 15  |     | ns    |

| toLZ             | Output Enable (OE) to Output Active (Note 12)            | 5                  |     | 5   |     | 5   |     | ns    |

| t <sub>HZ1</sub> | Chip Deselection (CS1) to Output in Hi-Z (Notes 2 and 3) | 0                  | 20  | 0   | 25  | 0   | 30  | ns    |

| t <sub>HZ2</sub> | Chip Deselection (CS2) to Output in Hi-Z (Notes 2 and 3) | 0                  | 20  | 0   | 25  | 0   | 30  | ns    |

| tonz             | Output Disable (OE) to Output in Hi-Z (Notes 2 and 3)    | 0                  | 15  | 0   | 20  | 0   | 25  | ns    |

| toha             | Output Hold from Address Change                          | 5                  |     | 5   |     | 5   |     | ns    |

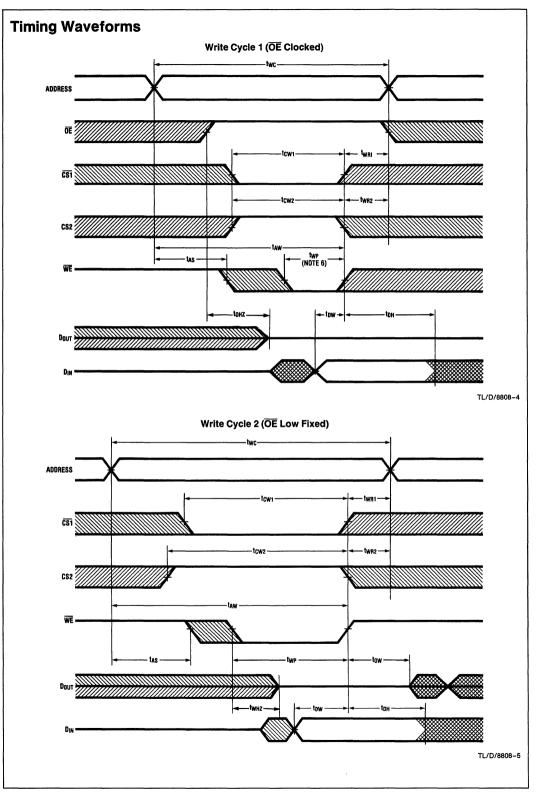

| WRITE C'         | YCLE                                                     |                    |     |     |     |     |     |       |

| twc              | Write Cycle Time                                         | 45                 |     | 55  |     | 70  |     | ns    |

| t <sub>CW1</sub> | Chip Selection (CS1) to End of Write (Note 10)           | 40                 |     | 50  |     | 60  |     | ns    |

| t <sub>CW2</sub> | Chip Selection (CS2) to End of Write                     | 40                 |     | 50  |     | 60  |     | ns    |

| t <sub>AS</sub>  | Address Setup Time (Note 7)                              | 0                  |     | 0   |     | 0   |     | ns    |

| t <sub>AW</sub>  | Address Valid to End of Write                            | 40                 |     | 50  |     | 60  |     | ns    |

| t <sub>WP</sub>  | Write Pulse Width (Note 6)                               | 35                 |     | 40  |     | 50  |     | ns    |

| t <sub>WR1</sub> | Write Recovery Time from CS1 (Note 8)                    | 0                  |     | 0   |     | 0   |     | ns    |

| t <sub>WR2</sub> | Write Recovery Time from CS2 (Note 8)                    | 0                  |     | 0   |     | 0   |     | ns    |

| t <sub>WHZ</sub> | Beginning of Write to Output in Hi-Z (Note 9)            | 0                  | 15  | 0   | 20  | 0   | 25  | ns    |

| t <sub>DW</sub>  | Data Valid to Write Time Overlap                         | 20                 |     | 25  |     | 35  |     | ns    |

| t <sub>DH</sub>  | Data Hold from End of Write                              | 0                  |     | 0   |     | 0   |     | ns    |

| tonz             | Output Disable (OE) to Output in Hi-Z                    | 0                  | 15  | 0   | 20  | 0   | 25  | ns    |

| tow              | Output Active from End of Write                          | 0                  |     | 0   |     | 0   |     | ns    |

<sup>\*</sup>Applies to Standard and L Versions.

Note 1: AC test conditions  $T_A = 0$ °C to +70°C,  $V_{CC} = 5V \pm 10$ %.

Note 2: t<sub>HZ</sub> and t<sub>OHZ</sub> are defined as the time at which the outputs achieve the open circuit condition and are determined as:

High to TRI-STATE, measured  $V_{OH}$  (DC) -0.10VLow to TRI-STATE, measured  $V_{OL}$  (DC) +0.10V

Note 3: At any given temperature and voltage condition, thz MAX is less than tLZ MIN, both for a given device and from device to device (guaranteed, not tested).

Note 4: WE is high for read cycle.

Note 5:  $T_A = 25$ °C, f = 1.0 MHz. This parameter is sampled and not 100% tested.

Note 6: A write occurs during the overlap (twp) of a low CS1 and a high CS2 and a low WE.

Note 7: t<sub>AS</sub> is measured from the address changes to the beginning of the write.

Note 8:  $t_{WR}$  is measured from the earliest of  $\overline{CS1}$  or  $\overline{WE}$  going high or CS2 going low to the end of the write cycle.

Note 9: If CS1 is low and CS2 is high during this period, I/O pins are in the output state. At this time, the data input signals of opposite phase to the outputs must not be applied.

Note 10: If the CST low transition occurs simultaneously with the WE low transition or after the WE transition, the outputs will remain in a Hi-Z state.

Note 11: CS2 controls the address buffers,  $\overline{WE}$  buffer,  $\overline{CS1}$  buffer,  $\overline{D_{IN}}$  buffer and  $\overline{OE}$  buffer. When CS2 controls the data retention mode, all inputs (address, I/O,  $\overline{WE}$ ,  $\overline{CS1}$ ,  $\overline{OE}$ ) can be in the high impedance state. When  $\overline{CS1}$  controls the data retention mode, CS2 must be at  $V_{IH}$ , CMOS. All other input levels (address,  $\overline{OE}$ ,  $\overline{WE}$ , I/O) can be in the high impedance state.

Note 12: Output active level is defined as steady state TRI-STATE level  $\pm 0.1 V$ .

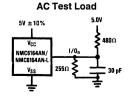

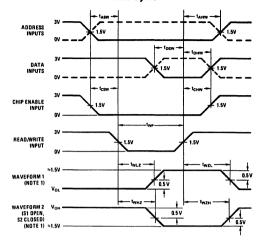

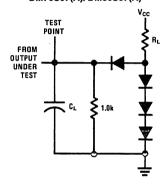

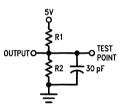

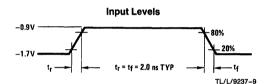

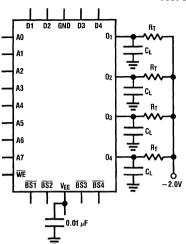

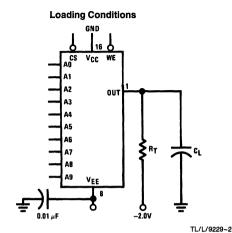

#### **AC Test Conditions**

$\label{eq:local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_$

(Including Jig & Probe Capacitance)

TL/D/8808-3

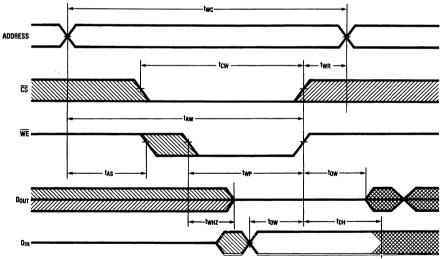

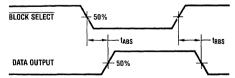

# Timing Waveforms (Continued)

TL/D/8808-6

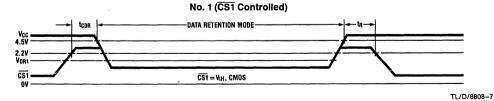

# Low V<sub>CC</sub> Data Retention (L Version)

| Symbol             | Parameter                            | Conditions                                                             | Min             | Max | Units |

|--------------------|--------------------------------------|------------------------------------------------------------------------|-----------------|-----|-------|

| V <sub>DR1</sub>   | V <sub>CC</sub> for Data Retention   | CS1 > V <sub>IH</sub> , CMOS (Note 11)<br>CS2 > V <sub>IH</sub> , CMOS | 2.0             | 5.5 | ٧     |

| V <sub>DR2</sub>   | V <sub>CC</sub> for Data Retention   | CS2 < V <sub>IL</sub> , CMOS (Note 11)                                 | 2.0             | 5.5 | ٧     |

| ICCDR1             | Data Retention Current               | $V_{CC} = 2V$ $\overline{CS1} > V_{IH}$ , CMOS $CS2 > V_{IH}$ , CMOS   |                 | 40  | μΑ    |

| I <sub>CCDR2</sub> | Data Retention Current               | V <sub>CC</sub> = 2V<br>CS2 < V <sub>IL</sub> , CMOS                   |                 | 40  | μΑ    |

| tCDR               | Chip Deselect to Data Retention Time | See Retention Waveform                                                 | 0               |     | ns    |

| t <sub>R</sub>     | Operation Recovery Time              | See Retention Waveform                                                 | t <sub>RC</sub> |     | ns    |

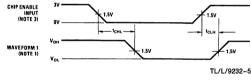

# Low V<sub>CC</sub> Data Retention Waveforms

TL/D/8808-8

## **ADVANCED INFORMATION**

April 1987

# NMC61256N/NMC61256N-L 32,768 x 8-Bit Static RAM

#### **General Description**

The NMC61256N/NMC61256N-L is a 32,768 by 8-bit, new generation static RAM. It is fabricated with National's proprietary microCMOS double-polysilicon technology which combines high performance and high density with low power consumption and excellent reliability.

The NMC61256N/NMC61256N-L operates with a single 5V power supply with  $\pm 10\%$  tolerance. Additional battery back-up operation is available (L version) for data retention down to 2V, with low standby current.

Packaging is in standard 28-pin plastic DIP.

In addition to the inputs and outputs being TTL compatible, the outputs are also CMOS compatible, in that capacitive loads are driven to  $V_{CC}$  or  $V_{SS}$ .

#### **Features**

- Single power supply: 5V ±10%

- Fast access time 70 ns/100 ns/120 ns max

- Equal access and cycle times

- Completely static RAM: no clock or timing strobe required

- Low standby power and low power operation Standby: 50 μW, typical

Operation: 10 mW/MHz, typical

- Battery back-up operation available (L version) with data retention supply voltage: 2V-5.5V

- Common data input and output, TRI-STATE® output

- TTL compatible: all inputs and outputs

- CMOS compatible: outputs drive capacitive loads to V<sub>CC</sub> or V<sub>SS</sub>

- Standard 28-pin package configuration

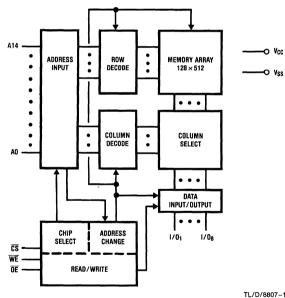

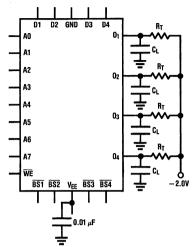

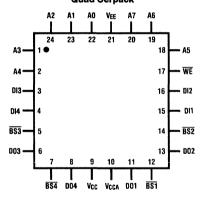

## **Block and Connection Diagrams**

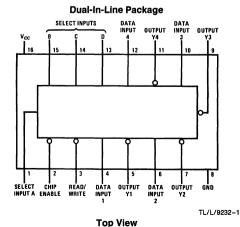

#### **Dual-In-Line Package**

**Top View**

Order Number NMC61256N or NMC61256N-L See NS Package Number N28A

| Order<br>Number<br>Parameter     | NMC61256N-70L | NMC61256N-70 | NMC61256N-100L | NMC61256N-100 | NMC61256N-120L | NMC61256N-120 |

|----------------------------------|---------------|--------------|----------------|---------------|----------------|---------------|

| Access<br>Time (ns)              | 70            | 70           | 100            | 100           | 120            | 120           |

| I <sub>CC</sub> Standby,<br>CMOS | 500 μΑ        | 2 mA         | 500 μA         | 2 mA          | 500 μΑ         | 2 mA          |

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/Distributors for availability and specifications.

ESD rating to be determined.

# Recommended DC Operating Conditions

| Oorialtions                                                      | Min                          | Max                          | Units  |

|------------------------------------------------------------------|------------------------------|------------------------------|--------|

| V <sub>CC</sub> Supply Voltage                                   | 4.5                          | 5.5                          | ٧      |

| V <sub>SS</sub> Supply Voltage                                   | 0                            | 0                            | ٧      |

| V <sub>IH</sub> , Input High Voltage<br>(Logic 1)<br>TTL<br>CMOS | 2.2<br>V <sub>CC</sub> – 0.2 | 6.0<br>V <sub>CC</sub> + 0.2 | V<br>V |

| V <sub>IL</sub> , Input Low Voltage<br>(Logic 0)<br>TTL<br>CMOS  | -0.3<br>-0.3                 | 0.8<br>0.2                   | V<br>V |

| T <sub>OPR</sub> , Operating Temp                                | 0                            | 70                           | °C     |

# DC Electrical Characteristics at recommended operating conditions

| Syn                               | lodn                                   | Parameter                       | Conditions                                                                                                             | Min                   | Max                   | Units |

|-----------------------------------|----------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-------|

| l <sub>LI</sub>                   |                                        | Input Leakage Current           | $V_{IN} = V_{SS}$ to $V_{CC}$                                                                                          | -2                    | 2                     | μΑ    |

| lro                               | I <sub>LO</sub> Output Leakage Current |                                 | $\overline{CS}$ or $\overline{OE} = V_{IH}$<br>$V_{I/O} = V_{SS}$ to $V_{CC}$                                          | -2                    | 2                     | μΑ    |

| ICC Active Quiescent Current, TTL |                                        | Active Quiescent Current, TTL   | All Inputs at TTL Levels $\overline{\text{CS}} = \text{V}_{\text{IL}} \text{TTL}, \text{I}_{\text{I/O}} = \text{0 mA}$ |                       | 25                    | mA    |

| Icc                               | Std.                                   |                                 |                                                                                                                        |                       | 2                     | mA    |

|                                   | L                                      | •                               | $\overline{\text{CS}} = V_{\text{IL}} \text{ CMOS}, I_{\text{I/O}} = 0 \text{ mA}$                                     |                       | 500                   | μΑ    |

| I <sub>CC1</sub>                  |                                        | Average Operating Current, TTL  | $T_{RC} = T_{RC}$ Min<br>$\overline{CS} = V_{IL}$ TTL, $I_{I/O} = 0$ mA<br>All Inputs at TTL Levels                    |                       | 50                    | mA    |

|                                   |                                        | Average Operating Current, CMOS | $T_{RC} = T_{RC}$ Min<br>$\overline{CS} = V_{IL}$ TTL, $I_{I/O} = 0$ mA<br>All Inputs at CMOS Levels                   |                       | 30                    | mA    |

| I <sub>SB</sub>                   | Std.                                   | Standby Power Supply Current    | CS = V <sub>IH</sub> TTL                                                                                               |                       | 4                     | mA    |

|                                   | L                                      |                                 | $I_{I/O} = 0 \text{ mA}$                                                                                               |                       | 2                     | mA    |

| I <sub>SB1</sub>                  | Std.                                   | Standby Power Supply Current    | CS = V <sub>IH</sub> CMOS                                                                                              |                       | 2                     | mA    |

|                                   | L                                      |                                 |                                                                                                                        |                       | 500                   | μΑ    |

| V <sub>OL</sub>                   |                                        | Output Low Voltage, TTL         | I <sub>OL</sub> = 8 mA                                                                                                 |                       | 0.4                   | ٧     |

|                                   |                                        | Output Low Voltage, CMOS        | I <sub>OL</sub> = ±10 μA                                                                                               | -0.2                  | 0.2                   | ٧     |

| V <sub>OH</sub>                   |                                        | Output High Voltage, TTL        | I <sub>OH</sub> = −4 mA                                                                                                | 2.4                   |                       | ٧     |

|                                   |                                        | Output High Voltage, CMOS       | I <sub>OH</sub> = ±10 μA                                                                                               | V <sub>CC</sub> - 0.2 | V <sub>CC</sub> + 0.2 | ٧     |

# Capacitance

| Symbol           | Parameter                | Conditions                     | Max | Units |

|------------------|--------------------------|--------------------------------|-----|-------|

| C <sub>IN</sub>  | Input Capacitance        | V <sub>IN</sub> = 0V (Note 5)  | 8   | pF    |

| C <sub>I/O</sub> | Input/Output Capacitance | V <sub>I/O</sub> = 0V (Note 5) | 10  | pF    |

# **Truth Table**

| Mode                      | WE | CS | ŌĒ | 1/0              | Current                            |

|---------------------------|----|----|----|------------------|------------------------------------|

| Not Selected (Power Down) | •  | Н  | •  | Hi-Z             | I <sub>SB</sub> , I <sub>SB1</sub> |

| Output Disabled           | Н  | L  | Н  | Hi-Z             | Icc, Icc1                          |

| Read                      | Н  | L  | L  | D <sub>OUT</sub> | Icc, Icc1                          |

| Write                     | L  | L  |    | DiN              | lcc, lcc1                          |

<sup>• =</sup> Don't care (H or L), H = Logic HIGH Level, L = Logic LOW Level

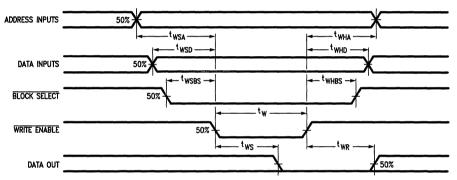

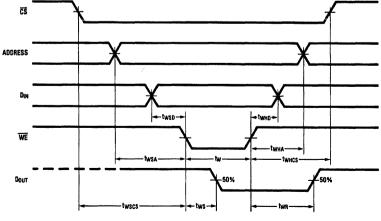

taw

twp

twR

twhz

tow

t<sub>DH</sub>

tonz

tow

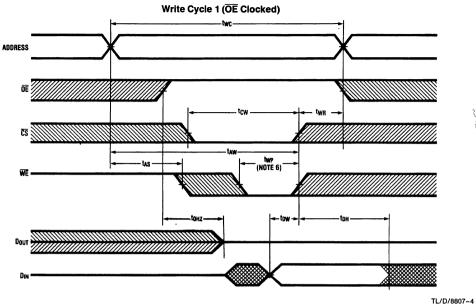

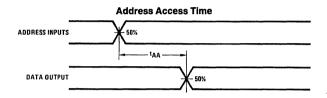

#### AC Electrical Characteristics\* (Note 1) NMC61256N/NMC61256N-L **Symbol** Parameter -70 -100 -120 Units Min Max Min Max Min Max **READ CYCLE** (Note 4) Read Cycle Time 70 100 120 ns Address Access Time 70 100 120 $t_{AA}$ ns Chip Selection (CS) to Output Valid 70 100 120 tco ns Output Enable (OE) to Output Valid 30 50 60 ns toe Chip Selection (CS) to Output Active (Note 11) tı 7 15 15 15 ns Output Enable (OE) to Output Active (Note 11) 5 5 5 tolz ns Chip Deselection (CS) to Output in Hi-Z (Notes 2 and 3) 0 0 tHZ 0 30 35 40 Output Disable (OE) to Output in Hi-Z (Notes 2 and 3) 0 25 0 35 0 40 t<sub>OHZ</sub> ns Output Hold from Address Change 5 10 10 ns **tOHA** WRITE CYCLE Write Cycle Time 70 100 120 twc ns Chip Selection (CS) to End of Write (Note 10) 60 80 85 ns tcw Address Setup Time (Note 7) 0 0 0 tAS ns Address Valid to End of Write 60 80 85 ns

40

0

0

30

0

0

0

25

25

60

0

0

35

0

0

0

35

35

70

0

0

40

0

0

0

40

40

ns

ns

ns

ns

ns

ns

ns

Note 1: AC test conditions  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{CC} = 5V \pm 10\%$ .

Output Active from End of Write

Write Pulse Width (Note 6)

Write Recovery Time from CS (Note 8)

Output Disable (OE) to Output in Hi-Z

Data Valid to Write Time Overlap

Data Hold from End of Write

Beginning of Write to Output in Hi-Z (Note 9)

Note 2: tHZ and tOHZ are defined as the time at which the outputs achieve the open circuit condition and are determined as:

High to TRI-STATE, measured VOH (DC) - 0.10V

Low to TRI-STATE, measured VOL (DC) + 0.10V

Note 3: At any given temperature and voltage condition, t<sub>HZ MAX</sub> is less than t<sub>LZ MIN</sub>, both for a given device and from device to device (guaranteed not tested). Note 4: WE is high for read cycle.

Note 5:  $T_A = 25$ °C, f = 1.0 MHz. This parameter is sampled and not 100% tested.

Note 6: A write occurs during the overlap ( $t_{WP}$ ) of a low  $\overline{CS}$  and a low  $\overline{WE}$ .

Note 7: t<sub>AS</sub> is measured from the address changes to the beginning of the write.

Note 8: two is measured from the earliest of CS or WE going high to the end of the write cycle.

Note 9: If CS is low during this period, I/O pins are in the output state. At this time, the data input signals of opposite phase to the outputs must not be applied. Note 10: If the CS low transition occurs simultaneously with the WE low transition or after the WE transition, the outputs will remain in a Hi-Z state.

Note 11: Output active level is defined as steady state TRI-STATE level ±0.1V.

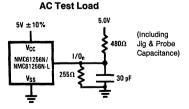

## **AC Test Conditions**

$V_{IH} = 3.0V, V_{IL} = 0.0V$ Input pulse levels: Input rise and fall times: All input timing reference levels: 1.5V Output timing reference levels:  $V_{OH} = 2.0V, V_{OI} = 0.8V$

TL/D/8807-3

<sup>\*</sup>Applies to Standard and L Versions.

TL/D/8807-5

# Timing Waveforms (Continued)

TL/D/8807-6

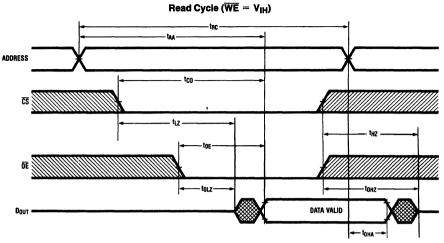

# Low V<sub>CC</sub> Data Retention (L Version)

| Symbol          | Parameter                            | Parameter Conditions                                           |                 | Max | Units |

|-----------------|--------------------------------------|----------------------------------------------------------------|-----------------|-----|-------|

| V <sub>DR</sub> | V <sub>CC</sub> for Data Retention   | CS > VIH, CMOS                                                 | 2.0             | 5.5 | ٧     |

| ICCDR           | Data Retention Current               | V <sub>CC</sub> = 2V<br><del>CS</del> > V <sub>IH</sub> , CMOS |                 | 200 | μΑ    |

| tcor            | Chip Deselect to Data Retention Time | See Retention Waveform                                         | 0               |     | ns    |

| t <sub>R</sub>  | Operation Recovery Time              | See Retention Waveform                                         | t <sub>RC</sub> |     | ns    |

# Low V<sub>CC</sub> Data Retention Waveform

TL/D/8807-7

Section 2

TTL RAMs

# **Section 2 Contents**

|                                          |                                             | PAGE<br>NUMBER |

|------------------------------------------|---------------------------------------------|----------------|

| TTL RAM Selection Guide                  |                                             | 2-3            |

| DEVICE                                   | DESCRIPTION                                 |                |

| DM54S189, DM74S189                       | 64-Bit (16 x 4) TRI-STATE RAM               | 2-4            |

| DM74S289                                 | 64-Bit Open-Collector RAM                   | 2-4            |

| DM54S189A, DM74S189A                     | High Speed 64-Bit TRI-STATE RAM             | 2-4            |

| DM85S06                                  | Open Collector                              | 2-12           |

| DM75S07, DM85S07                         | TRI-STATE                                   | 2-12           |

| DM75S07A, DM85S07A                       | High Speed TRI-STATE Non-Inverting, 64-Bit  |                |

|                                          | (16 x 4) RAMs                               | 2-12           |

| DM75S68A, DM85S68,<br>DM75S68A, DM85S68A | 16 x 4 Edge Triggered Registers             | 2-20           |

| IDM29705, 29705A                         | 16 Word by 4-Bit Two Port RAM/Register File | 2-24           |

# **TTL RAM Selection Guide**

| Size<br>(Bits) | Organization     | Outputs* | Pins<br>(DIP) | P/N       | TAA | Icc | Temp            |

|----------------|------------------|----------|---------------|-----------|-----|-----|-----------------|

| INVERTI        | NG RAMS          |          |               |           |     |     |                 |

| 64             | 16 x 4           | TS       | 16            | DM54S189  | 50  | 110 | -55°C to +125°C |

|                | 16 x 4           | TS       | 16            | DM74S189  | 35  | 110 | 0°C to +70°C    |

|                | 16 x 4           | TS       | 16            | DM54S189A | 30  | 100 | -55°C to +125°C |

|                | 16 x 4           | TS       | 16            | DM74S189A | 25  | 100 | 0°C to +70°C    |

|                | 16 x 4           | ОС       | 16            | DM74S289  | 35  | 110 | 0°C to +70°C    |

| NON-INV        | ERTING RAMS      |          |               |           |     |     |                 |

| 64             | 16 x 4           | TS       | 16            | DM75S07   | 50  | 100 | -55°C to +125°C |

|                | 16 x 4           | TS       | 16            | DM85S07   | 35  | 100 | 0°C to +70°C    |

|                | 16 x 4           | TS       | 16            | DM75S07A  | 30  | 100 | -55°C to +125°C |

|                | 16 x 4           | TS       | 16            | DM85S07A  | 25  | 100 | 0°C to +70°C    |

|                | 16 x 4           | ос       | 16            | DM85S06   | 35  | 100 | 0°C to +70°C    |

| EDGE T         | RIGGERED REGISTE | RS       |               |           |     |     |                 |

| 64             | 16 x 4           | TS       | 18            | DM75S68   | 55  | 100 | -55°C to +125°C |

|                | 16 x 4           | TS       | 18            | DM85S68   | 40  | 100 | 0°C to +70°C    |

|                | 16 x 4           | TS       | 18            | DM75S68A  | 45  | 100 | -55°C to +125°C |

|                | 16 x 4           | TS       | 18            | DM85S68A  | 24  | 100 | 0°C to +70°C    |

<sup>\*</sup>TS = TRI-STATE® outputs

OC = Open Collector outputs

April 1987

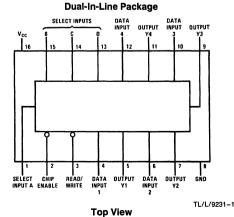

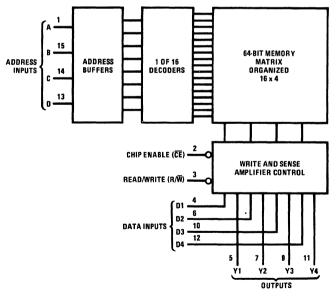

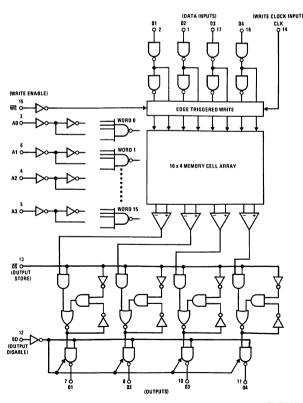

# DM54S189/DM74S189 64-Bit (16 x 4) TRI-STATE® RAM DM74S289 64-Bit Open-Collector RAM DM54S189A/DM74S189A High Speed 64-Bit TRI-STATE RAM

#### **General Description**

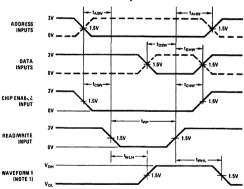

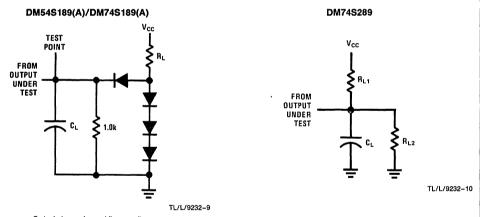

These 64-bit active-element memories are monolithic Schottky-clamped transistor-transistor logic (TTL) arrays organized as 16 words of 4 bits each. They are fully decoded and feature a chip-enable input to simplify decoding required to achieve the desired system organization. The memories feature PNP input transistors that reduce the low level input current requirement to a maximum of -0.25~mA, only one-eighth that of a DM74S standard load factor. The chip-enable circuitry is implemented with minimal delay times to compensate for added system decoding.

The TRI-STATE output combines the convenience of an open-collector with the speed of a totem-pole output; it can be bus-connected to other similar outputs; yet it retains the fast rise time characteristics of the TTL totem-pole output. Systems utilizing data bus lines with a defined pull-up impedance can employ the open-collector DM74S289.

Write Cycle: The complement of the information at the data input is written into the selected location when both the chip-enable input and the read/write input are low. While the read/write input is low, the outputs are in the high-impedance state. When a number of the DM74S189 outputs are bus connected, this high-impedance state will neither load nor drive the bus line, but it will allow the bus line to be driven by another active output or a passive pull-up if desired

Read Cycle: The stored information (complement of information applied at the data inputs during the write cycle) is

available at the outputs when the read/write input is high and the chip-enable is low. When the chip-enable is high, the outputs will be in the high-impedance state.

The fast access time of the DM74S189A makes it particularly attractive for implementing high-performance memory functions requiring access times less than 25 ns. The high capacitive drive capability of the outputs permits expansion without additional output buffering. The unique functional capability of the DM74S189A outputs being at a high-impedance during writing, combined with the data inputs being inhibited during reading, means that both data inputs and outputs can be connected to the data lines of a bus-organized system without the need for interface circuits.

#### **Features**

- Schottky-clamped for high speed applications (S189A)

Access from chip-enable input

17 ns max

Access from address inputs

25 ns max

- TRI-STATE outputs drive bus-organized systems and/or high capacitive loads (S189, S189A)

- DM74S289 are functionally equivalent and have opencollector outputs

- DM54SXXX is guaranteed for operation over the full military temperature range of -55°C to +125°C

- Compatible with most TTL circuits

- Chip-enable input simplifies system decoding

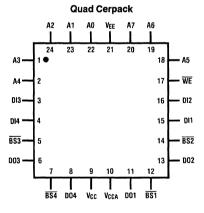

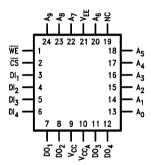

# **Connection Diagram**

DM74S189J, DM74S189AJ, DM74S289J, DM74S189N, DM74S189AN or DM74S289N See NS Package Number J16A or N16E

Order Number DM54S189J, DM54S189AJ,

## **Truth Table**

|                                     | lnp             | uts            |                |

|-------------------------------------|-----------------|----------------|----------------|

| Function                            | Chip-<br>Enable | Read/<br>Write | Output         |

| Write (Store<br>Complement of Data) | L               | L              | High-Impedance |

| Read                                | L               | Н              | Stored Data    |

| Inhibit                             | Н               | Х              | High-Impedance |

H = High Level, L = Low Level, X = Don't Care

| <b>Absolute Maximum Rat</b>                                                                                 | ings (Note 1)     | Operating Condit                              | ions              |                   |            |

|-------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------|-------------------|-------------------|------------|

| If Military/Aerospace specified decontact the National Semiconduc<br>Distributors for availability and spec | tor Sales Office/ | Supply Voltage (V <sub>CC</sub> )<br>DM54S189 | <b>Min</b><br>4.5 | <b>Max</b><br>5.5 | Units<br>V |

| Supply Voltage, V <sub>CC</sub>                                                                             | 7.0V              | DM74S189, DM74S289                            | 4.75              | 5.25              | V          |

| Input Voltage                                                                                               | 5.5V              | Temperature (T <sub>A</sub> )                 |                   |                   |            |

| Output Voltage                                                                                              | 5.5V              | DM54S189                                      | -55               | + 125             | °C         |

| Storage Temperature Range                                                                                   | -65°C to +150°C   | DM74S189, DM74S289                            | 0                 | +70               | °C         |

| Lead Temperature (Soldering, 10 sec.)                                                                       | +300°C            |                                               |                   |                   |            |

# DM54S189, DM74S189, DM74S289 Electrical Characteristics over recommended operating free-air temperature range unless otherwise noted (Notes 2 and 3)

| Symbol          | Parameter                                               | Coi                                                                    | nditions                             | Min | Тур | Max  | Units |

|-----------------|---------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------|-----|-----|------|-------|