# INS4001 ROM & I/O port, INS4002-1 RAM, INS4003 shift register INS4004 CPU, four-bit integrated processing system INS4008/INS4009 in a four-bit integrated processing system (FIPS)

#### general description

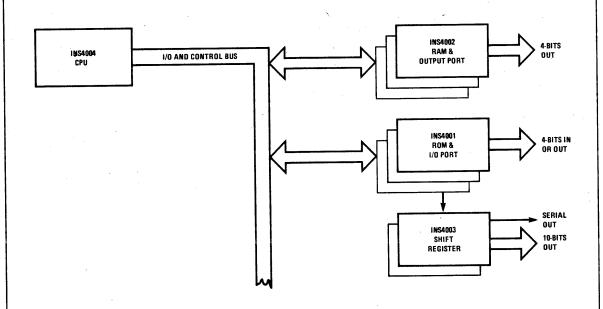

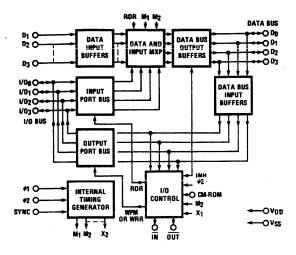

FIPS is a four-bit, general-purpose microprocessor chip set designed for application in intelligent terminals, traffic signals, measuring instruments, numeric control and process control systems. It interfaces easily with switches, keyboards, displays, and other peripheral devices; and it provides a compact and powerful replacement for random logic in many control systems.

INS4002, INS4003, and INS4004 are standard building blocks for system control, I/O, and temporary data storage. The INS4001 ROM is mask-programmed to customer specifications and holds the application program for the FIPS controller. The FIPS microprocessor can interface directly with up to 4K x 8 of ROM, 1280 x 4 RAM, and 128 I/O lines. A small amount of additional logic will interface FIPS with up to 48 RAM or ROM packages in any combination, and 192 I/O lines. The minimum system configuration consists of one CPU and one ROM.

The National Semiconductor FIPS microprocessor is fabricated from PMOS, Silicon-gate technology for high

reliability and producibility. Its powerful instruction set includes binary and decimal arithmetic, conditional branch, and indirect addressing instructions.

#### features

- General purpose programmable microprocessor

- 45 instructions, including:

Conditional Branch Indirect Fetch Binary/Decimal Arithmetic

- Easy memory expansion to 32K bits of ROM and 4K bits of RAM

- 16-pin dual in-line package allows compact designs

- Parallel operation for higher performance

- Simple memory and I/O interface for low system cost

- Second source for the MCS-4\* microprocessor chips 4001, 4002-1, 4002-2, 4003, and 4004

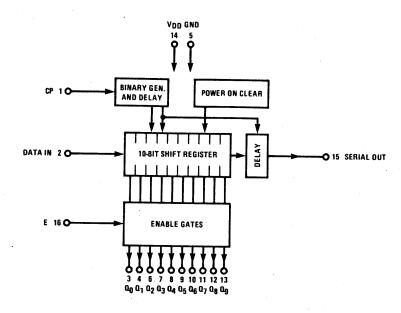

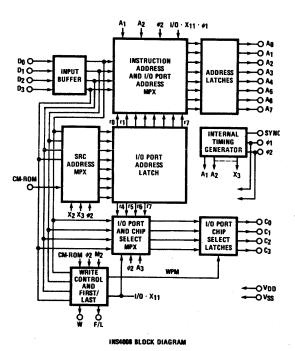

# block diagram-FIPS microprocessor chip set

\*MCS-4 is a registered trademark of INTEL Corp.

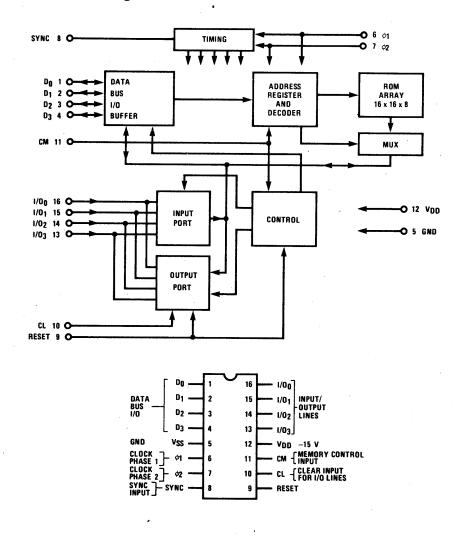

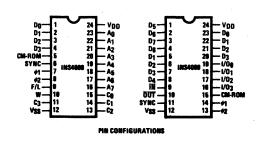

# INS4001 256×8 bit mask-programmed ROM and 4-bit I/O port

The INS4001 is a 2K metal-mask ROM which interfaces directly to the INS4004 CPU and is used to store the control program for the FIPS system. Its address decoding capability is also used to control the selection of a built-in 4-bit I/O port. Data is transferred between the ROM and the CPU via a time-multiplexed, 4-bit Data Bus.

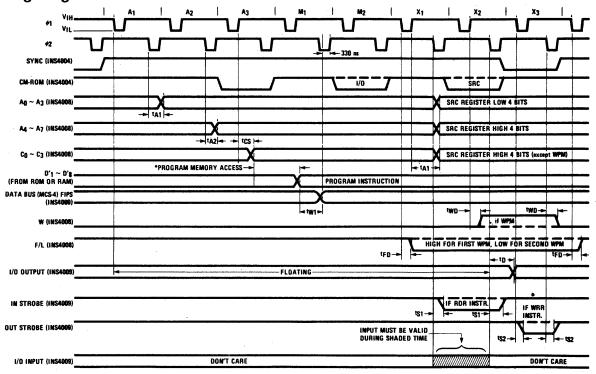

#### **ROM OPERATION**

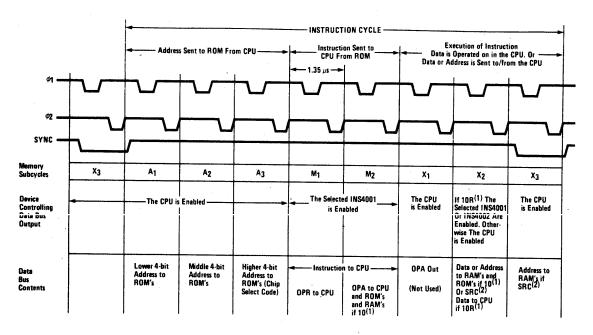

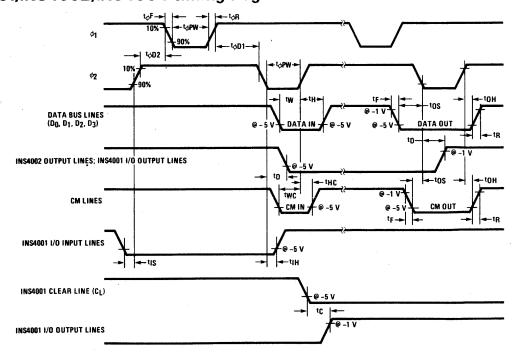

During ROM access, 12-bit addresses and 8-bit data words are multiplexed onto the 4-bit Data Bus connecting the INS4001 with the CPU. (See FIPS Basic Instruction Cycle Timing Diagram). During the three address periods following a SYNC command from the CPU, addresses which select one of 256 words per ROM, and one of 16 ROM chips, are passed to the INS4001. During the next two time periods, 8 bits of instruction are transferred from the ROM to the CPU. A command

signal (CM) is provided from the CPU, and is used to select a ROM bank (group of 16 ROMs).

#### I/O PORT OPERATION

In this mode of operation, the chip routes data directly between the Data Bus and a 4-bit I/O port which is part of the chip. Each chip has the capability to identify itself for I/O operations, and to recognize and execute I/O commands from the CPU. An external signal (CL) may be applied to asynchronously clear the output register during normal operation.

All internal flip-flops will be reset when the RESET line goes low (negative voltage).

Each I/O pin can be selected as an input or output line by metal mask option. Inputs and outputs may be selected as direct or inverted. An on-chip resistor tying the inputs to either VDD or VSS is also optional.

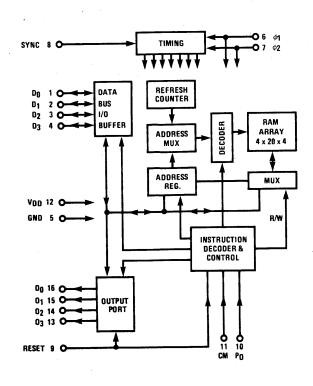

# INS4002 320-bit RAM and 4-bit output port

The INS4002 combines the functions of 4-bit parallel read/write data storage and 4-bit output/control lines which facilitate data transfer between the CPU and a peripheral device.

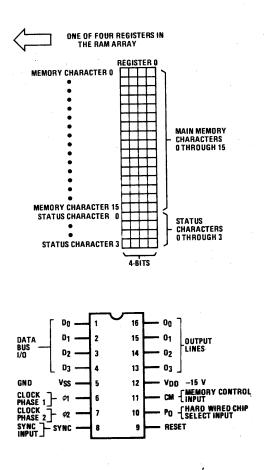

#### **RAM OPERATION**

RAM storage in the INS4002 is organized as 4 registers of 20 4-bit characters each (16 main memory and 4 status characters). Main memory locations are selected during an SRC instruction, while status locations are selected during the actual I/O or RAM instruction.

When doing a RAM data transfer, the CPU first executes an SRC instruction, which sends out the contents of the designated index register pair (X<sub>2</sub> X<sub>3</sub>) as an address to the RAM. These bits are decoded as shown in the diagram below.

| X <sub>2</sub>                                              | Х3                                                          |  |  |  |  |

|-------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|

| D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> | D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> |  |  |  |  |

| Chip # (0 - 3) Register # (0 - 3)                           | Main Memory Character #<br>(0 - 15)                         |  |  |  |  |

Selection of different RAM chips is based upon a metalmask address option (INS4002-1 or INS4002-2) and an external pin, PO, which may be wired to either VDD or VSS. Decoding is as shown below:

| CHIP# | OPTION    | PO ·     | D3 | D <sub>2</sub> |

|-------|-----------|----------|----|----------------|

| 0     | INS4002-1 | GND      | 0  | 0              |

| 1     | INS4002-1 | $V_{DD}$ | 0  | 1              |

| 2     | INS4002-2 | GND      | 1  | 0              |

| . 3   | INS4002-2 | $V_{DD}$ | 1  | 1              |

Timing is based upon two externally-supplied clock signals, and a SYNC signal provided by the CPU. Internal refresh circuitry maintains memory data in the cells of the chip.

#### **OUTPUT PORT OPERATION**

The INS4002 has the capability to transfer data directly from the system Data Bus through a 4-bit Output Port to an external peripheral device. When the external RESET line goes low, the memory and all static flipflops are cleared. To completely clear memory, the RESET line must be held low for at least 32 memory cycles (32 x 8 clock periods).

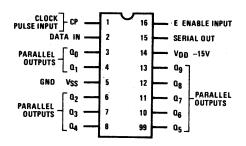

# INS4003 10-bit serial-in/parallel-out shift register

The INS4003 10-bit static shift register is used to increase the number of output lines available from the microprocessor system to interface with peripheral devices.

Data is loaded serially into the Shift Register, and is then available in parallel on 10 output lines which can be accessed through enable logic. When the ENABLE line (E) is low, shift register contents are available at pins  $Q_0$  -  $Q_0$ . When E is high, these pins are at VSS.

A Serial-Data-Out line is also available from the Shift Register, and it allows an indefinite number of Shift Registers to be cascaded together to provide any required number of output lines, in multiples of 10. This serial output line is not affected by the E line.

Data is clocked through the Shift Register by a signal on the CP line. An internal initialization circuit clears the shift register between the application of the supply voltage and the first CP signal.

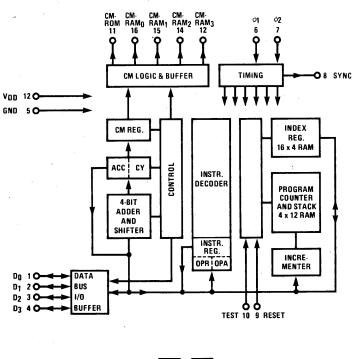

#### INS4004 4-bit central processing unit (CPU)

The INS4004 is the Central Processing Unit of the FIPS microprocessor system. It includes the necessary control logic to request program instructions from main memory (INS4001 ROMs), decode the instructions and execute them. It is designed to interface directly with the INS4001, INS4002, and INS4003 chips. Communication with the outside world is accomplished through I/O ports included in these chips.

The CPU itself consists of a 4-bit ALU, 16 4-bit index registers, a 12-bit program counter (PC), three levels of PC stack, an instruction register, and miscellaneous control logic. Communication with other chips is accomplished over a time-multiplexed 4-bit Data Bus.

In operation, the CPU sends a SYNC signal to the ROMs and RAMs in the system, followed by 12 bits of address data (during the next three clock cycles), to select the next instruction to be executed. The selected ROM

sends back 8 bits of instruction during the following two clock times, and this information is stored in the OPR and OPA registers within the CPU. The CPU executes the instruction during the next three clock times.

CPU instructions are drawn from the INS4001 ROMs, arranged in banks of 16 ROMs each. Bank switching is done under program control, with the CPU selectively enabling one bank of ROMs to fetch an instruction.

The CPU provides a Conditional Jump instruction which is used to test an external input pin. A RESET signal may be supplied to the CPU to clear all registers and flip-flops. After RESET, the program will start from step "0," executing program instructions.

The INS4004 CPU provides a total of 45 program instructions, which are specified in the table on the following page.

#### system timing

FIPS Basic Instruction Cycle

#### instruction set

[Those instructions preceded by an asterisk (\*) are 2 word instructions that occupy 2 successive locations in ROM] **MACHINE INSTRUCTIONS**

| MNEMONIC | OPR                                                                    | OPA                                                                                                                        | DESCRIPTION OF OPERATION                                                                                                                                                                                                                                                                                                                                                                     |

|----------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOP      | 0 0 0 0                                                                | 0 0 0 0                                                                                                                    | No operation.                                                                                                                                                                                                                                                                                                                                                                                |

| *JCN     | 0 0 0 1<br>A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> | C <sub>1</sub> C <sub>2</sub> C <sub>3</sub> C <sub>4</sub><br>A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> | Jump to ROM address A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> A <sub>3</sub> A <sub>4</sub> A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> A <sub>1</sub> (within the same ROM that contains this JCN instruction) if condition C <sub>1</sub> C <sub>2</sub> C <sub>3</sub> C <sub>4</sub> <sup>(1)</sup> is true, otherwise skip (go to the next Instruction in sequence). |

| *FIM     | 0 0 1 0<br>D <sub>2</sub> D <sub>2</sub> D <sub>2</sub> D <sub>2</sub> | R R R 0<br>D <sub>1</sub> D <sub>1</sub> D <sub>1</sub> D <sub>1</sub>                                                     | Fetch immediate (direct) from ROM Data D <sub>2</sub> , D <sub>1</sub> to index register pair location RRR. (2)                                                                                                                                                                                                                                                                              |

| SRC      | 0 0 1 0                                                                | R R R 1                                                                                                                    | Send register control. Send the address (contents of index register pair RRR) to ROM and RAM at X <sub>2</sub> and X <sub>3</sub> time in the Instruction Cycle.                                                                                                                                                                                                                             |

| FIN      | 0 0 1 1                                                                | R R R O                                                                                                                    | Fetch indirect from ROM. Send contents of index register pair location 0 out as an address. Data fetched is placed into register pair location RRR.                                                                                                                                                                                                                                          |

| JIN      | 0 0 1 1                                                                | RRR1                                                                                                                       | Jump indirect. Send contents of register pair RRR out as an address at $A_1$ and $A_2$ time in the Instruction Cycle.                                                                                                                                                                                                                                                                        |

| *JUN     | 0 1 0 0<br>A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> | A3 A3 A3 A3<br>A1 A1 A1 A1                                                                                                 | Jump unconditional to ROM address A <sub>3</sub> , A <sub>2</sub> , A <sub>1</sub> .                                                                                                                                                                                                                                                                                                         |

| *JMS     | 0 1 0 1<br>A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> | A <sub>3</sub> A <sub>3</sub> A <sub>3</sub> A <sub>3</sub><br>A A A A                                                     | Jump to subroutine ROM address A <sub>3</sub> , A <sub>2</sub> , A <sub>1</sub> , save old address. (Up 1 level in stack.)                                                                                                                                                                                                                                                                   |

| INC      | 0 1 1 0                                                                | RRRR                                                                                                                       | Increment contents of register RRRR.(3)                                                                                                                                                                                                                                                                                                                                                      |

| *ISZ     | 0 1 1 1<br>A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> A <sub>2</sub> | R R R R<br>A <sub>1</sub> A <sub>1</sub> A <sub>1</sub>                                                                    | Increment contents of register RRRR. Go to ROM address $A_2$ , $A_1$ (within the same ROM that contains this ISZ instruction) if result $\neq 0$ , otherwise skip (go to the next instruction in sequence).                                                                                                                                                                                  |

| ADD      | 1000                                                                   | RRRR                                                                                                                       | Add contents of register RRRR to accumulator with carry.                                                                                                                                                                                                                                                                                                                                     |

| SUB      | 1 0 0 1                                                                | RRRR                                                                                                                       | Subtract contents of register RRRR to accumulator with borrow.                                                                                                                                                                                                                                                                                                                               |

| LD       | 1 0 1 0                                                                | RRRR                                                                                                                       | Load contents of register RRRR to accumulator.                                                                                                                                                                                                                                                                                                                                               |

| хсн      | 1 0 1 1                                                                | RRRR                                                                                                                       | Exchange contents of index register RRRR and accumulator.                                                                                                                                                                                                                                                                                                                                    |

| BBL      | 1 1 0 0                                                                | DDDD                                                                                                                       | Branch back (down 1 level in stack) and load data DDDD to accumulator.                                                                                                                                                                                                                                                                                                                       |

| LDM      | 1 1 0 1                                                                | DDDD                                                                                                                       | Load data DDDD to accumulator.                                                                                                                                                                                                                                                                                                                                                               |

# input/output and RAM instructions

[The RAM's and ROM's operated on in the I/O and RAM instructions have been previously selected by the last SRC instruction executed.]

| OPR     | ОРА                                                                                                                                   | DESCRIPTION OF OPERATION                                                                           |

|---------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 1 1 1 0 |                                                                                                                                       | Write the contents of the accumulator into the previously selected RAM main memory character.      |

| 1 1 1 0 | 0 0 0 1                                                                                                                               | Write the contents of the accumulator into the previously selected RAM output port. (Output Lines) |

| 1 1 1 0 | 0 0 1 0                                                                                                                               | Write the contents of the accumulator into the previously selected ROM output port. (I/O Lines)    |

| 1 1 1 0 | 0 1 0 0                                                                                                                               | Write the contents of the accumulator into the previously selected RAM status character 0.         |

| 1 1 1 0 | 0 1 0 1                                                                                                                               | Write the contents of the accumulator into the previously selected RAM status character 1.         |

| 1 1 1 0 | 0 1 1 0                                                                                                                               | Write the contents of the accumulator into the previously selected RAM status character 2.         |

| 1 1 1 0 | 0 1 1 1                                                                                                                               | Write the contents of the accumulator into the previously selected RAM status character 3.         |

| 1 1 1 0 | 1 0 0 0                                                                                                                               | Subtract the previously selected RAM main memory character from accumulator with borrow.           |

| 1 1 1 0 | 1 0 0 1                                                                                                                               | Read the previously selected RAM main memory character into the accumulator.                       |

| 1 1 1 0 | 1 0 1 0                                                                                                                               | Read the contents of the previously selected ROM input port into the accumulator. (I/O Lines)      |

| 1 1 1 0 | 1 0 1 1                                                                                                                               | Add the previously selected RAM main memory character to accumulator with carry.                   |

| 1 1 1 0 | 1 1 0 0                                                                                                                               | Read the previously selected RAM status character 0 into accumulator.                              |

| 1 1 1 0 | 1 1 0 1                                                                                                                               | Read the previously selected RAM status character 1 into accumulator.                              |

| 1 1 1 0 | 1 1 1 0                                                                                                                               | Read the previously selected RAM status character 2 into accumulator.                              |

| 1 1 1 0 | 1 1 1 1                                                                                                                               | Read the previously selected RAM status character 3 into accumulator.                              |

|         | 1 1 1 0  1 1 1 0  1 1 1 0  1 1 1 0  1 1 1 0  1 1 1 0  1 1 1 0  1 1 1 0  1 1 1 0  1 1 1 0  1 1 1 0  1 1 1 0  1 1 1 0  1 1 1 0  1 1 1 0 | 1 1 1 0 0 0 0 0 0  1 1 1 0 0 0 0 0 1  1 1 1 0 0 0 0                                                |

# accumulator group instructions

| CLB | 1 1 1 1 | 0 0 0 0 | Clear both. (Accumulator and carry)                                                                      |

|-----|---------|---------|----------------------------------------------------------------------------------------------------------|

|     | 1 1 1 1 | 0 0 0 1 | Clear carry.                                                                                             |

| CLC | ' ' '   |         |                                                                                                          |

| IAC | 1 1 1 1 | 0 0 1 0 | Increment accumulator.                                                                                   |

| CMC | 1 1 1 1 | 0 0 1 1 | Complement carry.                                                                                        |

| CMA | 1 1 1 1 | 0 1 0 0 | Complement accumulator.                                                                                  |

| RAL | 1 1 1 1 | 0 1 0 1 | Rotate left. (Accumulator and carry)                                                                     |

| RAR | 1 1 1 1 | 0 1 1 0 | Rotate right. (Accumulator and carry)                                                                    |

| TCC | 1 1 1 1 | 0 1 1 1 | Transmit carry to accumulator and clear carry.                                                           |

| DAC | 1 1 1 1 | 1 0 0 0 | Decrement accumulator.                                                                                   |

| TCS | 1 1 1 1 | 1 0 0 1 | Transfer carry subtract and clear carry.                                                                 |

| STC | 1 1 1 1 | 1 0 1 0 | Set carry.                                                                                               |

| DAA | 1 1 1 1 | 1 0 1 1 | Decimal adjust accumulator.                                                                              |

| КВР | 1 1 1 1 | 1 1 0 0 | Keyboard process. Converts the contents of the accumulator from a one out of four code to a binary code. |

| DCL | 1 1 1 1 | 1 1 0 1 | Designate command line.                                                                                  |

NOTES: (1) The condition code is assigned as follows:

$C_1 = 1$  Invert jump condition.

C<sub>2</sub> = 1 Jump if accumulator is zero

C<sub>4</sub> = 1 Jump if test signal is a 0

C<sub>1</sub> = 0 Not invert jump condition

C<sub>3</sub> = 1 Jump if carry/link is a 1

<sup>(2)</sup> RRR is the address of 1 of 8 index register pairs in the CPU.

<sup>(3)</sup> RRRR is the address of 1 of 16 index registers in the CPU.

<sup>(4)</sup> Each RAM chip has 4 registers, each with twenty 4-bit characters subdivided into 16 main memory characters and 4 status characters. Chip number, RAM register and main memory character are addressed by an SRC instruction. For the selected chip and register, however, status character locations are selected by the instruction code (OPA).

#### absolute maximum ratings

Ambient Temperature Under Bias Storage Temperature Input Voltages and Supply Voltage with Respect to V<sub>SS</sub> Power Dissipation 0°C to +70°C -55°C to +150°C

> +0.5 to -20 V 1.0 W

\*Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

#### d.c. and operating characteristics

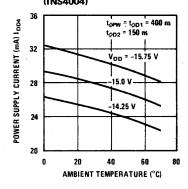

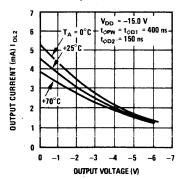

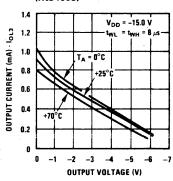

$T_A = 0^{\circ}\text{C}$  to +70°C;  $V_{DD} = -15 \text{ V} \pm 5\%$ ,  $V_{SS} = \text{GND}$ ,  $t_{\phi PW} = t_{\phi D1} = 400 \text{ ns}$ ,  $t_{\phi D2} = 150 \text{ ns}$ , unless otherwise specified. Logic "0" is defined as the more positive voltage ( $V_{IH}, V_{OH}$ ), Logic "1" is defined as the more negative voltage ( $V_{IL}, V_{OL}$ ).

| 00000          | 0)/0              |                                                  |                      | LIMIT                | ·                     |       |                                                                                                                           |

|----------------|-------------------|--------------------------------------------------|----------------------|----------------------|-----------------------|-------|---------------------------------------------------------------------------------------------------------------------------|

| PRODUCT        | SYMBOL            | PARAMETER                                        | MIN.                 | TYP.(1)              | MAX.                  | UNIT  | TEST CONDITIONS                                                                                                           |

| SUPPLY CURREN  | Τ                 |                                                  |                      |                      |                       |       |                                                                                                                           |

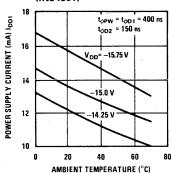

| INS4001        | I <sub>DD1</sub>  | Average Supply Current                           |                      | 15                   | 30                    | mA    | T <sub>A</sub> = 25°C                                                                                                     |

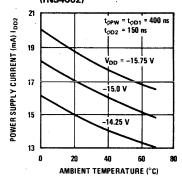

| INS4002        | I <sub>DD2</sub>  | Average Supply Current                           |                      | 17                   | 33                    | mA    | TA = 25°C                                                                                                                 |

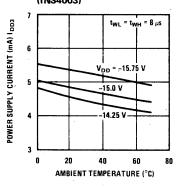

| INS4003        | I <sub>DD3</sub>  | Average Supply Current                           |                      | 5.0                  | 8.5                   | mA    |                                                                                                                           |

| INS4004        | IDD4              | Average Supply Current                           |                      | 30                   | 40                    | mÁ I  | tWL = tWH = 8 μsec; T <sub>A</sub> = 25°C                                                                                 |

| INPUT CHARACTE |                   | INPUTS EXCEPT I/O INPUT                          | PINS                 | 1                    | 1 .0                  | 1111/ | 1A - 29 C                                                                                                                 |

| INS4001/2/4    |                   |                                                  | 1                    | I                    | 1                     |       |                                                                                                                           |

| INS4001/2/4    | LI                | Input Leakage Current                            |                      | Ī                    | 10                    | μΑ    | V <sub>IL</sub> = V <sub>DD</sub>                                                                                         |

| 11434001/2/4   | ViH               | Input High Voltage<br>(Except Clocks)            | V <sub>SS</sub> -1.5 |                      | V <sub>SS</sub> +0.3  | V     |                                                                                                                           |

| INS4001/2/4    | VIL               | Input Low Voltage<br>(Except Clocks)             | V <sub>DD</sub>      |                      | V <sub>SS</sub> -5.5  | v     |                                                                                                                           |

| INS4001/2/4    | VILC              | Clock Input Low Voltage                          | VDD                  |                      | V <sub>SS</sub> -13.4 | v     |                                                                                                                           |

| INS4001/2/4    | VIHC              | Clock Input High Voltage                         | V <sub>SS</sub> -1.5 |                      | V <sub>SS</sub> =13.4 | v     |                                                                                                                           |

| DUTPUT CHARAC  | TERISTICS (A      | LL OUTPUTS EXCEPT I/O O                          |                      |                      | 1 33 5.5              | للسلط |                                                                                                                           |

| INS4001/2/4    | <sup>I</sup> LO   | Data Bus Output Leakage                          | 1                    | - <i>,</i>           | 10                    |       |                                                                                                                           |

|                |                   | Current                                          |                      |                      | 10                    | μΑ    | $V_{OUT} = -12V$ , Chip disabled                                                                                          |

| INS4001/2/4    | Voн               | Output High Voltage                              |                      | VSS                  | V <sub>SS</sub> -0.5  | v     | Driving 4000 Series loads only                                                                                            |

| INS4001/2/4    | IOL1              | Data Lines Sinking<br>Current "1" Level          | 10                   | 18                   | 1 33 0.0              | mA    | VOUT = 0V                                                                                                                 |

| INS4004        | IOL5              | CM-ROM Sinking Current "1" Level                 | 6.5                  | 12                   |                       | mA    | V <sub>OUT</sub> = 0V                                                                                                     |

| INS4004        | lOL6              | CM-RAM Lines Sinking<br>Current "1" Level        | 2.5                  | 4                    |                       | mA    | V <sub>OUT</sub> = 0V                                                                                                     |

| INS4001/2/4    | V <sub>OL1</sub>  | Data Lines, CM Lines,<br>Sync Output Low Voltage | V <sub>SS</sub> -12  | V <sub>SS</sub> -10  | V <sub>SS</sub> -6.5  | v     | I <sub>OL1</sub> = 500 μA                                                                                                 |

| INS4001/2/4    | R <sub>OH1</sub>  | Output Resistance Data<br>Data Lines "0" Level   |                      | 150                  | 250                   | Ω     | V <sub>OUT</sub> = 0.5 V                                                                                                  |

| INS4004        | R <sub>OH5</sub>  | CM-ROM Output<br>Resistance "0" Level            |                      | 320                  | 600                   | Ω     | V <sub>OUT</sub> = -0.5 V                                                                                                 |

| INS4004        | R <sub>OH6</sub>  | CM-RAM Lines Output<br>Resistance "0" Level      |                      | 1.1                  | 1.8                   | ΚΩ    | V <sub>OUT</sub> = -0.5 V                                                                                                 |

| O INPUT CHARAC | CTERISTICS        | 789                                              | L L                  |                      |                       |       |                                                                                                                           |

| INS4001/3      | ILI               | Input Leakage Current                            | П                    |                      | 40                    |       |                                                                                                                           |

| INS4001/3      | VIH               |                                                  | ا ا                  |                      | 10                    | μΑ    | V <sub>IL</sub> = V <sub>DD</sub>                                                                                         |

| INS4001/3      | VIH<br>VIL(2)     | Input High Voltage                               | V <sub>SS</sub> -1.5 |                      | V <sub>SS</sub> +0.3  | v     |                                                                                                                           |

| INS4001/3      |                   | Input Low Voltage                                | VDD                  |                      | V <sub>SS</sub> -4.2  | v     |                                                                                                                           |

|                | RI                | I/O Pins Input Resistance                        | 10                   | 18                   | 35                    | ΚΩ    | Internal input resistor is optional                                                                                       |

| O OUTPUT CHAR  | ACTERISTICS       |                                                  |                      |                      |                       |       |                                                                                                                           |

| INS4001/2      | IOL2              | I/O Output Line Sinking<br>Current, "1" Level    | 2.5                  | 5                    | -                     | mA    | $V_{OUT}$ = 0V. For $T^2L$ compatibility a 12K $\Omega$ (±10%) resistor between output and $V_{DD}$ should be added (3).  |

| INS4003        | lOL3              | Parallel Out Pins Sinking<br>Current, "1" Level  | 0.6                  | 1.0                  |                       | mA    | $V_{OUT}$ = 0V. For $T^2L$ compatibility a 5.6K $\Omega$ (±10%) resistor between output and $V_{DD}$ should be added (3). |

| INS4003        | IOL4              | Serial Out Sinking<br>Current, "1" Level         | 1.0                  | 2.0                  |                       | mA    | V <sub>OUT</sub> = 0V                                                                                                     |

| INS4001/2      | V <sub>OL2</sub>  | I/O Output Lines Out-<br>put Low Voltage         | V <sub>SS</sub> -12  | V <sub>SS</sub> -7.5 | V <sub>SS</sub> -6.5  | V     | I <sub>OL2</sub> = 50 μA                                                                                                  |

| INS4003        | VOL3              | Output Low Voltage                               | V <sub>SS</sub> -11  | V <sub>SS</sub> -7.5 | VSS-6.5               | v l   | I <sub>OL3</sub> = 10 μA                                                                                                  |

| INS4001/2      | R <sub>OH2</sub>  | Output Resistance<br>I/O Lines "O" Level         |                      | 1.2                  | 1.8                   | ΚΩ    | V <sub>OUT</sub> = -0.5 V                                                                                                 |

| INS4003        | R <sub>OH3</sub>  | Parallel-Out Pins Output<br>Resistance "0" Level |                      | 400                  | 750                   | Ω     | V <sub>OUT</sub> = -0.5 V                                                                                                 |

| INS4003        | R <sub>OH</sub> 4 | Serial Out Output<br>Resistance "0" Level        |                      | 650                  | 1200                  | Ω     | V <sub>OUT</sub> = -0.5 V                                                                                                 |

Note 1: Typical values are for  $T_A = 25^{\circ}C$  and Nominal Voltages.

Note 2: If non-inverting input option is used,  $V_{IL} = -6.5$  Volts maximum.

Note 3: For  $T^2L$  compatibility on the I/O lines the supply voltages should be  $V_{DD} = -10 \text{ V} \pm 5\%$ ,  $V_{SS} = +5 \text{ V} \pm 5\%$ .

## typical d.c. characteristics

Power Supply Current vs Temperature (INS4001)

Power Supply Current vs Temperature (INS4002)

Power Supply Current vs Temperature (INS4003)

Power Supply Current vs Temperature (INS4004)

Output Current vs Output Voltage (INS4001, INS4002)

Output Current vs Output Voltage (INS4003)

# system timing instruction set $T_A = 0^{\circ} C \text{ to } +70^{\circ} C; V_{DD} = -15 \text{ V } \pm 5\%, V_{SS} = GND$

|             |                                    | ·                                                                   | LII  | LIMIT |      |                                                                                                      |

|-------------|------------------------------------|---------------------------------------------------------------------|------|-------|------|------------------------------------------------------------------------------------------------------|

| PRODUCT     | SYMBOL                             | TEST                                                                | MIN. | MAX.  | UNIT | CONDITIONS                                                                                           |

| INS4001/2/4 | t <sub>cy</sub>                    | Clock Period                                                        | 1.35 | 2     | μs   |                                                                                                      |

|             | <sup>t</sup> φR<br><sup>t</sup> φF | Clock Rise and Fall Times                                           |      | 50    | ns   |                                                                                                      |

|             | <sup>t</sup> φPW                   | Clock Width                                                         | 380  | 480   | ns   |                                                                                                      |

|             | <sup>t</sup> φD1                   | Clock Delay from $\phi_1$ to $\phi_2$                               | 400  | 550   | ns   |                                                                                                      |

|             | <sup>t</sup> φD2                   | Clock Delay from $\phi_2$ to $\phi_1$                               | 150  |       | ns   |                                                                                                      |

|             | tw                                 | Data-In Write Time                                                  | 350  |       | ns   |                                                                                                      |

|             | tH                                 | Data-In Hold Time                                                   | 40   |       | ns   | ·                                                                                                    |

|             | <sup>t</sup> OS <sup>(1)</sup>     | Set Time for Data Out,<br>SYNC, CM-ROM,<br>(2)CM-RAM, (2)Lines      | 0    |       | ns   | C <sub>OUT</sub> = 500 pF for data lines<br>500 pF for SYNC<br>160 pF for CM.ROM<br>50 pF for CM.RAM |

|             | tOH                                | Holdtime for Data Out, Sync, CM-ROM, CM-RAM Lines                   | 50   |       | ns   | C <sub>OUT</sub> = 20 pF                                                                             |

|             | tRtF                               | Rise and Fall Times for<br>Data Out, SYNC, CM-<br>ROM, CM-RAM Lines |      | 500   | ns   | C <sub>OUT</sub> = 500 pF for data lines<br>500 pF for SYNC<br>160 pF for CM-ROM<br>50 pF for CM-RAM |

| INS4001/2   | tD                                 | I/O Output Lines Delay                                              |      | 600   | ns   | C <sub>OUT</sub> = 20 pF                                                                             |

|             | tWC                                | CM Write Time                                                       | 350  |       | ns   |                                                                                                      |

| •           | tHC                                | CM Hold Time                                                        | 10   |       | ns   |                                                                                                      |

| INS4001     | tis                                | I/O Input Lines Set<br>Time                                         | 50   |       | ns   |                                                                                                      |

|             | чн                                 | I/O Input Lines Hold<br>Time                                        | 100  |       | ,    |                                                                                                      |

|             | <sup>t</sup> C <sup>(3)</sup>      | I/O Output Lines Delay<br>on Clear                                  |      | 200   | ns   | C <sub>OUT</sub> = 20 pF                                                                             |

#### NOTES

#### INS4001,INS4002,INS4004 timing diagram

<sup>(1)</sup> Date out, SYNC, CM-ROM, and CM-RAM lines are clocked out with the trailing edge of the  $\phi_2$  clock.

<sup>(2)</sup> The CM-ROM and the selected CM-RAM lines are always activated during A<sub>3</sub> time. They are also activated during M<sub>2</sub> time if an I/O and RAM instruction was fetched by the CPU, and during X<sub>2</sub> time if an SRC instruction was fetched by the CPU;

<sup>(3)</sup> Pin  $C_L$  on INS4001 is used to asynchronously clear the output flip? flops associated with the I/O lines.

INS4003 a.c. characteristics  $T_A = 0^{\circ} C$  to  $+70^{\circ} C$ ;  $V_{DD} = -15 \pm 5\%$ ,  $V_{SS} = GND$

|                 |                           | LIMIT    |          | ]    | •                        |  |  |

|-----------------|---------------------------|----------|----------|------|--------------------------|--|--|

| SYMBOL          | TEST                      | MIN.     | MAX.     | UNIT | CONDITIONS               |  |  |

| tWL             | CP Low Width              | 6        | 10,000   | μs   | ,                        |  |  |

| tWH             | CP High Width             | 6        | Note (1) | μs   |                          |  |  |

| tCD             | Clock-On to Data-Off Time | 3        |          | μs   | •                        |  |  |

| <sup>t</sup> Dd | CP to Data Set Delay      | Note (2) | 250      | ns   | • .                      |  |  |

| t <sub>d1</sub> | CP to Data Out Delay      | 250      | 1,750    | ns   |                          |  |  |

| td2             | Enable to Data Out Delay  |          | 350      | ns   | C <sub>OUT</sub> = 20 pF |  |  |

| td3             | CP to Serial Out Delay    | 200      | 1,250    | ns   | C <sub>OUT</sub> = 20 pF |  |  |

NOTES:  $(1)_{tWH}$  can be any time greater than 6  $\mu$ sec.

(2) Data can occur prior to CP.

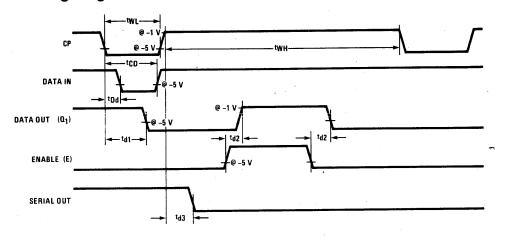

#### INS4003 timing diagram

capacitance f = 1 MHz; V<sub>IN</sub> = 0 V; T<sub>A</sub> = 25°C; Unmeasured Pins Grounded.

|               |                          |                                     | LIMIT (pF) |      |  |

|---------------|--------------------------|-------------------------------------|------------|------|--|

| PRODUCT       | SYMBOL                   | TEST                                | TYP.       | MAX. |  |

| INS4001/2/3/4 | CIN                      | Input <sup>(1)</sup><br>Capacitance | 5          | 10   |  |

| INS4001/2     | $C_{\phi 1}, C_{\phi 2}$ | Clock Input<br>Capacitance          | 8          | 15   |  |

| INS4004       | $C_{\phi 1}, C_{\phi 2}$ | Clock Input<br>Capacitance          | 14         | 20   |  |

|           |                 |                                | LIMI | T (pF) |

|-----------|-----------------|--------------------------------|------|--------|

| PRODUCT   | SYMBOL          | TEST                           | TYP. | MAX.   |

| INS4002/4 | C <sub>D1</sub> | Data Bus I/O Lines Capacitance | 6.5  | 10     |

| INS4001   | C <sub>D2</sub> | Data Bus I/O Lines Capacitance | 9.5  | 15     |

NOTE: (1) Refers to all input pins except data bus I/O and  $\phi_1$  and  $\phi_2$ .

# typical load characteristics

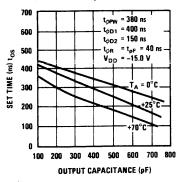

Set Time vs Output Capacitance (Data Lines for INS4001, INS4002, INS4004 & Sync for INS4004)

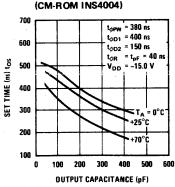

Set Time vs Output Capacitance (CM-ROM INS4004)

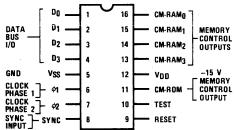

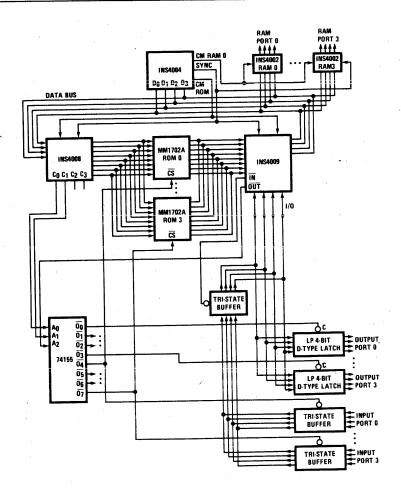

# INS4008/INS4009 in a four-bit integrated processing system (FIPS)

The INS4008/4009 standard memory and I/O interface set provides the complete control functions performed by the INS4001. The INS4008/4009 are completely compatible with other members of the FIPS family. All activity is still under control of the INS4004 CPU. One set of INS4008/4009 and several TTL decoders are sufficient to interface to 4k words of program memory, sixteen four-bit input ports and sixteen four-bit output ports.

It should be noted that in any FIPS configuration the program memory is distinct from the read/write data storage (INS4002 RAM). Using the INS4008/4009, programs can now be stored and executed from RAM memory, but this RAM memory is distinct from the INS4002 read/write data storage. RAM program memory will be organized in eight bit words and 256 word pages, just like the memory array inside the INS4001. Any combination of PROM, ROM, and RAM will be referred to as program memory.

The accompanying diagrams show the internal organization of both the INS4008 and INS4009.

The INS4008 is the address latch chip which interfaces the INS4004 to standard PROMs, ROMs and RAMs used for program memory. The INS4008 latches the eight bit program address sent out by the CPU during A1 and A2 time. During A3 time it latches the ROM chip number from the INS4004. The eight bit program address is then presented at pins A0 through A7 and the four bit chip number (also referred to as page number) is presented at pins C0 through C3. These four bits must be decoded externally and one page of program memory is selected.

The INS4009 then transfers the eight bit instruction from program memory to the INS4004 four bits at a time at M1 and M2. The command signal sent by the CPU activates the INS4009 and initiates this transfer.

When the CPU executes an SRC (Send Register Control) instruction, the INS4008 responds by storing the I/O address in its eight bit SRC register. The content of this SRC register is always transferred to the address lines (A0 through A7) and the chip select lines (C0 through C3) at X1 time. The appropriate I/O port is then selected by decoding the chip select lines. The IN and OUT lines of the INS4009 indicate whether an input or output operation will occur.

The INS4009 is primarily an instruction and I/O transfer device. When the CPU executes an RDR (Read ROM Port) instruction, the INS4009 will send an input strobe (pin 9) to enable the selected input port. It also enables I/O input buffers to transfer the input data from the I/O bus to the data bus. When the INS4009 interprets a WRR (Write ROM Port) instruction, it transfers output data from the CPU to the I/O bus and sends an output strobe (pin 10) to enable the selected output port. A formerly undefined instruction is now used in conjunction with the INS4008/4009 to write data into the RAM program memory. This new instruction is

called WPM (Write Program Memory - 1110 0011). When an instruction is to be stored in RAM program memory, it is written in two four-bit segments. The F/L signal from the INS4008 keeps track of which half is being written. When the CPU executes a WPM instruction, the chip select lines of the INS4008 are jammed with "1111". In the system design this should be designated as the RAM channel. The W line on the INS4008 is also activated by the WPM instruction. The previously selected SRC address on line A0 through A7 of the INS4008 becomes the address of the RAM word being written. By appropriately decoding the chip select lines, the W line, and F/L, the write strobes can be generated for the memory. The F/L line is initially high when power comes on. It then pulses low when every second WPM is executed. A high on the F/L line means that the first four bits are being written, and a low means that the last four bits are being written. The INS4009 transfers the segment of the instruction to the  $\ensuremath{\text{I/O}}$  bus at X2 of the WPM instruction. The SRC address sent to RAM is only 8 bits. When more than one page of RAM (256 bytes) is being written, an output port must be used to supply additional address lines for higher order addresses.

INS4009 BLOCK DIAGRAN

# DEFINITION OF WRITE PROGRAM MEMORY INSTRUCTION

Mnemonic:

WPM

OPR OPA:

1111 0011

Symbolic:

$1111 \rightarrow C_3C_2C_1C_0$  of INS4008

ACC → I/O3I/O2I/O1I/O0 of INS4009

SRC Address → A<sub>0</sub> - A<sub>7</sub> of INS4008

Description:

The chip select lines of the INS4008 are forced to "1111" at X1 time and the content of the accumulator is available on the INS4009 I/O bus at X2. RAM program memory can be loaded four bits at a time. The previous SRC address is sent out on lines A0 through A7 of INS4008.

# SYSTEM ILLUSTRATIONS USING THE 4008 AND 4009

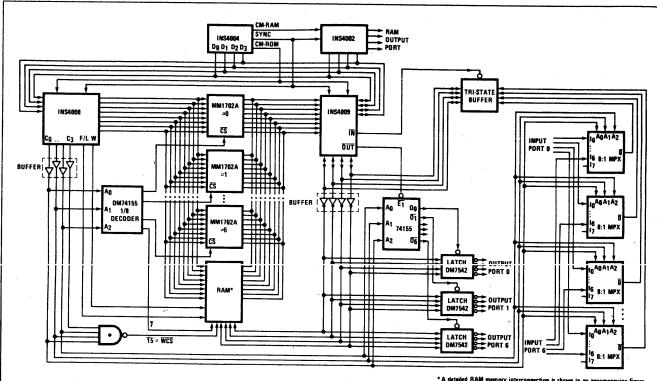

Example 1: Four MM1702A PROMs and Four I/O Ports. Four MM1702As are used for program storage and four four-bit I/O ports are used. In this case D-type output latches are used and a one of eight decoder 3205 is used to decode both the input and output strobes. Note that the I/O bus is buffered from the outputs. Buffers are needed only when the current sinking requirement on the bus exceeds 1.6 mA. In small systems low power TTL could be used and buffers could be avoided.

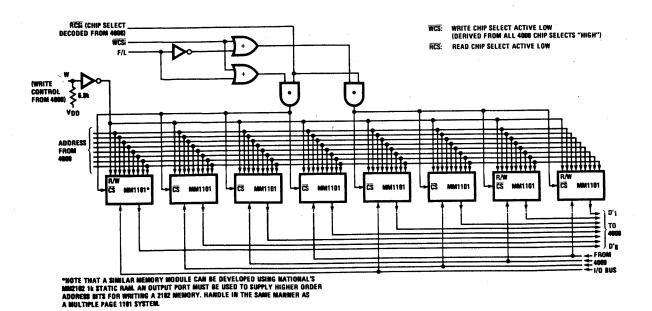

Example 2: Read/Write Memory for Program Storage. This example shows only the RAM portion of a system when RAM is used for program memory. Note that the chip selects are tied together in groups of four. The chip selects are gated with the F/L control line for writing only four bits at a time when executing a WPM instruction. They are also gated with the decoding of the chip selects from the INS4008 for normal program execution. The MM1101 (256 words x 1 bit) is shown. A similar system using the MM2102 (1k words x 1 bit) could be developed.

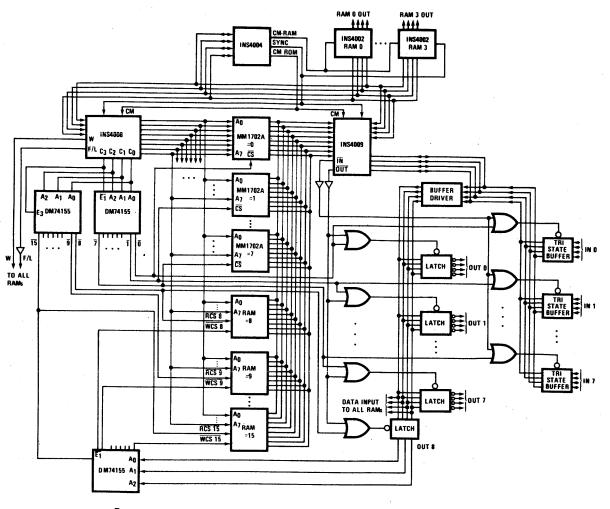

Example 3: Seven MM1702A PROMs, One RAM Block, and Seven I/O Ports. This example uses a single page of RAM program memory shown in Example 2 in a complete system. In this case the input ports are 8:1 multiplexers which are buffered from the I/O bus by a quad tri-state buffer. The input port selection is then the function of the multiplexers. The output ports are latches and the port selection is done using a DM74155 decoder.

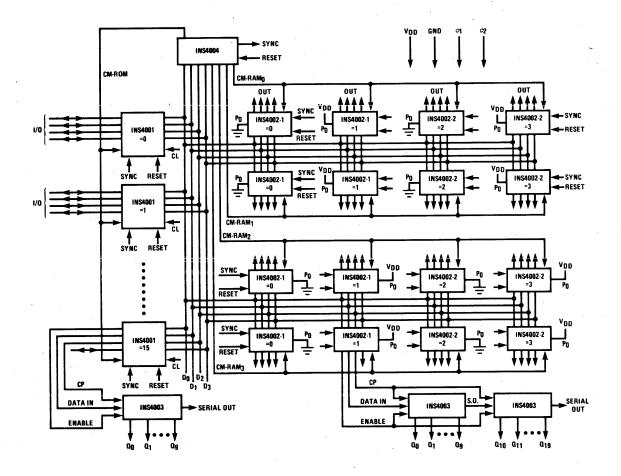

Example 4: Eight MM1702A PROMs, Eight RAM Blocks, and Eight I/O Ports. Program memory organized with 2k bytes in ROM and 2k bytes in RAM. Each basic RAM block can be organized as in Example 2. When more than one block of RAM is used, the write chip select (WCS) for each RAM block is generated by properly gating chip select 15 with special decoding for page selection. Output port eight is dedicated to this selection function. This is only necessary when the RAM program memory is being written. In this example standard TTL logic elements are used for I/O port selection rather than decoders as shown in previous examples. In this case all input ports are tri-state buffers.

The following differences exist between a FIPS system using INS4001 program memory and a system using INS4008/4009 program memory:

- For normal operation, INS4001 ROMs cannot be used in the same system with INS4008/4009.

- 2. Memory address, memory data, I/O bus, and control lines from both INS4008 and INS4009 are defined with respect to positive logic. The FIPS data and control lines from the INS4004 are defined with respect to negative logic. As a result, in program memory used with the INS4009, programs should be coded with logic "1" = high level and logic "0" = low level (i.e., NOP = 0000 0000 = NNNN NNNN). Note that programs are defined for the INS4001 in terms of negative logic such that NOP = 0000 0000 = PPPP PPPP. Carefully check all tapes submitted for metal mask ROMs to be sure that the correct logic definitions are used.

- Input and output data from the INS4009 I/O bus is defined in terms of positive logic. If these interface devices are used for prototyping an INS4001 program memory, care should be taken to be sure that the I/O ports for the INS4001s are defined consistent with the INS4008/4009 system.

- 4. An I/O port associated with the INS4009 can have lines with both input and output capability. On the INS4001 each I/O line may have only a single function, either input or output.

- The RAM program memory cannot be used as a substitute for the INS4002 read/write data storage. They perform distinctly different functions.

- 6. CM-ROM and CM-RAM<sub>0</sub> cannot be used to control INS4002s when CM-ROM is used for INS4008/4009 and the WPM instruction is being used. The reason is that the WPM instruction is interpreted as a Write Memory '(WRM) by INS4002s connected to the same CM line as INS4008/4009. CM-RAM<sub>0</sub> in absence of a DCL behaves exactly like CM-ROM.

#### a.c. characteristics

$T_A$  = 0°C to +70°C,  $V_{SS}$  -  $V_{DD}$  = 15 V  $\pm$  5%. All clock, sync, CM-ROM, data bus, and I/O timing specifications are identical with the INS4001 and INS4004.

| Symbol                      | Parameter                                                  | Product      | Li   | Limit |         | T 0 l'a'                            |  |

|-----------------------------|------------------------------------------------------------|--------------|------|-------|---------|-------------------------------------|--|

|                             | r at attle tet                                             | Product      | Min. | Max.  | Unit    | Test Conditions                     |  |

| t <sub>CY</sub>             | Clock Period                                               | INS4008/4009 | 1.35 | 2.0   | μs      |                                     |  |

| $t_{\phi R}$ , $t_{\phi F}$ | Clock Rise and Fall Time                                   | INS4008/4009 |      | 50    | ns      |                                     |  |

| $t_{\phi}$ PW               | Clock Width                                                | INS4008/4009 | 380  | 480   | ns      |                                     |  |

| t <sub>φD1</sub>            | Clock Delay from $\phi_1$ to $\phi_2$                      | INS4008/4009 | 400  | 500   | ns      |                                     |  |

| t <sub>øD2</sub>            | Clock Delay from $\phi_2$ to $\phi_1$                      | INS4008/4009 | 150  |       | ns      |                                     |  |

| t <sub>A1</sub>             | Address to Output Delay at A <sub>1</sub> , X <sub>1</sub> | INS4008      |      | 1     | μs      | C <sub>L</sub> = 250 pF             |  |

| t <sub>A2</sub>             | Address to Output Delay at A <sub>2</sub>                  | INS4008      |      | 580   | μs      | C <sub>L</sub> = 250 pF             |  |

| ics                         | Chip Select Output Delay at A <sub>3</sub>                 | INS4008      |      | 300   | l<br>ns | C <sub>L</sub> = 50 pF              |  |

| t <sub>WD</sub>             | W Output Delay                                             | INS4008      | ŀ    | 600   | ns      | C <sub>L</sub> = 100 pF             |  |

| t <sub>FD</sub>             | F/L Output Delay                                           | INS4008      | 0.1  | 1     | μs      | C <sub>L</sub> = 100 pF             |  |

| t <sub>WI</sub>             | Data In Write Time                                         | INS4009      | 470  |       | ns      | C <sub>L</sub> = 200 pF on data bus |  |

| $t_{D}$                     | I/O Output Delay                                           | INS4009      |      | 1.0   | μs      | C <sub>L</sub> = 300 pF             |  |

| t <sub>S1</sub>             | IN Strobe Delay                                            | INS4009      |      | 450   | ns      | C <sub>L</sub> = 50 pF              |  |

| t <sub>S2</sub>             | OUT Strobe Delay                                           | INS4009      |      | 1.0   | μs      | C <sub>L</sub> = 50 pF              |  |

#### timing diagram

\*PROGRAM MEMORY ACCESS TIME (CHIP SELECT TO DATA OUT) MUST BE LESS THAN OR EQUAL TO 900 m.

#### capacitance

$f = 1 \text{ MHz}, V_{IN} = V_{SS}, T_A = +25^{\circ}C.$

| Symbol           |                    |           | Limit | t (pF) |                  | D                 | Product   | Limit | (pF) |

|------------------|--------------------|-----------|-------|--------|------------------|-------------------|-----------|-------|------|

|                  | Parameter          | Product   | Тур.  | Max.   | Symbol           | Parameter         | Product   | Тур.  | Max. |

| CIN              | Input Capacitance  | INS4008   | 5     | 10     | C <sub>I/O</sub> | Data Bus and I/O  | INS4008/9 | 8     | 10   |

|                  |                    | INS4009   | 8     | 15     |                  | Capacitance       |           |       |      |

| C <sub>OUT</sub> | Output Capacitance | INS4008/9 | 8     | 10     | $C_{\phi}$       | Clock Capacitance | INS4008/9 | 12    | 20   |

Example 1. Four MM 1702As and Four I/O Ports

Example 2. Read/Write Memory for Program Storage

Example 3. Program Memory with Seven Pages of PROM and One Page of RAM

Example 4. Program Memory with Eight Pages of PROM and Eight Pages of RAM

## FIPS system interconnection

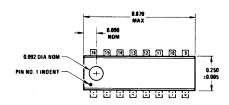

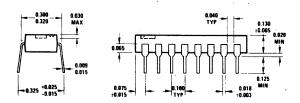

### physical dimensions

Molded Dual-In-Line Package (N)

## ordering information

| NS PART NUMBER | EQUIVALENT INTEL <sup>TM</sup> PART | FUNCTION                        |

|----------------|-------------------------------------|---------------------------------|

| INS4001        | 4001                                | 256 x 8 ROM & 4-Bit I/O Port    |

| INS4002-1      | 4002-1                              | 320-Bit RAM & 4-Bit Output Port |

| INS4002-2      | 4002-2 }                            |                                 |

| INS4003        | 4003 <sup>*</sup>                   | Shift Register                  |

| INS4004        | 4004                                | СРО                             |

| INS4008        | 4008                                | Standard Memory                 |

| INS4009        | 4009                                | I/O Interface Set               |

National Semiconductor Corporation 2900 Semiconductor Drive, Santa Clara, California 95051, (408) 732-5000/TWX (910) 339-9240

National Semiconductor GmbH 808 Fuerstenfeldbruck, Industriestrasse 10, West Germany, Tele. (08141) 1371/Telex 27649 National Semiconductor (UK) Ltd.

Larkfield Industrial Estate, Greenock, Scotland, Tele. (0475) 33251/Telex 778-632