**Series 32000**

DB32016 Development Board User's Manual Publication Number 420310111-001A Customer Order Number NSP-DB32016-M March 1984

Series 32000™

DB32016 Development Board User's Manual

©1984 National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

# REVISION RECORD

| REVISION | RELEASE DATE | SUMMARY OF CHANGES            |

|----------|--------------|-------------------------------|

| A        | 03/84        | First Release.                |

|          |              | DB16000A Development Board    |

|          |              | User's Manual                 |

|          |              | Publication No. 420310111-001 |

#### PREFACE

This manual provides detailed information on using the DB16000A Development Board. It includes descriptions of the board hardware as well as providing set-up and operating procedures.

Reference Documents. The following documents support the DB16000 Development Board and NS16000 Family:

| NS16000 | Programmer's Reference Manual              | (Pub.  | No. | 420306565-001) |

|---------|--------------------------------------------|--------|-----|----------------|

| NS16000 | Cross-Assembler Reference Manual           | (Pub.  | No. | 420306619-002) |

| NS16000 | Pascal Language and Compiler               | (Pub.  | No. | 420306618-002) |

|         | Reference Manual                           |        |     |                |

| NS16000 | NSX16 Cross-Support Utilities              | (Pub.  | No. | 420306617-002) |

|         | Reference Manual                           |        |     |                |

| NS16000 | Development Board Monitor                  | (Pub.  | No. | 420308221-002) |

|         | Reference Manual                           |        |     |                |

| NS16000 | NSX16 Operations Manual                    | (Pub.  | No. | 424009011-002) |

| NS16000 | Run-Time Support Library Reference Manual  | (Pub.  | No. | 420308038-002) |

| ทร16000 | Symbolic Debugger Reference Manual         | (Pub.  | No. | 420306676-002) |

| NS16000 | Floating-Point Support Library             | (Pub.  | No. | 420308220-002) |

|         | Reference Manual                           |        |     |                |

| NS16000 | ISE/16: NS16032 and NS08032                | (Pub.  | No. | 420306675-002) |

|         | In-System Emulators User's Manual          | _      |     |                |

| NS16000 | BLMX-16: Board Level Multi-Tasking         | (Pub.  | No. | 420308147-001) |

|         | Executive System Reference Manual          |        |     |                |

| NS16000 | TDS: Tiny Development System               | (Pub.  | No. | 420306440-001) |

| NS16000 | DB32000 Development Board                  | (Pub.  | No. | 420010144-001) |

|         | User's Manual                              |        |     |                |

| NS16000 | GENIX Cross-Support Software Programmers M | Manual |     |                |

|         | Volume 1                                   | (Pub.  | No. | 424010106-001) |

|         | Volume 2                                   | (Pub.  | No. | 424010106-002) |

| ทร16000 | GENIX Programmer's Manual                  |        |     |                |

|         | Volume 1                                   | •      |     | 424308225-001) |

|         | Volume 2                                   | (Pub.  | No. | 424308225-002) |

| NS16000 | SYS16 System Manual                        | (Pub.  | No. | 420308225-001) |

The information contained in this manual is for reference only and is subject to change without notice.

No part of this document may be reproduced in any form or by any means without the prior written consent of National Semiconductor Corporation.

NS16000, GENIX and STARPLEX II are trademarks of National Semiconductor Corporation.

MULTIBUS, iSBX, and Multimodule are trademarks of Intel Corporation. VAX, VMS are trademarks of Digital Equipment Corporation.

To enhance product positioning, National Semiconductor has recently changed the NS16000 Family names to Series 32000 Family names. The DB16000A development board has been renumbered the DB32016 development board to coincide with these changes. Replace "NS16000 Family" and "DB16000A" with "Series 32000 Family" and "DB32016", respectively, wherever applicable. A revised manual, completely renamed, will be available at a later date.

# CONTENTS

| Chapter    |         |                                             | Page                                          |

|------------|---------|---------------------------------------------|-----------------------------------------------|

| 1 I        | NTRODUC | TION                                        |                                               |

| -          | .2 F    | AANUAL SCOPE AND ORGANIZATION               | 1-1<br>1-1<br>1-2<br>1-2                      |

|            |         | Physical Description                        | 1-3<br>1-3<br>1-5<br>1-6                      |

| 1          | 1 1     | Parallel I/O  Serial I/O  MULTIBUS I/O  BLX | 1-6<br>1-6<br>1-7<br>1-7<br>1-7<br>1-7<br>1-7 |

| 1          | .4 F    | RELATED DOCUMENTATION                       | 1-10                                          |

| <b>2</b> C | PERATI  | NG CONFIGURATIONS                           |                                               |

| 2          | 2.2 t   | USER MODES                                  | 2-1<br>2-1<br>2-2<br>2-2                      |

|            | :       | Stand-Alone Requirements and Setup          | 2-4<br>2-6<br>2-7<br>2-8                      |

| 2          |         | NS16000 FAMILIY CONFIGURATIONS              | 2-11                                          |

| 2          | :       | MULTIBUS SYSTEM CONFIGURATIONS              | 2-12                                          |

| 3 HARI     | DWARE O | RGANIZATION                                 |                                               |

|            | 3.1     | INTRODUCTION                                | 3-1                                           |

|            |         | DOCUMENTATION CONVENTION                    |                                               |

| :          |         | CPU MODULE                                  | 3-2<br>3-2<br>3-2<br>3-3                      |

| :          |         | MEMORY MODULE                               | 3-3<br>3-4                                    |

# CONTENTS (Cont.)

| Chapte | r          |                                                        |                                                                                                                                                                                                             | Page                            |

|--------|------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|        | 3.5        | 1/0 MODUL<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5 | RS232C Serial Communication Ports Parallel Port Switches and Indicators ICU MULTIBUS Interface                                                                                                              | 3-5<br>3-5<br>3-5<br>3-5        |

| 4      | PROGRA     | M INTERFAC                                             | CE                                                                                                                                                                                                          |                                 |

|        | 4.1        | ADDRESSAE                                              | CION                                                                                                                                                                                                        | 4-1<br>4-1<br>4-3               |

|        |            | 4.2.2                                                  | Parallel I/O                                                                                                                                                                                                | 4-3<br>4-6                      |

| 5      | HARDWA     | RE OPTIONS                                             |                                                                                                                                                                                                             |                                 |

|        | 5.1<br>5.2 | OPTION PR                                              | NS16082 MMU Installation (U76, W4, W7)                                                                                                                                                                      | 5-1<br>5-2<br>5-2<br>5-4<br>5-4 |

|        |            | 5.2.2                                                  | NS16202 ICU Installation (U21, U22, W19, W19A). CTTL Frequency Alteration (U30, W1, W3)  PROM Installation                                                                                                  | 5-6<br>5-6<br>5-7<br>5-9        |

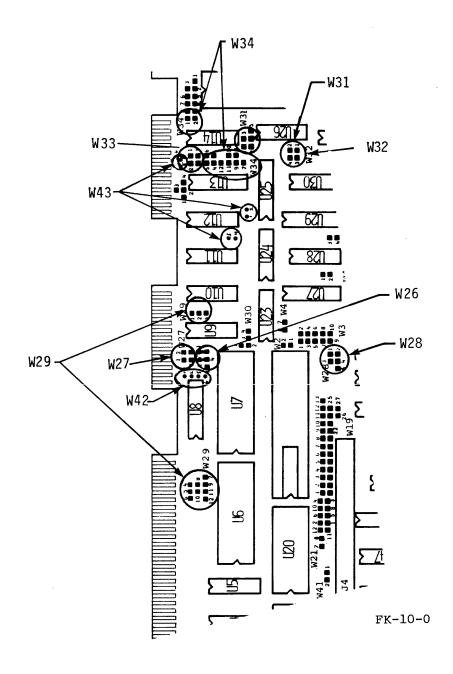

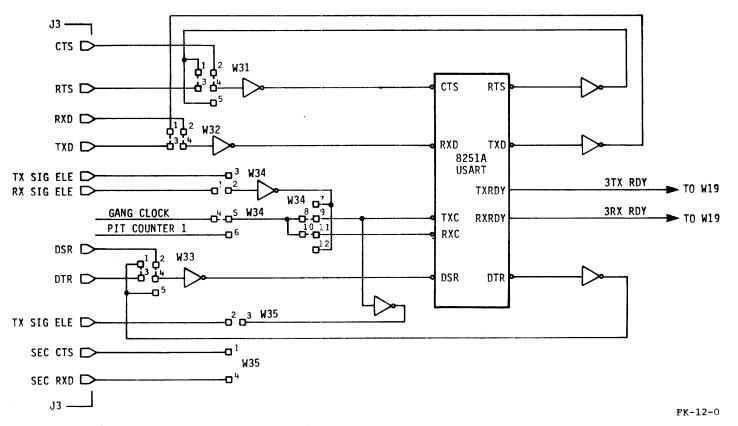

|        |            | 5.2.3                                                  | Wait State Compensation (W3)  Serial I/O  Clock Sources and Baud Rate Configuration (W29, W34)  DTE and DCE Configurations (W26, W27, W28, W31, W32, W33)  Handshake Signal Loop-Back (W26, W28, W31, W33). | 5-14                            |

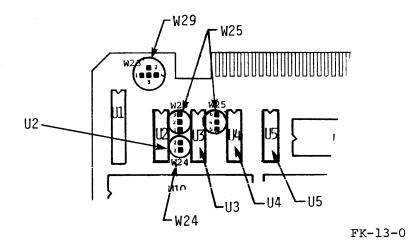

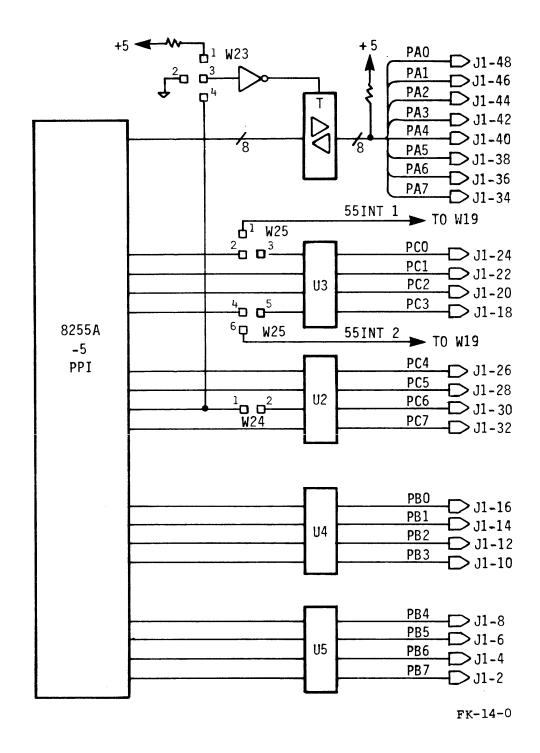

|        |            | 5.2.4                                                  | Parallel I/O (PIO)                                                                                                                                                                                          | 5-21<br>5-21<br>5-23<br>5-23    |

# CONTENTS (Cont.)

| Chapte | er         |                                                                                                         |                                                                                                                                                                                                                                 | Page                                          |

|--------|------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

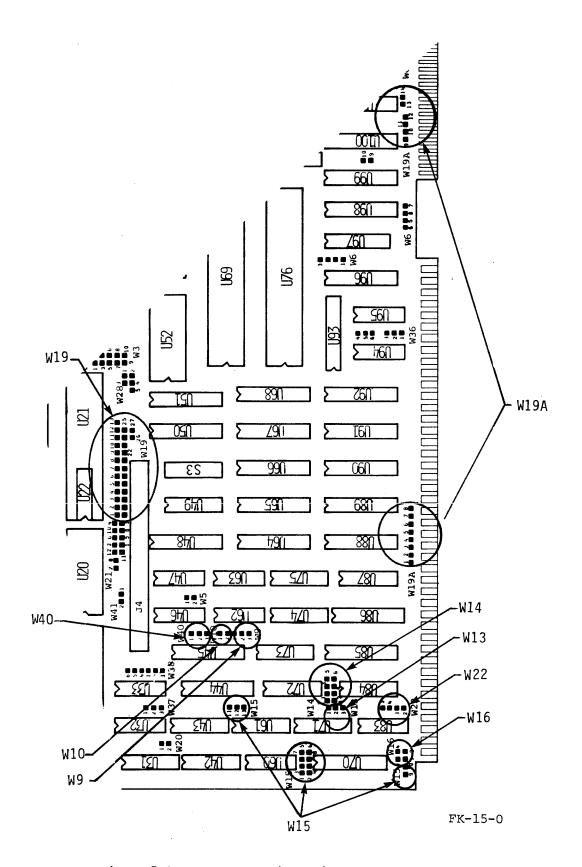

|        | 5•3        | 5.2.5<br>5.2.6<br>OPTION S<br>5.3.1<br>5.3.2<br>5.3.3                                                   | MULTIBUS I/O  Arbitration Options (W9, W10, W40)  Dual-Port RAM (W13, W14, W15, W16)  Bus Clocks (W22)  BLX I/O (J4, W38, W41)  SUMMARY  Jumper Option Tabulation  Socketed Option Tabulation  Standard Shipping Configurations | 5-25<br>5-28<br>5-30<br>5-30<br>5-34<br>5-34  |

| Append | lix        |                                                                                                         |                                                                                                                                                                                                                                 | Page                                          |

| A      | DB1600     | OA CONFI                                                                                                | DENCE TEST                                                                                                                                                                                                                      | A-1                                           |

|        | A.1<br>A.2 |                                                                                                         | DESCRIPTION  CE CHARACTERISTICS  DIP Switch Settings  LED Indicators                                                                                                                                                            | A-1<br>A-1<br>A-1                             |

|        | A.3        | A.2.4                                                                                                   | RAM Usage  QUENCE  CPU Test  Configuration and Exception Setup  J2 Transmitter Test  J2 Receiver Test  J3 Loopback Test  J3 Transmitter Test                                                                                    | A-3<br>A-4<br>A-4<br>A-4<br>A-5<br>A-5        |

|        |            | A.3.7<br>A.3.8<br>A.3.9<br>A.3.10<br>A.3.11<br>A.3.12<br>A.3.13<br>A.3.14<br>A.3.15<br>A.3.16<br>A.3.17 | J3 Receiver Test  J3 Loopback Test  RAM Data Test  RAM Address Test  RAM Refresh Test  MMU Register Test  MMU Trace Test  Floating-Point Unit Test  Programmable Interval Timer Test  Interrupt Control Unit Timer Test         | A-5<br>A-5<br>A-6<br>A-6<br>A-6<br>A-7<br>A-7 |

|        |            | π 2 1Q                                                                                                  | Interrupt Control Unit Interrupt Test                                                                                                                                                                                           |                                               |

## ILLUSTRATIONS

1-1

DB16000A Topography

1-4

2-1

DB16000A User Modes

2-3

2-2

Serial Cable for Edge Connector

2-5

Page

Figure

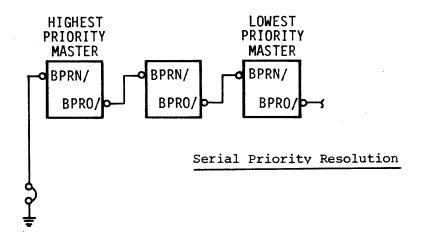

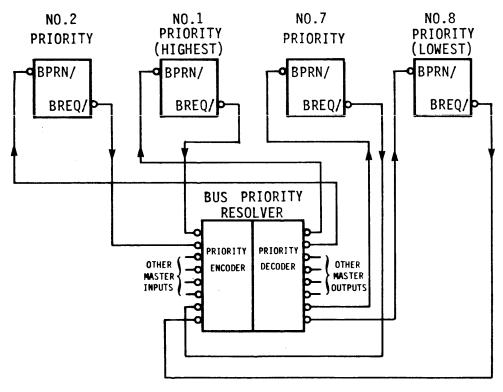

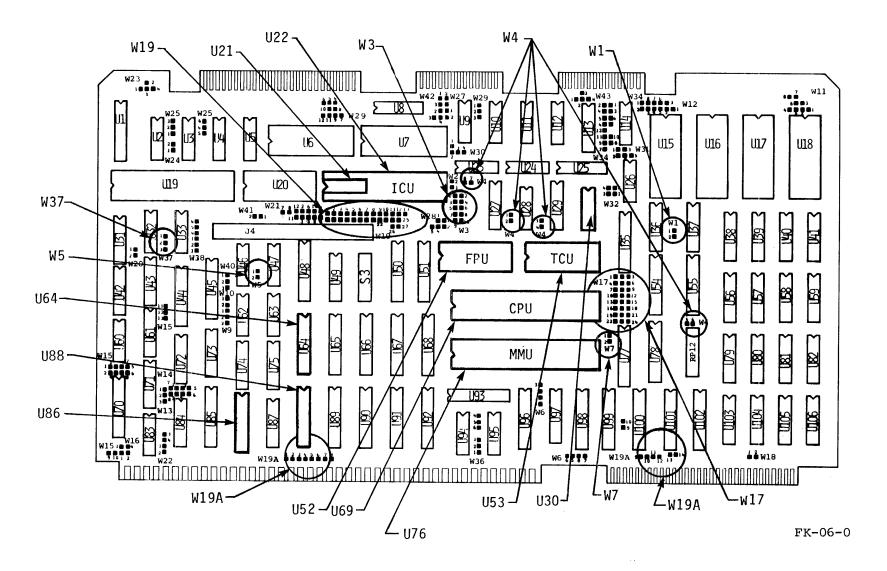

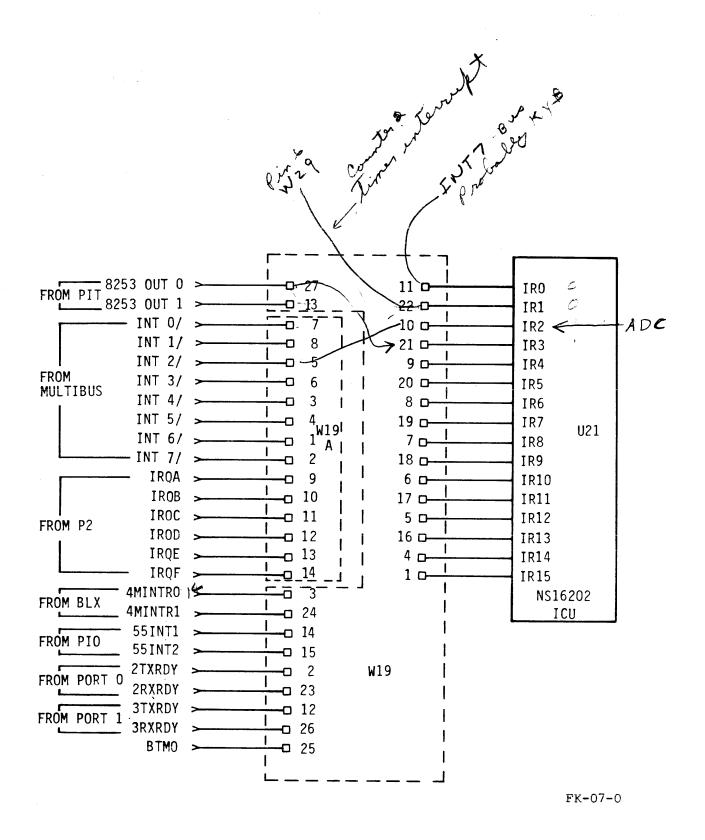

|    | 5-11                                                                                                                       | Edge Connector Using Male-to-Male Cable  MULTIBUS Priority Resolution Schemes  NS16000 Option Items  ICU Interrupt Matrix  PROM Option Items  24-Pin PROM Installation  Serial I/O Option Items  Factory Configuration, DCE Port 0  Factory Configuration, DTE Port 1  PIO Option Items  PIO Block Diagram  MULTIBUS I/O Option Items  BLX Option Items  Jumper Locations                                                                                                                                         | 2-14<br>5-3<br>5-5<br>5-8<br>5-12<br>5-16<br>5-19<br>5-20<br>5-22<br>5-24<br>5-26<br>5-33                               |

|----|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

|    |                                                                                                                            | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                         |

| Тá | able                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page                                                                                                                    |

|    | 1-2<br>1-3<br>1-4<br>1-5<br>1-6<br>1-7<br>1-8<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6 | J2 AND J3 PIN/SIGNAL P1 PIN/SIGNAL P2 PIN/SIGNAL P1 SIGNAL DEFINITION P2 SIGNAL DEFINITION J4 BLX PIN/SIGNAL BLX SIGNAL DEFINITION DB16000A ADDRESS SPACE CONFIGURATION REGISTER CONTROL FUNCTIONS PPI INTERNAL REGISTER ADDRESSES PIT INTERNAL REGISTER ADDRESSES ICU REGISTER ADDRESSING BANK CAPACITY FOR INSTALLED PROM TYPES PROM BANK CAPACITY AND ADDRESS SELECTIONS PROM BANK CONFIGURATION JUMPERS VS. PROM TYPE PROM WAIT STATE COMPENSATION MEGABYTE RANGE SELECTION DUAL PORT START ADDRESS SELECTION | 1-11<br>1-13<br>1-14<br>1-17<br>1-19<br>1-20<br>4-2<br>4-4<br>4-5<br>4-7<br>4-8<br>5-10<br>5-11<br>5-13<br>5-15<br>5-29 |

|    | 5-8<br>5-9<br>5-10                                                                                                         | DUAL PORT PRIVACY SELECTION  JUMPER OPTIONS  SOCKETED OPTIONS  FACTORY CONFIGURED JUMPER AND SOCKERT OPTIONS  DIP SWITCH SETTINGS                                                                                                                                                                                                                                                                                                                                                                                 | 5-36<br>5-44<br>5-45                                                                                                    |

#### Chapter 1

#### INTRODUCTION AND OVERVIEW

#### 1.1 MANUAL SCOPE AND ORGANIZATION

The DB16000A development board is a complete microcomputer system. It is designed to assist the user in evaluating NS16000 microprocessors, slave processors, and support chips in a variety of application environments. This manual details the extent of the DB16000A's flexibility, and the manner in which hardware options may be implemented.

In most cases, this manual should be used in conjunction with an appropriate software user's manual to gain a complete understanding of the DB16000A as a system. The DB16000A is factory-configured with TDS (Tiny Development System) software in on-board PROM; therefore, the TDS user's manual should be consulted for operating information once the hardware is properly configured.

The remaining sections of Chapter 1 contain a brief overview of the DB16000A's hardware capability, as well as physical, environmental, and electrical interconnect specifications.

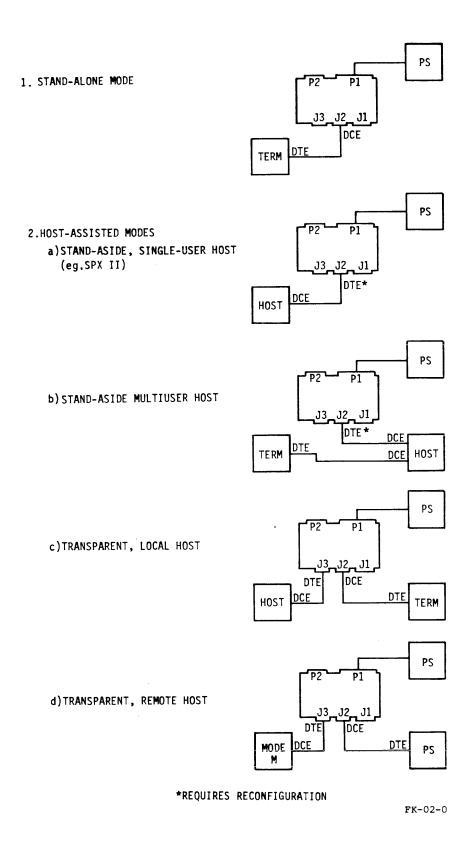

Chapter 2, "Operating Configurations", describes the DB16000A's intended use as an evaluation/development tool. Variations in user mode configuration, 16K family mix, and MULTIBUS usage are explained.

Chapter 3, "Hardware Organization", explains the functional organization of DB16000A hardware. This chapter is intended for use in conjunction with schematics supplied with the DB16000A; however, the text alone is sufficient to gain a general understanding of the hardware implementation.

Chapter 4, "Program Interface", contains information necessary to operate DB16000A hardware under program control. The means of program access and manipulation of hardware is explained.

Chapter 5, "Hardware Options", describes how the DB16000A hardware functions may be altered.

#### 1.2 PRODUCT DESCRIPTION

The following is a brief overview of DB16000A.

#### 1.2.1 Features

- 10 MHz operation (DB16000A-110) or 6 MHz operation (DB16000A-006)

- CPU socket accepts either an NS16032 or NS08032 microprocessor (NS16032 supplied in factory configuration)

- Socket for NS16081 floating-point unit--extremely high speed floating-point arithmetic (NS16081 is installed in DB16000A-110)

- Socket for NS16082 memory management unit--demand-paged virtual memory management (NS16082 is installed in DB16000A-110)

- Socket for NS16202 interrupt controller unit--provides up to 16 levels of maskable, vectored interrupts (NS16202 is installed in DB16000A-110)

- NS16201 timing control unit--provides CPU and TTL-level clocks

- 128K bytes of on-board, dual-port dynamic RAM

- Dual-port RAM external address jumper selectable

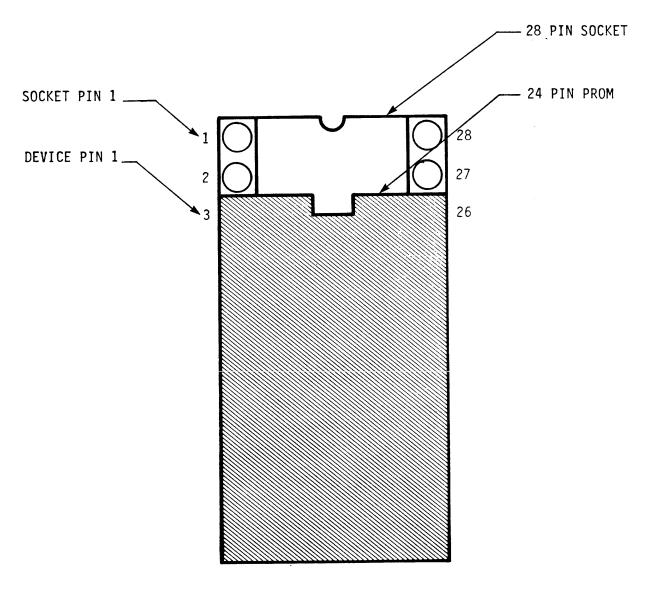

- Four sockets for up to 96K bytes of 24/28-pin ROM or EPROM

- TDS16A (Tiny Development System) software in PROM

- One BLX expansion module connector for additional I/O capability

- 24 programmable, parallel I/O lines

- Two programmable synchronous/asynchronous RS232 compatible serial data ports

- Three programmable 16-bit timer/event counters

- MULTIBUS interface with multimaster capability

- MULTIBUS BCLK and CCLK meet MULTIBUS specifications regardless of CPU speed

- 24-bit addressing allowing access of up to 16M bytes of combined system memory and I/O

#### 1.2.2 Functions

The DB16000A may be operated in either of two configurations:

- Stand-alone

- Host-assisted

In stand-alone mode, the factory-configured TDS on-board software can be used to edit, assemble, and debug small programs. The intent is to allow the user to explore the NS16000 instruction set.

In host-assisted mode, the DB16000A is used in conjunction with a larger host computer. The host, together with development software, is used to develop programs for execution on the DB16000A. In this case, the DB16000A functions as a native NS16000 execution/debug environment for the host-developed program. An appropriate monitor program replaces TDS, allowing the program to be downloaded and controlled by the host.

The DB16000A's flexibility is further enhanced by its MULTIBUS interface. In all user modes, additional MULTIBUS compatible boards can be used to expand the DB16000A's I/O capability.

Further, the DB16000A permits the user to selectively evaluate combinations of NS16000 family members from the following set:

- NS16032 32-bit CPU; 16-bit data bus

- NS08032 32-bit CPU; 8-bit data bus

- NS16082 MMU; memory management slave processor

- NS16081 FPU; floating-point slave processor

- NS16202 ICU; interrupt controller

- NS16201 TCU; timing control unit

Note that the NS16082 can not be used in conjunction with the NS08032.

## 1.2.3 Physical Description

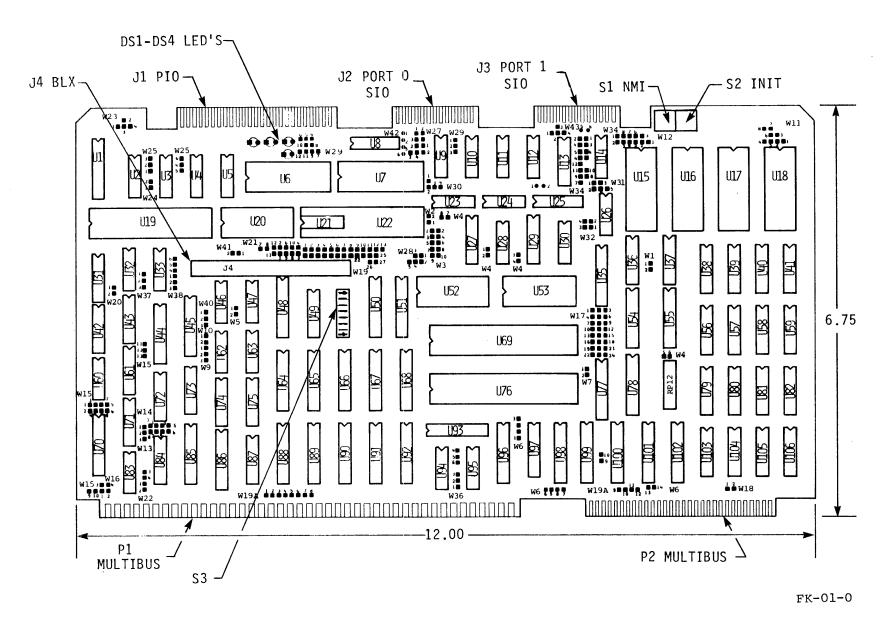

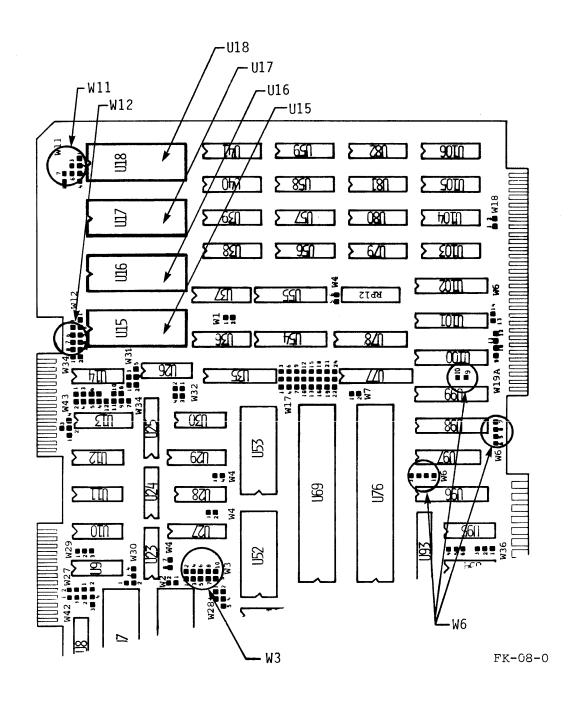

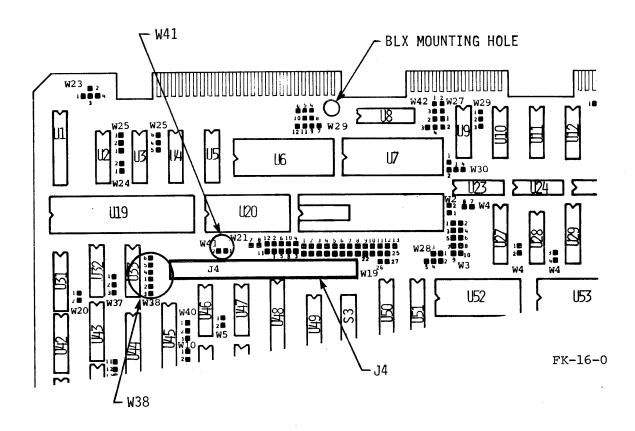

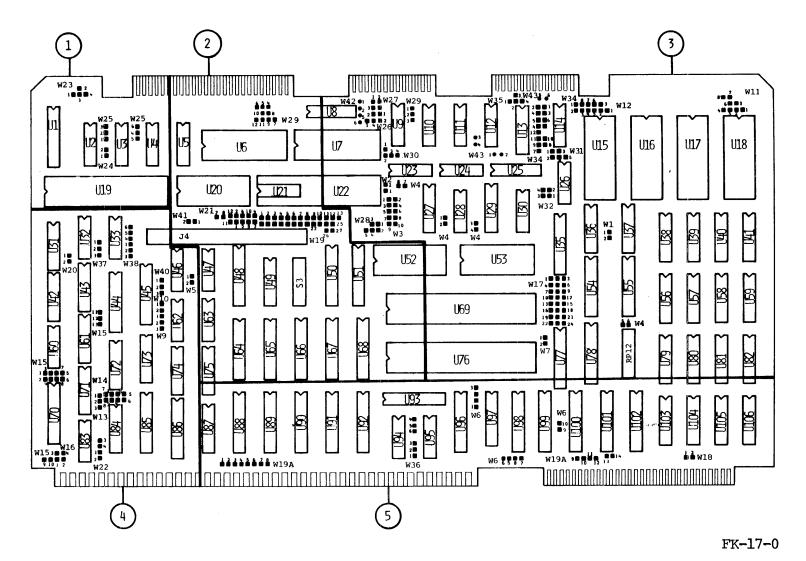

The DB16000A (Figure 1-1) is a rectangular printed circuit assembly measuring 6.75 inches by 12 inches. The board is specifically designed for use in MULTIBUS compatible card cages. If a card cage is not used, the board may be placed on a nonconductive surface for operation.

Three physical features of the DB16000A are:

- Six connectors

- Three switches

- Four LED indicators

Connectors. Six connectors on the DB16000A provide interfaces to peripherals and the MULTIBUS interface. Three connectors (J1, J2, and J3) are found on the front edge of the assembly, two connectors (P1 and P2) are found on the rear edge of the assembly, and one connector J4 is positioned near the front edge of the assembly.

Figure 1-1 DB16000A Topography

Connector J1 is a 50-pin pc tongue connector with 25 0.1-inch spaced contacts on each side of the board. The connector is dedicated for parallel I/O use. Note that all contacts (odd numbered) on the component side of the board are connected to ground. Therefore, a mating flat-cable assembly will have alternate conductors grounded, reducing noise coupling among adjacent signals.

Some vendors of mating connectors to J1 are:

- 3M #3415-0001

- AMP #88083-1

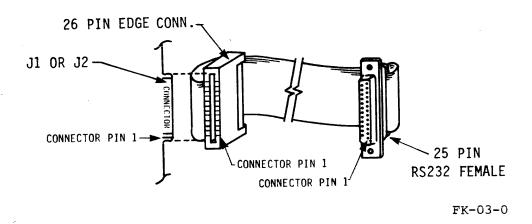

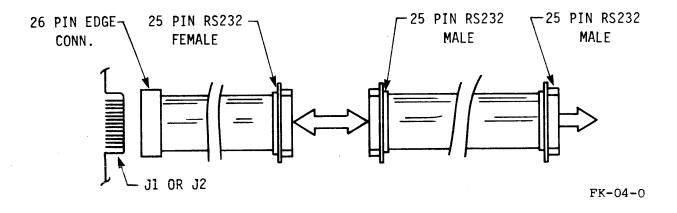

Connectors J2 and J3 are 26-pin pc tongue connectors with 13 0.1-inch spaced contacts on each side of the board. These connectors are dedicated for serial I/O (RS232C) use. The DB16000A is designed to permit the use of "flat cable" assemblies for J2 and J3 connection.

Some vendors of mating connectors to J2 and J3 are:

- 3M #3462-0001 CRIMP

- AMP #88106-1

Connector P1 is an 86-pin pc tongue connector with 43 0.156-inch spaced contacts on each side of the board. P1 is the principle means of connection to the MULTIBUS interface. In addition, all power for the DB16000A is provided through this connector.

Some vendors of mating connectors to P1 are:

- Viking #2KH43/9AMK12 (for soldered connections)

- Elfab #BW1562D43PBB (for wire wrap connections)

Connector P2 is a 60-pin pc tongue connector with 30 0.1-inch spaced contacts on each side of the board. P2 is the auxilliary bus connector, providing access to the upper MULTIBUS address bits and various DB16000A control signals.

Some vendors of mating connectors to P2 are:

- Elfab #BS1020A30PBB (for soldered connections)

- Viking #3KH30/9JNK (for wire wrap connections)

Connector J4 consists of a BLX (Board Level Expansion) connector. J4 permits installation of 8- or 16-bit expansion boards; e.g. National Semiconductor Corporation's BLX-351. The connector consists of a 36-pin field for 8-bit expansion modules, plus an additional 8-pin field for 16-bit capability. Refer to National Semiconductor Corporation's Board Level Computer products databook for further information on expansion boards.

<u>Switches</u>. Two pushbutton switches (S1 and S2), and one 8-position DIP switch (S3) are provided on the DB16000A.

S1, labeled NMI, introduces a nonmaskable interrupt to the DB16000A's CPU when pressed. S2, labeled INIT, resets the board when pressed. Both switches are located on the front edge of the board assembly.

S3 consists of eight SPST switches in a dual in-line package. S3 is utilized by firmware to indicate options invoked by the user; e.g. serial port baud rate. The switch is located near the center of the board.

<u>Indicators</u>. Four LED indicators (DS1 through DS4) are mounted near the front edge of the board assembly.

DS1 through DS3 are controlled by the content of a program addressed register. These are provided for use by the TDS power on confidence test program to indicate test status. They may also be used to indicate any other information the user desires.

DS4 is driven directly by a one-shot timer whose period is approximately 15 milliseconds. DS4 will light up whenever there is no memory or I/O access completed by the CPU within this period. This is useful for indicating a MULTIBUS timeout or malfunctioning CPU.

#### 1.3 SPECIFICATIONS

## 1.3.1 Environment

The DB16000A is designed for operation in an office or laboratory environment. Avoid confining the DB16000A in a closed space, unless sufficient air flow is provided to ensure all components are operated within their specified temperature range.

Temperature: Operating 0°C to 55°C

Nonoperating -40°C to 75°C

• Humidity: 5% to 95% relative, noncondensing

• Altitude: Operating 15,000 ft.

Nonoperating 25,000 ft.

## 1.3.2 Power Requirements

The DB16000A requires three regulated DC voltages for operation:

- +12 volt DC, +10%, 50 mA maximum

- -12 volt DC, +10%, 50 mA maximum

- +5 volt DC, +5%, 7.5 A maximum

## 1.3.3 Interfaces

There are five interfaces provided in the DB16000A:

- Parallel I/O (J1)

- Serial I/O Port 0 (J2)

- Serial I/O Port 1 (J3)

- MULTIBUS I/O (P1 and P2)

- BLX (J4)

The following sections detail connector pinout and signal definitions for each of the interfaces.

<u>Parallel I/O.</u> A 24-line parallel interface provides a means of controlling I/O devices. The function of each line is defined under program control. Jumper options, as well as socketed interface transceivers, are provided for the purpose of altering the factory configuration.

The 24 interface lines are organized as three, 8-bit ports: Port A, Port B, and Port C.

Table 1-1 lists J1 pin numbers, bit assignment, interface element, signal direction, and termination for the factory configuration.

<u>Serial I/O.</u> The DB16000A serial interfaces are designed to provide a wide variety of synchronous and asynchronous, RS232C compatible communications. Jumper options are provided for the purpose of altering the configuration of each interface.

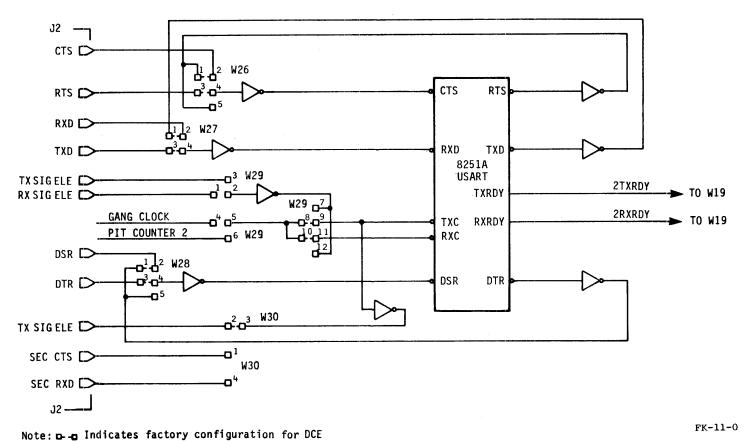

As configured by the factory, Port 0 (J2) is intended to connect to an RS232C compatible terminal, and is configured as DCE (Data Communication Equipment). Port 1 (J3) is configured as DTE (Data Terminal Equipment), and is intended for connection to a modem or host computer. Both interfaces are set for 9600 baud asynchronous communication.

Table 1-2 lists pinout, signal definition and direction for the factory configuration.

MULTIBUS I/O. The DB16000A incorporates a MULTIBUS interface, allowing the user to configure larger systems. Most often, the DB16000A would be used in conjunction with MULTIBUS compatible expansion RAM, disk controller, or serial controller boards. However there is no restriction, beyond MULTIBUS compliance.

TABLE 1-1 J1 PIO PIN/SIGNAL

| PIN | SIGNAL | PIN | SIGNAL        | INTERFACE | DIRECTION | TERMINATION |

|-----|--------|-----|---------------|-----------|-----------|-------------|

| 1   | GND    | 2   | Port B, bit 7 | 7437      | OUT       | NONE        |

| 3   | GND    | 4   | Port B, bit 6 | 7437      | OUT       | NONE        |

| 5   | GND    | 6   | Port B, bit 5 | 7437      | OUT       | NONE        |

| 7   | GND    | 8   | Port B, bit 4 | 7437      | OUT       | NONE        |

| 9   | GND    | 10  | Port B, bit 3 | 7437      | OUT       | NONE        |

| 11  | GND    | 12  | Port B, bit 2 | 7437      | OUT       | NONE        |

| 13  | GND    | 14  | Port B, bit 1 | 7437      | OUT       | NONE        |

| 15  | GND    | 16  | Port B, bit 0 | 7437      | OUT       | NONE        |

| 17  | GND    | 18  | Port C, bit 3 | 7437      | OUT       | NONE        |

| 19  | GND    | 20  | Port C, bit 2 | 7437      | OUT       | NONE        |

| 21  | GND    | 22  | Port C, bit 1 | 7437      | OUT       | NONE        |

| 23  | GND    | 24  | Port C, bit 0 | 7437      | OUT       | NONE        |

| 25  | GND    | 26  | Port C, bit 4 | 7437      | OUT       | NONE        |

| 27  | GND    | 28  | Port C, bit 5 | 7437      | OUT       | NONE        |

| 29  | GND    | 30  | Port C, bit 6 | 7437      | OUT       | NONE        |

| 31  | GND    | 32  | Port C, bit 7 | 7437      | OUT       | NONE        |

| 33  | GND    | 34  | Port A, bit 7 | 8303      | IN/OUT    | 4.7K PU     |

| 35  | GND    | 36  | Port A, bit 6 | 8303      | IN/OUT    | 4.7K PU     |

| 37  | GND    | 38  | Port A, bit 5 | 8303      | IN/OUT    | 4.7K PU     |

| 39  | GND    | 40  | Port A, bit 4 | 8303      | IN/OUT    | 4.7K PU     |

| 41  | GND    | 42  | Port A, bit 3 | 8303      | IN/OUT    | 4.7K PU     |

| 43  | GND    | 44  | Port A, bit 2 | 8303      | IN/OUT    | 4.7K PU     |

| 45  | GND    | 46  | Port A, bit 1 | 8303      | IN/OUT    | 4.7K PU     |

| 47  | GND    | 48  | Port A, bit 0 | 8303      | IN/OUT    | 4.7K PU     |

| 49  | GND    | 50  | No Connect    |           |           |             |

TABLE 1-2 J2 AND J3 PIN/SIGNAL

|                   | RS232<br>PIN | J2/J3<br>PIN | SIGNAL<br>NAME | FUNCTION                     | J2 (DCE) IN/OUT | J3 (DTE)<br>IN/OUT |

|-------------------|--------------|--------------|----------------|------------------------------|-----------------|--------------------|

|                   | V 1 w        | 2            | GND            | Logic Ground                 |                 |                    |

| :                 | √ 2          | 4            | TXD            | Transmit Data receive Action | IN              | OUT                |

|                   | / 3          | 6            | RXD            | Receive Data Ormani data     | OUT             | IN                 |

|                   | , 4          | 8            | RTS            | Request to Send              | IN              | OUT                |

|                   | √ *<br>√ 5:  | 10           | CTS            | Clear to Send                | OUT             | IN                 |

| الم الحق ورجمه ز  | and of       | 12~          | DSR            | Data Set Ready               | OUT             | IN                 |

| grane .           | . J 7        | 14           | GND            | Logic Ground                 |                 |                    |

| المع مشعار        | 1 detects    | 16           |                |                              |                 |                    |

| العدي الرافيلومية | 9            | 18           |                |                              |                 |                    |

|                   | 10           | 20           |                |                              |                 |                    |

|                   | 11           | 22           | +12            | +12 VDC TTY Interface Power  | NC              | NC                 |

|                   | 12           | 24           |                |                              |                 |                    |

|                   | * 13         | 26           | SCTS           | Secondary Clear to Send      | 11C             | NC                 |

|                   | 14           | 1            |                |                              |                 |                    |

|                   | 14           | 3            | TSET           | Transmit Sig. Timing (DCE    | NC              | NC                 |

|                   |              | 3            | 1951           | Source)                      | NC              | 140                |

|                   | 16           | 5            | SRXD           | Secondary Receive Data       | NC              | NC                 |

|                   | v/ 17.∞      | 7            | RSET           | Receive Sig. Timing (DCE     | NC              | NC                 |

|                   |              |              |                | Source)                      | ·               |                    |

|                   | 18           | 9            |                |                              |                 |                    |

|                   | 19           | 11           |                |                              |                 |                    |

|                   | √ 20         | 13           | DTR            | Data Terminal Ready          | IN              | OUT                |

|                   | 21           | 15           |                |                              |                 |                    |

|                   | 22           | 17           |                |                              |                 |                    |

|                   | 23           | 19           | -12            | -12 VDC TTY Interface Power  | NC              | NC                 |

|                   | J 24         | 21           | TSET           | Transmit Sig. Timing (DTE    | NC              | NC                 |

|                   |              |              |                | Source)                      |                 |                    |

|                   | 25           | 23           | +5             | +5 VDC TTY Interface Power   | NC              | NC _               |

The DB16000A's MULTIBUS compliance levels (refer to Intel MULTIBUS Specification, 9800683-04) are:

- Master--D16 M24 I16 V0 El; indicationg 8/16-bit data path, 24-bit memory address path, 8 or 16-bit I/O address path, and level or edge triggered non-bus vectored interrupts (if the NS16202 is installed)

- Slave--D16 M24; indicating 8/16-bit data path and 24-bit memory address path.

The user must be mindful of MULTIBUS compliance levels when constructing a MULTIBUS system. Compliance levels among boards in the system need not be the same. However, system bus transactions between any two boards must be in accordance with the lowest level of compliance. For example, a master with 8/16-bit data path may transact with a slave possessing an 8-bit data path. In this case, transactions are limited to 8-bit data.

Table 1-3 lists P1 pin numbers and signal names. Likewise, Table 1-4 lists P2 pin numbers and signal names. Table 1-5 defines P1 signals and Table 1-6 defines P2 signals.

NOTE: Most signals in P2 pertain to the DB16000A's CPU cluster. These signals are provided as reference only; the user is not advised to incorporate these signals in external circuitry.

BLX. The board level expansion connector is provided as an additional means of extending the DB16000A's I/O capability; e.g. additional serial or parallel interfaces may be added.

Table 1-7 lists the connector pinout and signal names for J4. Table 1-8 lists signal definitions.

## 1.4 RELATED DOCUMENTATION

The documents listed in the Preface of this manual may be helpful while using the DB16000A.

In addition, the user should have on hand any pertinent documentation for peripheral devices (e.g. printer or terminal and other MULTIBUS boards to be interfaced with DB16000A.

This manual makes no attempt to instruct the user in proper design of NS16000-based hardware or software.

TABLE 1-3 P1 PIN/SIGNAL

| ET INCOT ON  |                             | (COMPONENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SIDE)        |      | (SOLDER     | SIDE)          |          |

|--------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------------|----------------|----------|

| FUNCTION     | PIN                         | MNEMONIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DESCRIPTION  | PIN  | MNEMONIC    | DESCRIPTION    |          |

|              | 1                           | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Signal GND   | 2    | GND         | Signal GND     |          |

|              | 3                           | +5 <b>V</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | +5 VDC       | 4    | +5 <b>v</b> | +5 VDC         |          |

| POWER        | 5                           | +5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | +5 VDC       | 6    | +5V         | +5 VDC         |          |

| SUPPLIES     | 7                           | +12V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +12 VDC      | 8    | +12V        | +12 VDC        |          |

|              | 9                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              | 10   |             |                |          |

|              | 11                          | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Signal GND   | 12   | GND         | Signal GND     |          |

|              | 13                          | BCLK/ NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Bus Clock    | 14   | INIT/ UC    | Initialize     |          |

|              | 15                          | BPRN GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Bus Priority | 16   | BPRO/ N.C   | Bus Priority   |          |

|              |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | In           |      |             | Out            |          |

| BUS          | 17                          | BUSY/ NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Bus Busy     | 18   | BREO/ N.C   | Bus Request    |          |

| CONTROLS     | 19                          | MRDC/ NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Memory Read  | 20 / | MWTC/) NC   | Memory Write - | -RD XWAX |

|              |                             | RD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Command      |      | WR          | Command        |          |

|              | 21                          | IORC/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I/O Read     | 22   | IOWC/       | I/O Write      |          |

|              |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Command      |      |             | Command        |          |

|              | 23                          | XACK/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Transfer     | 24   | INH1/       | Inhibit 1      |          |

| ,            | - New F. Landgeman Per Life | The same of the sa | Acknowledge  | \$   |             | Disable RAM    |          |