# Data Book Cyrix Corporation Confidential

October 29, 1998 - Revision 2.0

Addenda and other updates for this manual can be obtained from Cyrix Web site: www.cyrix.com.

©1998 Copyright Cyrix Corporation. All rights reserved. Printed in the United States of America

Cyrix is a registered trademark of Cyrix Corporation.

Cyrix Trademarks include: Cx5520, Display Compression Technology (DCT), MediaGX, XpressAUDIO, XpressGRAPHICS, XpressRAM, Virtual System Architecture (VSA)

All other products mentioned herein are trademarks of their respective owners and are hereby recognized as such. Cyrix is a wholly-owned subsidiary of National Semiconductor® Corp.

Cyrix Corporation 2703 North Central Expressway Richardson, Texas 75080 United States of America

Cyrix Corporation (Cyrix) reserves the right to make changes in the devices or specification described herein without notice. Before design-in or order placement, customers are advised to verify that the information on which orders or design activities are based is current. Cyrix warrants its products to conform to current specifications in accordance with Cyrix' standard warranty. Testing is performed to the extent necessary as determined by Cyrix to support this warranty. Unless explicitly specified by customer order requirements, and agreed to in writing by Cyrix, not all device characteristics are necessarily tested. Cyrix assumes no liability, unless specifically agreed to in writing, for customer's product design or infringement of patents or copyrights of third parties arising from use of Cyrix devices. No license, either express or implied, to Cyrix patents, copyrights, or other intellectual property rights pertaining to any machine or combination of Cyrix devices is hereby granted. Cyrix products are not intended for use in any medical, life saving, or life sustaining systems. Information in this document is subject to change without notice.

#### MediaGX™ MMX™-Enhanced Processor

Integrated x86 Solution with MMX Support

#### Introduction

#### **♦ High Performance**

- Processor speeds up to 300MHz

- Write-Back cache

- Memory management with Load Store and Memory-Read Bypassing

- Six-stage integer pipeline

- XpressRAM™ and XpressGRAPHICS™

#### ♦ MediaGX™ MMX™-Enhanced Processor

- Processor Integrated Functions:

- Graphics Pipeline

- Memory Controller (SDRAM)

- Display Controller

- PCI Controller

- Interfaces with Cx5520 or Cx5530 I/O Companion chip

- 320 SPGA or 352 BGA package

#### ♦ x86 Instruction Set with MMX Support

- Compatible with MMX Technology

- Runs Windows<sup>®</sup>95, Windows 3.x, Windows NT, DOS, UNIX<sup>®</sup>, OS/2<sup>®</sup>, Solaris<sup>®</sup>, and others

The MediaGX™ MMX™-Enhanced Processor, in combination with the Cx5520 or Cx5530 I/O Companion chip provides advanced video and audio functions and permits direct interface to memory. This high-performance 64-bit processor is x86 instruction set compatible and supports MMX technology.

This processor is the latest member of the Cyrix MediaGX family, offering high performance, fully accelerated 2D graphics, a synchronous memory interface and a PCI bus controller, all on a single chip. As described in separate manuals, the Cx5520 and Cx5530 I/O Companion chips enable the full features of the MediaGX processor with MMX support. These features include full VGA and VESA video, 16-bit stereo sound, IDE interface, ISA interface, SMM power management, and AT compatibility logic. In addition, the newer Cx5530 provides an Ultra DMA/33 interface, MPEG2 assist, and is AC97 Version 2.0 compliant audio.

**Internal Block Diagram**

# MediaGX<sup>TM</sup> MMX<sup>TM</sup>-Enhanced Processor Integrated x86 Solution with MMX Support

## **Table of Contents**

| 1 | Ove  | rview                                             |

|---|------|---------------------------------------------------|

|   | 1.1  | Architecture                                      |

|   |      | 1.1.1 Integer Unit                                |

|   |      | 1.1.2 Floating Point Unit                         |

|   |      | 1.1.3 Write-Back Cache Unit                       |

|   |      | 1.1.4 Memory Management Unit                      |

|   |      | 1.1.5 Internal Bus Interface Unit                 |

|   | 1.2  | Integrated Functions                              |

|   |      | 1.2.1 Graphics Accelerator                        |

|   |      | 1.2.2 Display Controller                          |

|   |      | 1.2.3 XpressRAM™ Memory Subsystem                 |

|   |      | 1.2.4 PCI Controller                              |

|   | 1.3  | System Designs                                    |

| 2 | Sign | al Definitions                                    |

|   | 2.1  | Pin Assignments                                   |

|   | 2.2  | Signal Descriptions                               |

|   |      | 2.2.1 System Interface Signals                    |

|   |      | 2.2.2 PCI Interface Signals                       |

|   |      | 2.2.3 Memory Controller Interface Signals         |

|   |      | 2.2.4 Video Interface Signals                     |

|   |      | 2.2.5 Power, Ground, and No Connect Signals       |

|   |      | 2.2.6 Cyrix Internal Test and Measurement Signals |

|   | 2.3  | Subsystem Signal Connections                      |

|   | 2.4  | Power Planes                                      |

| 3 | Proc | essor Programming                                 |

|   | 3.1  | Core Processor Initialization                     |

|   | 3.2  | Instruction Set Overview                          |

|   |      | 3.2.1 Lock Prefix                                 |

| 3.3  | Register Sets                                       |

|------|-----------------------------------------------------|

|      | 3.3.1 Application Register Set                      |

|      | 3.3.2 System Register Set                           |

|      | 3.3.3 Model Specific Register                       |

|      | 3.3.4 Time Stamp Counter                            |

| 3.4  | Address Spaces                                      |

|      | 3.4.1 I/O Address Space                             |

|      | 3.4.2 Memory Address Space                          |

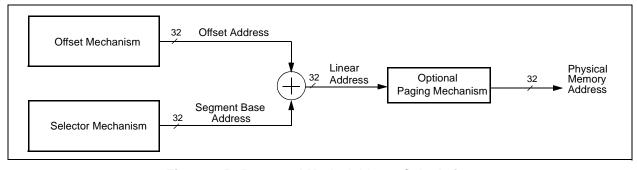

| 3.5  | Offset, Segment, and Paging Mechanisms              |

| 3.6  | Offset Mechanism                                    |

| 3.7  | Descriptors and Segment Mechanisms                  |

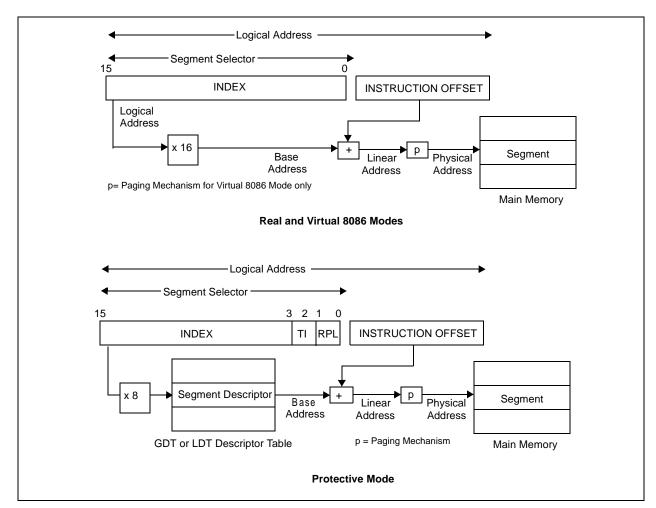

|      | 3.7.1 Real and Virtual 8086 Mode Segment Mechanisms |

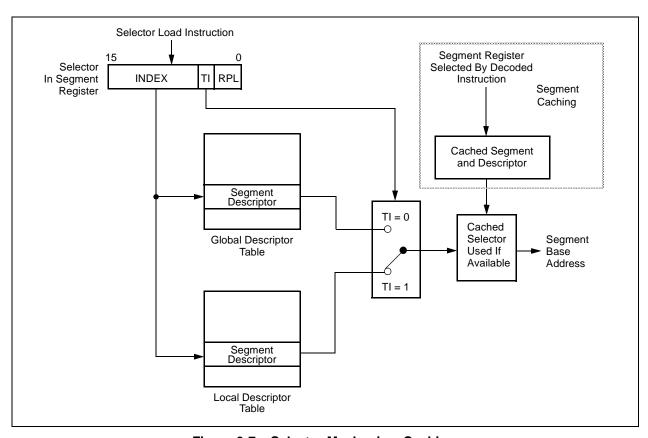

|      | 3.7.2 Segment Mechanism in Protective Mode          |

|      | 3.7.3 GDTR and LDTR Registers                       |

|      | 3.7.4 Descriptor Bit Structure                      |

|      | 3.7.5 Gate Descriptors                              |

| 3.8  | Multitasking and Task State Segments                |

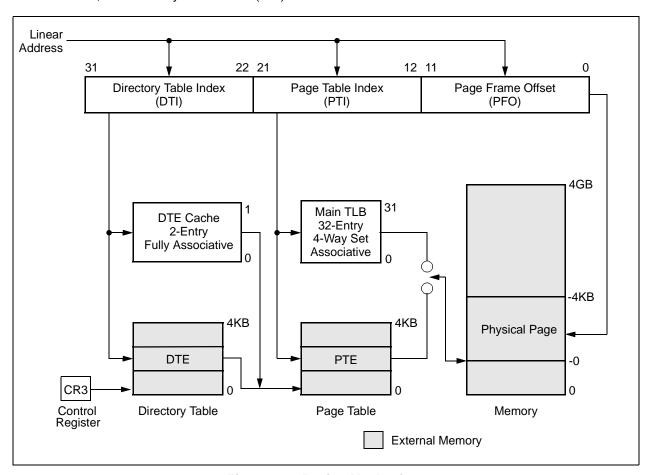

| 3.9  | Paging Mechanism                                    |

| 3.10 | Interrupts and Exceptions                           |

|      | 3.10.1 Interrupts                                   |

|      | 3.10.2 Exceptions                                   |

|      | 3.10.3 Interrupt Vectors                            |

|      | 3.10.4 Interrupt and Exception Priorities           |

|      | 3.10.5 Exceptions in Real Mode                      |

|      | 3.10.6 Error Codes                                  |

| 3.11 | System Management Mode                              |

|      | 3.11.1 SMM Enhancements                             |

|      | 3.11.2 SMM Operation                                |

|      | 3.11.3 The SMI# Pin                                 |

|      | 3.11.4 SMM Configuration Registers                  |

|      | 3.11.5 SMM Memory Space Header                      |

|      | 3.11.6 SMM Instructions                             |

|      | 3.11.7 SMM Memory Space                             |

|      | 3.11.8 SMI Generation                               |

|      | 3.11.9 SMI Service Routine Execution                |

| 3.12 | Shutdown and Halt                                   |

|   | 3.13 | Protection                                             |

|---|------|--------------------------------------------------------|

|   |      | 3.13.1 Privilege Levels                                |

|   |      | 3.13.2 I/O Privilege Levels                            |

|   |      | 3.13.3 Privilege Level Transfers                       |

|   |      | 3.13.4 Initialization and Transition to Protected Mode |

|   | 3.14 | Virtual 8086 Mode                                      |

|   |      | 3.14.1 Memory Addressing                               |

|   |      | 3.14.2 Protection                                      |

|   |      | 3.14.3 Interrupt Handling                              |

|   |      | 3.14.4 Entering and Leaving Virtual 8086 Mode          |

|   | 3.15 | Floating Point Unit Operations                         |

|   |      | 3.15.1 FPU (Floating Point Unit) Register Set          |

|   |      | 3.15.2 FPU Tag Word Register                           |

|   |      | 3.15.3 FPU Status Register                             |

|   |      | 3.15.4 FPU Mode Control Register                       |

|   | 14   | unated Francisco                                       |

| 4 | _    | grated Functions                                       |

|   | 4.1  | Integrated Functions Programming Interface             |

|   |      | 4.1.1 Graphics Control Register                        |

|   |      | 4.1.2 Control Registers                                |

|   |      | 4.1.3 Graphics Memory                                  |

|   |      | 4.1.4 L1 Cache Controller                              |

|   |      | 4.1.5 Display Driver Instructions                      |

|   | 4.0  | 4.1.6 CPU_READ/CPU_WRITE Instructions                  |

|   | 4.2  | Internal Bus Interface Unit                            |

|   |      | 4.2.1 FPU Error Support                                |

|   |      | 4.2.2 A20M Support                                     |

|   |      | 4.2.3 SMI Generation                                   |

|   |      | 4.2.4 640KB to 1MB Region                              |

|   |      | 4.2.5 Internal Bus Interface Unit Registers            |

|   | 4.3  | Memory Controller                                      |

|   |      | 4.3.1 Memory Array Configuration                       |

|   |      | 4.3.2 Memory Organizations                             |

|   |      | 4.3.3 SDRAM Commands                                   |

|   |      | 4.3.4 Memory Controller Register Description           |

|   |      | 4.3.5 Address Translation                              |

|   |      | 4.3.6 Memory Cycles                                    |

|   |      | 4.3.7 SDRAM Interface Clocking                         |

|       | 0 11 51 11                                        |

|-------|---------------------------------------------------|

| 4.4   | Graphics Pipeline                                 |

|       | 4.4.1 BitBLT/Vector Engine                        |

|       | 4.4.2 Master/Slave Registers                      |

|       | 4.4.3 Pattern Generation                          |

|       | 4.4.4 Source Expansion                            |

|       | 4.4.5 Raster Operations                           |

|       | 4.4.6 Graphics Pipeline Register Descriptions     |

| 4.5   | Display Controller                                |

|       | 4.5.1 Display FIFO                                |

|       | 4.5.2 Compression Technology                      |

|       | 4.5.3 Motion Video Acceleration Support           |

|       | 4.5.4 Hardware Cursor                             |

|       | 4.5.5 Display Timing Generator                    |

|       | 4.5.6 Dither and Frame-Rate Modulation            |

|       | 4.5.7 Display Modes                               |

|       | 4.5.8 Graphics Memory Map                         |

|       | 4.5.9 Display Controller Registers                |

|       | 4.5.10 Memory Organization Registers              |

|       | 4.5.11 Timing Registers                           |

|       | 4.5.12 Cursor Position Registers                  |

|       | 4.5.13 Color Registers                            |

|       | 4.5.14 Palette Access Registers                   |

|       | 4.5.15 Cx5520/Cx5530 Display Controller Interface |

| 4.6   | PCI Controller                                    |

|       | 4.6.1 X-Bus PCI Slave                             |

|       | 4.6.2 X-Bus PCI Master                            |

|       | 4.6.3 PCI Arbiter                                 |

|       | 4.6.4 Generating Configuration Cycles             |

|       | 4.6.5 Generating Special Cycles                   |

|       | 4.6.6 PCI Configuration Space Control Registers   |

|       | 4.6.7 PCI Configuration Space Registers           |

|       | 4.6.8 PCI Cycles                                  |

|       | •                                                 |

| Virtu | ual Subsystem Architecture                        |

| 5.1   | Virtual VGA                                       |

|       | 5.1.1 Traditional VGA Hardware                    |

5

|   | 5.2  | MediaGX™ Virtual VGA                                 |

|---|------|------------------------------------------------------|

|   |      | 5.2.1 Datapath Elements                              |

|   |      | 5.2.2 Video Refresh                                  |

|   |      | 5.2.3 MediaGX VGA Hardware                           |

|   |      | 5.2.4 VGA Video BIOS                                 |

|   |      | 5.2.5 Virtual VGA Register Descriptions              |

| 6 | Pow  | er Management                                        |

|   | 6.1  | APM Support                                          |

|   | 6.2  | CPU Suspend Command Registers                        |

|   | 6.3  | Suspend Modulation                                   |

|   | 6.4  | 3-Volt Suspend Mode                                  |

|   | 6.5  | Suspend Mode and Bus Cycles                          |

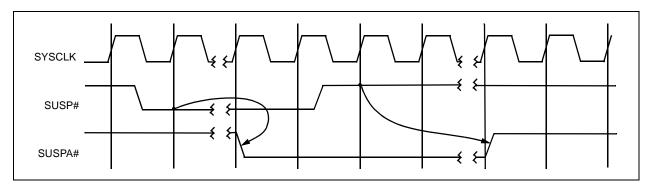

|   |      | 6.5.1 Initiating Suspend with SUSP#                  |

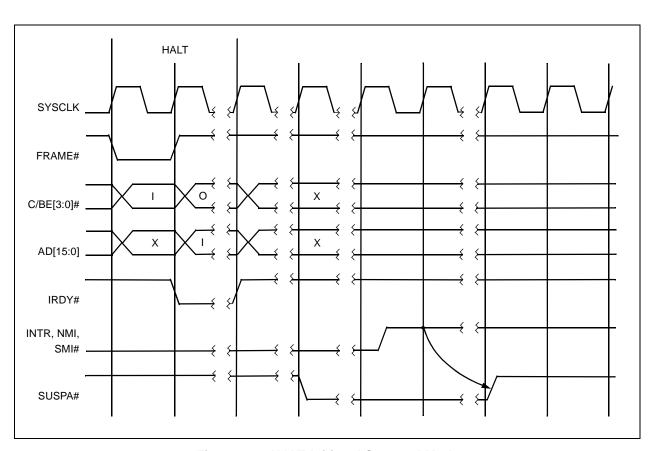

|   |      | 6.5.2 Initiating Suspend with HALT                   |

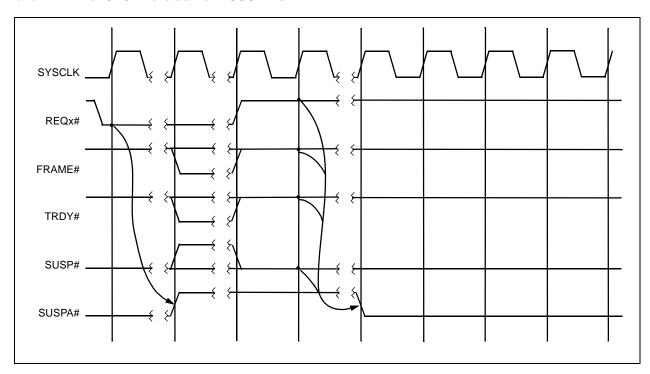

|   |      | 6.5.3 Responding to a PCI Access During Suspend Mode |

|   |      | 6.5.4 Stopping the Input Clock                       |

|   | 6.6  | MediaGX Processor Serial Bus                         |

|   |      | 6.6.1 Serial Packet Transmission                     |

|   | 6.7  | Power Management Registers                           |

| 7 | Flec | trical Specifications                                |

| • | 7.1  | Part Numbers                                         |

|   | 7.2  | Electrical Connections                               |

|   |      | 7.2.1 Power/Ground Connections and Decoupling        |

|   |      | 7.2.2 Power Sequencing the Core and I/O Voltages     |

|   |      | 7.2.3 NC-Designated Pins                             |

|   |      | 7.2.4 Pull-Up and Pull-Down Resistors                |

|   |      | 7.2.5 Unused Input Pins                              |

|   | 7.3  | Absolute Maximum Ratings                             |

|   | 7.4  | Recommended Operating Conditions                     |

|   | 7.5  | DC Characteristics                                   |

|   | 7.6  | AC Characteristics                                   |

| • | D    |                                                      |

| 8 |      | rage Specifications                                  |

|   | 8.1  | Thermal Characteristics                              |

|   | 8.2  | Mechanical Package Outlines                          |

| 9    | Instr | uction  | Set           |            |           |       |      |     |     |   | <br> |  |  |  | <br> |  |  |  | 233 |

|------|-------|---------|---------------|------------|-----------|-------|------|-----|-----|---|------|--|--|--|------|--|--|--|-----|

|      | 9.1   | Gener   | al Instruct   | ion Set I  | Format    |       |      |     |     |   | <br> |  |  |  |      |  |  |  | 234 |

|      |       | 9.1.1   | Prefix (Op    | otional)   |           |       |      |     |     |   | <br> |  |  |  |      |  |  |  | 235 |

|      |       | 9.1.2   | Opcode        |            |           |       |      |     |     |   |      |  |  |  |      |  |  |  | 235 |

|      |       | 9.1.3   | mod and       | r/m Byte   | (Memo     | ry Ad | ldre | ssi | ing | ) | <br> |  |  |  |      |  |  |  | 237 |

|      |       | 9.1.4   | reg Field     |            |           |       |      |     |     |   | <br> |  |  |  |      |  |  |  | 238 |

|      |       | 9.1.5   | s-i-b Byte    | (Scale,    | Indexing  | g, Ba | se)  |     |     |   |      |  |  |  |      |  |  |  | 239 |

|      | 9.2   | CPUID   | ) Instruction | on         |           |       |      |     |     |   |      |  |  |  |      |  |  |  | 240 |

|      |       | 9.2.1   | Standard      | CPUID      | Levels    |       |      |     |     |   |      |  |  |  |      |  |  |  | 241 |

|      |       | 9.2.2   | Extended      | CPUID      | Levels    |       |      |     |     |   |      |  |  |  |      |  |  |  | 243 |

|      | 9.3   | Proces  | ssor Core     | Instructi  | on Set    |       |      |     |     |   |      |  |  |  |      |  |  |  | 245 |

|      | 9.4   | FPU Ir  | nstruction    | Set        |           |       |      |     |     |   | <br> |  |  |  |      |  |  |  | 260 |

|      | 9.5   | $MMX^T$ | ™ Instructi   | on Set     |           |       |      |     |     |   |      |  |  |  |      |  |  |  | 266 |

|      | 9.6   | Cyrix I | Extended      | $MMX^{TM}$ | Instructi | on S  | et . |     |     |   |      |  |  |  |      |  |  |  | 272 |

| Appe | endix | Α       | Support       | Docume     | entation  |       |      |     |     |   | <br> |  |  |  | <br> |  |  |  | 275 |

|      |       |         | Order Info    |            |           |       |      |     |     |   |      |  |  |  |      |  |  |  |     |

|      |       | A.2     | Data Boo      | k Revisi   | on Histo  | rv .  |      |     |     |   |      |  |  |  |      |  |  |  | 276 |

## List of Figures and Tables

## List of Figures

| Figure 1-1  | Internal Block Diagram                            |

|-------------|---------------------------------------------------|

| Figure 1-2  | System Block Diagram                              |

| Figure 1-3  | Cx9210 Interface System Diagram                   |

| Figure 2-1  | Functional Block Diagram                          |

| Figure 2-2  | 352 BGA Pin Assignment Diagram                    |

| Figure 2-3  | 320 SPGA Pin Assignment Diagram                   |

| Figure 2-4  | Subsystem Signal Connections                      |

| Figure 2-5  | PIXEL Signal Connections                          |

| Figure 2-6  | BGA Recommended Split Power Plane and Decoupling  |

| Figure 2-7  | SPGA Recommended Split Power Plane and Decoupling |

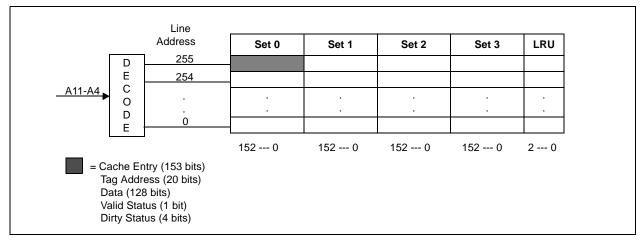

| Figure 3-1  | CPU Cache Architecture                            |

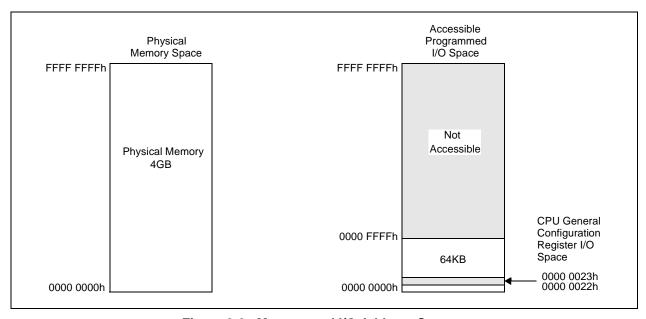

| Figure 3-2  | Memory and I/O Address Spaces                     |

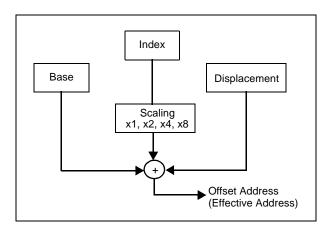

| Figure 3-3  | Offset Address Calculation                        |

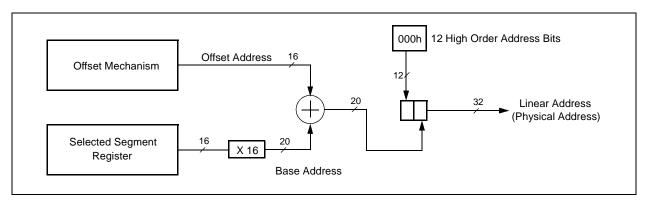

| Figure 3-4  | Real Mode Address Calculation                     |

| Figure 3-5  | Protected Mode Address Calculation                |

| Figure 3-6  | Selector Mechanisms                               |

| Figure 3-7  | Selector Mechanism Caching                        |

| Figure 3-8  | Paging Mechanism                                  |

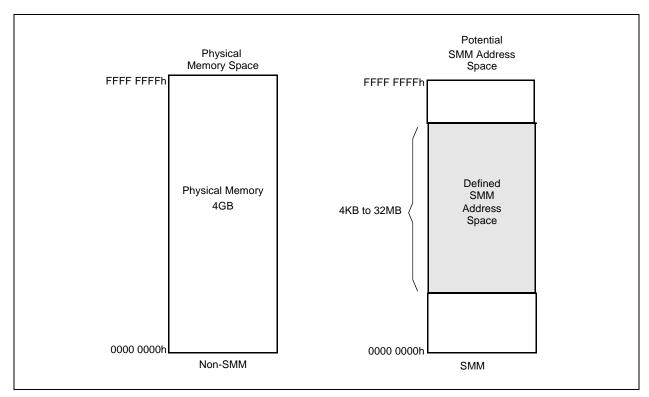

| Figure 3-9  | System Management Memory Address Space            |

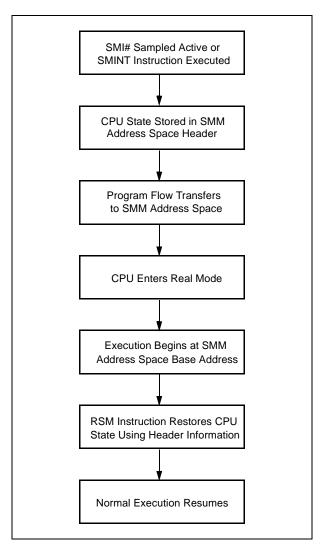

| Figure 3-10 | SMM Execution Flow                                |

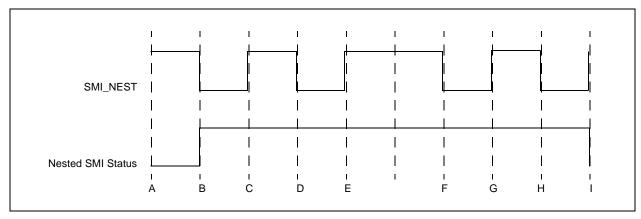

| Figure 3-11 | SMI Nesting State Machine                         |

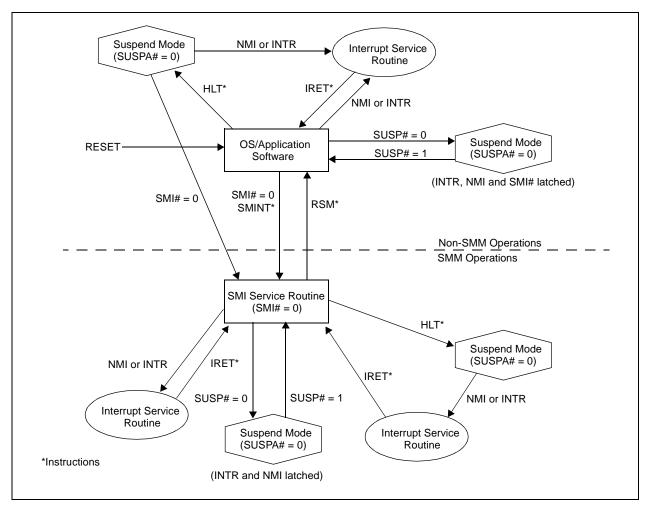

| Figure 3-12 | SMM and Suspend Mode State Diagram                |

| Figure 4-1  | Internal Block Diagram                            |

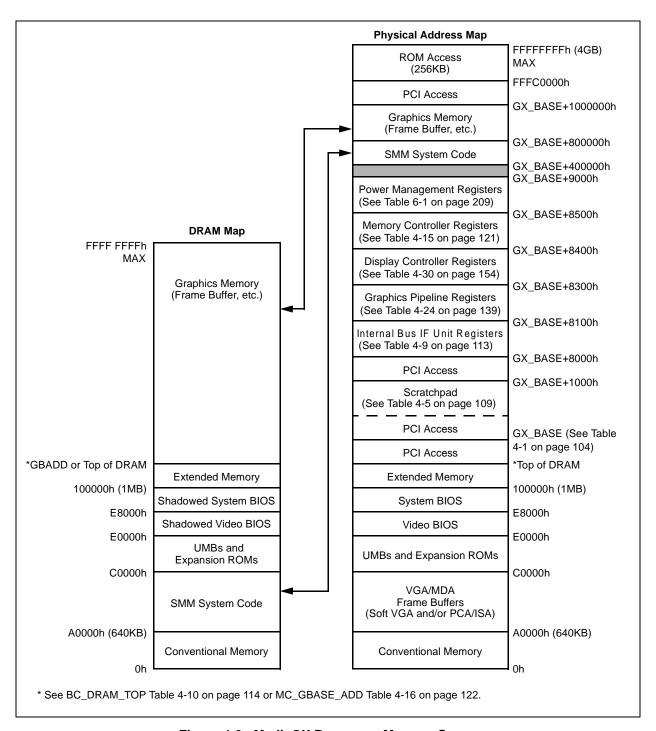

| Figure 4-2  | MediaGX Processor Memory Space                    |

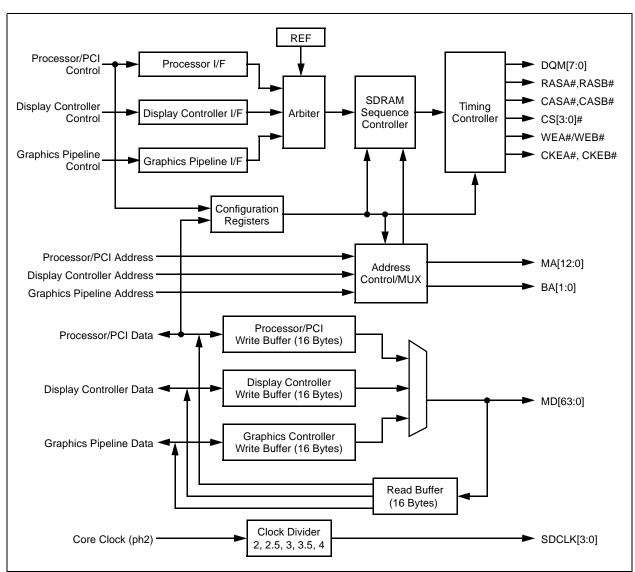

| Figure 4-3  | Memory Controller Block Diagram                   |

| Figure 4-4  | Memory Array Configuration                        |

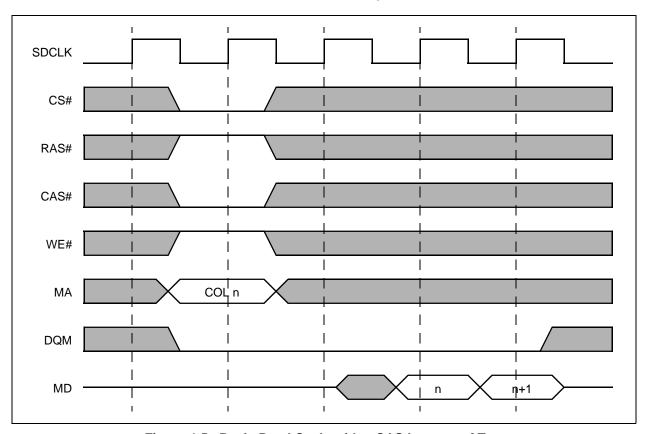

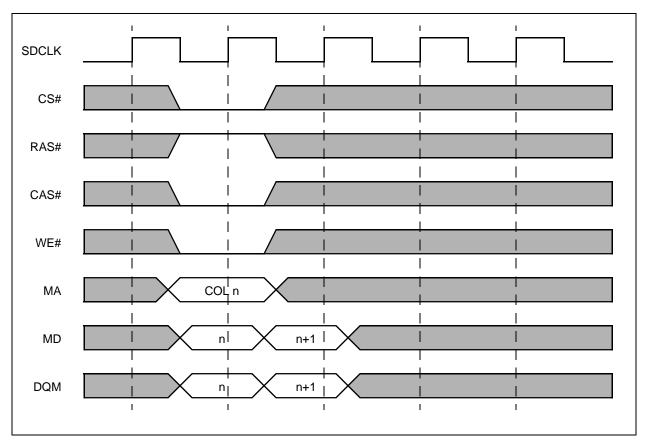

| Figure 4-5  | Basic Read Cycle with a CAS Latency of Two        |

| Figure 4-6  | Basic Write Cycle                                 |

| Figure 4-7  | Auto Refresh Cycle                                |

| Figure 4-8  | Read/Write Command to a New Row Address           |

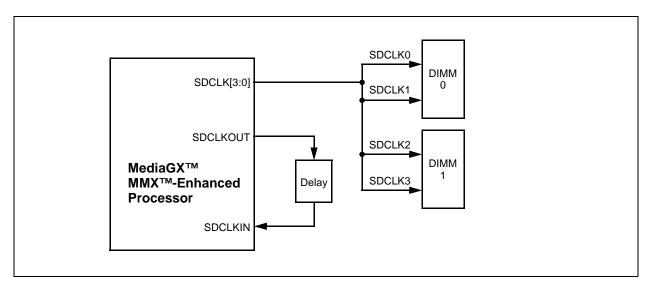

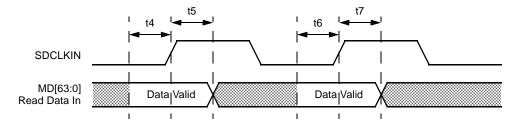

| Figure 4-9  | SDCLKIN Clocking                                  |

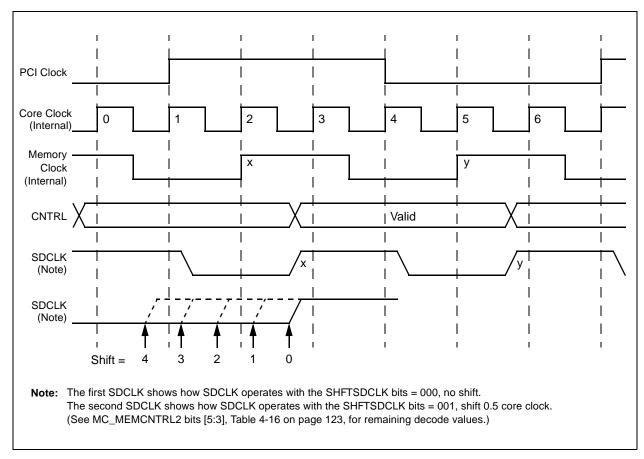

| Figure 4-10 | Effects of SHFTSDCLK Programming Bits Example     |

| Figure 4-11 | Graphics Pipeline Block Diagram                   |

| Figure 4-12 | Example of Monochrome Patterns                    |

| Figure 4-13 | Example of Dither Patterns                        |

| Figure 4-14 | Display Controller Block Diagram                                 |

|-------------|------------------------------------------------------------------|

| Figure 4-15 | Pixel Arrangement Within a DWORD                                 |

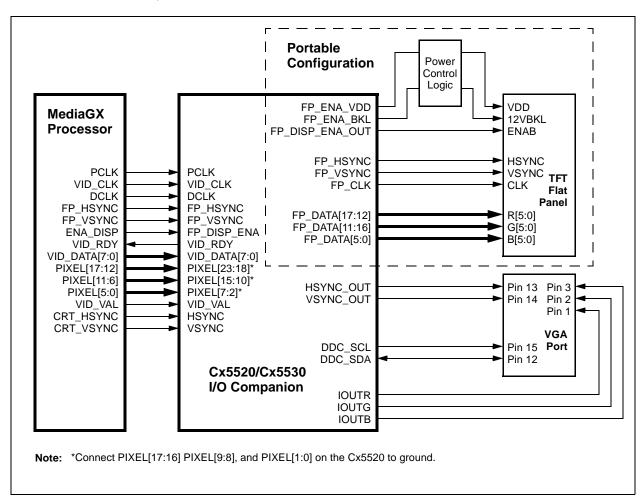

| Figure 4-16 | Display Controller Signal Connections                            |

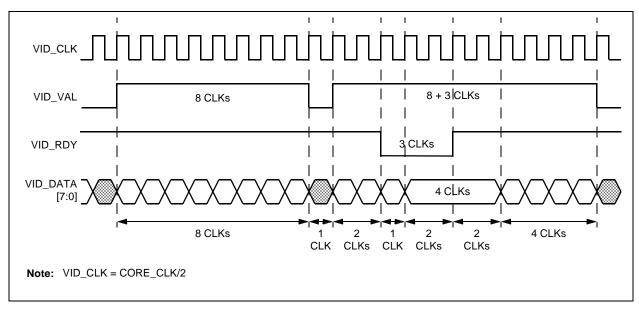

| Figure 4-17 | Video Port Data Transfer (Cx5520/Cx5530)                         |

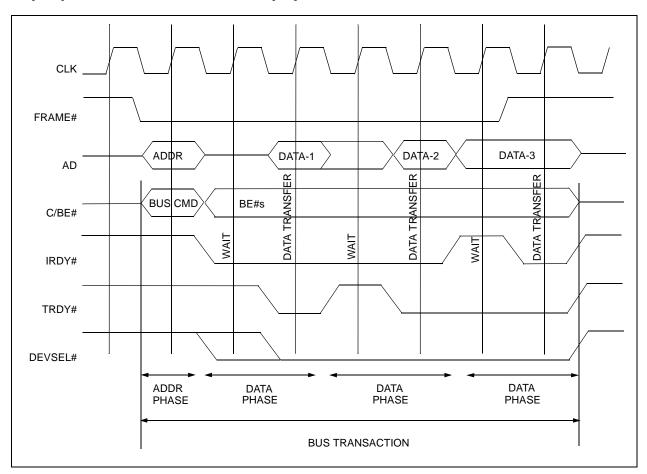

| Figure 4-18 | Basic Read Operation                                             |

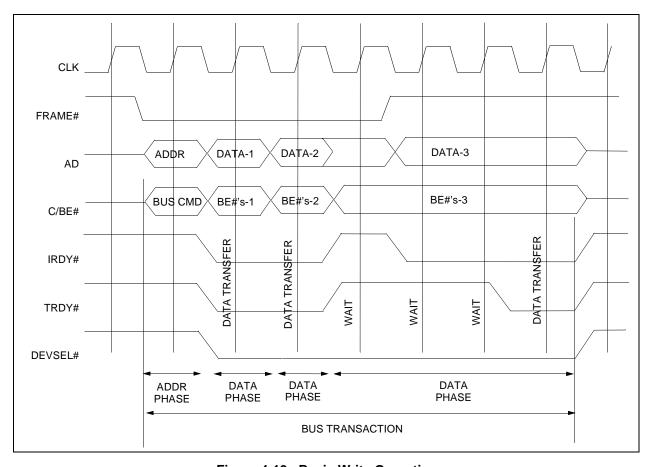

| Figure 4-19 | Basic Write Operation                                            |

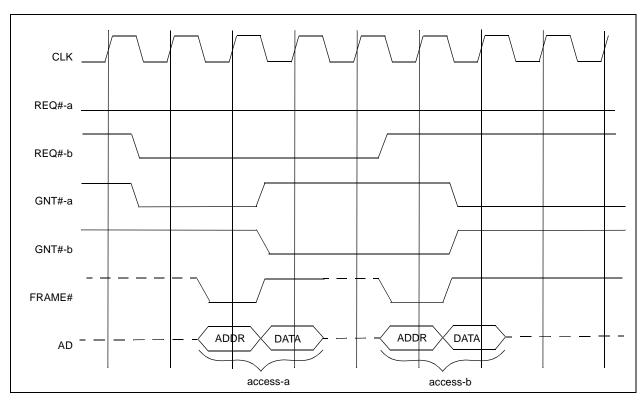

| Figure 4-20 | Basic Arbitration                                                |

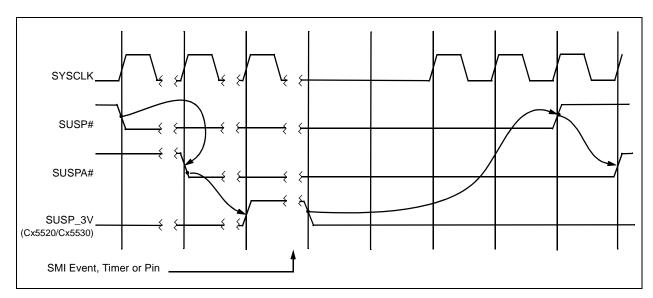

| Figure 6-1  | SUSP#-Initiated Suspend Mode                                     |

| Figure 6-2  | HALT-Initiated Suspend Mode                                      |

| Figure 6-3  | PCI Access During Suspend Mode                                   |

| Figure 6-4  | Stopping SYSCLK During Suspend Mode                              |

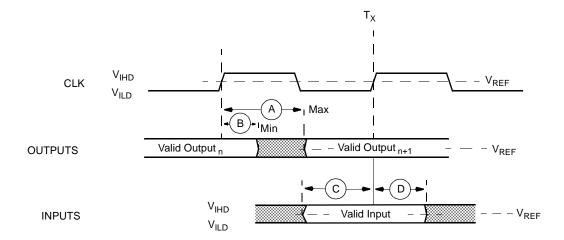

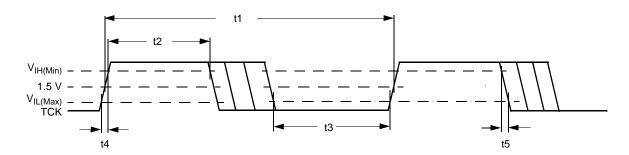

| Figure 7-1  | Drive Level and Measurement Points for Switching Characteristics |

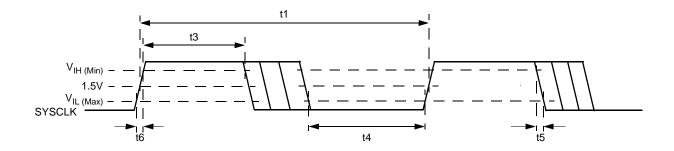

| Figure 7-2  | SYSCLK Timing and Measurement Points                             |

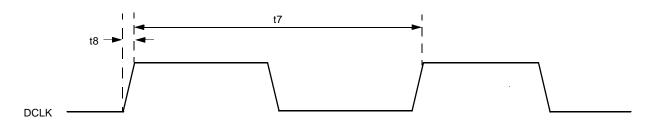

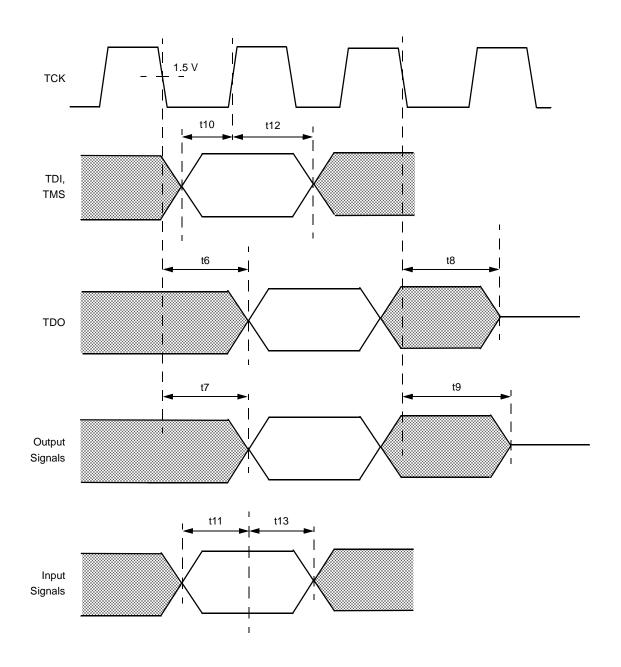

| Figure 7-3  | DCLK Timing and Measurement Points                               |

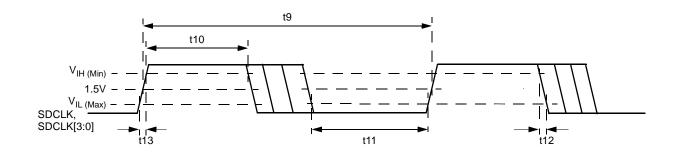

| Figure 7-4  | SDCLK, SDCLK[3:0] Timing and Measurement Points                  |

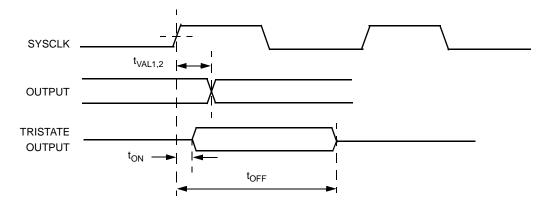

| Figure 7-5  | Output Timing                                                    |

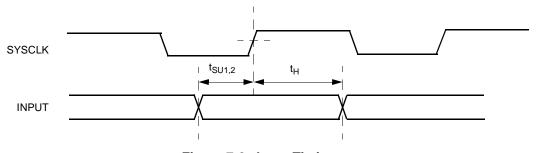

| Figure 7-6  | Input Timing                                                     |

| Figure 7-7  | Output Valid Timing                                              |

| Figure 7-8  | Setup and Hold Timings - Read Data In                            |

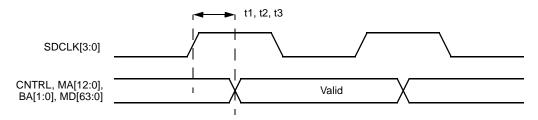

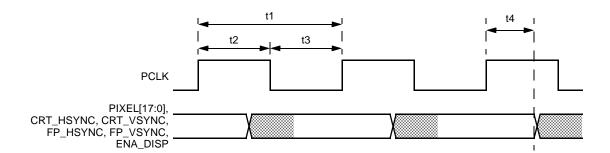

| Figure 7-9  | Graphics Port Timing                                             |

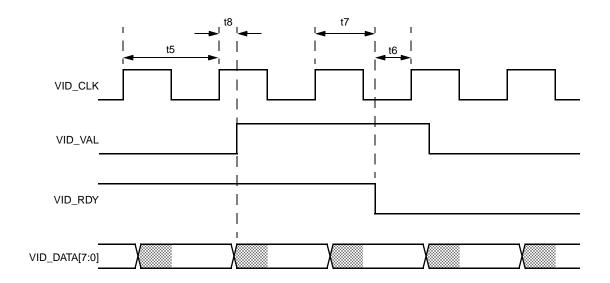

| Figure 7-10 | Video Port Timing                                                |

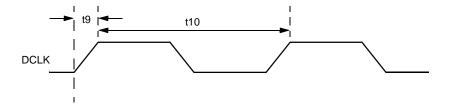

| Figure 7-11 | DCLK Timing                                                      |

| Figure 7-12 | TCK Timing and Measurement Points                                |

| Figure 7-13 | JTAG Test Timings                                                |

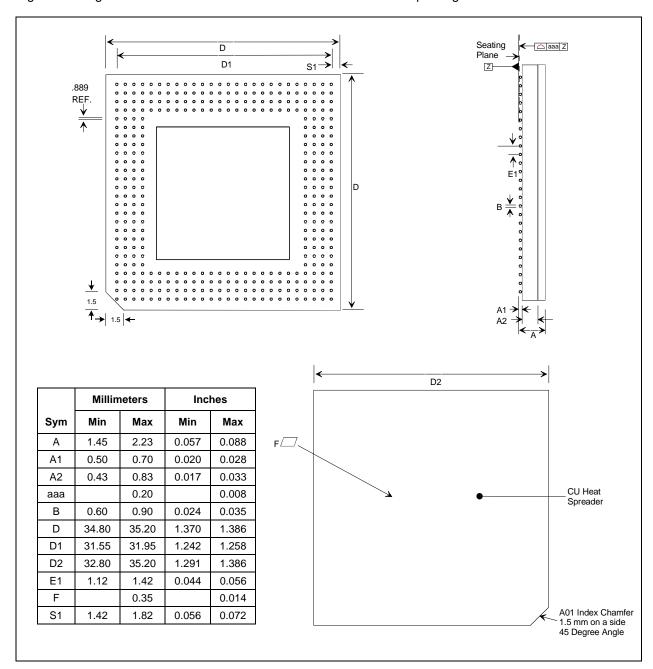

| Figure 8-1  | 352-Terminal BGA Mechanical Package Outline                      |

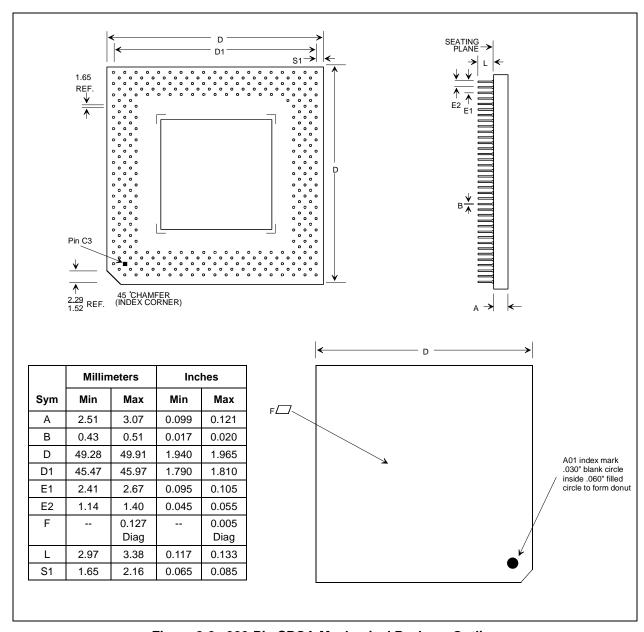

| Figure 8-2  | 320-Pin SPGA Mechanical Package Outline                          |

## List of Figures and Tables

## **List of Tables**

| Table 2-1  | Pin Type Definitions                                            |

|------------|-----------------------------------------------------------------|

| Table 2-2  | 352 BGA Pin Assignments - Sorted by Pin Number                  |

| Table 2-3  | 352 BGA Pin Assignments - Sorted Alphabetically by Signal Name  |

| Table 2-4  | 320 SPGA Pin Assignments - Sorted by Pin Number                 |

| Table 2-5  | 320 SPGA Pin Assignments - Sorted Alphabetically by Signal Name |

| Table 3-1  | Initialized Core Register Controls                              |

| Table 3-2  | Application Register Set                                        |

| Table 3-3  | Segment Register Selection Rules                                |

| Table 3-4  | EFLAGS Register                                                 |

| Table 3-5  | System Register Set                                             |

| Table 3-6  | Control Registers Map                                           |

| Table 3-7  | CR4-CR0 Bit Definitions                                         |

| Table 3-8  | Effects of Various Combinations of EM, TS, and MP Bits          |

| Table 3-9  | Configuration Register Summary                                  |

| Table 3-10 | Configuration Register Map                                      |

| Table 3-11 | Configuration Registers                                         |

| Table 3-12 | Debug Registers                                                 |

| Table 3-13 | DR7 and DR6 Bit Definitions                                     |

| Table 3-14 | Test Registers                                                  |

| Table 3-15 | TR7-TR6 Bit Definitions                                         |

| Table 3-16 | TR5-TR3 Bit Definitions                                         |

| Table 3-17 | Cache Test Operations                                           |

| Table 3-18 | Memory Addressing Modes                                         |

| Table 3-19 | GDTR, LDTR and IDTR Registers                                   |

| Table 3-20 | Application and System Segment Descriptors                      |

| Table 3-21 | Application and System Segment Descriptors Bit Definitions      |

| Table 3-22 | Application and System Segment Descriptors TYPE Bit Definitions |

| Table 3-23 | Gate Descriptors                                                |

| Table 3-24 | Gate Descriptors Bit Definitions                                |

| Table 3-25 | 32-Bit Task State Segment (TSS) Table                           |

| Table 3-26 | 16-Bit Task State Segment (TSS) Table                           |

| Table 3-27 | Directory Table Entry (DTE) and Page Table Entry (PTE)          |

| Table 3-28 | Interrupt Vector Assignments                                    |

| Table 3-29 | Interrupt and Exception Priorities                              |

| Table 3-30 | Exception Changes in Real Mode                                  |

| Table 3-31 | Error Codes                                              |

|------------|----------------------------------------------------------|

| Table 3-32 | Error Code Bit Definitions                               |

| Table 3-33 | SMI# and SMINT Recognition Requirements                  |

| Table 3-34 | SMM Memory Space Header                                  |

| Table 3-35 | SMM Memory Space Header Description                      |

| Table 3-36 | SMM Instruction Set                                      |

| Table 3-37 | Descriptor Types Used for Control Transfer               |

| Table 3-38 | FPU Registers                                            |

| Table 4-1  | GCR Register                                             |

| Table 4-2  | Display Resolution Skip Counts                           |

| Table 4-3  | L1 Cache BitBLT Register Summary                         |

| Table 4-4  | L1 Cache BitBLT Registers                                |

| Table 4-5  | Scratchpad Organization                                  |

| Table 4-6  | Display Driver Instructions                              |

| Table 4-7  | CPU-Access Instructions                                  |

| Table 4-8  | Address Map for CPU-Access Registers                     |

| Table 4-9  | Internal Bus Interface Unit Register Summary             |

| Table 4-10 | Internal Bus Interface Unit Registers                    |

| Table 4-11 | Region-Control-Field Bit Definitions                     |

| Table 4-12 | Synchronous DRAM Configurations                          |

| Table 4-13 | Basic Command Truth Table                                |

| Table 4-14 | Address Line Programming during MRS Cycles               |

| Table 4-15 | Memory Controller Register Summary                       |

| Table 4-16 | Memory Controller Registers                              |

| Table 4-17 | Auto LOI 2 DIMMs, Same Size, 1 DIMM Bank                 |

| Table 4-18 | Auto LOI 2 DIMMs, Same Size, 2 DIMM Banks                |

| Table 4-19 | Non-Auto LOI 1 or 2 DIMMs, Different Sizes, 1 DIMM Bank  |

| Table 4-20 | Non-Auto LOI 1 or 2 DIMMs, Different Sizes, 2 DIMM Banks |

| Table 4-21 | Graphics Pipeline Registers                              |

| Table 4-22 | GP_RASTER_MODE Bit Patterns                              |

| Table 4-23 | Common Raster Operations                                 |

| Table 4-24 | Graphics Pipeline Configuration Register Summary         |

| Table 4-25 | Graphics Pipeline Configuration Registers                |

| Table 4-26 | TFT Panel Display Modes                                  |

| Table 4-27 | TFT Panel Data Bus Formats                               |

## List of Figures and Tables

| Table 4-28 | CRT RAMDAC Data Bus Formats                                      |

|------------|------------------------------------------------------------------|

| Table 4-29 | CRT Display Modes                                                |

| Table 4-30 | Display Controller Register Summary                              |

| Table 4-31 | Display Controller Configuration and Status Registers            |

| Table 4-32 | Display Controller Memory Organization Registers                 |

| Table 4-33 | Display Controller Timing Registers                              |

| Table 4-34 | Display Controller Cursor Position Registers                     |

| Table 4-35 | Display Controller Color Registers                               |

| Table 4-36 | Display Controller Palette and RAM Diagnostic Registers          |

| Table 4-37 | Special-Cycle Code to CONFIG_ADDRESS                             |

| Table 4-38 | PCI Configuration Registers                                      |

| Table 4-39 | Format for Accessing the Internal PCI Configuration Registers    |

| Table 4-40 | PCI Configuration Space Register Summary                         |

| Table 4-41 | PCI Configuration Registers                                      |

| Table 5-1  | Standard VGA Modes                                               |

| Table 5-2  | VGA Configuration Registers Summary                              |

| Table 5-3  | VGA Configuration Registers                                      |

| Table 5-4  | Virtual VGA Register Summary                                     |

| Table 5-5  | Virtual VGA Registers                                            |

| Table 6-1  | Power Management Register Summary                                |

| Table 6-2  | Power Management Control and Status Registers                    |

| Table 6-3  | Power Management Programmable Address Region Registers           |

| Table 7-1  | Part Numbers                                                     |

| Table 7-2  | Pins with 20-kohm Internal Resistor                              |

| Table 7-3  | Absolute Maximum Ratings                                         |

| Table 7-4  | Recommended Operating Conditions                                 |

| Table 7-5  | DC Characteristics (at Recommended Operating Conditions)         |

| Table 7-6  | Drive Level and Measurement Points for Switching Characteristics |

| Table 7-7  | Clock Signals                                                    |

| Table 7-8  | System Signals                                                   |

| Table 7-9  | PCI Interface Signals                                            |

| Table 7-10 | SDRAM Interface Signals                                          |

| Table 7-11 | Video Interface Signals                                          |

| Table 7-12 | JTAG AC Specification                                            |

| Table 8-1  | Case to Ambient Thermal Resistance Examples for 70°C Product     |

| Table 8-2  | Case to Ambient Thermal Resistance Examples for 85°C Product | 228 |

|------------|--------------------------------------------------------------|-----|

| Table 8-3  | Mechanical Package Outline Legend                            | 231 |

| Table 9-1  | General Instruction Set Format                               | 234 |

| Table 9-2  | Instruction Fields                                           | 234 |

| Table 9-3  | Instruction Prefix Summary                                   | 235 |

| Table 9-4  | w Field Encoding                                             | 235 |

| Table 9-5  | d Field Encoding                                             | 236 |

| Table 9-6  | s Field Encoding                                             | 236 |

| Table 9-7  | eee Field Encoding                                           | 236 |

| Table 9-8  | General Registers Selected by mod r/m Fields and w Field     | 237 |

| Table 9-9  | mod r/m Field Encoding                                       | 237 |

| Table 9-10 | General Registers Selected by reg Field                      | 238 |

| Table 9-11 | sreg2 Field Encoding                                         | 238 |

| Table 9-12 | sreg3 Field Encoding                                         | 238 |

| Table 9-13 | ss Field Encoding                                            | 239 |

| Table 9-14 | index Field Encoding                                         | 239 |

| Table 9-15 | mod base Field Encoding                                      | 239 |

| Table 9-16 | CPUID Levels Summary                                         | 240 |

| Table 9-17 | CPUID Data Returned when EAX = 0                             | 241 |

| Table 9-18 | EAX, EBX, ECX CPUID Data Returned when EAX = 1               | 241 |

| Table 9-19 | EDX CPUID Data Returned when EAX = 1                         | 242 |

| Table 9-20 | Standard CPUID with EAX = 0000 0002h                         | 242 |

| Table 9-21 | Maximum Extended CPUID Level                                 | 243 |

| Table 9-22 | EAX, EBX, ECX CPUID Data Returned when EAX = 8000 0001h      | 243 |

| Table 9-23 | EDX CPUID Data Returned when EAX = 8000 0001h                | 243 |

| Table 9-24 | Official CPU Name                                            | 244 |

| Table 9-25 | Standard CPUID with EAX = 8000 0005h                         | 244 |

| Table 9-26 | Processor Core Instruction Set Table Legend                  | 245 |

| Table 9-27 | Processor Core Instruction Set Summary                       | 246 |

| Table 9-28 | FPU Instruction Set Table Legend                             | 260 |

| Table 9-29 | FPU Instruction Set Summary                                  | 261 |

| Table 9-30 | MMX Instruction Set Table Legend                             | 266 |

| Table 9-31 | MMX Instruction Set Summary                                  | 267 |

| Table 9-32 | Cyrix Extend MMX Instruction Set Table Legend                | 272 |

| Table 9-33 | Cyrix Extended MMX Instruction Set Summary                   | 273 |

#### MediaGX™ MMX™-Enhanced Processor

Integrated x86 Solution with MMX Support

#### 1 Overview

The Cyrix MediaGX<sup>TM</sup> MMX<sup>TM</sup>-Enhanced Processor is the latest member of the Cyrix MediaGX processor family. It is an advanced 64-bit x86 compatible processor offering high performance, fully accelerated 2D graphics, a 64-bit synchronous DRAM controller and a PCI bus controller, all on a single chip. Plus it is compatible with MMX<sup>TM</sup> technology. This latest generation of the MediaGX processor enables a new class of low cost, premium performance notebook/desktop computer designs.

The MediaGX processor core is a proven design that offers competitive CPU performance. It has integer and floating point execution units that are based on sixth-generation technology. The integer core contains a single, six-stage execution pipeline and offers advanced features such as operand forwarding, branch target buffers, and extensive write buffering. A 16KB write-back L1 cache is accessed in a unique fashion that eliminates pipeline stalls to fetch operands that hit in the cache.

In addition to the advanced CPU features, the MediaGX processor integrates a host of functions which are typically implemented with external components. A full-function graphics accelerator provides pixel processing and rendering functions.

A separate on-chip video buffer enables >30FPS MPEG1 video playback when used together with either the Cx5520™ or Cx5530™ I/O Companion chip. Graphics and system memory accesses are supported by a tightly-coupled synchronous DRAM (SDRAM) memory controller. This tightly coupled memory subsystem eliminates the need for an external L2 cache.

The MediaGX processor includes Cyrix's Virtual System Architecture<sup>™</sup> (VSA<sup>™</sup>) enabling Xpress-GRAPHICS<sup>™</sup> and XpressAUDIO<sup>™</sup> as well as generic emulation capabilities. Software handler routines for XpressGRAPHICS and XpressAUDIO are included in the BIOS and provide compatible VGA and 16-bit industry standard audio emulation. XpressAUDIO technology eliminates much of the hardware traditionally associated with audio functions.

#### **General Features**

- · Packaged in:

- 352-Terminal Ball Grid Array (BGA) or

- 320-Pin Staggered Pin Grid Array (SPGA)

- 0.35-micron four layer metal CMOS process

- Split rail design (3.3V I/O and 2.9V core)

#### 64-Bit x86 Processor

- Supports the MMX<sup>™</sup> instruction set extension for the acceleration of multimedia applications

- · Speeds offered up to 300MHz

- 16KB unified L1 cache

- Integrated Floating Point Unit (FPU)

- Re-entrant System Management Mode (SMM) enhanced for the Cyrix Virtual System Architecture

#### **PCI Controller**

- Fixed, rotating, hybrid, or ping-pong arbitration

- Supports up to three PCI bus masters

- Synchronous CPU and PCI bus clock frequency

- Supports concurrency between PCI master and L1 cache

#### **Power Management**

- Designed to support Cx5520/Cx5530 power management architecture

- CPU only Suspend or full 3V Suspend supported:

- Clocks to CPU core stopped for CPU Suspend

- All on-chip clocks stopped for 3V Suspend

- Suspend refresh supported for 3V Suspend

#### Virtual Systems Architecture™

- New architecture allowing OS independent (software) virtualization of hardware functions

- Provides compatible high performance legacy VGA core functionality

**Note:** GUI (Graphical User Interface) graphics acceleration is pure hardware.

Provides Cyrix's 16-bit XpressAUDIO™

#### 2D Graphics Accelerator

- Graphics pipeline performance significantly increased over previous generations by pipelining burst reads/writes

- · Accelerates BitBLTs, line draw, text

- Supports all 256 raster operations

- Supports transparent BLTs

- Runs at core clock frequency

- · Full VGA and VESA mode support

- Special "Driver level" instructions utilize internal scratchpad for enhanced performance

#### **Display Controller**

- Video Generator (VG) improves memory efficiency for display refresh with SDRAM

- Supports a separate MPEG1 video buffer and data path to enable video acceleration in the Cx5520

- Supports a separate MPEG2 video buffer and data path to enable video acceleration in the Cx5530

- Internal palette RAM for use with the Cx5520/Cx5530

- Direct interface to Cx5520/Cx5530 for CRT and TFT flat panel support which eliminates need for external RAMDAC

- Hardware frame buffer compressor/decompressor

- Hardware cursor

- Supports up to 1280x1024x8 BPP and 1024x768x16 BPP

#### XpressRAM™ Memory Subsystem

- · Memory control/interface directly from CPU

- 64-Bit wide memory bus

- SDRAM bus operating frequency range of 66 to 100MHz

- Support for:

- Two 168-pin unbuffered DIMMs

- Up to 16 open banks simultaneously

- Single or 16-byte reads (burst length of two)

- LVTTL technology compatible

#### 1.1 Architecture

The Cyrix MediaGX MMX-Enhanced Processor represents a new generation of x86-compatible 64-bit microprocessors with sixth-generation features. The decoupled load/store unit (within the memory management unit) allows multiple instructions in a single clock cycle. Other features include single-cycle execution, single-cycle instruction decode, 16KB write-back cache, and clock rates up to 300MHz. These features are made possible by the use of advanced-process technologies and superpipelining.

The MediaGX processor has low power consumption at all clock frequencies. Where additional power savings are required, designers can make use of Suspend mode, Stop Clock capability, and System Management Mode (SMM).

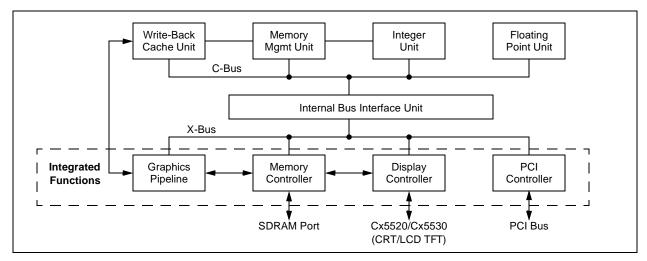

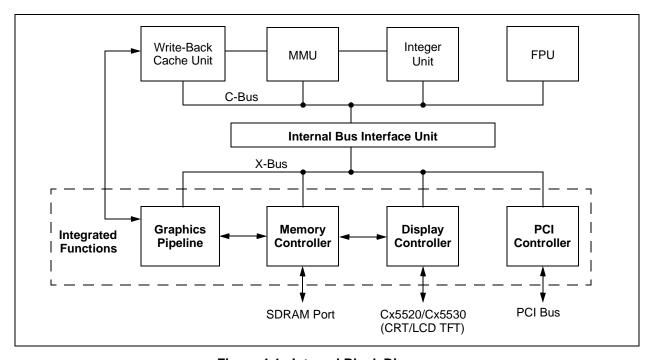

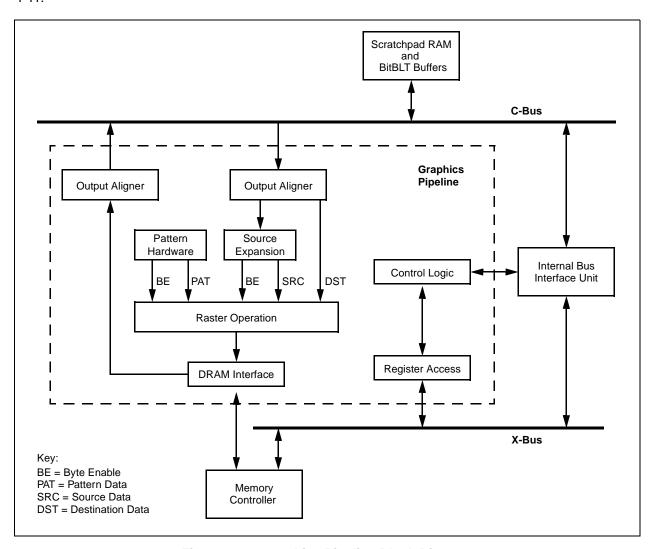

The MediaGX processor is divided into major functional blocks (as shown in Figure 1-1):

- · Integer Unit

- Floating Point Unit (FPU)

- · Write-Back Cache Unit

- Memory Management Unit (MMU)

- · Internal Bus Interface Unit

- Integrated Functions

Instructions are executed in the integer unit and in the floating point unit. The cache unit stores the most recently used data and instructions and provides fast access to this information for the integer and floating point units.

Figure 1-1 Internal Block Diagram

#### 1.1.1 Integer Unit

The integer unit consists of:

- · Instruction Buffer

- · Instruction Fetch

- Instruction Decoder and Execution

The superpipelined integer unit fetches, decodes, and executes x86 instructions through the use of a six-stage integer pipeline.

The instruction fetch pipeline stage generates, from the on-chip cache, a continuous high-speed instruction stream for use by the processor. Up to 128 bits of code are read during a single clock cycle.

Branch prediction logic within the prefetch unit generates a predicted target address for unconditional or conditional branch instructions. When a branch instruction is detected, the instruction fetch stage starts loading instructions at the predicted address within a single clock cycle. Up to 48 bytes of code are queued prior to the instruction decode stage.

The instruction decode stage evaluates the code stream provided by the instruction fetch stage and determines the number of bytes in each instruction and the instruction type. Instructions are processed and decoded at a maximum rate of one instruction per clock.

The address calculation function is super-pipelined and contains two stages, AC1 and AC2. If the instruction refers to a memory operand, AC1 calculates a linear memory address for the instruction.

The AC2 stage performs any required memory management functions, cache accesses, and register file accesses. If a floating point instruction is detected by AC2, the instruction is sent to the floating point unit for processing.

The execution stage, under control of microcode, executes instructions using the operands provided by the address calculation stage.

Write-back, the last stage of the integer unit, updates the register file within the integer unit or writes to the load/store unit within the memory management unit.

#### 1.1.2 Floating Point Unit

The FPU (Floating Point Unit) interfaces to the integer unit and the cache unit through a 64-bit bus. The FPU is x87-instruction-set compatible and adheres to the IEEE-754 standard. Because almost all applications that contain FPU instructions also contain integer instructions, the MediaGX processor's FPU achieves high performance by completing integer and FPU operations in parallel.

FPU instructions are dispatched to the pipeline within the integer unit. The address calculation stage of the pipeline checks for memory management exceptions and accesses memory operands for use by the FPU. Once the instructions and operands have been provided to the FPU, the FPU completes instruction execution independently of the integer unit.

#### 1.1.3 Write-Back Cache Unit

The 16KB write-back unified cache is a data/instruction cache and is configured as fourway set associative. The cache stores up to 16KB of code and data in 1024 cache lines.

The MediaGX processor provides the ability to allocate a portion of the L1 cache as a scratchpad, which is used to accelerate the Virtual Systems Architecture algorithms as well as for some graphics operations.

#### 1.1.4 Memory Management Unit

The memory management unit (MMU) translates the linear address supplied by the integer unit into a physical address to be used by the cache unit and the internal bus interface unit. Memory management procedures are x86-compatible, adhering to standard paging mechanisms.

The MMU also contains a load/store unit that is responsible for scheduling cache and external memory accesses. The load/store unit incorporates two performance-enhancing features:

- Load-store reordering that gives priority to memory reads required by the integer unit over writes to external memory.

- Memory-read bypassing that eliminates unnecessary memory reads by using valid data from the execution unit.

#### 1.1.5 Internal Bus Interface Unit

The internal bus interface unit provides a bridge from the MediaGX processor to the integrated system functions (i.e., memory subsystem, display controller, graphics pipeline) and the PCI bus interface.

When external memory access is required, the physical address is calculated by the memory management unit and then passed to the internal bus interface unit, which translates the cycle to an X-Bus cycle (the X-Bus is a Cyrix proprietary internal bus which provides a common interface for all of the system modules). The X-Bus memory cycle now is arbitrated between other pending X-Bus memory requests to the SDRAM controller before completing.

In addition, the internal bus interface unit provides configuration control for up to 20 different regions within system memory with separate controls for read access, write access, cacheability, and PCI access.

#### 1.2 Integrated Functions

The MediaGX processor integrates the following functions traditionally implemented using external devices:

- High-performance 2D graphics accelerator

- Separate CRT and TFT data paths from the display controller

- · SDRAM memory controller

- PCI bridge

The processor has also been enhanced to support Cyrix's proprietary Virtual System Architecture (VSA) implementation.

The MediaGX processor implements a Unified Memory Architecture (UMA). By using Cyrix's Display Compression Technology<sup>™</sup> (DCT), the performance degradation inherent in traditional UMA systems is eliminated.

#### 1.2.1 Graphics Accelerator

The graphics accelerator is a full-featured GUI (Graphical User Interface) accelerator. The graphics pipeline implements a bitBLT engine for frame buffer bitBLTs and rectangular fills. Additional instructions in the integer unit may be processed, as the bitBLT engine assists the CPU in the bitBLT operations that take place between system memory and the frame buffer. This combination of hardware and software is used by the display driver to provide very fast transfers in both directions between system memory and the frame buffer. The bitBLT engine also draws randomly-oriented vectors, and scanlines for polygon fill. All of the pipeline operations described in the following list can be applied to any bitBLT operation.

## **Integrated Functions**

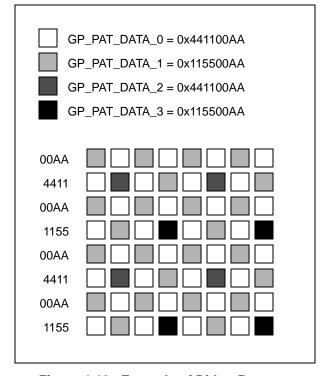

- Pattern Memory. Render with 8x8 dither, 8x8 monochrome, or 8x1 color pattern.

- Color Expansion. Expand monochrome bitmaps to full-depth 8- or 16-bit colors.

- Transparency. Suppresses drawing of background pixels for transparent text.

- Raster Operations. Boolean operation combines source, destination, and pattern bitmaps.

#### 1.2.2 Display Controller

The display port is a direct interface to the Cx5520/Cx5530 which drives a TFT flat panel display, LCD panel, or a CRT display.

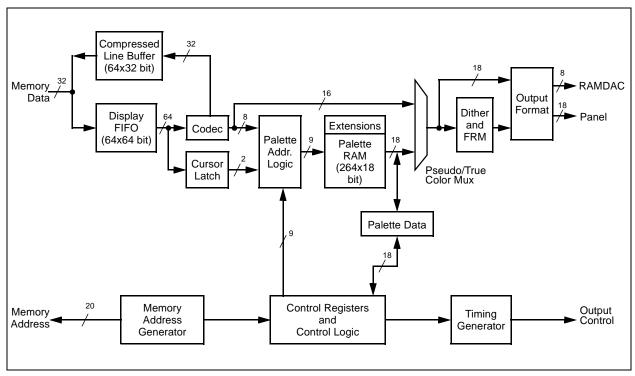

The display controller (video generator) retrieves image data from the frame buffer region of memory, performs a color-look-up if required, inserts the cursor overlay into the pixel stream, generates display timing, and formats the pixel data for output to a variety of display devices. The display controller contains Display Compression Technology (DCT) that allows the MediaGX processor to refresh the display from a compressed copy of the frame buffer. DCT typically decreases the screen-refresh bandwidth requirement by a factor of 15 to 20, further minimizing bandwidth contention.

# 1.2.3 XpressRAM™ Memory Subsystem

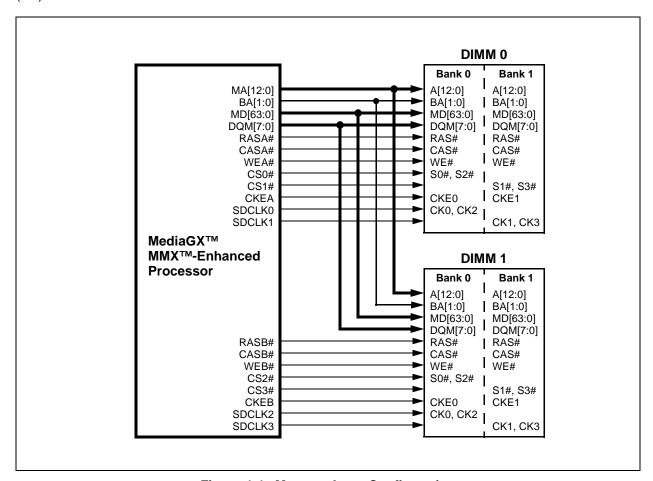

The memory controller drives a 64-bit SDRAM port directly. The SDRAM memory array contains both the main system memory and the graphics frame buffer. Up to four module banks of SDRAM are supported. Each module bank will have two or four component banks depending on the memory size and organization. The maximum configuration is four module banks with four component banks providing a total of 16 open banks. The maximum memory size is 1GB.

The memory controller handles multiple requests for memory data from the MediaGX processor, the graphics accelerator and the display controller. The memory controller contains extensive buffering logic that helps minimize contention for memory bandwidth between graphics and CPU requests. The memory controller cooperates with the internal bus controller to determine the cacheability of all memory references.

#### 1.2.4 PCI Controller

The MediaGX processor incorporates a full-function PCI interface module that includes the PCI arbiter. All accesses to external I/O devices are sent over the PCI bus, although most memory accesses are serviced by the SDRAM controller. The Internal Bus Interface Unit contains address mapping logic that determines if memory accesses are targeted for the SDRAM or for the PCI bus.

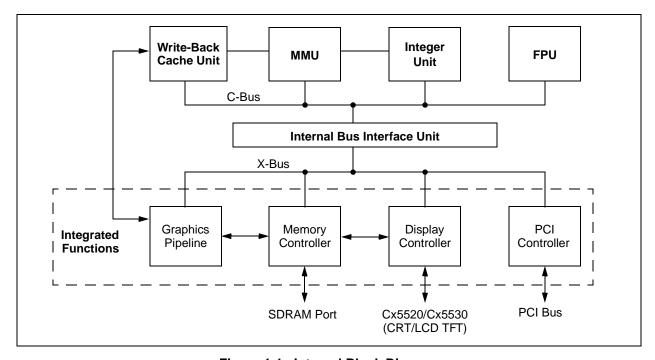

#### 1.3 System Designs

The Cyrix MediaGX™ Integrated Subsystem with MMX™ support consists of two chips, the MediaGX MMX-Enhanced Processor and the Cx5520™ or Cx5530™ I/O Companion. The subsystem provides high performance using 64-bit x86 processing. The two chips integrate video, audio and memory interface functions normally performed by external hardware.

As described in separate manuals, the Cx5520 and Cx5530 enable the full features of the MediaGX processor with MMX support. These features

include full VGA and VESA video, 16-bit stereo sound, IDE interface, ISA interface, SMM power management, and AT compatibility logic. In addition, the newer Cx5530 provides an Ultra DMA/33 interface, MPEG2 assist, and AC97 Version 2.0 compliant audio.

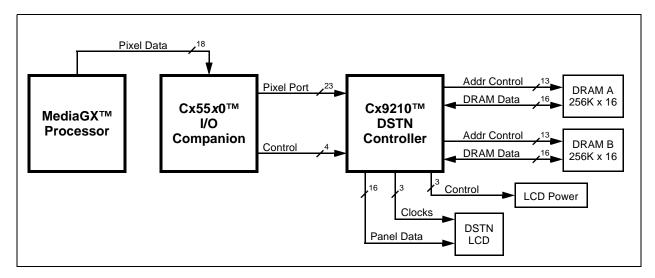

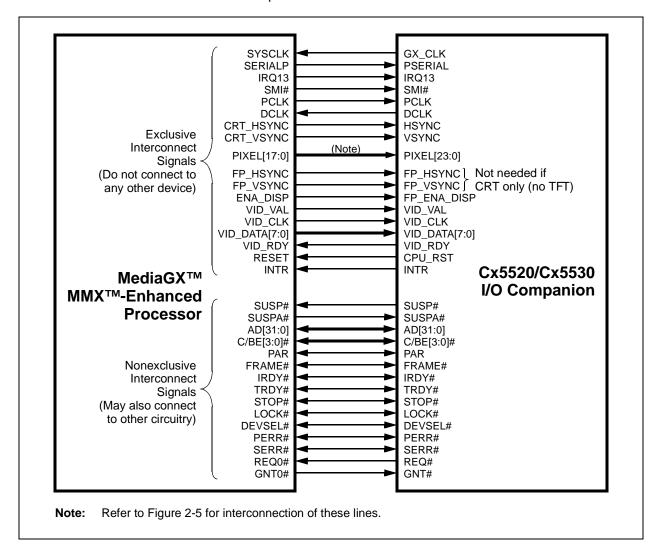

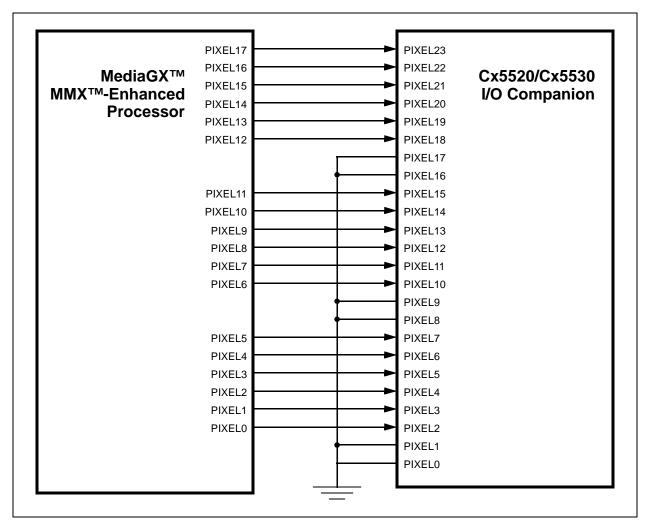

Figure 1-2 shows a basic block system diagram (refer to Figure 2-4 on page 34 for detailed subsystem interconnection signals). It includes the Cyrix Cx9210™ Dual-Scan Flat Panel Display Controller for designs that need to interface to a DSTN panel (instead of TFT panel).

Figure 1-2 System Block Diagram

## System Designs

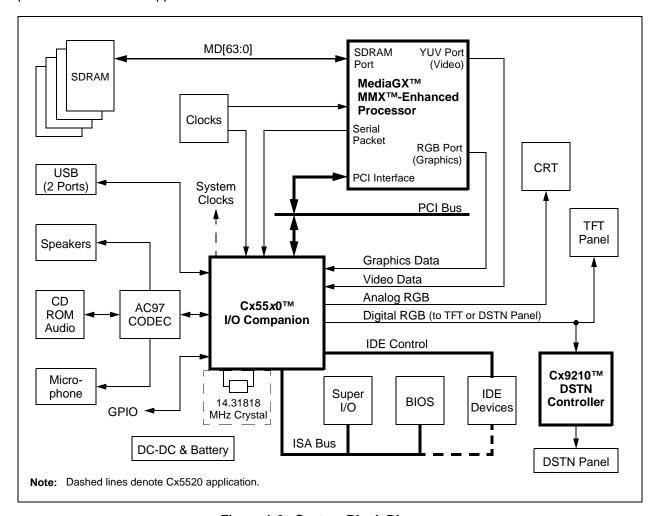

The Cx9210 converts the digital RGB output of a Cx5520 or Cx5530 I/O Companion chip to the digital output suitable for driving a dual-scan color STN (DSTN) flat panel LCD. It connects to the digital RGB output of a MediaGX<sup>TM</sup> processor or Cx55x0 and drives the graphics data onto a dual-

scan flat panel LCD. It can drive all standard dualscan color STN flat panels up to 1024x768 resolution. Figure 1-3 shows an example of a Cx9210 interface in a typical MediaGX Integrated Subsystem.

Figure 1-3 Cx9210 Interface System Diagram

#### MediaGX™ MMX™-Enhanced Processor

Integrated x86 Solution with MMX™ Support

## 2 Signal Definitions

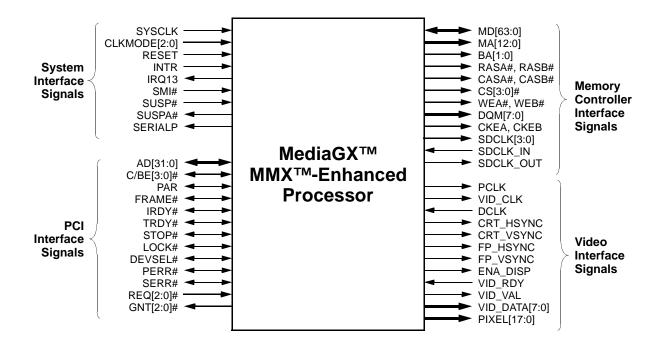

This section describes the external interface of the MediaGX processor. Figure 2-1 shows the signals

organized by their functional interface groups (internal test and electrical pins are not shown).

Figure 2-1 Functional Block Diagram

## **Pin Assignments**

#### 2.1 Pin Assignments

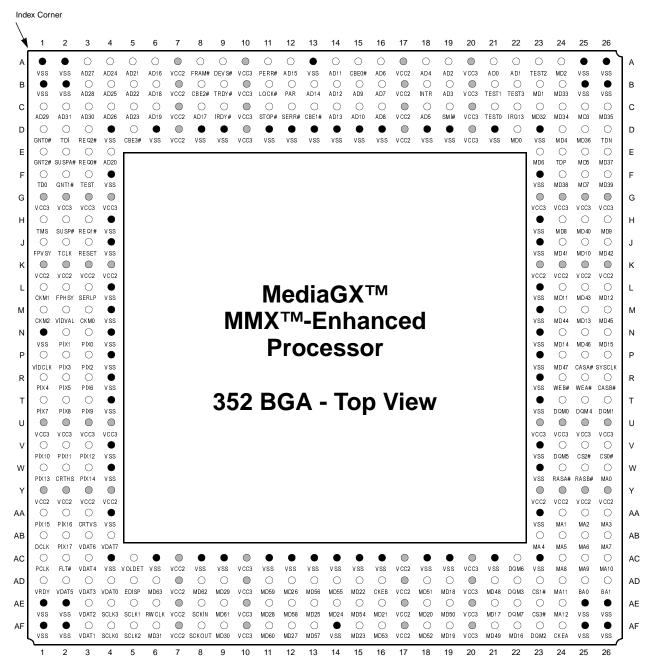

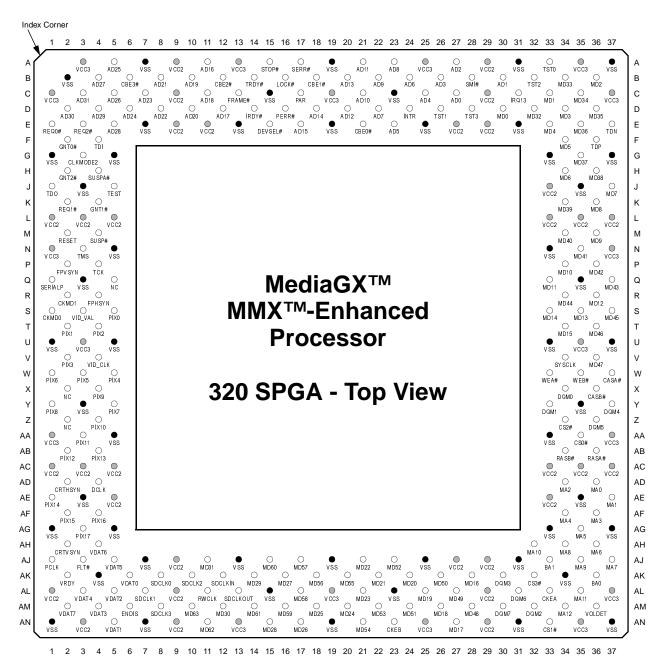

The MediaGX MMX-Enhanced processor is available in two packages, a 352 BGA package and a 320 SPGA package.

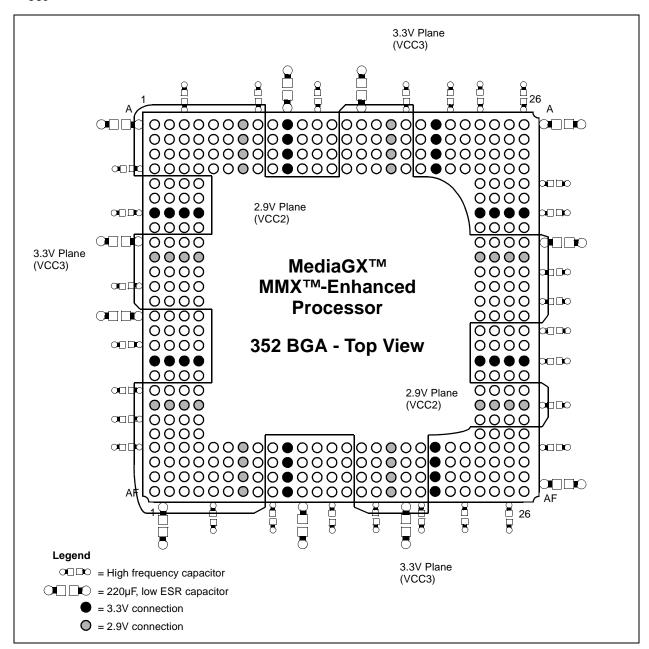

The pin assignment for the 352 BGA is shown in Figure 2-2. Tables 2-2 and 2-3 are pin assignment lists for the 352 BGA sorted by pin number and alphabetically by signal name, respectively.

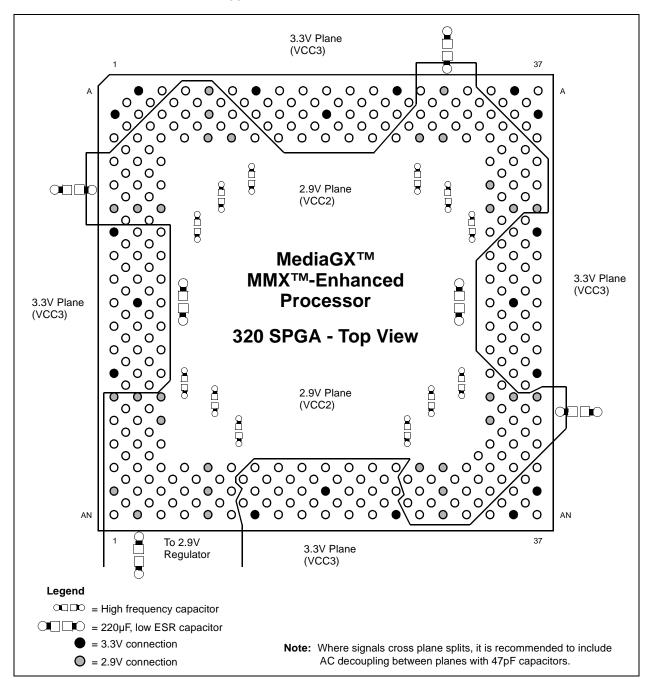

The 320 SPGA pin assignment is shown in Figure 2-3. Tables 2-4 and 2-5 are pin assignment lists for the 320 SPGA sorted by pin number and alphabetically by signal name, respectively.

Abbreviations used in Tables 2-4 through 2-5 are shown in Table 2-1.

Section 2.2 on page 21 describes the signals which are grouped according their functional group.

**Table 2-1** Pin Type Definitions

| Mnemonic  | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I         | Standard input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| I/O       | Bidirectional pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0         | Totem-pole output.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OD        | Open-drain output structure that allows multiple devices to share the pin in a wired-OR configuration                                                                                                                                                                                                                                                                                                                                                                          |

| PU        | Pull-up resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PD        | Pull-down resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| s/t/s     | Sustained tristate, an active-low tristate signal owned and driven by one and only one agent at a time. The agent that drives an s/t/s pin low must drive it high for at least one clock before letting it float. A new agent cannot start driving an s/t/s signal any sooner than one clock after the previous owner lets it float. A pull-up resistor is required to sustain the inactive state until another agent drives it, and must be provided by the central resource. |

| VCC (PWR) | Power pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VSS (GND) | Ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| #         | The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at a high voltage level.                                                                                                                                                                                                                                  |

Note: Signal names have been abbreviated in this figure due to space constraints.

- = GND termina

- = PWR terminal (VCC2 = VCC\_CORE; VCC3 = VCC\_IO)

Figure 2-2 352 BGA Pin Assignment Diagram

## Pin Assignments

Table 2-2 352 BGA Pin Assignments - Sorted by Pin Number

| Pin<br>No. | Signal Name |   | Pin<br>No. | Signal Name | Pin<br>No. | Signal Name |     | Pin<br>No. | Signal Name |     | Pin<br>No. | Signal Name |

|------------|-------------|---|------------|-------------|------------|-------------|-----|------------|-------------|-----|------------|-------------|

| A1         | VSS         |   | B15        | AD9         | D3         | REQ2#       |     | G1         | VCC3        | 1   | M1         | CLKMODE2    |

| A2         | VSS         |   | B16        | AD7         | D4         | VSS         |     | G2         | VCC3        | ĺĺ  | M2         | VID_VAL     |

| А3         | AD27        |   | B17        | VCC2        | D5         | C/BE3#      |     | G3         | VCC3        | ĺĺ  | М3         | CLKMODE0    |

| A4         | AD24        |   | B18        | INTR        | D6         | VSS         |     | G4         | VCC3        | ĺĺ  | M4         | VSS         |

| A5         | AD21        |   | B19        | AD3         | D7         | VCC2        |     | G23        | VCC3        | 1 [ | M23        | VSS         |

| A6         | AD16        |   | B20        | VCC3        | D8         | VSS         |     | G24        | VCC3        | ll  | M24        | MD44        |

| A7         | VCC2        |   | B21        | TEST1       | D9         | VSS         |     | G25        | VCC3        | ll  | M25        | MD13        |

| A8         | FRAME#      |   | B22        | TEST3       | D10        | VCC3        |     | G26        | VCC3        | ll  | M26        | MD45        |

| A9         | DEVSEL#     |   | B23        | MD1         | D11        | VSS         |     | H1         | TMS         | ll  | N1         | VSS         |

| A10        | VCC3        |   | B24        | MD33        | D12        | VSS         |     | H2         | SUSP#       | 1 [ | N2         | PIXEL1      |

| A11        | PERR#       |   | B25        | VSS         | D13        | VSS         |     | НЗ         | REQ1#       | ll  | N3         | PIXEL0      |

| A12        | AD15        |   | B26        | VSS         | D14        | VSS         |     | H4         | VSS         | 1 [ | N4         | VSS         |

| A13        | VSS         |   | C1         | AD29        | D15        | VSS         |     | H23        | VSS         | ll  | N23        | VSS         |

| A14        | AD11        |   | C2         | AD31        | D16        | VSS         |     | H24        | MD8         | ll  | N24        | MD14        |

| A15        | C/BE0#      |   | C3         | AD30        | D17        | VCC2        |     | H25        | MD40        | ll  | N25        | MD46        |

| A16        | AD6         |   | C4         | AD26        | D18        | VSS         |     | H26        | MD9         | 1 [ | N26        | MD15        |

| A17        | VCC2        |   | C5         | AD23        | D19        | VSS         |     | J1         | FP_VSYNC    | ll  | P1         | VID_CLK     |

| A18        | AD4         |   | C6         | AD19        | D20        | VCC3        |     | J2         | TCLK        | 1 [ | P2         | PIXEL3      |

| A19        | AD2         |   | C7         | VCC2        | D21        | VSS         |     | J3         | RESET       | 1 [ | P3         | PIXEL2      |

| A20        | VCC3        |   | C8         | AD17        | D22        | MD0         |     | J4         | VSS         | ll  | P4         | VSS         |

| A21        | AD0         | Ī | C9         | IRDY#       | D23        | VSS         |     | J23        | VSS         |     | P23        | VSS         |

| A22        | AD1         |   | C10        | VCC3        | D24        | MD4         |     | J24        | MD41        | ll  | P24        | MD47        |

| A23        | TEST2       | Ī | C11        | STOP#       | D25        | MD36        |     | J25        | MD10        |     | P25        | CASA#       |

| A24        | MD2         |   | C12        | SERR#       | D26        | TDN         |     | J26        | MD42        | ll  | P26        | SYSCLK      |

| A25        | VSS         |   | C13        | C/BE1#      | E1         | GNT2#       |     | K1         | VCC2        | 1 [ | R1         | PIXEL4      |

| A26        | VSS         |   | C14        | AD13        | E2         | SUSPA#      |     | K2         | VCC2        | ll  | R2         | PIXEL5      |

| B1         | VSS         |   | C15        | AD10        | E3         | REQ0#       |     | K3         | VCC2        | ll  | R3         | PIXEL6      |

| B2         | VSS         |   | C16        | AD8         | E4         | AD20        |     | K4         | VCC2        | ll  | R4         | VSS         |

| В3         | AD28        | Ī | C17        | VCC2        | E23        | MD6         |     | K23        | VCC2        |     | R23        | VSS         |

| В4         | AD25        | Ī | C18        | AD5         | E24        | TDP         |     | K24        | VCC2        |     | R24        | WEB#        |

| B5         | AD22        |   | C19        | SMI#        | E25        | MD5         |     | K25        | VCC2        | ll  | R25        | WEA#        |

| В6         | AD18        | Ī | C20        | VCC3        | E26        | MD37        |     | K26        | VCC2        |     | R26        | CASB#       |

| В7         | VCC2        |   | C21        | TEST0       | F1         | TDO         |     | L1         | CLKMODE1    | ll  | T1         | PIXEL7      |

| B8         | C/BE2#      |   | C22        | IRQ13       | F2         | GNT1#       | ] [ | L2         | FP_HSYNC    | ] [ | T2         | PIXEL8      |

| В9         | TRDY#       |   | C23        | MD32        | F3         | TEST        |     | L3         | SERIALP     | ] [ | Т3         | PIXEL9      |

| B10        | VCC3        |   | C24        | MD34        | F4         | VSS         |     | L4         | VSS         | ] [ | T4         | VSS         |

| B11        | LOCK#       |   | C25        | MD3         | F23        | VSS         | 1   | L23        | VSS         | ]   | T23        | VSS         |

| B12        | PAR         |   | C26        | MD35        | F24        | MD38        |     | L24        | MD11        | ] [ | T24        | DQM0        |

| B13        | AD14        |   | D1         | GNT0#       | F25        | MD7         | 1   | L25        | MD43        | ] [ | T25        | DQM4        |

| B14        | AD12        |   | D2         | TDI         | F26        | MD39        | ] [ | L26        | MD12        | ] [ | T26        | DQM1        |

Table 2-2 352 BGA Pin Assignments - Sorted by Pin Number (cont.)

| Pin<br>No. | Signal Name |

|------------|-------------|

| U1         | VCC3        |

| U2         | VCC3        |

| U3         | VCC3        |

| U4         | VCC3        |

| U23        | VCC3        |

| U24        | VCC3        |

| U25        | VCC3        |

| U26        | VCC3        |

| V1         | PIXEL10     |

| V2         | PIXEL11     |

| V3         | PIXEL12     |

| V4         | VSS         |

| V23        | VSS         |

| V24        | DQM5        |

| V25        | CS2#        |

| V26        | CS0#        |

| W1         | PIXEL13     |

| W2         | CRT_HSYNC   |

| W3         | PIXEL14     |

| W4         | VSS         |

| W23        | VSS         |

| W24        | RASA#       |

| W25        | RASB#       |

| W26        | MA0         |

| Y1         | VCC2        |

| Y2         | VCC2        |

| Y3         | VCC2        |

| Y4         | VCC2        |

| Y23        | VCC2        |

| Y24        | VCC2        |

| Y25        | VCC2        |

| Pin  |             |

|------|-------------|

| No.  | Signal Name |

| Y26  | VCC2        |

| AA1  | PIXEL15     |

| AA2  | PIXEL16     |

| AA3  | CRT_VSYNC   |

| AA4  | VSS         |

| AA23 | VSS         |

| AA24 | MA1         |

| AA25 | MA2         |

| AA26 | MA3         |

| AB1  | DCLK        |

| AB2  | PIXEL17     |

| AB3  | VID_DATA6   |

| AB4  | VID_DATA7   |

| AB23 | MA4         |

| AB24 | MA5         |

| AB25 | MA6         |

| AB26 | MA7         |

| AC1  | PCLK        |

| AC2  | FLT#        |

| AC3  | VID_DATA4   |

| AC4  | VSS         |

| AC5  | VOLDET      |

| AC6  | VSS         |

| AC7  | VCC2        |

| AC8  | VSS         |

| AC9  | VSS         |

| AC10 | VCC3        |

| AC11 | VSS         |

| AC12 | VSS         |

| AC13 | VSS         |

| AC14 | VSS         |

| Pin<br>No. | Signal Name |

|------------|-------------|

| AC15       | VSS         |

| AC16       | VSS         |

| AC17       | VCC2        |

| AC18       | VSS         |

| AC19       | VSS         |

| AC20       | VCC3        |

| AC21       | VSS         |

| AC22       | DQM6        |

| AC23       | VSS         |

| AC24       | MA8         |

| AC25       | MA9         |

| AC26       | MA10        |

| AD1        | VID_RDY     |

| AD2        | VID_DATA5   |

| AD3        | VID_DATA3   |

| AD4        | VID_DATA0   |

| AD5        | ENA_DISP    |

| AD6        | MD63        |

| AD7        | VCC2        |

| AD8        | MD62        |

| AD9        | MD29        |

| AD10       | VCC3        |

| AD11       | MD59        |

| AD12       | MD26        |

| AD13       | MD56        |

| AD14       | MD55        |

| AD15       | MD22        |

| AD16       | CKEB        |

| AD17       | VCC2        |

| AD18       | MD51        |

| AD19       | MD18        |

| Pin<br>No. | Signal Name |

|------------|-------------|

| AD20       | VCC3        |

| AD21       | MD48        |

| AD22       | DQM3        |

| AD23       | CS1#        |

| AD24       | MA11        |

| AD25       | BA0         |

| AD26       | BA1         |

| AE1        | VSS         |

| AE2        | VSS         |

| AE3        | VID_DATA2   |

| AE4        | SDCLK3      |

| AE5        | SDCLK1      |

| AE6        | RW_CLK      |

| AE7        | VCC2        |

| AE8        | SDCLK_IN    |

| AE9        | MD61        |

| AE10       | VCC3        |

| AE11       | MD28        |

| AE12       | MD58        |

| AE13       | MD25        |

| AE14       | MD24        |

| AE15       | MD54        |

| AE16       | MD21        |

| AE17       | VCC2        |

| AE18       | MD20        |

| AE19       | MD50        |

| AE20       | VCC3        |

| AE21       | MD17        |

| AE22       | DQM7        |

| AE23       | CS3#        |

| AE24       | MA12        |

| 1          |             |

|------------|-------------|

| Pin<br>No. | Signal Name |

| AE25       | VSS         |

| AE26       | VSS         |

| AF1        | VSS         |

| AF2        | VSS         |

| AF3        | VID_DATA1   |

| AF4        | SDCLK0      |

| AF5        | SDCLK2      |

| AF6        | MD31        |

| AF7        | VCC2        |

| AF8        | SDCLK_OUT   |

| AF9        | MD30        |

| AF10       | VCC3        |

| AF11       | MD60        |

| AF12       | MD27        |

| AF13       | MD57        |

| AF14       | VSS         |

| AF15       | MD23        |

| AF16       | MD53        |

| AF17       | VCC2        |

| AF18       | MD52        |

| AF19       | MD19        |

| AF20       | VCC3        |

| AF21       | MD49        |

| AF22       | MD16        |

| AF23       | DQM2        |

| AF24       | CKEA        |

| AF25       | VSS         |

| AF26       | VSS         |

## Pin Assignments

Table 2-3 352 BGA Pin Assignments - Sorted Alphabetically by Signal Name

|             | 1        | 1       |             | 1     | 1        | ' <del>-                                   </del> | <u> </u> | <u> </u> |             | i e   |            |

|-------------|----------|---------|-------------|-------|----------|---------------------------------------------------|----------|----------|-------------|-------|------------|

| Signal Name | Type     | Pin No. | Signal Name | Type  | Pin No.  | Signal Name                                       | Type     | Pin No.  | Signal Name | Type  | Pin No.    |

| AD0         | I/O      | A21     | CRT_HSYNC   | 0     | W2       | MD4                                               | I/O      | D24      | MD49        | I/O   | AF21       |

| AD1         | I/O      | A22     | CRT_VSYNC   | 0     | AA3      | MD5                                               | I/O      | E25      | MD50        | I/O   | AE19       |

| AD2         | I/O      | A19     | CS0#        | 0     | V26      | MD6                                               | I/O      | E23      | MD51        | I/O   | AD18       |

| AD3         | I/O      | B19     | CS1#        | 0     | AD23     | MD7                                               | I/O      | F25      | MD52        | I/O   | AF18       |

| AD4         | I/O      | A18     | CS2#        | 0     | V25      | MD8                                               | I/O      | H24      | MD53        | I/O   | AF16       |

| AD5         | I/O      | C18     | CS3#        | 0     | AE23     | MD9                                               | I/O      | H26      | MD54        | I/O   | AE15       |

| AD6         | I/O      | A16     | DCLK        | - 1   | AB1      | MD10                                              | I/O      | J25      | MD55        | I/O   | AD14       |

| AD7         | I/O      | B16     | DEVSEL#     | s/t/s | A9 (PU)  | MD11                                              | I/O      | L24      | MD56        | I/O   | AD13       |

| AD8         | I/O      | C16     | DQM0        | 0     | T24      | MD12                                              | I/O      | L26      | MD57        | I/O   | AF13       |

| AD9         | I/O      | B15     | DQM1        | 0     | T26      | MD13                                              | I/O      | M25      | MD58        | I/O   | AE12       |

| AD10        | I/O      | C15     | DQM2        | 0     | AF23     | MD14                                              | I/O      | N24      | MD59        | I/O   | AD11       |

| AD11        | I/O      | A14     | DQM3        | 0     | AD22     | MD15                                              | I/O      | N26      | MD60        | I/O   | AF11       |

| AD12        | I/O      | B14     | DQM4        | 0     | T25      | MD16                                              | I/O      | AF22     | MD61        | I/O   | AE9        |

| AD13        | I/O      | C14     | DQM5        | 0     | V24      | MD17                                              | I/O      | AE21     | MD62        | I/O   | AD8        |

| AD14        | I/O      | B13     | DQM6        | 0     | AC22     | MD18                                              | I/O      | AD19     | MD63        | I/O   | AD6        |

| AD15        | I/O      | A12     | DQM7        | 0     | AE22     | MD19                                              | I/O      | AF19     | PAR         | I/O   | B12        |

| AD16        | I/O      | A6      | ENA_DISP    | 0     | AD5      | MD20                                              | I/O      | AE18     | PCLK        | 0     | AC1        |

| AD17        | I/O      | C8      | FLT#        | I     | AC2      | MD21                                              | I/O      | AE16     | PERR#       | s/t/s | A11 (PU)   |

| AD18        | I/O      | В6      | FP_HSYNC    | 0     | L2       | MD22                                              | I/O      | AD15     | PIXEL0      | 0     | N3         |

| AD19        | I/O      | C6      | FP_VSYNC    | 0     | J1       | MD23                                              | I/O      | AF15     | PIXEL1      | 0     | N2         |

| AD20        | I/O      | E4      | FRAME#      | s/t/s | A8 (PU)  | MD24                                              | I/O      | AE14     | PIXEL2      | 0     | P3         |

| AD21        | I/O      | A5      | GNT0#       | 0     | D1       | MD25                                              | I/O      | AE13     | PIXEL3      | 0     | P2         |

| AD22        | I/O      | B5      | GNT1#       | 0     | F2       | MD26                                              | I/O      | AD12     | PIXEL4      | 0     | R1         |

| AD23        | I/O      | C5      | GNT2#       | 0     | E1       | MD27                                              | I/O      | AF12     | PIXEL5      | 0     | R2         |

| AD24        | I/O      | A4      | INTR        | I     | B18      | MD28                                              | I/O      | AE11     | PIXEL6      | 0     | R3         |

| AD25        | I/O      | B4      | IRDY#       | s/t/s | C9 (PU)  | MD29                                              | I/O      | AD9      | PIXEL7      | 0     | T1         |

| AD26        | I/O      | C4      | IRQ13       | 0     | C22      | MD30                                              | I/O      | AF9      | PIXEL8      | 0     | T2         |

| AD27        | I/O      | A3      | LOCK#       | s/t/s | B11 (PU) | MD31                                              | I/O      | AF6      | PIXEL9      | 0     | Т3         |

| AD28        | I/O      | В3      | MA0         | 0     | W26      | MD32                                              | I/O      | C23      | PIXEL10     | 0     | V1         |

| AD29        | I/O      | C1      | MA1         | 0     | AA24     | MD33                                              | I/O      | B24      | PIXEL11     | 0     | V2         |

| AD30        | I/O      | C3      | MA2         | 0     | AA25     | MD34                                              | I/O      | C24      | PIXEL12     | 0     | V3         |

| AD31        | I/O      | C2      | MA3         | 0     | AA26     | MD35                                              | I/O      | C26      | PIXEL13     | 0     | W1         |