## **National Semiconductor**

Order No. IMP-16P/937A Pub. No. 4200037A

# IMP-16P Users Manual

**Volume 1**

## IMP-16P MICROCOMPUTER

IMP-16P

USERS MANUAL

YOLUME 1

September 1974

© National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

## PREFACE

The IMP-16P Users Manual provides information to assist the IMP-16P user in the development of software and hardware for microprocessor system designs. Contained herein are procedures for Control Panel, Card Reader and Teletype operation. In addition, general, intermediate, and detailed functional descriptions are presented for the various assemblies and associated firmware incorporated into the design of the IMP-16 Microcomputer. Also included are descriptions of interface considerations and system verification procedures. For purposes of system development and maintenance, the user should have a working knowledge of computer programming, digital circuit logic, and integrated circuits.

The material in this manual is subject to change without notice. Circuit details and other data supplied with the engineering documentation that accompany equipment take precedence over the information contained in this manual.

Copies of this manual and other National Semiconductor publications may be obtained from the sales offices listed on the back cover.

## CONTENTS

| Chapter |               |                                                 | Page |

|---------|---------------|-------------------------------------------------|------|

| 1       | GENERAI       | L INFORMATION                                   | 1-1  |

|         | 1.1           | IMP-16P MICROCOMPUTER                           | 1-1  |

|         | 1.1.1         | General Description                             | 1-1  |

|         | 1.1.2         | Operational Features                            | 1-2  |

|         | 1.2           | MAJOR UNITS AND OPTIONS                         | 1-4  |

|         | 1.2.1         | Card Cage                                       | 1-4  |

|         | 1.2.2         | IMP-16C/200 or /300 CPU Card                    | 1-4  |

|         | 1.2.3         | Memory Timing and Control Card                  | 1-6  |

|         | 1.2.4         | Memory Storage Card                             | 1-6  |

|         | 1.2.5         | Control Panel Interface Card                    | 1-6  |

|         | 1.2.6         | TTY/Card Reader Interface Card                  | 1-6  |

|         | 1.2.7         | Programmers Control Panel                       | 1-6  |

|         | 1.2.8         | Operators Control Panel                         | 1-6  |

|         | 1.2.9         | Power Supplies                                  | 1-7  |

|         | 1.2.10        | Units and Options                               | 1-7  |

|         | 1.3           | INSTRUCTION SETS                                | 1-11 |

|         | 1.4           | IMP-16P BASIC SOFTWARE                          | 1-12 |

|         | 1.4.1         | Diagnostic Programs                             | 1-12 |

|         | 1.4.2         | Loaders                                         | 1-12 |

|         | <b>1.4.</b> 3 | Resident Assembler                              | 1-13 |

|         | 1.4.4         | Debug                                           | 1-13 |

|         | 1.4.5         | Source Editor (EDIT 16)                         | 1-13 |

|         | 1.5           | MANUAL ORGANIZATION                             | 1-14 |

|         | 1.6           | RELATED PUBLICATIONS                            | 1-15 |

| 2       | CONTROI       | L PANEL OPERATION                               | 2-1  |

|         | 2.1           | INTRODUCTION                                    | 2-1  |

|         | 2.2           | OPERATORS CONTROL PANEL                         | 2-1  |

|         | 2.3           | PROGRAMMERS CONTROL PANEL                       | 2-2  |

|         | 2.4           | IMP-16P OPERATING PROCEDURES                    | 2-5  |

|         | 2.4.1         | Power Up                                        | 2-5  |

|         | 2.4.2         | Power Down                                      | 2-5  |

|         | 2.4.3         | Program Loading                                 | 2-5  |

|         | 2.4.4         | Program Execution                               | 2-5  |

|         | 2.4.5         | Debugging Software                              | 2-5  |

|         | 2.5           | CONTROL PANEL SERVICE ROUTINE                   | 2-5  |

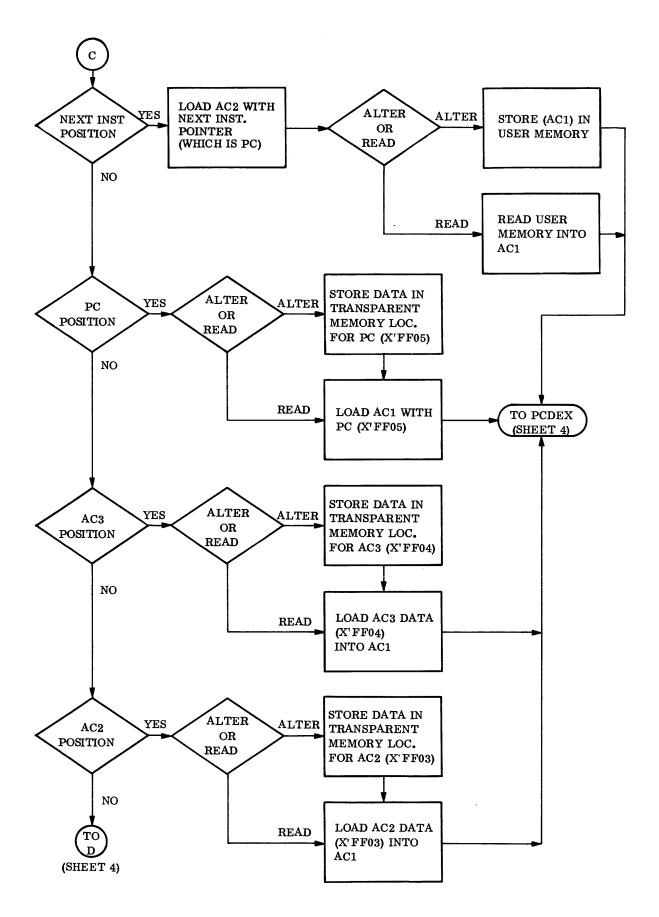

|         | 2.5.1         | Entry and Save CPU Contents                     | 2-10 |

|         | 2.5.2         | Read Command and Data Words                     | 2-10 |

|         | 2.5.3         | Command Switch Active                           | 2-10 |

|         | 2.5.4         | Display Selector Rotary Switch Position Testing | 2-11 |

|         | 2.5.5         | Display Data and Address (PCDEX)                | 2-11 |

|         | 2.5.6         | Restore CPU Contents and Exit                   | 2-11 |

| 3       | TELETYI       | PE OPERATION                                    | 3-1  |

|         | 3.1           | INTRODUCTION                                    | 3-1  |

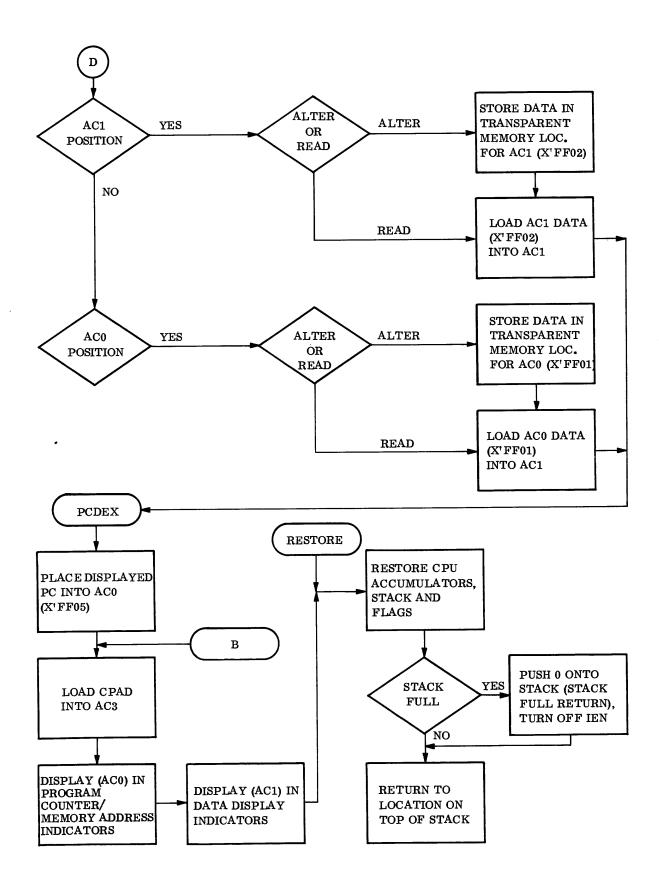

|         | 3.2           | ABSOLUTE PAPER TAPE LOADER ROUTINE              | 3-1  |

|         | 3.2.1         | Operating Procedure                             | 3-1  |

|         | 3.2.2         | Absolute Paper Tape Loader Routine Description  | 3-2  |

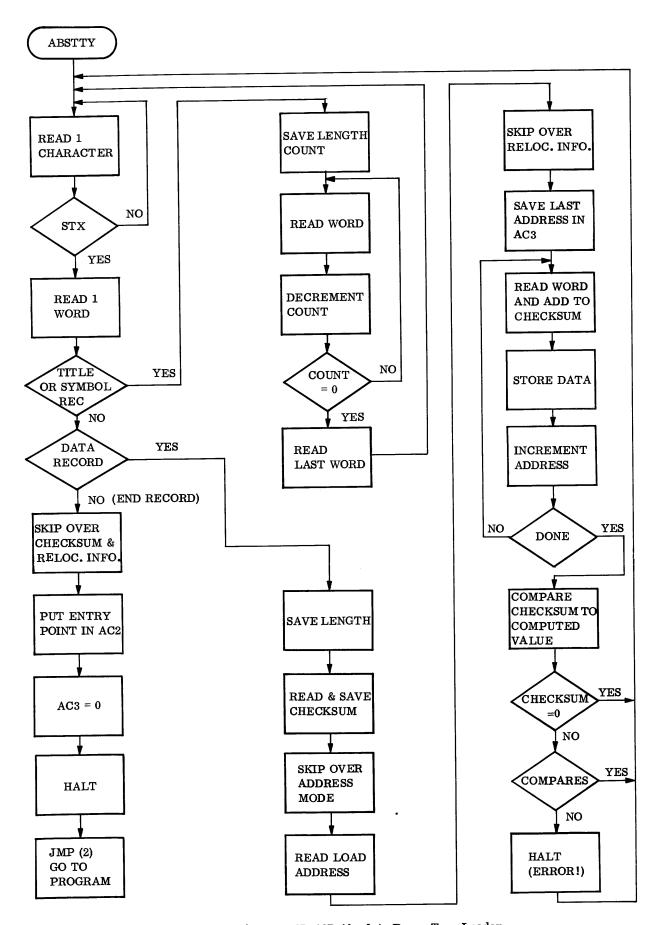

|         | 3.3           | TELETYPE FIRMWARE SUBROUTINES                   | 3-4  |

|         | 3.3.1         | GETC Subroutine Description                     | 3-6  |

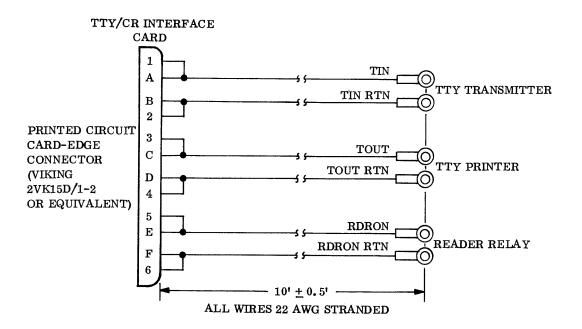

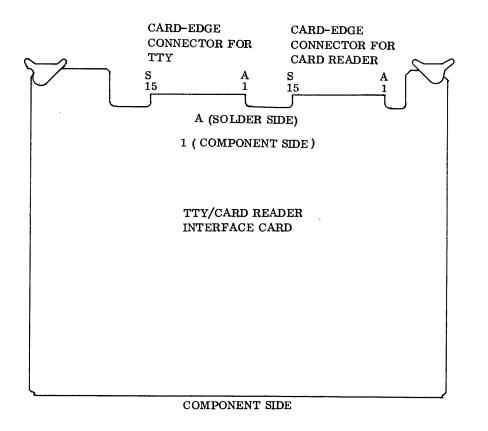

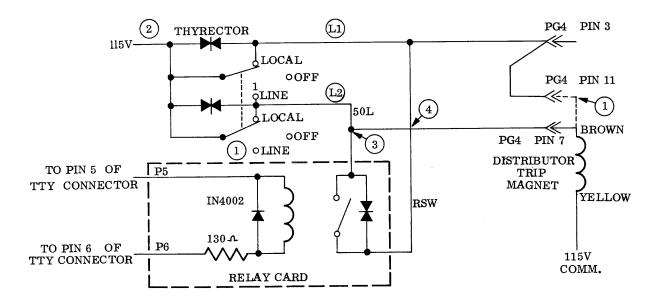

|         | 3.4           | PPT READER/TTY INTERCONNECT                     | 3-7  |

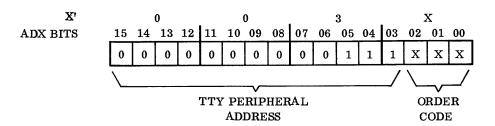

|         | 3.5           | TELETYPE PERIPHERAL ADDRESSING                  | 3-7  |

## CONTENTS (Continued)

| Chapter |                                        |                                                                      | Page          |

|---------|----------------------------------------|----------------------------------------------------------------------|---------------|

| 4       | CARD REA                               | DER OPERATION                                                        | 4-1           |

|         | 4.1                                    | INTRODUCTION                                                         | 4-1           |

|         | 4.2                                    | CARD READER OPERATION                                                | 4-1           |

|         | 4.3                                    | CARD READER ROUTINES                                                 | 4-2           |

|         | 4.3.1                                  | Absolute Card Reader Loader Routine                                  | 4-2           |

|         | 4.3.2                                  | Readcard and Convert Routines                                        | 4-5           |

|         | 4.4                                    | CARD READER INTERCONNECT                                             | 4-6           |

|         | 4.5                                    | CARD READER PERIPHERAL ADDRESSING                                    | 4-8           |

| 5       | SYSTEM VI                              | ERIFICATION                                                          | 5-1           |

| •       | 5.1                                    | INTRODUCTION                                                         | 5-1           |

|         | 5.2                                    | INITIAL SYSTEM VERIFICATION                                          | 5-1           |

|         | 5.2.1                                  | Control Panel Verification                                           | 5-1           |

|         | 5.2.2                                  | Operational Verification                                             | 5-3           |

|         | 5.2.3                                  | TTY/Card Reader Program Verification                                 | 5-5           |

|         | 5.3                                    | VERIFICATION OF TTY/CARD READER INTERFACE                            | 5-7           |

|         | 5.3.1                                  | Card Reader Interface                                                | 5-7           |

|         | 5.3.2                                  | TTY Interface                                                        | 5-8           |

|         | 5. 4                                   | DIAGNOSTIC PROGRAMS                                                  | 5-9           |

|         | 5.4.1                                  | CPU Diagnostic                                                       | 5-9           |

|         | 5.4.2                                  | CPUXDI Loading Via Card Reader                                       | 5-11          |

|         | 5.4.3                                  | CPUXDI Loading Via Paper Tape Reader                                 | 5-11          |

|         | 5. 4. 4                                | CPUXDI Normal Operating Sequence                                     | 5-12          |

|         | 5. 4. 5                                | Memory Diagnostic                                                    | 5-12<br>5-13  |

|         | 5. 4. 6                                | MEMDIL Loading Via Card Reader                                       | 5-15<br>5-15  |

|         | 5. 4. 7                                | MEMDIL Loading Via Card Reader  MEMDIL Loading Via Paper Tape Reader | 5-15<br>5-15  |

|         | 5.4.8                                  | MEMDIL Normal Operating Sequence                                     | 5-16          |

|         | 5. 5                                   | PROGRAM DEBUG CONSIDERATIONS                                         | 5-10<br>5-17  |

|         | 5.5.1                                  | Introduction to Debug                                                | 5-17          |

|         | 5.5.2                                  | Use of Debug                                                         | 5 <b>-1</b> 7 |

| •       | ************************************** | T. GOLVETTE LETTONS                                                  |               |

| 6       |                                        | E CONSIDERATIONS                                                     | 6-1           |

|         | 6.1                                    | INTRODUCTION                                                         | 6-1           |

|         | 6.2                                    | PROGRAM-CONTROLLED INPUT/OUTPUT                                      | 6-1           |

|         | 6.2.1                                  | Peripheral Devices                                                   | 6-1           |

|         | 6.2.2                                  | Memory Storage                                                       | 6-1           |

|         | 6.2.3                                  | Instruction Execution Times                                          | 6-5           |

|         | 6.2.4                                  | Programmed Time Delay                                                | 6-12          |

|         | 6.2.5                                  | Imput/Output Programming Examples                                    | 6-14          |

|         | 6.3                                    | INTERRUPT PROCESSING                                                 | 6-14          |

|         | 6.3.1                                  | Interrupt Response                                                   | 6-14          |

|         | 6.3.2                                  | Interrupt Latency Time                                               | 6-14          |

|         | 6.3.3                                  | Interrupt Service Considerations                                     | 6-15          |

|         | 6.4                                    | IMP-16P AND CPU INTERFACING SIGNALS                                  | 6-16          |

|         | 6.4.1                                  | Address and Data Signals                                             | 6-16          |

|         | 6.4.2                                  | External Timing, Control and Status Signals                          | 6-22          |

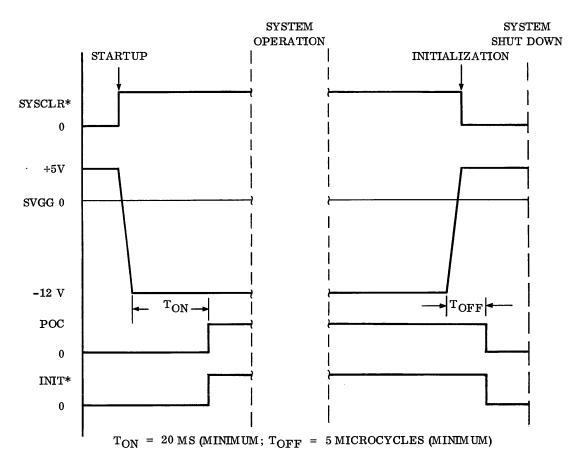

|         | 6.4.3                                  | System Initialization                                                | 6-24          |

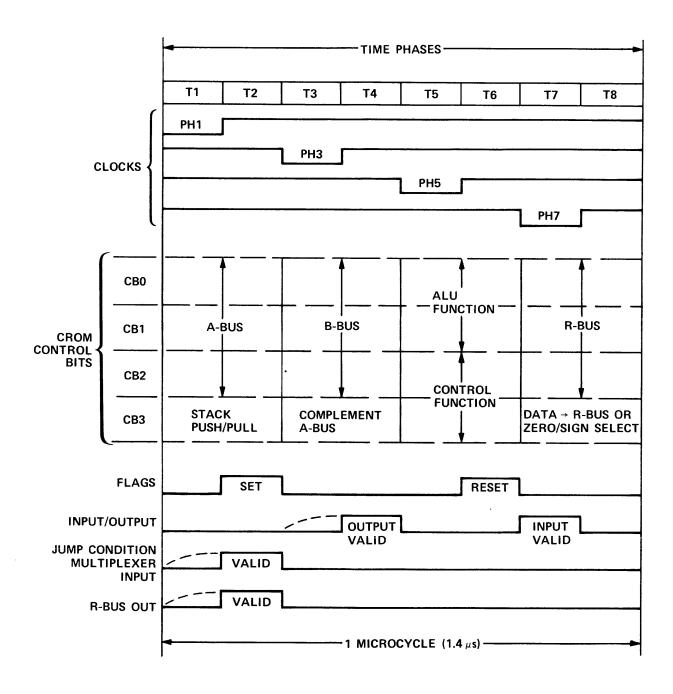

|         | 6.4.4                                  | Basic Instruction Cycle                                              | 6-25          |

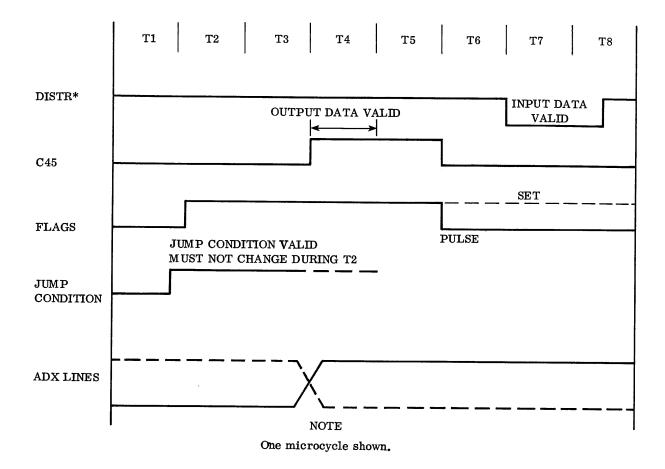

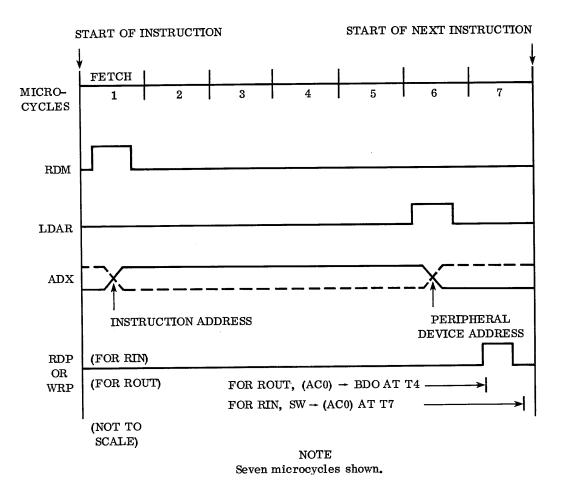

|         | 6.4.5                                  | Input/Output Timing and Control Signals                              | 6-27          |

|         | 6.5                                    | MEMORY MANAGEMENT                                                    | 6-28          |

|         | 6.5.1                                  | Relocating PROM Addresses                                            | 6-28          |

|         | 6.5.2                                  | Memory Expansion                                                     | 6-29          |

|         | 6.6                                    | PERIPHERAL ADDRESS ASSIGNMENTS                                       | 6-30          |

|         | 6.7                                    | POWER SUPPLY REQUIREMENTS                                            | 6-30          |

## CONTENTS (Continued)

| Chapter |           |                                                     | Page |

|---------|-----------|-----------------------------------------------------|------|

| 7       | FUNCTION  | AL DESCRIPTION                                      | 7-1  |

|         | 7.1       | INTRODUCTION                                        | 7-1  |

|         | 7.2       | IMP-16P OVERALL FUNCTIONAL DESCRIPTION              | 7-1  |

|         | 7.3       | CENTRAL PROCESSING UNIT (CPU)                       | 7-3  |

|         | 7.4       | MEMORY                                              | 7-5  |

|         | 7.4.1     | Basic Operating Modes                               | 7-5  |

|         | 7.4.1.1   | Read Operation                                      | 7-5  |

|         | 7.4.1.2   | Write Operation                                     | 7-7  |

|         | 7.4.1.3   | Refresh Operation                                   | 7-7  |

|         | 7.4.2     | Memory Timing and Control Card Detailed Description | 7-9  |

|         | 7.4.2.1   | Address Logic                                       | 7-9  |

|         | 7.4.2.2   | Timing Logic                                        | 7-10 |

|         | 7.4.2.3   | Decoding Logic                                      | 7-10 |

|         | 7.4.2.4   | Write Pulse/Data Control Logic                      | 7-10 |

|         | 7.4.2.5   | Refresh Logic                                       | 7-11 |

|         | 7.4.2.6   | Write Cycle                                         | 7-11 |

|         | 7.4.2.7   | Read Cycle                                          | 7-12 |

|         | 7.4.2.8   | Refresh Cycle                                       | 7-12 |

|         | 7.4.3     | Memory Storage Card Detailed Description            | 7-13 |

|         | 7.4.3.1   | 4 by 16 Memory Array                                | 7-13 |

|         | 7.4.3.2   | Clock Drivers                                       | 7-13 |

|         | 7.4.3.3   | TTL Logic                                           | 7-13 |

|         | 7.4.4     | Description of Various Memory Operating Modes       | 7-14 |

|         | 7.4.4.1   | Read Cycle                                          | 7-14 |

|         | 7.4.4.2   | Write Cycle                                         | 7-15 |

|         | 7.4.4.3   | Refresh Cycle                                       | 7-15 |

|         | 7.5       | TTY/CARD READER INTERFACE CARD FUNCTIONAL           |      |

|         | -         | DESCRIPTION                                         | 7-16 |

|         | 7.5.1     | General Description                                 | 7-16 |

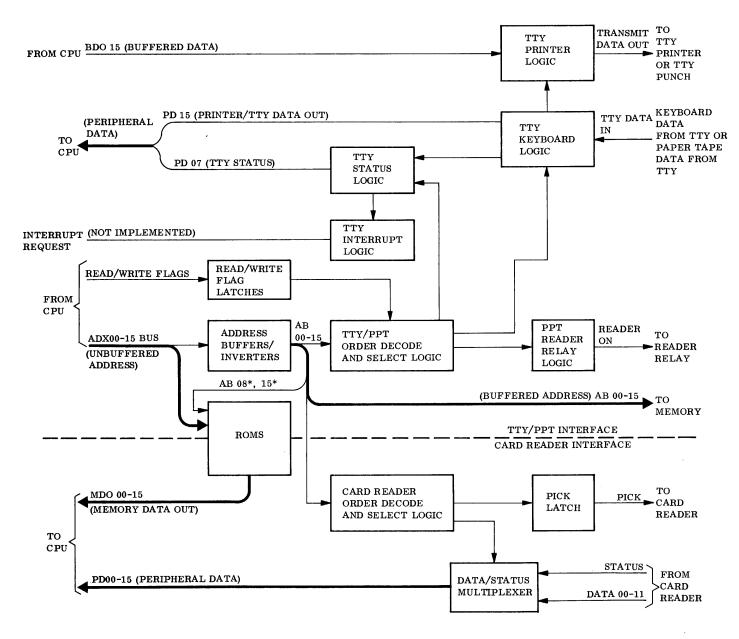

|         | 7.5.1.1   | TTY Interface Section                               | 7-16 |

|         | 7.5.1.2   | Card Reader Interface Section                       | 7-16 |

|         | 7.5.2     | TTY Interface Detailed Description                  | 7-16 |

|         | 7.5.2.1   | Initialization                                      | 7-18 |

|         | 7.5.2.2   | Address Generation                                  | 7-18 |

|         | 7.5.2.3   | Program Addressing and Control                      | 7-18 |

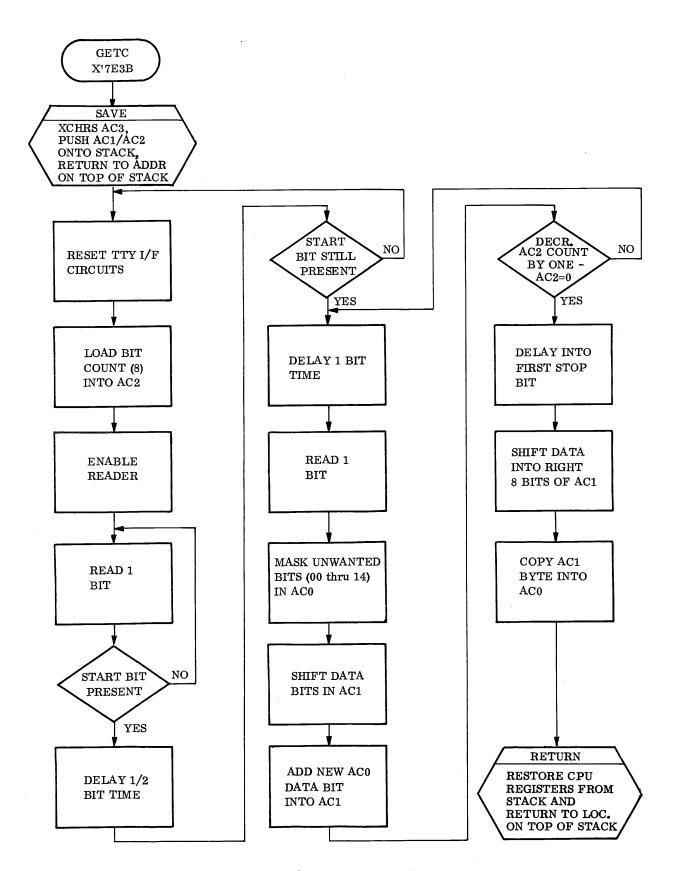

|         | 7.5.2.4   | ABSTTY ROM Program and Subroutines                  | 7-19 |

|         | 7.5.2.5   | RIN/ROUT Instruction Execution                      | 7-20 |

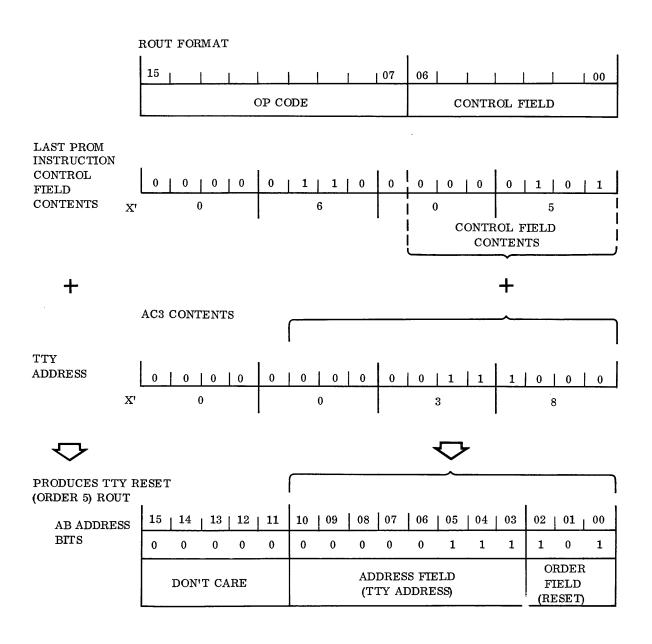

|         | 7.5.2.6   | Reset (Order 5) ROUT Decoding                       | 7-20 |

|         | 7.5.2.7   | Data Input From PPT Reader or TTY Keyboard          | 7-22 |

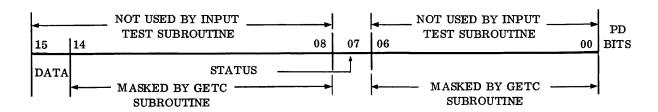

|         | 7.5.2.7.1 | TTY Status                                          | 7-22 |

|         | 7.5.2.8   | Data Output to TTY Printer or Paper Tape Punch      | 7-23 |

|         | 7.5.3     | Card Reader Interface Detailed Description          | 7-23 |

|         | 7.5.3.1   | Initialization and Addressing                       | 7-23 |

|         | 7.5.3.2   | ABSCR ROM Program and Subroutines                   | 7-23 |

|         | 7.5.3.3   | Card Reader Control                                 | 7-24 |

|         | 7.5.3.4   | RIN/ROUT Instruction Generation                     | 7-25 |

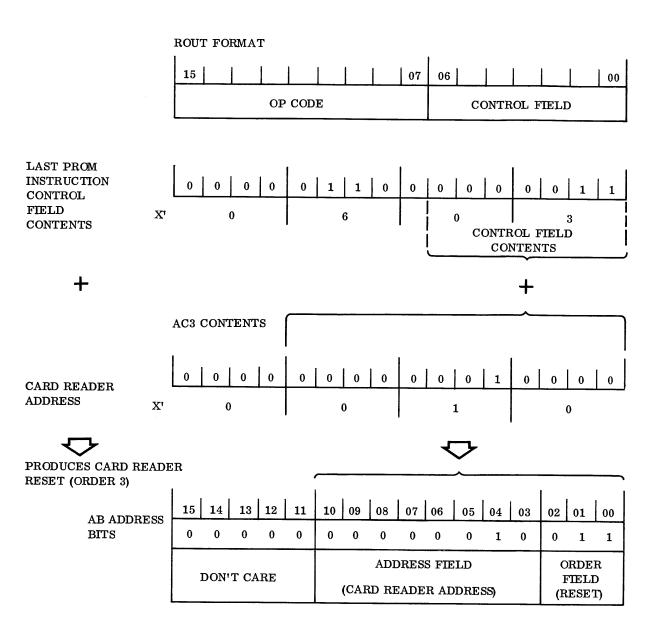

|         | 7.5.3.5   | Reset ROUT (Order 3) Decoding                       | 7-25 |

|         | 7.5.3.6   | Read Enable and Set Pick Decoding                   | 7-25 |

|         | 7.5.3.7   | Data Transfer                                       | 7-26 |

|         | 7.6       | CONTROL PANEL                                       | 7-27 |

|         | 7.6.1     | General Description                                 | 7-27 |

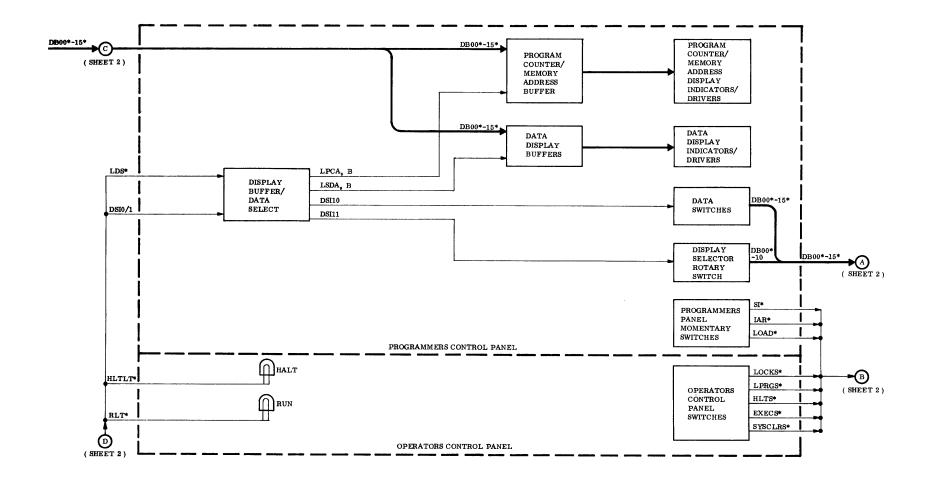

|         | 7.6.2     | Control Panel Detailed Description                  | 7-29 |

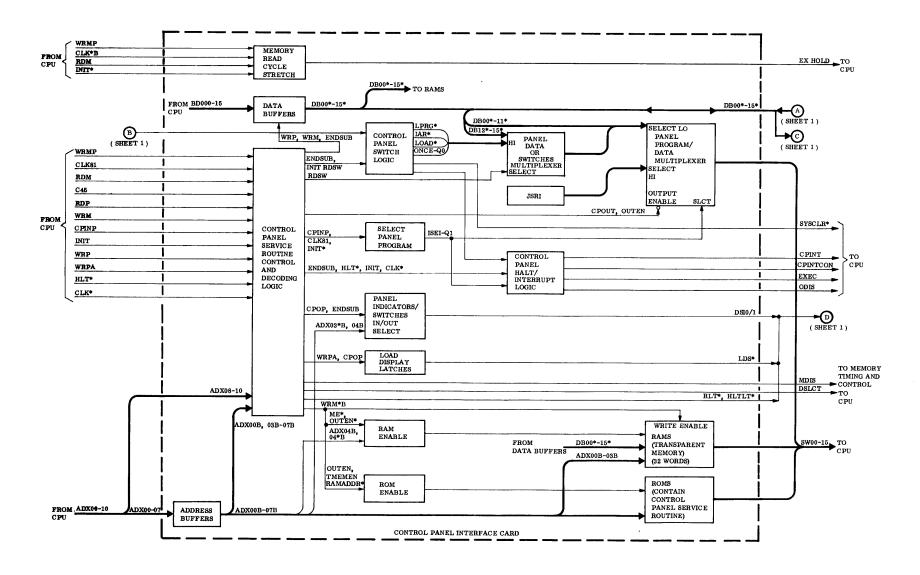

|         | 7.6.3     | Control Panel Interface Card General Description    | 7-32 |

|         | 7.6.4     | Control Panel Interface Card Detailed Description   | 7-34 |

|         | 7.6.4.1   | Control Panel Intermets                             | 7-34 |

## CONTENTS (Continued)

| Chapter |          |                                                     | Page |

|---------|----------|-----------------------------------------------------|------|

|         | 7.6.4.2  | Control Panel Service Routine Entry                 | 7-36 |

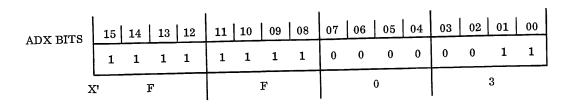

|         | 7.6.4.3  | Save CPU Contents in Transparent Memory             | 7-37 |

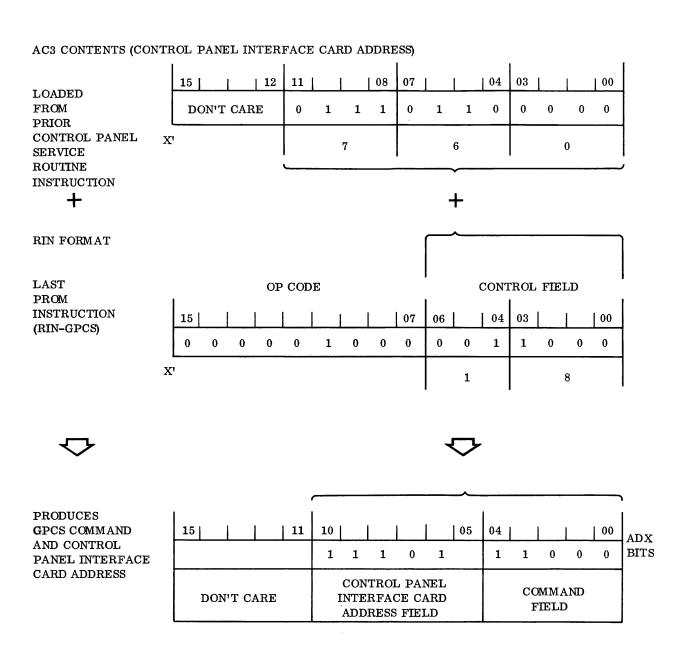

|         | 7.6.4.4  | Transfer of Commands and Data To/From Control Panel | 7-39 |

|         | 7.6.4.5  | Get Panel Control Switch                            | 7-39 |

|         | 7.6.4.6  | Load Program                                        | 7-41 |

|         | 7.6.4.7  | Single Instruction                                  | 7-42 |

|         | 7.6.4.8  | Memory Read Cycle Stretch                           | 7-43 |

|         | 7.6.4.9  | Get Data Switches                                   | 7-43 |

|         | 7.6.4.10 | Load Program Counter Display Register               | 7-44 |

|         | 7.6.4.11 | Load Display Register                               | 7-44 |

|         | 7.6.4.12 | Enable User Memory                                  | 7-45 |

|         | 7.6.4.13 | Restore CPU Contents                                | 7-46 |

## ILLUSTRATIONS

| Figure |                                                                      | Page |

|--------|----------------------------------------------------------------------|------|

| 1/1-1  | IMP-16P/200/300 Microcomputer                                        | 1-0  |

| 1/1-2  | IMP-16P Generalized Bus Structure                                    | 1-1  |

| 1/1-3  | Top Internal View of IMP-16P                                         | 1-5  |

| 1/2-1  | IMP-16P Operators Control Panel                                      | 2-1  |

| 1/2-2  | IMP-16P Programmers Control Panel                                    | 2-3  |

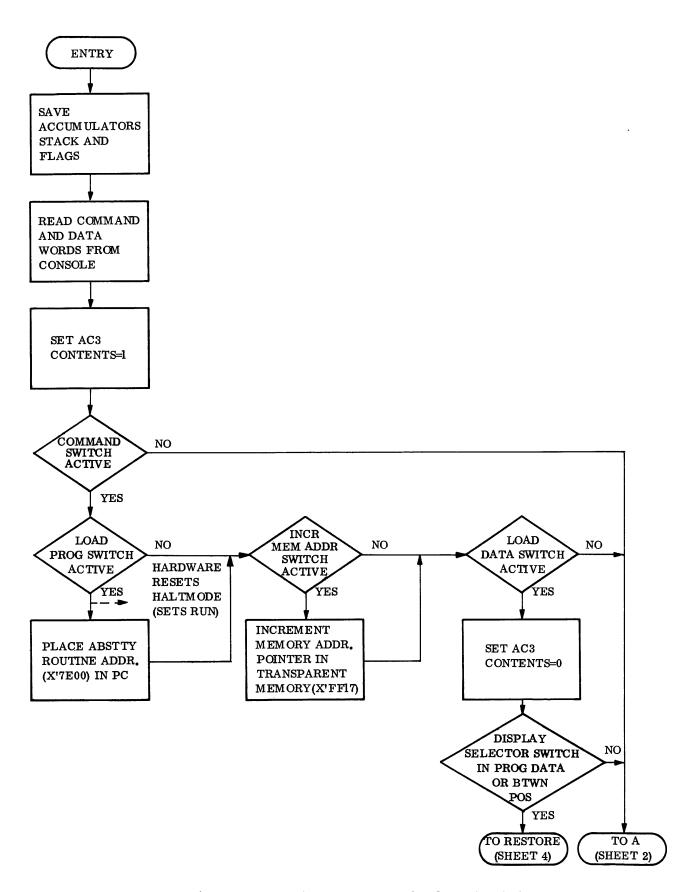

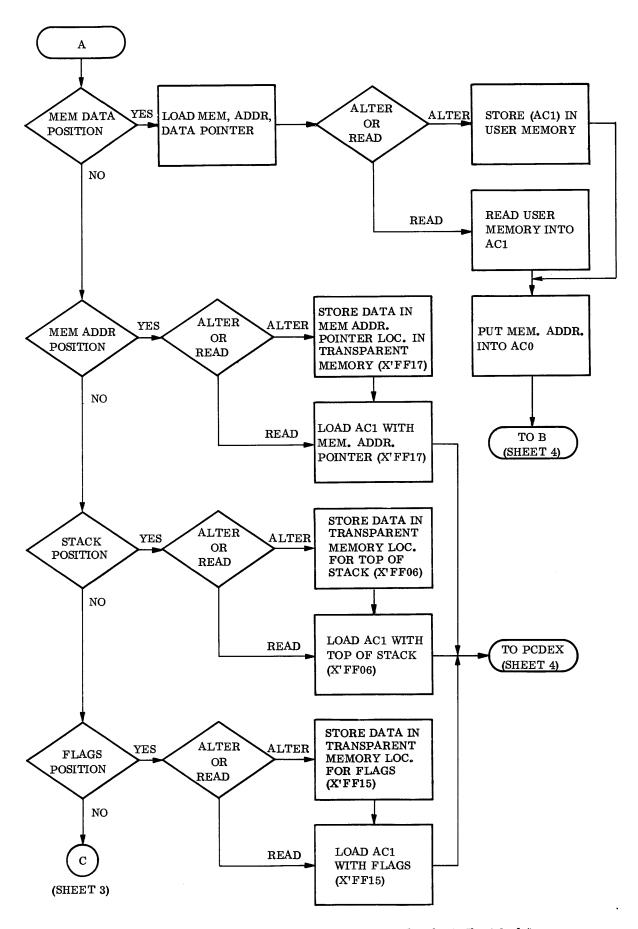

| 1/2-3  | Control Panel Service Routine Flowchart                              | 2-6  |

| 1/3-1  | IMP-16P Absolute Paper Tape Loader                                   | 3-3  |

| 1/3-2  | GETC Flowchart                                                       | 3-5  |

| 1/3-3  | IMP-16P to TTY Interconnect                                          | 3-8  |

| 1/3-4  | Physical Location of TTY and Card Reader Connectors                  | 3-8  |

| 1/3-5  | PPT Reader Relay Installation                                        | 3-9  |

| 1/3-6  | TTY Address Bit Configuration                                        | 3-9  |

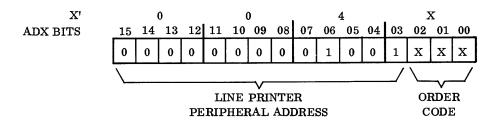

| 1/3-7  | Line Printer Address Bit Configuration                               | 3-9  |

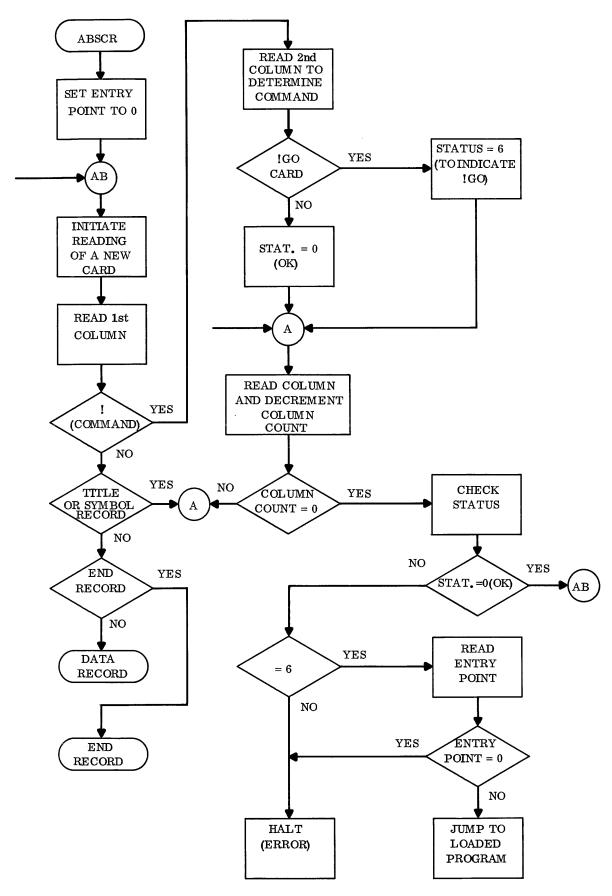

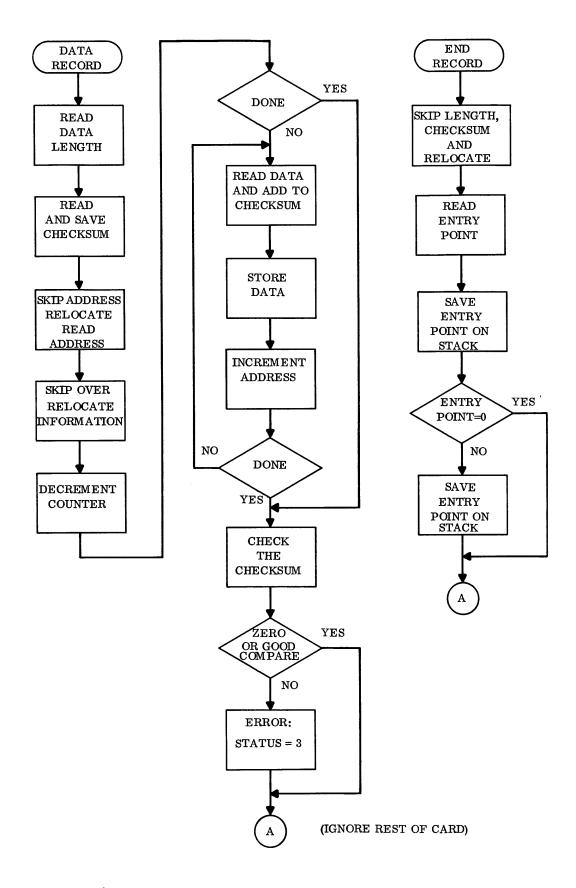

| 1/4-1  | Absolute Card Reader Loader Routine Flowchart                        | 4-3  |

| 1/4-2  | IMP-16P to Card Reader Interconnect                                  | 4-7  |

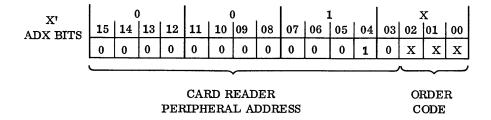

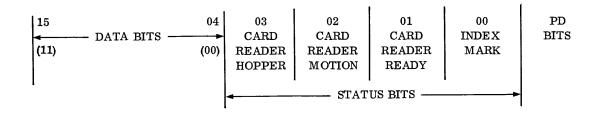

| 1/4-3  | Card Reader Address Bit Configuration                                | 4-8  |

| 1/6-1  | IMP-16P Buses for Interfacing Peripherals and Add-On Memory          | 6-2  |

| 1/6-2  | Memory Addressing Using Load and Store Instruction Format            | 6-3  |

| 1/6-3  | IMP-16P Memory Map                                                   | 6-4  |

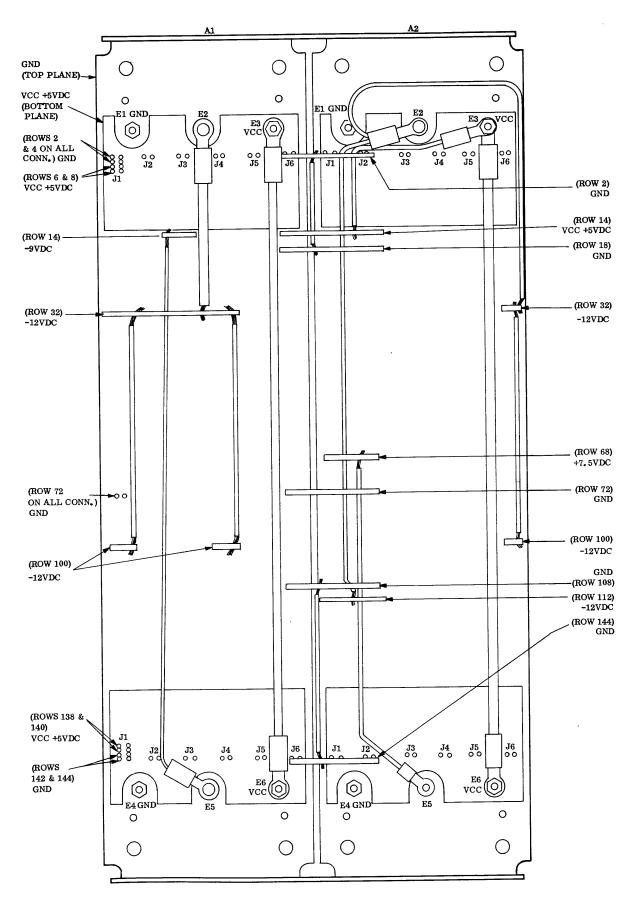

| 1/6-4  | IMP-16P Card Cage Backplane Voltage Terminals                        | 6-21 |

| 1/6-5  | Power On and System Clear Initialization                             | 6-25 |

| 1/6-6  | IMP-16P CPU Timing                                                   | 6-26 |

| 1/6-7  | CPU Timing for Peripheral Interfacing                                | 6-28 |

| 1/6-8  | RIN/ROUT Timing Sequence                                             | 6-29 |

| 1/6-9  | Memory Storage Cards Interconnect for 64K of Memory                  | 6-31 |

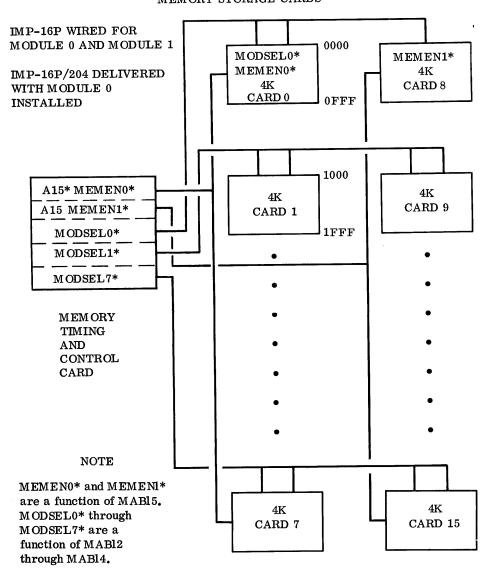

| 1/7-1  | IMP-16P Major Functional Units                                       | 7-2  |

| 1/7-2  | CPU Major Functional Units                                           | 7-4  |

| 1/7-3  | IMP-16P Memory Simplified Block Diagram                              | 7-6  |

| 1/7-4  | TTY/Card Reader Interface Card, Simplified Block Diagram             | 7-17 |

| 1/7-5  | CPU Composition of TTY Reset (Order 5) ROUT Instruction              | 7-21 |

| 1/7-6  | TTY Interface Word Format                                            | 7-22 |

| 1/7-7  | CPU Composition of Card Reader Reset (Order 3) ROUT Instruction      | 7-26 |

| 1/7-8  | Card Reader Interface Output Word Format                             | 7-27 |

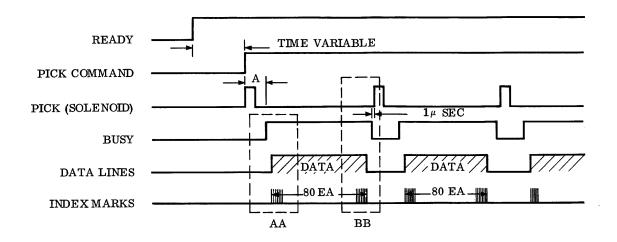

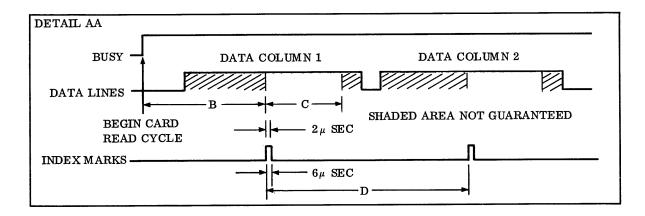

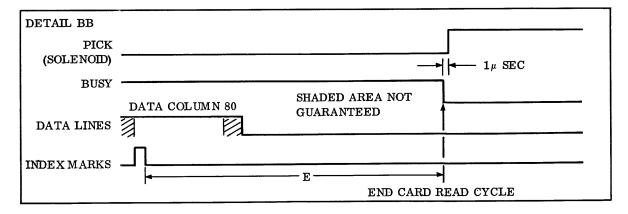

| 1/7-9  | Standard Interface Timing for Documation M Card Readers              | 7-28 |

| 1/7-10 | Control Panel and Control Panel Interface Card Overall Block Diagram | 7-30 |

| 1/7-11 | ADX Bit Configuration for Transparent Memory Address X'FF03          | 7-37 |

| 1/7-12 | CPU Composition of ADX00-10 Bits by GPCS RIN Instruction             | 7-40 |

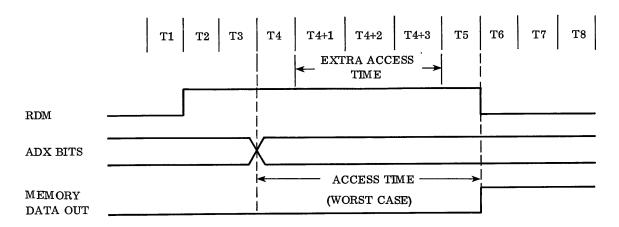

| 1/7-13 | Memory Access Time Extended by EXHOLD                                | 7-43 |

## TABLES

| Table         |                                                          | Page         |

|---------------|----------------------------------------------------------|--------------|

| 1/1-1         | IMP-16P Operational Features                             | 1-2          |

| 1/1-2         | IMP-16P Major Units and Options                          | 1-7          |

| <b>1/1-</b> 3 | IMP-16 Basic Instruction Set                             | 1-11         |

| 1/1-4         | IMP-16 Extended Instruction Set                          | <b>1-1</b> 2 |

| 1/1-5         | Related Publications                                     | 1-15         |

| 1/2-1         | Operators Control Panel Controls and Indicators          | 2-1          |

| 1/2-2         | Programmers Control Panel Controls and Indicators        | 2-3          |

| 1/3-1         | TTY Character Receive/Send Subroutines                   | 3-4          |

| 1/4-1         | Error Code Description                                   | 4-2          |

| 1/4-2         | RDCRD and CNVRT Calling Subroutine Sequences             | 4-6          |

| 1/6-1         | Summary of Direct Addressing Modes                       | 6-5          |

| 1/6-2         | Execution Times of IMP-16P Instructions                  | 6-6          |

| 1/6-3         | IMP-16P Instructions Used for NOPs                       | 6-12         |

| 1/6-4         | Delay Generation Using Successive Instructions           | 6-13         |

| 1/6-5         | Buffered Address Bus Lines, Location and Loading         | 6-17         |

| 1/6-6         | CPU Buffered Data Bus Lines, Location and Loading        | 6-17         |

| 1/6-7         | Peripheral Data Bus Lines, Location and Loading          | 6-18         |

| 1/6-8         | Memory Address In Bus Lines, Location and Loading        | 6-18         |

| 1/6-9         | Memory Data In Bus Lines, Location and Loading           | 6-19         |

| 1/6-10        | Memory Data Out Bus Lines, Location and Loading          | 6-20         |

| 1/6-11        | CPU External Control, Timing and Status Signals          | 6-22         |

| 1/6-12        | Memory Address Range Versus Control Signals              | 6-31         |

| 1/6-13        | IMP-16P System Power Requirements                        | 6-32         |

| 1/7-1         | Definitions of Included Signal Mnemonics/Abbreviations   | 7-8          |

| 1/7-2         | Memory Signals With Name Changes                         | 7-8          |

| 1/7-3         | Memory Address Decoding                                  | 7-9          |

| 1/7-4         | States of Write Pulse/Data Control Signals               | 7-10         |

| 1/7-5         | Output States of Reset or Initialized TTY Functions      | 7-18         |

| 1/7-6         | Program and Subroutines Contained in TTY ROMs            | 7-19         |

| 1/7 - 7       | TTY ABSTTY Program/Subroutines RIN/ROUT Instructions     | 7-20         |

| 1/7-8         | First Six GETC Subroutine Instructions                   | 7-20         |

| 1/7-9         | Programs Contained in Card Reader ROMs                   | 7-24         |

| 1/7-10        | Card Reader ABSCR Program RIN/ROUT Instructions          | 7-24         |

| 1/7-11        | First Four ABSCR Program Instructions                    | 7-25         |

| 1/7-12        | Display Buffer/Data Select Function Truth Table          | 7-32         |

| 1/7-13        | DSIO/DSI1 Decoded Operational Control                    | 7-35         |

| 1/7-14        | DB Bit Assignments for Control Panel Switches            | 7-35         |

| 1/7-15        | Transparent Memory Locations of Saved CPU Contents       | 7-38         |

| 1/7-16        | Control Panel Service Routine RIN/ROUT Instructions      | 7-39         |

| A-1           | IMP-16P Mnemonics/Abbreviations, Definitions and Sources | A-2          |

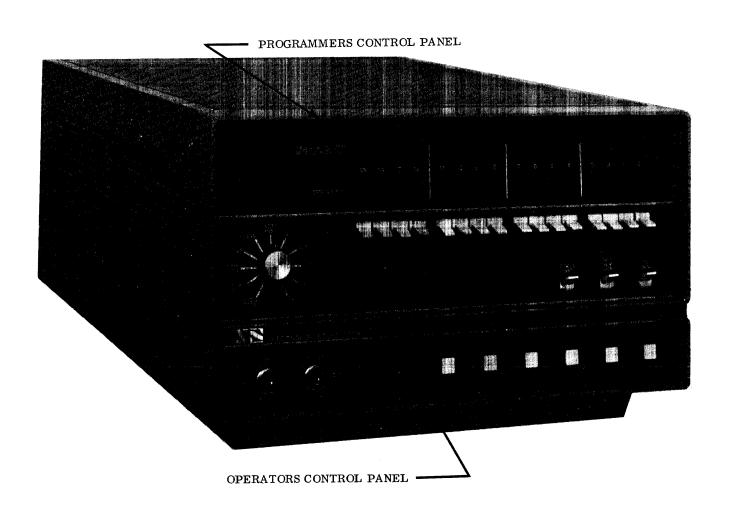

Figure 1/1-1. IMP-16P/200/300 Microcomputer

## Chapter 1

## GENERAL INFORMATION

## 1.1 IMP-16P MICROCOMPUTER

## 1.1.1 General Description

The IMP-16P Microcomputer is a prototyping tool specifically designed to facilitate development of computer-oriented systems incorporating the IMP-16 instruction set in any hardware form including chips, cards, or systems. The IMP-16P (see figure 1/1-1) provides an economical and convenient means of expediting the development of software and hardware for the intended microprocessor system. The inherent features make the IMP-16P a flexible tool that is suitable for use in a wide variety of microprocessor system designs.

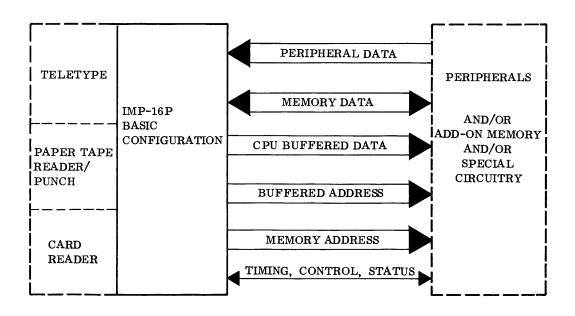

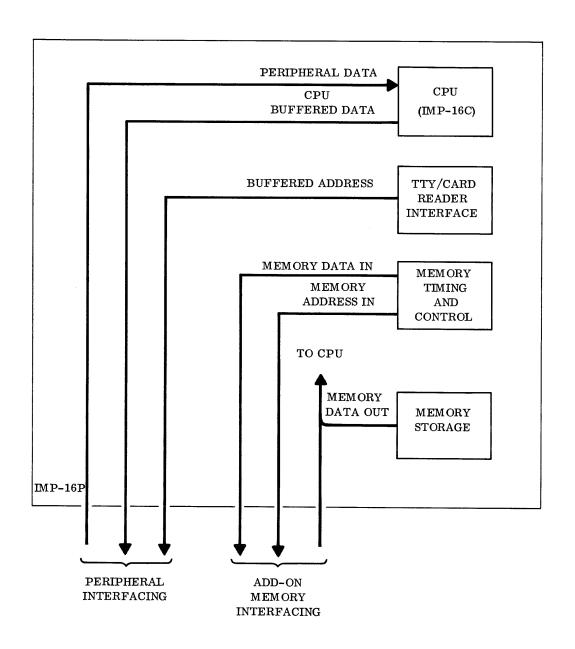

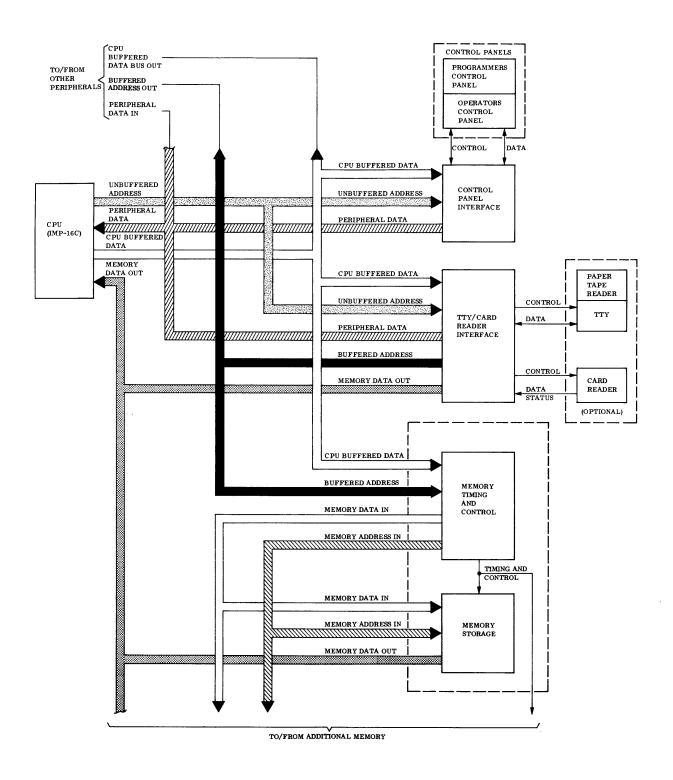

The bus structure of the IMP-16P (see figure 1/1-2) permits the expansion flexibility required to accommodate diverse microprocessor system designs. Six buses are available for use by peripherals, add-on memory or special circuits. The Peripheral Data Bus is provided to route data from peripherals to the microprocessor, hereafter also referred to as the Central Processing Unit (CPU). The Memory Data Bus permits two-way communication between the CPU and memory. The CPU Buffered Data Bus transfers CPU data to peripherals. The Buffered Address Bus is used to address peripherals while the Memory Address Bus provides addressing for add-on memory. Timing, control, and status flag signals are interchanged between the IMP-16P and peripherals to achieve proper software execution and peripheral device control.

Figure 1/1-2. IMP-16P Generalized Bus Structure

Teletype (TTY) and Card Reader peripherals, as well as add-on memory, are optionally available but not supplied as part of the basic IMP-16P Microcomputer. The combination of a TTY and an IMP-16P provides the minimum equipment and software necessary for immediate evaluation and design implementation of the IMP-16.

#### NOTE

Chapter 5, System Verification, contains the instructions and procedures required to verify proper operation of the basic IMP-16P upon initial receipt.

#### 1.1.2 Operational Features

The basic IMP-16P Microcomputer is available as either the IMP-16P/200 or the IMP-16P/300. The two basic versions differ only in the microprocessor supplied with the IMP-16P. The IMP-16P/200 contains the IMP-16C/200 Microprocessor, having one Control Read-Only Memory (CROM), whereas the IMP-16P/300 contains the IMP-16C/300 Microprocessor, having two CROMs. The one CROM on the IMP-16C/200 Microprocessor is programmed to implement a basic instruction set. The second CROM on the IMP-16C/300 Microprocessor implements the extended instruction set.

The IMP-16P Microcomputers can be user-altered to suit individual requirements. To facilitate alteration or expansion, the basic IMP-16P is supplied with five blank internal card slots. The blank card slots may be used for additional memory, or, by using optionally available prototyping cards, special peripheral interfacing or other custom circuits may be fabricated to expand the IMP-16P to meet the system design requirements within the limits of the power supplies. The basic IMP-16P contains interfacing for a Card Reader and TTY. The Card Reader and TTY are dedicated for IMP-16P software input or output and debugging of the prototype software.

The Programmers and Operators Control Panels (see figure 1/1-1) facilitate software development/debugging and provide a convenient means of controlling IMP-16P operation. Complete descriptions of the controls and indicators on the Programmers and Operators Control Panels are presented in chapter 2, Control Panel Operation. Refer to table 1/1-1 for a complete listing of the basic IMP-16P operational features

Table 1/1-1. IMP-16P Operational Features

| Feature         | Description                                                                                               |  |

|-----------------|-----------------------------------------------------------------------------------------------------------|--|

| Word Length     | 16 bits                                                                                                   |  |

| Instruction Set | 43 in IMP-16P/200 (implemented by CPU-resident microprogram)                                              |  |

|                 | 60 available in IMP-16P/300 (includes<br>43 as for IMP-16P/200 and 17 additional<br>instructions)         |  |

| Arithmetic      | Parallel, binary, fixed point, twos complement                                                            |  |

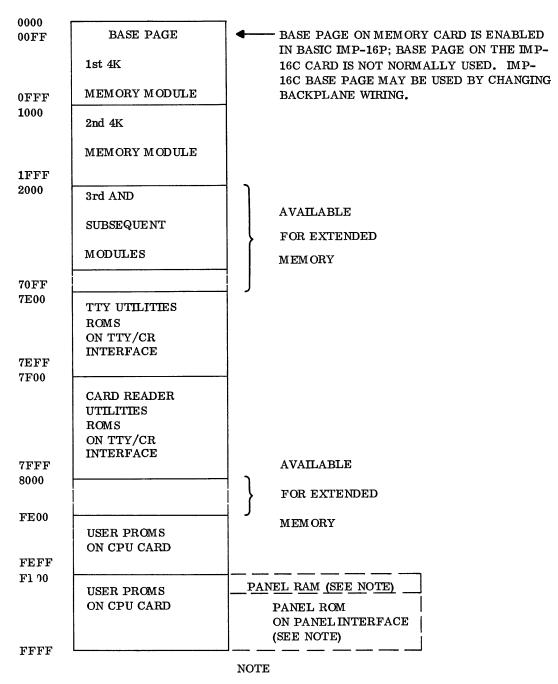

| Memory          | 16-bit words of semiconductor memory expandable in increments of 4,096 words to a maximum of 65,536 words |  |

Table 1/1-1. IMP-16P Operational Features (Continued)

| Feature                                  | Description                                                                                               |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Addressing Modes                         | • Page size of 256 words                                                                                  |

|                                          | Direct and indirect modes                                                                                 |

|                                          | Base page - 256 words                                                                                     |

|                                          | • Current page - 256 words                                                                                |

|                                          | • Relative to Accumulator 2 or 3* - 256                                                                   |

|                                          | words  * Indexing gives maximum range of 65,536 words in page sizes of 256                                |

|                                          | words each                                                                                                |

| Typical Instruction–<br>Execution Speeds | • Register-to-register addition - 4.55 $\mu$ s                                                            |

| 2.100 1.100 1.700 1.11                   | • Memory-to-register addition - 7.7 μs                                                                    |

|                                          | • Register input/output - 10.5 μs                                                                         |

| Operating Speed                          | 1.4 μs microcycle time                                                                                    |

| Input/Output and<br>Control              | • 16-bit CPU Buffered Data Bus                                                                            |

| Control                                  | • 16-bit Peripheral Data Bus                                                                              |

|                                          | • 16-bit Buffered Address Bus                                                                             |

|                                          | • 16-bit Memory Data Bus                                                                                  |

|                                          | • 16-bit Memory Address Bus                                                                               |

|                                          | • 16 general purpose control flags                                                                        |

|                                          | • 1 general interrupt condition                                                                           |

|                                          | • 1 vectored interrupt input                                                                              |

|                                          | • 4 general purpose jump condition inputs                                                                 |

| Input Power (at 25°C)                    | 105 to 125 VAC at 60 Hz (220 VAC, 50 Hz optional)                                                         |

| Temperature                              | • Operating: 0° to 50° C                                                                                  |

|                                          | • Storage: -20° to 70° C                                                                                  |

| Humidity                                 | Maximum of 90% relative humidity without condensation                                                     |

| Dimensions of Chassis                    | 12 inches (30.5 centimeters) high<br>17 inches (43.2 centimeters) wide<br>24 inches (61 centimeters) deep |

#### 1.2 MAJOR UNITS AND OPTIONS

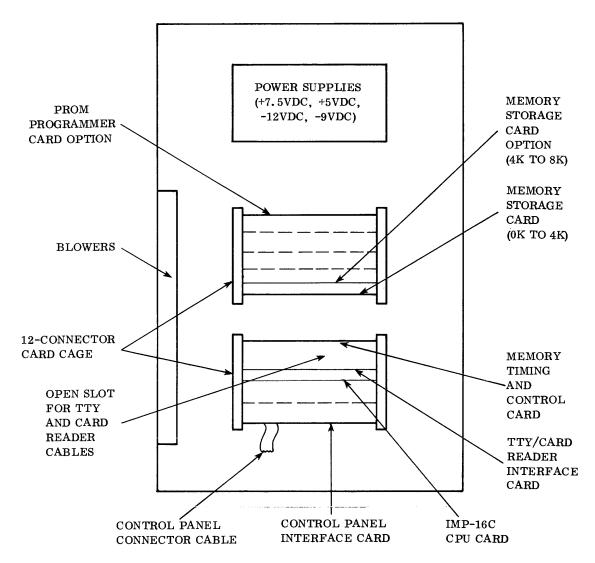

The basic IMP-16P configuration includes Programmers and Operators Control Panels and a chassis. The chassis houses the internal direct current power supplies and a card cage. Figure 1/1-3 illustrates a top view of the IMP-16P internal complement. The following paragraphs give general descriptions of the major assemblies in the basic IMP-16P Microcomputer. For detailed functional descriptions, refer to chapter 7, Functional Description.

## 1.2.1 Card Cage

The 12-connector card cage, supplied with the basic IMP-16P, contains five 8-1/2-inch by 11-inch circuit cards supplied as part of the basic microcomputer configuration. The circuit cards supplied are as follows:

- IMP-16C/200 or /300 CPU Card

- Memory Timing and Control Card

- · Memory Storage Card

- Control Panel Interface Card

- TTY/Card Reader Interface Card

#### NOTE

The basic IMP-16P is supplied with the card cage wired to accommodate an additional 4096 words of memory and the PROM Programmer Card.

The five blank connectors shown in figure 1/1-3 are provided for expansion as previously described. The five blank connectors must be user-wired, with the exception of the +5-volt power supply voltage and ground lines, when IMP-16P expansion is desired. If more expansion is required, optional 6-connector card cages are available for installation into the basic IMP-16P configuration. Several different types of prototyping cards are available and can be plugged into the blank card slots for IMP-16P expansion.

## NOTE

When expansion of the basic IMP-16P is to be implemented, first review chapter 6, Interface Considerations, to determine power supply requirements.

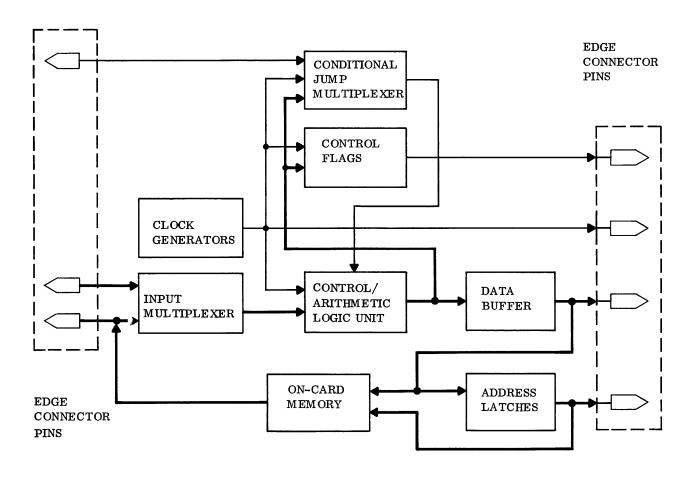

## 1.2.2 IMP-16C/200 or /300 CPU Card

The IMP-16C/200 or /300 CPU Card is the microprocessor around which the intended system software and hardware are designed. For more detailed information, refer to the IMP-16C Application Manual, National Semiconductor Publication Order No. IMP-16C/921C.

NOTE

BROKEN LINES IN CARD CAGE

INDICATE LOCATIONS

AVAILABLE FOR ADDITIONAL

CARDS

Figure 1/1-3. Top Internal View of IMP-16P

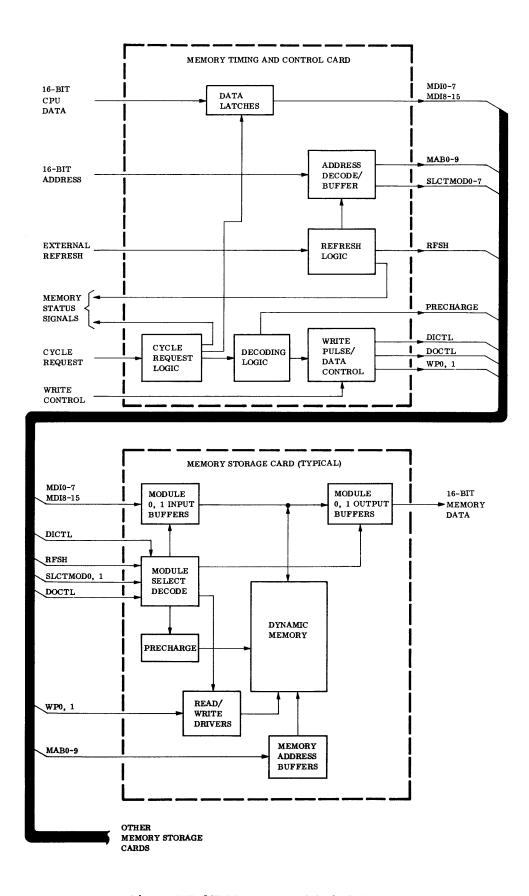

## 1.2.3 Memory Timing and Control Card

The Memory Timing and Control Card generates, under IMP-16C/200 or /300 CPU Card control, the signals required for proper operation of the Memory Storage Cards. In addition, intervals between refresh cycles, which are required by the Dynamic Memory on the Memory Storage Cards, are provided by the Memory Timing and Control Card. One Memory Timing and Control Card can service up to eight Memory Storage Cards.

## 1.2.4 Memory Storage Card

The Memory Storage Card utilizes Dynamic Semiconductor Random Access Memory (RAM) to provide 4096 16-bit words of Read/Write Memory storage. The basic IMP-16P is factory-wired to accommodate two 4096-word Memory Storage Cards.

## 1.2.5 Control Panel Interface Card

The Control Panel Interface Card provides interfacing between the Programmers and Operators Control Panels and the microprocessor. The interfacing permits the Program Counter, accumulators, flags, top of the stack, or data to be displayed and/or modified at the Programmers Control Panel.

## 1.2.6 TTY/Card Reader Interface Card

The TTY/Card Reader Interface Card provides interfacing between the microprocessor and a TTY and/or Card Reader. The TTY and Card Reader provide a means for loading IMP-16P diagnostics, prototype system software, and the Debug Routine for the prototype software, into the IMP-16P via the Paper Tape (PPT) Reader, TTY or Card Reader.

## 1.2.7 Programmers Control Panel

The Programmers Control Panel contains an array of data switches, data and address indicators, and function switches. The Programmers Control Panel switches and indicators may be used to address, load, and examine the contents of the microprocessor accumulators, Program Counter, flags, and top of the stack, or Memory Storage Card memory locations.

#### NOTE

Throughout the manual, the X' preceding an address or data value denotes a hexadecimal number.

## 1.2.8 Operators Control Panel

The Operators Control Panel controls basic IMP-16P operations such as power on/off, Programmers Control Panel lock/unlock, run, halt, system initialization, and loading data via a PPT Reader. Keylock switches are incorporated for locking and unlocking the Programmers Control Panel and turning on or off IMP-16P power. Two additional auxiliary switches (AUX1 and AUX2) may be user-wired, as required.

## 1.2.9 Power Supplies

The basic IMP-16P comes equipped with +7.5-, +5-, -12-, and -9-volt power supplies which fulfill the secondary voltage and current requirements of the basic IMP-16P configuration. The +5- and -12-volt supplies employ foldback current limiting. The +5- and -12-volt supplies also are equipped with overvoltage protection.

## 1.2.10 Units and Options

The basic and optional hardware, firmware, and software items for the IMP-16P are listed in table 1/1-2.

Table 1/1-2. IMP-16P Major Units and Options

| Item | Units, Contents, Options                                                                                                                                                                                 | Order Number                                                                                                                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| . 1  | Basic IMP-16P Microcomputer                                                                                                                                                                              | IMP-16P/yxx                                                                                                                                       |

|      | HARDWARE:                                                                                                                                                                                                | NOTE                                                                                                                                              |

|      | • Chassis, wired for the following: two 4096 word Memory Storage Cards, Card Reader/TTY Interface Card, Memory Timing and Control Card, Control Panel Interface Card, PROM Programmer Card, and CPU Card | The IMP-16P is available with one or more 4K RAM memory modules, as IMP-16P/yxx.  'xx' is the approximate number of thousands of memory words in- |

|      | • Power Supply Assembly                                                                                                                                                                                  | cluded with the system. Thus, an<br>8K system would be designated                                                                                 |

| :    | • CPU Card                                                                                                                                                                                               | IMP-16P/y08.  'y' is '2' if the system uses an                                                                                                    |

|      | • IMP-16C/200 CPU Card includes<br>one CROM (containing standard<br>instruction set), socket for second<br>CROM and four sockets for ROMs or<br>PROMs (MM5213 or MM5203)                                 | imP-16C/200 CPU Card (no extended instruction), or is a '3' if the system includes an IMP-16C/300 CPU Card (has extended instruction set).        |

|      | or                                                                                                                                                                                                       |                                                                                                                                                   |

|      | • IMP-16C/300 CPU Card includes two<br>CROMs (containing standard and ex-<br>tended instruction sets) and four<br>sockets for ROMs or PROMs (MM5213<br>or MM5203)                                        |                                                                                                                                                   |

|      | • 4096-Word Read/Write Memory Storage<br>Card                                                                                                                                                            |                                                                                                                                                   |

|      | • Memory Timing and Control Card                                                                                                                                                                         |                                                                                                                                                   |

|      | • TTY/Card Reader Interface Card                                                                                                                                                                         |                                                                                                                                                   |

|      | Control Panel Interface Card                                                                                                                                                                             |                                                                                                                                                   |

|      | • 12-Connector Card Cage                                                                                                                                                                                 |                                                                                                                                                   |

|      | Operators Control Panel                                                                                                                                                                                  |                                                                                                                                                   |

Table 1/1-2. IMP-16P Major Units and Options (Continued)

| Item | Units, Contents, Options                                                                         | Order Number               |

|------|--------------------------------------------------------------------------------------------------|----------------------------|

|      | Programmers Control Panel                                                                        |                            |

|      | REFERENCE MANUALS:                                                                               |                            |

|      | • IMP-16P Users Manual                                                                           |                            |

|      | IMP-16C Application Manual                                                                       |                            |

|      | • IMP-16 Programming and Assembler<br>Manual                                                     |                            |

|      | • IMP-16 Utilities Reference Manual                                                              |                            |

|      | • Tymshare Users Manual                                                                          |                            |

|      | • IMP-16C Interfacing Guide                                                                      |                            |

|      | SOFTWARE:                                                                                        |                            |

|      | • IMP-16P Software Debug Routine                                                                 |                            |

|      | • Self-Assembler                                                                                 |                            |

|      | Diagnostic Programs                                                                              |                            |

|      | • Paper Tape Source Editor                                                                       |                            |

|      | FIRMWARE:                                                                                        |                            |

|      | Control Panel Service Routine                                                                    |                            |

|      | Basic Loaders (Paper Tape and Card<br>Reader)                                                    |                            |

|      | Basic Teletype and Card Reader Service<br>Routines                                               |                            |

| 2    | IMP-16C/200 or IMP-16C/300 Micro-<br>processor Card                                              | IMP-16C/200 or IMP-16C/300 |

| 3    | ROM Diagnostic Program (ROMDI)                                                                   | IMP-16F/501                |

|      | 4-RCM set for verifying standard in-<br>struction set operation of IMP-16C/200<br>or IMP-16C/300 |                            |

| 4    | ROM Diagnostic Program (ROMDIX)                                                                  | IMP-16F/502                |

|      | 4-ROM set for verifying extended instruction set operation (IMP-16C/300 only)                    |                            |

Table 1/1-2. IMP-16P Major Units and Options (Continued)

| Item | Units, Contents, Options                                                                                       | Order Number |

|------|----------------------------------------------------------------------------------------------------------------|--------------|

| 5    | ROM Utility Program (CUTIL) - for<br>IMP-16C only                                                              | IMP-16F/000  |

|      | Contains TTY, Control Panel, and binary paper tape punch routines (2 ROMs)                                     |              |

| 6    | ROM Program Debugging Routine (DEBUGC) - for IMP-16C only                                                      | IMP-16F/002  |

|      | Use with CUTIL for simple debugging aid (2 ROMs)                                                               |              |

| 7    | ROM Utility Program (CMEMDI) - for<br>IMP-16C only                                                             | IMP-16F/500  |

|      | Memory diagnostic, Control Panel, and demonstration programs (2 ROMs)                                          |              |

| 8    | IMP-16 Assembler (Cross Assembler written in FORTRAN)                                                          | IMP-16S/900A |

|      | • Source deck                                                                                                  |              |

|      | • Listing                                                                                                      |              |

|      | • IMP-16 Programming and Assembler<br>Manual                                                                   |              |

|      | • Card decks with listings for format conversion routines                                                      |              |

| 9    | Card Reader (Documation Model M300L - 300 cards per minute)                                                    | IMP-00/825   |

| 10   | Teletype (ASR Model 33)                                                                                        | IMP-00/810   |

| 11   | 4K Memory Storage Card (RAM)                                                                                   | IMP-16P/004  |

| 12   | Memory Timing and Control<br>Card (controls up to eight IMP-16P/004<br>Memory Storage Cards)                   | IMP-16P/004T |

| 13   | Prototyping Card - 64-socket blank circuit<br>card for use with wire-wrapped sockets<br>(sockets not included) | IMP-00H/891  |

| 14   | Prototyping Card - 90-socket blank circuit<br>card for use with wire-wrapped sockets<br>(sockets not included) | IMP-00H/892  |

Table 1/1-2. IMP-16P Major Units and Options (Continued)

| Item | Units, Contents, Options                                                                                                                 | Order Number |

|------|------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 15   | Card Extender                                                                                                                            | IMP-00H/890  |

| 16   | 3-Card Connector Panel:                                                                                                                  | IMP-00H/881  |

|      | Card frame with three 144-pin wire-<br>wrap connectors and card guides,<br>spaced to accommodate wire-wrap<br>Prototyping Cards          |              |

| 17   | 6-Card Connector Panel:                                                                                                                  | IMP-00H/880  |

|      | Card frame as above but with six 144-<br>pin wire-wrap connectors and card<br>guides, spaced to accommodate PC<br>cards                  |              |

| 18   | Prototyping Card - blank circuit card for use with wire-wrapped sockets (sockets not included) and incorporating the following features: | IMP-00H/893  |

|      | • Provides up to 64 14-, 16-, or 18-pin socket positions                                                                                 |              |

|      | <ul> <li>Provides up to nine 24-pin socket positions</li> </ul>                                                                          |              |

|      | <ul> <li>Provides up to three 40-pin socket positions</li> </ul>                                                                         |              |

|      | <ul> <li>Provides thoroughly distributed positions for decoupling capacitors</li> </ul>                                                  |              |

|      | <ul> <li>All backplane connections are available for wire wrapping using 8 standard<br/>16-pin sockets</li> </ul>                        |              |

|      | • I/O connection via a 6/12 printed cir-<br>cuit card-edge connector                                                                     |              |

|      | <ul> <li>Provides up to two I/O connections via<br/>15/30 printed circuit card-edge connec-<br/>tors</li> </ul>                          |              |

|      | Provides up to two 3M wire-wrap card<br>headers of any number of connections<br>up to 50                                                 |              |

|      | Wire-wrap connections possible to all<br>I/O connectors                                                                                  |              |

| 19   | Connector - 15-position, double-row contacts                                                                                             |              |

## 1.3 INSTRUCTION SETS

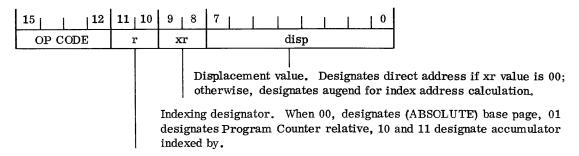

The available IMP-16P instruction sets include a basic instruction set and an extended instruction set. The basic instruction set contains 43 instructions that are implemented by one CROM in the IMP-16P/200 Microcomputer (see table 1/1-3). The extended instruction set contains an additional 17 instructions that are implemented by a second CROM in the IMP-16P/300 Microcomputer (see table 1/1-4). Thus, the difference between an IMP-16P/200 and an IMP-16P/300 is the addition of one CROM, containing the extended instruction set, to the IMP-16C CPU Card. The second CROM is a 24-pin IC that can be plugged into an existing socket on the IMP-16P/200 CPU Card, thereby creating an IMP-16P/300. Since the basic instructions are common to all IMP-16 microprocessors, the IMP-16P can be used to develop programs for other IMP-16 microprocessor systems. For a more comprehensive description of the instructions and associated word formats, refer to chapter 6, Interface Considerations.

Table 1/1-3. IMP-16 Basic Instruction Set

| Instruction                              | Mnemonic |

|------------------------------------------|----------|

| Memory Reference Instructions            |          |

| Load                                     | LD       |

| Load Indirect <sup>a</sup>               | LD       |

| Store                                    | ST       |

| Store Indirect <sup>a</sup>              | ST       |

| Add                                      | ADD      |

| Subtract                                 | SUB      |

| Jump                                     | JMP      |

| Jump Indirect <sup>a</sup>               | JMP      |

| Jump to Subroutine                       | JSR      |

| Jump to Subroutine Indirect <sup>a</sup> | JSR      |

| Increment and Skip if Zero               | ISZ      |

| Decrement and Skip if Zero               | DSZ      |

| Skip if AND is Zero                      | SKAZ     |

| Skip if Greater                          | SKG      |

| Skip if Not Equal                        | SKNE     |

| AND                                      | AND      |

| OR                                       | OR       |

| Register Reference Instructions          |          |

| Push onto Stack Register                 | PUSH     |

| Pull from Stack                          | PULL     |

| Add immediate Skip if Zero               | AISZ     |

| Load Immediate                           | LI       |

| Complement and Add Immediate             | CAI      |

| Register Copy                            | RCPY     |

| Exchange Register and Top of Stack       | XCHRS    |

| Exchange Registers                       | RXCH     |

| Register AND                             | RAND     |

| Register EXCLUSIVE OR                    | RXOR     |

| Register Add                             | RADD     |

| Shift Left                               | SHL      |

| Shift Right                              | SHR      |

| Rotate Left                              | ROL      |

| Rotate Right                             | ROR      |

|                                          |          |

a - The symbol @ must precede the designation of the memory location whose contents become the effective address by indirection. The @ must precede the operand (in the operand field).

Table 1/1-3. IMP-16 Basic Instruction Set (Continued)

| Instruction                                                                                           | Mnemonic                            |

|-------------------------------------------------------------------------------------------------------|-------------------------------------|

| Input/Output, Flag, and Halt Instructions                                                             |                                     |

| Set Flag<br>Pulse Flag<br>Push Flags on Stack<br>Pull Flags from Stack<br>Register In<br>Register Out | SFLG PFLG PUSHF PULLF RIN ROUT HALT |

| Halt Transfer of Control Instructions                                                                 | nabi                                |

| Branch-On-Condition<br>Return from Subroutine<br>Return from Interrupt<br>Jump to Subroutine Implied  | BOC<br>RTS<br>RTI<br>JSRI           |

Table 1/1-4. IMP-16 Extended Instruction Set

| Instruction                           | Mnemonic |

|---------------------------------------|----------|

| Multiply                              | MPY      |

| Divide                                | DIV      |

| Double Precision Add                  | DADD     |

| Double Precision Subtract             | DSUB     |

| Load Byte                             | LDB      |

| Store Byte                            | STB      |

| Set Status Flag                       | SETST    |

| Clear Status Flag                     | CLRST    |

| Skip if Status Flag True              | SKSTF    |

| Set Bit                               | SETBIT   |

| Clear Bit                             | CLRBIT   |

| Complement Bit                        | CMPBIT   |

| Skip if Bit True                      | SKBIT    |

| Interrupt Scan                        | ISCAN    |

| Jump Indirect to Level Zero Interrupt | JINT     |

| Jump Through Pointer                  | JMPP     |

| Jump to Subroutine Through Pointer    | JSRP     |

## 1.4 IMP-16P BASIC SOFTWARE

## 1.4.1 Diagnostic Programs

Diagnostic programs are available for extensively testing the CPU and the Read/Write Memory to verify proper operation of both. Detailed descriptions of the CPU and Memory diagnostics are presented together with loading procedures in chapter 5, System Verification.

## 1.4.2 Loaders

A variety of loaders is available for entering programs produced by an assembler into Read/Write Memory. The program input media may be either punched cards or paper tape. The program format may be either absolute or relocatable modules. The following firmware loaders (resident in ROMs within the IMP-16P) are provided:

Paper Tape Loader - Loads an absolute program module via a PPT Reader.

Pressing the LOAD PROG Switch on the Operators

Control Panel implements the Paper Tape Loader

firmware.

Card Reader Loader - Loads one or more absolute program modules via a Card

Reader.

#### 1.4.3 Resident Assembler

The resident assembler runs with a minimum of 4K words of memory and a TTY, accepts free format source statements from either the keyboard or paper tape and produces an unlinked Relocatable Load Module on paper tape and an object listing on the TTY printer. Three passes over the source program are required by the resident assembler. The assembler listing is produced on pass two and a binary output paper tape is produced on pass three. If the object listing or Relocatable Load Module is to be suppressed, only two passes are required.

A second resident assembler is supplied with the IMP-16P Microcomputers containing a memory storage capacity of 8192 words, or greater. The second resident assembler permits the use of a Card Reader, high speed printer and the . FORM directive.

## 1.4.4 Debug

Debug is a relocatable object program that supervises the operation of a user-generated program during software checkout. Debug provides the following facilities for testing programs:

- Printing selected areas of memory in hexadecimal or ASCII format.

- Modifying the contents of selected areas in memory.

- Modifying CPU registers and stack.

- Inserting instruction breakpoint halts.

- · Taking memory snapshots during execution of user-generated programs.

- · Initiating execution at any point in the program.

- · Searching memory.

For more information concerning Debug, refer to chapter 5, System Verification, or the IMP-16 Utilities Reference Manual, National Semiconductor Publication Order No. IMP-16S/025Y.

## 1.4.5 Source Editor (EDIT 16)

EDIT 16 is a paper tape source editor program that can be used with the IMP-16P. EDIT 16 enables editing of a previously prepared source program (or any text) or generates and edits new text. Once loaded, the program is self-starting and provides approximately 4000 characters of working storage in a 4K processor.

The normal editing procedure is to input text, edit the text, and output the edited text.

Prepared text, in punched paper tape format, is read into the IMP-16P through the TTY PPT Reader. New text is generated by typing lines of text on the TTY keyboard. Output text is punched on the TTY paper tape punch.

EDIT 16 commands are line oriented. Automatic line renumbering is performed when lines are inserted, deleted and moved. For further information, refer to the IMP-16 Utilities Reference Manual, National Semiconductor Publication Order No. IMP-16S/025Y.

#### 1.5 MANUAL ORGANIZATION

This manual is separated into two volumes. Volume 1 contains the introductory, operational and functional descriptions required for tutorial purpose as well as the interface requirements and verification procedures. Volume 2 contains the schematic, block and timing diagrams for support of the text in volume 1 and any required interface design or maintenance.

The functional description is organized to provide contiguous coverage of a particular function, from general to detailed information. For an overview of general functions of the entire microcomputer, it is recommended that the user read the general descriptions only. Then, to obtain a detailed explanation, the user may read the general and detailed descriptions in their entirety.

The table and figure numbers referenced herein denote the volume, chapter and, then, the figure or table number, in that order. For example, figure 1/2-3 is interpreted as (contained in) volume 1/ (referenced in) chapter 2 - figure 3. Another example, figure 2/4-6 is interpreted as (contained in) volume 2/chapter 4 (volume 1 contains reference text) - figure 6.

Refer to engineering documentation package for revised data. Information supplied in this manual is current only to time of printing.

The remainder of volume 1 of this manual comprises six additional chapters which provide information as follows:

- Chapter 2, Control Panel Operation, describes the function and use of the controls and indicators contained on the Programmers and Operators Control Panels. In addition, the firmware that enables CPU-to-Control Panel communication is described.

- Chapter 3, Teletype Operation, provides operating procedures for a TTY connected to the IMP-16P. In addition, a description of the associated firmware is presented.

- Chapter 4, Card Reader Operation, provides operating procedures for a Card Reader connected to the IMP-16P. A description of the associated firmware is also given.

- Chapter 5, System Verification, contains procedures that can be used to verify proper operation of the IMP-16P. In addition, the diagnostic programs for the IMP-16P and the Debug program for user-developed software are discussed.

- Chapter 6, Interface Considerations, provides interfacing information relevant to the design of external equipment controllers and associated software.

- Chapter 7, Functional Description, provides an overall functional description of the IMP-16P. In addition, detailed functional descriptions of the major assemblies comprising the IMP-16P are presented.

The mnemonics and abbreviations used throughout volumns 1 and 2 are listed in appendix A, and circuit diagram of the various devices appearing on the schematic diagrams are in appendix B. Both appendixes are located following the diagrams in volume 2.

## 1.6 RELATED PUBLICATIONS

Table 1/1-5 lists the National Semiconductor publications related to the IMP-16P and this manual.

Table 1/1-5. Related Publications

| Title                                       | Order Number |

|---------------------------------------------|--------------|

| IMP-16 Programming and Assembler<br>Manual  | IMP-16S/102Y |

| IMP-16 Utilities Reference Manual           | IMP-16S/025Y |

| Timesharing Users Manual                    | IMP-16S/118Y |

| IMP-16C Application Manual                  | IMP-16C/921  |

| DEBUG C Utility Program Reference<br>Manual | IMP-16S/048Y |

| IMP-16 PROM Programmer Reference<br>Manual  | IMP-16P/955  |

## Chapter 2

## CONTROL PANEL OPERATION

## 2.1 INTRODUCTION

This chapter contains the IMP-16P operating procedures along with descriptions of controls and indicators located on the Operators and Programmers Control Panels. Also included is a description of the Control Panel Service Routine contained in Read-Only Memory (ROM) on the Control Panel Interface Card.

## 2.2 OPERATORS CONTROL PANEL

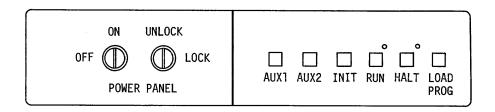

The Operators Control Panel, shown in figure 1/2-1, provides all controls necessary for loading and executing programs. Table 1/2-1 lists the Operators Control Panel controls and indicators and describes the associated function of each.

Figure 1/2-1. IMP-16P Operators Control Panel

Table 1/2-1. Operators Control Panel Controls and Indicators

| Control/Indicator                    | Function                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER<br>(two-position<br>keyswitch) | Prevents unauthorized application or removal of system power. In OFF position, system power is disconnected. In ON position, system power is connected. When switched from OFF to ON position, all CPU registers and interface control flags are cleared. After clearing, microcomputer enters Halt mode and awaits operator input via Programmers or Operators Control Panels. Key is removable from either position. |

| PANEL<br>(two-position<br>keyswitch) | Restricts destructive system access. In UNLOCK position, all panel controls (including Programmers Control Panel) are operable. In LOCK position, only RUN Control is operable. Key is removable from either position.                                                                                                                                                                                                 |

Table 1/2-1. Operators Control Panel Controls and Indicators (Continued)

| Control/Indicator                           | Function                                                                                                                                                                                                                            |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUX1, AUX2<br>(SPDT pushbutton<br>switches) | Wired to six connector plug which fits onto six consecutive pins of 144-pin backplane connector. Available for implementation as user function.                                                                                     |

| INIT<br>(SPDT pushbutton<br>switch)         | When pressed, IMP-16 enters Halt mode, all CPU registers and interface control flags are cleared, and CPU Program Counter is set equal to X'FFFE. Functions performed are identical to POWER ON, but without loss of memory data.   |

| RUN<br>(SPDT pushbutton<br>switch)          | When pressed, exeuction begins at location specified by CPU Program Counter contents.                                                                                                                                               |

| RUN<br>(lamp indicator)                     | Lights when program is running.                                                                                                                                                                                                     |

| HALT<br>(SPDT pushbutton<br>switch)         | When pressed, terminates program execution at end of current instruction. Produces same effect as execution of Halt Instruction, except Halt Flag is not pulsed.  Microcomputer enters Halt mode and awaits further operator input. |

| HALT<br>(lamp indicator)                    | Lights when halt occurs.                                                                                                                                                                                                            |

| LOAD PROG<br>(SPDT pushbutton<br>switch)    | Operable only when HALT Lamp is lit. When pressed and released, forces program branch to Absolute Paper Tape Loader program stored in ROM. Causes CPU 16-word pushdown stack to be cleared and accumulators to be altered.          |

## 2.3 PROGRAMMERS CONTROL PANEL

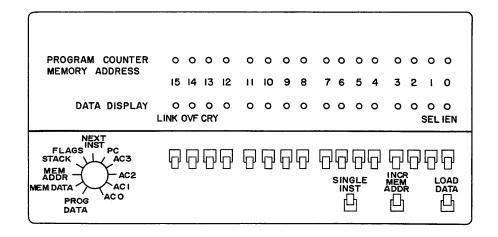

The Programmers Control Panel, shown in figure 1/2-2, provides complete program debug facilities in addition to normal operational features. The Programmers Control Panel interfaces with the Peripheral and CPU Buffered Data Buses via the Programmers Panel Interface Card. The Control Panel Service Routine for the Control Panel is stored in ROMs located on the Control Panel Interface Card. Communication between the Programmers Control Panel and Control Panel Interface Card is accomplished via a flat grey cable. Table 1/2-2 lists the Programmers Control Panel controls and indicators and describes the associated function of each.

Figure 1/2-2. IMP-16P Programmers Control Panel

Table 1/2-2. Programmers Control Panel Controls and Indicators

| Control/Indicator                                          | Function                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROGRAM COUNTER/<br>MEMORY ADDRESS<br>(16 lamp indicators) | Normally indicate current value of Program Counter.  However, when Display Selector Rotary Switch is in MEM DATA position, current memory address is displayed.                                                                                                                               |

|                                                            | NOTE                                                                                                                                                                                                                                                                                          |

|                                                            | When Display Selector Rotary Switch is in PROG DATA position, data displayed by PROGRAM COUNTER/MEMORY ADDRESS indicators has no meaning.                                                                                                                                                     |

| DATA DISPLAY<br>(16 lamp indicators)                       | Display information selected by position of Display Selector Rotary Switch. Bit assignments of internal flags are indicated when Display Selector Rotary Switch is in FLAGS position.                                                                                                         |

| Data Entry<br>(16 two-position<br>toggle switches)         | Load data into CPU register or memory storage location as specified by Display Selector Rotary Switch when LOAD DATA Pushbutton is pressed. Data Entry Switches load a '1' in up position and a '0' in down position.                                                                         |

| SINGLE INST<br>(momentary switch)                          | When pressed, instruction in memory storage location specified by CPU Program Counter contents is executed. SINGLE INST Switch is disabled by LOCK Keyswitch and is operable only when HALT Indicator is lit.                                                                                 |