Integrated Microprocessor IPC-16

# **PACE Technical Description**

June 1975

© National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

# **PREFACE**

This technical description defines and explains the utilization of the entire complement of hardware and software items that comprise and support the *single-chip* PACE (Processing and Control Element). PACE is a full-feature Control Processing Unit that is manufactured by the National Semiconductor Corporation.

The information contained herein is up-to-date at the time of publication but is subject to change without notice. Therefore, it is suggested that the National Semiconductor local sales office be contacted for the latest information pertaining to PACE.

# **CONTENTS**

| Chapter |         | Page                                                                         |

|---------|---------|------------------------------------------------------------------------------|

| 1       | INTROD  | OUCTION TO PACE                                                              |

|         | 1.1     | DESCRIPTION                                                                  |

|         | 1.2     | OUTSTANDING FEATURES OF PACE                                                 |

|         | 1.3     | PACE APPLICATIONS                                                            |

|         | 1.4     | DYNAMICS OF PACE DEVELOPMENT                                                 |

|         | 1.5     | PACE FAMILY OF CHIPS                                                         |

|         | 1.5.1   | PACE Blue Chips                                                              |

|         | 1.5.2   | PACE Green Chips                                                             |

|         | 1.5.3   | PACE Memory Chips                                                            |

|         | 1.6     | PACE APPLICATION CARDS                                                       |

|         | 1.7     | PACE MICROPROCESSOR DEVELOPMENT SYSTEM                                       |

|         | 1.8     | SOFTWARE SUPPORT                                                             |

|         | 1.9     | SPECIFYING HARDWARE BEHAVIOR WITH SOFTWARE                                   |

|         | 1.10    | TYPES OF SOFTWARE                                                            |

|         | 1.10.1  | PACE Editor • • • • • • • • • • • • • • • • • • •                            |

|         | 1.10.2  | PACE Assemblers                                                              |

|         | 1.10.3  | PACE SM/PL Compiler                                                          |

|         | 1.10.4  | IMP-16/PACE Translator                                                       |

|         | 1.10.5  | PACE Loaders                                                                 |

|         | 1.10.6  | PACE Input/Output Routines                                                   |

|         | 1.10.7  | PACE DEBUG Program                                                           |

|         |         |                                                                              |

| 2       | PACE AI | ND FAMILY OF CHIPS                                                           |

| -       |         | •                                                                            |

|         | 2.1     | INTRODUCTION                                                                 |

|         | 2.2     | PACE MICROPROCESSOR                                                          |

|         | 2.2.1   | General Description                                                          |

|         | 2.2.2   | External Clock Requirements                                                  |

|         | 2.2.3   | Description of Hardwired Signals and Timing                                  |

|         | 2.2.4   | Descriptions of Status and Control Flags                                     |

|         | 2.2.5   | Input/Output Bus Structure                                                   |

|         | 2.2.6   | Data Representation                                                          |

|         | 2.3     | PACE INSTRUCTION SET                                                         |

|         | 2.3.1   | Memory Addressing                                                            |

|         | 2.3.2   | Instruction Summary 2 – 12                                                   |

|         | 2.4     | PACE SUPPORT CHIPS                                                           |

|         | 2.4.1   | System Timing Element (STE)                                                  |

|         | 2.4.2   | Bidirectional Transceiver Element (BTE/8)                                    |

|         | 2.4.3   | Interface Latch Element (ILE/8, ILE/16) · · · · · · · · · · · · · · · 2 - 16 |

|         | 2.4.4   | Address Latch Element (ALE)                                                  |

|         | 2.4.5   | RAM                                                                          |

|         | 2.4.6   | ROM · · · · · · · · · · · · · · · · · · ·                                    |

|         | 2.5     | PACE APPLICATION INFORMATION AND EXAMPLES 2 - 28                             |

|         | 2.5.1   | Minimum Chip Configuration • • • • • • • • • • • • • • • • • 2 – 28          |

|         | 2.5.2   | Input/Output Control Techniques                                              |

|         | 2.5.3   | Use of Jump Conditions and Flags                                             |

|         | 2.5.4   | Use of Interrupts                                                            |

|         | 2.5.5   | Implementation of Initialize and Cycle Extend Signals                        |

|         | 2.5.6   | Implementation of DMA                                                        |

|         | 2.5.7   | Minimal Control Panel                                                        |

|         |         |                                                                              |

# **CONTENTS (Continued)**

| Chapter                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page                                                                                                                     |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 3                                                                                           | PACE APPLICATION CARDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                          |

|                                                                                             | 3.1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-2                                                                                                                      |

| 4                                                                                           | PACE MICROPROCESSOR DEVELOPMENT SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                          |

| 5                                                                                           | PACE SUPPORT FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                          |

|                                                                                             | 5.1       TECHNICAL CONSULTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5 - 1<br>5 - 1<br>5 - 1<br>5 - 2                                                                                         |

| APPENDIX A                                                                                  | PACE HARDWARE/SOFTWARE PRODUCT SUMMARIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                          |

| APPENDIX B                                                                                  | PACE INSTRUCTION RELATED SUMMARIES AND PROGRAM EXAMPLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                          |

|                                                                                             | LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                          |

| Table                                                                                       | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                                                                                                     |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>3-1<br>4-1                                               | Descriptions of PACE Hardwired Signals  Descriptions of Status and Control Flags  Summary of Direct Addressing Modes  Address Bit Control Configurations  Locations of Interrupt Pointers  Sources of Accessory Equipment for PACE Application Cards  Power Requirements of Circuit Cards Usable in IPC-16P.                                                                                                                                                                                                                                                                                                                                         | 2 - 9<br>2 - 12<br>2 - 24<br>2 - 32<br>3 - 1                                                                             |

|                                                                                             | LIST OF ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ~                                                                                                                        |

| gure                                                                                        | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                                                                                                     |

| - 1<br>- 2<br>- 3<br>- 4<br>- 5<br>- 6<br>- 7<br>- 8<br>- 9<br>- 10<br>- 11<br>- 12<br>- 13 | PACE Chip and Circuit Layout PACE Functional Block Diagram Dynamics of Utilization of PACE. System Timing Element (STE) Provides All Timing Requirements. Bidirectional Transceiver Element (BTE) Provides High-fanout TTL Buses Address Latch Element (ALE) Provides Memory Address Latching Interface Latch Element (ILE) Provides Interface Storage for Peripherals Implementation of RAM and ROM With On-chip Address Latches Implementation of ROM and PROM Without On-chip Address Latches One-board PACE Application System PACE Computer Programs Software Used to Assemble or Compile on PACE PACE Software Implemented on a Host Computer. | . 1 - 2<br>. 1 - 5<br>. 1 - 6<br>. 1 - 7<br>. 1 - 7<br>. 1 - 8<br>. 1 - 8<br>. 1 - 9<br>. 1 - 11<br>. 1 - 12<br>. 1 - 13 |

# LIST OF ILLUSTRATIONS (Continued)

| Figure                       | Title                                                                                       | Page   |

|------------------------------|---------------------------------------------------------------------------------------------|--------|

| 1 – 14                       | PACE Loading Sequence                                                                       | 1 - 15 |

| 2 - 1                        | PACE Microprocessor Functional Block Diagram                                                | 2-2    |

| 2 - 2                        | External Clock Timing Parameters                                                            |        |

| 2-3                          | PACE Microprocessor Pin Assignments                                                         |        |

| 2-4                          | Address Output and Data Input Timing Diagram                                                |        |

| 2-5                          | Data Output Timing Diagram                                                                  |        |

| 2-6                          | Extend I/O Signal Timing Diagram                                                            |        |

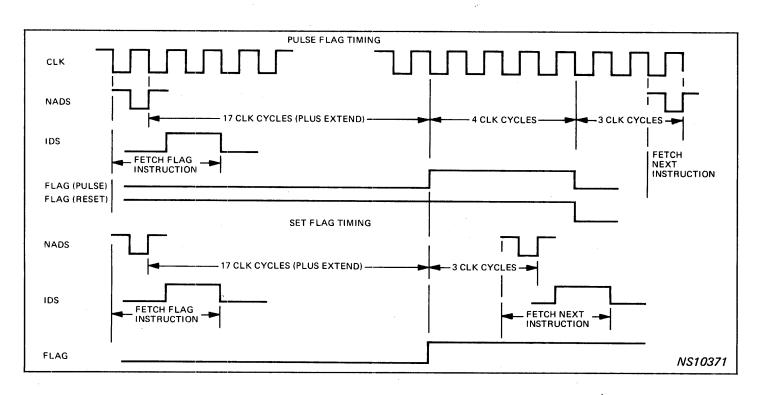

| 2 - 7                        | Pulse and Set Flag Timing Diagram                                                           |        |

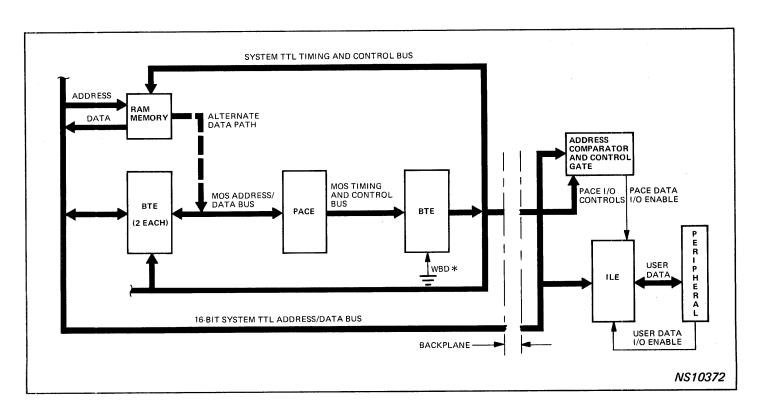

| 2-8                          | Fully Multiplexed Bus Structure                                                             |        |

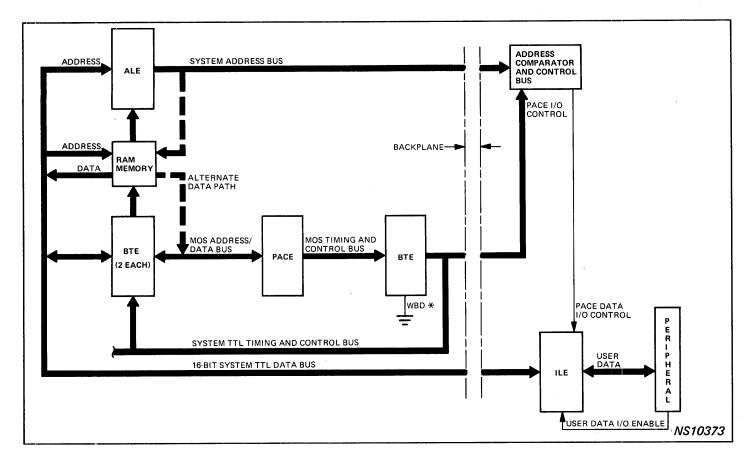

| 2-9                          | Separate Address/Multiplexed Data Bus Structure                                             |        |

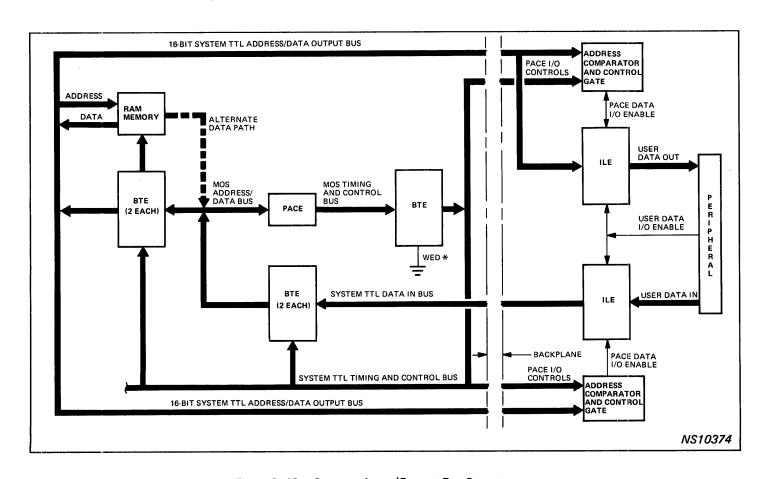

| 2 - 10                       | Separate Input/Output Bus Structure                                                         |        |

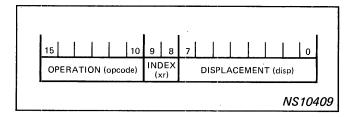

| 2-11                         | Memory-reference Instruction Format                                                         |        |

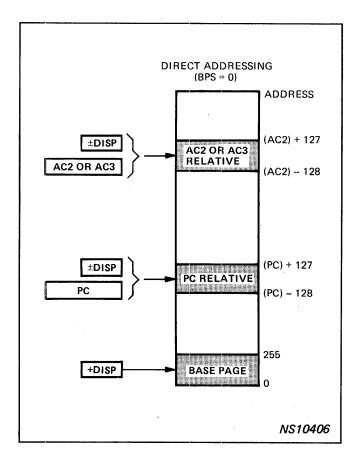

| 2 - 12                       | Direct Memory Addressing (BPS = 0)                                                          |        |

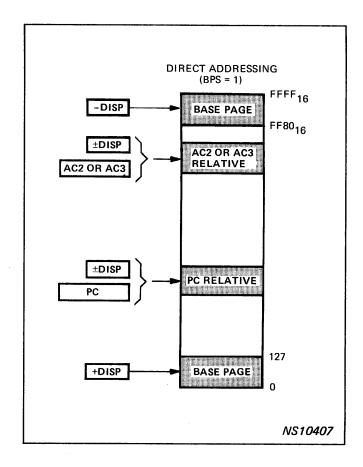

| 2 - 13                       | Direct Memory Addressing (BPS = 1)                                                          |        |

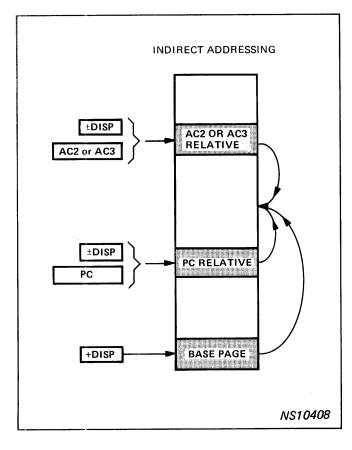

| 2 - 14                       | Indirect Memory Addressing                                                                  |        |

| 2 - 15                       | STE Functional Block Diagram                                                                |        |

| 2 - 16                       | Relative Timing of STE Output Waveforms                                                     |        |

| 2 - 17                       | STE to PACE Interconnection                                                                 |        |

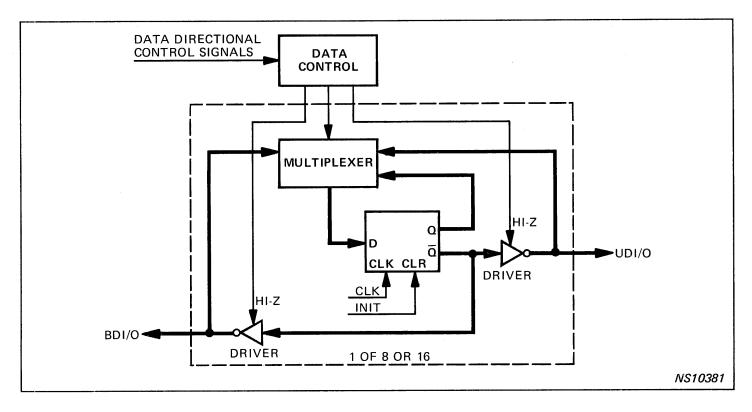

| 2 - 18                       | BTE Functional Block Diagram                                                                |        |

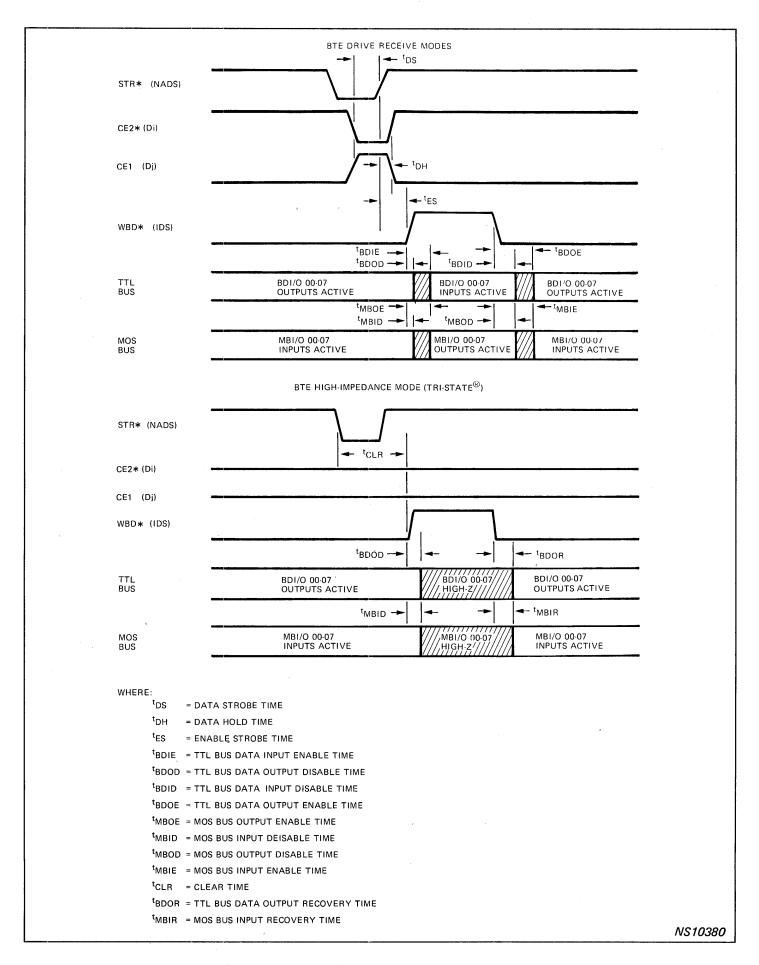

| 2 - 19                       | BTE System Implementation                                                                   |        |

| 2 - 20                       | BTE Operational Modes Timing Diagram                                                        |        |

| 2-21                         | ILE Functional Block Diagram                                                                |        |

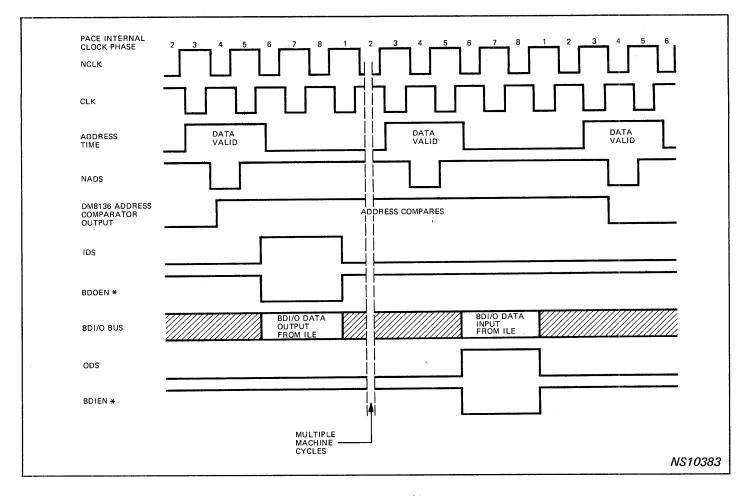

| 2 - 22                       | ILE System Implementation                                                                   |        |

| 2 - 23                       | ILE Idealized BDI/O Timing Diagram                                                          |        |

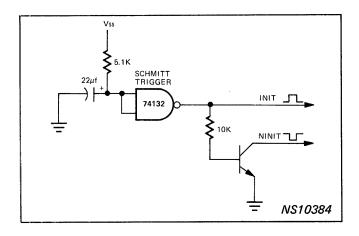

| 2 - 24                       | Circuit For Generating INIT                                                                 |        |

| 2 - 25                       | ALE/16 Functional Block Diagram                                                             |        |

| 2 - 26                       | ALE System Implementation                                                                   |        |

| 2-27                         | Idealized ALE Address and Memory Data Transfer Timing Diagram                               |        |

| 2 - 28                       | RAM Functional Block Diagram                                                                |        |

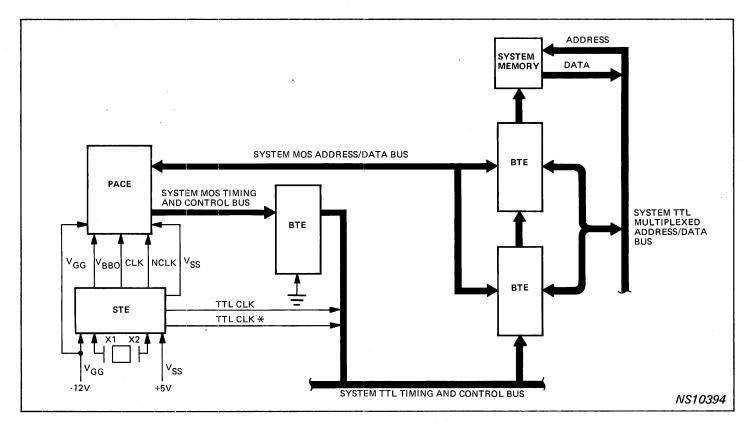

| 2 - 20<br>2 - 29             | Typical System Implementation of RAM and ROM                                                |        |

| 2-29                         | Address Bit Configurations Versus Hexadecimal Address                                       |        |

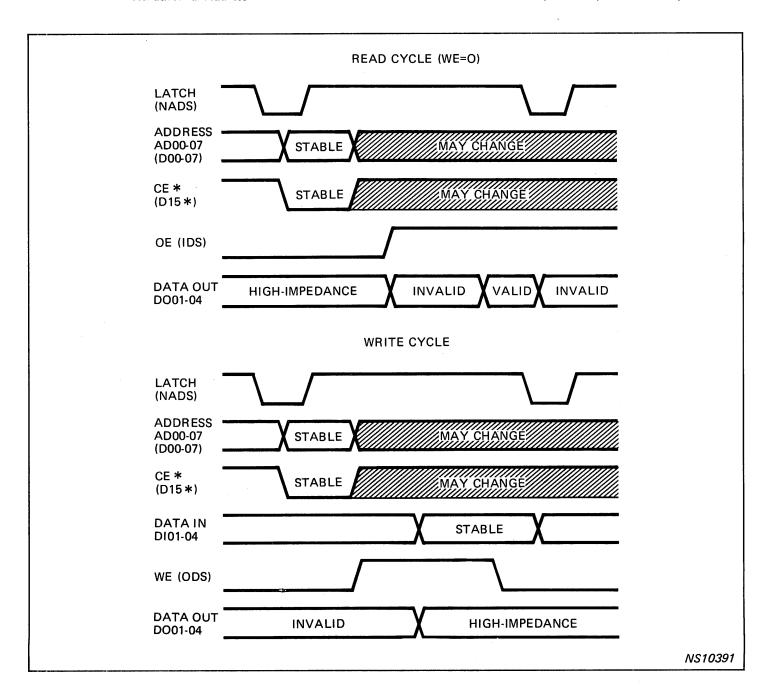

| 2-30<br>2-31                 | RAM Timing Diagram                                                                          |        |

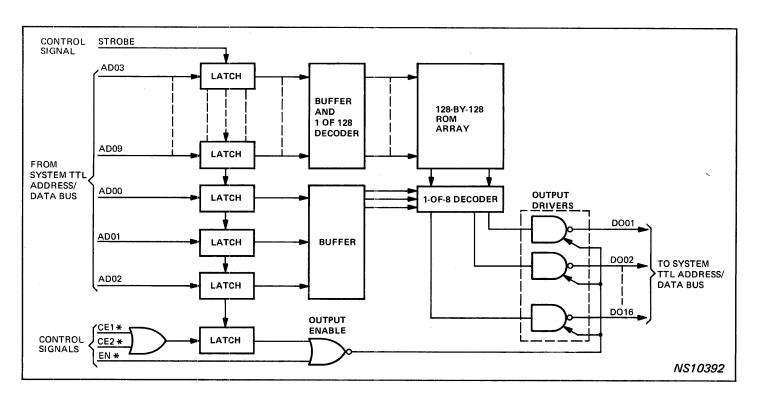

| 2-32                         | ROM Functional Block Diagram                                                                |        |

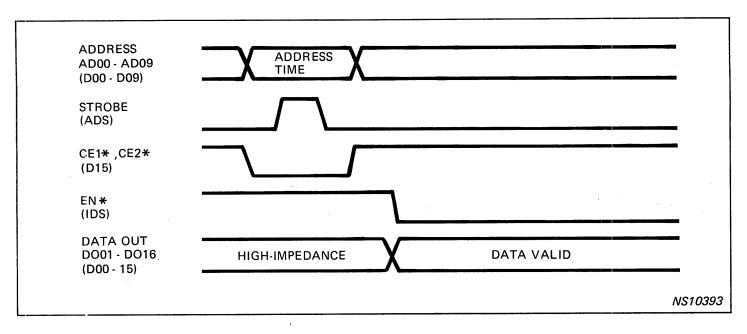

| 2-32                         | ROM Timing Diagram                                                                          |        |

| 2 - 33<br>2 - 34             | Minimum Chip Configuration                                                                  |        |

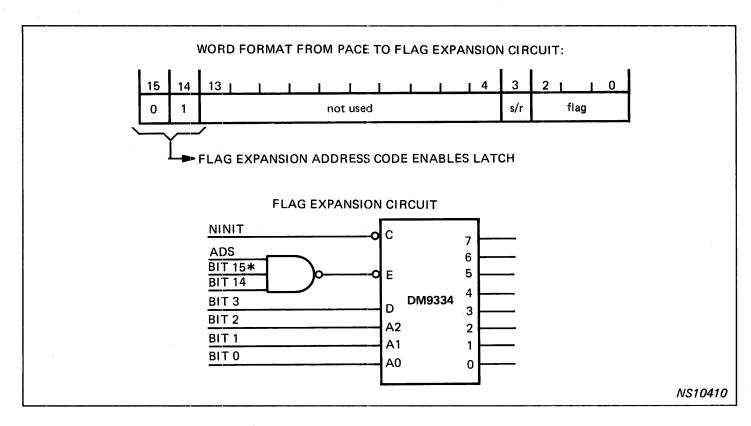

| 2 - 3 <del>4</del><br>2 - 35 | One Possible Circuit and Word Format for Obtaining Additional Flags                         |        |

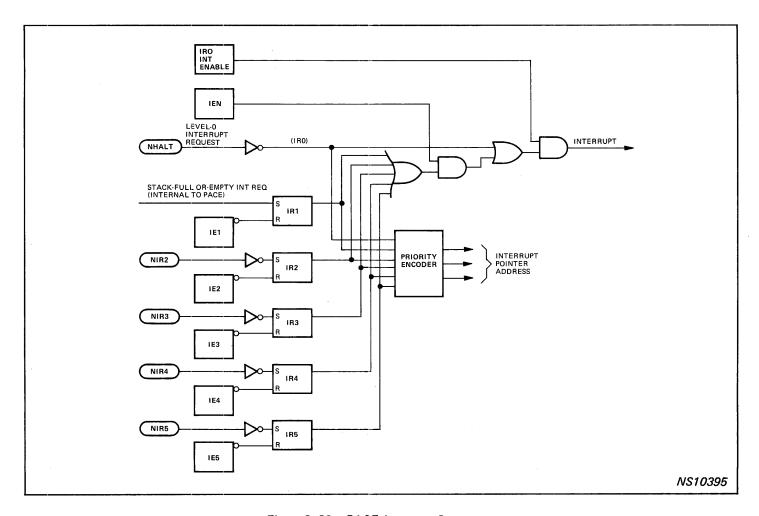

| 2 - 36                       | PACE Interrupt System                                                                       |        |

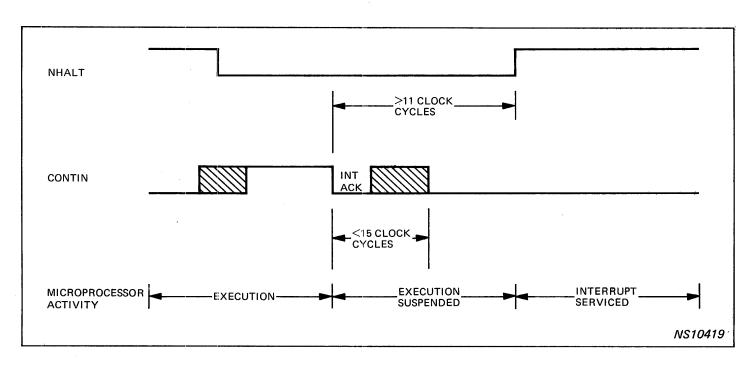

| 2 - 30<br>2 - 37             | Relative Timing for Level-0 Interrupt Generation                                            |        |

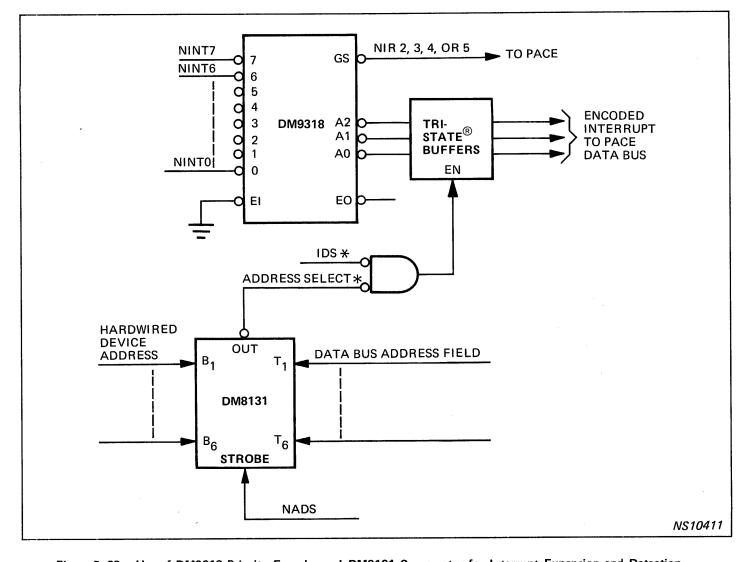

| 2 - 38                       | Use of DM9318 Priority Encoder and DM8131 Comparator for Interrupt Expansion and Detection. |        |

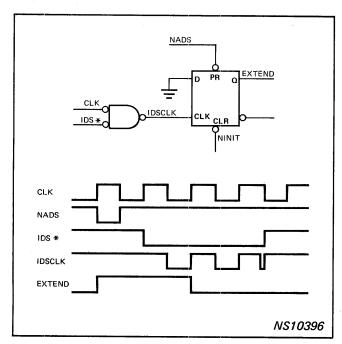

| 2-39                         | Circuit and Timing Diagram for One Clock Cycle Extend                                       |        |

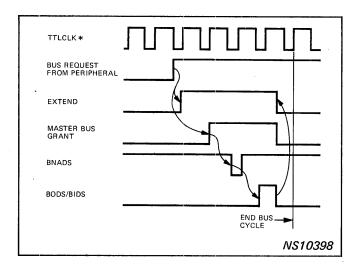

| 2-40                         | System Implementation of DMA Bus Controller                                                 |        |

| 2-41                         | Timing Required from DMA Bus Controller                                                     |        |

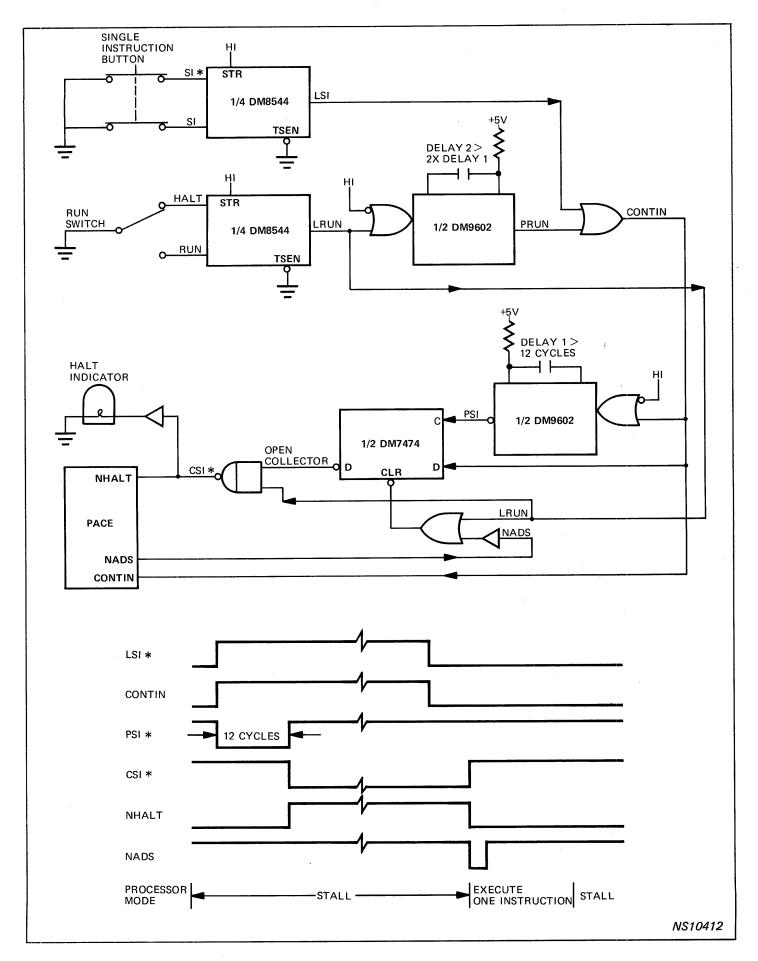

| 2-42                         | Timing Diagram for Externally Applied NHALT and CONTIN Signals                              |        |

| 2 - 43                       | Control Panel Logic and Timing (Plus Time Line)                                             |        |

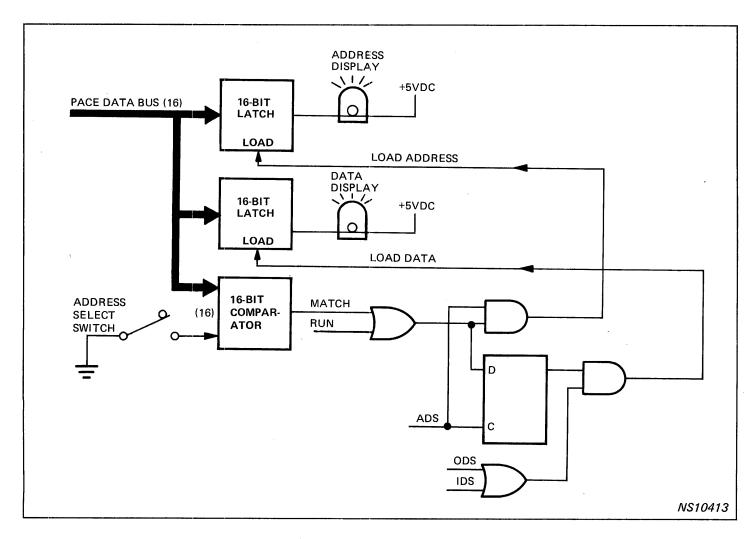

| 2 - 44                       | Panel Data Display Logic                                                                    |        |

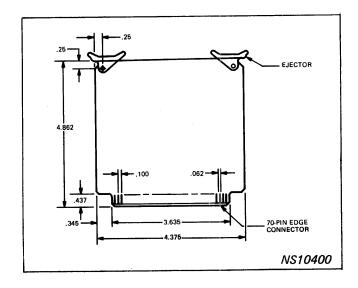

| 3-1                          | PACE Application Cards Dimensional Details                                                  | 3-1    |

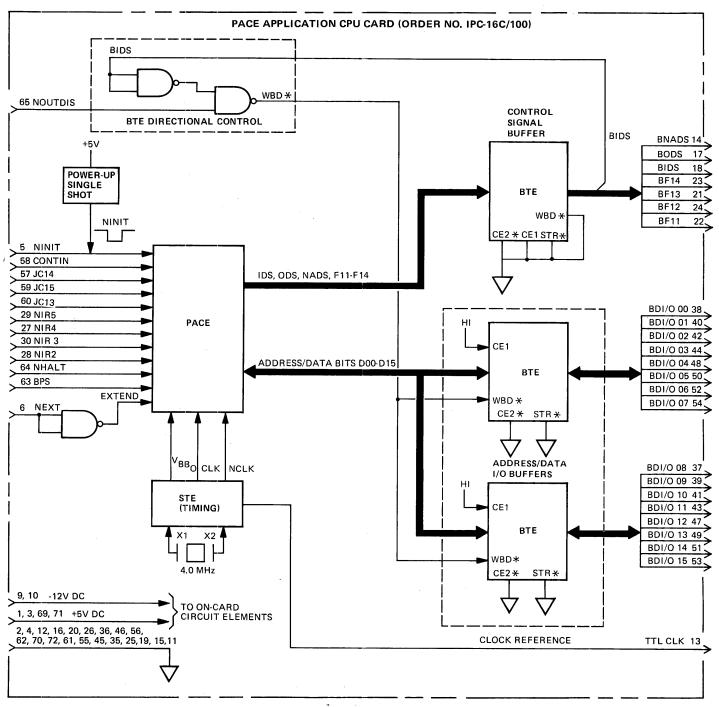

| 3-1                          | PACE Application CPU Card Functional Block Diagram                                          |        |

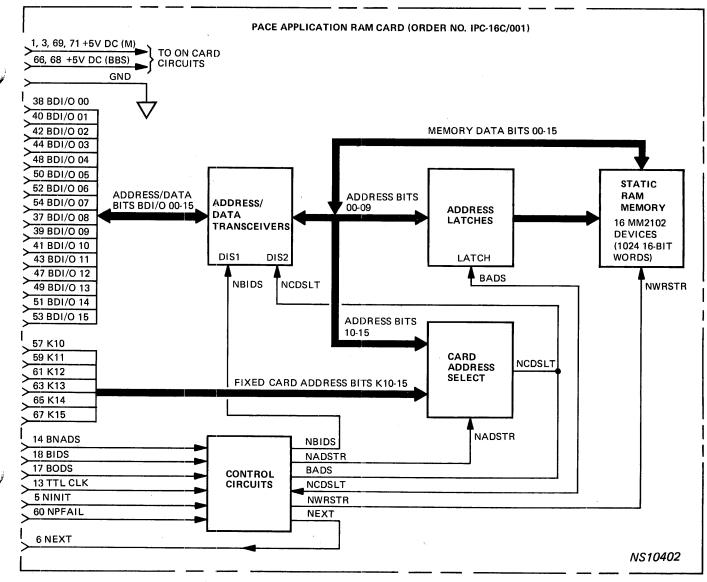

| 3-3                          | PACE Application RAM Card Functional Block Diagram                                          |        |

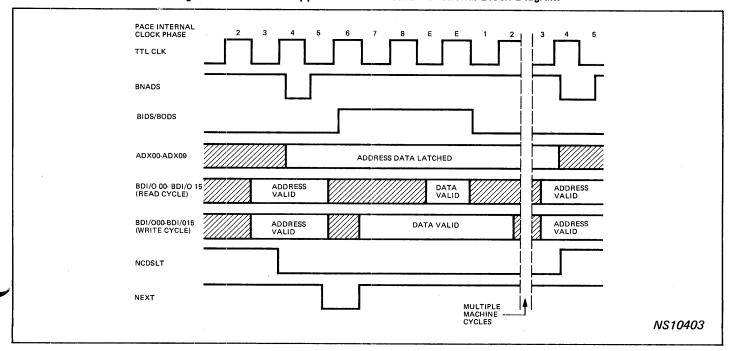

| 3-3                          | PACE Application RAM Card Timing Diagram                                                    |        |

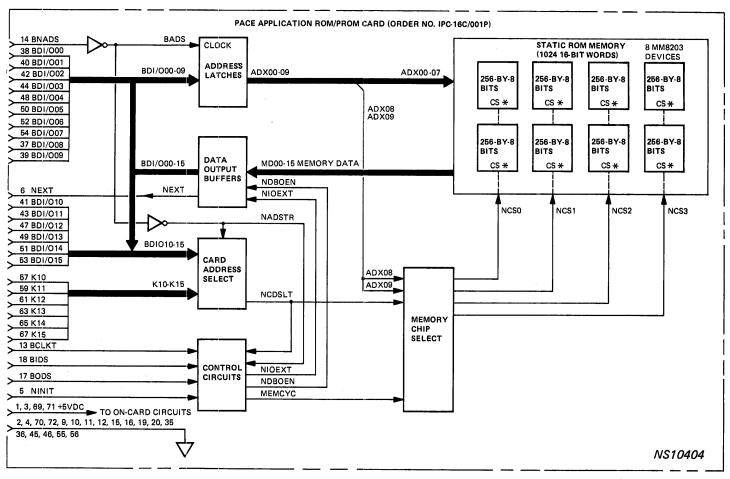

| 3-4                          | PACE Application ROM/PROM Card Functional Block Diagram                                     |        |

| 3-6                          | PACE Application ROM/PROM Card Functional Block Diagram                                     |        |

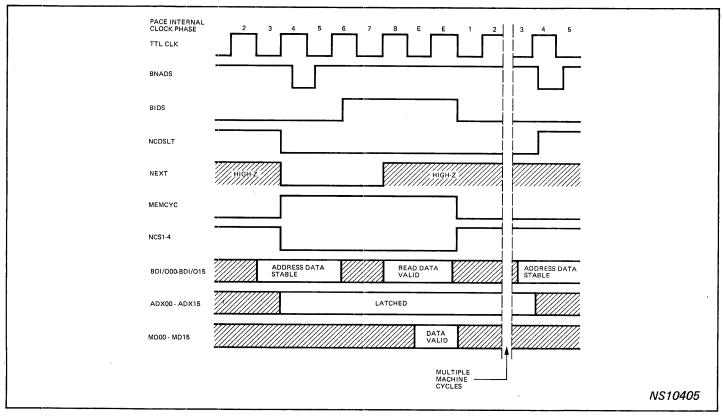

| 4-1                          | PACE Application ROM/PROM Card Timing Diagram                                               |        |

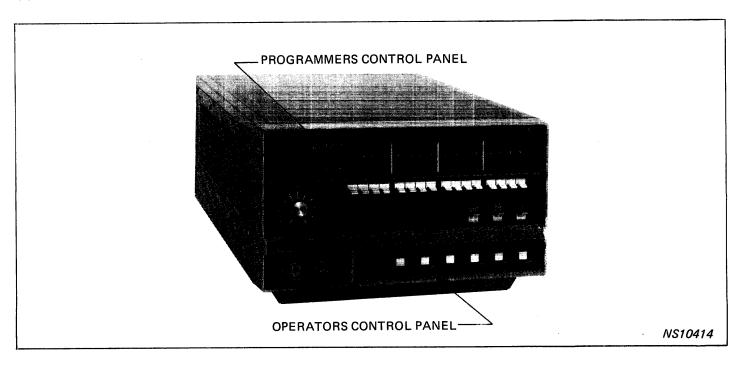

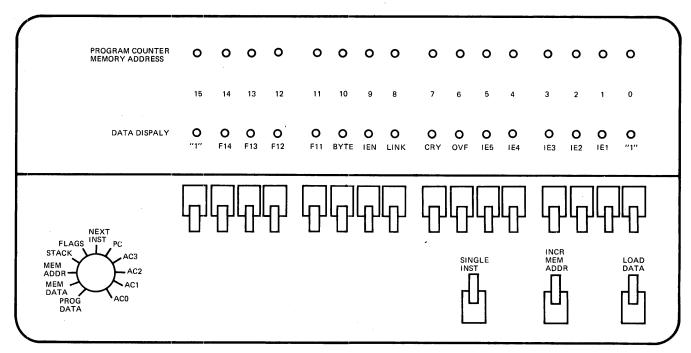

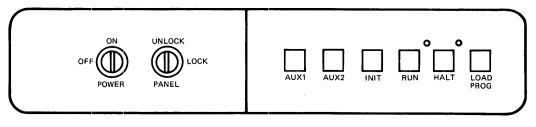

| 4 - 1                        | IPC-16P Programmers Control Panel                                                           |        |

| 4-2                          | Operators Control Panel                                                                     |        |

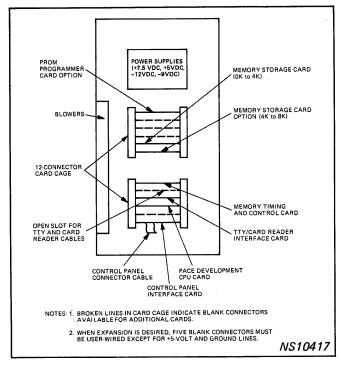

| 4-3                          | Top Internal View of IPC-16P                                                                | 1-2    |

| 4-4                          | IPC-16P Generalized Bus Structure                                                           |        |

| 4-0                          | IFC-TOF Generalized bus surdicine                                                           | 4-3    |

# CHAPTER 1 INTRODUCTION TO PACE

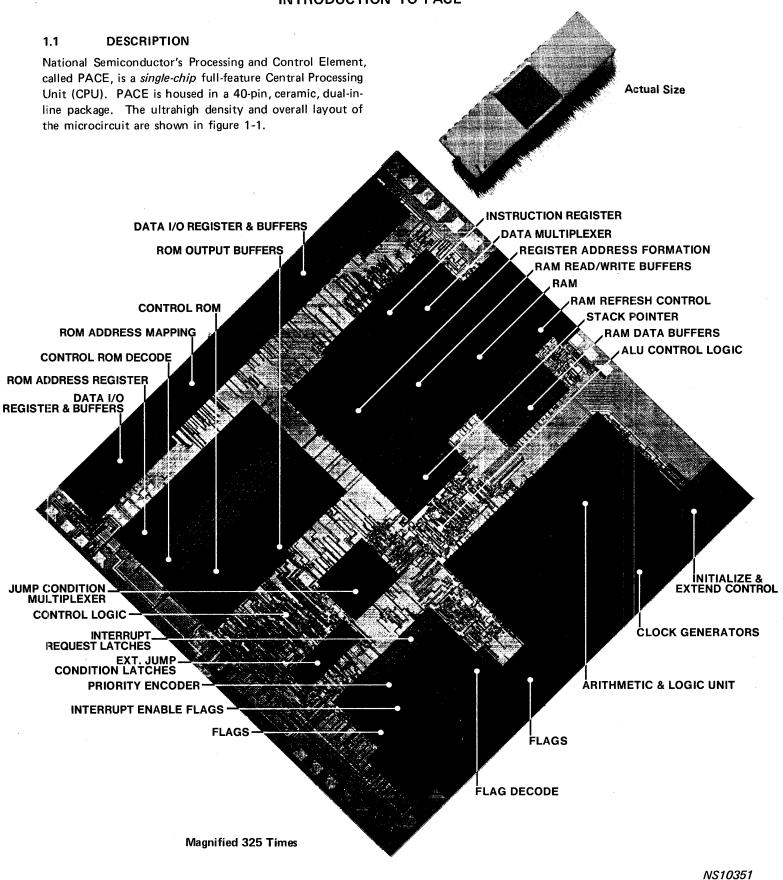

Figure 1-1. PACE Chip and Circuit Layout

Figure 1-2. PACE Functional Block Diagram

PACE also is called a microprocessor, the prefix *micro* relating to the microscopic size of the physical circuit and components on the chip. An extraordinary amount of data-processing capability is provided in one component by the *single-chip* microconstruction.

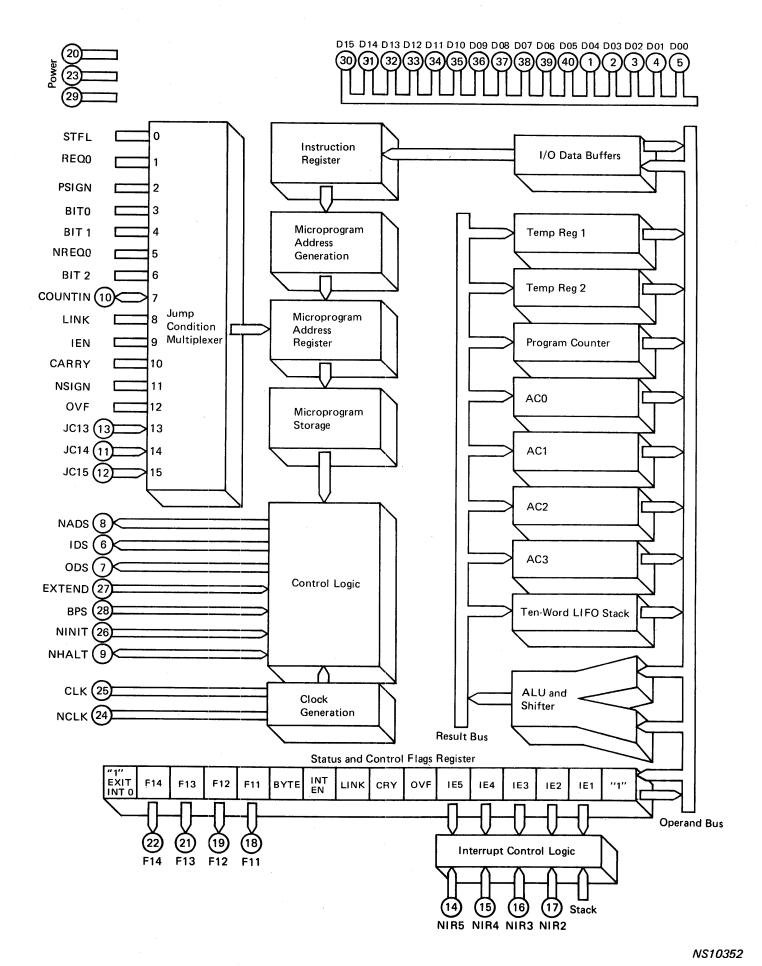

Figure 1-2 reveals the CPU architecture and pinouts of the single-chip PACE — consisting of registers, control logic, an arithmetic unit, and the data buses. Some of the outstanding operational features of the PACE microprocessor are listed below.

#### Features

- 16-bit instruction word offers addressing flexibility and speed.

- 8- or 16-bit data word interfaces increase application flexibility.

- 45 instruction types provide efficient programming.

- Common memory and peripheral addressing means powerful I/O instructions.

- Shares instructions with National Semiconductor's IMP-16, allowing software compatibility.

- Four general-purpose accumulators reduce memory data transfers.

- 10-word Stack is utilized for interrupt processing/data storage.

- Six vectored priority-interrupt levels speed interrupt service and simplify hardware.

- Programmer-accessible status register may be preserved, tested, or modified.

- Typical 10-microsecond instruction execution guarantees high throughput.

- 1K-by-16 Read-Only Memory allows single-memory package systems.

- Single-phase true and complement clock minimizes external components.

- +5-volt and -12-volt standard supplies ensure minimum cost.

The PACE MOS/LSI chip is produced using silicon-gate, P-channel enhancement-mode standard-process technology. This means that the following very significant advantages are realized.

- Lower cost per function

- Lower component count

- Simplified design

- Higher reliability

- High noise immunity

- Low threshold voltage

Among some of the benefits of a single-chip device with the above-listed advantages are the following.

LOWER COMPONENT COUNT --- Generally, this means lower procurement, incoming testing, inventory, handling, rework, and assembly cost — and higher reliability.

- SIMPLIFIED DESIGN --- LSI devices enable engineering design groups to take advantage of prepackaged circuits that are self-contained and perform a unified function. Also, a design group not strongly oriented towards digital design may make use of the latest techniques and devices without requiring expertise related to the design methods of interfacing the circuits internal to LSI devices. In summary, use of LSI devices requires considerably less engineering time to develop a product.

- HIGHER RELIABILITY --- The long history of field maintenance of all types of electronic systems clearly demonstrates the high reliability of LSI devices. System maintenance has shown that the reliability of low-power circuits is inversely proportional to the number of component lead connections in the system. This factor, coupled with the abundant functional capability of LSI, greatly increases the probability that an LSI-based system will function properly over extended periods of time.

- IMPROVED PERFORMANCE --- PACE offers higher throughput because of a powerful instruction set, a proven architecture, and 16-bit address generation and data handling.

- LOWER COST --- The reduction of cost is an aggregate savings resulting from the other advantages already enumerated. In the microprocessor field, the inherent functional superiority of high-density devices is seldom questioned. The superior performance of the single-chip PACE, coupled with reduced engineering and assembly cost, higher reliability, lower operating and maintenance costs, and smaller size of the microprocessor, definitely results in a much better performance-to-price ratio than heretofore possible. It makes the PACE microprocessor the most competitive processor on the market.

# 1.2 OUTSTANDING FEATURES OF PACE

The outstanding features of PACE are described in detail later. Nevertheless, to provide an overall view of the many favorable facets of PACE, these features are listed and briefly described below.

- 8- OR 16-BIT DATA HANDLING --- PACE is cost effective in applications dominated by 8-bit data interfaces. Efficient coding and address generation found only in 16-bit microprocessors are extended to 8-bit applications.

- INCREASED THROUGHPUT --- PACE minimizes data and program storage requirements, while increasing data-processing throughput.

- COMPATIBILITY WITH NATIONAL SEMICON-DUCTOR'S IMP-16 MICROPROCESSORS --- May use Source Statement Translator to convert IMP-16 software to PACE software without incurring significant development costs. The IMP-16 and PACE may be used together in a digital hybrid system, allowing common software and peripheral interfaces.

- PACE BLUE CHIPS --- Support CPU. Include System Timing Element and 8-bit Bidirectional Transceiver Element.

- PACE GREEN CHIPS --- Peripheral interface chips, including Interface Latch Elements and Address Latch Elements. Provide storage and buffering between the PACE system TTL bus and user peripherals or memory. Available in 8-bit and 16-bit units, accommodating PACE's unique ability to operate on both 8-bit and 16-bit data.

- PACE MEMORY CHIPS --- Designed for optional use with PACE. Include 256-by-4-bit Random Access Memory (having on-chip address latches), 1024-by-16-bit Read-Only Memory (having on-chip address latches), and 512-by-8-bit erasable Programmable Read-Only Memory.

- PACE APPLICATION CARDS --- Intended for prototyping, preproduction and small production runs.

Prefabricated and pretested CPU, Random Access Memory, Read-Only Memory/Programmable Read-Only Memory, input/output, and special functions are provided.

- PACE DEVELOPMENT SYSTEM --- May be used to evaluate the microprocessor and to develop and debug a myriad of application hardware and software. Includes a Control Panel and interfaces for Teletypewriter, Card Reader, and Tape Reader. Available options include Line Printer, dual-drive Floppy Disc, and Programmable Read-Only Memory Programmer.

- FIELD SUPPORT --- Microprocessor specialists (engineers) that understand hardware, software, and PACE applications. Available domestically and internationally and offer on-site technical assistance.

- BACK-UP APPLICATION SUPPORT --- National Semiconductor's home-base technical-support specialists support the microprocessor specialist in the field and, as required, provide direct support to users.

- FACTORY SERVICE --- Will repair any of our microprocessor products. This service is for both the OEM customer and the end user...

- TRAINING --- Offers elementary to advanced training, with locations in the West, Midwest, and East.

Courses are in-depth and include hands-on instruction.

- USER GROUP --- Membership open to users and others interested in microprocessors. Provides a vehicle of communications between members and with National Semiconductor. Makes programs available from its User Group Software Library.

- SOFTWARE SUPPORT -- Includes Source Statement Editor, Assemblers, Loaders, Debug Routine, Utilities, and Diagnostics. (Also, as previously mentioned, a Source Statement Translator converts IMP-16 software to PACE software.)

- DOCUMENTATION --- Offers a Product Description that helps you to determine the suitability of a microprocessor to a particular application. A Technical

Description gives a more in-depth understanding such that benchmarks may be established, programs written, and systems designed. A PACE Users Manual describes the use of PACE equipment and software.

# 1.3 PACE APPLICATIONS

Applications for PACE could very well be in the thousands. The suitability of PACE will, in many cases, be a matter of evaluation by potential users for their particular needs. A few applications are listed.

- Test system and instrument control

- Process controllers

- Machine tool control

- Terminal control

- Small business machines

- Traffic controllers

- Word-processing systems

- Peripheral device controllers

- Educational controllers

- Sophisticated games

- Distributed and multiprocessor systems

- Automotive controller

# 1.4 DYNAMICS OF PACE DEVELOPMENT

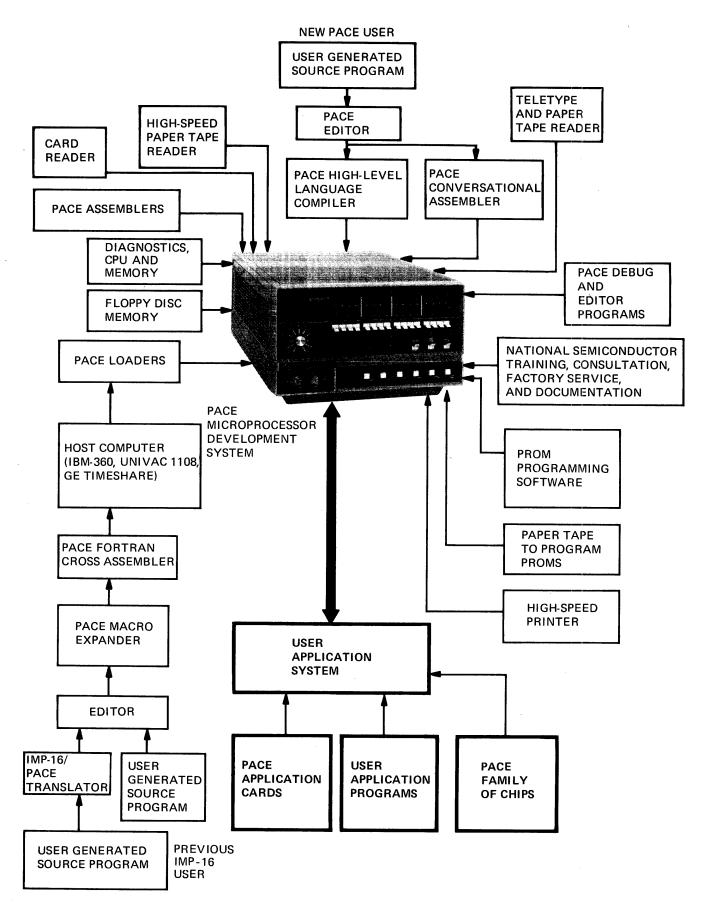

Developing a user's application system around the PACE chip can best be performed by utilizing the software and hardware support items provided by the PACE Microprocessor Development System. The *dynamics* of developing a user's application system are shown in figure 1-3. Obviously, there's more to microprocessing than a microprocessor.

Without this array of software and hardware support, a user would have to expend considerable manpower, time, and money to develop his application of a microprocessor-based system. But with National Semiconductor's total support development system, the user immediately can start work on his own application or system. In addition, the experience of National Semiconductor's staff engaged in design, applications, documentation, field support, back-up technical support, factory service, and training is readily available to help not only experienced designers but also newcomers throughout their development programs. We do our best to make it easy to use PACE and our other microprocessor products.

# 1.5 PACE FAMILY OF CHIPS

The PACE family of chips comprise three types: Blue, Green, and Memory devices. The chips facilitate system development and provide the main functional building blocks for interfacing, timing, and data/program storage. The chips are briefly described in the immediately following paragraphs, and their utilization in system applications is further described in chapter 2.

NS10353

Figure 1-3. Dynamics of Utilization of PACE

# 1.5.1 PACE BLUE CHIPS

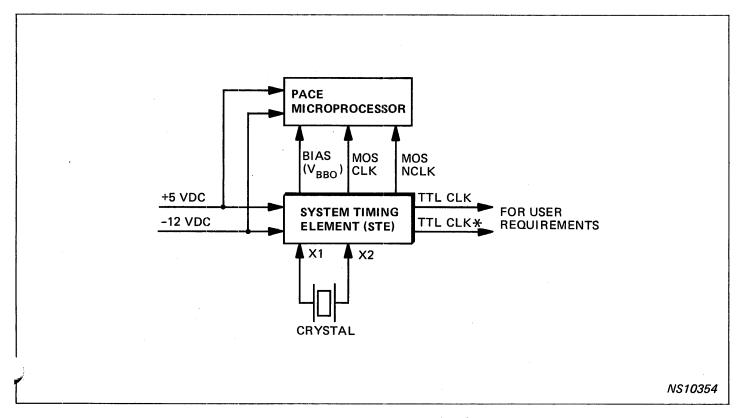

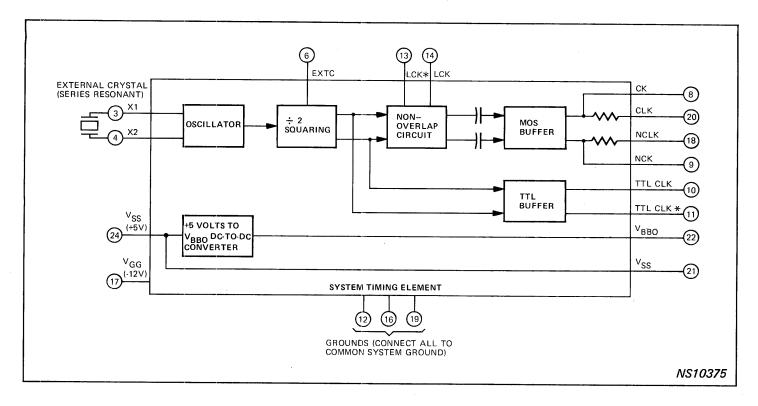

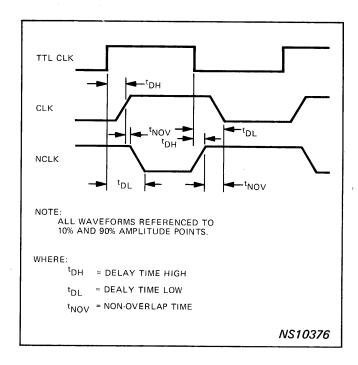

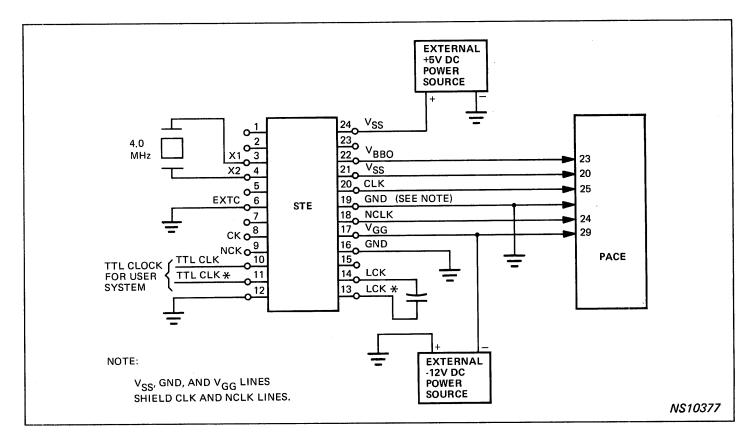

The PACE Blue Chips interface directly with the PACE microprocessor and include a System Timing Element (STE) and an 8-bit Bidirectional Transceiver Element (BTE). The TE requires application of +5 and -12 volts and the addition of only an external crystal (as shown in figure 1-4) to produce the MOS clock signals and substrate bias voltage required by the PACE microprocessor. In addition, the STE provides external TTL clock signals to accommodate user requirements.

#### NOTE

All signal names beginning with N or followed by an asterisk (\*) denote complemented signals that are asserted or activated by a logic '0'. Otherwise, signals are asserted by a logic '1'.

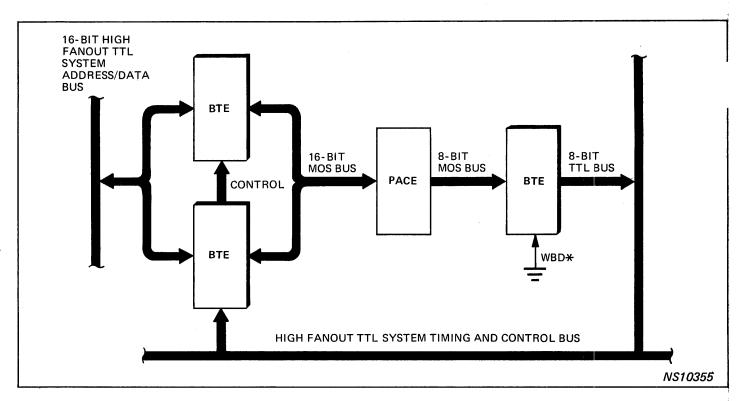

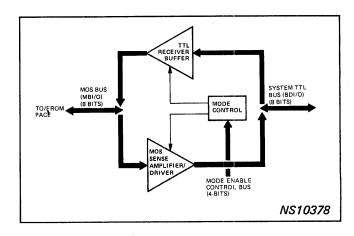

The BTE is an 8-bit transceiver that provides controlled translation of signals between the PACE microprocessor MOS buses and the system TTL buses. The BTE has a high-fanout TTL capability (up to 30 TTL loads). One BTE connected in a driver-only mode (WBD\* control signal grounded) to the PACE microprocessor permits buffering for the System TTL Timing and Control Bus, thereby providing seven TTL control signals and flags for distribution as shown in figure 1-5. Two BTEs can be used to take advantage of the PACE capability to operate with a single time-multiplexed System TTL Address/Data Bus. Thus, system component count and interconnections are mini-

mized. Time multiplexing of the System TTL Address/Data Bus for the Address, Data In, and Data Out Cycles is provided by PACE control signals that are routed over the System TTL Timing and Control Bus.

# 1.5.2 PACE GREEN CHIPS

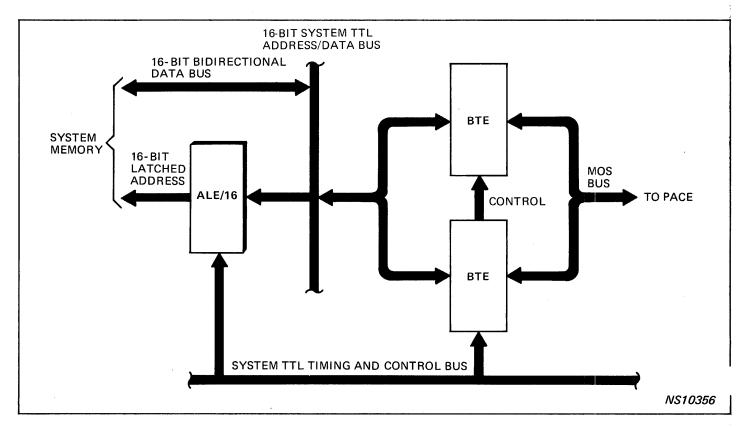

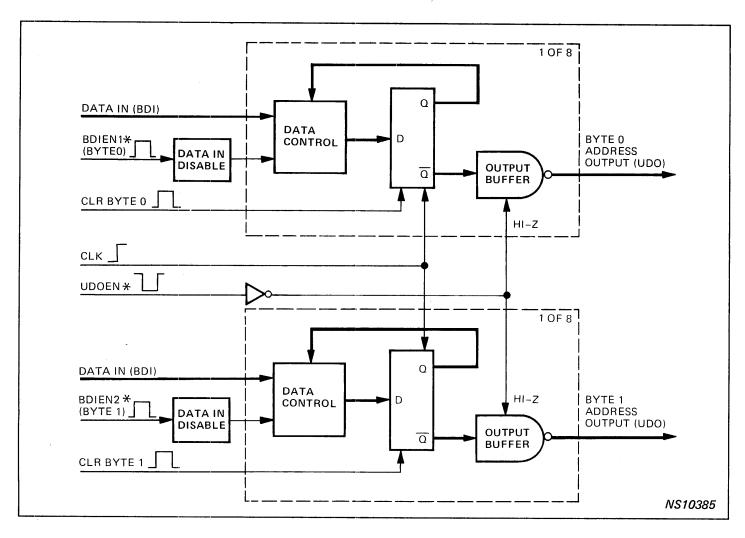

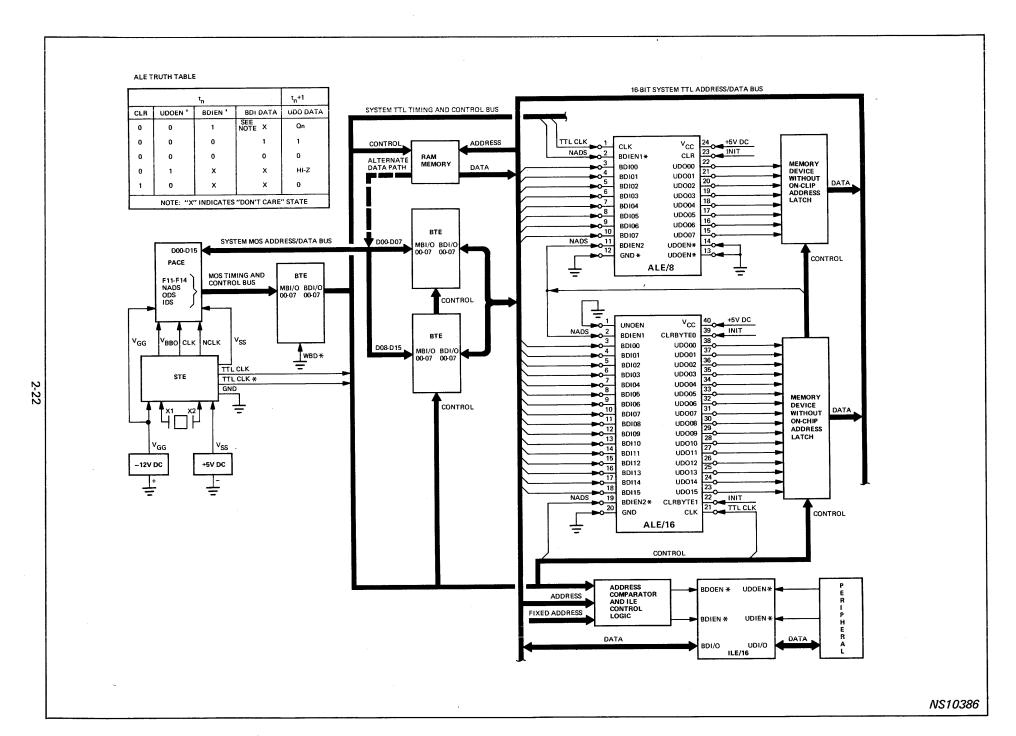

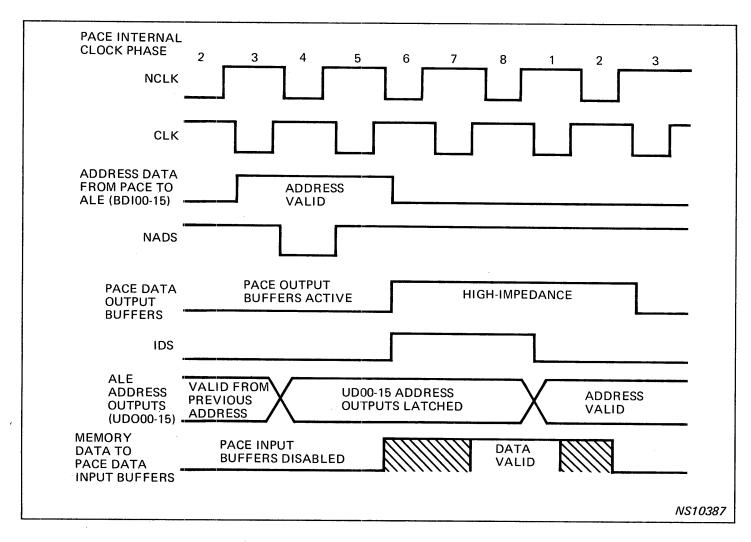

The PACE Green Chips interface with the system TTL buses and memory or user peripherals. The PACE Green Chips include an Address Latch Element (ALE) and an Interface Latch Element (ILE). The Address and Interface Latch Elements are available in either 8-bit or 16-bit packages. The ALE provides memory address latching for single, time-multiplexed address/data bus systems using memory devices that do not have on-chip address latches. Figure 1-6 shows a portion of a typical system using a 16-bit ALE.

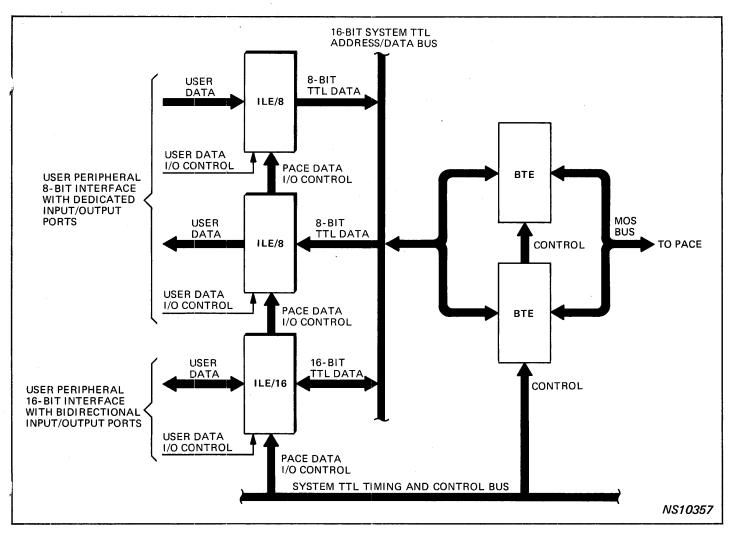

The ILE provides latched interfacing between the System TTL Address/Data Bus and the user peripherals. The user data and PACE data I/O controls can be connected to the ILE control inputs, as shown in figure 1-7, to provide either unidirectional or bidirectional peripheral data latching for either 8-bit or 16-bit peripheral data words. Timing and control signals from the PACE microprocessor are routed over the System TTL Timing and Control Bus to effect data input/output transfers between the ILE and the System TTL Address/Data Bus at the appropriate time. When data transfers are not effected, the ILE can be driven to a high-impedance state at the ILE-to-System TTL Address/Data Bus Interface and/or the ILE-to-peripheral Interface.

Figure 1-4. System Timing Element (STE) Provides

All Timing Requirements

Figure 1-5. Bidirectional Transceiver Element (BTE)

Provides High-fanout TTL Buses

Figure 1-6. Address Latch Element (ALE) Provides

Memory Address Latching

Figure 1-7. Interface Latch Element (ILE) Provides

Interface Storage for Peripherals

Figure 1-8. Implementation of RAM and ROM With On-chip Address Latches

# 1.5.3 PACE MEMORY CHIPS

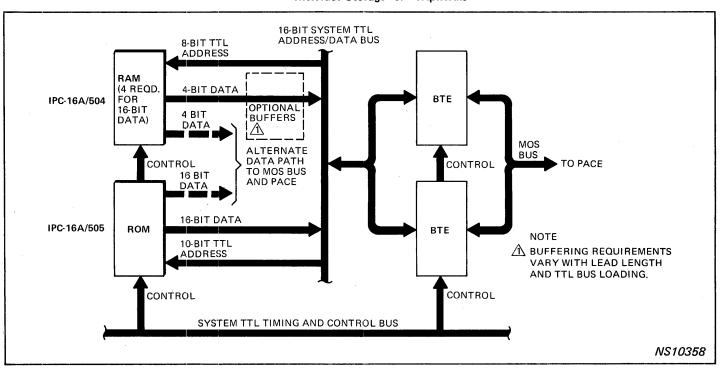

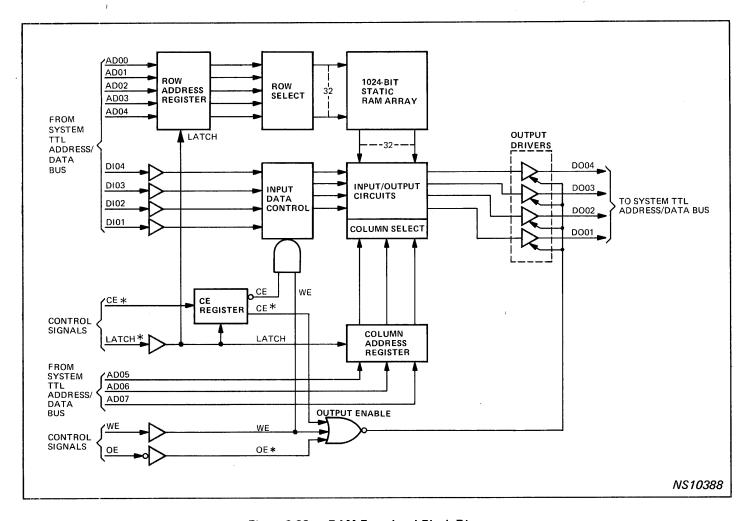

The PACE Memory Chips include a read/write Random Access Memory (RAM), two Read-Only Memories (ROMs), and a Programmable Read-Only Memory (PROM). The RAM provides 256-by-4 bits of static read/write memory and also contains on-chip address latches and latched chip enables. Consequently, no need exists for ALEs between the System TTL Address/Data Bus and the RAM as shown in figure 1-8. Since the RAM contains static memory and utilizes only a +5-volt dc power source for operation, the hardware design is simplified for system applications using battery back-up or auto-fail/restart features that are often encountered in such applications as process control. Memory accessing is under control of the PACE microprocessor which provides control signals to the memory chips at the appropriate time by way of the System TTL Timing and Control Bus. The control signals permit the RAM to accept address information or to effect data I/O transfers.

The two available ROMs differ in memory density, presence of on-chip address latches, access time, and cost. The IPC-16A/505 ROM, shown in figure 1-8, is a high-performance, high-density (1024-by-16 bits) ROM that has on-chip address latches and requires only a +5-volt power supply. The 1024-by-16 bits of memory provide a control storage capacity that is sufficient for many applications. In addition, the on-chip address latches permit complete system implementation without supplemental address latches, and the bipolar technology eliminates the need for buffering in many cases. Thus, the IPC-16A/505 ROM is the ultimate solution to the low-cost storage requirements for high-volume systems.

Memory accessing of the ROM-stored data is accomplished by presenting address information on the System TTL Address/Data Bus at a time when the appropriate control signals are supplied by the PACE microprocessor over the System TTL Timing and Control Bus. In a similar manner, addressed data is read from memory onto the System TTL Address/Data Bus by the proper application of signals over the System TTL Timing and Control Bus. Since the CPU inputs are TTL compatible, the memory output can use the MOS bus as an alternate data path.

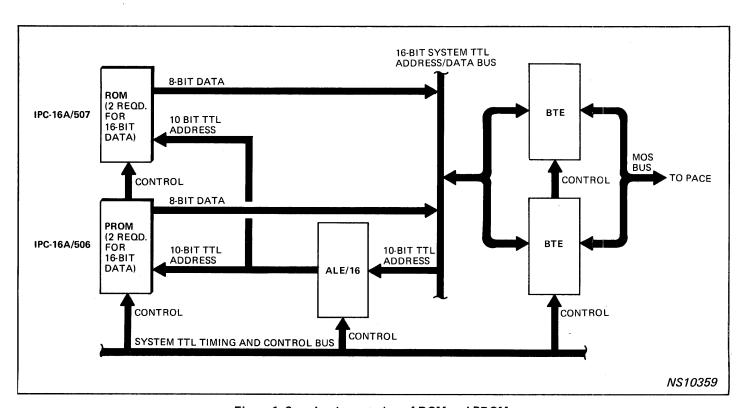

The IPC-16A/506 PROM contains 512-by-8 bits of ultraviolet erasable memory to provide a low-cost control storage solution for program development and for low-volume applications. Since the IPC-16A/506 PROM does not contain on-chip address latches, the ALE provides a convenient means to implement the IPC-16A/506 PROM, as shown in figure 1-9. Memory accessing is accomplished in a manner similar to the IPC-16A/505 ROM previously described, except the ALE is latched by the PACE microprocessor control signals when address information is present on the System TTL Address/Data Bus. Furthermore, the access time of the IPC-16A/506 requires the use of Cycle Extend as detailed in chapter 2.

Figure 1-9 also includes implementation of the IPC-16A/507 ROM. The ROM provides 512-by-8 bits of memory storage. The ROM is pin-for-pin compatible with the IPC-16A/506 PROM. Memory accessing is accomplished in the manner previously described for the IPC-16A/506 PROM.

Figure 1-9. Implementation of ROM and PROM Without On-chip Address Latches

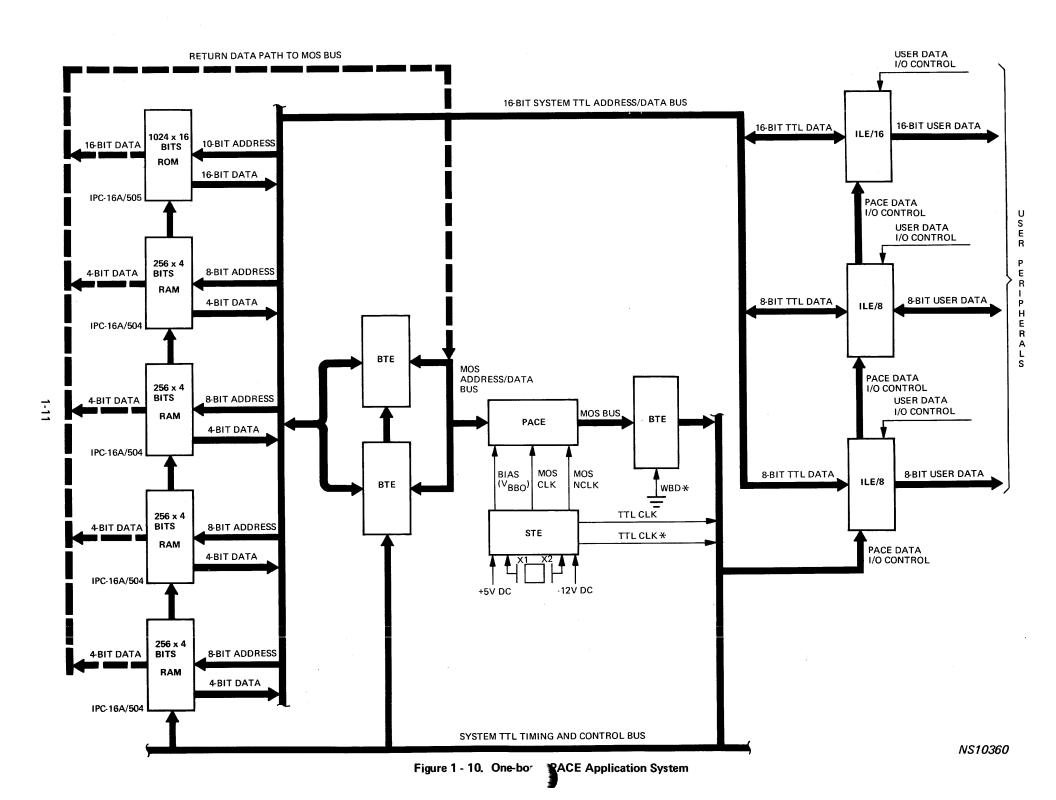

Figure 1-10 illustrates a typical one-board PACE application system containing 1024 16-bit words of ROM and 256 16-bit words of read/write RAM memory. The system shown in figure 1-10 is just one of many configurations that can be realized by using the PACE microprocessor and the associated family of chips. Using the PACE microprocessor and family of chips, the designer can put together an inexpensive but powerful microcomputer system in a minimum of time to meet individual requirements.

# 1.6 PACE APPLICATION CARDS

The following application cards support system design around the PACE microprocessor.

- PACE Application CPU Card

- PACE Application RAM Card

- PACE Application ROM/PROM Card

Future application cards will include:

- PACE Application Input/Output Interfacing Card

- PACE Application Multiply/Divide Card

- PACE Application DMA Controller Card

The application cards measure 4.375 inches by 4.862 inches and comprise circuits that implement the intended function of the card. The design-tested, proven application cards can be inserted into a universal card cage to immediately form the basis of a custom microcomputer system, thereby expediting hardware development. The application cards also can be used for end applications. The small card size particularly suits the use of application cards in physically confined situations such as portable equipment.

# 1.7 PACE MICROPROCESSOR DEVELOPMENT SYSTEM

The PACE Microprocessor Development System (IPC-16P), together with the available software and peripherals, provides a convenient means to expedite the hardware/software development stages of a system incorporating a PACE microprocessor. To facilitate software development, the the IPC-16P contains a Control Panel with various data indicators and switches that permit the user to examine and modify software during the development stage. In addition. the IPC-16P contains read/write memory (expandable to 32K words) as well as all required Card Reader/High-Speed Paper Tape Reader and Teletype®(TTY) interfacing and firmware (programs stored in ROM). The firmware consists of the routines necessary to permit peripherals (such as the TTY) to be used for loading, examining, or modifying software during development. Additional peripheral options include the Disc Operating System, Line Printer, and PROM Programmer.

The IPC-16P is similar to the National Semiconductor IMP-16P. The most important difference between the two systems is the PACE Development CPU Card contained in the IPC-16P. Consequently, the PACE Development CPU Card is separately available and, together with a field conversion kit, permits reconfiguration of an IMP-16P System for use as a PACE Microprocessor Development System.

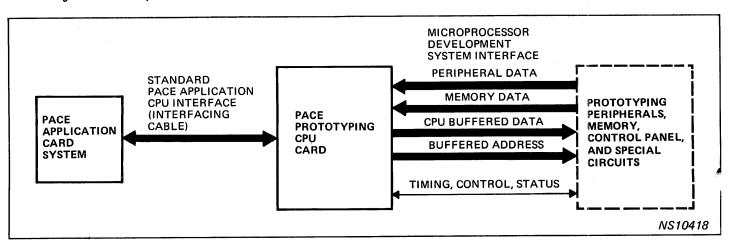

The PACE Development CPU Card is supplied with a cable that permits connection of the IPC-16P into an application system in place of a PACE Application CPU Card. Thus, the prototyping features inherent to the IPC-16P Control Panel, peripherals, and software can be used to develop a user application system containing PACE application cards.

#### NOTE

A hardware summary table of the PACE product line is located in appendix A, table A-1.

# 1.8 SOFTWARE SUPPORT

The importance of National Semiconductor-supplied support software cannot be overemphasized. The microprocessor design process is most efficient when the designer fully appreciates and uses the support software.

# 1.9 SPECIFYING HARDWARE BEHAVIOR WITH SOFTWARE

The microprocessor approach differs from older, discretelogic controllers in only one important way, and all differences in approach stem from the following.

- In the random-logic approach, a set of logic is wired to handle each function, and all logic operations proceed in parallel.

- In the microprocessor approach, one central set of logic is provided inside the microprocessor. The central set of logic is rewired in real time, under control of the program, to handle each of the logic functions in serial.

Thus, the discrete-logic designer buys a set of functions and then wires the functions to perform a specific job. On the other hand, the microprocessor user buys a microprocessor and then must tell the microprocessor how to wire itself, from microsecond to microsecond, to perform different jobs.

The purpose of the system software is to aid the user in describing, designing, and debugging a microsecond-to-microsecond description of the microprocessor wiring. Such a description, when rendered in terms the microprocessor can understand, is called a program.

# 1.10 TYPES OF SOFTWARE

One of the most important steps in the programming process is the translation of the program description from commands that the programmer writes and understands into binary strings that the microprocessor uses to perform operations. Two types of commonly used translator programs are assemblers and compilers.

Utility programs facilitate the preparation of input code (using the Editor Program) and the debugging of the resultant object code (using the Debug Program) and, also, are used to enter the programs (using the Loader Program) into the Microprocessor Development System.

The following paragraphs provide more detailed descriptions of assembler and compiler programs and three types of utility programs (Editor, Debug, and Loaders).

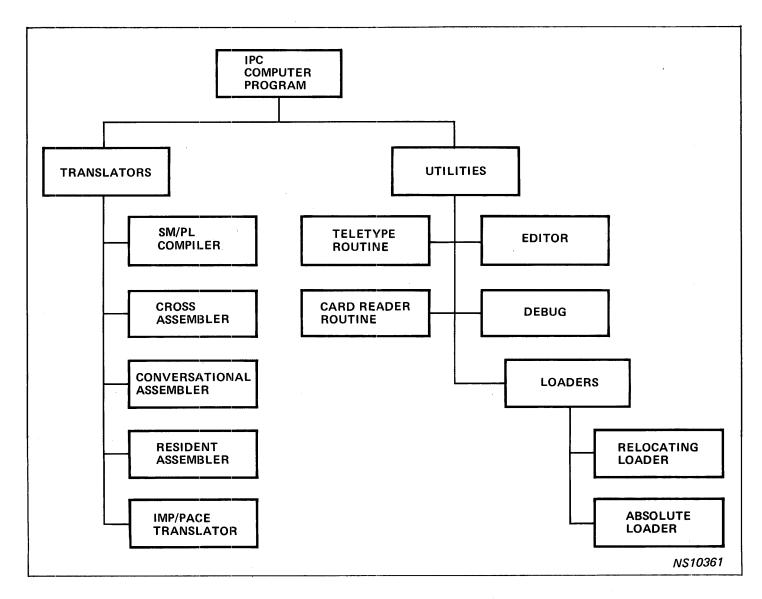

Figure 1-11 gives a birds-eye view of the PACE computer-program breakdown.

#### NOTE

A software summary table of the PACE software line is located in appendix A, table A-2.

# 1.10.1 PACE EDITOR

The PACE Editor enables the generation of new source statement text and the modification of existing source text in preparation for program assembly. The normal editing procedure is to input assembly-language source statements and comments, edit the text, and output the edited text, along with a punched paper tape suitable for input to the assembler.

# 1.10.2 PACE ASSEMBLERS

The user has the alternative of selecting among four PACE assemblers: the PACE Resident Assembler, the PACE IMP-16 Cross Assembler, the PACE Conversational Assembler, and the PACE FORTRAN Cross Assembler. All Assemblers are completely compatible in programs assembled and vary only in operating environments.

The PACE Resident Assembler runs on an IPC-16P. The PACE IMP-16 Cross Assembler runs on an IMP-16P or IMP-16L with a minimum of 4K words of memory and a TTY. The PACE Resident Assembler and PACE IMP-16 Cross Assembler accept *free-format* source statements from either the keyboard, paper tape, or a card reader and produce a Load Module (LM) on paper tape and an object listing on the TTY printer. The Resident and Cross Assemblers require three passes over the source program; however, if either the object listing or the LM is suppressed, only two passes are required.

Figure 1-11. PACE Computer Programs

The PACE Conversational Assembler, which runs on an IPC-16P and combines the features of an editor and a resident assembler, simplifies the editing and assembly procedures by eliminating the need for multiple loadings of an editor, a resident assembler, and the user-generated program. The PACE Conversational Assembler requires 8K words of memory for operation.

The PACE FORTRAN Cross Assembler Program generates an object program from a source program on a host computer for subsequent execution by a PACE microprocessor. The assembler may be used on different host processors since the assembler is written in FORTRAN IV (USA Standard Language Subset). The assembler requires 100K bytes of memory and the following minimum hardware complement: processor input unit, scratch unit, list output unit, and binary output unit.

The PACE FORTRAN Cross Assembler accepts *free-format* source statements and, in two passes, produces an LM (object program) and a program listing.

# 1.10,3 PACE SM/PL COMPILER

The PACE SM/PL Compiler is a high-level computer program written in IPC assembly language. Comparable to high-level-language programming of the large-scale computers and minicomputers, the SM/PL Compiler considerably simplifies microcomputer programming. This results in fewer pro-

gramming manhours and shortens leadtime - and, hence, reduces programming cost.

The SM/PL Compiler runs on an IPC-16P Microprocessor Development System, with a requirement of at least 12K memory words. The object code thus produced is highly efficient – in many cases comparable to the object code produced by programs written in the IPC assembly language. The object code is in standard Relocatable-Load-Module (RLM) format. All IPC peripherals are supported by the SM/PL Compiler.

A sequence of declarations and statements comprise the language of the SM/PL Compiler. Declarations control allocation of storage, define simple macros, and define procedures. Statements compute results and store them in a location defined by a variable name; statements also provide conditional tests and branching, iteration control, and procedure innovation.

Compiler procedures are in the form of subroutines that are defined by declarations and called by statements. Each subroutine may represent a program module, so a particular program may perform a number of tasks, each task being implemented by a subroutine. These subroutines are available to be used as procedures as part of other similar programs.

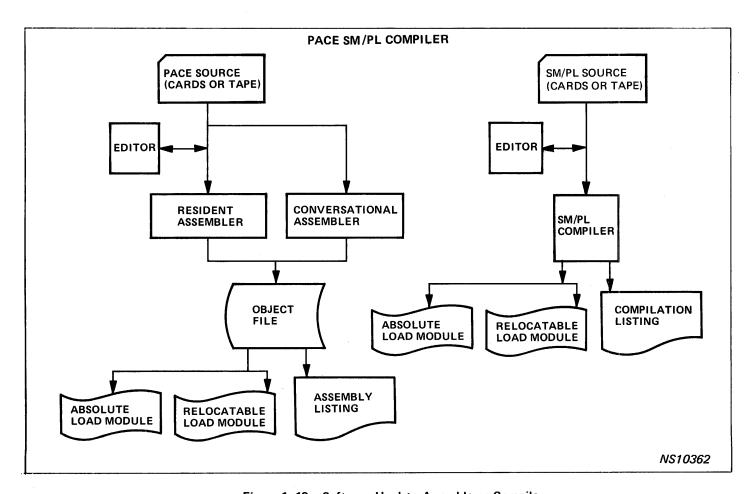

Figure 1-12 illustrates the software used to assemble or compile on PACE.

Figure 1-12. Software Used to Assemble or Compile on PACE

# 1.10.4 IMP-16/PACE TRANSLATOR

The IMP-16/PACE Translator is an ANSI FORTRAN program that transliterates source programs written in IMP-16 assembly language into PACE source programs that can be assembled and executed.

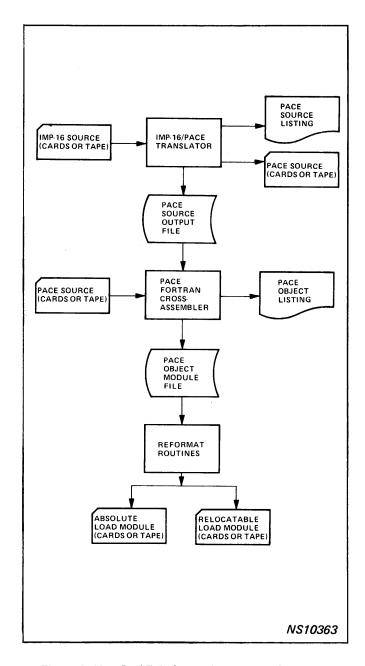

The IMP-16/PACE Translator is installed and available to users of the General Electric National Timesharing Service under the program name TRAN\$\$ to translate an existing IMP-16 assembly-language file into PACE assembly language so the new file may be assembled for execution on the PACE microprocessor. Figure 1-13 illustrates how PACE software is implemented on a host computer.

# 1.10.5 PACE LOADERS

The PACE loaders are programs that read and load one or more LMs, produced by a PACE assembler, into the main memory for execution.

The output by the PACE FORTRAN Cross Assembler is reformatted into an LM before loading into the PACE memory for execution. ANSI FORTRAN programs are available to reformat the output from the PACE FORTRAN Cross Assembler into an LM suitable to the loader and loading method employed.

The outputs from the PACE Resident Assembler and the PACE IMP-16 Cross Assembler do not require reformatting. The LMs are output directly from the PACE Resident Assembler and PACE IMP-16 Cross Assembler onto paper tape.

Two methods are available for loading data into the main memory for execution: absolute and relocatable. Each loading method involves tradeoffs among the following considerations: the complexity of the loading process, the amount of work that must be performed by the user, and the flexibility available to the user at load time (versus assembly time).

Several PACE programs are available for loading correctly formatted LMs into the PACE memory for execution: PACE Relocating Loader (PACE General Loader), PACE Absolute Card Reader Loader, and PACE Absolute Paper Tape Loader. The loading methods and the loaders available for each method are described in the following paragraphs.

# 1.10.5.1 PACE Absolute Loaders

A PACE Absolute Loader, resident in the ROM of the IPC-16P, loads one or more programs into preallocated, fixed areas of memory. The exact memory areas to be occupied by each user-generated program must be determined by the user before assembly. Also, any linking of one program to another or to common, shared data must be accomplished at assembly time by assignment of common labels to fixed, absolute addresses in memory. The advantages of using a PACE Absolute Loader are that a small, simple loader may be used and no commands are required at load time.

Figure 1-13. PACE Software Implemented on a Host Computer

# 1.10.5.2 PACE Relocating Loader

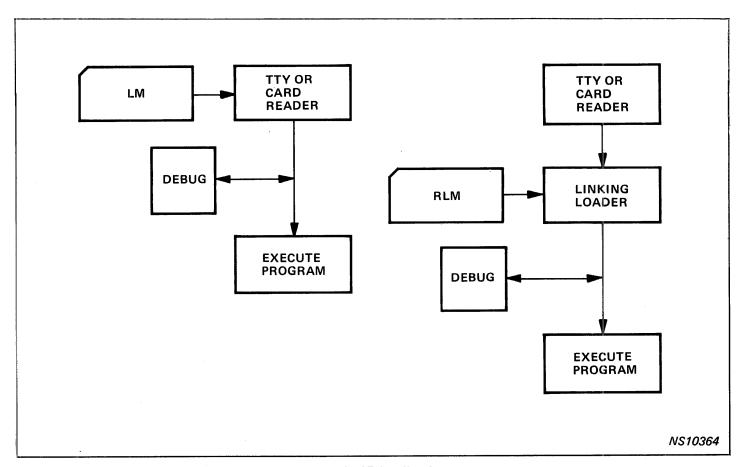

The PACE Relocating Loader (PACE General Loader) is a command-driven PACE program that reads one or more relocatable LMs from either the Card Reader or the Paper Tape Reader, relocates object code, and transfers control to the specified entry point. The PACE Relocating Loader provides the most flexible loading process. The PACE Relocating Loader process allows relocation of programs at LM load time rather than at assembly time. The PACE Relocating Loader follows either an inherent method for allocating programs to available memory or user-generated instructions that designate where each program should be loaded. Figure 1-14 illustrates the PACE loading sequence.

# 1.10.6 PACE INPUT/OUTPUT ROUTINES

The PACE Input/Output Routines are described in the following paragraphs.

# 1.10.6.1 PACE Teletype Routines

The PACE Teletype Routines reside in ROM on the TTY/Card Reader Interface Card of the IPC-16P System. The routines are used to send and receive information to and from the TTY or to receive data from the Paper Tape Reader. When both a High-speed Paper Tape Reader and a TTY Paper Tape Reader are used, the program verifies the tape reader that first supplies data and, subsequently, accepts input data from that tape reader.

# 1.10.6.2 PACE Card Reader Routine

The PACE Card Reader Routine resides in ROM on the TTY/Card Reader Interface Card of the IPC-16P System. The PACE Card Reader Routine accepts an absolute LM in Hollerith-coded card format and loads the data into main memory. There are no restrictions on loadable addresses; any read/write memory location can be used.

# 1.10.7 PACE DEBUG PROGRAM

The PACE Debug Program supervises the operation of a user program during checkout. This program provides the following facilities for testing computer programs:

- Printing selected areas of memory in hexadecimal or ASCII format

- Modifying the contents of selected areas in memory

- Modifying computer registers and stack

- Inserting instruction breakpoint halts

- Taking memory snapshots during execution of a user program

- Initiating execution at any point in a program

- Searching memory

Figure 1-14 PACE Loading Sequence

# **CHAPTER 2**

# PACE AND FAMILY OF CHIPS

#### 2.1 INTRODUCTION

The following paragraphs provide additional descriptive information and in-depth application data concerning the PACE microprocessor and family of chips. The PACE instruction set and addressing methods are detailed in appendix B. The instruction set description includes the instruction word bit configuration, assembler format, and instruction execution time formula for each instruction type. Applications data are provided for input/output control techniques, use of jump conditions and flags, interrupts, Cycle Extends, and DMA operation.

# NOTE

Since this document was prepared during the final design phase of the PACE product line, some discrepancies may exist in the timing and electrical specifications presented with the following application information. For preliminary design purposes, refer to the latest data sheets to verify the timing and electrical parameters.

# 2.2 PACE MICROPROCESSOR

The PACE microprocessor provides the control and timing signals required for system or subsystem operation in addition to providing data manipulation and storage capabilities. The following paragraphs provide more information regarding the PACE microprocessor.

# 2.2.1 GENERAL DESCRIPTION

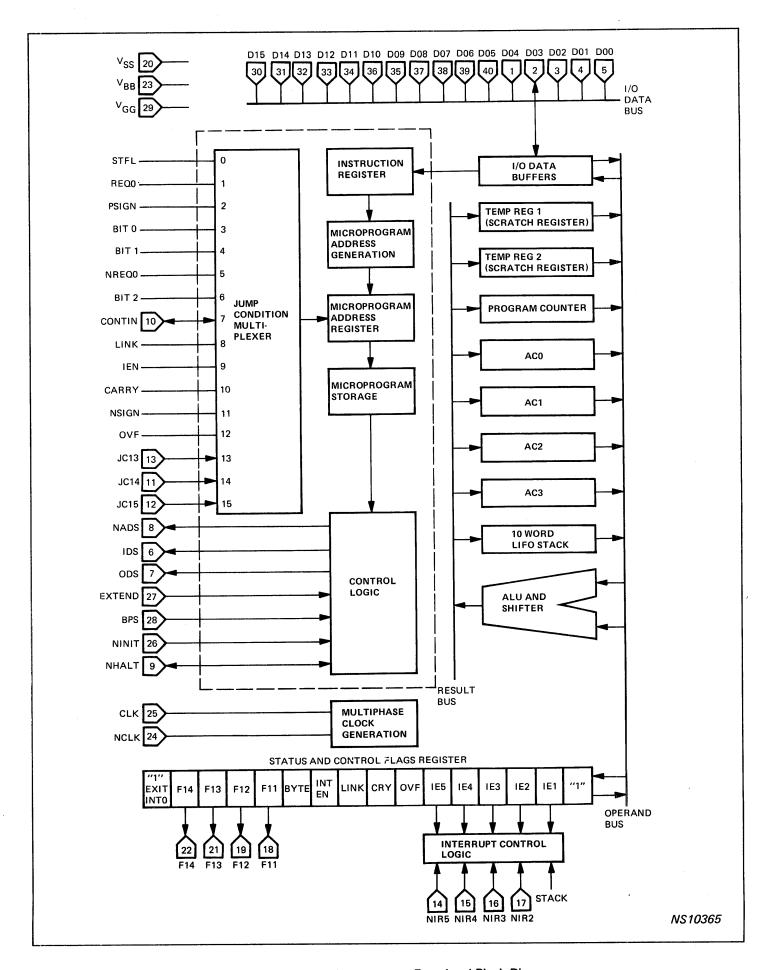

Data transfers between PACE (see figure 2-1) and memory or peripheral devices are effected over the 16-bit (D00-D15) parallel Input/Output Data Bus. The Input/Output Data Bus interfaces with the Instruction Register and the Operand Bus by way of the I/O Data Buffers. The Operand Bus also interfaces with seven registers (Temporary Registers 1 and 2, Program Counter, and AC0 through AC3) and a 10word Stack. The seven registers and Stack are provided for data storage. Four of the registers (AC0 through AC3) are available to the programmer as general-purpose accumulators. The Program Counter contains the address of the next instruction. The contents of any selected register or the Stack are routed over the Operand Bus to the Arithmetic and Logic Unit (ALU) and Shifter. Resultant ALU and Shifter output is returned to the selected register or Stack, as appropriate, by way of the Result Bus. The ALU and Shifter, besides performing arithmetic operations, also sets status flags in accordance with the data length (8-bit or 16bit) selected by the state of the BYTE Status Flag.

All status information is stored in the 16-bit Status and Control Flags Register. The Status and Control Flags Register contents can be loaded onto the Operand Bus for temporary storage on the Stack or in any accumulator for examination or modification of status information.

Instructions under execution by PACE are stored in the Instruction Register and are interpreted and executed by a microprogram stored in an on-chip ROM. Instruction execution time is determined by the instruction under execution, memory access time, and the external clock frequency.

# 2.2.2 EXTERNAL CLOCK REQUIREMENTS

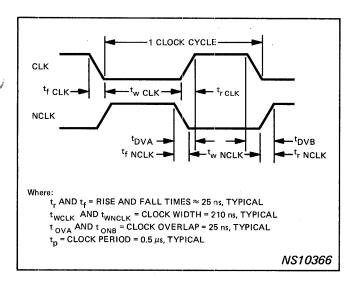

The external clock signals (see figure 2-2) applied to PACE must consist of single-phase true and complement signals such as those produced by a System Timing Element (STE). PACE uses the external clock signals to generate internal multiphase clock signals that provide control timing for microprocessor operations.

# 2.2.3 DESCRIPTION OF HARDWIRED SIGNALS AND TIMING

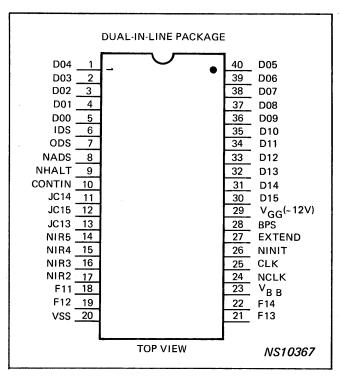

PACE operations are controlled by software which rewires the PACE Control Logic in real time (at a speed determined by the external clock) to handle each microprocessor function in serial order. The clock and other signals that require hardwired connection to the PACE microprocessor are described in table 2-1. Pin assignments for the PACE CPU are shown in figure 2-3.

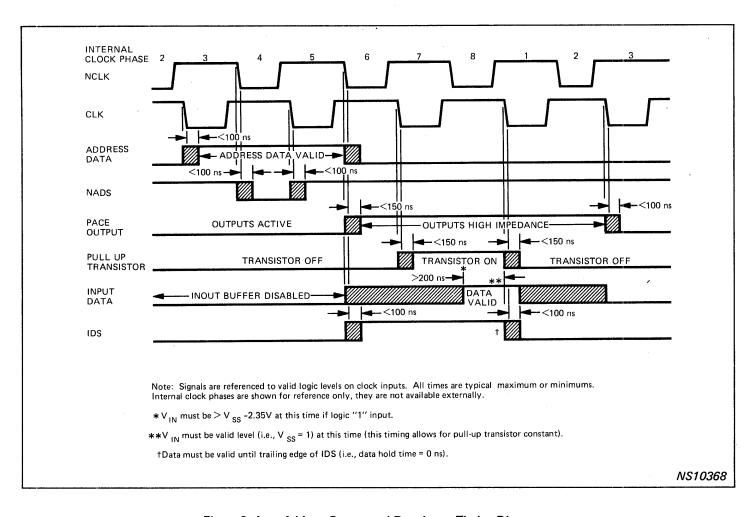

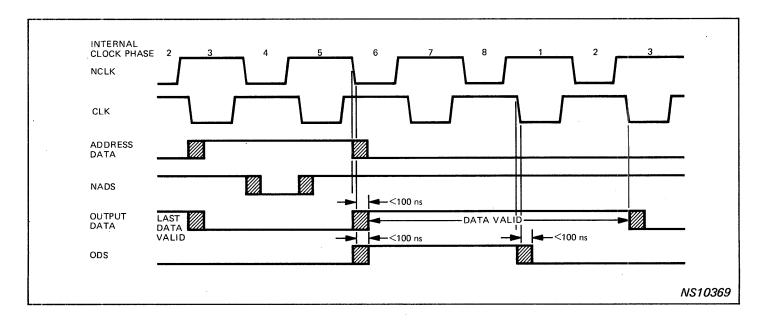

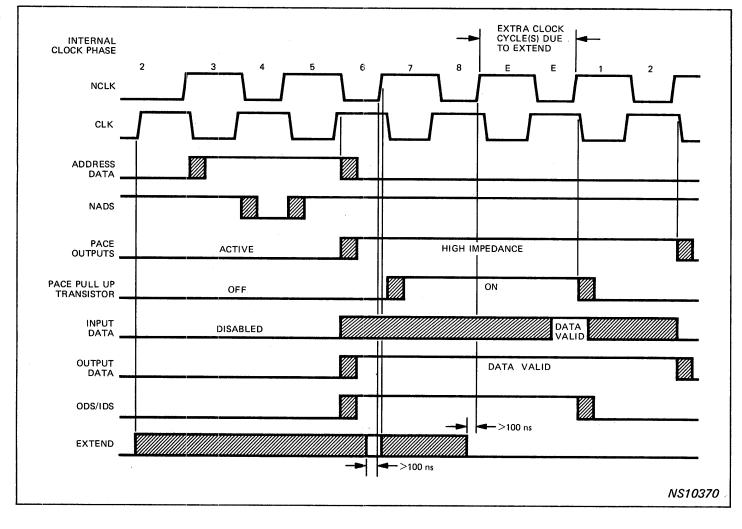

Instructions consist of four machine cycles or more, depending on the operations performed. The timing shown in figures 2-4, 2-5, and 2-6 represent the first machine cycle of the instruction being executed. The number of cycles for the instructions are given in appendix B.

# **NOTES**

- 1. Positive logic convention is used throughout this manual. A logic '1' or high signal corresponds to a morepositive voltage level. A logic '0' or low signal corresponds to a morenegative voltage level. All signal names beginning with 'N' or followed by an asterisk (\*) denote complemented signals that are asserted or activated by a logic '0'. Otherwise, signals are asserted by a logic '1'.

- Bits are numbered from 00 to 15, right to left, with bit 00 representing the least significant bit.

- 3. The X' preceding a value denotes the hexadecimal numbering system.

Figure 2-1. PACE Microprocessor Functional Block Diagram

Figure 2-2. External Clock Timing Parameters

Figure 2-3. PACE Microprocessor Pin Assignments

Table 2-1. Descriptions of PACE Hardwired Signals

| Signal<br>Mnemonic/Name                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                           | NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                           | <ol> <li>Some of the PACE microprocessor functions and buses referred to in the signal descriptions are illustrated in figure 2-1.</li> <li>Refer to figures 2-4, 2-5, and 2-6 when signal descriptions discuss address output/data input timing, data output timing, and extending I/O signal timing, respectively.</li> <li>Figure 2-7 illustrates user flag timing considerations.</li> </ol>                                                                                                                                                                                   |  |  |

| CLK, NCLK/<br>True and complemented clock | External true and complemented clock inputs to PACE. Used in generation of PACE internal multiphase clock signals that provide timing control for internal PACE functions.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| D00-D15/Data Bits 00-15                   | Input/output MOS Data Bus Lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| IDS/Input Data Strobe                     | PACE output signal used to enable external devices so data can be placed on-line to PACE. IDS operation is as follows:  1. Following output of peripheral or memory address information from PACE (see figure 2-4), D00-D15 data line drivers (internal to PACE) assume high-impedance state and PACE Control Logic drives IDS Signal high.  2. IDS remains high for approximately 1.5 CLK periods.  3. Valid input data to PACE must be present on D00-D15 Input/Output Data Bus Lines when IDS is driven low again by Control Logic after approximately 1.5-CLK-period duration. |  |  |

Table 2-1. Descriptions of PACE Hardwired Signals (Continued)

| Signal<br>Mnemonic/Name       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ODS/Output Data Strobe        | PACE output signal used to enable external devices to accept data output from PACE. ODS operation is as follows:  1. Following output of peripheral or memory address information from PACE (see figure 2-5), data are placed on D00-D15 Input/Output Data Bus Lines by PACE.  2. At approximately the same time that data are placed on Input/Output Data Bus, ODS Signal is driven high by PACE Control Logic to signify that output data from PACE are available to memory or peripherals.  3. ODS remains high for approximately 1.5 CLK periods.  4. Output data remain on Input/Output Data Bus after ODS is driven low again by Control Logic after approximately 1.5-CLK-period duration. Thus, ODS trailing edge can be used to clock PACE output data into External Data Latch (ALE). ODS can also be used as read/write control signal for external RAM memory elements. |

| NADS/Address Data Strobe      | PACE output signal used to clock address information from PACE into ALE. After address information (see figures 2-4 and 2-5) is placed on Input/Output Data Bus by PACE, NADS Signal is driven low for approximately 0.5 CLK period by PACE Control Logic. NADS is active in middle of approximately 1.5 CLK periods that address information is valid. Thus, either edge of NADS can be used to clock address information into ALE.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| EXTEND/Extended Data Transfer | PACE input signal used to temporarily increase time duration of data input/output transfers to accommodate accessing of slow memories or peripherals without altering CLK frequency.  EXTEND Signal must be driven high at beginning of ODS or IDS Signal (see figure 2-6). If EXTEND is held high as indicated in figure 2-6, data-transfer operation is extended by 1 CLK period. Holding EXTEND high for additional n clock periods increases data-transfer timing by n + 1 clock periods.                                                                                                                                                                                                                                                                                                                                                                                       |

| NINIT/Initialize              | PACE input signal that initializes microprocessor functions. When NINIT is low, PACE operation is suspended and all PACE strobe signals (IDS, ODS, NADS, and so forth) are set to inactive state. After NINIT completes low-to-high transition, the following conditions are effected:  1. PACE Program Counter contents are set to zero. 2. Internal Stack Pointer (indicates last Stack level accessed) is cleared. 3. All flags and interrupt enables are set low except Level-0 Interrupt Enable which is set high. All other registers contain an arbitrary value.                                                                                                                                                                                                                                                                                                             |

| NHALT/Control Panel Halt      | PACE Control Logic input/output signal used for nonmaskable Level-0 Interrupt, microprocessor stall, and programmed HALT indicator output. When NHALT is applied as low input, microprocessor operation halts after completing execution of current instruction. When Halt Instruction is executed, NHALT Line is driven low by PACE Control Logic for a 7/8 duty cycle. Microprocessor can be stalled by using external open-collector driver to hold NHALT Line low for desired time duration, thereby overriding NHALT output buffer on PACE chip.                                                                                                                                                                                                                                                                                                                               |

Table 2-1. Descriptions of PACE Hardwired Signals (Continued)

| Signal<br>Mnemonic/Name                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONTIN/Continue Jump Condition                     | PACE Jump Condition Multiplexer input/output signal used to sense external signal through BOC Instruction. Also used to restore microprocessor operation from suspended state or cause subroutine branch to Level-0 Interrupt Service Routine (generally used to implement Control Panel functions). Driving CONTIN Input high for 4 CLK periods, minimum, causes halted microprocessor to resume operation. As output, CONTIN is driven low for approximately 3 clock periods by PACE Jump Condition Multiplexer to acknowledge that microprocessor operation is stalled. CONTIN Line must be pulsed to terminate Halt Instruction. |

| BPS/Base Page Select                               | Input signal to PACE Control Logic that enables one of two base-page addressing schemes to be selected. When BPS is low, first 256 words of memory constitute base page (page zero). When BPS is high, first 128 memory words and last 128 memory words constitute base page.                                                                                                                                                                                                                                                                                                                                                        |

| JC13, 14, 15/Jump Conditions 13,<br>14, and 15     | User-specified branch-condition inputs to PACE Jump Condition Multiplexer. Some possible uses are testing system status and receiving serial data. When JC13, 14, or 15 is high, PACE Branch-On Condition Instruction effects program branch if Jump Condition Input is true.                                                                                                                                                                                                                                                                                                                                                        |

| F11, 12, 13, 14/Flags 11, 12,<br>13, and 14        | PACE Status and Control Flags Register general-purpose control flag outputs. F11-14 may be used for direct control of system functions or serial data output. Individual flags may be set by PACE Set Flag Instruction and pulsed or reset by Pulse Flag Instruction (see figure 2-7). Push Flag and Pull Flag Instructions permit contents of Status and Control Flags Register to be saved on Stack during Interrupt Service Routine or subroutine execution, and then restored.                                                                                                                                                   |

| NIR2, 3, 4, 5/Interrupt Requests 2, 3,<br>4, and 5 | Inputs to PACE Interrupt Control Logic. When NIR2, 3, 4, or 5 Input is low for 1 CLK period, minimum, corresponding internal Interrupt Request Latch is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |