## The PACE Microprocessor

# A Logic Designer's Guide to Program Equivalents of TTL Functions

**MARCH 1976**

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

Manufactured under one or more of the following U.S. patents: 3083262, 3189758, 3231797, 3303356, 3317671, 3323071, 3381071, 3408542, 3421025, 3426423, 3440498, 3518750, 3519897, 3557431, 3560765, 3566218, 3571630, 3575609, 3579059, 3593069, 3597640, 3607469, 3617859, 3631312, 3633052, 3638131, 3648071, 3651565, 3693248.

National does not assume any responsibility for use of any circuitry described; no circuit patent licenses are implied; and National reserves the right, at any time without notice, to change said circuitry.

## **PREFACE**

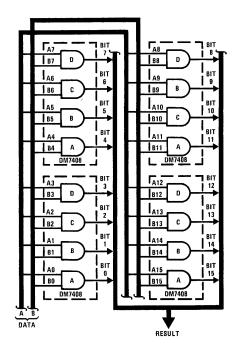

This handbook is intended for the TTL system designer; it shows him how standard TTL/MSI logic functions are implemented in software for the PACE microprocessor. This handbook in fact describes two classes of hardware simulation by PACE.

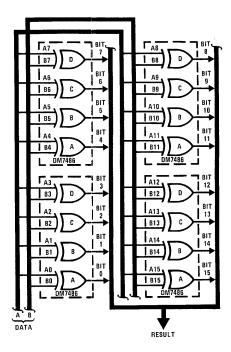

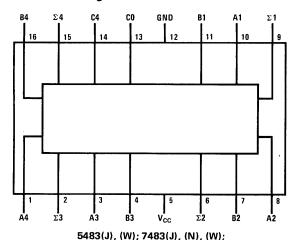

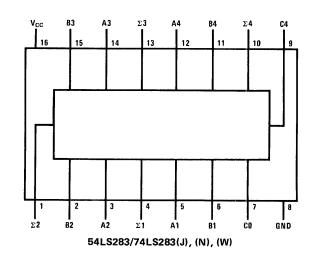

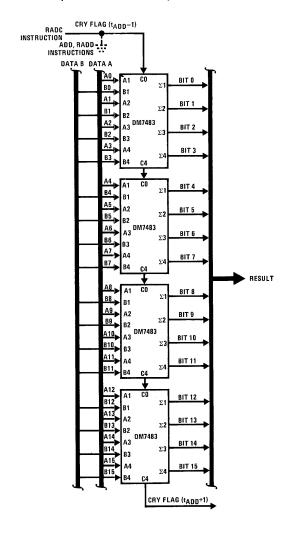

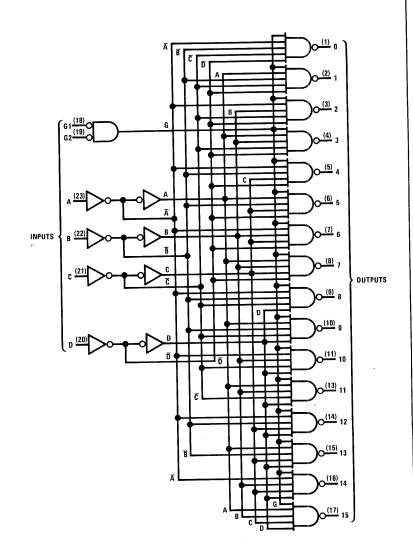

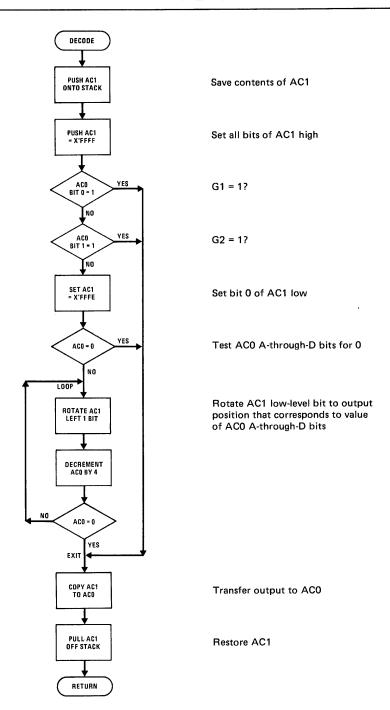

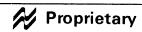

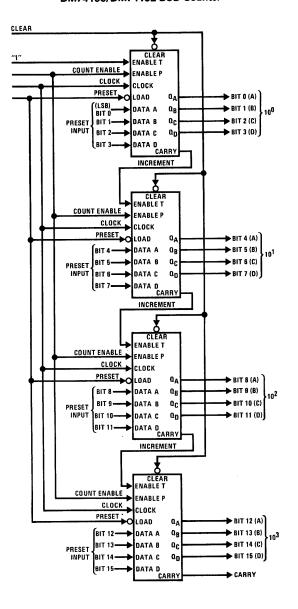

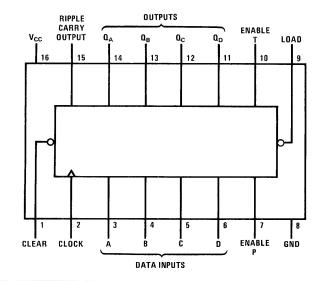

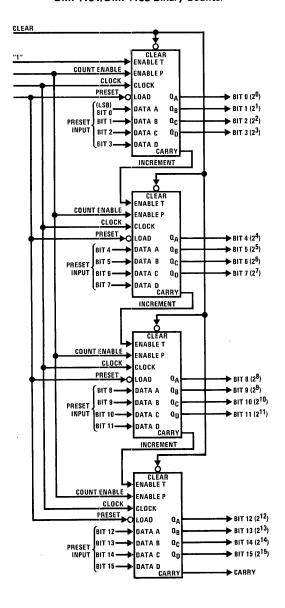

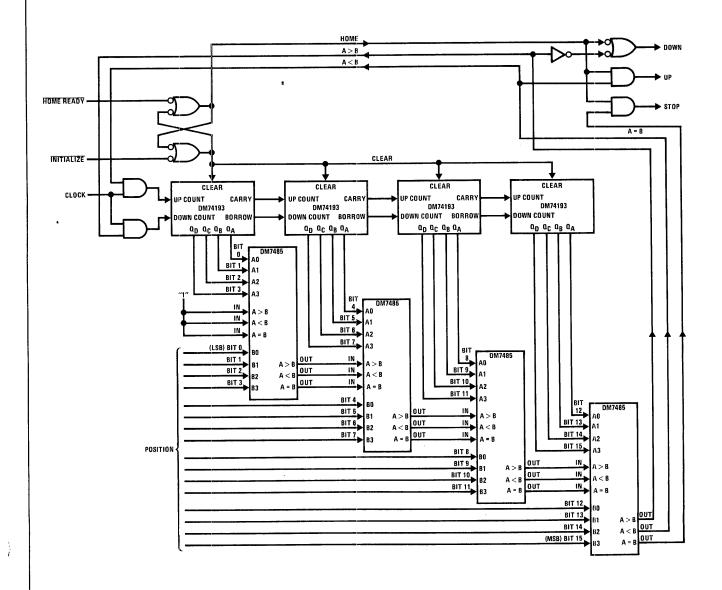

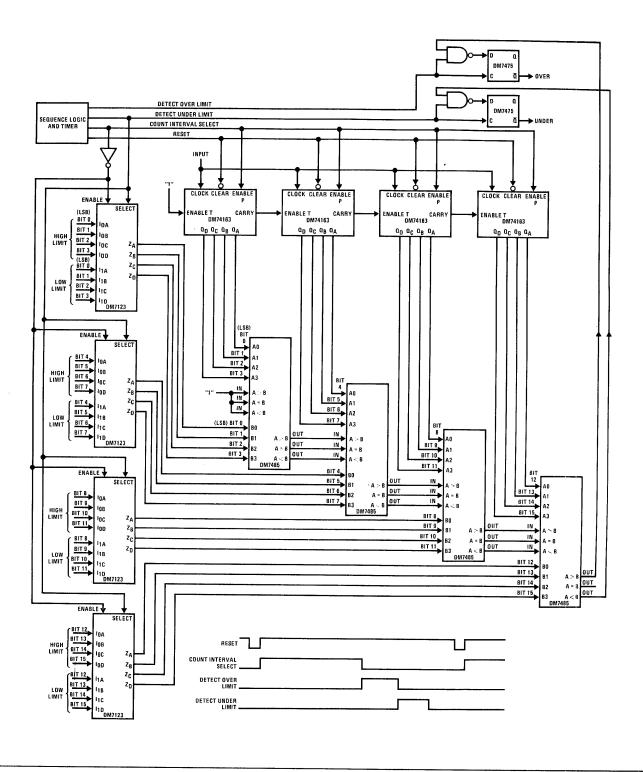

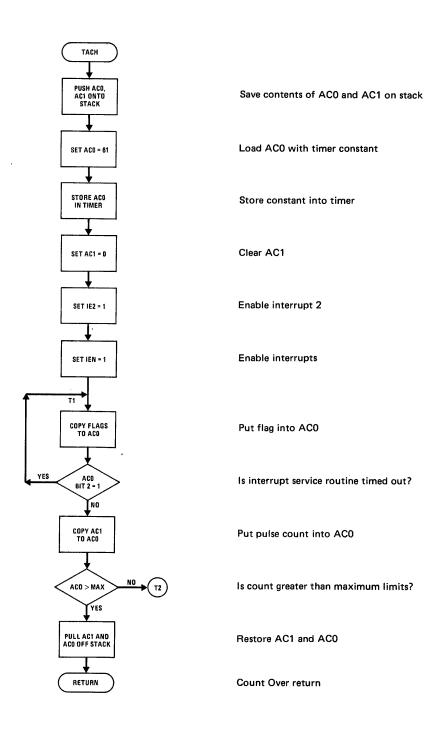

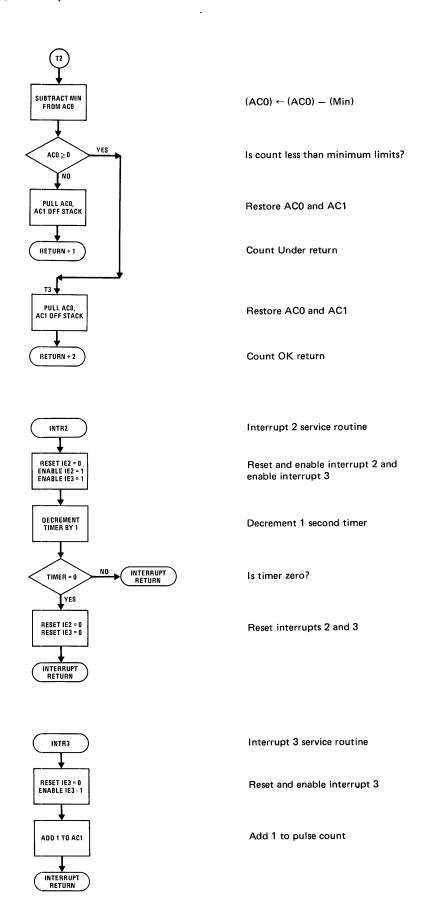

The first class describes the simulation of standard, single-package TTL functions (e.g., a DM74154 4-line to 16-line decoder/demultiplexer) by software routines (although about half of this class are examples of multiple-package extensions of standard 4-bit functions to 16 bits), while the second class describes the simulation in software of multiple, "non-standard," subsystem functions (e.g., a tachometer comprised of four DM7413 binary counters, four DM7485 comparators, and four DM7123 multiplexers.

With one exception, the second class of simulations — the subsystems — are presented as a single entity. That is, the routines for the various building blocks of the subsystem are not presented individually; instead, a single software solution is presented as a cohesive whole in much the same way that a designer (one used to thinking in terms of software) would approach the problem.

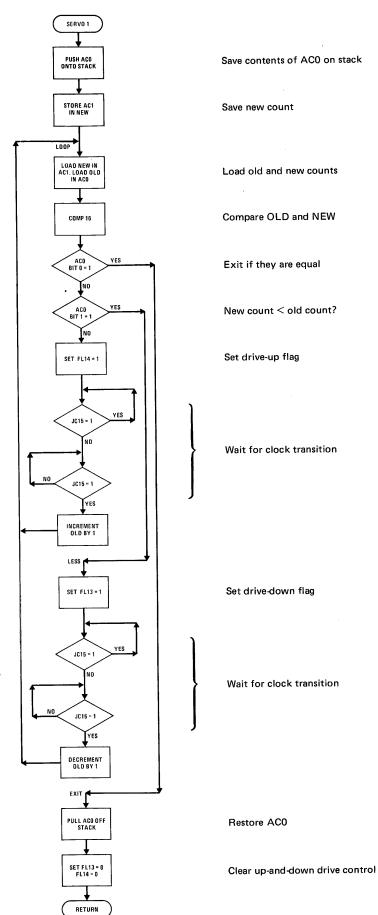

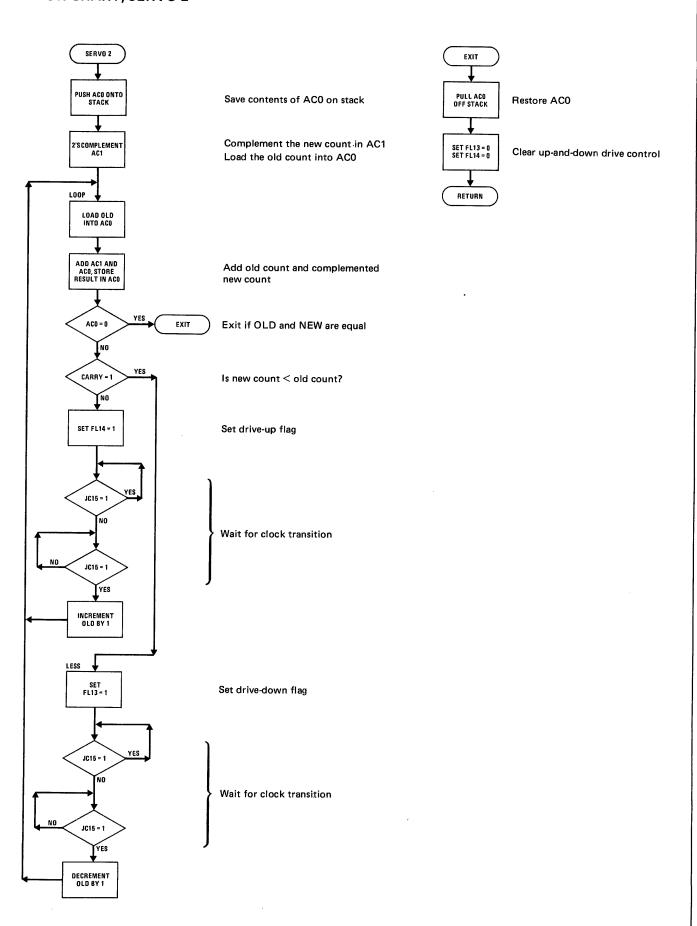

To bridge the gap between the single-package simulations and the subsystem simulations — that is, to show the linking of the subsystem's building blocks — one subsystem simulation (the digital servo) is presented in both a step-by-step manner (to show its building-block components, their subroutines, and how these subroutines are meshed to form the complete subsystem function), and as a final, single routine that is a somewhat more elegant blend of its component parts.

All of the simulations have been desk-checked and assembled; in fact, this handbook reproduces the actual "no error" assembled program print-outs. This is by no means a guarantee that any given simulation will run immediately on any given PACE system; this no-run phenomenon, common to all software-controlled systems, is explained on page 1-5.

All simulations in this handbook conform to several ground rules. For the standard TTL function simulations, it is assumed that:

- 1. Input conditions are set into, and outputs formed in, one of PACE's four accumulators (ACO, AC1, AC2, or AC3);

- 2. The result of the operations the output is left in an accumulator (i.e., transfers to and from memory or peripherals are not shown); and,

- 3. The interrupt, flag, and jump-condition capabilities of the PACE microprocessor are not used.

For subsystem simulations, the first two rules (nos. 1 and 2) remain in effect, but rule no. 3 is voided: interrupts, flags, and jump conditions are exploited.

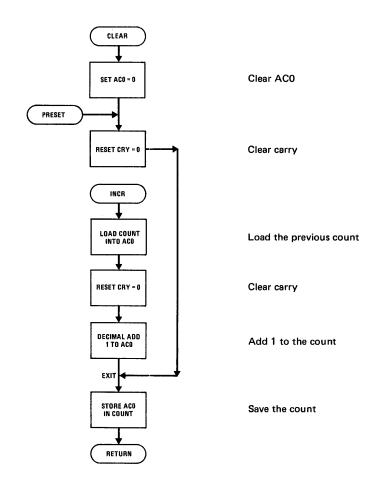

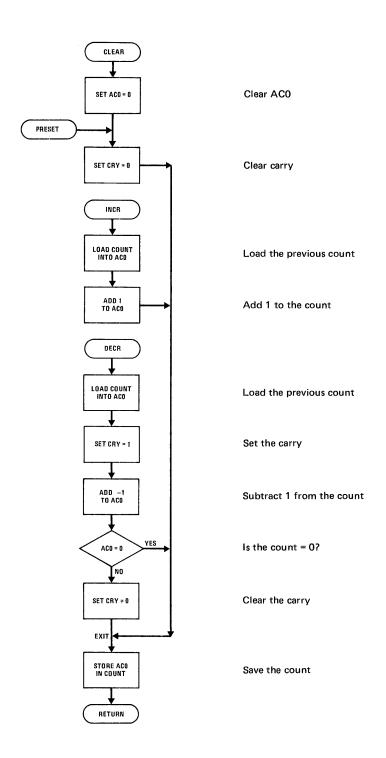

Note that for the TTL counter simulations we bend (slightly) rule no. 3 so that the carry flag (status register bit 7) is set to indicate the finish of the count sequence; the simulations, in fact, are written in a way that ensures the carry flag will be reset by every subroutine call that does not result in completion of the count sequence.

In practice, however, instructions associated with a carry-flag reset may be unnecessary, as such resets are needed only when the carry flag either is tested following every return to the main program or is automatically included as an input by a DECA or SUBB instruction following the subroutine.

Where applicable, each DECA or SUBB instruction within *any* subroutine is preceded by a reset of the carry flag (PFLG 15 instruction); again, this procedure may not be needed in practice if you know that the carry flag is in the reset state when the subroutine is called by the main program.

The programs in this book have been assembled in relocatable mode, rather than in absolute mode. In relocatable mode, the starting address of the program is defined when the binary object code (of the assembled program) is loaded into memory by the loader program; in absolute mode the starting address is defined when the program is assembled.

If an absolute program had been loaded starting at, say, location X'100, but the programmer now wants to load the program starting at, say, location X'200, he or she must reassemble the program with the new starting address. A relocatable program, on the other hand, may be loaded starting at location X'100, X'200, or any other location.

The programmer normally would use an absolute-sector (.ASECT) directive in the program to indicate absolute mode, or a base-page-sector (.BSECT) or top-page-sector (.TSECT) directive to indicate relocatable mode. But since the PACE assembler initializes in the top-page-sector relocatable mode, a directive is not required.

# **TABLE of CONTENTS**

| PREFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | iii                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| The Classical Computer Microprogramming Software and the Microprocessor The Software Process                                                                                                                                                                                                                                                                                                                                                                                                         | 1-1<br>1-1<br>1-3<br>1-3<br>1-4                                |

| Data Representation  Memory Addressing Instruction Summary (Table 4) Branch Instructions Skip Instructions Memory Data-Transfer Instructions Memory Data-Operate Instructions Register Data-Transfer Instructions Register Data-Operate Instructions                                                                                                                                                                                                                                                 | -12                                                            |

| Taking Data Out of PACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-1<br>3-1<br>3-1<br>3-2                                       |

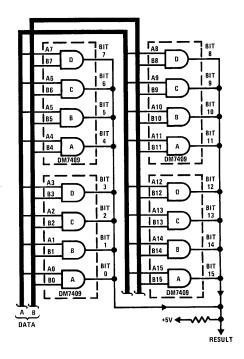

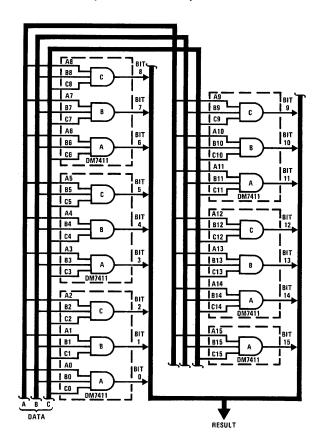

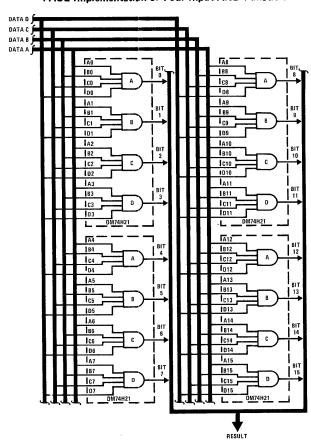

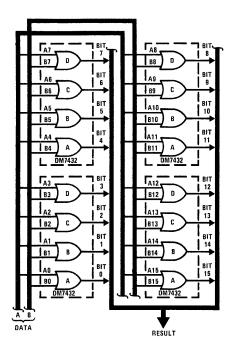

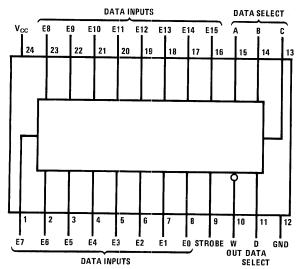

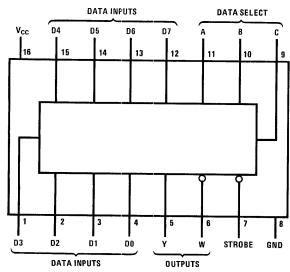

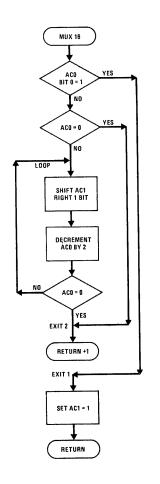

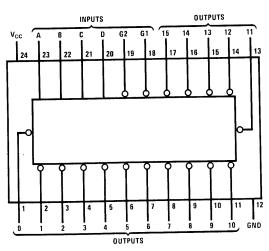

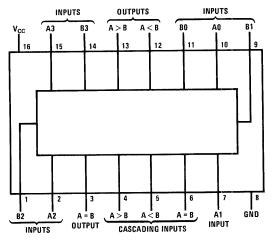

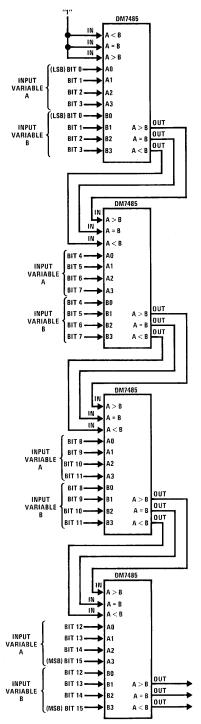

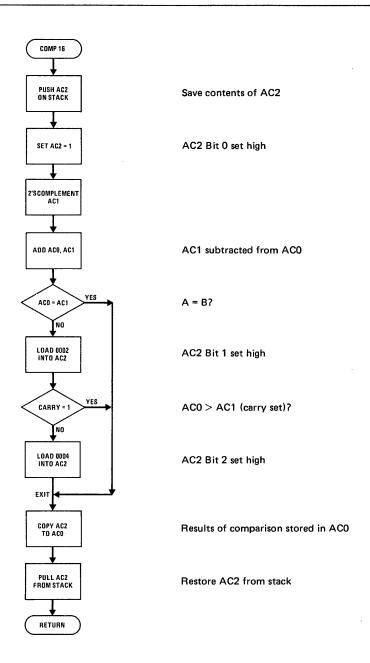

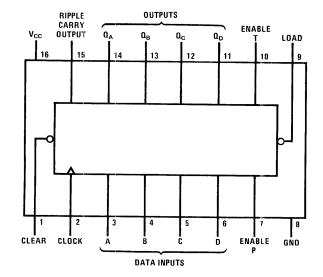

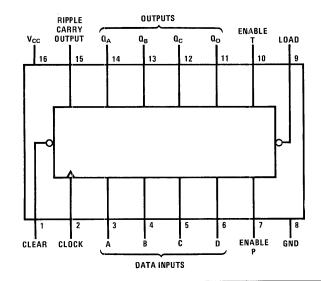

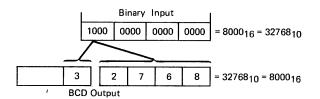

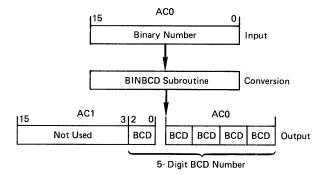

| Triple 3-Input AND Gate       2         Dual 4-Input AND Gate       2         Quad 2-Input OR Gate       4-         Quad 2-Input EXCLUSIVE-OR Gate       4-         Binary Full Adder       4-         Monostable Multivibrator       4-         16-Line to 1-Line Multiplexer       4-         4-Line to 16-Line Decoder/Demultiplexer       4-         Parity Generator/Checker       4-         16-Bit Magnitude Comparator       4-         BCD Counter       4-         Binary Counter       4- | 11<br>12<br>14<br>17<br>20<br>23<br>28<br>31<br>34<br>37<br>43 |

| Subsystems       4-         Digital Servo.       4-         Digital Tachometer       4-         Modulo-N Divider       4-         Real-Time Clock and Interval Timer       4-         Pseudo-Random Number Generation       4-         State Sequencer       4-         Switch Bounce Detection       4-                                                                                                                                                                                             | -69<br>-72<br>-74<br>-76                                       |

| B. Positive Powers of Two. C. Negative Powers of Two D. The Hexadecimal Number System                                                                                                                                                                                                                                                                                                                                                                                                                | 10                                                             |

#### CHAPTER 1-A BRIEF INTRODUCTION TO MICROPROCESSING

Today, a computer connotes a machine that, once it is set up for a specific problem, performs a computation automatically and without human intervention. The present use of the term "computer" has a second connotation-it usually refers to an electronic machine, although mechanical and electromechanical computers do exist. Two important factors dictate the intimate association between computers and electronics: no known principle other than electronics allows a machine to attain the speeds now commonplace in both large- and small-scale computers; and, no other principle permits comparable design convenience. In particular, digital computers use numbers that are represented by the presence or absence of a voltage level or pulse on a given signal line. A single pulse defines one "bit" (short for binary digit, a base-2 number); a group of pulses considered as a unit is called a "word", where a word may represent a computational quantity or a machine directive.

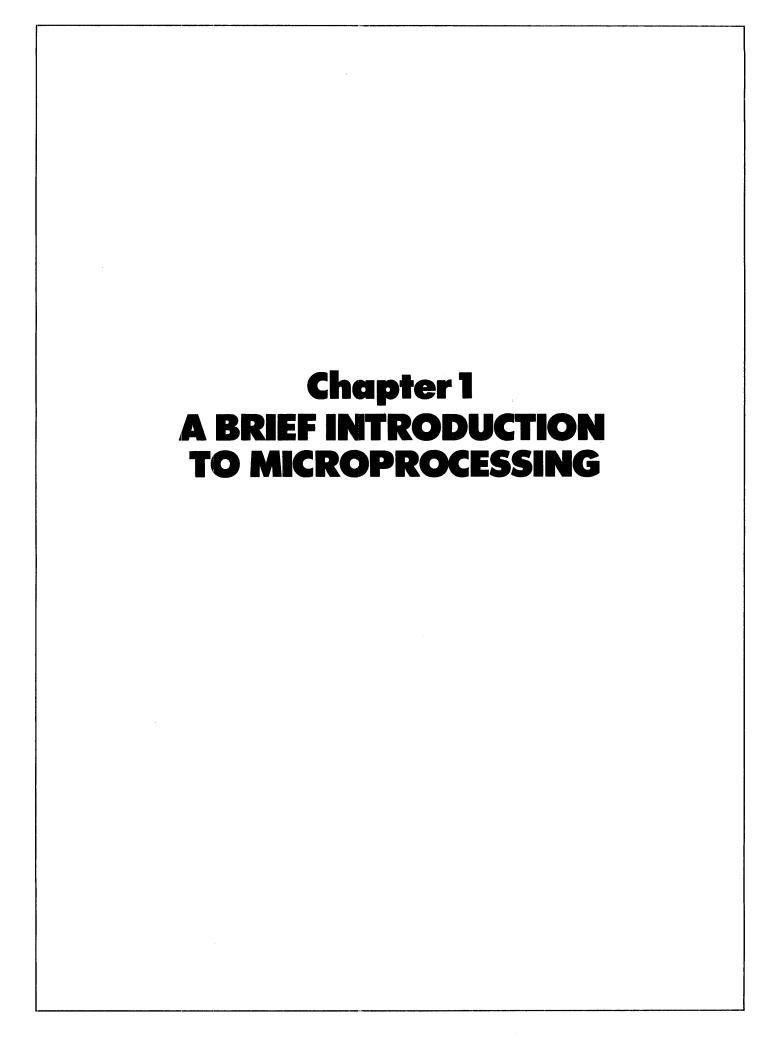

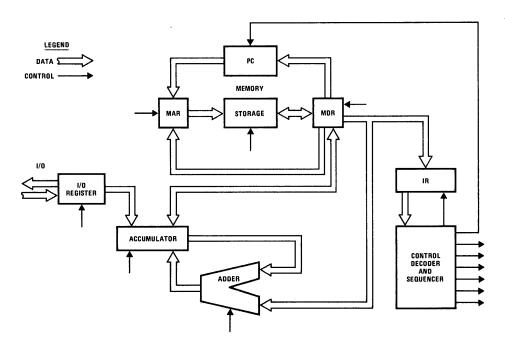

For purposes of illustration, we shall compare two systems for solving simple mathematical expressions, both of which are comprised of the classical elements of a computer: an input/output device, a memory, a control section, and an arithmetic and logic unit or ALU (the computational element). The control section, together with the ALU, is considered to be the central processing unit (CPU). (See Figure 1)

FIGURE 1. Basic Elements of a Digital Computer

#### THE MAN-CALCULATOR

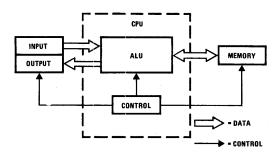

The first system (Figure 2) is comprised of a man and a calculator. The man's fingers represent the input, his eyes coupled with the calculator's output represent the system output, the calculator electronics function as the ALU, and his brain serves as the memory as well as the

FIGURE 2. Man + Calculator = Computer

control section. Here is the sequence of events that occurs when our man-calculator solves the problem 6 + 2 = ?

- 1. Brain accesses first number to be added, a "6";

- 2. Brain orders hand to depress "6" key;

- 3. Brain identifies addition operation;

- 4. Brain orders hand to depress "+" key;

- 5. Brain accesses second number to be added, a "2";

- Brain determines that all necessary information has been provided and signals the ALU to complete computation by ordering hand to depress "=" key;

- 7. ALU (calculator) makes computation;

- 8. ALU displays result on readout;

- 9. Eyes signal brain, brain recognizes this number as the result of the specific calculation;

- Brain stores result, "8", in a location that it appropriately identifies to itself to facilitate later recall.

#### THE CLASSICAL COMPUTER

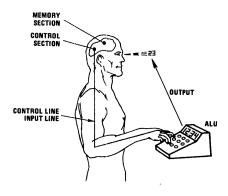

We shall now develop a classical computer and illustrate how it might be used to solve the same problem. To begin, note that the memory (Figure 3) is composed of storage space for a large number of words; each storage space is identified by a unique "address". The word stored at a given address may be either computational data or a machine directive (such as add, read from memory, etc.). Two temporary storage registers, each capable of containing one word, complete the memory. These registers are designated as "memory address register" (MAR) and "memory data register" (MDR). The MAR contains the binary representation of the address at which information is to be read out of memory or written (stored) into memory, while the MDR contains the data being exchanged with memory.

FIGURE 3. Elements of a Memory

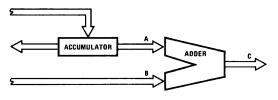

Turning to the ALU, Figure 4 shows that this portion of a computer, in its simplest form, comprises an "adder" that adds (or performs similar logical operations upon) two inputs A and B and produces an output at C, and an "accumulator", which maintains intermediate results of a computation or numbers for a pending computation.

FIGURE 4. Arithmetic and Logic Unit

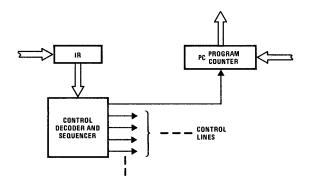

The remainder of the CPU, the control portion, is implemented using an "instruction register" (IR), a "control decoder and sequencer", and a program counter (PC). These are shown in Figure 5. A machine directive (instruction) is transferred into the IR and is subsequently interpreted by the decoder/sequencer, which issues the appropriate control pulses to the other computer elements. The PC contains, at any given time, the address in memory of the next machine directive or instruction. This counter is normally incremented by a count of one immediately following the reading of a new instruction. The PC contents may be replaced by the contents of a specified memory location if the last instruction was of the "jump" class. This causes the next instruction to be read from a program-specified location, instead of from the next sequential location as is the general rule.

FIGURE 5. Computer Control

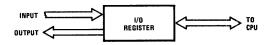

Finally, a means of input/output (I/O) is provided by an "I/O Register", through which data is exchanged with external (peripheral) devices. (Figure 6.)

FIGURE 6. I/O Register Interface

We have now collected all the basic elements of a computer; all that remains to do is to interconnect them into a functioning, automatic processor. *Figure 7* shows such an interconnection, and represents a complete computer.

The analysis continues with the execution of the same problem used to illustrate the man-calculator, but somewhat rephrased:

"Read-in a number from the I/O. Store it in memory location 50. Read-in another number from the I/O. Add the two numbers together. Store the result in memory location 60, and halt."

A "program" has been written to execute this task, and is stored in consecutive memory locations beginning at 100. This program, written in an artificial symbolic language, is shown in Table 1.

**TABLE 1. Sample Program**

| Memory Location | Instruction (Contents)      |

|-----------------|-----------------------------|

| 100             | Input to accumulator        |

| 101             | Store accumulator at 50     |

| 102             | Input to accumulator        |

| 103             | Add accum, Loc. 50          |

|                 | Place result in accumulator |

| 104             | Store accumulator at 60     |

| 105             | Halt                        |

FIGURE 7. Simplified CPU and Memory

#### **Computer States**

All computers spend about equal periods of time in one of two distinct states: "fetch", or "execute". In the fetch state, the computer reads from memory the next sequential instruction and places it in the instruction register (IR). In the execute state, that instruction is carried out as a series of transfers from one register to another and as various ALU operations. Table 2 examines the program shown in Table 1, as it is actually executed, by specifying the contents of each register at each machine cycle (time interval) and assuming the computer is now ready to fetch the first instruction in our program.

All computers (processors, CPU's, etc.) operate in a similar manner, regardless of their size or intended purpose, although many variations are possible within the basic architectural framework. Common variations include, for example, highly-sophisticated I/O structures (some of which have direct and/or autonomous communications with memory), multiple accumulators for programming flexibility, index registers that allow a memory address to be modified by a computed value, multi-level interrupt capability, and on and on.

#### **MICROPROGRAMMING**

One of the most exciting architectural concepts to gain popularity in the past few years is that of microprogrammed control. A microprogrammed computer differs from the classical example in its control-unit implementation. The classical machine has for its control unit an assemblage of logic elements (gates, counters, flip-flops, etc.) interconnected to realize certain combinatorial and sequential Boolean equations. On the other hand, a microprogrammed machine uses the concept of a "computer within a computer." That is, the control unit has all the functional elements that comprise a classical computer, including read-only memory (ROM).

The "inner computer", which (generally) is not apparent to the user, executes the user's program instructions by executing a series of its own microinstructions, thereby controlling data transfers and all functions from computed results. And this means that changing the stored microprogram that generates the control signals alters the entire complexion of the computer. By altering a few words stored in the ROM, the computer behaves in an entirely new fashion — it can execute a completely different set of instructions, simulate other computers, tailor itself to a specified application. It is this capability for "custom-tailoring" that allows a microprogrammed machine to be optimized for a given usage. By so extracting the utmost measure of efficiency, a microprogram-controlled machine is less costly and easier to adapt to any given situation, no matter how diverse or demanding.

#### Software and the Microprocessor

It is possible to program a device that isn't a computer at all. An operational amplifier, for example, is a circuit that is basically a multiplier. Something is put in, something comes out; the op amp performs a linear function. But this building block can do something other than multiplication: a capacitor, for example, connected from the op amp's output to its input, creates a "programmed-by-wire" integrator.

As it is with the op amp, so it is with the microprocessor. A microprocessor is a super circuit—a black box with a transfer function that changes in accordance with a set of commands called a program. Inside the black box (i.e., on the chip) is a collection of building-block logic—an assemblage of many logic elements. You can in fact replace the microprocessor in any system with sets of random logic on PC boards, but you would have to change the logic boards on each clock pulse!

Thus, if you know what a flip-flop does you know what it does inside or outside a microprocessor; an AND gate ANDs whether it's inside a microprocessor or on a lab bench. But in a microprocessor literally thousands of such logic elements are squeezed onto one or two chips. And this creates a problem: too much information, too few pins.

TABLE 2. Register Content

| NOTES | PC  | ACCUM. | MAR | MDR   | I/O REG. | IR    | MEMORY<br>(R=READ)<br>(W=WRITE) | STATE   |

|-------|-----|--------|-----|-------|----------|-------|---------------------------------|---------|

|       | 100 | ?      | ?   | ?     | ?        | ?     | ?                               | ?       |

| Start | 100 | ?      | 100 | (100) | ?        | (100) | R                               | Fetch   |

| Input | 100 | 6      | 100 | (100) | 6        | (100) |                                 | Execute |

|       | 101 | 6      | 101 | (101) | ?        | (101) | R                               | Fetch   |

| Store | 101 | 6      | 50  | 6     | ?        | (101) | w                               | Execute |

|       | 102 | 6      | 102 | (102) | ?        | (102) | R                               | Fetch   |

| Input | 102 | 2      | 102 | (102) | 2        | (102) |                                 | Execute |

| ·     | 103 | 2      | 103 | (103) | ?        | (103) | R                               | Fetch   |

|       | 103 | 2      | 50  | 6     | ?        | (103) | R                               | Fetch   |

| Add   | 103 | 8      | 50  | 6     | ?        | (103) |                                 | Execute |

|       | 104 | 8      | 104 | (104) | ?        | (104) | R                               | Fetch   |

| Store | 104 | 8      | 60  | 8     | ?        | (104) | w                               | Execute |

|       | 105 | 8      | 105 | (105) | ?        | (105) | R                               | Fetch   |

| Halt  | 105 | 8      | 105 | (105) | ?        | (105) |                                 | Execute |

To overcome the pin problem, microprocessor manufacturers strap every logic element to every other logic element through a set of buses that allows mutual, element-to-element communications. Bus connections are made through a series of electronic switches; opening and closing the switches transfers the data through the microprocessor's maze to produce a control function. And it is software that sets the switches. System software is a set of tools, supplied by the microprocessor manufacturer, that allows you to construct application programs—programs that let the microprocessor do something.

To appreciate what software does for you, consider an elementary operation such as addition. Get A, get B, add them together and come out with C. Easy? In decimal notation, yes. But this trivial problem is not quite as simple when one speaks in binary. Dealing with long binary numbers is complex and difficult because one's and zero's aren't a natural language for Homo Sapiens. We have problems trying to figure out what's going on when we look at raw binary; writing it is even more troublesome.

Can you imagine looking down 14 sheets of printout, each with 65 lines of binary gibberish, attempting to determine what you did wrong? Yet this is ultimately how you program a job on a microprocessor. You have to write the story of how the processor is to wire itself from microsecond to microsecond. So all system software, the whole range of it that every manufacturer offers, is aimed at only one thing: to get you from the stated idea to the working program as painlessly and as rapidly as possible.

#### The Software Process

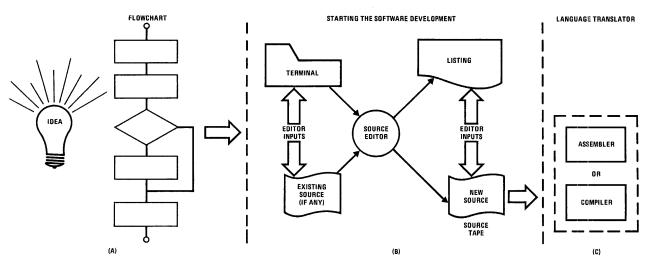

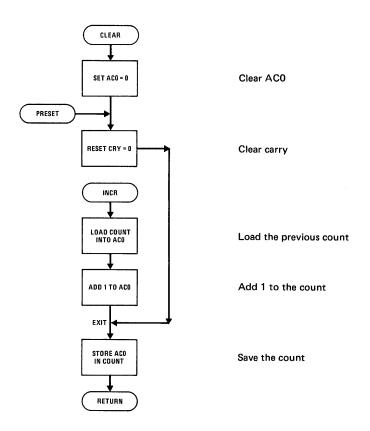

In the construction of application software, you first evolve a flowchart (Figure 8A) that describes the functions to be performed and their order. (At this stage

your thought processes and activities resemble those of the random-logic designer.) Once the chart is laid out, you start to code the program in either a high-level or a mnemonic-shorthand language that both you and your system understand. Here you encounter your first piece of software, the Text or Source Editor (Figure 8B).

Most microprocessor users write on continuous media (paper tape or cassettes), which do not allow you to get in and pull out one piece. Thus, corrections on a continuous source involve making a wholly new source—a constant problem and an awfully wasteful task. But there is a utility program called a Source Editor that lets you do the entire job with a Teletype<sup>®</sup> and a microprocessor Development System. If you make an error, just tell the Editor what changes to make and it's done! The Editor helps you massage the source code until it looks like it's going to work. Then, with the corrected (?) program in the Editor's memory cells, you push a button and a paper tape (or whatever) is put into your hands.

The "whatever" that has just been put into your hands has one minor, relatively insignificant, but fatal error—the microprocessor cannot understand a single bit or byte of it. But do not despair: an electronic Translator (Figure 8C) converts the continuous, source-mnemonic shorthand into something the microprocessor can understand.

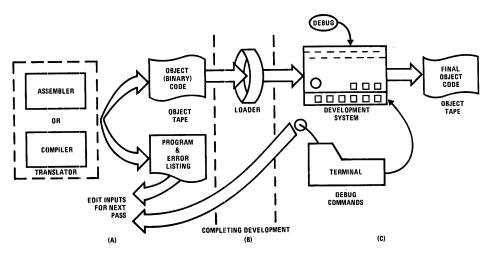

The Translator (Figure 9A) takes the source tape and gives back three outputs:

- The Program Listing—a copy of both the source and binary object codes;

- The Error Listing—a roster of all grammatical, label, and syntax errors; and,

- The Binary Object Code—a paper tape (or whatever) with the machine-readable binary translation of the program.

FIGURE 8. The programmer's ideas, expressed in a flowchart, are written out in mnemonic form to serve as Editor inputs. New inputs plus sections of existing programs are combined to form a new Source; this Source is the input to the language Translator.

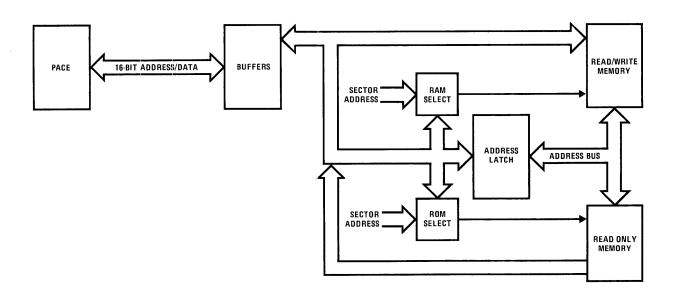

FIGURE 9. Translator outputs include: an Error Listing (to serve as Editor inputs on the next pass); a Program Listing; and a tape of the translated program (the Object Tape). The Object Tape is deposited by the Loader into Read/Write Memory inside the Development System. Here the new code is run by the DEBUG program according to commands input by you. The code can be modified via terminal inputs until it runs properly; working code is then dumped from memory. Note that although a workable object tape may exist at this time, your job is not complete until you edit and retranslate your Source to produce code identical to the working code.

But there are two types of Translators—the Assembler and its exotic cousin, the Compiler—and there may be some argument as to which translation device is the more useful: Should you use an Assembler or a Compiler to translate the mnemonic source? The difference is in the mnemonics.

If you happen to have run programs on minicomputers, then you've been exposed to the so-called "assembly language" mnemonics: LD means load; JMP means jump; ST means store; etc. It's the shortest language (outside of raw binary) used to talk with the processor. Programming with this shorthand is a bit tricky but an assembler-type Translator gives you a better feel for the machine and you can usually pare down the number of statements necessary to get the message across; and this saves time and money.

On the other hand, a compiler-type Translator lets you write in a high-level language that looks like English (Fortran, etc.). Its statements can easily be read by someone with no training at all. The Compiler translates these statements into a series of machine commands that carry out the desired function with the advantages of faster programming and a self-documenting program that you can read directly. But you often pay for this ease of use: since the Compiler deals with more general statements, it often translates in an inefficient way using more machine commands than really necessary at that level. Extra statements consume memory and result in slower program execution.

So, in retrospect, Compilers cut programming time and costs, but raise system costs. Assemblers do just the opposite. Which should you use? Compilers are most useful to those of you who constantly re-program your systems and make few versions of each program. Assembler users, on the other hand, will be those of you who will program the system once, then reproduce it a thousand or more times; programming costs are amortized over the production run and in memory savings.

At this point in the writing of a program many of you will wish that you could forget the whole thing, for there are programs with one hundred code lines that come out of the Translator with four hundred errors! But forge onward. Make another pass through the Source Editor (and another, and another. . .), to correct the errors that the Translator has spotted. Eventually, you will get your reward, the sweetest line ever printed on a computer listing: "ASSEMBLY COMPLETE - NO ERRORS." Actually, that statement simply means that the Assembler didn't find any errors. And you soon find out that this has almost nothing to do with whether or not the program will run on a machine. The reason is that the Assembler, although it helps you weed out logic errors from the program that you wrote, cannot tell you whether or not that program does exactly what you think it's going to do. In other words, there can be (and very probably will be) logic differences between your vision (of what's needed to perform a function) and that of the machine. Such an error may be one as simple as your forgetting to set a flag at some point; unimportant, perhaps, to your charting of a problem's solution, but all-important to the machine for without that bit of information your program cannot run. But other utility programs (such as DEBUG) are available to help you solve such problems.

Now that the Translator has provided you a binary tape with your program on it, you must somehow get the program into the machine's memory along with whatever other software routines your program needs for operation. The Loader (Figure 9B) does this for you; it reads your tape into a microprocessor Development System (Figure 9C), allocates memory space to the program, and stores the code in the appropriate location. Typically, several sections of memory are needed for different functions (executable code, interrupt calls, subroutine linkages, etc.), and it is up to the Loader to see that each part of the program is put into the right place. Loaders are available to load from Teletypes, paper-tape readers, and, sometimes, high-speed bulk storage devices.

Once the program is loaded, you cross your fingers and hit the RUN switch. As we've already said, very probably nothing will happen.

Now, if you are using random logic and find it doesn't work, you unplug it, repair any damaged hardware, and then try to determine what's wrong. With an oscilloscope on the gates and clocks, you try to see what's happening. But in the microprocessor only one set of logic exists, re-wiring itself at the speed of light. If you don't have any idea what's going on, the oscilloscope can't help you. What you need is a different type of fault-finding tool. The tool is a program, called DEBUG, that lets you use a Teletype as a scope to help you find out what's happening. DEBUG is loaded into a Development System first, then your program is entered. You peck away at the TTY and say, "DEBUG, run my program from here to there, stop it, and tell me what is in memory." The TTY rattles and you've got the answer on a printout. "Show me what is in these accumulators." DEBUG does! "Show me this, show me that." Done, done. As your program is stepped through, you'll encounter parts that don't work. These snags are cajoled and fondled individually until the whole thing runs-perfectly-and you have a working object code that represents your algorithm in ones and zeros.

There is an alternative to the microprocessor debug section of a Development System. It is called a Simulator, and it typically runs on a large computer and includes both debug and simulation. To use it, load the binary code into the computer, call the Simulator, and then direct it to exercise the code to find the defects. However, this approach can only take you part of the way; it will not isolate timing problems that have to do with the outside world.

When the Simulator wants an input, it stops and asks for one. You sit there and peck away at the typewriter, which is fine if you want to test things that are slow. But if you wish to test a program that operates, say, a 100-kHz I/O converter, you won't be able to keep up with it. So the Simulator can only take you so far. Ultimately you have to return to the hardware prototype approach, and this is why the microprocessor manufacturers have felt it necessary to produce sophisticated hardware prototyping tools.

We at National believe a Simulator really doesn't help. We encourage users to take the Development System itself, put in the actual interfaces to be used, and use DEBUG to massage the program in real-time and watch what it does.

#### **CHAPTER 2 — THE PACE INSTRUCTION SET**

This chapter contains detailed descriptions of the instructions provided by the PACE microprocessor. The PACE microprocessor provides a general purpose mix of 45 instructions, which are divided into eight format groups as follows:

- Branch instructions

- Skip instructions

- Memory data-transfer instructions

- Memory data-operate instructions

- Register data-transfer instructions

- Register data-operate instructions

- Shift and rotate instructions

- Miscellaneous instructions

Many of the 45 instructions comprising the eight format groups could be generally classified as falling into one of three instruction classes:

- Memory-reference instructions

- Register instructions

- Data-transfer instructions

The memory-reference instructions use a flexible memory addressing scheme that provides three floating memory pages of 256 words each and one fixed memory page of 256 words. The register instructions provide a convenient means of data manipulation without accessing memory. The data-transfer instructions provide a convenient means of moving data among the functional blocks of the PACE microprocessor system.

In the PACE microprocessor, data is represented in the twos-complement number system, in which the negative of a number is formed by complementing each bit and, then, adding one to the complemented value of the number. The most-significant bit position indicates the sign of the number, 0 for positive and 1 for negative. With a single 16-bit value, the greatest positive number is X'7FFFF or (32767) 10, and the most negative number is X'8000 or (32768) 10. When the 8-bit data length is selected, the largest positive number is X'7F or (127) 10, and the most negative number is X'80 or (128) 10.

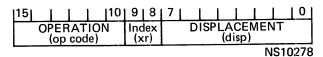

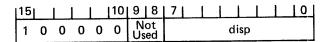

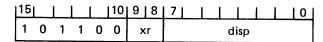

Both direct and indirect memory addressing instructions are included in the PACE instruction set. Direct memory addressing has three available modes: base-page; Program-Counter (PC) relative; and, indexed. The addressing mode is specified by the xr field of the instruction as illustrated in *Figure 10*.

FIGURE 10. Memory-Reference Instruction Format

When the xr field is 00, base-page (page zero) addressing is specified. Two types of base-page addressing are available. The type of base-page addressing selected is

determined by the state of the Base-Page Select Signal (BPS) input. When BPS is low (0), the 16-bit memory address is formed by setting bits 8 through 15 to zero and using the 8-bit displacement (disp) field for bits 0 through 7. Thus, the first 256 words of memory (locations 0 through 255) can be addressed. When BPS is high (1), the 16-bit memory address is formed by setting bits 8 through 15 equal to bit 7 of the disp field and using disp for bits 0 through 7. Thus, the first 128 words (0 through 127) and the last 128 words (X'FF80 through X'FFFF) of memory can be addressed. The latter technique is useful for splitting the base page between read/write and read-only memories or between memory and peripheral devices. Consequently, base-page addressing provides a convenient means of accessing data or peripherals.

When the xr field is 01, addressing relative to the PC is specified. During the PC-relative addressing mode, the memory address is formed by adding the contents of PC to the value of the disp field, which is interpreted as a signed number. The 8-bit disp field is interpreted as a 16-bit value with the bit 7 value used for bits 8 through 15, thereby permitting representation of numbers from -128 through 127.

When the memory address is formed, the PC already is incremented and contains an address value that is one greater than the location of the current instruction. Thus, memory addresses that can be referenced range from 127 locations below through 128 locations above the address of the current instruction.

The indexed (or accumulator-relative) mode of addressing permits any memory location within the 65,536 word-address-space to be referenced. The disp field, as in PC-relative addressing, is interpreted as a signed value ranging from -128 through 127. The memory address is formed by adding disp to the contents of either Accumulator AC2 (when xr = 10) or Accumulator AC3 (when xr = 11). Table 3 presents a summary of the direct addressing modes.

**TABLE 3. Summary of Direct Addressing Modes**

| xr<br>FIELD | ADDRESSING MODE          | EFFECTIVE<br>ADDRESS |

|-------------|--------------------------|----------------------|

| 00          | Base-Page                | EA = disp            |

| 01          | Program-Counter-Relative | EA = disp + (PC)     |

| 10          | AC2-Relative (indexed)   | EA = disp + (AC2)    |

| 11          | AC3-Relative (indexed)   | EA = disp + (AC3)    |

|             |                          |                      |

Note 1: For base-page addressing, disp is positive and in range of 000 to 255 when BPS is low (0); or disp is signed number in range of -128 to +127 when BPS is high (1).

Note 2: PC contains value one greater than address of current instruction.

Note 3: For relative addressing, display range is -128 to +127.

Indirect addressing consists of first establishing an address in the same manner as direct addressing (by either the base-page, PC-relative, or indexed mode). The contents of the memory location at the selected address then are used as the operand address.

NOTE: As explained in Chapter 2 of the PACE Users Manual, the memory addressing modes also are used for peripheral I/O operations. Address space must be divided between memory and I/O devices. Chapter 10 of that manual discusses addressing relevant to assembly language programming, and Chapter 7 discusses the address assignments used in the PACE Microprocessor Development System.

A summary of the 45 PACE instructions is provided in Table 4, which shows the instruction mnemonic, meaning, a symbolic representation of the instruction, the assembler format, and the instruction format. Table 5 defines the notation and symbols used in Table 4 and the remainder of this chapter. The notations are presented in alphabetical order and, then, the symbols are listed. Upper-case mnemonics refer to fields in the instruction word. Lower-case mnemonics refer to the numerical value of the corresponding fields. In cases where both upper- and lower-case mnemonics are composed of the same letters, only the lower-case mnemonic is given. The use of lower-case notation designates variables.

**TABLE 4. PACE Instruction Summary**

|    | Mnemonic                                         | Meaning                                                                                                                                                                                                                    | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Assemi                                        | bler Format                                                              | Instruction Format                                                                                                                                                                         |

|----|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | Branch Instr                                     | uctions                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               |                                                                          |                                                                                                                                                                                            |

|    | BOC<br>JMP<br>JMP@<br>JSR<br>JSR@<br>RTS<br>RTI  | Branch On Condition Jump Jump Indirect Jump To Subroutine Jump To Subroutine Indirect Return from Subroutine Return from Interrupt                                                                                         | (PC) ← (PC) + disp if cc true<br>(PC) ← EA<br>(PC) ← (EA)<br>(STK) ← (PC), (PC) ← EA<br>(STK) ← (PC), (PC) ← (EA)<br>(PC) ← (STK) + disp<br>(PC) ← (STK) + disp, IEN = 1                                                                                                                                                                                                                                                                                                                                                         | BOC<br>JMP<br>JMP<br>JSR<br>JSR<br>RTS<br>RTI | cc,disp disp (xr) @disp (xr) disp (xr) @disp (xr) disp (xr) disp disp    | 0 1 0 0                                                                                                                                                                                    |

| 2. | Skip Instruct                                    | tions                                                                                                                                                                                                                      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |                                                                          |                                                                                                                                                                                            |

|    | SKNE<br>SKG<br>SKAZ<br>ISZ<br>DSZ<br>AISZ        | Skip if Not Equal Skip if Greater Skip if And is Zero Increment and Skip if Zero Decrement and Skip if Zero Add Immediate, Skip if Zero                                                                                    | If $(ACr) \neq (EA)$ , $(PC) \leftarrow (PC) + 1$<br>If $(AC0) > (EA)$ , $(PC) \leftarrow (PC) + 1$<br>If $((AC0) \land (EA)) = 0$ , $(PC) \leftarrow (PC) + 1$<br>$(EA) \leftarrow (EA) + 1$ , if $(EA) = 0$ , $(PC) \leftarrow (PC) + 1$<br>$(EA) \leftarrow (EA) - 1$ , if $(EA) = 0$ , $(PC) \leftarrow (PC) + 1$<br>$(ACr) \leftarrow (ACr) + disp$ , if $(ACr) = 0$ , $(PC) \leftarrow (PC) + 1$                                                                                                                           | SKNE<br>SKG<br>SKAZ<br>ISZ<br>DSZ<br>AISZ     | r,disp (xr) 0,disp (xr) 0,disp (xr) disp (xr) disp (xr) disp (xr) r,disp | 1 1 1 1 r xr disp<br>1 0 0 1 1 1<br>1 0 1 1 1 0<br>1 0 0 0 1 1<br>1 0 1 0 1 1<br>0 1 1 1 1 0 r                                                                                             |

| 3. | Memory Data                                      | a Transfer Instructions                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               | 1,44,44                                                                  |                                                                                                                                                                                            |

|    | LD<br>LD@<br>ST<br>ST@<br>LSEX                   | Load Indirect<br>Store<br>Store Indirect<br>Load With Sign Extended                                                                                                                                                        | (ACr) ← (EA)<br>(AC0) ← ((EA))<br>(EA) ← (ACr)<br>((EA)) ← (AC0)<br>(AC0) ← (EA) bit 7 extended                                                                                                                                                                                                                                                                                                                                                                                                                                  | LD<br>LD<br>ST<br>ST<br>LSEX                  | r,disp (xr) 0,@disp (xr) r,disp (xr) 0,@disp (xr) 0,disp (xr)            | 1 1 0 0 r xr disp<br>1 0 1 0 0 0<br>1 1 0 1 r<br>1 0 1 1 0 0<br>1 1 0 1 1 1 1                                                                                                              |

| 4. | Memory Data                                      | a Operate Instructions                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               |                                                                          |                                                                                                                                                                                            |

|    | AND<br>OR<br>ADD<br>SUBB<br>DECA                 | And<br>Or<br>Add<br>Subtract with Borrow<br>Decimal Add                                                                                                                                                                    | $(AC0) \leftarrow (AC0) \land (EA)$<br>$(AC0) \leftarrow (AC0) \lor (EA)$<br>$(ACr) \leftarrow (ACr) + (EA), OV, CY$<br>$(AC0) \leftarrow (AC0) + \sim (EA) + (CY), OV, CY$<br>$(AC0) \leftarrow (AC0) + \sim (EA) + \sim (CY), OV, CY$                                                                                                                                                                                                                                                                                          | AND<br>OR<br>ADD<br>SUBB<br>DECA              | 0,disp (xr) 0,disp (xr) r,disp (xr) 0,disp (xr) 0,disp (xr)              | 1 0 1 0 1 0 xr disp 1 0 1 0 0 1 1 1 1 0 r 1 0 0 1 0 0 1 0 0 1 0                                                                                                                            |

| 5. | Register Data                                    | Transfer Instructions                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               |                                                                          |                                                                                                                                                                                            |

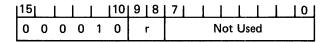

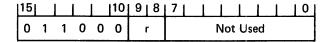

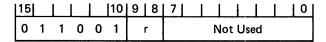

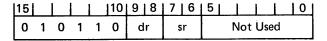

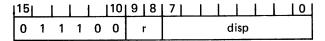

|    | LI RCPY RXCH XCHRS CFR CRF PUSH PULL PUSHF PULLF | Load Immediate Register Copy Register Exchange Exchange Register and Stack Copy Flags Into Register Copy Register Into Flags Push Register Onto Stack Pull Stack Into Register Push Flags Onto Stack Pull Stack Into Flags | $ \begin{array}{ll} (ACr) \; \leftarrow \; disp \\ (ACdr) \; \leftarrow \; (ACsr) \\ (ACdr) \; \leftarrow \; (ACsr), \; (ACsr) \; \leftarrow \; (ACdr) \\ (STK) \; \leftarrow \; (ACr), \; (ACr) \; \leftarrow \; (STK) \\ (ACr) \; \leftarrow \; (FR) \\ (FR) \; \leftarrow \; (ACr) \\ (STK) \; \leftarrow \; (ACr) \\ (ACr) \; \leftarrow \; (STK) \\ (STK) \; \leftarrow \; (STK) \\ (FR) \; \leftarrow \; (STK) \\ (FR) \; \leftarrow \; (FR) \\ (FR) \; \leftarrow \; (FR) \\ (FR) \; \leftarrow \; (STK) \\ \end{array} $ | LI RCPY RXCH XCHRS CFR CRF PUSH PULL PUSHF    | r,disp<br>sr,dr<br>sr,dr<br>r<br>r<br>r<br>r                             | 0 1 0 1 0 0 r disp<br>0 1 0 1 1 1 dr sr not used<br>0 1 1 0 1 1 r not used<br>0 0 0 0 1 1 r not used<br>0 0 0 0 0 1<br>0 1 0 0 0 0 0<br>0 1 1 0 0 0<br>0 1 1 0 0 0<br>0 1 1 0 0 1 not used |

| c  |                                                  | <u>-</u>                                                                                                                                                                                                                   | (117)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PULLP                                         |                                                                          | 0 0 0 1 0 0                                                                                                                                                                                |

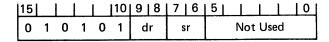

|    | RADD<br>RADC<br>RAND<br>RXOR<br>CAI              | Operate Instructions Register Add Register Add With Carry Register And Register Exclusive OR Complement and Add Immediate                                                                                                  | $(ACdr) \leftarrow (ACdr) + (ACsr), OV, CY$<br>$(ACdr) \leftarrow (ACdr) + (ACsr) + (CY), OV, CY$<br>$(ACdr) \leftarrow (ACdr) \wedge (ACsr).$<br>$(ACdr) \leftarrow (ACdr) \wedge (ACsr)$<br>$(ACdr) \leftarrow (ACdr) \wedge (ACsr)$                                                                                                                                                                                                                                                                                           | RADD<br>RADC<br>RAND<br>RXOR<br>CAI           | sr,dr<br>sr,dr<br>sr,dr<br>sr,dr<br>r,disp                               | 0 1 1 0 1 0 dr sr not used 0 1 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1                                                                                                                     |

| 7. | Shift And Ro                                     | tate Instructions                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               |                                                                          |                                                                                                                                                                                            |

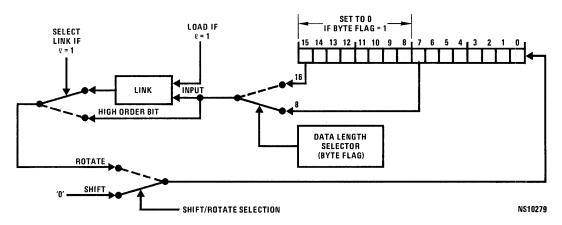

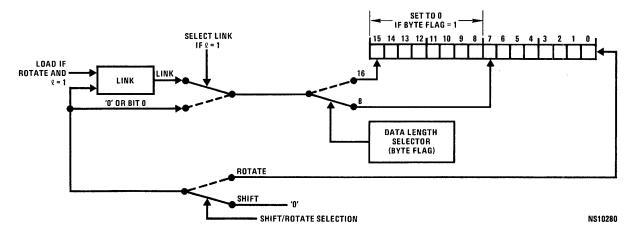

|    | SHL<br>SHR<br>ROL<br>ROR                         | Shift Left<br>Shift Right<br>Rotate Left<br>Rotate Right                                                                                                                                                                   | (ACr) ← (ACr) shifted left n places, w/wo link (ACr) ← (ACr) shifted right n places, w/wo link (ACr) ← (ACr) rotated left n places, w/wo link (ACr) ← (ACr) rotated right n places, w/wo link                                                                                                                                                                                                                                                                                                                                    | SHL<br>SHR<br>ROL<br>ROR                      | r,n,l<br>r,n,l<br>r,n,l<br>r,n,l                                         | 0 0 1 0 1 0 r n R<br>0 0 1 0 1 1<br>0 0 1 0 0 0<br>0 0 1 0 0 1                                                                                                                             |

| 8. | Miscellaneous                                    |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               |                                                                          |                                                                                                                                                                                            |

|    | HALT<br>SFLG<br>PFLG                             | Halt<br>Set Flag<br>Pulse Flag                                                                                                                                                                                             | Halt $(FR)_{fc} \leftarrow 1$ $(FR)_{fc} \leftarrow 1$ , $(FR)_{fc} \leftarrow 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                | HALT<br>SFLG<br>PFLG                          | fc<br>fc                                                                 | 0 0 0 0 0 0 0 not used 0 0 1 1 fc 1 not used 0 0 1 1 fc 0                                                                                                                                  |

TABLE 5. Notations/Symbols Used in Instruction Descriptions

| NOTATION/<br>SYMBOL | MEANING                                                                                                                                                                                                                                                                  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACr                 | Denotes specific working register (AC0, AC1, AC2, or AC3), where r is number of accumulator referenced in instruction.                                                                                                                                                   |

| СС                  | Denotes 4-bit condition code value for conditional branch instructions.                                                                                                                                                                                                  |

| CRY                 | Indicates Carry Flag is set if carry exists due to instruction (either addition or subtraction) or reset if no carry exists.                                                                                                                                             |

| disp                | Stands for displacement value and represents operand in nonmemory-reference instruction or address field in memory-reference instruction. Disp is 8-bit, signed twos-complement number except when base page is referenced; in latter case, disp is unsigned if BPS = 0. |

| dr                  | Denotes number of destination working register specified in instruction-word field. Working register is ACO, AC1, AC2, or AC3.                                                                                                                                           |

| EA                  | Denotes effective address specified by instructions directly, indirectly, or by indexing. Effective address contents are used during execution of instruction. See Table 3.                                                                                              |

| fc                  | Denotes number of referenced flag.                                                                                                                                                                                                                                       |

|                     | NOTE                                                                                                                                                                                                                                                                     |

|                     | Refer to Chapter 2, PACE Users Manual, for flag assignments.                                                                                                                                                                                                             |

| FR                  | Denotes Status Flag Register.                                                                                                                                                                                                                                            |

| IEN                 | Denotes Interrupt Enable Flag.                                                                                                                                                                                                                                           |

| Q                   | Denotes inclusion of 1-bit Link (LINK) Flag in shift operations.                                                                                                                                                                                                         |

| n                   | Unsigned number indicating number of bit positions to be shifted in shift and rotate instructions.                                                                                                                                                                       |

| OVF                 | Indicates Overflow Flag is set if overflow exists due to instruction (either addition or subtraction) or is reset if no overflow exists. Overflow occurs if signs of operands are alike and sign of result is different from operands.                                   |

| PC                  | Denotes Program Counter. During address formation, PC is incremented by 1 to contain address 1 greater than that of instruction being executed.                                                                                                                          |

| r                   | Denotes number of working register specified in instruction-word field. Working register is AC0, AC1, AC2, or AC3.                                                                                                                                                       |

| STK                 | Denotes top word of 10-word last-in/first-out stack.                                                                                                                                                                                                                     |

| sr                  | Denotes number of source working register specified in instruction-word field. Working register is AC0, AC1, AC2, or AC3.                                                                                                                                                |

| xr                  | When not zero, xr value designates number of register to be used in indexed and relative memory addressing modes. When zero, base-page addressing is indicated. See Table 3.                                                                                             |

| ()                  | Denotes contents of item within parentheses. (ACr) is read as 'contents of ACr'. (EA) is read as 'contents of EA'.                                                                                                                                                       |

| [ ]                 | Denotes 'result of'.                                                                                                                                                                                                                                                     |

| ~                   | Indicates logical complement (ones complement) of value on right-hand side of $\sim$ .                                                                                                                                                                                   |

| $\rightarrow$       | Means 'replaces'.                                                                                                                                                                                                                                                        |

| <b>←</b>            | Means 'is replaced by'.                                                                                                                                                                                                                                                  |

| @                   | Appearing in operand field of instruction, denotes indirect addressing.                                                                                                                                                                                                  |

| <sup>+</sup> 10     | Modulo 10 addition.                                                                                                                                                                                                                                                      |

| $\wedge$            | Denotes AND operation.                                                                                                                                                                                                                                                   |

| <b>V</b>            | Denotes OR operation.                                                                                                                                                                                                                                                    |

| $\forall$           | Denotes EXCLUSIVE-OR operation.                                                                                                                                                                                                                                          |

The **BRANCH INSTRUCTIONS** group consists of the seven following instructions: BOC, JMP, JMP@, JSR, JSR@, RTI, and RTS.

NOTE: JMP@ and JSR@ are specified to the Assembler as JMP and JSR with indirection specified by the address field.

Six of the seven instructions (excepting BOC) address memory and peripheral devices, and each is described as follows:

- Name of instruction followed by mnemonic in parentheses

- Binary instruction format

- Operation in equation notation

- Assembly language instruction format (see "Assembler" chapter, PACE Users Manual, for further information)

- Description of operation

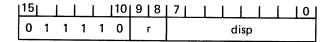

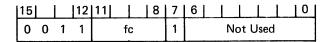

#### **BRANCH ON CONDITION (BOC)**

| - 1 | 15 |   | <u> </u> | 12 | 111 | $\perp$ | [8] | 7 | <u></u> | <u> </u> | L | 1    | 1 | 1 | ] 0 | 1 |

|-----|----|---|----------|----|-----|---------|-----|---|---------|----------|---|------|---|---|-----|---|

|     | 0  | 1 | 0        | 0  |     | cc      |     |   |         |          | C | disp | ) |   |     |   |

**Operation:** (PC)  $\leftarrow$  (PC) + disp (sign extended) if condition is true.

Format: BOC cc, disp

Description: There are 16 possible condition codes (cc). The condition codes are listed in Table 6. If the condition for branching designated by cc is true, the value of disp (sign extended from bit 7 through bit 15) is added to PC and the sum is stored in PC.

NOTE: PC addresses the location following the BOC when the addition occurs (that is, the branch is relative to the next instruction after BOC).

The initial contents of PC are lost. Program control is transferred to the location specified by the contents of the new PC.

**TABLE 6. Branch Conditions**

| CONDITION CODE (cc) | MNEMONIC | CONDITION                        |

|---------------------|----------|----------------------------------|

| 0000                | STFL     | Stack full.                      |

| 0001                | REQ0     | (ACO) equal to zero (1).         |

| 0010                | PSIGN    | (ACO) has positive sign (2).     |

| 0011                | віто     | Bit 0 of AC0 true.               |

| 0100                | BIT1     | Bit 1 of AC0 true.               |

| 0101                | NREQ0    | (ACO) is nonzero (1).            |

| 0110                | BIT2     | Bit 2 of AC0 is true.            |

| 0111                | CONTIN   | CONTIN (continue) input is true. |

| 1000                | LINK     | LINK is true.                    |

| 1001                | IEN      | IEN is true.                     |

| 1010                | CARRY    | CARRY is true.                   |

| 1011                | NSIGN    | (ACO) has negative sign (2).     |

| 1100                | OVF      | OVF is true.                     |

| 1101                | JC13     | JC13 input is true (3).          |

| 1110                | JC14     | JC14 input is true.              |

| 1111                | JC15     | JC15 input is true.              |

Note 1: If selected data length is 8 bits, only bits 0 through 7 of ACO are tested.

Note 2: Bit 7 is sign bit (instead of bit 15) if selected data length is 8 bits.

Note 3: JC13 is used by PACE Microprocessor Development System and is not accessible during prototyping.

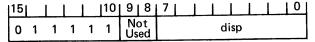

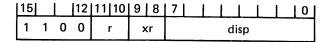

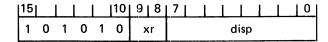

#### JUMP (JMP)

| ١ | 15 |   |   |   | <u></u> | 10 | 9   | 8  | 7 | $\perp$ |      | $\perp$ | L | 10 |

|---|----|---|---|---|---------|----|-----|----|---|---------|------|---------|---|----|

|   | 0  | 0 | 0 | 1 | 1       | 0  | ۰ ا | ۲r |   |         | disp |         |   |    |

Operation: (PC) ← EA

Format: JMP disp (xr)

**Description:** The effective address EA replaces the contents of PC. The next instruction is fetched from the location designated by the new contents of PC.

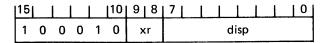

#### JUMP INDIRECT (JMP@)

| 15 |   |   |   | L | 10 | 9 | 8 | 7 |  |    | L., | <br><u> </u> | 0 |

|----|---|---|---|---|----|---|---|---|--|----|-----|--------------|---|

| 1  | 0 | 0 | 1 | 1 | 0  | × | r |   |  | di | sp  |              |   |

Operation:  $(PC) \leftarrow (EA)$

Format: JMP@ @disp (xr)

**Description:** The contents of the effective address replace the contents of PC. The next instruction is fetched from the location designated by the new contents of PC.

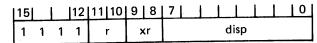

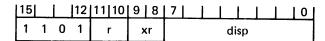

#### JUMP TO SUBROUTINE (JSR)

| 15 |   |   | L |   | 10 | 9   8 | 7 | 丄 | L | 1    |   | <br>10 |

|----|---|---|---|---|----|-------|---|---|---|------|---|--------|

| 0  | 0 | 0 | 1 | 0 | 1  | xr    |   |   |   | disp | ) |        |

Operation: (STK)  $\leftarrow$  (PC), (PC)  $\leftarrow$  EA

Format: JSR disp (xr)

**Description:** The contents of PC are stored in the top of the stack. The effective address replaces the contents of PC. The next instruction is fetched from the location designated by the new contents of PC.

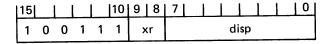

### JUMP TO SUBROUTINE INDIRECT (JSR@)

| ı | 15 |   | L | L |   | 10 | 9 | 8  | 7 | L | L |      | $\perp$ | <br> | L | 0 |

|---|----|---|---|---|---|----|---|----|---|---|---|------|---------|------|---|---|

|   | 1  | 0 | 0 | 1 | 0 | 1  | , | Ċr |   |   |   | disp | )       |      |   |   |

Operation:  $(STK) \leftarrow (PC), (PC) \leftarrow (EA)$

Format: JSR @disp (xr)

**Description:** The contents of PC are stored in the top of the stack. The contents of the effective address replace the contents of PC. The next instruction is fetched from the location designated by the new contents of PC.

#### RETURN FROM SUBROUTINE (RTS)

Operation: (PC) ← (STK) + disp (sign extended)

Format: RTS disp

**Description:** The contents of PC are replaced by disp added to the contents pulled from the top of the stack. Program control is transferred to the location specified by the new contents of PC.

**NOTE:** RTS is used primarily to return from subroutines entered by JSR.

#### **RETURN FROM INTERRUPT (RTI)**

Operation: (PC)

(STK) + disp (sign extended), IEN = 1

Format: RTI disp

**Description:** The Interrupt Enable Flag (IEN) is set. The contents of PC are replaced by disp added to the contents pulled from the top of the stack. Program control is transferred to the location specified by the new contents of PC.

NOTE: RTI is used primarily to exit from an interrupt routine.

Six **SKIP INSTRUCTIONS** are provided: SKNE, SKG, SKAZ, AISZ, ISZ, and DSZ.

#### SKIP IF NOT EQUAL (SKNE)

Operation: If  $(ACr) \neq (EA)$ ,  $(PC) \leftarrow (PC) + 1$

Format: SKNE r, disp (xr)

Description: The contents of ACr and the contents of the effective memory location EA are compared. If the contents of ACr and the effective memory location EA are not equal, the next instruction in sequence is skipped. The contents of ACr and EA are unaltered. If an 8-bit data length is selected, only the lower 8 bits are compared.

#### SKIP IF GREATER (SKG)

Operation: If (ACO) > (EA),  $(PC) \leftarrow (PC) + 1$

Format: SKG 0, disp (xr)

Description: The contents of ACO and the contents of the effective memory location EA are compared as signed numbers. If the contents of ACO are greater (more positive) than the contents of EA, the next instruction in sequence is skipped. The contents of ACO and EA are unaltered.

NOTE: The comparison is performed by subtraction. If an 8-bit data length is selected, only the lower 8 bits are compared.

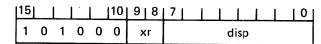

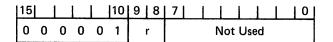

#### SKIP IF AND IS ZERO (SKAZ)

| 15 |   | <u> </u> |   |   | 10 | 9 | 8  | 7 | L |     |   | [0] |

|----|---|----------|---|---|----|---|----|---|---|-----|---|-----|

| 1  | 0 | 1        | 1 | 1 | 0  | > | (r |   |   | dis | ) |     |

Operation: If  $[(AC0) \land (EA)] = 0$ ,  $(PC) \leftarrow (PC) + 1$

Format: SKAZ 0, disp (xr)

**Description:** The contents of AC0 and the contents of the effective memory location EA are ANDed. If the result equals zero, the next instruction in sequence is skipped. The contents of AC0 and EA are unaltered. If an 8-bit data length is selected, only the lower 8 bits are tested.

#### **INCREMENT AND SKIP IF ZERO (ISZ)**

| 15 |   | <u> </u> |   | L | 10 | 9 | 8 | 7 | Ĺ | L |          |   | ] 0 | 1 |

|----|---|----------|---|---|----|---|---|---|---|---|----------|---|-----|---|

| 1  | 0 | 0        | 0 | 1 | 1  | × | r |   |   |   | <br>disp | ) |     | 1 |

Operation: (EA)  $\leftarrow$  (EA) +1; if (EA) = 0, (PC)  $\leftarrow$  (PC) + 1

Format: ISZ disp (xr)

**Description:** The contents of EA are incremented by one. If the new contents of EA equal zero, the next instruction in sequence is skipped. If an 8-bit data length is selected, only the lower 8 bits are tested.

#### **DECREMENT AND SKIP IF ZERO (DSZ)**

| 1 | 15 |   |   |   |   | 10 | 9 | 8 | 7 | L |  |      |   | 1 | ı | 0 |

|---|----|---|---|---|---|----|---|---|---|---|--|------|---|---|---|---|

|   | 1  | 0 | 1 | 0 | 1 | 1  | × | r |   |   |  | disp | ) |   |   |   |

Operation: (EA)  $\leftarrow$  (EA) -1; if (EA) = 0, (PC)  $\leftarrow$  (PC) +1

Format: DSZ disp (xr)

Description: The contents of EA are decremented by one. If the new contents of EA equal zero, the next instruction in sequence is skipped. If an 8-bit data length is selected, only the lower 8 bits are tested.

#### ADD IMMEDIATE, SKIP IF ZERO (AISZ)

**Operation:** (ACr)  $\leftarrow$  (ACr) + disp (sign extended). If new (ACr) = 0, (PC)  $\leftarrow$  (PC) + 1

Format: AISZ r, disp

rormat: AISZ r,disp

Description: The contents of Register ACr are replaced by the sum of the contents of ACr and disp (sign bit 7 extended through bit 15). The initial contents of ACr are lost. If the new contents of ACr equal zero, the contents of PC are incremented by one, thus skipping the next instruction. The AISZ Instruction always tests the full 16-bit result independent of the data length selected.

NOTE: Testing the 16-bit result in conjunction with no change to the status indicators allows AISZ to be conveniently used for modifying 16-bit index values while working with 8-bit data.

The five MEMORY DATA-TRANSFER INSTRUCTIONS (LD, LD@, ST, ST@, and LSEX) effect data transfers between the registers and memory or peripheral devices.

#### LOAD (LD)

Operation:  $(ACr) \leftarrow (EA)$

Format: LD r, disp (xr)

**Description:** The contents of ACr are replaced by the contents of EA. The initial contents of ACr are lost; the contents of EA are unaltered.

#### LOAD INDIRECT (LD@)

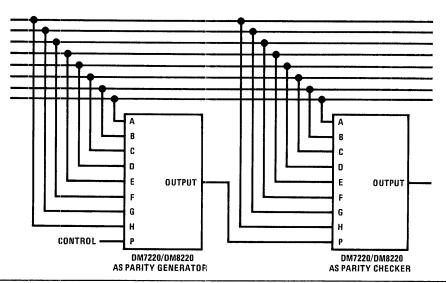

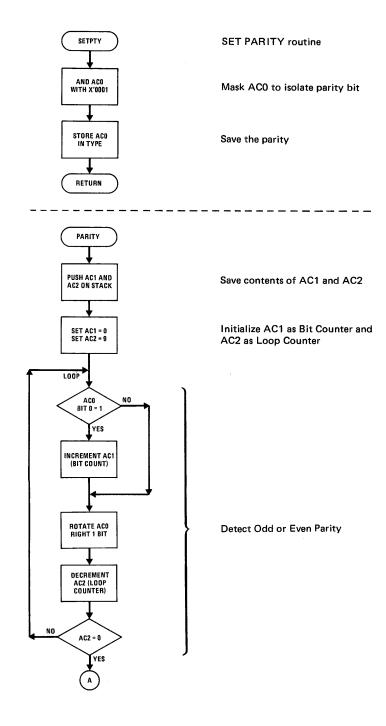

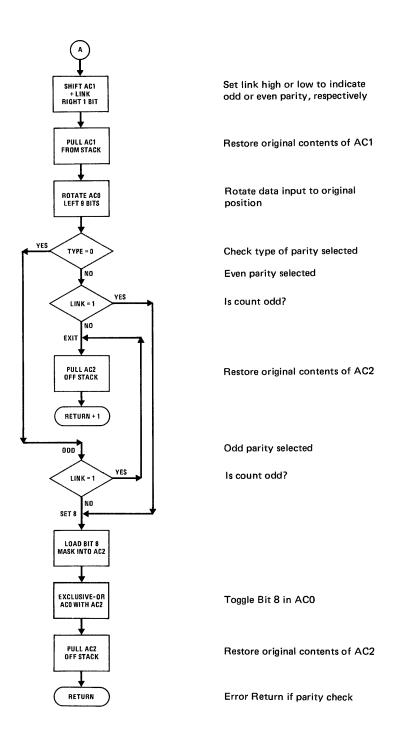

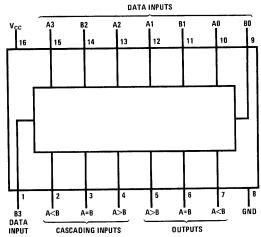

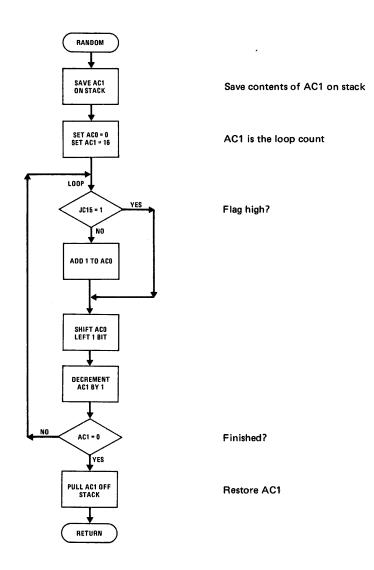

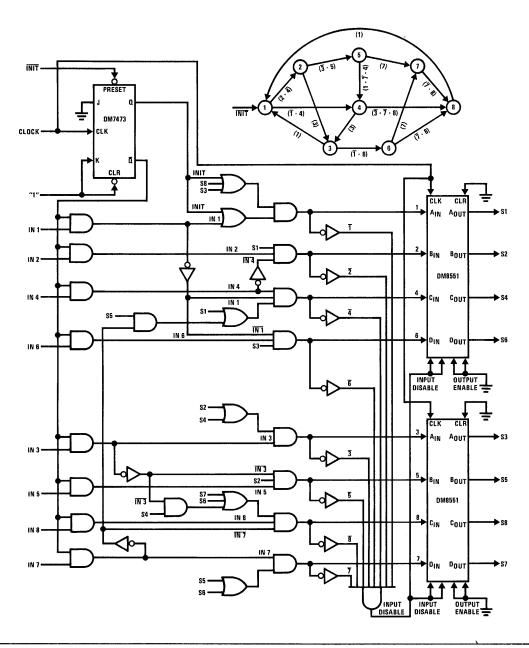

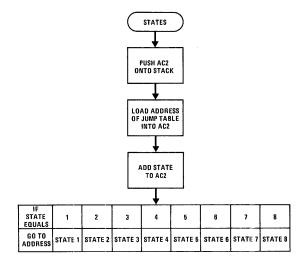

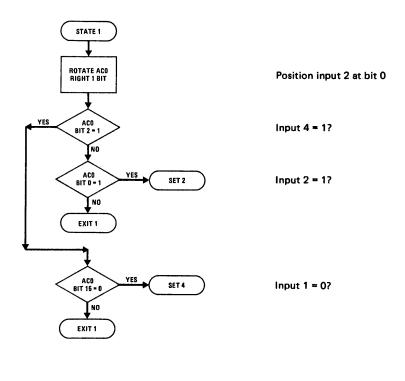

Operation:  $(AC0) \leftarrow ((EA))$