National Semiconductor

Publication Number 420305292-001A Order Number IPC-16A/928 March 1977 \$5.00

PACE Processing And Control Element

Microprocessor System Design Manual

© National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

#### **PREFACE**

The PACE System Design Manual serves as a source of basic design information. Included are descriptions of the PACE Microprocessor: its architecture, operational characteristics, instruction set, basic requirements for designing PACE-based systems, and both memory and peripheral interfacing techniques. The material has been presented in such a way as to provide design criteria not only for PACE but also to provide other pertinent design information that interrelates PACE to various other support and interfacing devices.

The material within this publication is up-to-date at the time of publication but is subject to change without notice.

Copies of this publication and other National Semiconductor publications may be obtained from the National Semiconductor sales office or distributor serving your locality.

Other PACE publications that may be of interest are listed below:

- PACE Logic Designers Guide to Programmed Equivalents to TTL Functions, Order Number IPC-16A/927. Explains how standard TTL/MSI functions may be implemented by software using the PACE Microprocessor.

- PACE Assembly Language Programming Manual, Order Number IPC-16S/969Y. Provides tutorial and reference information required for writing user application programs. Includes detailed descriptions of the assembly language, source statements, programming techniques, and assembly input/output formats.

- PACE Development System Users Manual, Order Number IPC-16P/108Y. Comprises comprehensive descriptions of the PACE Development System, including both operational and functional information.

- IPC-16A/520D MOS/LSI Single-Chip 16-Bit Microprocessor (PACE) Data Sheet. Provides parametric specifications of PACE. (Also includes some of the functional data provided in this manual.)

- PACE Microprocessor Disc Operating System (DOS) Users Manual, Order Number IPC-16P/840Y. Comprises PACE DOS operational procedures for both equipment and software.

- PACE Microprocessor Low Cost Development System Users Manual, Order Number IPC-16P/301Y. Provides installation, operational, and interfacing information.

- National Semiconductor Memory Data Book.

Various other National Semiconductor publications pertaining to PACE-based products are or will be available. Contact our local sales office or distributor for information.

## TABLE OF CONTENTS

| Chapter |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page                                          |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 1       | AN INTRODUCTION TO PACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |

|         | 1.0 INTRODUCTION 1.1 THE PACE MICROPROCESSOR 1.2 PACE DESIGN SUPPORT 1.3 PACE SUPPORT CHIPS 1.4 DEVELOPMENT SYSTEMS 1.5 PACE SUPPORT SOFTWARE 1.6 SUPPORT SERVICES AND PERSONNEL                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-1<br>1-3<br>1-4<br>1-4<br>1-6               |

| 2       | PACE MICROPROCESSOR DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |

|         | 2.1 GENERAL DESCRIPTION 2.1.1 PACE Architecture 2.1.2 PACE Interface Signal Descriptions 2.2 PACE TIMING REQUIREMENTS 2.3 INITIALIZATION 2.4 DATA INPUT/OUTPUT OPERATIONS 2.4.1 Data Input Operations 2.4.2 Data Output Operations 2.4.3 Use of EXTEND Signal 2.5 STATUS AND CONTROL FLAGS 2.6 JUMP CONDITIONS 2.7 INTERRUPT SYSTEM 2.7.1 User-Specified Interrupts 2.7.2 Stack Interrupts 2.8 NHALT AND CONTIN SIGNALS 2.8.1 Programmed Halt 2.8.2 Processor Stall 2.8.3 Level-0 Interrupts 2.9 PACE INSTRUCTION SET 2.9.1 Data Representation 2.9.2 Addressing Modes 2.9.2.1 Direct Addressing 2.9.2.2 Indirect Addressing | 2-1<br>2-1<br>2-3<br>2-3<br>2-6<br>2-6<br>2-6 |

| 3       | DESIGNING PACE SYSTEMS: BASIC REQUIREMENTS AND CONCEPTS  3.0 INTRODUCTION 3.1 SYSTEM TIMING AND POWER 3.1.1 Frequency Control 3.1.2 Nonoverlap Requirements and Control 3.1.3 Substrate Bias Voltage (V <sub>BB</sub> ) Generation 3.2 SYSTEM INITIALIZATION 3.3 BUFFERING SYSTEM BUSES                                                                                                                                                                                                                                                                                                                                      | 3-1<br>3-3<br>3-4<br>3-4<br>3-4<br>3-5        |

|         | 3.4 A BUFFERED PACE CPU MODULE 3.5 SYSTEM BUS STRUCTURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-7<br>3-7                                    |

# **TABLE OF CONTENTS (Continued)**

| Chapter |            |                                                 | Page       |

|---------|------------|-------------------------------------------------|------------|

| 3       | 3.6<br>3.7 | ADDRESS LATCHING                                | 3-9<br>3-9 |

| 4       | MEMO       | DRY INTERFACING                                 |            |

|         | 4.0        | INTRODUCTION                                    | 4-1        |

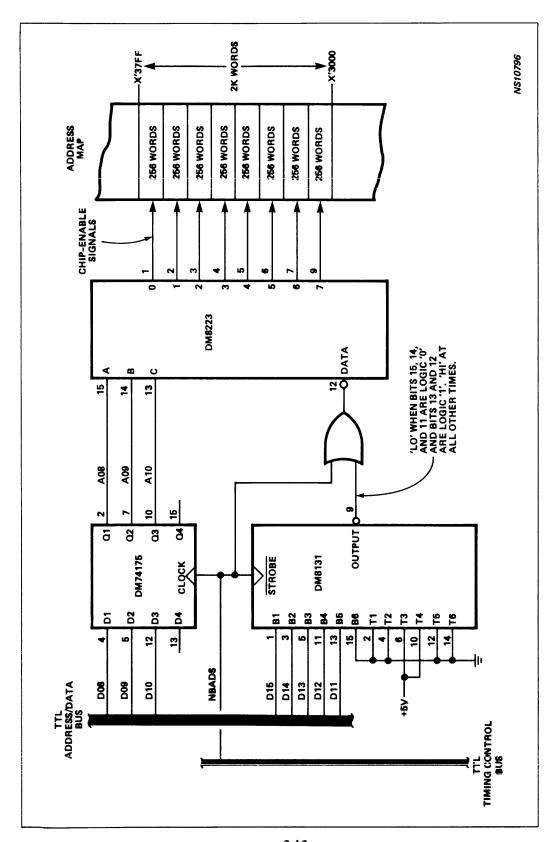

|         | 4.1        | INTERFACING TO MEMORY WITH ON-CHIP LATCHES      | 4-1        |

|         | 4.1.1      | A Typical Interface to RAM with On-Chip Latches | 4-3        |

|         | 4.1.2      | A Typical Interface to ROM with On-Chip Latches | 4-3        |

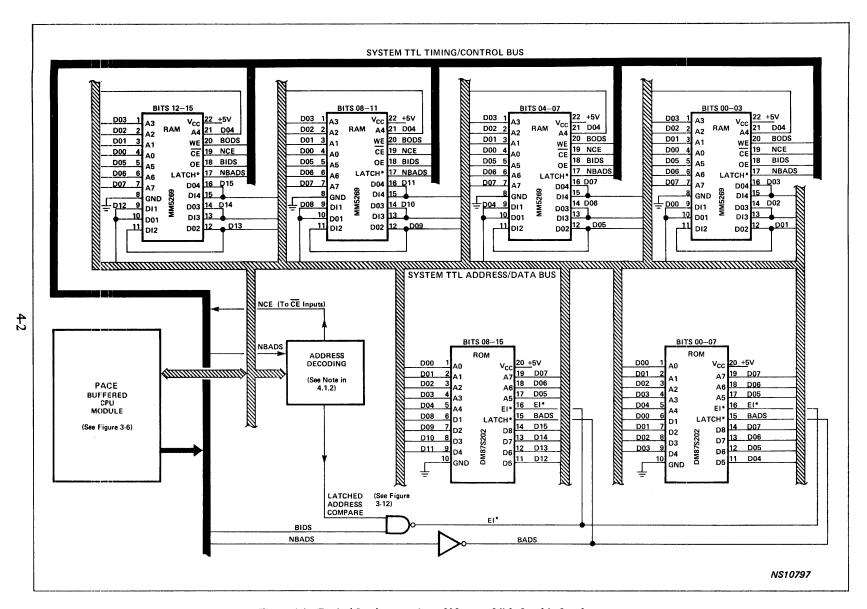

|         | 4.2        | INTERFACING TO MEMORY WITHOUT ON-CHIP LATCHES   | 4-4        |

|         | 4.2.1      | Interfacing to MM2101 RAM                       | 4-6        |

|         | 4.2.2      | Interfacing to MM5214 ROM                       | 4-6        |

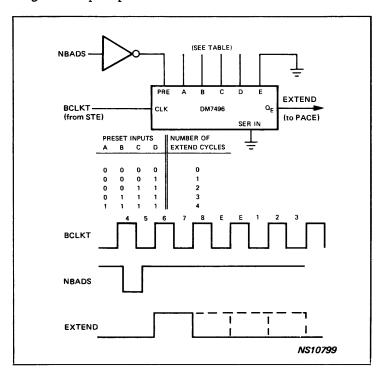

|         | 4.3        | INTERFACING WITH SLOW MEMORIES                  | 4-7        |

| 5       | PERIP      | PHERAL INTERFACING TECHNIQUES                   |            |

|         | 5.0        | INTRODUCTION                                    | 5-1        |

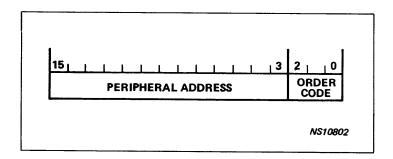

|         | 5.1        | PERIPHERAL INSTRUCTIONS AND ADDRESSING          | 5-1        |

|         | 5.2        | INPUT/OUTPUT PORTS                              | 5-1        |

|         | 5.3        | SPECIAL CONSIDERATIONS WHEN INTERFACING         |            |

|         |            | 8-BIT PERIPHERALS                               | 5-3        |

|         | 5.3.1      | Hardware Considerations                         | 5-3        |

|         | 5.3.2      | Software Considerations                         | 5-5        |

|         | 5.4        | INTERFACING WITH SLOW PERIPHERALS               | 5-6        |

|         | 5.5        | PERIPHERAL CONTROL                              | 5-6        |

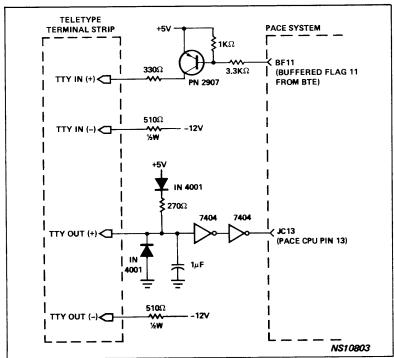

|         | 5.6        | SERIAL INPUT/OUTPUT                             | 5-8        |

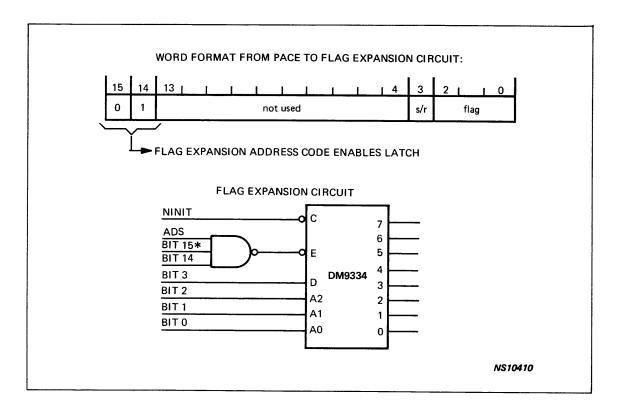

|         | 5.7        | EXPANDING JUMP CONDITIONS AND FLAGS             | 5-9        |

|         | 5.8        | INTERRUPT DRIVEN INPUT/OUTPUT                   | 5-9        |

|         | 5.9        | EXPANDING THE INTERRUPT SYSTEM                  | 5-10       |

| APPENDI | X A PACE   | INSTRUCTION RELATED SUMMARIES                   | A-1        |

|         |            | LIST OF TABLES                                  |            |

| Table   |            | Title                                           | Page       |

| 2-1     | PACE       | Interface Signal Descriptions                   | 2-4        |

| 2-2     | Descri     | iptions of Status and Control Flags             | 2-10       |

| 2-3     | Branc      | h Conditions                                    | 2-11       |

| 2-4     |            | ions of Interrupt Pointers                      | 2-14       |

| 2-5     |            | Instruction Summary                             | 2-19       |

| 2-6     | Summ       | nary of Direct Addressing Modes                 | 2-21       |

| 4-1     | Stand      | ard Memory Devices for Use in PACE Systems      | 4-1        |

| 5-1     |            | ole Order Codes for a Cassette or Tape Drive    | 5-7        |

| A-1     | Notat      | tions/Symbols Used in Instruction Descriptions  | A-2        |

# LIST OF TABLES (Continued)

| Table      | Title                                                                  |              |  |  |  |

|------------|------------------------------------------------------------------------|--------------|--|--|--|

| A-2<br>A-3 | PACE Instruction Summary                                               | A-4<br>A-14  |  |  |  |

|            | ILLUSTRATIONS                                                          |              |  |  |  |

|            | ILLUSTRATIONS                                                          |              |  |  |  |

| Figure     | Title                                                                  | Page         |  |  |  |

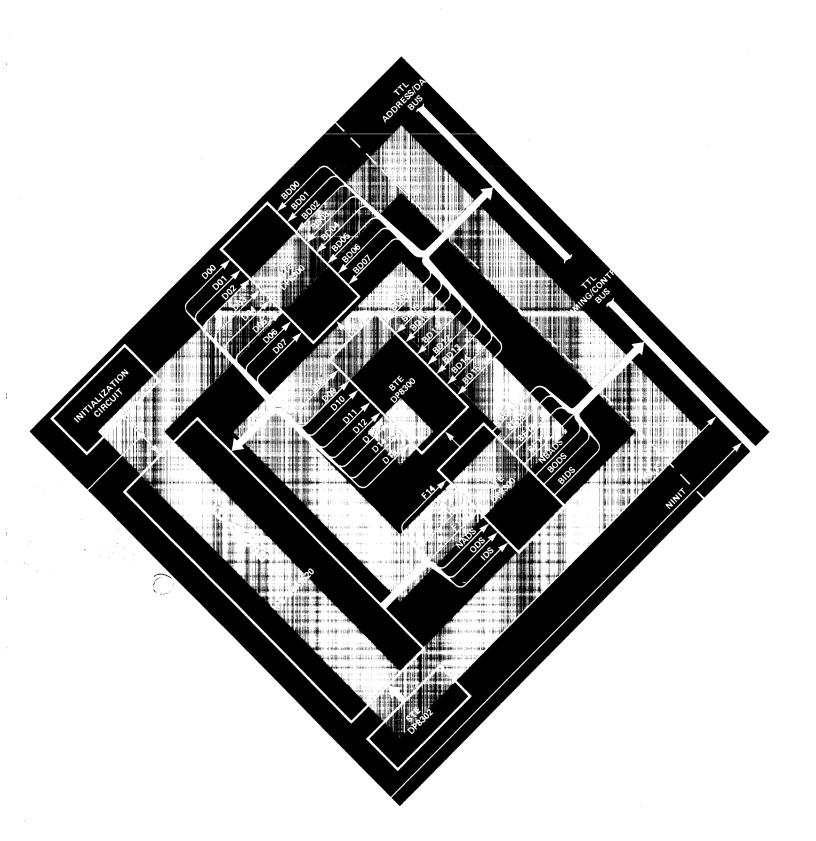

| 1-1        | PACE Resources                                                         | 1-2          |  |  |  |

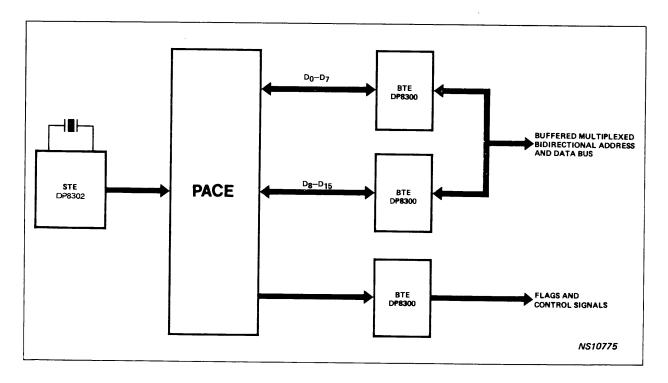

| 1-2        | PACE-STE-BTE Relationship                                              | 1-3          |  |  |  |

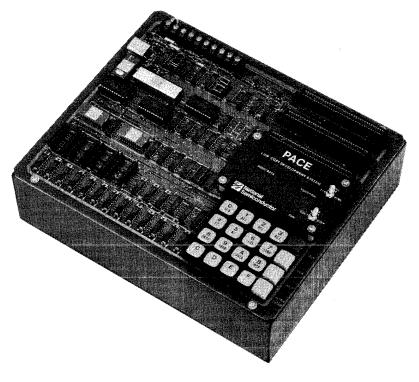

| 1-3        | PACE Low Cost Development System (LCDS)                                | 1-5          |  |  |  |

| 1-4        | PACE Microprocessor Development System (IPC-16P)                       | 1-5          |  |  |  |

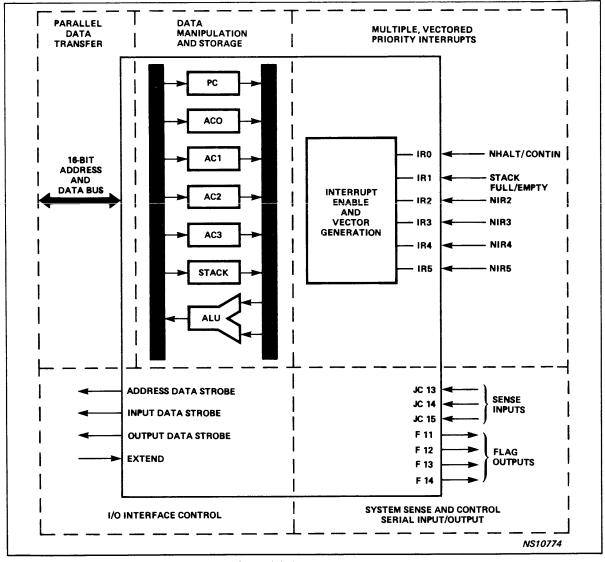

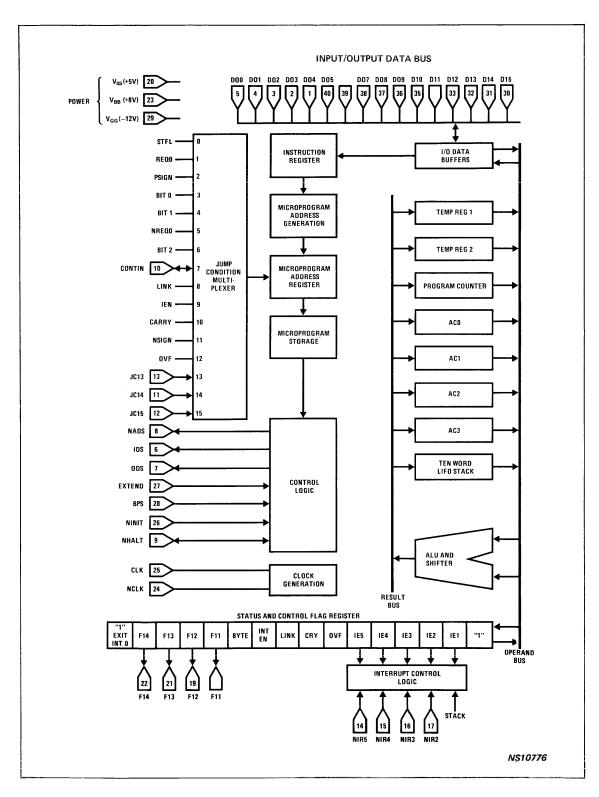

| 2-1        | PACE Detailed Block Diagram                                            | 2-2          |  |  |  |

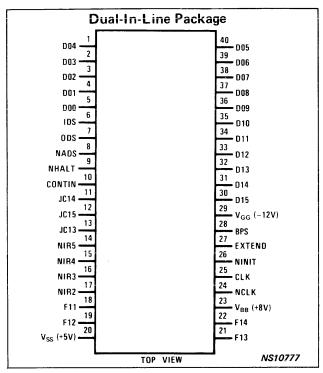

| 2-2        | PACE Pin Assignments                                                   | 2-5          |  |  |  |

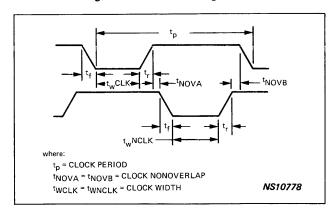

| 2-3        | External Clock Timing                                                  | 2-5          |  |  |  |

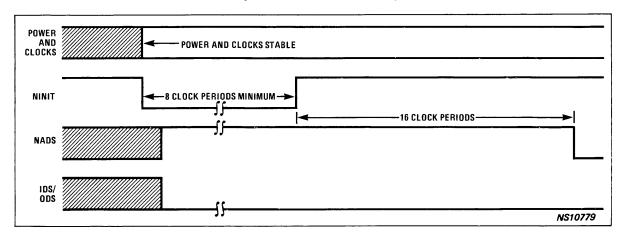

| 2-4        | Initialization Timing                                                  | 2-5          |  |  |  |

| 2-5        | Address Output and Data Input Timing                                   | 2-7          |  |  |  |

| 2-6        | Data Output Timing                                                     | 2-7          |  |  |  |

| 2-7        | Extend I/O Signal Timing                                               | 2-8          |  |  |  |

| 2-8        | Suspend I/O Signal Timing                                              | 2-9          |  |  |  |

| 2-9        | Pulse and Set Flag Timing Diagram                                      | 2-11         |  |  |  |

| 2-10       | PACE Interrupt System                                                  | 2-12         |  |  |  |

| 2-11       | Timing Diagram for Processor Stall Using NHALT and CONTIN Signals      | 2-13         |  |  |  |

| 2-12       | Relative Timing for Level-0 Interrupt Generation                       | 2-14         |  |  |  |

| 2-13       | Circuit to Prevent Conflicts Between Level-0 and In-Process Interrupts | 2-17<br>2-21 |  |  |  |

| 2-14       | Memory-reference Instruction Format                                    | 2-21<br>3-2  |  |  |  |

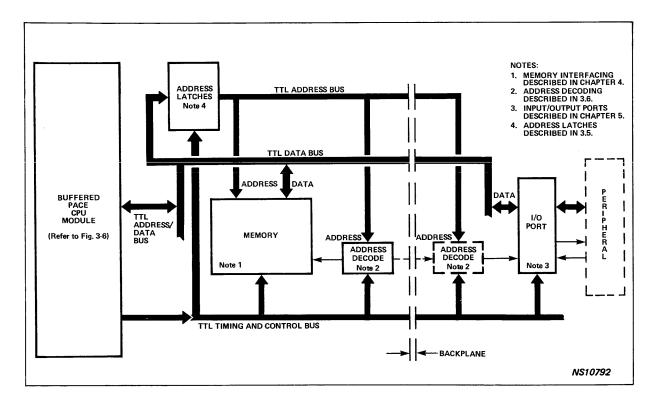

| 3-1        | Example of PACE System Configuration                                   | 3-2<br>3-3   |  |  |  |

| 3-2<br>3-3 | PACE-STE Interconnection and V <sub>BB</sub> Generation                | 3-3<br>3-4   |  |  |  |

| 3-3<br>3-4 | BTE Functional Block Diagram                                           | 3-5          |  |  |  |

| 3-4<br>3-5 | BTE System Implementation                                              | 3-3<br>3-6   |  |  |  |

| 3-3<br>3-6 | Buffered PACE CPU Module                                               | 3-8          |  |  |  |

| 3-0<br>3-7 | Fully Multiplexed Bus Structure                                        | 3-9          |  |  |  |

| 3-7        | Separate Address/Multiplexed Data Bus Structure                        | 3-9          |  |  |  |

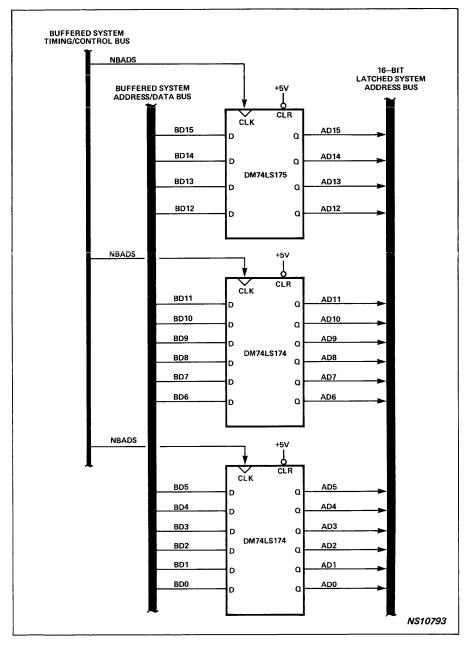

| 3-9        | Latched Address Bus Using Hex/Quad Flip Flops                          | 3-10         |  |  |  |

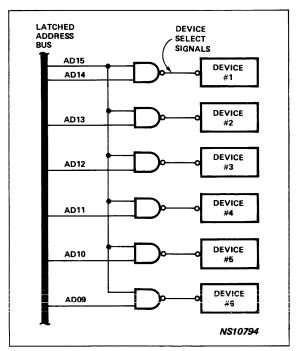

| 3-10       | Using Address Bits as Device Select Signals                            | 3-11         |  |  |  |

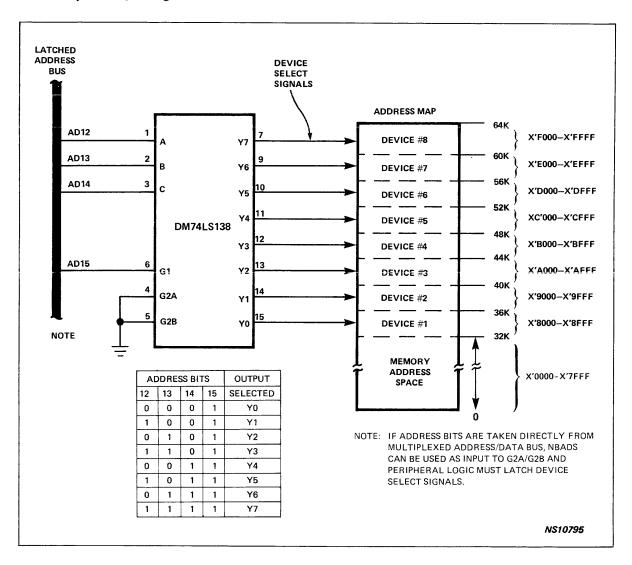

| 3-10       | Using a 3-to-8 Line Decoder to Generate Device Select Signals          | 3-11         |  |  |  |

| 3-11       | Using A Bus Comparator and a Demultiplexer to Enable Memory Devices    | 3-13         |  |  |  |

| 4-1        | Typical Implementation of Memory With On-chip Latches                  | 4-2          |  |  |  |

| 4-2        | Typical Implementation of Memory Without On-chip Latches               | 4-5          |  |  |  |

| 4-3        | Circuit and Timing Diagram for Up to Four Clock Cycle Extend           | 4-6          |  |  |  |

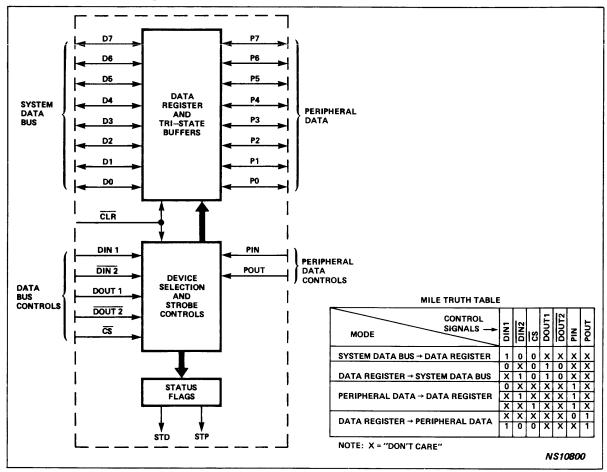

| 5-1        | MILE Block Diagram                                                     | 5-2          |  |  |  |

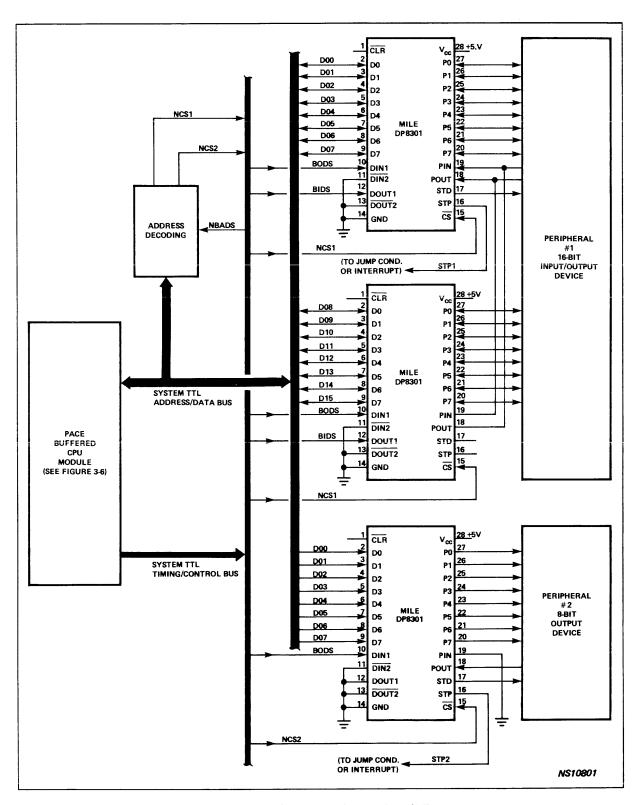

| 5-2        | Typical System Implementation of MILEs                                 | 5-4          |  |  |  |

| 5-3        | Using Address Word for Control                                         | 5-7          |  |  |  |

| 5-4        | PACE/Teletype Interface Circuit                                        | 5-8          |  |  |  |

| 5-5        | One Possible Circuit and Word Format for Obtaining Additional Flags    | 5-9          |  |  |  |

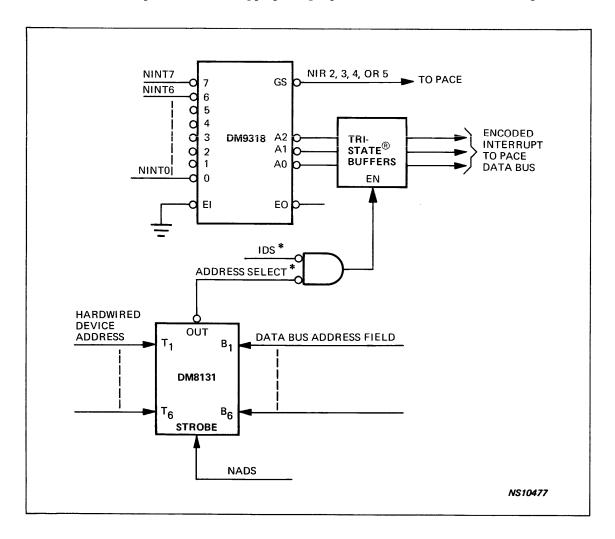

| 5-6        | Use of DM9318 Priority Encoder and DM8131 Comparator for               | -            |  |  |  |

|            | Interrupt Expansion and Detection                                      | 5-11         |  |  |  |

#### Chapter 1

#### AN INTRODUCTION TO PACE

#### 1.0 INTRODUCTION

National Semiconductor's Process and Control Element (PACE) was the industry's first single-chip 16-bit microprocessor, and PACE continues to provide designers with the built-in sophistication that results in cost-effective systems and simplicity of application. As the microprocessor marketplace reaches maturity, some lessons learned during similar stages of minicomputer development are being rediscovered. Foremost among these lessons is an appreciation of the importance of word length: the inherent power and advantages of a 16-bit processing system over 8-bit systems are once again being realized. PACE is a true 16-bit microprocessor and, in addition to the innate superiority obtained from this fact, it incorporates a variety of other features that result in ease-of-use and uncluttered, economical implementation of powerful systems. The paragraphs that follow highlight the features of PACE and the resources that are available to support development of PACE-based systems. A detailed description of PACE is provided in chapter 2. Chapters 3, 4, and 5 provide guidelines and examples to assist in the design of PACE systems.

#### 1.1 THE PACE MICROPROCESSOR

Some of the resources of PACE are illustrated in figure 1-1. PACE makes use of 16-bit data words and 16-bit instruction words, and features a powerful, efficient, and flexible set of 45 instruction types. The 16-bit instruction words greatly increase the power of PACE instructions beyond those of 8-bit processors. Further, the full 16-bit PACE-generated address words increase both efficiency and throughput over those of conventional 8-bit processors. This results from the elimination of multiple-precision operations usually required for 8-bit data elements, and the reduction of program memory overhead.

System memory requirements are further reduced by the four general-purpose working registers (accumulators ACO – AC3) and a ten-word last-in-first-out (LIFO) stack provided by PACE. The accumulators reduce the number of memory load and store operations associated with saving temporary and intermediate results. The LIFO stack provides additional on-chip storage and further reduces program and data storage overhead while inherently reducing interrupt-response time (because it saves return addresses during interrupt servicing and subroutine execution). Thus, the accumulators and stack reduce memory overhead by providing on-chip storage, and increase system throughput by reducing the number of memory-access operations required.

Interfacing PACE to input/output devices is simplified by three data strobe signals that synchronize parallel data transfers, three sense inputs, and four flag outputs that can be used to implement device control functions and serial data transfers, and a multiple vectored priority interrupt structure for fast response to real-time control situations.

Parallel data transfers occur via the multiplexed address/data bus and, since PACE uses common memory input/output address space (memory-mapped input/output) the entire PACE repertoire of memory-reference instructions can be used to implement efficient and powerful input/output interfaces with a minimum of hardware. The Extend Signal further simplifies interfaces by permitting operation with slower devices with minimal penalties to system speed.

The three sense inputs (JC13, JC14, and JC15) are individually testable (along with 13 internal status sense conditions) by a conditional branch instruction in software and can be used for serial data input or to sense external system conditions. Serial data output can be accomplished using the four flag outputs (F11–F14): these software controlled outputs can be set, cleared, and pulsed by the user's program and are also useful for directly controlling system functions or setting software status indicators.

Figure 1-1. PACE Resources

The on-chip, 6-level, vectored, priority-interrupt structure provided by PACE, eliminates the need for any external, off-chip interrupt hardware. The interrupt vector feature provides automatic interrupt identification and thus eliminates program storage overhead and saves time — the time that other processors usually require for polling in order to identify the interrupting device. The interrupt system can be expanded easily by placing more than one peripheral on a priority level using a simple open-collector connection for a wired-OR input to an interrupt-request line.

This brief overview has highlighted some of the outstanding features of PACE. A fuller understanding and appreciation of the advantages and benefits derived from these PACE features can be gained from more-detailed discussions. Chapters 2 through 5 provide these detailed discussions along with useful examples and techniques to assist PACE system designers.

## 1.2 PACE DESIGN SUPPORT

The successful application of any microprocessor, including PACE, demands a variety of supporting products and services ranging from support chips, cards, and development systems to software, training, and field support.

PACE is fully supported throughout this spectrum of products and services. National Semiconductor's total support system ensures that the designer will have access to the tools he needs to efficiently implement his application. The paragraphs that follow describe the design support resources that are available.

## 1.3 PACE SUPPORT CHIPS

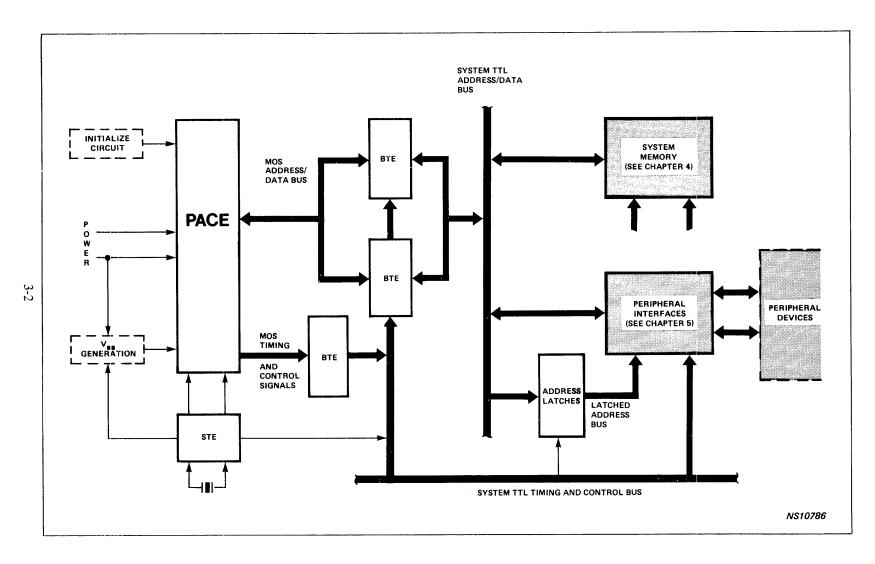

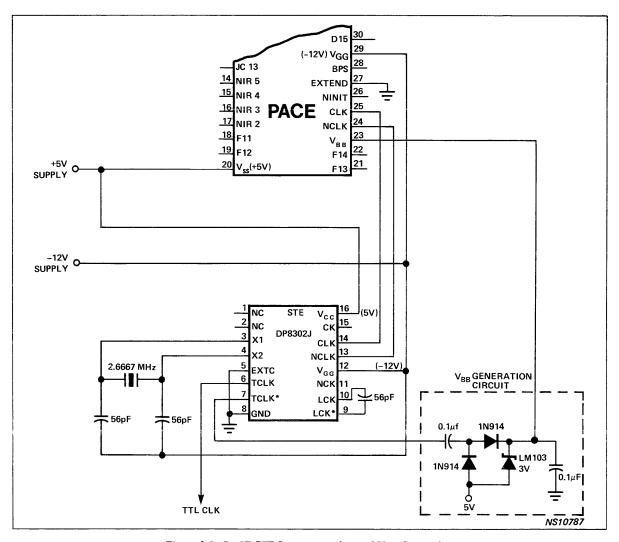

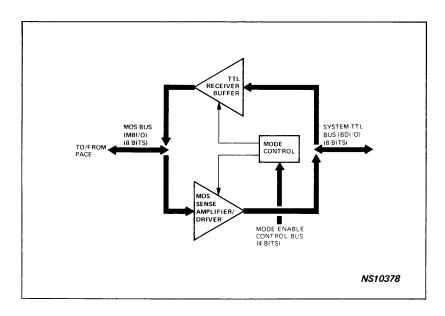

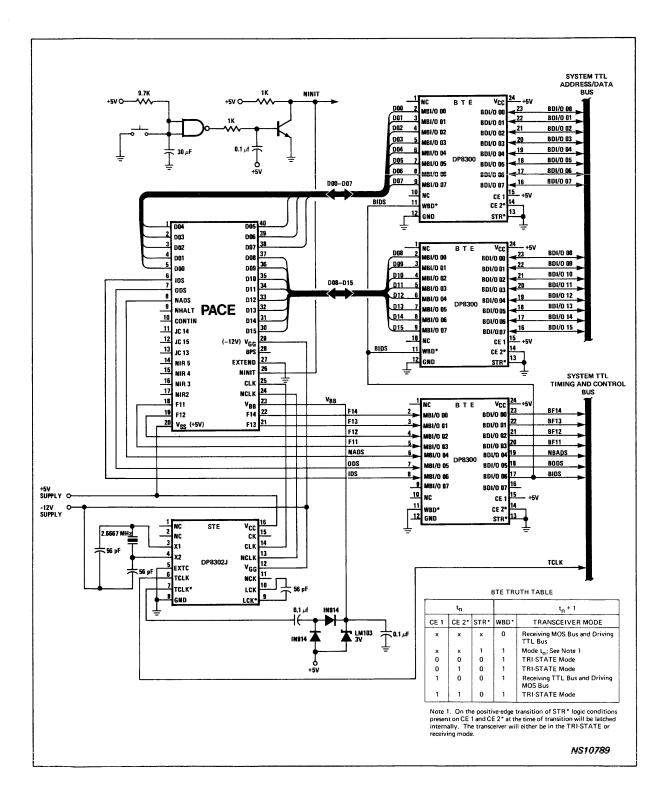

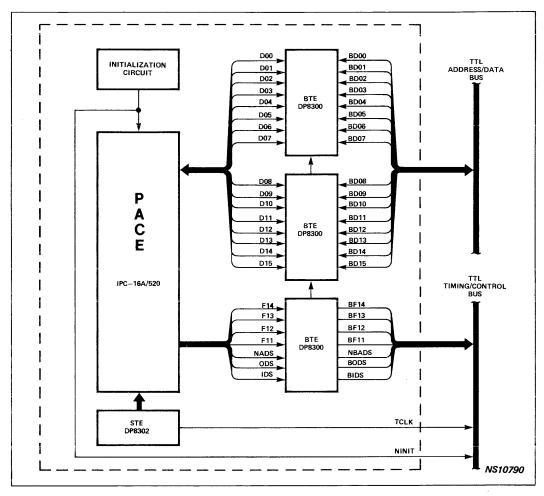

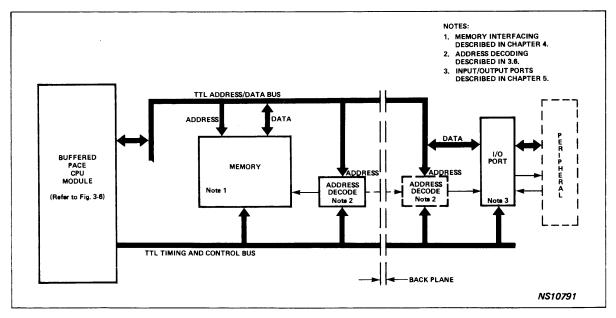

Three specially designed chips are available to simplify development of PACE systems. The System Timing Element (STE) DP8302 produces the MOS nonoverlapping clock signals required by PACE and also supplies two TTL clock signals to accommodate user requirements. The Bidirectional Transceiver Element (BTE) DP8300 is an 8-bit transceiver that provides controlled translation of signals between the PACE microprocessor MOS buses and the system TTL buses. The Microprocessor Interface Latch Element (MILE) DP8301 provides an 8-bit latched interface between the System TTL Address/ Data Bus and the user peripherals.

Figure 1-2 illustrates the relationship of the STE and BTE to PACE. The STE requires application of +5 and -12 volts and the addition of only an external crystal to produce the MOS and TTL clock signals. Three BTEs provide a fully buffered PACE CPU. One BTE connected in a driver-only mode to PACE permits

Figure 1-2. PACE-STE-BTE Relationship

buffering for the System TTL Timing and Control Bus, thereby providing seven TTL control signals and flags for distribution throughout the system. Two BTEs operate bidirectionally to buffer the 16-bit, time-multiplexed Address/Data Bus. Use of the STE and BTEs with PACE is described in detail in chapter 3. Chapter 5 includes a detailed discussion of system implementation of the MILE.

Because of the full complement of control signals provided by PACE, no other special components are required in the design of PACE systems. A variety of widely available, standard memory components can be used. Chapter 4 lists some of the more-popular memory devices and provides examples to illustrate the simplicity with which PACE can be interfaced to memory.

#### 1.4 DEVELOPMENT SYSTEMS

Three PACE systems are available to simplify and speed the design and development of PACE-based application systems.

The PACE Low-Cost Development System (LCDS), shown in figure 1-3, allows the user to check out hardware and interface designs in a real-time environment, and can also be used to build software packages and convert them to firmware. The LCDS requires only the addition of a power supply to be fully operational, and the system can be expanded by connection of a TTY or RS-232-compatible terminal to the interface circuits provided on the LCDS. On-card ROMs contain a debug program and the input/output subroutines for communication with an optional terminal. Jumper options allow baud rates of 110, 150, 300, or 1200 bits-per-second to be selected. Further system expansion is easily accommodated using the three bussed sockets that accept compatible PACE Memory Application Cards and user-designed interface cards. A Cable Card is also available to extend the system bus to an external card cage.

The IPC-16P PACE Development System, shown in figure 1-4, is intended primarily to simplify the development of applications software. This system is a full-featured microcomputer and includes a comprehensive front panel to monitor and control system operation. A full array of peripheral options are available to extend the power of this system, and memory can be expanded from the standard configuration of 8K 16-bit words up to 32K 16-bit words. A powerful resident software package (described in 1.5) is provided to expedite the development of the user's application programs.

The PACE Disc Operating System (DOS) provides all the capabilities of the IPC-16P and further increases throughput and flexibility by providing the convenient mass storage capability of dual floppy disc drives. Included with the system is a DISC/CRT Interface Card that provides interfacing between the microprocessor, the dual disc drives, and a user-provided, optional CRT terminal. A DOS Monitor System is provided on a Read-Only-Memory (ROM) card and controls system configuration and linkage to other software subsystems. Also included on the ROM card is a File Input/Output Subsystem that provides the peripheral communication required by the remainder of the PACE DOS. A powerful disc-resident software package (described in 1.5) is included on a single diskette and completes the total-system capability obtained through use of the PACE DOS.

NS10737

Figure 1-3. PACE Low Cost Development System (LCDS)

NS10414

Figure 1-4. PACE Microprocessor Development System (IPC-16P)

#### 1.5 PACE SUPPORT SOFTWARE

PACE is supported by a full complement of software provided to meet the needs of designers at every level of product development.

A BASIC interpreter has been developed for use with PACE and allows programs for design feasibility studies to be generated quickly and easily. This enhanced version of BASIC features real-time input/output and calls to assembly language subroutines. The BASIC interpreter is currently available for use with the PACE Development Systems and soon will be available for use with the PACE LCDS.

A Macro Assembler is also available and this powerful software tool permits extremely efficient assembly language programs to be generated with maximum ease. The Macro Assembler is memory resident in the IPC-16P and is provided on diskette with the PACE DOS Microprocessor Development System.

PACE DOS also includes a disc-resident File Manager Program that relieves the user of burdensome house-keeping tasks. The File Manager handles disc sector assignment automatically, and provides easy control of file maintenance and execution, space allocation, and file protection.

For users who do not have access to a PACE Development System, two cross assemblers are available. One version of the cross assembler runs on an IMP-16P or an IMP-16L Development System. A FORTRAN Cross Assembler is also available and allows programs to be developed on a variety of different host computers, including 16-bit minicomputers.

In addition to these primary software tools, a comprehensive array of editors, loaders, debug programs, and diagnostics are available to meet the needs of PACE system designers.

#### 1.6 SUPPORT SERVICES AND PERSONNEL

A design effort does not end with the arrival of PACE hardware and software — it is just beginning. Recognizing this, National Semiconductor's support of PACE begins with training and predesign consultation and continues throughout your design cycle and beyond.

Microprocessor Training Centers, located in Miami, Florida and Santa Clara, California provide an intensive exploration of microprocessor applications with a good mix of hardware/software theory and hands-on laboratory experience. Beyond the classroom, applications engineers are available throughout the world and at our home base to help you analyze your specific application and translate your needs into a viable hardware/software configuration.

Consultation is available from the design concept stage through delivery of your final product and continuing education is available from COMPUTE (Club of Microprocessor Programmers, Users, and Technical Experts), an informal organization sponsored by National Semiconductor, dedicated to the distribution of ideas and techniques relating to the use of microprocessors.

### Chapter 2

#### PACE MICROPROCESSOR DESCRIPTION

## 2.1 GENERAL DESCRIPTION

The PACE (Processing and Control Element) is a single-chip, 16-bit microprocessor packaged in a standard 40-pin package. PACE is a true 16-bit central processing unit; it makes use of 16-bit instruction words and 16-bit data words, and features a powerful, efficient, and flexible set of 45 instructions. All instructions use a single-word, 16-bit format — thus reducing memory accesses and program storage requirements.

#### 2.1.1 PACE Architecture

The architecture of PACE (shown in figure 2-1) features a number of resources to minimize system program and read/write storage, to increase throughput, and to reduce the amount of external support hardware. PACE provides all the control and timing signals required for system or subsystem operation; these signals are described in detail in the sections that follow. Powerful and flexible data manipulation capabilities, the primary function of the central processing unit, and extensive internal data storage capacity that reduce the number of input/output cycles are also provided by PACE.

Data transfers between PACE (see figure 2-1) and memory or peripheral devices are effected over the 16-bit (D00-D15) parallel Input/Output Data Bus. The Input/Output Data Bus interfaces with the Instruction Register and the Operand Bus by way of the I/O Data Buffers. The Operand Bus also interfaces with seven registers (Temporary Registers 1 and 2, Program Counter, and AC0 through AC3) and a 10-word Stack. The seven registers and the Stack are provided for data storage. Four of the registers (AC0 through AC3) are available to the programmer as general-purpose accumulators. The Program Counter contains the address of the next instruction. The contents of any selected register or the Stack are routed over the Operand Bus to the Arithmetic and Logic Unit (ALU) and Shifter. Resultant ALU and Shifter output is returned to the selected register or Stack, as appropriate, by way of the Result Bus. The ALU and Shifter, besides performing arithmetic operations, also sets status flags in accordance with the data length (8-bit or 16-bit) selected by the state of the BYTE Status Flag.

All status information is stored in the 16-bit Status and Control Flags Register. The Status and Control Flags Register contents can be loaded onto the Operand Bus for temporary storage on the Stack or in any accumulator for examination or modification of status information.

Instructions under execution by PACE are stored in the Instruction Register and are interpreted and executed by a microprogram stored in an on-chip ROM. Instruction execution time is determined by the instruction under execution and memory access time. Appendix A provides an instruction summary, including the information required to calculate instruction execution times.

## 2.1.2 PACE Interface Signal Descriptions

PACE communicates with other system devices with its interface signals available via the 40 hardwired pins connected to PACE internal circuits. Three of the pins are used for input power and two are used for clock inputs. The remaining 35 pins are used to transfer 16-bit address and data information, to output control and timing synchronization information, and to accept control inputs that affect the operation of PACE.

Figure 2-1. PACE Detailed Block Diagram

The pin assignments for PACE are shown in figure 2-2. Brief descriptions of the PACE interface signals are provided in table 2-1. Details on the use of the interface signals are provided later in this chapter and references to the appropriate sections are included in table 2-1.

#### **NOTES**

- Positive logic convention is used throughout this manual.

A logic '1' or high signal corresponds to a more-positive voltage level. A logic '0' or low signal corresponds to a more-negative voltage level. All signal names beginning with 'N' or followed by an asterisk (\*) denote complemented signals that are asserted or activated by a logic '0'. Otherwise, signals are asserted by a logic '1'.

- 2. Bits are numbered from 00 to 15, right to left, with bit 00 representing the least significant bit.

- The X' preceding a value denotes the hexadecimal numbering system.

## 2.2 PACE TIMING REQUIREMENTS

PACE requires single-phase, nonoverlapping true and complemented clock inputs as shown in figure 2-3. (Refer to PACE data sheet for detailed timing specifications.) The required timing inputs can be provided using the System Timing Element (STE) that is described in chapter 3 (3.1). PACE uses the external clock signals to generate internal multiphase clock signals that provide control timing for microprocessor operations. Four external time periods (t<sub>p</sub> in figure 2-3) correspond to eight internal clock phases that comprise a single machine cycle of the PACE microprocessor. Figures 2-5 through 2-8 (which appear later in this chapter) illustrate the relationship between external clocks and internal clock phases. The execution of each PACE instruction requires four or more machine cycles, plus any required input/output cycle extends. (Appendix A provides an explanation of the method for computing actual execution times.)

#### 2.3 INITIALIZATION

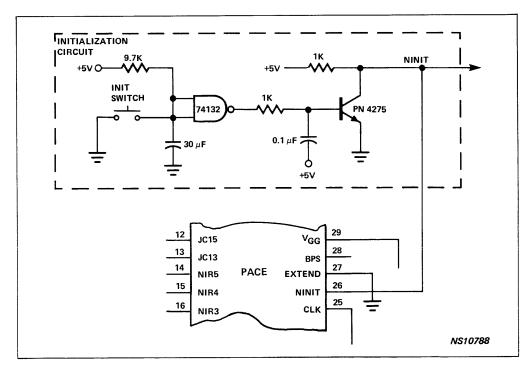

The PACE Initialize Signal (NINIT) input may be used at any time to initialize the microprocessor and should always be used after system power-up. Application of a low NINIT Signal clears the Stack Pointer, sets the flags to zero, sets the level-0 Interrupt Enable True, and sets the Program Counter contents to zero. The accumulators assume an arbitrary state. The NADS, IDS, and ODS data strobes are set false. Thus, if it is desired to initialize PACE during program execution, NINIT should be inhibited until after any data output cycle, that may be in progress, is completed. Inhibiting NINIT prevents erroneous data from being written to memory.

The minimum pulse width for NINIT is eight clock periods as shown in figure 2-4. The PACE data strobes (NADS, ODS, and IDS) are inactive for 16 clock cycles after the trailing edge of the NINIT Signal occurs. After the 16 clock cycles, the first NADS Signal occurs and the first instruction is accessed from memory location X'0000, unless a Level-0 Interrupt (Control Panel Interrupt) is present. All other interrupt levels are disabled.

Table 2-1. PACE Interface Signal Descriptions

| Signal/Description                                                                                                                                                                                                                                                                                                                                                    | Reference<br>Section | Signal/Description                                                                                                                                                                                                                                                                                                                                                                                                             | Reference<br>Section |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| CLK, NCLK (inputs) — External true and complemented clock inputs.                                                                                                                                                                                                                                                                                                     | 2.2                  | NIR2, NIR3, NIR4, NIR5 (input) — Interrupt Requests 2, 3, 4, and 5. When these negative-true input signals are low for 1 CLK period, minimum, the associated                                                                                                                                                                                                                                                                   | 2.7<br>2.7.1         |

| D00-D15 (input/output) — Data bus lines. Bidirectional MOS data lines used for input and output of data and for output of 16-bit addresses on I/O cycles.                                                                                                                                                                                                             | 2.4.1<br>2.4.2       | internal Interrupt Request Latch is set if the corresponding interrupt enable has been set by users program. The interrupt will be serviced after completion of current instruction if the Master Interrupt Enable                                                                                                                                                                                                             |                      |

| NADS (output) — Address Data Strobe. The negative-<br>true NADS signal is sent out at the beginning of every<br>data input/output cycle and indicates that a memory                                                                                                                                                                                                   | 2.4.1<br>2.4.2       | is set. Interrupt Requests are prioritized, with NIR5 having lowest priority.                                                                                                                                                                                                                                                                                                                                                  |                      |

| or peripheral address has been output on the data bus<br>lines. The address is stable on the data bus while the<br>NADS signal is active low.                                                                                                                                                                                                                         |                      | NHALT (input/output) — Halt. When the negative-<br>true NHALT signal is driven low by external logic, it<br>effects microprocessor stall or 'Level-0' Interrupt, de-<br>pending on timing of CONTIN signal. When not con-                                                                                                                                                                                                      | 2.8                  |

| ODS (output) — Output Data Strobe. The ODS signal indicates to external circuits that the data bus contains valid output data.                                                                                                                                                                                                                                        | 2.42                 | trolled by external logic, NHALT is driven low by PACE for 7/8 duty cycle while programmed halt condition exists. Programmed halt is initiated by the Halt Instruction and terminated by pulsing                                                                                                                                                                                                                               |                      |

| IDS (output) — Input Data Strobe. The IDS signal indicates to external devices that PACE is performing a data input cycle. The signal should be used by memory or peripheral devices to gate data onto the PACE                                                                                                                                                       | 2.4.1                | CONTIN line via external logic,  CONTIN (input/output) — Continue. The CONTIN signal is used in input mode to terminate programmed                                                                                                                                                                                                                                                                                             | 2.8                  |

| data bus lines.  EXTEND (input) — Extended Data Transfer. The                                                                                                                                                                                                                                                                                                         | 2.4.3                | halt, or to exercise microprocessor stall and Level-0 Interrupt, or as a jump-condition input that can be tested using a BOC instruction. In the output mode,                                                                                                                                                                                                                                                                  |                      |

| EXTEND signal is used by slower memory or peripheral devices to temporarily increase time duration of data input/output transfers. The EXTEND signal                                                                                                                                                                                                                  |                      | CONTIN transmits an interrupt acknowledge pulse to acknowledge CPU response to an active interrupt input.                                                                                                                                                                                                                                                                                                                      |                      |

| should be driven high at the beginning of ODS or IDS signal and held high until output data has been captured or input data is made available to data bus. The EXTEND signal can also be used to suspend input/output operations by applying the signal after the end of ODS or IDS.                                                                                  |                      | BPS (input) — Base Page Select. The BPS signal enables one of two base-page addressing schemes to be selected. When BPS is low, first 256 words of memory constitute base page (page zero). When BPS is high, first 128 memory words and last 128 memory words constitute base page.                                                                                                                                           | 2.9.2                |

| JC13, JC14, JC15 (input) — Jump Conditions 13, 14, and 15, JC13, 14, and 15 are user-specified inputs that can be tested using Branch-On-Condition (BOC) Instructions. If jump condition input specified in BOC Instruction is high, a program branch is effected. The JC13-JC15 signals are useful for testing status of external devices and receiving serial data. | 2.6                  | NINIT (input) — Initialize. While the negative-true NINIT signal is low, PACE operation is suspended, and IDS/ODS signals are set to inactive state. After NINIT completes low-to-high transition, the program counter is set to zero, the internal stack pointer is cleared, and all flags and interrupt enables are set low except Level-0 Interrupt Enable which is set high. All other registers contain arbitrary values. | 2.3                  |

| F11, F12, F13, F14 (output) — General-purpose control flag outputs from PACE Status and Control Flags Register. Individual flags may be set by Set Flag Instruction and pulsed or reset by Pulse Flag Instruction. The F11-F14 signals may be used for direct control of system functions or serial data output.                                                      | 2.5                  | V <sub>SS</sub> +5 Volts, V <sub>GG</sub> -12 Volts V <sub>BB</sub> V <sub>SS</sub> +3 Volts (substrate bias)                                                                                                                                                                                                                                                                                                                  |                      |

Figure 2-2. PACE Pin Assignments

Figure 2-3. External Clock Timing

Figure 2-4. Initialization Timing

#### NOTE

If the NINIT input is held true (low) before power and/or clocks are totally stable, the NADS and NHALT outputs may have an undefined state for eight clock cycles after NINIT goes false (high). In order to initialize properly every time, NINIT should go true (low) after all the power supplies and clocks have stabilized.

## 2.4 DATA INPUT/OUTPUT OPERATIONS

The primary means PACE uses to communicate with external system devices is via 16-bit parallel data input/output (I/O) operations. The descriptions that follow apply both to memory devices (for either instruction fetch operations or data transfer operations) and to peripheral devices (using parallel data transfer techniques).

Parallel data transfers between PACE and external memory or peripheral devices take place over the 16 data lines (D00-D15). All input/output transactions consist of an address-output interval followed by a data-transfer interval. The data transfers are synchronized by the NADS, IDS, and ODS signals that are generated by PACE, and the EXTEND signal can be applied to PACE using external logic to increase the input/output cycle time.

## 2.4.1 Data Input Operation

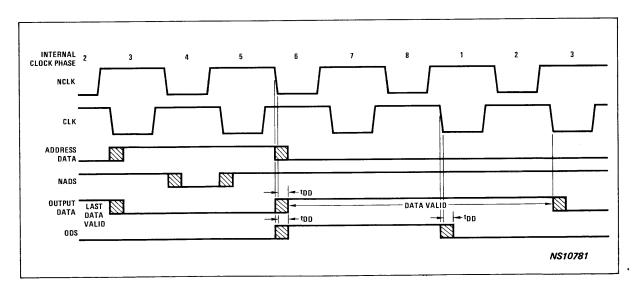

Data input timing is shown in figure 2-5. Address data become valid one clock phase prior to the Address Data Strobe (NADS) and remain valid for one clock phase afterwards. Typically, NADS is used to strobe the address data into a latch, either internal or external to the system memory chips, or to clock decoded peripheral addresses into a flip-flop.

Following the output of address information, the output address drivers internal to PACE assume a high-impedance state and the Input Data Strobe (IDS) Signal goes high. The IDS Signal may be used to disable external output sense amplifiers and to enable input buffers. The IDS Signal remains high for three clock widths: the data lines must be driven to valid input data logic levels by the end of IDS.

Typically, the data-input timing allows operation of PACE in a system at maximum frequency if the system memory access time is less than two clock periods. If longer access time is required, the EXTEND signal may be used to increase the input/output cycle time. Use of the EXTEND signal is described in 2.4.3.

## 2.4.2 Data Output Operations

Timing for data-output operations is shown in figure 2-6. The address-output portion of the operation is identical to that described for data-input operations. Following the address, output data is placed on the data lines and, at approximately the same time, the Output Data Strobe (ODS) Signal goes high. The ODS Signal is used typically as a read-write signal for memory and as an output-data latch strobe for peripheral interfaces. Since output data remain valid following termination of the ODS Signal, the trailing edge of ODS can be used to clock the data into an external latch. The EXTEND signal (described in the paragraph that follows) can be used to extend the time that output data remain valid.

Figure 2-5. Address Output and Data Input Timing

Figure 2-6. Data Output Timing

## 2.4.3 Use of EXTEND Signal

The EXTEND signal may be used either to increase the time duration of a data-input/output cycle or to suspend all PACE-initiated input/output operations.

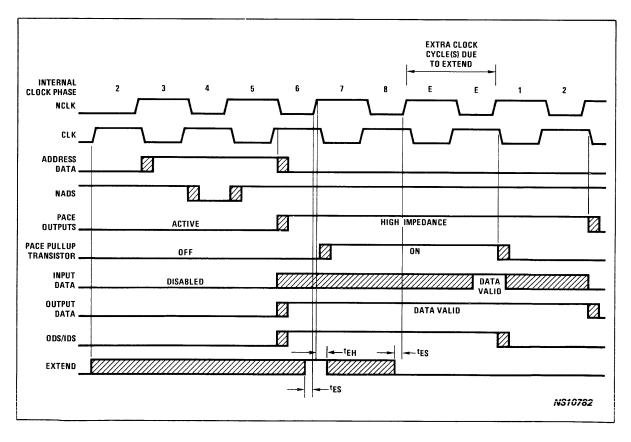

Figure 2-7 shows the timing required when using EXTEND to lengthen the input/output cycle. The EXTEND signal may go high (true) during the address time or immediately after the start of IDS or ODS, but EXTEND must be true prior to the end of internal phase 6.

## **NOTE**

If the EXTEND signal is not used, it should be tied to ground.

The timing shown in figure 2-7 provides the minimum extend of one clock period. Holding EXTEND true for n additional clock periods longer causes an extension of n + 1 clock periods. The EXTEND signal duration must not exceed the specified minimum refresh requirements of the PACE device. (Refer to appendix C for specifications.)

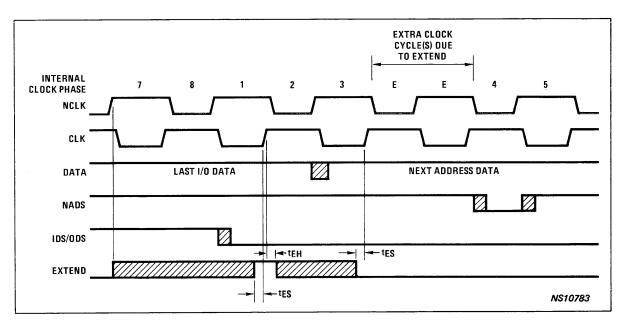

The EXTEND signal may also be used to suspend PACE input/output operations. This may be desirable in Direct Memory Access or multiprocessor systems to prevent input/output operations by PACE when the bus is in use by another device. Input/output operations are suspended by using the EXTEND signal immediately following an IDS or an ODS as shown in figure 2-8.

Figure 2-7. Extend I/O Signal Timing

Figure 2-8. Suspend I/O Signal Timing

## 2.5 STATUS AND CONTROL FLAGS

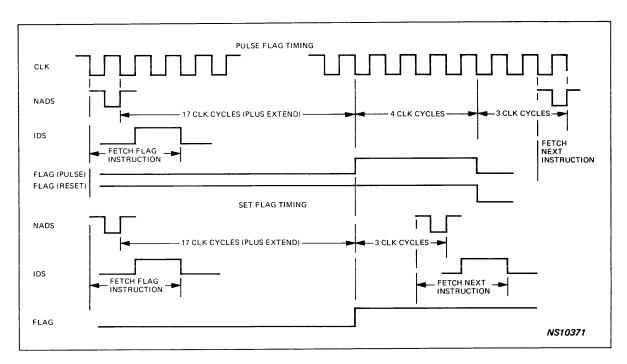

Fourteen status and control flags are provided by the PACE microprocessor in the Status and Control Flag Register. The flags contained in this register can be accessed or restored as a 16-bit data word by using the Copy Flags to Register or Copy Register to Flags Instructions. Similarly, the contents of the register can be saved on the Stack or retrieved from the Stack. Individual flags can be set by using the Set Flag Instruction and reset or pulsed using the Pulse Flag Instruction. Four of the bits (F11, F12, F13, and F14) in the Status and Control Flag Register drive PACE output pins and may be used to directly control system functions or to accomplish serial data output. Table 2-2 provides descriptions of the individual status and control flags. Figure 2-9 shows the timing for Set Flag and Pulse Flag Instruction operations.

## 2.6 JUMP CONDITIONS

The PACE microprocessor contains a Jump Condition Multiplexer that samples the 16 jump conditions listed and described in table 2-3. The Branch-On-Condition Instruction (BOC) tests the output of the jump condition multiplexer. If the condition for branching (selected by the condition code specified in the BOC Instruction) is active, a branch occurs; otherwise, the next sequential instruction is executed. Note that 12 of the conditional jumps test conditions internal to PACE. The remaining four jump conditions (CONTIN, JC13, JC14, and JC15) are connected to PACE input pins and can be used to test external user-specified conditions. These jump condition inputs are also useful as serial data inputs.

#### **NOTE**

The CONTIN signal can also be used in conjunction with the NHALT signal to implement several special-purpose processor functions as described in 2.8.

Table 2-2. Descriptions of Status and Control Flags

| Register Bit          | Flag Name                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Flag Code (fc)                       |

|-----------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 0                     | High ('1')                      | Bit 0 is not used and is always in logic '1' state. Referencing bit 0 with SFLG or PFLG Instruction has no effect. (May be used as NOP Instruction.)                                                                                                                                                                                                                                                                                                                                                                            | 0000                                 |

| 1<br>2<br>3<br>4<br>5 | IE1<br>IE2<br>IE3<br>IE4<br>IE5 | Flags IE1 through IE5 serve as Interrupt Enable Flags for five of six PACE interrupt levels. If Interrupt Enable is high and associated Interrupt Request occurs, microprocessor executes Interrupt Service Routine. If Interrupt Enable is low, associated Interrupt Request is ignored.                                                                                                                                                                                                                                       | 0001<br>0010<br>0011<br>0100<br>0101 |

| 6                     | OVF                             | Overflow Flag is set to state of twos-complement arithmetic overflow by arithmetic instructions. Overflow Flag is set high if sign bits (most significant bit) of two operands are identical and sign bit of result is different from sign bit of operands. If A, B, and R are sign bits of operands and result, then Overflow Flag is set according to equation  OVF = (A·B·R) + (A·B·R)  Sign bit is most significant bit for data length selected; thus, if data length is 8 bits, then bit 7 is sign bit; if data length is |                                      |

| 7                     | CRY                             | 16, then bit 15 is sign bit. State of OVF Flag is affected by instructions ADD, DECA, SUBB, RADD, and RADC.  Carry Flag is set to state of binary or decimal carry output of adder by arithmetic instructions. Carry output is derived from most significant bit for data length specified by BYTE Flag.  State of CRY Flag is affected by instructions ADD, DECA, SUBB, RADD, and RADC.                                                                                                                                        | 0111                                 |

| 8                     | LINK                            | Link Flag is included in shift and rotate operations as specified by Shift and Rotate Instructions. Link Flag is unaffected if not selected.                                                                                                                                                                                                                                                                                                                                                                                    | 1000                                 |

| 9                     | IEN                             | Master Interrupt Enable Flag simultaneously inhibits all five of lowest-priority interrupt levels. No Interrupt Request is serviced unless individual Interrupt Enable Flag for associated Interrupt Request and master Interrupt Enable Flag are high. IEN Flag is set low every time any interrupt (except Level-0) is serviced. IEN Flag is set high by execution of Return To Interrupt Instruction (RTI).                                                                                                                  |                                      |

| 10                    | ВҮТЕ                            | BYTE Flag selects 8-bit data length when high and 16-bit data length when low.                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1010                                 |

| 11<br>12<br>13<br>14  | F11<br>F12<br>F13<br>F14        | Flags 11 through 14 are general-purpose control flags. Flags 11 through 14 drive PACE output pins and may be used to directly control system functions.                                                                                                                                                                                                                                                                                                                                                                         | 1011<br>1100<br>1101<br>1110         |

| 15                    | High ('1')                      | Bit 15 is not functional and is always in logic '1' state. Addressing bit 15 with SFLG or PFLG Instruction sets the Level-0 Interrupt Enable high. The Level-0 Interrupt is described in Section 2.8.3.                                                                                                                                                                                                                                                                                                                         | 1111                                 |

Figure 2-9. Pulse and Set Flag Timing Diagram

Table 2-3. Branch Conditions

| Condition Code (cc) | Mnemonic                          | Condition                                  |

|---------------------|-----------------------------------|--------------------------------------------|

| 0000                | STFL                              | Stack Full (contains nine or more words).  |

| 0001                | REQ0                              | (AC0) equal to zero (see note 1).          |

| 0010                | PSIGN                             | (ACO) has positive sign (see note 2).      |

| 0011                | ВІТО                              | Bit 0 of AC0 true.                         |

| 0100                | BIT 1                             | Bit 1 of AC0 true.                         |

| 0101                | NREQ0                             | (ACO) is nonzero (see note 1).             |

| 0110                | BIT2                              | Bit 2 of AC0 is true.                      |

| 0111                | CONTIN                            | CONTIN (continue) Input is true.           |

| 1000                | LINK                              | LINK is true.                              |

| 1001                | IEN                               | IEN is true.                               |

| 1010                | CARRY                             | CARRY is true.                             |

| 1011                | NSIGN                             | (ACO) has negative sign (see note 2).      |

| 1100                | OVF                               | OVF is true.                               |

| 1101                | JC13                              | JC13 Input is true.                        |

| 1110                | JC14                              | JC14 Input is true.                        |

| 1111                | JC15                              | JC15 Input is true.                        |

| NOTES: 1. I         | f selected data length is 8 bits  | , only bits 0 through 7 of AC0 are tested. |

| 2. E                | Bit 7 is sign bit (instead of bit | 15) if selected data length is 8 bits.     |

## 2.7 INTERRUPT SYSTEM

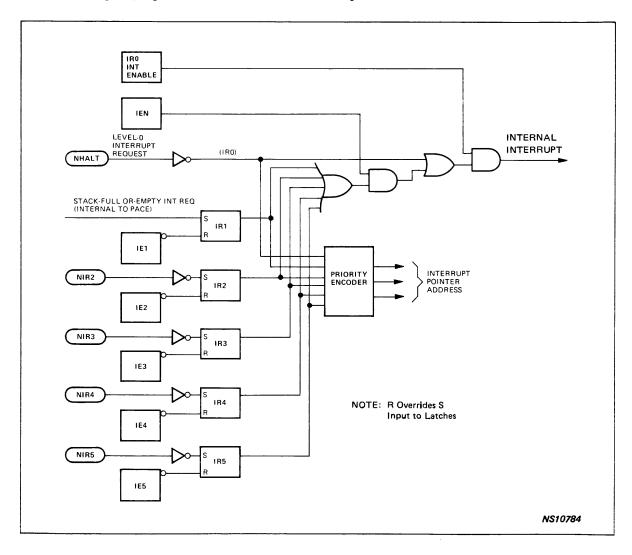

PACE provides a 6-level, vectored, priority interrupt structure. This allows automatic identification of the priority level of an interrupting device and allows all devices on an interrupt level to be enabled or disabled as a group, independent of other interrupt levels. An individual interrupt enable is provided in the Status Register for each level, as shown in figure 2-10, and a master interrupt enable (IEN) is provided for all five lower priority levels as a group. The state of the Internal Interrupt Signal is tested by PACE during the Instruction Fetch Routine (internal to PACE) that is executed after completion of each instruction. Thus, if the Internal Interrupt Signal is high, the interrupt is automatically serviced.

NIR2 through NIR5 are referred to as user-specified interrupts; their operation is described in 2.7.1. The Level-1 Interrupt is dedicated for use as a stack-full/stack-empty interrupt and is described in 2.7.2. The Level-0 Interrupt is a special-purpose, nonmaskable interrupt and requires user manipulation of the NHALT and CONTIN signals; implementation of the Level-0 Interrupt is described in 2.8.3.

Figure 2-10. PACE Interrupt System

## 2.7.1 User-Specified Interrupts

Negative-true Interrupt Request Inputs (NIR2 through NIR5) are provided to allow several interrupts to be wire-ORed to each input. When an Interrupt Request occurs, the associated Interrupt Request Latch (IR1 through IR5) is set if the corresponding Interrupt Enable Input is true. Since the Interrupt Request Latch can be set by any pulse exceeding one clock period, narrow timing or control pulses can be captured. If IEN is high, then an interrupt is generated and acknowledged after completing the current instruction. The interrupt acknowledge is provided by PACE on the CONTIN pin; refer to figures 2-11 and 2-12 and associated text for an explanation of the interrupt-acknowledge function of the CONTIN signal.

During the interrupt sequence, an address is provided by the output from the priority encoder. The address is used to access the Interrupt Pointer for the highest-priority Interrupt Request (IR0 has highest priority; IR5 has lowest priority). The Interrupt Pointers are stored in memory locations 2 through 8 (see table 2-4) for Interrupt Requests 1 through 5 and 0, respectively. The Interrupt Pointer specifies the starting address of the user-supplied Interrupt Service Routine for the particular interrupt level, except in the case of the Level-0 Interrupt (IR0), which is used primarily for alarm interrupts and Control Panel implementation (refer to 2.8.3 for details).

Before execution of the Interrupt Service Routine, the contents of the Program Counter are pushed onto the Stack and IEN is set low (false). This interrupt handling requires 28 clock cycles. The Interrupt Service Routine may set IEN high (true) after turning off the Interrupt Enable for the interrupt level currently being serviced (or resetting the Interrupt Request). The Interrupt Enable Flags can be set by the Set Flag (SFLG) and reset by the Pulse Flag (PFLG) Instructions. The Copy Register to Flags (CRF) Instruction can also be used to set or reset Interrupt Enable Flags. If an Interrupt Enable Flag is set or reset, one more

Figure 2-11. Timing Diagram for Processor Stall using NHALT and CONTIN Signals

instruction is executed before the interrupt is enabled or disabled. The Return From Interrupt Instruction (RTI) also may be used to set IEN true. In this case, there is no delay and a pending interrupt takes place immediately after execution of RTI.

## **NOTE**

The use of PFLG or CRF Instructions to disable the IEN flag allows one more instruction to be executed before the interrupts are disabled. If an interrupt should occur during execution of the PFLG or CRF Instruction, the subsequent use of RTI would leave IEN true (one) after the execution of PFLG IEN. To prevent this situation, the BOC Instruction may be used to test PFLG or CRF Instruction as follows:

PFLG IEN ; TURN OFF IEN BOC IEN, .-1 ; IS IEN FALSE?

; YES

Figure 2-12. Relative Timing for Level-0 Interrupt Generation

Table 2-4. Locations of Interrupt Pointers

| Interrupt Pointer          | Memory Location |

|----------------------------|-----------------|

| Interrupt-0 Program        | 8               |

| Interrupt-0 PC             | 7               |

| Interrupt 5                | 6               |

| Interrupt 4                | 5               |

| Interrupt 3                | 4               |

| Interrupt 2                | 3               |

| Interrupt 1                | 2               |

| Not Assigned               | 1               |

| Initialization Instruction | 0               |

It should be recognized that the function of the individual Interrupt Enables IE1-IE5 is to arm or disarm the Interrupt Request Latch, whereas the function of the Master Interrupt Enable (IEN) and Interrupt Enable IR0 is to enable or disable the latched Interrupt Request lines.

## 2.7.2 Stack Interrupts

The response to a Stack Interrupt (Interrupt Level-1) is the same as described for user-specified interrupts. The initiation of the interrupt request, however, is internal and occurs automatically when a stack-empty or stack-full condition exists. The Stack Interrupt consists of a pulse applied to the set input of Interrupt Request Latch 1 (see figure 2-10). The pulse sets the latch if the IEN1 Flag is true; otherwise, the pulse is ignored. The Stack is implemented with a RAM and a Pointer, which can access RAM locations 0 to 9. A pulse occurs when the Stack Pointer is at 0 (one entry on Stack), and a Read-Stack Operation occurs to empty the Stack. A pulse also occurs when the Stack Pointer is equal to 7 (eight entries on the Stack), and a Write-Stack Operation occurs to fill the ninth word and leave one word empty so it may be used by the interrupt. When a Stack Interrupt occurs, the condition of the Stack can be determined by using the Stackfull Jump Condition (STFL); if the interrupt was due to a stack-full condition, STFL equals 1; if due to a stack-empty condition, STFL equals 0.

With the interrupt scheme described, an interrupt does not occur at initialize but does occur every time the Stack becomes empty. If the Stack is to be extended into memory, a Stack-empty Interrupt is required but may be inhibited by turning off IEN1 in other cases. (Refer to the PACE Assembly Language Programming Manual for examples of techniques for extending the stack into memory.) In order to prevent a Stack Interrupt when both hardware and software stacks become empty, a dummy word may be pushed on the Stack by the Initialize Routine.

If a Stack Interrupt occurs while there is a level-3 or a level-4 interrupt present and enabled, the stack interrupt pointer will be accessed incorrectly from location 0 instead of location 2. Therefore, if the stack interrupt is used in conjunction with level-3 or level-4 interrupts, the contents of location 0 must equal the contents of location 2, which contains the address of the user's stack interrupt service routine. Since location 0 (zero) is also the initialize address, this means that location 0 must contain a value that serves a dual purpose:

- 1. It serves as an instruction during initialization.

- 2. It serves as an address if a Stack Interrupt occurs at the same time as a level-3 or a level-4 interrupt.

For example, a Copy Flags to Register 0 Instruction (CFR) has an opcode of 0400. Thus, if this instruction were contained at location 0, it could serve as both the initialize instruction and as a pointer to the Stack Interrupt Service routine, which would begin at location 0400. A few precautions must be observed when using this technique:

- 1. Test and branch, Copy Register to Flags (CRF), and skip instructions should not be used in location 0.

- 2. JMP and JSR Instructions must be used with caution.

- 3. Location 1 must contain a jump to the user's initialize routine (unless location 0 contained a jump).

- 4. Instructions used for location 0 must have an opcode of X'0400 or greater since any lesser value will be interpreted as a Halt Instruction.

## 2.8 NHALT AND CONTIN SIGNALS

The NHALT Signal performs three different functions: programmed halt indicator output, processor stall input, and nonmaskable Level-0 Interrupt input. The CONTIN Signal is used as an interrupt acknowledge output signal, as an input signal to continue processor activity after a programmed halt or a processor stall, and in conjunction with NHALT to initiate the Level-0 Interrupt. The use of NHALT and CONTIN to accomplish these functions is described in the paragraphs that follow.

#### **NOTE**

The CONTIN signal may also be used independently of the NHALT signal as a jump-condition input. Refer to 2.6 for details.

## 2.8.1 Programmed Halt

During normal program execution, the NHALT control line provides a high output. If a Halt Instruction is executed, the microprocessor NHALT output is driven low to indicate that microprocessor activity has been suspended. While PACE operation is in suspension, the NHALT output has a 7/8 duty cycle; that is, every eighth clock phase, the NHALT output goes high. The NHALT 7/8 cycle must be accounted for if the output is used as a logic signal but is of little concern if the output drives only a halt indicator. The NHALT output goes high after the Halt Instruction is terminated by application of the CONTIN Signal. The CONTIN input must go true (high) for a minimum of 16 clock cycles, and then low for 4 clock cycles for PACE operation to resume.

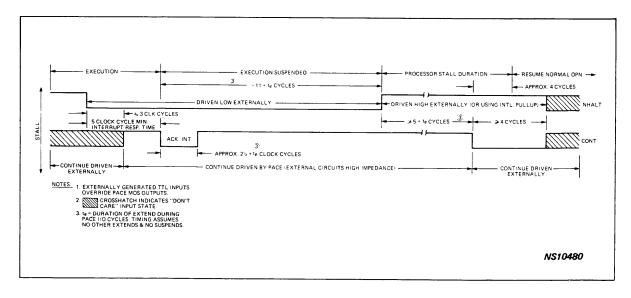

#### 2.82 Processor Stall

To suspend operation of PACE under external control, the NHALT signal may be driven low by an external gate, overriding the NHALT output buffer internal to PACE. Microprocessor operation then is suspended after execution of the current instruction. The suspension may last for an indefinite period of time without loss of CPU status and may be terminated by use of the CONTIN input (properly sequenced with removal of the NHALT input). The timing sequence for the NHALT and CONTIN Signals is shown in figure 2-11. The NHALT and CONTIN method for suspending PACE operation can be useful for Direct Memory Access block data transfers which require full bus-throughput capacity.

## 2.8.3 Level-0 Interrupts

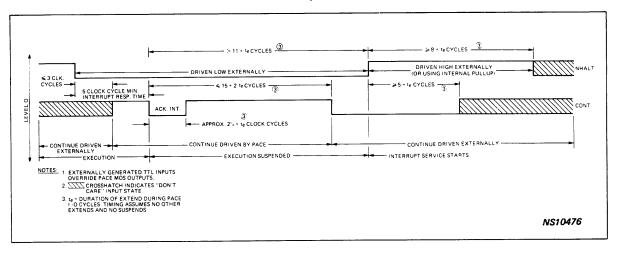

The Level-0 Interrupt is not maskable under program control and, therefore, is useful for alarm conditions (such as a power failure) or for implementing a software-based control panel. The PACE NHALT and CONTIN Signals are used to generate a Level-0 Interrupt. The required relative timing for Level-0 Interrupt generation is illustrated in figure 2-12, and, as shown, the CONTIN Signal can be used as an interrupt acknowledge to indicate that the interrupt is being processed by PACE.

For cases where an interrupt acknowledge is not required or where the CONTIN Signal is used as a sense input to the program, the CONTIN Signal can be held low continuously. While holding the CONTIN Signal continuously low, the NHALT Signal must be driven low at least for the duration of the longest instruction execution time plus eleven clock cycles to guarantee that a Level-0 Interrupt occurs.

When the NHALT Signal is subsequently driven to a high state, the Level-0 Interrupt servicing is initiated internally. Servicing consists of first setting the Level-0 Interrupt Enable (IR0 INT ENABLE in figure 2-10) low to lock out all other possible interrupts. Next, the contents of the PACE Program Counter are stored in the location specified by the contents of memory location 7 (see table 2-4). Then, the instruction at memory location 8 is executed. Storing the contents of the Program Counter in a memory location instead of on the Stack prevents generation of a Stack-full Interrupt.

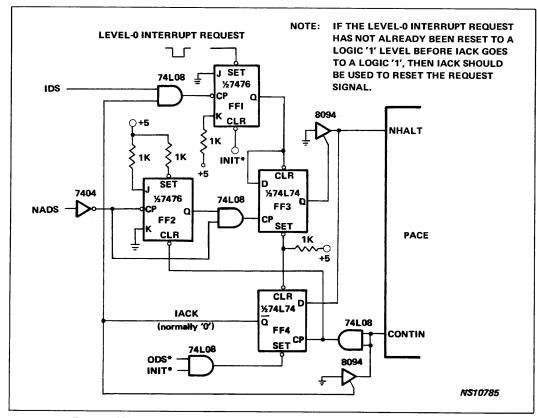

#### NOTE

If a Level-0 Interrupt occurs within the 12-clock-cycle period (excluding extend cycles) following the recognition (indicated by CONTIN signal) of any other interrupt, the processor either will stall or execute the level-0 interrupt using the wrong pointer address. This problem may be avoided by only allowing the level-0 interrupt leading edge to be applied to the PACE chip during an NADS, provided no interrupt acknowledge has occurred since the last NADS. Figure 2-13 shows one circuit that can be used to accomplish this. Note that the circuit has been designed to take care of proper 'level-0' execution only. If one desires to 'STALL' also, proper control gating will have to be added to the circuit.

To return from a Level-0 Interrupt, the PFLG15 or SFLG15 Instruction is executed to set the Level-0 Interrupt Enable Output high after execution of one additional instruction. The additional instruction is typically a JMP@ through the memory location to which the contents of memory location 7 point; memory

Figure 2-13. Circuit To Prevent Conflicts Between Level-0 and In-Process Interrupts

location 7 then restores the original contents of the Program Counter. Thus, a proper return to the interrupt program can be effected. For example, if memory location 7 contains X'1000, the PC contents are stored at memory location X'1000. To return from interrupt, a JMP@ X'1000 would be executed.

## 2.9 PACE INSTRUCTION SET

The PACE instruction set contains 45 instruction types that are capable of providing 337 individual instructions when flags, branch conditions, and other conditional signals or tests are considered. The 45 instruction types are divided into the following eight format groups:

- Branch Instructions

- Skip Instructions

- Memory Data-transfer Instructions (also serve as I/O instructions)

- Memory Data-operate Instructions

- Register Data-transfer Instructions

- Register Data-operate Instructions

- Shift and Rotate Instructions

- Miscellaneous Instructions

A summary of the PACE instructions is provided in table 2-5, which shows the instruction mnemonic, name, a symbolic representation of the instruction operation, and the instruction format. A more-detailed presentation of the instruction set is provided in appendix A.

There are no special PACE instructions for peripheral input/output. Instead, all of the memory-reference instructions can also be used with peripheral devices: this method provides a much wider variety of instructions for communications with peripherals.

#### 2.9.1 Data Representation

In the PACE microprocessor, data are represented in the twos-complement number system, in which the negative of a number is formed by complementing each bit and, then, adding one to the complemented value of the number. The most significant bit indicates the sign of the number: 0 for positive and 1 for negative. With a single 16-bit value, the greatest positive number is X'7FFF or  $32767_{10}$  and the most negative number is X'8000 or  $32768_{10}$ . When the 8-bit data length is selected, the largest positive number is X'7F or  $127_{10}$  and the most negative number is X'80 or  $128_{10}$ .

#### 2.9.2 Addressing Modes

Part of the power of the PACE microprocessor instruction set is derived from a flexible method of addressing used in memory-reference instructions (also used for peripheral devices). This method makes it possible to reference directly three 256-word 'pages' that may be located anywhere in memory, as well as another 256-word page in a fixed position in memory.

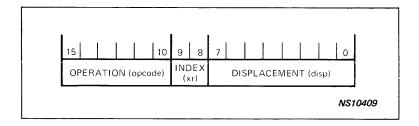

The fixed words form a 'base' page, and the others form three 'floating' pages. The mode of addressing is specified by the 2-bit XR field (bits 8 and 9) of the 16-bit instruction word, as shown in figure 2-14. The four available modes (base page, program-counter relative, AC2 relative, and AC3 relative) are summarized in table 2-6 and are described in the section that follows.

# Table 2-5. PACE Instruction Summary

|    | Mnemonic                                         | Name                                                                                                                                                                                                                       | Operation                                                                                                                                                                                                                                                                                                                                                                                              | Maximum Execution Time (Note)                                                                                                                                                                                               | Instruction Format                                                                                                                                                                            |