PORTIONS REPRODUCED WITH PERMISSION FROM NATIONAL SEMICONDUCTOR CORP.

## IPC-16A/500D-1 MOS/LSI single chip 16-bit microprocessor (PACE): general description

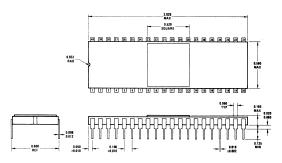

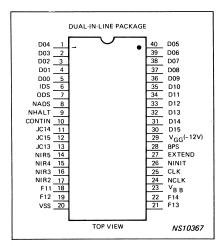

PACE (Processing And Control Element) is a single-chip. 16-bit microprocessor packaged in a standard, hermetically sealed, 40-pin ceramic dual-in-line package.

Silicon gate, P-channel enhancement mode standard process technology ensures high performance, high reliability and high producibility.

PACE is intended for use in applications where the convenience and efficiency of 16-bit word length is desired while maintaining the low cost inherent in single chip, fixed instruction microprocessors. The basic economics in conjunction with the users' ability to programmatically specify 8 or 16-bit data operations provides the following applications advantages:

(continued on page 3) Addressing flexibility,

Wide application

Allows software

compatibility

speed

#### features

■ 16-bit instruction word

word

Powerful instruction set

Common memory and peripheral addressing

Shares instructions with National's IMP-16 basic set 10-word stack

Six vectored priority

interrupt levels

Programmer accessible status register

2μs microcycle

Can utilize DM8531 1k-by-16 ROM

Two clock inputs

Four general purpose accumulators

data transfers Interrupt processing/

data storage Simplifies interrupt

Reduces memory

service and hardware May be preserved.

tested, or modified Fast instruction execution

> Single memory package Minimum external components

## applications

- Test system and instrument control

- Process controllers

- Machine tool control

- Terminal control

- Small business machines

- Traffic controllers Word processing systems

- Peripheral device controllers

- Educational systems

- Sophisticated games

- Distributed and multiprocessor systems

8 or 16-bit data

Efficient programming Powerful I/O

instructions

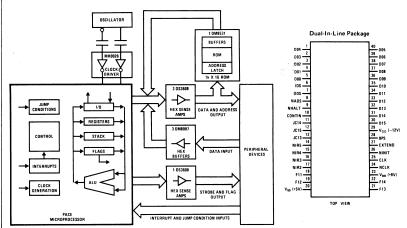

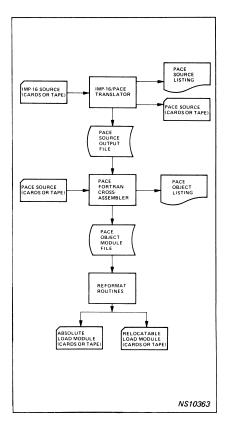

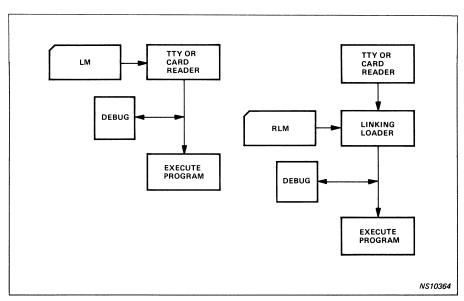

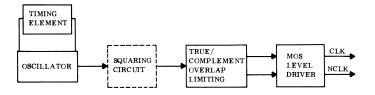

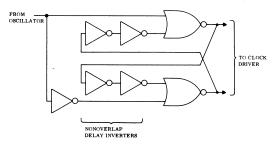

## block and connection diagrams

## PACE Specifications --- IPC-16A/500D-1

## ABSOLUTE MAXIMUM RATINGS (NOTE 1)

All Input or Output Voltages with Respect to

Most Positive Supply Voltage (VBB).....-0.3V to -20V

Operating Temperature Range.....+20°C to +45°C

Storage Temperature Range..... -65°C to +150°C Lead Temperature (soldering, 10 seconds).. +300°C

ELECTRICAL CHARACTERISTICS ( $T_A = +20$ °C to +45°C,  $V_{SS} = +5.14$   $\pm 2$ %,  $V_{GG} = -12.3$   $\pm 2$ %,  $V_{BB} = V_{SS} + 3V$ )

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CONDITIONS                                                                                                                                 | MIN                                  | TYP                                             | MAX                                                                 | UNITS                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------|

| OUTPUT SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                            |                                      |                                                 |                                                                     |                                                         |

| D00-D15, F11-F14, ODS, IDS, NADS (These are open drain outputs which may be used to drive DS3608 sense amps, or may be used with pull down resistors to provide a voltage output). Logic "1" Output Current (Note 7) Logic "0" Output Current NHALT, CONTIN Logic "1" Output Voltage Logic "0" Output Voltage                                                                                                                                                                                                                                                                             | V <sub>OUT</sub> = 2.0V<br>V <sub>G</sub> G ≼ V <sub>OUT</sub> ≤ V <sub>SS</sub><br>I <sub>OUT</sub> = 200 µa<br>I <sub>OUT</sub> = 200 µa | -0.8<br>VSS-1                        | -2.0                                            | -10<br>±10                                                          | mA<br>μA<br>V<br>V                                      |

| INPUT SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | *                                                                                                                                          |                                      | <b>L</b>                                        |                                                                     |                                                         |

| D00-D15, NIR2-NIR5, EXTEND, JC13-JC15, CONTIN, NINIT, NHALT (These are TTL compatible inputs.) (Note 2) Logic "1" Input Voltage Logic "0" Input Voltage Pullup Transistor "NON" Resistance (D00-D15) (Note 3) Pullup Transistor "NON" Resistance (except D00-D15) Logic "0" Input Current (D00-D15) Logic "0" Input Current (except D00-D15) Input Capacitance CLK, NCLK (These are MOS Clock Inputs.) Clock "1" Voltage (Note 5) Clock "1" Voltage Input Capacitance (Note 6) Bias Supply Current Average Power Dissipation                                                              | VIN = VSS - 1V<br>VIN = VSS - 1V<br>VIN = VSS - 1V<br>VIN = .4V<br>VIN = VSS,<br>fT = 500 kHz<br>VBB = VSS + 3.0V<br>tp=0.5 µs, TA 25°C    | VSS-1<br>VSS-1<br>VSS-1<br>VGG<br>30 | 4<br>2<br>-1.0<br>-2.0<br>10<br>80<br>30<br>700 | VSS+0.3<br>VSS-4.5<br>8<br>4<br>-3<br>-5<br>VSS+0.3<br>VGG+1<br>150 | V V kOhms kOhms mA pF V V pF pA mW                      |

| TIMING SPECIFICATIONS (SEE ADDITIONAL TIMING INFORMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TION FIGURES 7 T                                                                                                                           | HROUG                                | H 10)                                           | )                                                                   |                                                         |

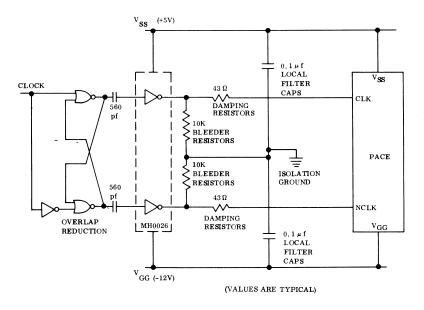

| CLK, NCLK (Referenced to 10% and 90% Amplitude) Rise and Fall Time (t <sub>r</sub> , t <sub>f</sub> ) Clock Width (t <sub>WCLK</sub> , t <sub>WNCLK</sub> ) Clock Overlap (tov A, tov B) Clock Period (tp) EXTEND Individual Extend Duration Propagation Delay F11-F14 (Note 8) NHALT, CONTIN (Note 9) NADS, 1DS, ODS, D00-D15 (Note 8) D00-D15 Input Setup Time (Note 10) NINIT Initialization Pulse Width NIR2-NIR5 Input Pulse Width to Set Latch                                                                                                                                      | V <sub>OUT</sub> = 2.0V<br>C <sub>L</sub> = 20 pF<br>V <sub>OUT</sub> = 2.0V                                                               | 10<br>220<br>0.5                     | 100<br>100<br>60<br>75                          | 25<br>-10<br>.55<br>1.0<br>300<br>200<br>100                        | ns ns ns ps ps ns ns ns ns ns clock cycles clock cycles |

| Note 1. Maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended and should be limited to those conditions specified under electrical characteristics.  Note 2. Pullup transistors provided on chip. (See figure 6.) Pullup transistors on JC13, JC14, JC15 are turned on one out of 8 clock intervals. Pullup transistors on D00-D15 are turned on during last clock period of Input Data Strobe (IDS). Other pullup transistors are on continuously when in data input mode.  Note 4. Pin 28 (BPS) is tied to VGG. |                                                                                                                                            |                                      |                                                 |                                                                     |                                                         |

Note 5.

Note 6.

Note 7. Note 8.

Clamp diodes and series damping resistors may be required to prevent clock overshoot. Clamp diodes and series damping resistors may be required to prevent clock overshoot. Capacitance is not constant and varies with clock voltage and internal state of processor. For VSsyNoury2.0 volts output current is a linear function of Vour. Delays measured from valid logic level on clock edge initiating change to valid current output level. Delay measured from valid logic level on clock edge initiating change to valid voltage output level. With respect to end of Input Data Strobe (IDS). (See figure 7.) Note 9.

Note 10.

## general description (con't)

PACE is particularly efficient when handling both 8 and 16-bit interfaces within the same microprocessor based system. Requirements for external hardware are minimized without sacrificing coding efficiency.

PACE is extremely cost effective in applications dominated by 8-bit data element interfaces. Coding and address generation efficiencies, as well as operating speeds for double precision operations found only in 16-bit microprocessors are extended to the 8-bit system.

The principal resources featured in PACE to minimize system program and read/write storage while increasing throughput include:

FOUR 16-BIT GENERAL PURPOSE WORKING REGISTERS available to the user reduce the number of memory load and store operations associated with saving temporary and intermediate results in system memory. This results in increased throughput with reduced program and data storage requirements.

AN INDEPENDENT 16-BIT STATUS AND CONTROL FLAG REGISTER automatically and continuously preserves system status. The user may operate on its contents as data, allowing masking, testing and modification of several bit fields simultaneously.

A TEN WORD (16-BIT) LAST-IN, FIRST-OUT (LIFO) STACK automatically preserves return addresses during interrupts revicing and sub-routine execution. The presence of a stack inherently decreases response time to interrupts while eliminating both program and read/write system storage overhead associated with storing stack information outside the microprocessor chip. In some applications the 10-word stack plus on-chip registers can totally eliminate the need for off-chip read/write memory.

STACK FULL/STACK EMPTY interrupts are provided to facilitate off-chip stack storage in those applications where additional stack capacity is desirable.

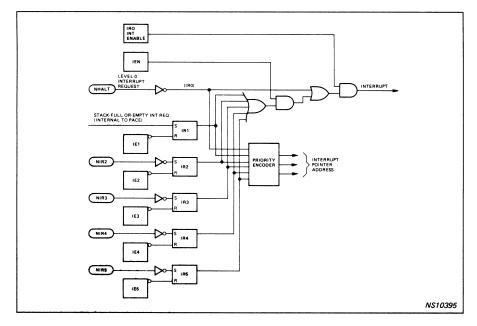

A SIX LEVEL, VECTORED PRIORITY INTERRUPT SYSTEM internal to the chip provides automatic interrupt identification, eliminating both program storage overhead and the time normally required to poll peripherals in order to identify the interrupting device. When more than six interrupts are involved, more than one peripheral may be placed on a priority-level by means of a simple open collector connection to the appropriate priority interrupt request line.

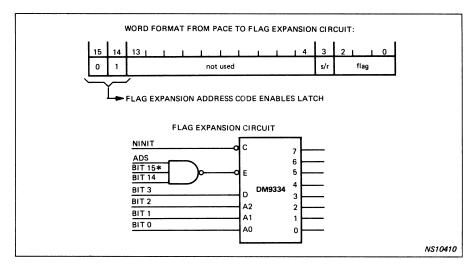

FOUR SENSE INPUTS AND FOUR CONTROL FLAG OUTPUTS allow the user to respond directly to specific combinations of status present in the microprocessor based system. This ability to respond directly to system status requires no external hardware and allows appriate control signal outputs to be generated programmatically, eliminating costly hardware, program overhead and throughput associated with implementing these functions over the system data bus.

Other PACE features which minimize the cost of external support hardware include easily generated clock inputs and I/O cycle extend capability.

The PACE single chip 16-bit microprocessor permits the implementation of a complete microprocessor system with 16,384 bits of read-only program storage and TTL data bus interface in fewer than a dozen standard support packages, as shown in the diagram on the first page.

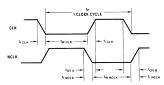

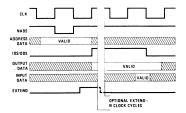

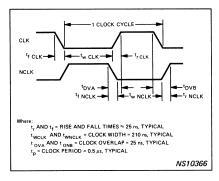

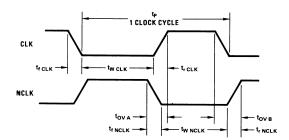

Note: Clock timing referenced to 10% and 90% amplitude points

FIGURE 1, Clock Timing

#### **FUNCTIONAL DESCRIPTION**

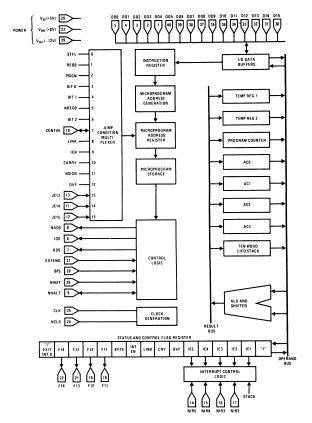

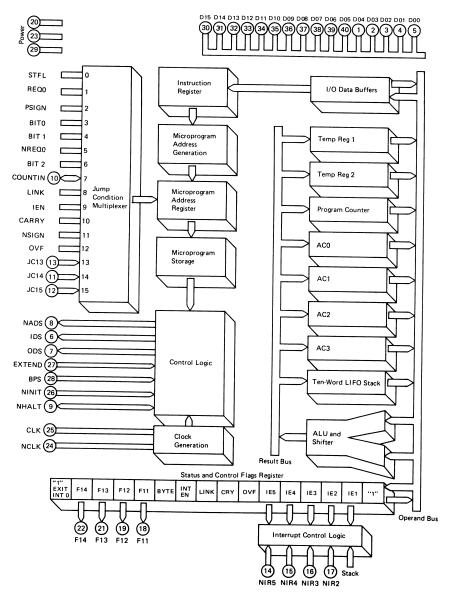

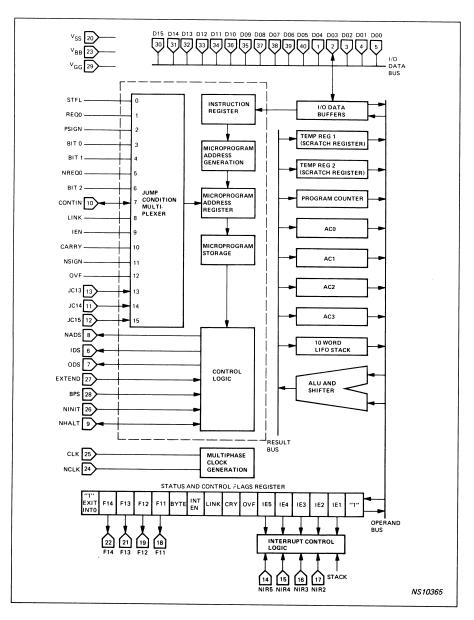

The PACE microprocessor, shown in Figure 2, provides 16-bit parallel data processing capability. This word length provides considerable convenience for addressing memory and peripheral devices and provides sufficient accuracy that many applications will not require the use of double precision arithmetic. It also provides increased speed by processing twice as many bits per cycle and reducing time consuming memory accesses. However, for those applications not requiring high accuracy, or for character processing, PACE provides the ability to operate on 8-bit data, while still providing 16-bit instructions and addressing capability.

#### Data Storage

Seven data registers are provided, four of which are directly available to the programmer (as accumulators ACO to AC3) for data storage and address formation. ACO is the principal working register, AC1 is the secondary working register, and AC2 and AC3 are page pointers or auxiliary data registers. The other three registers serve as a program counter and two temporary registers are used by the control section to effect the PACE instruction set.

Additional data storage is provided for up to ten words by a last-in, first-out or push-pull stack. The stack is used primarily for storing the contents of the program counter during subroutine execution and interrupt servicing. The stack may also be used for storing status information or data; in some applications, such as device controllers, the stack plus four accumulators may provide enough storage to eliminate the need for external read-write memory. For applications where the 10-word capacity of the stack is insufficient, external read-write memory may be used as a stack extension. This is facilitated by the provision of stack full and stack empty interrupts, allowing implementation of a simple stack service routine.

FIGURE 2. PACE Detailed Block Diagram

#### ALU

The arithmetic and logic unit (ALU) provides the data manipulation capability which is an essential feature of any microprocessor. The operations provided by the ALU include AND, OR, XOR, complement, shift left, shift right, mask byte and sign extend. Both binary and (4-digit per word) binary-coded-decimal (BCD) addition capability are provided, thus eliminating the program storage and execution time required to perform BCD to binary conversion.

A unique feature of the PACE ALU is the ability to operate on either 8 or 16-bit data, as specified by the programmer through the use of a status flag. This feature allows character oriented and other 8-bit applications to

be implemented and executed using an 8-bit peripheral data bus and read-write memory, while address formation and instruction storage are implemented in the more effective 16-bit data length.

#### Status

All status and control bits for PACE are provided in a single status flag register, whose contents may be loaded from or to any accumulator or the stack. This allows convenient testing, masking and storage of status. In addition, a number of status bits may be tested directly by the conditional branch instruction, and any bit may be individually set or reset. The function of each bit in the status flag register is listed in Table I and described

briefly below. The carry flag is set to the state of the carry output resulting from binary and BCD arithmetic instructions, and serves as a carry input for some of these instructions. The overflow flag is set true if an arithmetic overflow results from a binary arithmetic instruction.

TABLE I. Status Flag Register Bit Functions

| Register Bit | Flag Name | Function                                       |  |

|--------------|-----------|------------------------------------------------|--|

| 0            | "1"       | Not used-always logic 1                        |  |

| 1            | IE1       | Interrupt Enable Level 1                       |  |

| 2            | IE2       | Interrupt Enable Level 2                       |  |

| 3            | IE3       | Interrupt Enable Level 3                       |  |

| 4            | IE4       | Interrupt Enable Level 4                       |  |

| 5            | IE5       | Interrupt Enable Level 5                       |  |

| 6            | OVF       | Overflow                                       |  |

| 7            | CRY       | Carry                                          |  |

| 8            | LINK      | Link                                           |  |

| 9            | IEN       | Master Interrupt Enable                        |  |

| 10           | BYTE      | 8-bit data length                              |  |

| 11           | F11       | Flag 11                                        |  |

| 12           | F12       | Flag 12                                        |  |

| 13           | F13       | Flag 13                                        |  |

| 14           | F14       | Flag 14                                        |  |

| 15           | "1"       | Always logic 1, addressed for Interrupt 0 exit |  |

The link flag serves as a 1-bit extension for certain shift and rotate instructions. The byte flag is used to specify an 8-bit data length for data processing instructions, while arithmetic operations for address formation remain at the 16-bit data length. In the 8-bit data mode, modifications of the carry, overflow and link flag are based on the eight least significant data bits only.

Four flags (bits 10—14) are provided which may be assigned functions by the programmer. These flags drive output pins and may be used to directly control system functions or as software status flags. Bits 0 and 15 of the status register have not been implemented in hardware and always appear as a logic 1. The interrupt enable flags are explained below.

#### Control

The operation of the PACE microprocessor consists of repeatedly accessing or fetching instructions from the external program store and executing the operations specified by these instructions. These two steps are carried out under the control of a microprogram (the microprocessor is not designed for user microprogramming). The microprogram is similar to a state table specifying the series of states of system control signals necessary to carry out each instruction. Microprogram storage is provided by a programmable logic array, and microprogram routines are implemented to fetch and execute instructions. The fetch routine causes an instruction address to be transferred from the program counter register to the I/O bus and initiates an input data operation. When the instruction is provided on the data bus, the fetch routine causes it to be loaded into the instruction register. The instruction operation code is transformed into the address of the appropriate

instruction-execution routine by the address generation logic. As the last step of the fetch routine, this address is loaded into the microprogram address register, causing a branch to the appropriate instruction execution routine. The execution routine consists of one or more microinstructions to implement the functions required by the instruction. For example, the routine for a register ADD instruction would access the two accumulators to be added over the operand bus, cause the ALU to perform an ADD operation, load the carry and overflow flags from the ALU and store the result in the specified accumulator. The control logic interprets the microinstructions to carry out these operations. The final step of the execution routine is a jump back to the fetch routine to access the next instruction. Each microcycle requires 2us and 4 or 5 microcycles are typically required to fetch and execute a machine instruction Other routines implemented by the microprogram include interrupt servicing and system initialization. The microprogram controls the operation of a conditional jump multiplexer which is used to specify 16 conditions for the conditional branch instruction. The conditions which may be tested are indicated in Table II and include four signal inputs to the chip, which may be used to test external system conditions.

TABLE II. Branch Conditions

| Number | Mnemonic | Condition                              |

|--------|----------|----------------------------------------|

| 0      | STFL     | Stack full                             |

| 1      | REQ0     | (AC0) equal to zero <sup>(1)</sup>     |

| 2      | PSIGN    | (ACO) has positive sign <sup>(2)</sup> |

| 3      | BIT 0    | Bit 0 of AC0 true                      |

| 4      | BIT 1    | Bit 1 of AC0 true                      |

| 5      | NREQ0    | (AC0) is non-zero <sup>(1)</sup>       |

| 6      | BIT 2    | Bit 2 of AC0 is true                   |

| 7      | CONTIN   | CONTIN (continue) input is true        |

| 8      | LINK     | LINK is true                           |

| 9      | IEN      | IEN is true                            |

| 10     | CARRY    | CARRY is true                          |

| 11     | NSIGN    | (ACO) has negative sign <sup>(2)</sup> |

| 12     | OVF      | OVF is true                            |

| 13     | JC13     | JC13 input is true                     |

| 14     | JC14     | JC14 input is true                     |

| 15     | JC15     | JC15 input is true                     |

Note 1: If the selected data length is 8 bits, only bits 0-7 of ACO are tested.

Note 2: Bit 7 is the sign bit (instead of bit 15) if the selected data length is 8 bits

The control circuitry may be initialized at any time by use of the NINIT input signal. This will cause the stack addressing circuitry, all flags and the program counter to be set to zero, and the strobes to go false and level zero interrupt enable to go true. This signal should always be used to initialize the processor after applying power. The first instruction after initialization is accessed from location zero.

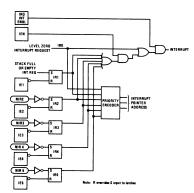

#### Interrupts

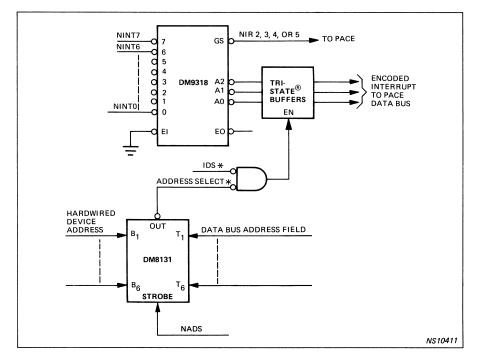

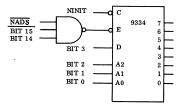

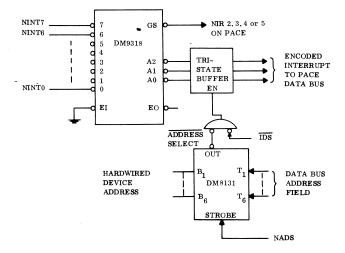

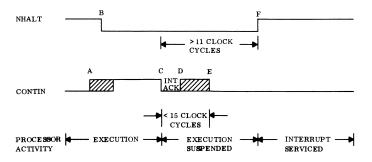

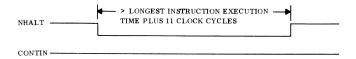

The PACE microprocessor provides a six level, vectored, priority interrupt structure. This allows automatic identification of an interrupting device's level and allows all devices on an interrupt level to be enabled or disabled as a group, independent of other interrupt levels. An individual interrupt enable is provided in the status register for each level, as shown in Figure 3, and a master

FIGURE 3. Interrupt System

interrupt enable (IEN) is provided for all 5 lower priority levels as a group. Negative true interrupt request inputs are provided to allow several interrupts to be "wire-ORed" on each input. When an interrupt request occurs, it will set the interrupt request latch if the corresponding interrupt enable is true. The latch will be set by any pulse exceeding one clock period in duration, which is useful for capturing narrow timing or control pulses. If the master interrupt enable (IEN) is true, then an interrupt will be generated. During the interrupt sequence an address is provided by the output of the priority encoder and is used to access the pointer for the highest-priority interrupt request (IRO is highest priority, IR5 is lowest priority). The pointers are stored in locations 2-7 (see Table III) for interrupt requests 1-5 and 0, respectively. The pointer specifies the starting address of the interrupt service routine for that particular interrupt level. Before executing the interrupt service routine, the program counter is pushed on the stack and IEN is set false. The interrupt service routine may set IEN true after turning off the interrupt enable for the level currently being serviced (or resetting the interrupt request). (The interrupt enables may be set and reset using the SFLG and PFLG instructions.)

The non-maskable level zero interrupt (IRO) is an exception to this interrupt procedure. It has a program counter storage location pointer (the program counter is not stored on the stack for this particular interrupt in order to preserve the processor state) which is followed by the level zero interrupt service routine. The IRO interrupt enable is cleared when a level zero interrupt

TABLE III. Interrupt Pointer Table

| Int 0 Program       |  |  |

|---------------------|--|--|

| Int 0 PC Pointer    |  |  |

| Int 5 Pointer       |  |  |

| Int 4 Pointer       |  |  |

| Int 3 Pointer       |  |  |

| Int 2 Pointer       |  |  |

| Int 1 Pointer       |  |  |

| Not Assigned        |  |  |

| Initialization Inst |  |  |

|                     |  |  |

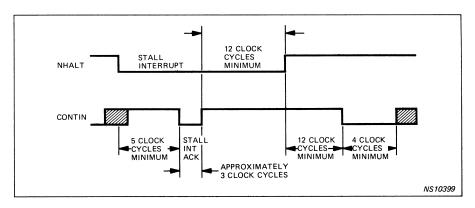

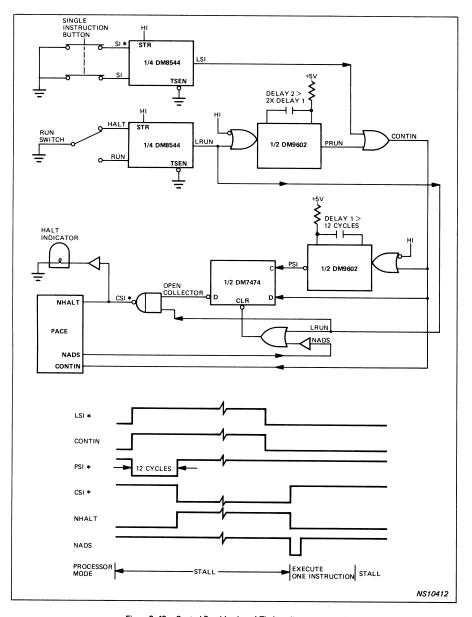

occurs (IEN is unaffected) and may be set true by addressing (non-existent) status flag 15. This allows execution of one more instruction (typically JMP®) to return from the IRO interrupt routine before another interrupt will be acknowledged. This interrupt level is typically used by the control panel, which then can always interrupt the application program and does not affect system status. The control panel service routine interprets and executes the functions specified by control panel switches and displays selected data on the panel lights. Level zero interrupts are generated by driving the NHALT signal line low.

#### Data Input and Output

All data transfers between PACE and external memories or peripheral devices take place over the 16 data lines (D00-D15) and are synchronized by the 4 control signals (NADS, IDS, ODS, and EXTEND). Data transfers occur during each instruction access and during the data accesses required by memory reference instructions. This class of instructions could perhaps more properly be called the "I/O reference class" in the case of the PACE microprocessor, since all data transfers, whether with memory or peripheral devices or a central processor data bus, occur through the execution of these instructions. This unified bus architecture is in contrast with many other microprocessors and minicomputers that have one instruction type (I/O class) for communication with peripheral devices and another instruction type (memory reference class) for communication with memories. The advantage of the approach used by PACE is that a wider variety of instructions (the entire memory reference class) is available for communication with peripherals. Thus, the DSZ (decrement and skip if zero) instruction can be used to decrement a peripheral device register, or the SKAZ (skip if AND is zero) instruction can be used to test the contents of a peripheral device status register. The LD (load) and ST (store) instructions are used for simple data transfers.

All I/O transactions consist of an address output interval followed by a data transfer interval. The address specifies a memory location or peripheral device. The allocation is entirely up to the user (within the requirements for interrupt pointers). A straightforward allocation would be to assign all addresses from 0000<sub>16</sub> to 7FFF<sub>16</sub> as memory addresses and all addresses from 8000<sub>16</sub> to FFFF<sub>16</sub> as peripheral device addresses. In this case, the most significant address bit specifies whether the transaction is with memory or a peripheral device. A variety of easily decoded address allocation schemes may be used, depending on the amount of ROM, RAM, peripheral devices and the particular application. Both address and data words are transmitted or received as 16-bit parallel data over the data lines (D00-D15). If 8-bit data is being transferred, the unused bits can be treated as "don't care" bits by the hardware and the 8-bit data length selected by the software.

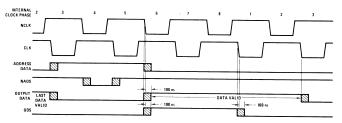

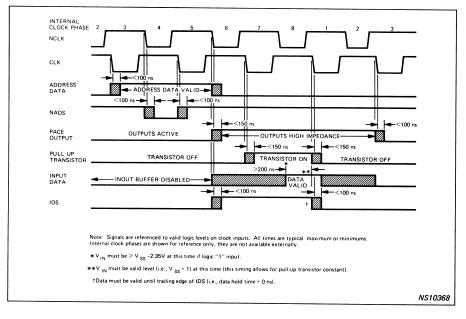

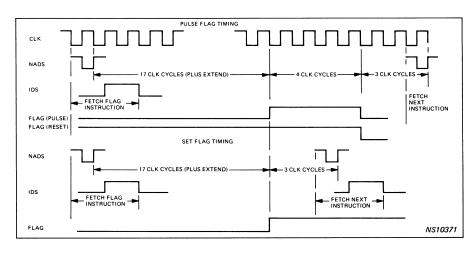

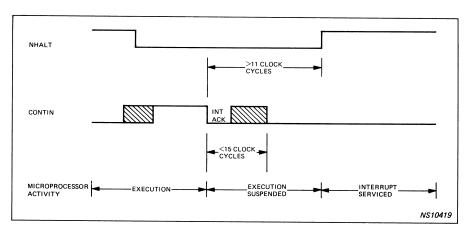

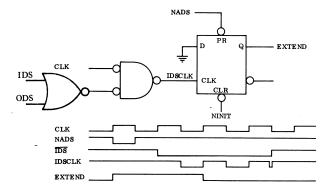

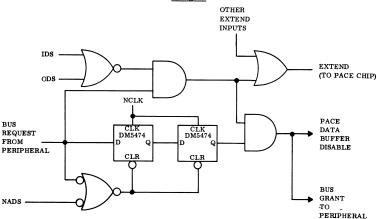

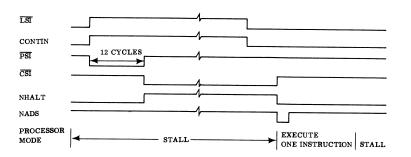

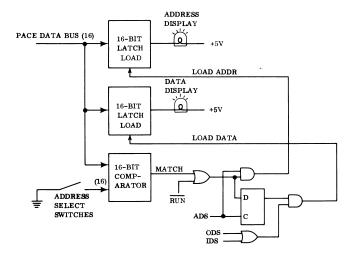

Data transfer operations are synchronized by the NADS (Address Data Strobe), IDS (Input Data Strobe), ODS (Output Data Strobe) and EXTEND signals as shown in Figure 4. Address data is provided on the 16 data lines. An NADS is provided in the center of the address data and may be used to strobe the address into an address latch. A number of memory products provide address

FIGURE 4. PACE I/O Timing

latches on the chip, which avoids the need for implementing this function externally. The input data strobe and output data strobe indicate the type of data transfer and may be used to enable TRI-STATE® I/O buffers and gate data into registers or memories as required by the system design. The EXTEND input allows the I/O cycle time to be extended by multiples of the clock cycle to adapt to a variety of memory and peripheral devices or for DMA bus interfacing.

#### INSTRUCTIONS

The PACE microprocessor provides a general-purpose mix of 45 instruction types. The memory reference instructions utilize a flexible memory addressing scheme providing three floating memory pages and one fixed page of 256 words each. The register instructions provide convenient data manipulation without requiring a memory access. The data transfer instructions provide a means of moving data among the functional blocks of the microprocessor system.

## **Addressing Modes**

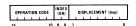

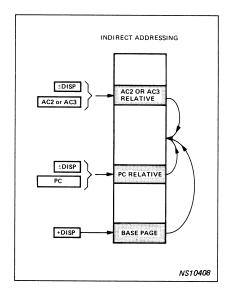

Instructions which use both direct and indirect memory addressing are included in the PACE instruction set. Three modes of direct memory addressing are available: base page, program counter relative, and index register relative. The mode of addressing is specified by the XR field of the instruction as illustrated in Figure 5.

FIGURE 5. Memory Reference Instruction Format

When the XR field is 00, base page (page zero) addressing is used. Two different types of base page addressing are available and may be selected by the base-page-select (BPS) signal input. If BPS = 0, the 16-bit memory address is formed by setting bits 8 through 15 to zero, and using the 8-bit displacement (disp) for bits 0 through 7; this permits addressing of the first 256 worst of memory (locations 0-255). If BPS = 1, the 16-bit memory address is formed by setting bits 8 through 15 equal to bit 7 of disp and using disp for bits 0 through FT his permits addressing the first 128 words (0 hrough FFF pg) of memory. The latter technique is useful for splitting the base page between read-write and read-only memories

or between memory and peripheral devices, so the convenience of base page addressing is available for accessing data or peripherals.

Addressing relative to the program counter (PC) is specified when the XR field is 01. With this mode, the memory address is formed by adding the contents of the program counter to the value of the displacement field interpreted as a signed two's complement number (that is, the 8-bit disp field is interpreted as a 16-bit value with bits 8 through 15 set equal to bit 7; this allows representation of numbers from -128 through +127). When the address is formed, the program counter has already been incremented and contains a value one greater than the location of the current instruction; thus, memory addresses that may be referenced as 127 locations below through 128 above the address of the current instruction.

With the index register relative mode of addressing, any memory location within the 65,536 word address space may be referenced. The disp field is interpreted as a signed value ranging from -128 through 127 as with PC relative addressing. The memory address is formed by adding disp to the contents of either accumulator AC2 (when XR = 10) or accumulator AC3 (when XR = 11).

This type of addressing is very desirable for microprocessor applications which require address computation at execution time, since the use of read-only-memory for program storage prevents address modification within the program storage memory. A summary of the direct addressing modes is presented in Table IV.

TABLE IV. Summary of Addressing Modes

| XR Field | Addressing Mode          | Effective Address |

|----------|--------------------------|-------------------|

| 00       | Base Page                | EA - disp         |

| 01       | Program Counter Relative | EA = disp + (PC)  |

| 10       | AC2 Relative (indexed)   | EA = disp + (AC2) |

| 11       | AC3 Relative (indexed)   | EA = disp + (AC3) |

Note 1: For base page addressing, disp is positive and in the range of 000 to 255 if BPS = 0, and is a signed number in the range of 128 to +127 if BPS = 1.

Note 2: For relative addressing, disp has a range of 128 to +127.

Indirect addressing consists of first establishing an address in the same fashion as with direct addressing [by either the base page, relative to PC, or indexed (relative to AC2 or AC3) mode]. The 16-bit contents of the memory location at this address is then used as the address of the operand, allowing any memory location to be addressed.

As noted previously, the memory addressing modes are also used for peripheral I/O operations. The address space must be divided between read-write memory, read-only memory and I/O devices.

#### Instruction Summary

The instruction set is divided into eight instruction classes as listed in Table V. The branch instructions provide the means to transfer control anywhere in the 16-bit addressing space. Conditional branches are effected using the BOC instruction, which allows testing any one of 16 conditions, including status flags, the contents of ACO, and user inputs to the chip. Additional testing capability is provided by the skip instructions, which provide memory or peripheral to register comparisons

#### TABLE V. PACE Instruction Summary

|    | Mnemonic                                                                    | Meaning                                                                                                                                                                                                                                                                      | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Assembler Format                                                                                                                                                                            | Instruction Format                                                                                                                                                                                           |

|----|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | 1. Branch Instructions                                                      |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                             |                                                                                                                                                                                                              |

|    | BOC<br>JMP<br>JMP@<br>JSR<br>JSR@<br>RTS<br>RTI                             | Branch On Condition Jump Jump Indirect Jump To Subroutine Jump To Subroutine Indirect Return from Subroutine Return from Interrupt                                                                                                                                           | (PC) ← (PC) + disp if c true<br>(PC) ← EA<br>(PC) ← EA<br>(STK) ← (PC), (PC) ← EA<br>(STK) ← (PC), (PC) ← (EA)<br>(PC) ← (STK) + disp, (EN = 1                                                                                                                                                                                                                                                                                                                                                    | BOC cc,disp JMP disp (xr) JMP @disp (xr) JSR disp (xr) JSR @disp (xr) RTS disp RTI disp                                                                                                     | 0 1 0 0 0 cc disp<br>0 0 0 1 1 1 0 xr disp<br>1 0 0 1 0 1 0 1 0<br>0 0 0 1 0 1 1<br>1 0 0 1 0 1                                                                                                              |

| 2. | Skip Instruct                                                               |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                             |                                                                                                                                                                                                              |

|    | SKNE<br>SKG<br>SKAZ<br>ISZ<br>DSZ<br>AISZ                                   | Skip if Not Equal<br>Skip if Greater<br>Skip if And is Zero<br>Increment and Skip if Zero<br>Decrement and Skip if Zero<br>Add Immediate, Skip if Zero                                                                                                                       | $\begin{split} &\text{If }(ACr) \neq (EA),  PC  \leftarrow  PC  + 1 \\ &\text{If }(AC0) > (EA),  PC  \leftarrow  PC  + 1 \\ &\text{If }  (AC0) > (EA),  PC  \leftarrow  PC  + 1 \\ &\text{If }  (AC0) > (EA)  = 0,  PC  \leftarrow  PC  + 1 \\ &\text{(EA)} \leftarrow  EA  + 1,  f(EA)  = 0,  PC  \leftarrow  PC  + 1 \\ &\text{(EA)} \leftarrow  EA  - 1,  f(EA)  = 0,  PC  \leftarrow  PC  + 1 \\ &\text{(ACr)} \leftarrow  ACr  +  Asp_i   f(ACr)  = 0,  PC  \leftarrow  PC  + 1 \end{split}$ | SKNE         r,disp (xr)           SKG         0,disp (xr)           SKAZ         0,disp (xr)           ISZ         disp (xr)           DSZ         disp (xr)           AISZ         r,disp | 1 1 1 1 1 r xr disp<br>1 0 0 1 1 1 1<br>1 0 0 0 1 1 1<br>1 0 1 0 1 0 1<br>1 0 1 0 1 1 1<br>0 1 1 1 1 1 0 r                                                                                                   |

| 3. | Memory Data                                                                 | Transfer Instructions                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                             |                                                                                                                                                                                                              |

|    | LD<br>LD@<br>ST<br>ST@<br>LSEX                                              | Load<br>Load Indirect<br>Store<br>Store Indirect<br>Load With Sign Extended                                                                                                                                                                                                  | (ACr) ← (EA)<br>(AC0) ← ((EA))<br>(EA) ← (ACr)<br>((EA)) ← (AC0)<br>(AC0) ← (EA) bit 7 extended                                                                                                                                                                                                                                                                                                                                                                                                   | LD r,disp (xr) LD 0,@disp (xr) ST r,disp (xr) ST 0,@disp (xr) LSEX 0,disp (xr)                                                                                                              | 1 1 0 0 r xr disp<br>1 0 1 0 0 0<br>1 1 0 1 r r<br>1 0 1 1 0 0<br>1 1 0 1 1 1 1                                                                                                                              |

| 4. | Memory Data                                                                 | Operate Instructions                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                             |                                                                                                                                                                                                              |

|    | AND<br>OR<br>ADD<br>SUBB<br>DECA                                            | And<br>Or<br>Add<br>Subtract with Borrow<br>Decimal Add                                                                                                                                                                                                                      | $ \begin{array}{lll} (AC0) & \leftarrow (AC0) \land (EA) \\ (AC0) & \leftarrow (AC0) \lor (EA) \\ (AC1) & \leftarrow (AC1) + (EA), OV, CY \\ (AC0) & \leftarrow (AC0) + \sim (EA) + (CY), OV, CY \\ (AC0) & \leftarrow (AC0) + _{10} (EA) + _{10} (CY), OV, CY \\ \end{array} $                                                                                                                                                                                                                   | AND 0,disp (xr) OR 0,disp (xr) ADD r,disp (xr) SUBB 0,disp (xr) DECA 0,disp (xr)                                                                                                            | 1 0 1 0 1 0 1 0 xr disp<br>1 0 1 0 0 1 1<br>1 1 1 0 r<br>1 0 0 1 0 0<br>1 0 0 0 1 0                                                                                                                          |

| 5. | Register Data                                                               | Transfer Instructions                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                             |                                                                                                                                                                                                              |

|    | LI<br>RCPY<br>RXCH<br>XCHRS<br>CFR<br>CRF<br>PUSH<br>PULL<br>PUSHF<br>PULLF | Load Immediate Register Copy Register Exchange Exchange Register and Stack Copy Flags Into Register Copy Register Into Register Copy Register Into Flags Push Register Onto Stack Pull Stack Into Register Push Flags Noto Stack Pull Stack Into Flags Pull Stack Into Flags | $\begin{split} (ACr) &= dsp \\ (ACdr) &= (ACsr) \\ (ACdr) &= (ACsr) \\ (ACdr) &= (ACsr) \\ (STK) &= (ACr), (ACr) &= (STK) \\ (ACr) &= (FR) \\ (FR) &= (ACr) \\ (STK) &= (FR) \\ (FR) &= (STK) \\ (FR) &= (STK) \\ \end{split}$                                                                                                                                                                                            | LI r,disp RCPY sr,dr RXCH sr,dr XCHRS r CFR r CRF r PUSH r PULL r PULLF                                                                                                                     | 0 1 0 1 0 0 0 disp<br>0 1 0 1 1 1 dr sr not used<br>0 1 0 0 1 1 1 r not used<br>0 0 0 0 1 1 0 0<br>0 1 1 0 0 1 0<br>0 0 0 0 0 1<br>0 1 1 0 0 0<br>0 0 0 0 1 0 0 |

| 6. | Register Data                                                               | Operate Instructions                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                             |                                                                                                                                                                                                              |

|    | RADD<br>RADC<br>RAND<br>RXOR<br>CAI                                         | Register Add<br>Register Add With Carry<br>Register And<br>Register Exclusive OR<br>Complement and Add Immediate                                                                                                                                                             | $ \begin{array}{ll} (ACdr) & \leftarrow (ACdr) + (ACsr),  OV,  CY \\ (ACdr) & \leftarrow (ACdr) + (ACsr) + (CY),  OV,  CY \\ (ACdr) & \leftarrow (ACdr) \wedge (ACsr) \\ (ACdr) & \leftarrow (ACdr) & \leftarrow (ACdr) \\ (ACdr) & \leftarrow (ACdr) & \leftarrow (ACdr) \\ (ACdr) & \leftarrow (ACdr) + disp \\ \end{array} $                                                                                                                                                                   | RADD sr,dr<br>RADC sr,dr<br>RAND sr,dr<br>RXOR sr,dr<br>CAI r,disp                                                                                                                          | 0 1 1 0 1 0 dr sr not used 0 1 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 1 1                                                                                                                                     |

| 7. | Shift And Ro                                                                | tate Instructions                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                             |                                                                                                                                                                                                              |

|    | SHL<br>SHR<br>ROL<br>ROR                                                    | Shift Left<br>Shift Right<br>Rotate Left<br>Rotate Right                                                                                                                                                                                                                     | $ \begin{aligned} & (ACr) \; \leftarrow \; (ACr) \; \text{shifted left n places, w/wo link} \\ & (ACr) \; \leftarrow \; (ACr) \; \text{shifted right n places, w/wo link} \\ & (ACr) \; \leftarrow \; (ACr) \; \text{rotated left n places, w/wo link} \\ & (ACr) \; \sim \; (ACr) \; \text{rotated right n places, w/wo link} \end{aligned} $                                                                                                                                                    | SHL r,n,ℓ<br>SHR r,n,ℓ<br>ROL r,n,ℓ<br>ROR r,n,ℓ                                                                                                                                            | 0 0 1 0 1 0 r n V<br>0 0 1 0 1 1 1<br>0 0 1 0 0 0<br>0 0 1 0 0 1                                                                                                                                             |

| 8. | Miscellaneous                                                               |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                             |                                                                                                                                                                                                              |

|    | HALT<br>SFLG<br>PFLG                                                        | Halt<br>Set Flag<br>Pulse Flag                                                                                                                                                                                                                                               | Halt $(FR)_{fc} \leftarrow 1$ $(FR)_{fc} \leftarrow 1$ , $(FR)_{fc} \leftarrow 0$                                                                                                                                                                                                                                                                                                                                                                                                                 | HALT<br>SFLG to<br>PFLG to                                                                                                                                                                  | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                        |

without altering data. The memory data transfer instructions provide data transfers between the accumulators and memory or peripheral devices. The load with sign extended is provided to convert 8-bit, two's complement data to 16-bit data, allowing 16-bit address modification when the 8-bit data length has been selected.

The memory data operate instructions provide operations between the principal working register (ACO) and memory or peripheral data. This includes both binary and BCD arithmetic instructions. The register data transfer instructions provide a very complete set of transfer possibilities between the accumulators, flag register and stack, and include the capability to load immediate data. Register data operate instructions provide logical and arithmetic operations between any two

accumulators. They may be used for address and data modification and to reduce the number of (time consuming) memory references in a program. The shift and rotate instructions allow 8 different operations which are useful for multiply, divide, bit scanning and serial input-output operations. The miscellaneous instructions include the capability to set or reset (pulse) any of the 16 bits of the status flag register individually. Instruction execution times are shown in Table VI.

A simple example program is provided by the binary multiply routine shown on page 9. This program multiplies the 16-bit value in AC2 by the 16-bit value in AC1 and provides a 32-bit result in AC0 (high order) and AC1 (low order). Worst case execution time is under one millisecond.

#### Binary Multiply Routine

| CONST: | .WORD           | X'FFFF                           | ; CONSTANT FOR DOUBLE PREC. ADD                                                                |

|--------|-----------------|----------------------------------|------------------------------------------------------------------------------------------------|

| START: | LI<br>LI<br>Cai | R1, 0<br>R3, 16<br>R0, 0         | ; CLEAR RESULT REGISTER<br>; LOOP COUNT TO AC3<br>; COMPLEMENT MULTIPLIER                      |

| LOOP:  | RADD<br>RADC    | R1, R1<br>R0,R0                  | : SHIFT RESULT LEFT INTO CARRY<br>: SHIFT CARRY INTO MULTIPLIER<br>: AND MULTIPLIER INTO CARRY |

|        |                 | RRY, TEST<br>R2, R1<br>R0, CONST | ; TEST FOR ADD<br>; ADD MULTIPLICAND TO RESULT<br>; ADD CARRY TO H.O. RESULT                   |

| TEST:  | AISZ<br>JMP LC  | R3, -1<br>IOP                    | ; DECREMENT LOOP COUNT<br>; REPEAT LOOP                                                        |

|        |                 |                                  |                                                                                                |

#### TABLE VI. Instruction Execution Times

|    | Mnemor | nic Meaning                 | Execution Time                     |

|----|--------|-----------------------------|------------------------------------|

| 1. | Branch | Instructions                |                                    |

|    | вос    | Branch On Condition         | 5M + E <sub>R</sub> + 1M if branch |

|    | JMP    | Jump                        | 4M + E <sub>B</sub>                |

|    | JMP@   | Jump Indirect               | 4M + 2E <sub>B</sub>               |

|    | JSR    | Jump To Subroutine          | 5M + E <sub>B</sub>                |

|    | JSR@   | Jump To Subroutine Indirect | 5M + 2E <sub>B</sub>               |

|    | RTS    | Return from Subroutine      | 5M + E <sub>B</sub>                |

|    | RTI    | Return from Interrupt       | 6M + E <sub>0</sub>                |

#### 2. Skip Instructions

| SKNE | Skip if Not Equal           | 5M + 2E <sub>R</sub> + 1M if skip                  |

|------|-----------------------------|----------------------------------------------------|

| SKG  | Skip if Greater             | 7M + 2E <sub>R</sub> + 1M if skip                  |

| SKAZ | Skip if And is Zero         | 5M + 2E <sub>R</sub> + 1M if skip                  |

| ISZ  | Increment and Skip if Zero  | 7M + 2E <sub>R</sub> + E <sub>W</sub> + 1M if skip |

| DSZ  | Decrement and Skip if Zero  | 7M + 2E <sub>R</sub> + E <sub>W</sub> + 1M if skip |

| AISZ | Add Immediate, Skip if Zero | 5M + E <sub>R</sub> + 1M if skip                   |

## 3. Memory Data Transfer Instructions

| LD   | Load                    | 4M + 2E <sub>B</sub>                  |

|------|-------------------------|---------------------------------------|

| LD@  | Load Indirect           | 5M + 3E <sub>B</sub>                  |

| ST   | Store                   | 4M + E <sub>R</sub> + E <sub>W</sub>  |

| ST@  | Store Indirect          | 4M + 2E <sub>B</sub> + E <sub>W</sub> |

| LSEX | Load With Sign Extended | 4M + 2En                              |

## 4. Memory Data Operate Instructions

| AND  | And                  | 4M + 2E <sub>R</sub> |

|------|----------------------|----------------------|

| OR   | Or                   | 4M + 2E <sub>B</sub> |

| ADD  | Add                  | 4M + 2E <sub>B</sub> |

| SUBB | Subtract With Borrow | 4M + 2E <sub>B</sub> |

| DECA | Decimal Add          | 7M + 2E <sub>P</sub> |

## 5. Register Data Transfer Instructions

| LI    | Load Immediate              | 4M + E <sub>R</sub> |

|-------|-----------------------------|---------------------|

| RCPY  | Register Copy               | 4M + E <sub>R</sub> |

| RXCH  | Register Exchange           | 6M + E <sub>R</sub> |

| XCHRS | Exchange Register and Stack | 6M + E <sub>R</sub> |

| CFR   | Copy Flags Into Register    | 4M + E <sub>R</sub> |

| CRF   | Copy Register Into Flags    | 4M + E <sub>R</sub> |

| PUSH  | Push Register Onto Stack    | 4M + E <sub>R</sub> |

| PULL  | Pull Stack Into Register    | 4M + E <sub>R</sub> |

| PUSHF | Push Flags Onto Stack       | 4M + E <sub>B</sub> |

| PULLF | Pull Stack Into Flags       | 4M + E <sub>R</sub> |

|       |                             |                     |

#### 6. Register Data Operate Instructions

| RADD | Register Add                 | 4M + E <sub>R</sub> |

|------|------------------------------|---------------------|

| RADC | Register Add With Carry      | 4M + E <sub>R</sub> |

| RAND | Register And                 | 4M + E <sub>R</sub> |

| RXOR | Register Exclusive Or        | 4M + E <sub>R</sub> |

| CAI  | Complement and Add Immediate | 5M + E <sub>R</sub> |

### 7. Shift And Rotate Instructions

| SHL<br>SHR<br>ROL<br>ROR | Shift Left<br>Shift Right<br>Rotate Left<br>Rotate Right | $(5 + 3n) M + E_{R}, n = 1 - 127;$<br>$6M + E_{R}, n = 0$ |

|--------------------------|----------------------------------------------------------|-----------------------------------------------------------|

|--------------------------|----------------------------------------------------------|-----------------------------------------------------------|

#### 8. Miscellaneous Instructions

| M = Machine cycl | e time = 4 clock periods E |    |   | tend |  |  |

|------------------|----------------------------|----|---|------|--|--|

| PFLG Pul         | ise Flag                   | 6M | + | ER   |  |  |

| SFLG Set         | Flag                       | 5M | + | ER   |  |  |

| HALT Hal         | lt                         |    |   |      |  |  |

While the instruction set is compact at 45 instruction types (or 337 individual instructions), it is powerful enough to allow considerably more efficient program coding than most microprocessors and compares favorably with many minicomputers.

#### I/O DESCRIPTION

#### **Drivers and Receivers**

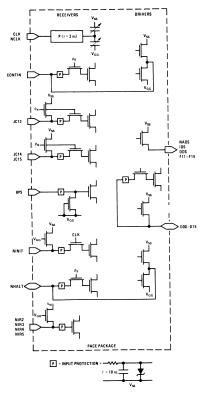

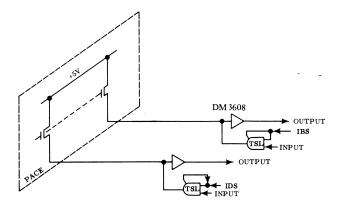

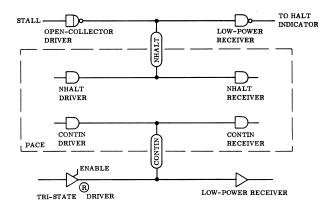

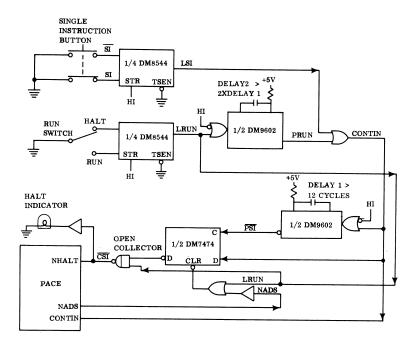

Equivalent circuits for PACE drivers and receivers are shown in Figure 6. All inputs have static charge protection circuits consisting of an RC filter and voltage clamp. These devices should still be handled with care, as the protection circuits can be destroyed by excessive static charge. Pullup transistors on several inputs are turned on during one of the eight internal clock phases. In the case of bidirectional signals, the output driver transistors also serve as input pullup transistors.

FIGURE 6. PACE Driver and Receiver Equivalent Circuits

#### Data I/O Timing

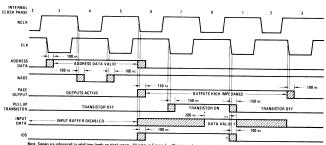

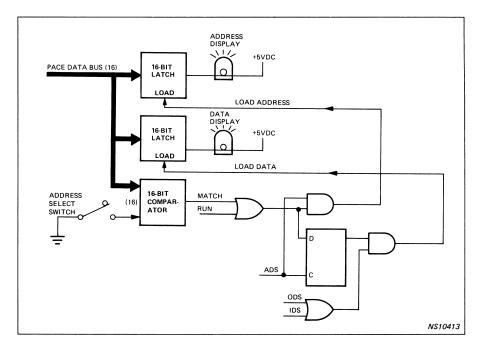

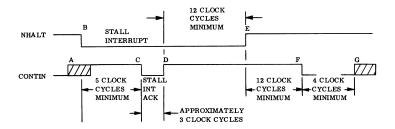

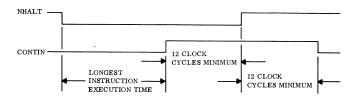

All data transfers between PACE and external memories or peripheral devices take place over the 16 data lines. These transfers are synchronized by the NADS, IDS, ODS and EXTEND signals. Timing for address data output is shown in Figure 7. All signal timing is referenced to valid logic "1" or logic "0" clock levels. Cross-hatched areas indicate uncertainty of output transitions or "don't care" (optional) states for data inputs. Address data becomes valid one clock phase prior to the Address Data Strobe and remains valid for one clock phase afterwards. Typically, NADS will be used to strobe the address data into a latch, either internal or external to the memory chips, or to clock decoded peripheral addresses into a flip-flop.

The PACE address output drivers assume a high impedance state during the data input interval as shown in Figure 7. The IDS signal may be used to disable the output sense amplifiers and enable TRI-STATE® input buffers. Increased power supply current may occur during the transition period of the TRI-STATE enable signal, when several devices may be simultaneously enabled. Therefore, good power and ground layout and bypass filtering practice should be observed. The data lines must be driven to valid input data logic levels by the end of IDS, and all logic 1 inputs must reach a minimum intermediate level of V<sub>SS</sub> - 2.35V 200 ns prior to the end of internal clock phase 8. TTL devices will actively drive the input to this minimum intermediate level and the transition will be completed by a combination of the on-chip pullup transistor and the (reduced) TTL output drive current. Typically, this data input timing will allow operation of the microprocessor in a system at maximum speed if the access time of the system memory is less than 700 ns. For memories with longer access times the clock frequency may be reduced or the I/O cycle extend feature may be used, as described below.

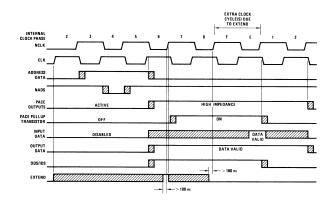

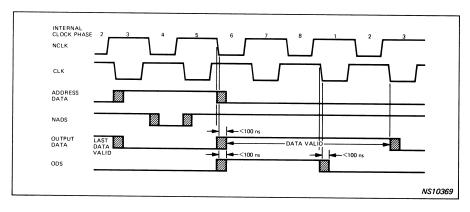

Data output timing is shown in Figure 8. Output data becomes valid at the leading edge of ODS and remains valid for one clock period following the trailing edge.

The Output Data Strobe is typically used as a read-write signal for memory and an output data latch strobe for peripheral interfaces.

$^*V_{IN}$  must be  $>V_{SS}-2.35V$  at this time if logic "1" input.  $^*V_{IN}$  must be valid level (i.e.,  $V_{SS}-1$ ) at this time (this timing a

Data must be valid until trailing edge of IDS (i.e., data hold time - 0 ns)

FIGURE 7. Address Output and Data Input Timing

FIGURE 8. Data Output Timing

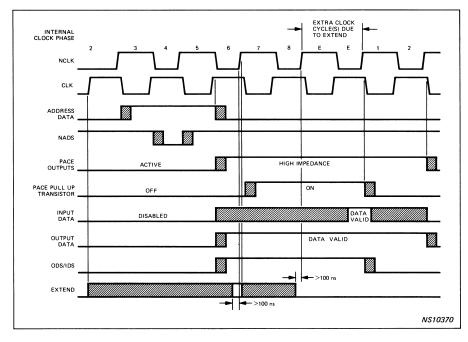

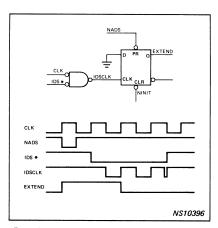

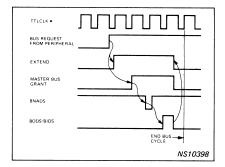

For systems utilizing memories with access times greater than 700 ns it may be desirable to use the EXTEND input to lengthen the I/O cycle by multiples of the clock period. Timing for this is shown in Figure 9. In the case of either input or output operations, the extend should be brought true prior to the end of internal phase 6. The timing shown in Figure 9 will provide the minimum extend of one clock period. Holding EXTEND true for and additional n clock periods longer will cause an extention of n+1 clock periods. As indicated in the electrical characteristics, there must be at least 64 non-extend clock cycles every 640 microseconds. This

includes the use of EXTEND for both extending and suspending I/O operations.

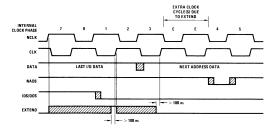

In DMA or multiprocessor systems it may be desirable to prevent I/O operations by PACE when the bus is in use by another device. This may be done by using the EXTEND signal immediately following an IDS or ODS as shown in Figure 10. Alternatively, the extend timing of Figure 9 may be used, as the extend function occurs independent of whether there is an I/O operation, that is, whenever the internal clock phase 6 occurs.

FIGURE 9. Extend I/O Signal Timing

FIGURE 10. Suspend I/O Signal Timing

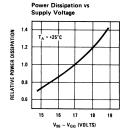

## typical performance characteristics

## physical dimensions

Cavity Dual-In-Line Package (D)

Manufactured under one or more of the following U.S. patents: 308262, 3189758, 3231797, 3303356, 3317671, 3323071, 3381071, 3408542, 3421025, 3426423, 3440498, 3518750, 3519897, 3557431, 3560765, 366218, 3571630, 3575609, 3593069, 3597609, 3607469, 3617859, 3631312, 3633052, 363131, 3648071, 3651565, 3693248.

National Semiconductor Corporation 2900 Semiconductor Drive, Santa Clara, California 95051, (408) 732-5000/TWX (910) 339-9240 National Semiconductor GmbH 806 Fuerstentejotruck, Industriestrasse 10, West Germany, Tele. (08141) 1371/Telex 05-27549

National Semiconductor (UK) Ltd.

Larkfield Industrial Estate, Greenock, Scotland, Tele. (0475) 33251/Telex 778-632

## INTRODUCTION TO PACE 1.1 DESCRIPTION National Semiconductor's Processing and Control Element, called PACE, is a single-chip full-feature Central Processing Unit (CPU). PACE is housed in a 40-pin, ceramic, dual-inline package. The ultrahigh density and overall layout of the microcircuit are shown in figure 1-1. NSTRUCTION REGISTER DATA I/O REGISTER & BUFFERŞ DATA MULTIPLEXER REGISTER ADDRESS FORMATION **ROM OUTPUT BUFFERS** RAM READ/WRITE BUFFERS RAM REFRESH CONTROL CONTROL ROM STACK POINTER ROM ADDRESS MAPPING RAM DATA BUFFERS ALU CONTROL LOGIC CONTROL ROM DECODE ROM ADDRESS REGISTER DATA I/O REGISTER & BUFFERŞ INITIALIZE & EXTEND CONTROL JUMP CONDITION MULTIPLEXER CONTROL LOGIC CLOCK GENERATORS INTERRUPT REQUEST LATCHES CONDITION L ARITHMETIC & LOGIC UNIT PRIORITY ENCODER INTERRUPT ENABLE FLAGS FLAGS FLAGS FLAG DECODE Magnified 325 Times

CHAPTER 1

Figure 1-1. PACE Chip and Circuit Layout

NS10351

Figure 1-2. PACE Functional Block Diagram

PACE also is called a microprocessor, the prefix micro relating to the microscopic size of the physical circuit and components on the chip. An extraordinary amount of data-processing capability is provided in one component by the single-chip microconstruction.

Figure 1-2 reveals the CPU architecture and pinouts of the single-chip PACE — consisting of registers, control logic, an arithmetic unit, and the data buses. Some of the outstanding operational features of the PACE microprocessor are listed below.

#### Features

- 16-bit instruction word offers addressing flexibility and speed.

- 8- or 16-bit data word interfaces increase application flexibility.

- 45 instruction types provide efficient programming.

- Common memory and peripheral addressing means powerful I/O instructions.

- Shares instructions with National Semiconductor's IMP-16, allowing software compatibility.

- Four general-purpose accumulators reduce memory data transfers.

- 10-word Stack is utilized for interrupt processing/data storage.

- Six vectored priority-interrupt levels speed interrupt service and simplify hardware.

- Programmer-accessible status register may be preserved, tested, or modified.

- Typical 10-microsecond instruction execution guarantees high throughput.

- 1K-by-16 Read-Only Memory allows single-memory package systems.

- Single-phase true and complement clock minimizes external components.

- +5-volt and -12-volt standard supplies ensure minimum cost

The PACE MOS/LSI chip is produced using silicon-gate, Pchannel enhancement-mode standard-process technology. This means that the following very significant advantages are realized.

- · Lower cost per function

- Lower component count

- Simplified design

- Higher reliability

- · High noise immunity

- Low threshold voltage

Among some of the benefits of a single-chip device with the above-listed advantages are the following.

LOWER COMPONENT COUNT --- Generally, this

means lower procurement, incoming testing, inventory, handling, rework, and assembly cost -- and higher reliability.

- SIMPLIFIED DESIGN --- LSI devices enable engineering design groups to take advantage of prepackaged

circuits that are self-contained and perform a unified

function. Also, a design group not strongly oriented

towards digital design may make use of the latest

techniques and devices without requiring expertise related to the design methods of interfacing the circuits

internal to LSI devices. In summary, use of LSI devices requires considerably less engineering time to

develop a product.

- HIGHER RELIABILITY The long history of field maintenance of all types of electronic systems clearly demonstrates the high reliability of LSI devices. System maintenance has shown that the reliability of low-power circuits is inversely proportional to the number of component lead connections in the system. This factor, coupled with the abundant functional capability of LSI, greatly increases the probability that an LSI-based system will function properly over extended periods of time.

- IMPROVED PERFORMANCE --- PACE offers higher throughput because of a powerful instruction set, a proven architecture, and 16-bit address generation and data handling.

- LOWER COST --- The reduction of cost is an aggregate savings resulting from the other advantages already enumerated. In the microprocessor field, the inherent functional superiority of high-density devices is seldom questioned. The superior performance of the single-chip PACE, coupled with reduced engineering and assembly cost, higher reliability, lower operating and maintenance costs, and smaller size of the microprocessor, definitely results in a much better performance-to-price ratio than heretofore possible. It makes the PACE microprocessor the most competitive processor on the market.

#### 1.2 OUTSTANDING FEATURES OF PACE

The outstanding features of PACE are described in detail later. Nevertheless, to provide an overall view of the many favorable facets of PACE, these features are listed and briefly described below.

- 8- OR 16-BIT DATA HANDLING --- PACE is cost effective in applications dominated by 8-bit data interfaces. Efficient coding and address generation found only in 16-bit microprocessors are extended to 8-bit applications.

- INCREASED THROUGHPUT --- PACE minimizes data and program storage requirements, while increasing data-processing throughput.

- USER GROUP --- Membership open to users and others interested in microprocessors. Provides a vehicle of communications between members and with National Semiconductor. Makes programs available from its User Group Software Library.

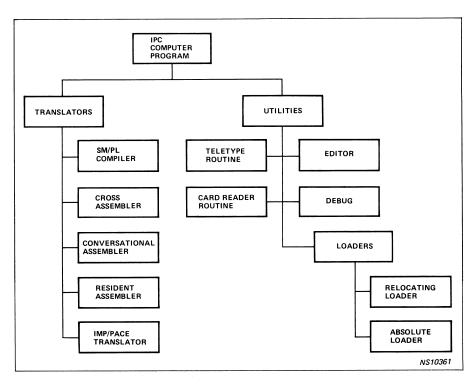

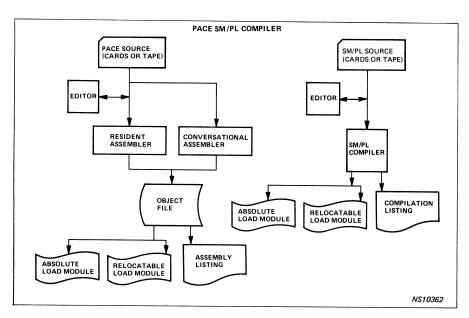

SOFTWARE SUPPORT --- Includes Source Statement Editor, Assemblers, Loaders, Debug Routine, Utilities, and Diagnostics. (Also, as previously mentioned, a Source Statement Translator converts IMP-16 software to PACE software.)

#### 1.3 PACE APPLICATIONS

Applications for PACE could very well be in the thousands. The suitability of PACE will, in many cases, be a matter of evaluation by potential users for their particular needs. A few applications are listed.

- Test system and instrument control

- Process controllers

- · Machine tool control

- Terminal control

- Small business machines

- Traffic controllers

- Word-processing systems

- Peripheral device controllers

- Educational controllers

- Sophisticated games

- · Distributed and multiprocessor systems

- Automotive controller

#### 1.8 SOFTWARE SUPPORT

The importance of National Semiconductor-supplied support software cannot be overemphasized. The microprocessor design process is most efficient when the designer fully appreciates and uses the support software.

## 1.9 SPECIFYING HARDWARE BEHAVIOR WITH SOFTWARE

The microprocessor approach differs from older, discretelogic controllers in only one important way, and all differences in approach stem from the following.

- In the random-logic approach, a set of logic is wired to handle each function, and all logic operations proceed in parallel.

- In the microprocessor approach, one central set of logic is provided inside the microprocessor. The central set of logic is rewired in real time, under control of the program, to handle each of the logic functions in regist.

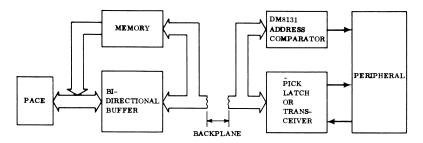

Thus, the discrete-logic designer buys a set of functions and then wires the functions to perform a specific job. On the other hand, the microprocessor user buys a microprocessor and then must tell the microprocessor how to wire itself, from microsecond to microsecond, to perform different jobs.