## USER'S MANUAL

# 16-BIT V SERIES<sup>TM</sup>

16-/8- AND 16-BIT MICROPROCESSORS

INSTRUCTION

V20<sup>TM</sup>, V30<sup>TM</sup> V20HL<sup>TM</sup>, V30HL<sup>TM</sup> V40<sup>TM</sup>, V50<sup>TM</sup> V40HL<sup>TM</sup>, V50HL<sup>TM</sup> V33A<sup>TM</sup> V53A<sup>TM</sup>

#### NOTES FOR CMOS DEVICES

#### 1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### 3 STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

V20, V30, V20HL, V30HL, V40, V50, V40HL, V50HL, V33A, V53A, and V series are trademarks of NEC Corporation.

InterTool is a trademark of Intermetrics Microsystems Software, Inc.

- The information in this document is current as of February, 1997. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of

third parties by or arising from the use of NEC semiconductor products listed in this document or any other

liability arising from the use of such products. No license, express, implied or otherwise, is granted under any

patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of customer's equipment shall be done under the full

responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third

parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC

semiconductor products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades:

- "Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

(Note)

- (1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

## **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- · Ordering information

- · Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### **NEC Electronics Inc. (U.S.)**

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### **NEC Electronics (Germany) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

#### **NEC Electronics (UK) Ltd.**

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### NEC Electronics Italiana s.r.l.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

#### **NEC Electronics (Germany) GmbH**

Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

#### **NEC Electronics (France) S.A.**

Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

#### **NEC Electronics (France) S.A.**

Madrid Office Madrid, Spain Tel: 91-504-2787 Fax: 91-504-2860

#### **NEC Electronics (Germany) GmbH**

Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

#### **NEC Electronics Hong Kong Ltd.**

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

#### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

#### **NEC Electronics Singapore Pte. Ltd.**

United Square, Singapore Tel: 65-253-8311

Tel: 65-253-8311 Fax: 65-250-3583

#### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

#### NEC do Brasil S.A.

Electron Devices Division Guarulhos-SP Brasil Tel: 55-11-6462-6810 Fax: 55-11-6462-6829

### **MAJOR REVISIONS IN THIS EDITION**

| Pages      | Contents                                                                                                                                                |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Throughout | The following products have been deleted:  • μPD70208 (A) (V40)  • μPD70216 (A) (V50)  • μPD70270 (V41 <sup>TM</sup> )  • μPD70280 (V51 <sup>TM</sup> ) |

The mark  $\star$  shows major revised points.

#### **PREFACE**

Readers

This manual is intended for engineers who wish to understand the functions of the following 16-bit V series microprocessors and design application systems using them.

| Parts Number | Nick Name |

|--------------|-----------|

| μPD70108     | V20       |

| μPD70116     | V30       |

| μPD70108H    | V20HL     |

| μPD70116H    | V30HL     |

| μPD70208     | V40       |

| μPD70216     | V50       |

| μPD70208H    | V40HL     |

| μPD70216H    | V50HL     |

| μPD70136A    | V33A      |

| μPD70236A    | V53A      |

**Purpose**

This manual is to introduce the instruction functions of the above 16-bit V series microprocessors.

Organization

Two volumes of the User's Manual of the above 16- bit V series microprocessors are available: Hardware Manual and Instruction Manual (this manual).

Hardware Manual Instruction Manual

General General

Pin Function Instruction Description

CPU Function Instruction Map

Internal Block Function

Correspondence of Mnemonic between  $\mu$ PD8086 and 8088

Bus Control Function Interrupt Function Standby Function Reset Function

Others

How to Read This Manual It is assumed that readers of this manual have a basic knowledge of electricity, logic circuits, and microcontrollers. Unless otherwise specified, the descriptions in this manual apply to all the models in the 16-bit V series microprocessors. Note that part number " $\mu$ PD70..." is referred to as "V..." in this manual.

To check the details of the function of an instruction whose mnemonic is known,

→ Refer to CHAPTER 2 INSTRUCTIONS (instructions are shown in alphabetic order of the mnemonic)

To understand the details of each instruction,

→ Read this manual in the order of the Table of Contents.

To understand the hardware functions of each product,

→ Refer to the **User's Manual - Hardware** (separate volume) for each product.

To find the electrical specifications

→ Refer to the data sheet for each product.

Legend Data significance : Left: high, right: low

> Active low :  $\overline{\times\!\times\!\times}$  (top bar over pin or signal name)

Memory map address : Top: high, bottom: low

Address representation: x indicates a segment value, and y indicates an offset value

in the following case:

x: yH

Note : Explanation of items marked with Note in the text

Caution : Important information

Remark : Supplement

Numeric notation : Binary ... xxxx or xxxxB

> Decimal ... ×××× Hexadecimal ... xxxxH

#### **Related documents**

The documents referred to in this publication may include preliminary versions. However, preliminary versions are not marked as such.

| Document     | Data Sheet | User's   | Manual      | Application Note   | Register | Q & A   |

|--------------|------------|----------|-------------|--------------------|----------|---------|

| Parts Number |            | Hardware | Instruction |                    | Table    |         |

| V20          | IC-1827    | IEM-871  | This        | -                  | -        | _       |

| V30          | IC-1828    |          | manual      |                    |          |         |

| V20HL        | IC-3552    | IEU-761  |             | _                  | -        | -       |

| V30HL        |            |          |             |                    |          |         |

| V40          | U10154E    | U10666E  |             | U10911E            | -        | U10554E |

| V50          |            |          |             | Software           |          |         |

| V40HL        | IC-3659    | U11610E  |             | U10037E            | -        | U11123E |

|              |            |          |             | Hardware Design    |          |         |

| V50HL        |            |          |             | U10911E            |          |         |

|              |            |          |             | Software           |          |         |

| V33A         | U10136E    | U10032E  |             | _                  | -        | -       |

| V53A         | U10120E    | U10108E  |             | U10188E            | -        | U10875E |

|              |            |          |             | Address Expansion, |          |         |

|              |            |          |             | Software           |          |         |

[MEMO]

Phase-out/Discontinued

### **TABLE OF CONTENTS**

| CHAPTER 1   | GENERAL                                                         | 1   |

|-------------|-----------------------------------------------------------------|-----|

| 1.1         | Classification of Instructions by Function                      | 2   |

| 1.2         | Instruction Word Format                                         | 3   |

| 1.3         | Functional Outline of Each Instruction                          | 3   |

|             | 1.3.1 Data transfer instructions                                | 3   |

|             | 1.3.2 Block manipulation instructions                           | 3   |

|             | 1.3.3 Bit field manipulation instructions                       | 3   |

|             | 1.3.4 I/O instructions                                          | 4   |

|             | 1.3.5 Operation instructions                                    | ∠   |

|             | 1.3.6 BCD operation instructions                                | ∠   |

|             | 1.3.7 BCD adjustment instructions                               | 5   |

|             | 1.3.8 Data conversion instruction                               | 5   |

|             | 1.3.9 Bit manipulation instructions                             | 5   |

|             | 1.3.10 Shift and rotate instructions                            | 5   |

|             | 1.3.11 Stack manipulation instructions                          | 5   |

|             | 1.3.12 Program branch instructions                              | 6   |

|             | 1.3.13 CPU control instructions                                 | 6   |

|             | 1.3.14 Mode select instructions                                 | 6   |

|             |                                                                 | _   |

|             | INSTRUCTIONS                                                    |     |

| 2.1         | Description of Instructions (in alphabetical order of mnemonic) |     |

| 2.2         | Number of Instruction Execution Clocks                          | 169 |

| APPENDIX A  | A REGISTER CONFIGURATION                                        | 185 |

|             | General-Purpose Registers (AW, BW, CW, DW)                      |     |

|             | Segment Registers (PS, SS, DS0, DS1)                            |     |

|             | Pointers (SP, BP)                                               |     |

|             | Program Counter (PC)                                            |     |

|             | Program Status Word (PSW)                                       |     |

|             | Index Registers (IX, IY)                                        |     |

| 70          |                                                                 |     |

| APPENDIX I  | 3 ADDRESSING MODES                                              | 191 |

|             | Instruction Address                                             |     |

|             | Memory Operand Address                                          |     |

|             |                                                                 |     |

| APPENDIX (  | INSTRUCTION MAP                                                 | 199 |

|             |                                                                 |     |

| APPENDIX I  | CORRESPONDENCE OF MNEMONICS OF $\mu$ PD8086 AND 8088            | 203 |

|             |                                                                 |     |

| APPENDIX I  | INSTRUCTION INDEX (mnemonic: by function)                       | 205 |

| VDDENIOIA i | INSTRUCTION INDEX (mnemonic: alphabetical order)                | 207 |

| ALLEINDIY I | - INSTRUCTION INDEX (IIIIemonic, alphabetical order)            |     |

### **LIST OF FIGURES**

| Figure No. | Title                                                                          | Page |

|------------|--------------------------------------------------------------------------------|------|

| 1-1        | Relations between Common Instructions and Dedicated Instructions of Each Model | 1    |

| 1-2        | Instruction Format                                                             | 3    |

| 1-3        | Operation of ALU When Operation Instruction Is Executed                        | 4    |

| 2-1        | Description Example                                                            | 12   |

| A-1        | PSW Configuration                                                              | 186  |

### LIST OF TABLES

| Table No. | Title                                                   | Page |

|-----------|---------------------------------------------------------|------|

| 1-1       | Classification of Instructions by Function              | 2    |

| 2-1       | Example of Flag Operation                               |      |

| 2-2       | Example of Operand Type                                 | 8    |

| 2-3       | Example of Instruction Word                             | 9    |

| 2-4       | Legend of Description of Instruction Format and Operand | 10   |

| 2-5       | Memory Addressing                                       | 11   |

| 2-6       | Selecting 8-/16-Bit General-Purpose Register            | 11   |

| 2-7       | Selecting Segment Register                              | 11   |

| 2-8       | Number of Instruction Execution Clocks                  | 170  |

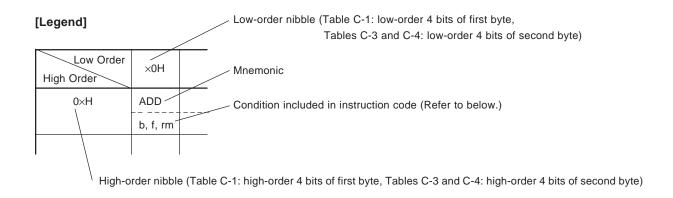

| C-1       | Instruction Map                                         | 200  |

| C-2       | Group1, Group2, Imm, and Shift Codes                    | 202  |

| C-3       | Group0 Codes                                            | 202  |

| C-4       | Group3 Codes                                            | 202  |

| D-1       | Register Correspondence with µPD8086 and 8088           | 203  |

| D-2       | Mnemonic Correspondence with uPD8086 and 8088           | 204  |

#### **CHAPTER 1 GENERAL**

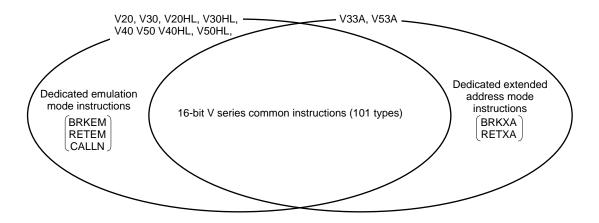

The 16-bit V series microprocessors have 101 common instructions that are completely compatible in terms of software, so that your software resources can be effectively utilized.

In addition to these common instructions, the V20, V30, V20HL, V30HL, V40, V50, V40HL, and V50HL have three dedicated instructions (BRKEM, RETEM, and CALLN) to support emulation mode.

The V33A and V53A have two dedicated instructions (BRKXA and RETXA) to support the extended address mode.

#### Figure 1-1. Relations between Common Instructions and Dedicated Instructions of Each Model

Remark For the emulation mode and extended address mode, refer to the Hardware Manual of each model.

### 1.1 Classification of Instructions by Function

The instructions of the 16-bit V series can be broadly divided by classification of function into the following 27 types.

Table 1-1. Classification of Instructions by Function

| Instruction Group                                       | Mnemonic (alphabetical order)                                                                                         |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Data transfer instructions                              | LDEA, MOV, TRANS, TRANSB, XCH                                                                                         |

| Repeat prefix                                           | REP, REPC, REPE, REPNC, REPNE, REPNZ, REPZ                                                                            |

| Primitive block transfer instructions                   | CMPBK, CMPBKB, CMPBKW, CMPM, CMPMB, CMPMW, LDM, LDMB, LDMW, MOVBK, MOVBKB, MOVBKW, STM, STMB, STMW                    |

| Bit field manipulation instructions                     | EXT, INS                                                                                                              |

| I/O instructions                                        | IN, OUT                                                                                                               |

| Primitive I/O instructions                              | INM, OUTM                                                                                                             |

| Add/subtract instructions                               | ADD, ADDC, SUB, SUBC                                                                                                  |

| BCD operation instructions                              | ADD4S, CMP4S, ROL4, ROR4, SUB4S                                                                                       |

| Increment/decrement instructions                        | DEC, INC                                                                                                              |

| Multiplication/division instructions                    | DIV, DIVU, MUL, MULU                                                                                                  |

| BCD adjustment instructions                             | ADJ4A, ADJ4S, ADJBA, ADJBS                                                                                            |

| Data conversion instructions                            | CVTBD, CVTBW, CVTDB, CVTWL                                                                                            |

| Compare instructions                                    | CMP                                                                                                                   |

| Complement operation instructions                       | NEG, NOT                                                                                                              |

| Logical operation instructions                          | AND, OR, TEST, XOR                                                                                                    |

| Bit manipulation instructions                           | CLR1, NOT1, SET1, TEST1                                                                                               |

| Shift instructions                                      | SHL, SHR, SHRA                                                                                                        |

| Rotate instructions                                     | ROL, ROLC, ROR, RORC                                                                                                  |

| Subroutine control instructions                         | CALL, RET                                                                                                             |

| Stack manipulation instructions                         | DISPOSE, POP, PREPARE, PUSH                                                                                           |

| Branch instruction                                      | BR                                                                                                                    |

| Conditional branch instructions                         | BC, BCWZ, BE, BGE, BGT, BH, BL, BLE, BLT, BN, BNC, BNE, BNH, BNL, BNV, BNZ, BP, BPE, BPO, BZ, BV, DBNZ, DBNZE, DBNZNE |

| Interrupt instructions                                  | BRK, BRKV, CHKIND, RETI                                                                                               |

| CPU control instructions                                | BUSLOCK, DI, EI, FPO1, FPO2, HALT, NOP, POLL                                                                          |

| Segment override prefix                                 | DS0:, DS1:, PS:, SS:                                                                                                  |

| Dedicated emulation mode instructions <sup>Note 1</sup> | BRKEM, CALLN, RETEM                                                                                                   |

| Dedicated extended address mode instructionsNote 2      | BRKXA, RETXA                                                                                                          |

Notes 1. Except V33A and V53A

2. V33A and V53A only

#### 1.2 Instruction Word Format

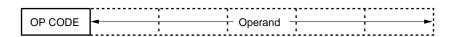

Basically, an instruction word (object code) is in the following format.

Figure 1-2. Instruction Format

Remark op code: 8-bit code indicating type of instruction

Operand: Field indicating register and memory address to be manipulated by instructions. Indicated

as a field of 0 to 5 bytes.

#### 1.3 Functional Outline of Each Instruction

#### 1.3.1 Data transfer instructions

The data transfer instructions transfer data between two registers and between a register and memory, without data manipulation. These instructions can be classified into the following four types.

To transfer general data (MOV) : Transfers a specified byte/word from the second operand to the first

operand. Can also directly transfer a numeric value to a register or

memory.

To transfer effective address (LDEA): Transfers the offset address (effective address) of the second operand

to the first operand.

To transfer conversion table (TRANS): Transfers 1 byte of a conversion table.

Exchanges general data (XCH) : Exchanges the contents of the first operand with those of the second

operand.

#### 1.3.2 Block manipulation instructions

A block (successive data) of bytes or words can be transferred or compared by using a repeat prefix and a primitive block transfer instruction.

The primitive block transfer instructions transfer, compare, and scan data, like the instructions that transfer data with the accumulator in block units. If a 1-byte repeat prefix is used, repetitive processing by hardware can be performed so that data can be manipulated successively.

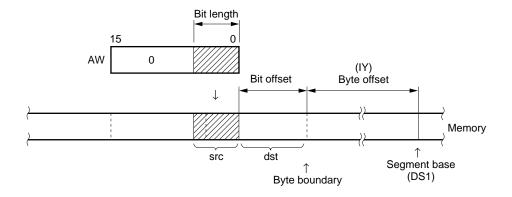

#### 1.3.3 Bit field manipulation instructions

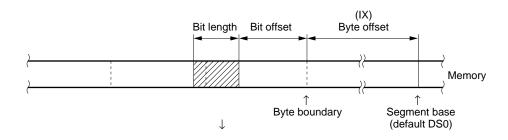

The bit field manipulation instructions can be used to transfer data of specified length between a specified bit field area and the AW register, with a contiguous memory area regarded as the bit field.

These instructions update a word offset (IX or IY register) and bit offset (8-bit general-purpose register) and automatically specify successive bit field data after the instructions have been executed. These instructions are useful for computer graphics and high-level languages and can support, for example, packed array of Pascal and data structure of record type.

#### 1.3.4 I/O instructions

The I/O instructions and primitive I/O instructions can read/write I/O devices.

The I/O devices transfer data with the CPU via the data bus by using these instructions.

#### 1.3.5 Operation instructions

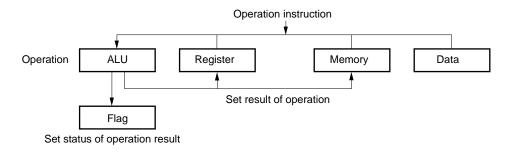

The following instructions can execute 8-/16-bit data operations.

Add/subtract, increment/decrement, multiplication, division, compare, complement operation, logical operation

The increment/decrement instructions can increment (+1) or decrement (-1) the 8-/16-bit data of the general-purpose registers or memory.

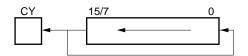

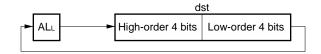

Each operation instruction is not executed in a register or memory whose contents are to be manipulated, but actually executed in the ALU. The result of the operation is set (1) or reset (0) to the flags of the program status word (PSW).

Figure 1-3. Operation of ALU When Operation Instruction Is Executed

#### 1.3.6 BCD operation instructions

The BCD operation instructions can be used to represent decimal numbers by using hexadecimal numbers for calculation.

These instructions can also be used to execute arithmetic operation or comparison of BCD strings in memory. Instructions that support rotating the BCD strings are also included.

Because the operand and comparison instructions are used to manipulate specific registers, they do not have an operand that specifies a packed BCD string.

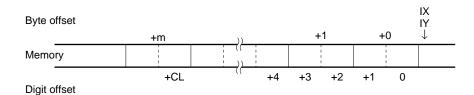

The first address of the source string (address of the byte data including LSD) is specified by the contents of the IX register in data segment 0 (DS0).

The first address (address of the byte data including LSD) of the destination string is specified by the contents of the IY register in data segment 1 (DS1).

The number of digits is specified by the contents of the CL register.

Because the destination string and source string must be of the same length, 0 is extended to the length of longer string if the lengths of the two are different.

#### 1.3.7 BCD adjustment instructions

BCD operation is supported by executing a BCD adjustment instruction before or after arithmetic operation.

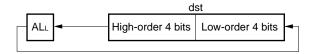

Because the BCD adjustment instructions are executed on the AL register, they do not have an operand. In the case of addition and subtraction, adjustment can be made to both packed BCD and unpacked BCD. In the case of multiplication and division, however, adjustment can be made to only unpacked BCD representation.

#### 1.3.8 Data conversion instruction

The data conversion instructions can convert the type and word length of binary and decimal numbers.

The CVTBD and CVTDB instructions convert binary numbers and 2-digit unpacked BCD.

The CVTBW and CVTWL instructions extend the sign in a register.

#### 1.3.9 Bit manipulation instructions

The bit manipulation instructions are used to execute logical operations on the bit data of the general-purpose registers or memory.

The operand of the instruction format is "reg, bit" or "mem, bit".

The first operand, reg or mem, specifies 8-/16-bit data including the bit data to be manipulated and codes a general-purpose register or an effective address.

The second operand bit indicates the address of the bit data in a byte or word, and uses the contents of CL or 8-bit immediate data. If reg or mem is 8-bit data, only the low-order 3 bits are the valid bit address. If reg or mem is 16-bit data, only the low-order 4 bits are the valid bit address, and the high-order bits are ignored.

#### 1.3.10 Shift and rotate instructions

The shift or rotate instructions shift or rotate the 8-/16-bit data of a general-purpose register or memory 1 bit or more (0 to 255).

The shift instructions are divided into arithmetic shift and logical shift instructions. Usually, the number of digits to be shifted is 1, but it can be changed depending on the value of the CL register each time the instruction has been executed if specified by the count operand of the instruction (255 max.). The arithmetic shift instruction inserts 0 to the LSB of the data shifted if the data has been shifted 1 bit to the left, and 1 to the MSB of the data if the data has been shifted 1 bit to the right. The logical shift instruction does not cause the value of the LSB or MSB to be changed even when the data has been shifted 1 bit.

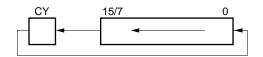

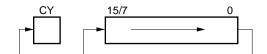

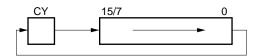

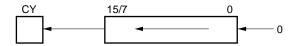

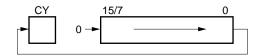

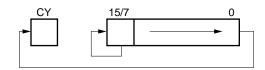

Like the shift instructions, the number of digits to be rotated by a rotate instruction is specified by the count operand of the instruction. This value is the value stored to the CL register. As a result of executing the rotate instruction, the CY and V flags are affected. The bit rotated out is always stored to the CY flag. The V flag always becomes undefined if two or more digits have been rotated. If only one digit is rotated and the MSB (extension) of the destination is affected as a result, the V flag is set to 1; otherwise, the flag is reset to 0. The CY flag can be used as the extension of the destination when the ROLC or ROR instruction is used.

#### 1.3.11 Stack manipulation instructions

The stack manipulation instructions are used to manipulate the stack in the memory.

The following four types of stack manipulation instructions are available.

PUSH : Saves data to the stack.

POP : Restores data from the stack.

PREPARE: Creates a stack frame and copies a frame pointer to secure an area for a local variable or to

reference a global variable.

DISPOSE: Restores the stack pointer (SP) and base pointer (BP) to the status before the PREPARE

instruction is executed.

#### 1.3.12 Program branch instructions

These instructions branch program execution to specified addresses. The following four types of branch instructions are available.

Subroutine control instructions : Save the contents of the program counter (PC) to the stack (CALL) or restore

the contents of the PC from the stack (RET).

Branch instruction : Branches the flow of an instruction to a specified address.

Conditional branch instructions: Branch the flow of instruction execution to a specified address depending

on the value of a flag.

Interrupt instructions : Temporarily stop execution of the program and controls flow of program

execution by means of software interrupts if an external device requests for

interrupt or if an operation error occurs.

#### 1.3.13 CPU control instructions

The CPU control instructions manipulate flags, synchronize the processor with an external device, or transfer data. An instruction that causes the CPU to execute nothing (NOP) is also available.

#### 1.3.14 Mode select instructions

#### (1) Emulation mode (except V33A and V53A)

The mode can be changed between the native and emulation modes by using a dedicated emulation mode instruction.

#### (2) Extended address mode (V33A and V53A only)

The mode can be changed between the normal address mode and extended address mode by using a dedicated extended address mode instruction.

#### **CHAPTER 2 INSTRUCTIONS**

#### 2.1 Description of Instructions (in alphabetical order of mnemonic)

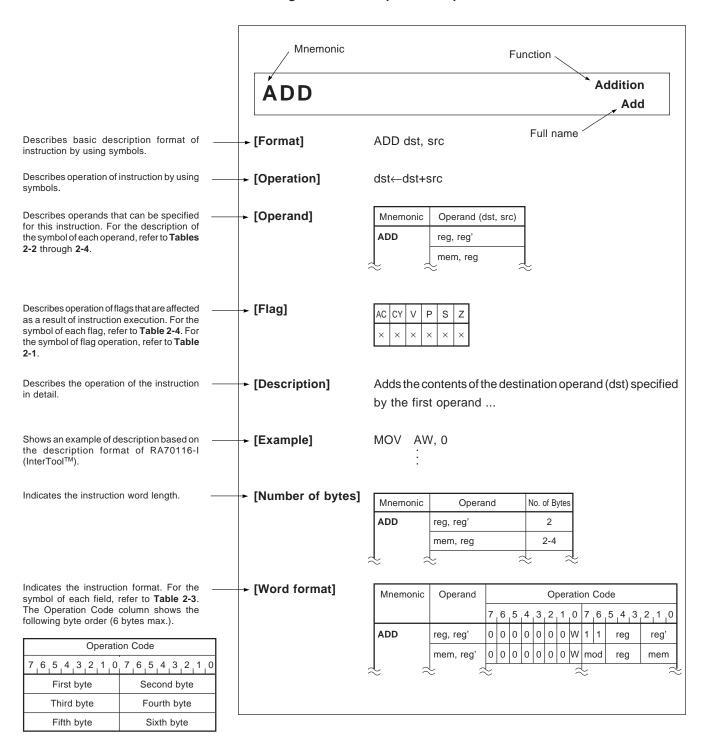

This chapter explains the following items for each instruction.

[Format]

[Operation]

[Operand]

[Flag]

[Description]

[Example]

[Number of bytes]

[Word format]

In [Format], [Operation], and [Operand], several identifiers are used.

Tables 2-2 through 2-4 show the identifiers used and their meanings, and Tables 2-5 through 2-7 explain how to select memory addressing modes, general-purpose registers, and segment registers.

[Flag] shows, by using identifiers, the operations of the flags that are affected as a result of executing the given instruction. Table 2-1 shows examples of operations of each flag.

Table 2-1. Example of Flag Operation

| Identifier | Description                                |

|------------|--------------------------------------------|

| Blank      | Not affected                               |

| 0          | Reset to 0                                 |

| 1          | Set to 1                                   |

| ×          | Set to 1 or reset to 0 depending on result |

| U          | Undefined                                  |

| R          | Restores previously saved value            |

### Table 2-2. Example of Operand Type

| Identifier  | Description                                                                                      |

|-------------|--------------------------------------------------------------------------------------------------|

| reg         | 8-/16-bit general-purpose register                                                               |

|             | (destination register for instruction using two 8-/16-bit general-purpose registers)             |

| reg'        | Source register for instruction using two 8-/16-bit general-purpose registers                    |

| reg8        | 8-bit general-purpose register                                                                   |

|             | (destination register for instruction using two 8-bit general-purpose registers)                 |

| reg8'       | Source register for instruction using two 8-bit general-purpose registers                        |

| reg16       | 16-bit general-purpose register                                                                  |

|             | (destination register for instruction using two 16-bit general-purpose registers)                |

| reg16'      | Source register for instruction using two 16-bit general-purpose registers                       |

| mem         | 8-/16-bit memory address                                                                         |

| mem8        | 8-bit memory address                                                                             |

| mem16       | 16-bit memory address                                                                            |

| mem32       | 32-bit memory address                                                                            |

| dmem        | 16-bit direct memory address                                                                     |

| imm         | 8-/16-bit immediate data                                                                         |

| imm3        | 3-bit immediate data                                                                             |

| imm4        | 4-bit immediate data                                                                             |

| imm8        | 8-bit immediate data                                                                             |

| imm16       | 16-bit immediate data                                                                            |

| acc         | Accumulator (AW or AL)                                                                           |

| sreg        | Segment register                                                                                 |

| src-table   | Name of 256-byte conversion table                                                                |

| src-block   | Name of source block addressed by IX register                                                    |

| dst-block   | Name of destination block addressed by IY register                                               |

| near-proc   | Procedure in current program segment                                                             |

| far-proc    | Procedure in other program segments                                                              |

| near-label  | Label in current program segment                                                                 |

| short-label | Label in range of end of instruction –128 to +127 bytes                                          |

| far-label   | Label in other program segments                                                                  |

| regptr16    | 16-bit general-purpose register having offset of call address in current program segment         |

| memptr16    | 16-bit memory address having offset of call address in current program segment                   |

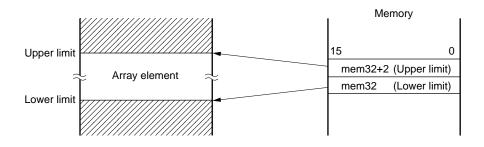

| memptr32    | 32-bit memory address having offset and segment data of call address in other program segments   |

| pop-value   | Number of bytes discarded from stack (0 to 64K, usually even number)                             |

| fp-op       | Immediate value identifying instruction code of floating-point coprocessor                       |

| R           | Register set (AW, BW, CW, DW, SP, BP, IX, IY)                                                    |

| DS1-spec    | DS1 or segment name/group name ASSUMEd to DS1                                                    |

| Seg-spec    | Any segment register name or segment name/group name ASSUMEd to segment register  Can be omitted |

| l J         | Call be Utilitied                                                                                |

Table 2-3. Example of Instruction Word

| Identifier     | Description                                                                       |

|----------------|-----------------------------------------------------------------------------------|

| W              | Byte/word field (0, 1)                                                            |

| reg            | Register field (000 to 111)                                                       |

| reg'           | Register field (000 to 111) (source register for instruction using two registers) |

| mod, mem       | Memory addressing specification bit (mod: 00 to 10, mem: 000 to 111)              |

| (disp-low)     | Low-order byte of option 16-bit displacement                                      |

| (disp-high)    | High-order byte of option 16-bit displacement                                     |

| disp-low       | Low-order byte of 16-bit displacement for PC relative addition                    |

| disp-high      | High-order byte of 16-bit displacement for PC relative addition                   |

| imm3           | 3-bit immediate data                                                              |

| imm4           | 4-bit immediate data                                                              |

| imm8           | 8-bit immediate data                                                              |

| imm16-low      | Low-order byte of 16-bit immediate data                                           |

| imm16-high     | High-order byte of 16-bit immediate data                                          |

| addr-low       | Low-order byte of 16-bit direct address                                           |

| addr-high      | High-order byte of 16-bit direct address                                          |

| sreg           | Segment register specification bit (00 to 11)                                     |

| s              | Sign extension specification bit (1: sign extension, 0: not sign extension)       |

| offset-low     | Low-order byte of 16-bit offset data loaded to PC                                 |

| offset-high    | High-order byte of 16-bit offset data loaded to PC                                |

| seg-low        | Low-order byte of 16-bit segment data loaded to PS                                |

| seg-high       | High-order byte of 16-bit segment data loaded to PS                               |

| pop-value-low  | Low-order byte of 16-bit data specifying number of bytes discarded from stack     |

| pop-value-high | High-order byte of 16-bit data specifying number of bytes discarded from stack    |

| disp8          | 8-bit displacement relatively added to PC                                         |

| X              |                                                                                   |

| XXX            | > Operation codes of floating-point coprocessor                                   |

| YYY            | Operation sedes of heating point coprocessor                                      |

| ZZZ            |                                                                                   |

Table 2-4. Legend of Description of Instruction Format and Operand (1/2)

| Identifier | Description                                            |

|------------|--------------------------------------------------------|

| dst        | Destination operand                                    |

| dst1       | Destination operand                                    |

| dst2       | Destination operand                                    |

| src        | Source operand                                         |

| src1       | Source operand                                         |

| src2       | Source operand                                         |

| target     | Target operand                                         |

| AW         | Accumulator (16 bits)                                  |

| AH         | Accumulator (high-order bytes)                         |

| AL         | Accumulator (low-order bytes)                          |

| BW         | BW register (16 bits)                                  |

| cw         | CW register (16 bits)                                  |

| CL         | CW register (low-order byte)                           |

| DW         | DW register (16 bits)                                  |

| BP         | Base pointer (16 bits)                                 |

| SP         | Stack pointer (16 bits)                                |

| PC         | Program counter (16 bits)                              |

| PSW        | Program status word (16 bits)                          |

| IX         | Index register (source) (16 bits)                      |

| IY         | Index register (destination) (16 bits)                 |

| PS         | Program segment register (16 bits)                     |

| SS         | Stack segment register (16 bits)                       |

| DS0        | Data segment 0 register (16 bits)                      |

| DS1        | Data segment 1 register (16 bits)                      |

| AC         | Auxiliary carry flag                                   |

| CY         | Carry flag                                             |

| Р          | Parity flag                                            |

| s          | Sign flag                                              |

| Z          | Zero flag                                              |

| DIR        | Direction flag                                         |

| IE         | Interrupt enable flag                                  |

| V          | Overflow flag                                          |

| BRK        | Break mode                                             |

| MD         | Mode flag (not provided to V33A and V53A)              |

| ()         | Memory contents indicated by ( )                       |

| disp       | Displacement (8/16 bits)                               |

| temp       | Temporary register (8/16/32 bits)                      |

| temp1      | Temporary register (16 bits)                           |

| temp2      | Temporary register (16 bits)                           |

| ТА         | Temporary register A (16 bits)                         |

| ТВ         | Temporary register B (16 bits)                         |

| TC         | Temporary register C (16 bits)                         |

| ext-disp8  | 16-bits as result of sign-extending 8-bit displacement |

| seg        | Immediate segment data (16 bits)                       |

| offset     | Immediate offset data (16 bits)                        |

Table 2-4. Legend of Description on Instruction Format and Operand (2/2)

| Identifier | Description                 |

|------------|-----------------------------|

| <b>←</b>   | Transfer direction          |

| +          | Add                         |

| _          | Subtract                    |

| ×          | Multiply                    |

| ÷          | Divide                      |

| %          | Modulo                      |

| ٨          | Logical product (AND)       |

| V          | Logical sum (OR)            |

| ₩          | Exclusive logical sum (XOR) |

| ×хН        | 2-digit hexadecimal value   |

| ××××H      | 4-digit hexadecimal value   |

Table 2-5. Memory Addressing

| mem mod | 00             | 01          | 10           |  |  |

|---------|----------------|-------------|--------------|--|--|

| 000     | BW+IX          | BW+IX+disp8 | BW+IX+disp16 |  |  |

| 001     | BW+IY          | BW+IY+disp8 | BW+IY+disp16 |  |  |

| 010     | BP+IX          | BP+IX+disp8 | BP+IX+disp16 |  |  |

| 011     | BP+IY          | BP+IY+disp8 | BP+IY+disp16 |  |  |

| 100     | IX             | IX+disp8    | IX+disp16    |  |  |

| 101     | IY             | IY+disp8    | IY+disp16    |  |  |

| 110     | Direct address | BP+disp8    | BP+disp16    |  |  |

| 111     | BW             | BW+disp8    | BW+disp16    |  |  |

Table 2-6. Selecting 8-/16-Bit General-Purpose Register

| reg, reg' | W = 0 | W = 1 |

|-----------|-------|-------|

| 000       | AL    | AW    |

| 001       | CL    | CW    |

| 010       | DL    | DW    |

| 011       | BL    | BW    |

| 100       | АН    | SP    |

| 101       | СН    | BP    |

| 110       | DH    | IX    |

| 111       | ВН    | IY    |

Table 2-7. Selecting Segment Register

| sreg |     |

|------|-----|

| 00   | DS1 |

| 01   | PS  |

| 10   | SS  |

| 11   | DS0 |

Figure 2-1. Description Example

ADD Addition

[Format]

#### [Operand, Operation]

| Mnemonic | Operand (dst, src) | Operation                    |

|----------|--------------------|------------------------------|

| ADD      | reg, reg'          | dst ← dst + src              |

|          | mem, reg           |                              |

|          | reg, mem           |                              |

|          | reg, imm           |                              |

|          | mem, imm           |                              |

|          | acc, imm           | [When W = 0] AL   AL + imm8  |

|          |                    | [When W = 1] AW ← AW + imm16 |

[Flag]

| AC | CY | V | Р | S | Z |

|----|----|---|---|---|---|

| ×  | ×  | × | × | × | × |

ADD dst, src

#### [Description]

Adds the contents of the destination operand (dst) specified by the first operand to the contents of the source operand (src) specified by the second operand, and stores the result to the destination operand (dst).

#### [Example]

To add the contents of memory 0:50H (word data) to the contents of the DW register, and store the result to 0.50H

MOV AW, 0 MOV DS1, AW MOV IY, 50H

ADD DS1: WORD PTR [IY], DW

#### [Number of bytes]

| Mnemonic | Operand   | No. of bytes |

|----------|-----------|--------------|

| ADD      | reg, reg' | 2            |

|          | mem, reg  | 2-4          |

|          | reg, mem  | 2-4          |

|          | reg, imm  | 3, 4         |

|          | mem, imm  | 3-6          |

|          | acc, imm  | 2, 3         |

| Mnemonic  | Operand   |            |     |      |       |      | C   | ре  | ratio | on (              | cod        | е  |        |         |       |  |  |  |

|-----------|-----------|------------|-----|------|-------|------|-----|-----|-------|-------------------|------------|----|--------|---------|-------|--|--|--|

| Winemonic | Operand   | 7          | 6   | 5    | 4     | 3    | 2   | 1   | 0     | 7                 | 6          | 5  | 4      | 3       | 2 1 0 |  |  |  |

| ADD       | reg, reg' | 0          | 0   | 0    | 0     | 0    | 0   | 1   | W     | 1                 | 1          |    | reg    |         | reg'  |  |  |  |

|           | mem, reg  | 0          | 0   | 0    | 0     | 0    | 0   | 0   | W     | m                 | od         |    | reg    |         | mem   |  |  |  |

|           |           |            |     | (0   | lisp  | -lov | v)  |     |       |                   |            | (d | isp-   | o-high) |       |  |  |  |

|           | reg, mem  | 0          | 0   | 0    | 0     | 0    | 0   | 1   | W     | m                 | od         |    | reg    |         | mem   |  |  |  |

|           |           |            |     | (0   | lisp  | -lov | v)  |     |       |                   |            | (d | isp-   | hig     | h)    |  |  |  |

|           | reg, imm  | 1          | 0   | 0    | 0     | 0    | 0   | s   | W     | 1                 | 1          | 0  | 0      | 0       | reg   |  |  |  |

|           |           |            | imr | n8 ( | or ii | nm   | 16- | low | ,     | imm16-high        |            |    |        |         | gh    |  |  |  |

|           | mem, imm  | 1          | 0   | 0    | 0     | 0    | 0   | s   | W     | m                 | mod (      |    | 0      | 0       | mem   |  |  |  |

|           |           | (disp-low) |     |      |       |      |     |     |       | (disp-high)       |            |    |        |         |       |  |  |  |

|           |           |            | imn | n8 ( | or ii | nm   | 16- | low | ,     |                   | imm16-high |    |        |         |       |  |  |  |

|           | acc, imm  | 0          | 0   | 0    | 0     | 0    | 1   | 0   | W     | imm8 or imm16-low |            |    | 16-low |         |       |  |  |  |

|           |           |            |     | im   | m1(   | 6-hi | gh  |     |       |                   |            |    |        | -       |       |  |  |  |

### ADD4S

**Decimal addition Add Nibble String**

[Format] ADD4S [DS1-spec:] dst-string, [Seg-spec:] src-string

ADD4S

[Operation] BCD string (IY, CL) ← BCD string (IY, CL) + BCD string (IX, CL)

[Operand]

| Mnemonic | Operand (dst, src)                                 |

|----------|----------------------------------------------------|

| ADD4S    | [DS1-spec : ] dst-string, [Seg-spec : ] src-string |

|          | None                                               |

[Flag]

| AC | CY | V | Р | S | Z |

|----|----|---|---|---|---|

| U  | ×  | U | U | U | × |

#### [Description]

Adds the packed BCD string addressed by the IX register to the packed BCD string addressed by the IY register, and stores the the result of the string addressed by the IY register. The string length (number of BCD digits) is determined by the CL register (the number of digits is d if the contents of CL is d) in a range of 1 to 254 digits.

The destination string must be always located in a segment specified by the DS1 register, the segment cannot be overridden. Although the default segment register of the source string is the DS0 register, the segment can be overridden, and the string can be located in a segment specified by any segment register.

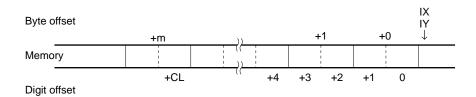

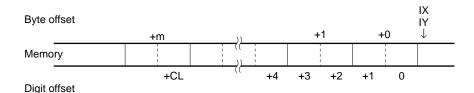

The format of a packed BCD string is as follows.

Caution The BCD string instruction always operates in units of an even number of digits. If an even number of digits is specified, therefore, the result of the operation and each flag operation are normal. If an odd number of digits is specified, however, an operation of an even number of digits, or an odd number of digits + 1, is executed. As a result, the result of the operation is an even number of digits and each flag indicates an even number of digits. To specify an odd number of digits, therefore, keep this in mind: Execute the BCD addition instruction, if the number of digits is odd, after clearing the high-order 4 bits of the most significant byte to "0". As a result, the carry is indicated by bit 4 of the most significant byte, and is not reflected in the flag.

[Example] MOV IX, OFFSET VAR\_1

MOV IY, OFFSET VAR\_2

MOV CL, 4

ADD4S

[Number of bytes] 2

| Mnemonic   | Operand                                          |  |   |   |   |   | C | ре | rati | on | cod | е |   |   |   |   |   |

|------------|--------------------------------------------------|--|---|---|---|---|---|----|------|----|-----|---|---|---|---|---|---|

| Willemonic | Operand                                          |  | 6 | 5 | 4 | 3 | 2 | 1  | 0    | 7  | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

| ADD4S      | [DS1-spec :] dst-string, [Seg-spec :] src-string |  | 0 | 0 | 0 | 1 | 1 | 1  | 1    | 0  | 0   | 1 | 0 | 0 | 0 | 0 | 0 |

|            | None                                             |  |   |   |   |   |   |    |      |    |     |   |   |   |   |   |   |

**ADDC**

Addition with carry

Add with Carry

[Format] ADDC dst, src

#### [Operand, Operation]

| Operand (dst, src) | Operation                                                                                   |

|--------------------|---------------------------------------------------------------------------------------------|

| reg, reg'          | $dst \leftarrow dst + src + CY$                                                             |

| mem, reg           |                                                                                             |

| reg, mem           |                                                                                             |

| reg, imm           |                                                                                             |

| mem, imm           |                                                                                             |

| acc, imm           | [When W = 0] AL $\leftarrow$ AL + imm8 + CY<br>[When W = 1] AW $\leftarrow$ AW + imm16 + CY |

|                    | reg, reg' mem, reg reg, mem reg, imm mem, imm                                               |

[Flag]

| AC | CY | ٧ | Р | S | Z |

|----|----|---|---|---|---|

| ×  | ×  | × | × | × | × |

#### [Description]

Adds the contents of the destination operand (dst) specified by the first operand to the contents of the source operand (src) specified by the second operand with the contents of the CY flag, and stores the result to the destination operand (dst).

[Example]

SET1 CY ; Sets CY flag to 1.

XOR AW, AW; AW = 0MOV BW, 0FFH; BW = 0FFH

ADDC AW, BW ; Contents of AW register = 100H

#### [Number of bytes]

| Mnemonic | Anemonic Operand |      |  |  |

|----------|------------------|------|--|--|

| ADDC     | reg, reg'        | 2    |  |  |

|          | mem, reg         | 2-4  |  |  |

|          | reg, mem         | 2-4  |  |  |

|          | reg, imm         | 3, 4 |  |  |

|          | mem, imm         | 3-6  |  |  |

|          | acc, imm         | 2, 3 |  |  |

| Mnemonic   | Operand   | Operation code    |            |                            |                   |      |    |    |             |      |     |    |      | ٦   |       |   |

|------------|-----------|-------------------|------------|----------------------------|-------------------|------|----|----|-------------|------|-----|----|------|-----|-------|---|

| WITCHIOTIC | Operand   | 7                 | 6          | 5                          | 4                 | 3    | 2  | 1  | 0           | 7    | 6   | 5  | 4    | 3   | 2 1 0 | ) |

| ADDC       | reg, reg' | 0                 | 0          | 0                          | 1                 | 0    | 0  | 1  | W           | 1    | 1   |    | reg  |     | regʻ  |   |

|            | mem, reg  | 0                 | 0          | 0                          | 1                 | 0    | 0  | 0  | W           | m    | od  |    | reg  |     | mem   | 1 |

|            |           |                   |            | (c                         | lisp              | -lov | v) |    |             |      |     | (d | isp- | hig | h)    |   |

|            | reg, mem  | 0                 | 0          | 0                          | 1                 | 0    | 0  | 1  | W           | m    | od  |    | reg  |     | mem   |   |

|            |           | (disp-low)        |            |                            |                   |      |    |    | (disp-high) |      |     |    |      |     |       |   |

|            | reg, imm  | 1                 | 0          | 0                          | 0                 | 0    | 0  | s  | W           | 1    | 1   | 0  | 1    | 0   | reg   |   |

|            |           |                   | imn        | n8 or imm16-low imm16-high |                   |      |    |    | gh          | ٦    |     |    |      |     |       |   |

|            | mem, imm  | 1                 | 0          | 0                          | 0                 | 0    | 0  | s  | W           | m    | od  | 0  | 1    | 0   | mem   |   |

|            |           |                   | (disp-low) |                            |                   |      |    |    | (d          | isp- | hig | h) |      |     |       |   |

|            |           | imm8 or imm16-low |            |                            | ,                 |      |    | im | m16         | 6-hi | gh  |    |      |     |       |   |

|            | acc, imm  | 0 0 0 1 0 1 0 W   |            |                            | imm8 or imm16-low |      |    | 7  |             |      |     |    |      |     |       |   |

|            |           |                   |            | im                         | m16               | 6-hi | gh |    |             |      | _   |    |      |     |       |   |

### ADJ4A

Packed decimal adjustment of result of addition

Adjust Nibble Add

[Format] ADJ4A

[Operation] Where AL  $^{\circ}$  0FH > 9 or AC = 1,

$\mathsf{AL} \leftarrow \mathsf{AL} + \mathsf{6}$

$\mathsf{AC} \leftarrow \mathsf{1}$

Where AL > 9FH or CY = 1

$\mathsf{AL} \leftarrow \mathsf{AL} + \mathsf{60H}$

$CY \leftarrow \mathbf{1}$

[Operand]

| Mnemonic | Operand |

|----------|---------|

| ADJ4A    | None    |

[Flag]

| AC | CY | V | Р | S | Z |

|----|----|---|---|---|---|

| ×  | ×  | U | × | × | × |

[Description]

$\label{eq:Adjusts} \mbox{Adjusts the contents of the AL register resulting from addition of two packed decimal}$

numbers into one packed decimal number.

[Example] ADJ4A

[Number of bytes] 1

| Mnemonic   |      | Operand |   |   |   | Operation code |   |   |   |   |  |  |  |  |  |

|------------|------|---------|---|---|---|----------------|---|---|---|---|--|--|--|--|--|

| Willemonie |      | Operand | 7 | 6 | 5 | 4              | 3 | 2 | 1 | 0 |  |  |  |  |  |

| ADJ4A      | None |         | 0 | 0 | 1 | 0              | 0 | 1 | 1 | 1 |  |  |  |  |  |

### ADJ4S

Packed decimal adjustment of result of subtraction

Adjust Nibble Subtract

[Format] ADJ4S

[Operation] Where AL  $^{\circ}$  0FH > 9 or AC = 1

$\begin{array}{l} AL \leftarrow AL - 6 \\ AC \leftarrow 1 \end{array}$

Where AL > 9FH or CY = 1

$\mathsf{AL} \leftarrow \mathsf{AL} - \mathsf{60H}$

$CY \leftarrow 1$

[Operand]

| Mnemonic | Operand |

|----------|---------|

| ADJ4S    | None    |

[Flag]

| AC | CY | V | Р | S | Z |

|----|----|---|---|---|---|

| ×  | ×  | U | × | × | × |

[Description] Adjusts the contents of the AL register resulting from subtracting two packed decimal

numbers into one packed decimal number.

[Example] SUB AW, BW

ADJ4S

[Number of bytes] 1

| Mnemonic   | Operand | Operation code |   |   |   |   |   |   |   |  |

|------------|---------|----------------|---|---|---|---|---|---|---|--|

| Willemonic |         | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| ADJ4S      | None    | 0              | 0 | 1 | 0 | 1 | 1 | 1 | 1 |  |

### **ADJBA**

Unpacked decimal adjustment of result of addition

Adjust Byte Add

[Format] ADJBA

[Operation] Where AL  $^{\circ}$  0FH > 9 or AC = 1

$AL \leftarrow AL + 6$   $AH \leftarrow AH + 1$  $AC \leftarrow 1$

$AC \leftarrow 1$   $CY \leftarrow AC$   $AL \leftarrow AL \land 0FH$

[Operand]

| Mnemonic | Operand |

|----------|---------|

| ADJBA    | None    |

[Description] Adjusts the contents of the AL register resulting from adding two unpacked decimal

numbers into one unpacked decimal number. The high-order 4 bits become 0.

[Example] ADJBA

[Number of bytes] 1

| Mnemonic   | Operand | Operation code |   |   |   |   |   |   |   |  |  |

|------------|---------|----------------|---|---|---|---|---|---|---|--|--|

| Willemonic | Operand | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

| ADJBA      | None    | 0              | 0 | 1 | 1 | 0 | 1 | 1 | 1 |  |  |

### **ADJBS**

Unpacked decimal adjustment of result of subtraction

Adjust Byte Subtract

[Format] ADJBS

[Operation] Where AL  $^{\circ}$  0FH > 9 or AC = 1

$AL \leftarrow AL - 6$   $AH \leftarrow AH - 1$   $AC \leftarrow 1$   $CY \leftarrow AC$   $AL \leftarrow AL \land 0FH$

[Operand]

| Mnemonic | Operand |

|----------|---------|

| ADJBS    | None    |

[Flag]

|   | AC | CY | ٧ | Р | S | Z |

|---|----|----|---|---|---|---|

| I | ×  | ×  | U | U | U | С |

[Description] Adjusts the contents of the AL register resulting from subtracting two unpacked decimal

numbers into one unpacked decimal number. The high-order 4-bits become 0.

[Example] SUB AW, BW

**ADJBS**

[Number of bytes] 1

| Mnemonic | Operand | Operation code |   |   |   |   |   |   |   |

|----------|---------|----------------|---|---|---|---|---|---|---|

|          | Operand | 7 6 5 4 3 2 1  |   |   |   |   | 1 | 0 |   |

| ADJBS    | None    | 0              | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

AND Logical product

[Format] AND dst, src

#### [Operand, Operation]

| Mnemonic | Operand (dst, src) | Operation                    |

|----------|--------------------|------------------------------|

| AND      | reg, reg'          | dst ← dst ^ src              |

|          | mem, reg           |                              |

|          | reg, mem           |                              |

|          | reg, imm           |                              |

|          | mem, imm           |                              |

|          | acc, imm           | [When W = 0] AL ← AL ^ imm8  |

|          |                    | [When W = 1] AW ← AW ^ imm16 |

[Flag]

| AC | CY | ٧ | Р | S | Z |

|----|----|---|---|---|---|

| U  | 0  | 0 | × | × | × |

[Description]

ANDs the contents of the destination operand (dst) specified by the first operand to the contents of the source operand (src) specified by the second operand, and stores the result to the destination operand (dst).

[Example]

MOV DW, IY AND DW, 7FFFH

[Number of bytes]

| Mnemonic | Operand   | No. of bytes |

|----------|-----------|--------------|

| AND      | reg, reg' | 2            |

|          | mem, reg  | 2-4          |

|          | reg, mem  | 2-4          |

|          | reg, imm  | 3, 4         |

|          | mem, imm  | 3-6          |

|          | acc, imm  | 2, 3         |

#### [Word format]

| Mnemonic   | Operand -                | Operation code             |     |      |       |    |     |       |   |   |             |     |      |    |     |    |  |

|------------|--------------------------|----------------------------|-----|------|-------|----|-----|-------|---|---|-------------|-----|------|----|-----|----|--|

| Willemonic | Operand                  | 7                          | 6   | 5    | 4     | 3  | 2   | 1     | 0 | 7 | 6           | 5   | 4    | 3  | 2 ′ | 0  |  |

| AND        | reg, reg'                | 0                          | 0   | 1    | 0     | 0  | 0   | 1     | W | 1 | 1           |     | reg  |    | re  | gʻ |  |

|            | mem, reg                 | 0                          | 0   | 1    | 0     | 0  | 0   | 0     | W | m | od          |     | reg  |    | mem |    |  |

|            |                          | (disp-low)                 |     |      |       |    |     |       |   |   | (disp-high) |     |      |    |     |    |  |

|            | reg, mem                 | 0                          | 0   | 1    | 0     | 0  | 0   | 1     | W | m | od          | reg |      |    | mem |    |  |

|            |                          | (disp-low)                 |     |      |       |    |     |       |   |   | (disp-high) |     |      |    |     |    |  |

|            | reg, imm <sup>Note</sup> | 1                          | 0   | 0    | 0     | 0  | 0   | 0     | W | 1 | 1           | 1   | 0    | 0  | re  | g  |  |

|            |                          |                            | imn | n8 ( | or ir | nm | 16- | low   |   |   | imm16-high  |     |      |    |     |    |  |

|            | mem, imm                 | 1                          | 0   | 0    | 0     | 0  | 0   | 0     | W | m | od          | 1   | 0    | 0  | me  | em |  |

|            |                          | (disp-low)                 |     |      |       |    |     |       |   |   | (disp-high) |     |      |    |     |    |  |

|            |                          | imm8 or imm16-low imm16-hi |     |      |       |    |     |       |   |   | imi         | m16 | 3-hi | gh |     |    |  |

|            | acc, imm                 |                            |     |      |       |    |     | 16-lo | w |   |             |     |      |    |     |    |  |

|            |                          | imm16-high                 |     |      |       |    |     |       |   |   | _           |     |      |    |     |    |  |

Note The following code may be created depending on the assembler or compiler used.

|   | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| I | 1    | 0 | 0 | 0 | 0 | 0 | 1 | W | 1 | 1 | 1 | 0 | 0 |   |   |   |

| ı | imm8 |   |   |   |   |   |   |   |   |   |   | - | - |   |   |   |

Even in this case, the instruction is executed normally. Note, however, that some emulators do not support the functions to disassemble and assemble this instruction.

BC BL Conditional branch where CY = 1

Branch if Carry

Branch if Lower

[Format] BC short-label

**BL** short-label

**[Operation]** Where CY = 1:  $PC \leftarrow PC + ext-disp8$

[Operand]

| Mnemonic | Operand     |

|----------|-------------|

| вс       | short-label |

| BL       |             |

[Flag]

| AC | CY | ٧ | Р | S | Z |

|----|----|---|---|---|---|

|    |    |   |   |   |   |

[Description]

Loads the current PC value with an 8-bit displacement added (actually, sign-extended 16 bits) to the PC when the CY flag is 1.

Execution can be branched in a segment where this instruction is placed and in an address range of -128 to +127 bytes.

[Example]

```

TEST AL, BL

BC SHORT LP4; LP4 = label

:

TEST AL, BL

BL SHORT LP5; LP5 = label

:

LP4:

```

[Number of bytes]

2

| Mnemonic | Operand     | Operation code |   |   |   |   |   |   |   |               |  |  |  |  |   |  |  |

|----------|-------------|----------------|---|---|---|---|---|---|---|---------------|--|--|--|--|---|--|--|

|          | Operand     | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7 6 5 4 3 2 1 |  |  |  |  | 0 |  |  |

| ВС       | short-label | 0              | 1 | 1 | 1 | 0 | 0 | 1 | 0 | disp8         |  |  |  |  |   |  |  |

| BL       |             |                |   |   |   |   |   |   |   |               |  |  |  |  |   |  |  |

# **BCWZ**

Conditional branch where CW = 0

Branch if CW equals Zero

[Format] BCWZ short-label

**[Operation]** Where CW = 0:  $PC \leftarrow PC + ext-disp8$

[Operand]

| Mnemonic | Operand     |

|----------|-------------|

| BCWZ     | short-label |

[Flag]

| AC | CY | V | Р | S | Z |

|----|----|---|---|---|---|

|    |    |   |   |   |   |

[Description]

Loads the current PC value with an 8-bit displacement added (actually, sign-extended 16 bits) to the PC if the value of the CW register is 0.

Execution can be branched in a segment where this instruction is placed and in an address range of -128 to +127 bytes. If the above condition is not satisfied, execution goes on to the next instruction.

[Example]

LP22:

. ADD AL, BL

BCWZ SHORT LP22 ; LP22 = label

[Number of bytes]

| Mnemonic | Operand -   | Operation code |   |   |   |   |   |   |   |       |   |   |   |   |   |   |

|----------|-------------|----------------|---|---|---|---|---|---|---|-------|---|---|---|---|---|---|

| Mnemonic |             | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7     | 6 | 5 | 4 | 3 | 2 | 1 |

| BCWZ     | short-label | 1              | 1 | 1 | 0 | 0 | 0 | 1 | 1 | disp8 |   |   |   |   |   |   |

BE

BZ

Conditional branch where Z = 1

Branch if Equal

Branch if Zero

[Format] BE short-label

BZ short-label

**[Operation]** Where Z = 1:  $PC \leftarrow PC + ext-disp8$

[Operand]

| Mnemonic | Operand     |

|----------|-------------|

| BE       | short-label |

| BZ       |             |

[Flag]

| AC | CY | ٧ | Р | S | Z |

|----|----|---|---|---|---|

|    |    |   |   |   |   |

[Description]

Loads the current PC value with an 8-bit displacement added (actually, sign-extended 16 bits) to the PC if the Z flag is 1.

Execution can be branched in a segment where this instruction is placed and in an address range of -128 to +127 bytes.

[Example]

[Number of bytes]

LOOP:

2

| Mnemonic       | Operand     | Operation code |   |   |   |   |   |   |   |   |   |   |      |   |   |     |   |

|----------------|-------------|----------------|---|---|---|---|---|---|---|---|---|---|------|---|---|-----|---|

| Mnemonic<br>BE | Орстана     | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7 | 6 | 5 | 4    | 3 | 2 | 1 ( | ) |

| BE             | short-label | 0              | 1 | 1 | 1 | 0 | 1 | 0 | 0 |   |   |   | disp | 8 |   |     |   |

| BZ             |             |                |   |   |   |   |   |   |   |   |   |   |      |   |   |     |   |

# **BGE**

Conditional branch where S + V = 0Branch if Greater Than or Equal

[Format] BGE short-label

**[Operation]** Where  $S \forall V = 0$ :  $PC \leftarrow PC + ext-disp8$

[Operand]

| Mnemonic | Operand     |

|----------|-------------|

| BGE      | short-label |

[Flag]

| AC | CY | > | Ρ | S | Z |

|----|----|---|---|---|---|

|    |    |   |   |   |   |

[Description]

Loads the current PC value with an 8-bit displacement added (actually, sign-extended 16 bits) to the PC if the result of exclusive OR (XOR) between the S and V flags is 0. Execution can be branched in a segment where this instruction is placed and in an address range of -128 to +127 bytes.

Execution goes on to the next instruction if the above condition is not satisfied.

[Example] SHL AL, 1

BGE SHORT LP16 ; LP16 = label

:

LP16:

[Number of bytes] 2

| Mnemonic | Operand     | Operation code |   |   |   |   |   |   |   |       |   |   |   |   |   |   |

|----------|-------------|----------------|---|---|---|---|---|---|---|-------|---|---|---|---|---|---|

|          | Орегани     | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7     | 6 | 5 | 4 | 3 | 2 | 1 |

| BGE      | short-label | 0              | 1 | 1 | 1 | 1 | 1 | 0 | 1 | disp8 |   |   |   |   |   |   |

**BGT**

Conditional branch where (S  $\forall$  V) v Z = 0 **Branch if Greater Than**

[Format] **BGT** short-label

$(S \forall V) \lor Z = 0$ :  $PC \leftarrow PC + ext-disp8$ [Operation]

[Operand]

| Mnemonic | Operand     |

|----------|-------------|

| BGT      | short-label |

[Flag]

| AC | CY | V | Р | S | Z |

|----|----|---|---|---|---|

|    |    |   |   |   |   |

[Description]

Loads the current PC value with an 8-bit displacement added (actually, sign-extended 16 bits) to the PC if the result of ORing between the result of exclusive OR (XOR) of the S and V flags, and the Z flag is 0.

Execution can be branched in a segment where this instruction is placed and in an address range of -128 to +127 bytes.

Execution goes on to the next instruction if the above condition is not satisfied.

[Example] LP18:

SHL AL, 1 BGT LP18

[Number of bytes]

2

| Mnemonic | Operand -   |   |   |   |   |   | С | )pei | ratio | on (  | cod | е |   |   |   |   |   |  |  |  |  |  |  |  |  |

|----------|-------------|---|---|---|---|---|---|------|-------|-------|-----|---|---|---|---|---|---|--|--|--|--|--|--|--|--|