# $\mu$ PD77230 Advanced Signal Processor

ADVANCED PRODUCT INFORMATION USER'S MANUAL March 1986

The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Electronics Inc., at its own discretion, may withdraw the device prior to production.

The information in this document is subject to change without notice. NEC Electronics Inc. assumes no responsibility for any errors or omissions that may appear in this document. Devices sold by NEC Electronics Inc. are covered by the warranty and patent indemnification provisions appearing in NEC Electronics Inc. Terms and Conditions of Sale only. NEC Electronics Inc. makes no warranty, express, statutory, implied, or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. NEC Electronics Inc. makes no warranty of merchantability or fitness for any purpose. NEC Electronics Inc. makes no commitment to update or to keep current the information contained in this document. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc.

|   |   |   | - |   |   |   |

|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |

|   |   |   |   |   | • |   |

|   |   |   |   |   | - |   |

|   | • |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

| ه |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   | • |

|   |   | • |   |   |   | • |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   | • |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

| • |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   | , |   |   |   |   |   |

|   |   | - |   |   | * |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   | • |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   | , |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   | • | • |   | • |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

# uPD77230 User's Manual

# TABLE OF CONTENTS

| 1. | INTRO                    | DUCTION1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 1.1<br>1.2<br>1.3<br>1.4 | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2. | PIN F                    | UNCTIONS2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3. | HARDW                    | ARE ARCHITECTURE3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|    | 3.1                      | Instruction ROM and Associated Circuits3-1 3.1.1 Instruction ROM3-1 3.1.2 Program counter3-1 3.1.3 Stack and stack pointer3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    | 3.2                      | Data ROM and Associated Circuits3-3 3.2.1 Data ROM3-3 3.2.2 ROM pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|    | 3.3                      | Data RAMs and Associated Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|    | 3.4                      | Floating point multiplier section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|    | 3.5                      | Processing Unit       3-1         3.5.1 P register       3-1         3.5.2 Q register       3-1         3.5.3 Shift and count circuit       3-2         3.5.4 Barrel shifter       3-2         3.5.5 Arithmetic and logic unit       3-2         3.5.6 Exponent arithmetic and logic unit       3-2         3.5.7 Working registers       3-2         3.5.8 Processor status words       3-2         3.5.9 Loop counter       3-3         3.5.10 Shift value register       3-3         3.5.11 Temporary register       3-3         3.5.12 Overflow and underflow processing       3-3 |

|    | 3.6                      | System Control Section3-3 3.6.1 Clock generator3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            | 3.6.2 Interrupt controller        |

|------------|-----------------------------------|

| 3.7        | Serial I/O Interface              |

| 3.8        | Parallel Interface in Master Mode |

| 3.9        | Parallel Interface in Slave Mode  |

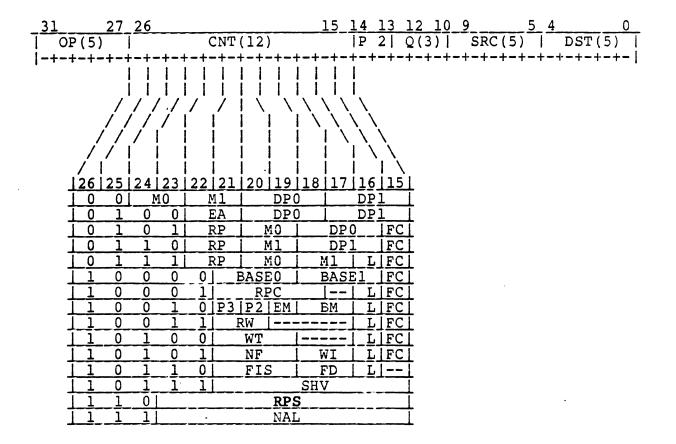

| 4. INST    | RUCTION SET4-1                    |

| 4.1<br>4.2 |                                   |

| 4.3        | OP Instruction                    |

| 4.4        | Data Load Instruction4-7          |

| 4.5        | Branch Instruction                |

| APPENDIX   | A. INSTRUCTION PIPELININGA-1      |

#### CHAPTER 1 INTRODUCTION

#### 1.1 General

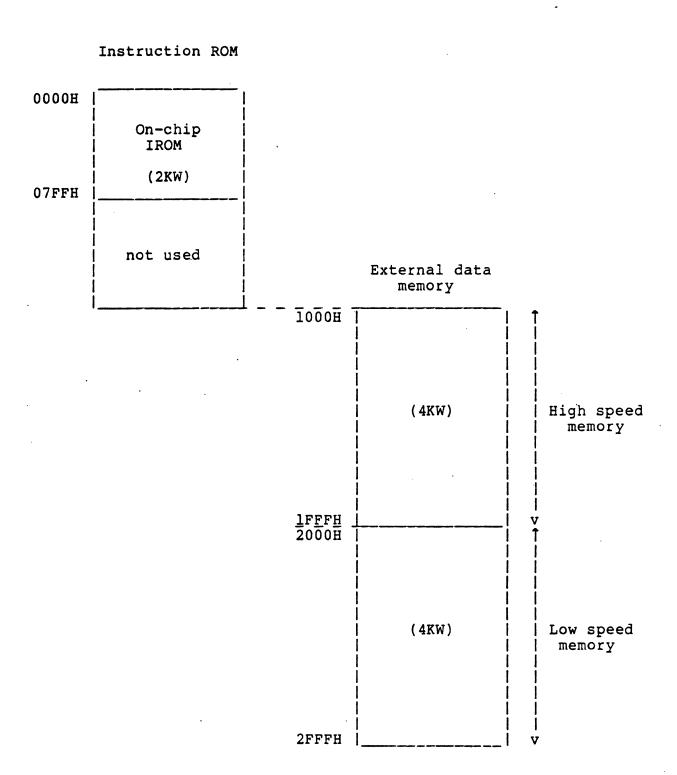

The uPD77230R Advanced Signal Processor (ASP) is a digital signal processor designed for both high speed and high accuracy. It can execute arithmetic operations with 32-bit floating-point data (8-bit exponent, 24-bit mantissa) or with 24-bit fixed-point data at a rate as fast as 150 ns/instruction. Its internal circuitry consists of a floating-point multiplier (32 bits x 32 bits), a 55-bit floating-point ALU, 2K x 32 bits of instruction ROM, 1K x 32 bits of data ROM, and a pair of separately addressable data RAM blocks, each one 512 x 32 bits. Two operation modes are available: master, and slave, which are externally selected. With master mode specified, up to 8K x 32 bits of external memory can be used, with up to 4K of that space usable for instruction memory. In slave mode, the uPD77230R has a 16-bit I/O port under control of a host processor, and can also support up to 8K words of external memory.

#### 1.2 Features

- 1) Arithmetic operation using 32-bit floating-point or 24-bit fixed-point data.

- \* 32-bit floating-point multiplier (8-bit exponent, 24 bit mantissa input, and 8-bit exponent, 47-bit mantissa output).

- \* 55-bit floating-point ALU (can also perform 47-bit fixed point ALU functions).

- \* 8 Working Registers, each 55 bits long.

- \* 47-bit bidirectional barrel shifter.

- 2) High-speed operation and effective data transfer.

- \* Instruction cycle of 150 ns max.

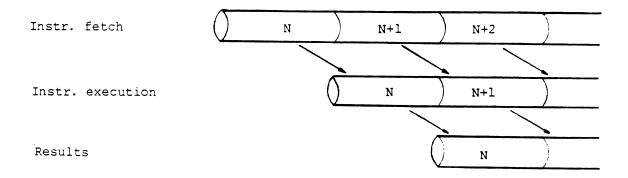

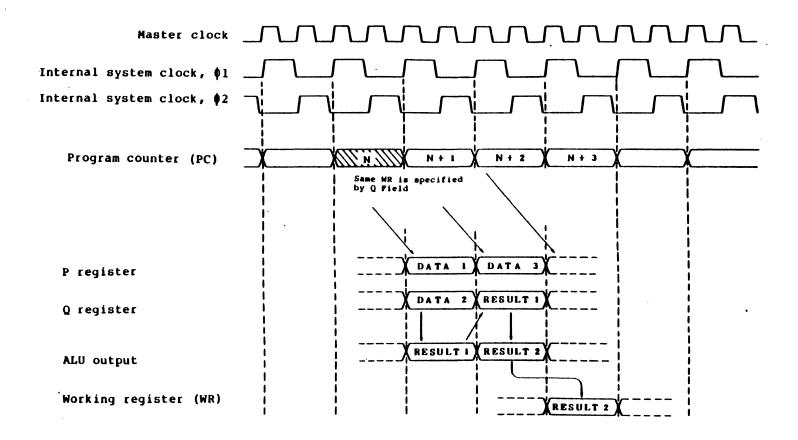

- \* Use of three-stage pipelining process.

- \* Dedicated data busses for internal RAM, multiplier, and ALU.

- 3) Architecture ideal for digital signal processing.

- \* Two separately addressable data RAM blocks.

- \* Data RAM pointers can perform ring count (modulo) operation.

- \* Data ROM pointer can be incremented by 2\*\*N, as well as ordinary increment and decrement.

- \* Both inputs to the multiplier can be loaded simultaneously with an ALU operation (which has access to the previous multiplier result) and pointer modification.

- 4) External interface may be used in a variety of system configurations.

- \* Master/slave mode selectable.

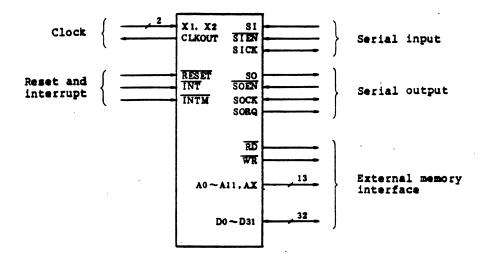

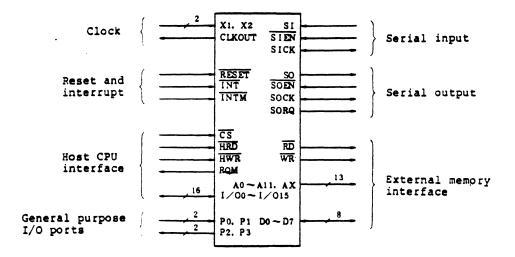

Figure 1-1. Master and slave mode functional pin groups.

a) Master mode.

b) Slave mode.

#### 1.3 Functional Blocks

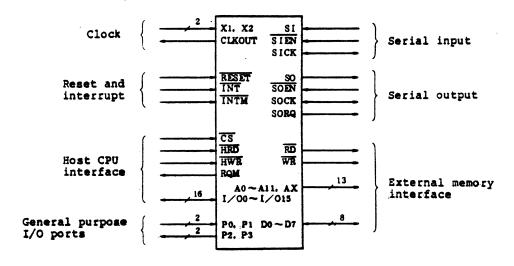

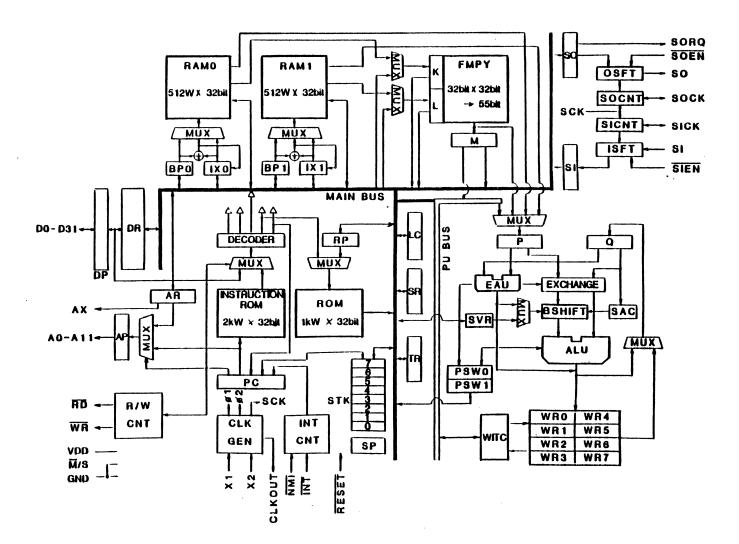

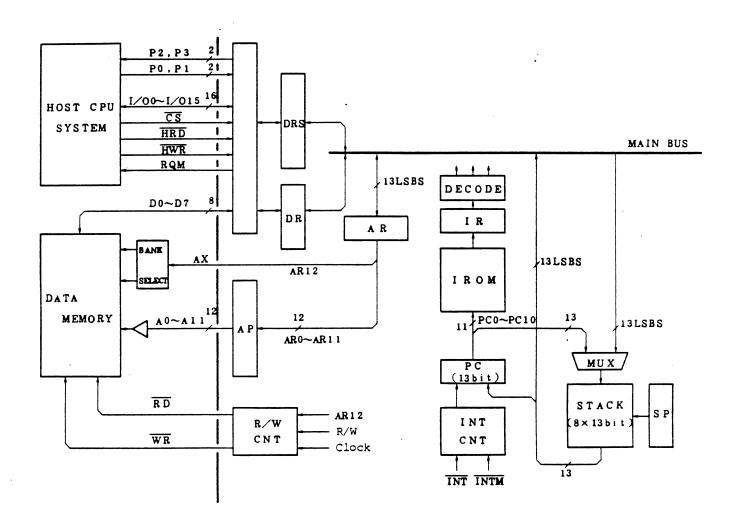

Figures 1-2 and 1-3 are the block diagrams of the uPD77230R. The internal circuitry can be broadly divided into the following functional blocks:

- \* Arithmetic operation processing section, including multiplier and ALU.

- \* Memory section, consisting of a data ROM and two separately addressable data RAM blocks.

- \* Instruction ROM.

- \* Parallel and serial I/O interface.

Table 1-1 lists the function of each block.

Figure 1-2. Master mode block diagram.

Figure 1-3. Slave mode block diagram.

Table 1-1. Functional blocks of the uPD77230R.

Multiplier and associated circuits

|                           | ISSACTUTED CITCUIT                      |                                                                                                                                    |

|---------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| <pre>  Abbreviation</pre> | Name                                    | Function                                                                                                                           |

| FMPY<br> <br> <br> <br>   | Floating-point<br>  multiplier<br> <br> | Multiplier for 32-bit<br>  floating-point data (8-bit  <br>  exponent, 24-bit mantissa)  <br>  32 bits X 32 bits ->  <br>  55 bits |

| K                         | K register<br>                          | Retains data input to FMPY   (32 bits)                                                                                             |

| L                         | L register<br>                          | Retains data input to FMPY   (32 bits)                                                                                             |

| M<br>                     | M register<br>                          | Retains multiplication  <br>  result of FMPY (55 bits)                                                                             |

| Abbreviation | ted circuits Name                                 | Function                                                            |

|--------------|---------------------------------------------------|---------------------------------------------------------------------|

| ALU          | Arithmetic and                                    | Performs arithmetic and                                             |

|              | logical unit                                      | logical operations on 47-bit mantissa data                          |

| EAU          | Exponent                                          | Performs arithmetic and                                             |

|              | arithmetic and                                    | logical operations on 8-bi                                          |

|              | logical unit                                      | exponent data                                                       |

| P            | P register  <br>                                  | <ul> <li>Retains data input to ALU<br/>and EAU (55 bits)</li> </ul> |

| Q            | Q register                                        | Retains data input to ALU and EAU (55 bits)                         |

| SAC          | Shift and count  <br>  circuit                    | Detects shift value of mantissa value in O                          |

| BSHIFT       | Barrel shifter                                    | Barrel shifter for mantisson in O and P registers                   |

| SVR          | Shift value  <br>  register                       | Sets shift value                                                    |

| WRO to WR7   | Working regis-  <br>  ters 0 to 7                 | Retain arithmetic operation results of ALU and EAU                  |

| PSW0         | Processor status <br>  word 0                     | Indicates arithmetic operation result status of ALU and EAU         |

| PSW1         | Processor status <br>  word 1                     | Indicates arithmetic operation result status of ALU and EAU         |

| WRTC         | Working regis-  <br>  ter transfer  <br>  control | Control format of transfer to/from working registers                |

Table 1-1 cont'd.

Data memories and associated circuits

| Abbreviation | Name                  | Function                                          |

|--------------|-----------------------|---------------------------------------------------|

| DATA ROM     | Data ROM              | Stores fixed data (lK words <br>  X 32 bits)      |

| RP           | ROM pointer           | Indicates current data  <br>  ROM address         |

| DATA RAM 0   | Data RAM 0            | Stores data (512 words X   32 bits)               |

| BASE 0       | Base pointer 0        | Indicates current base<br>  address of data RAM 0 |

| INDEX 0      | Index register<br>  0 | Indicates current index address of data RAM 0     |

| DATA RAM 1   | Data RAM l            | Stores data (512 words X   32 bits)               |

| BASE 1       | Base pointer l        | Indicates current base     address of data RAM l  |

| INDEX 1      | Index register<br>  1 | Indicates current index address of data RAM 1     |

| ADD          | Adder                 | Adder for base address and   index address        |

Instruction ROM and associated circuits

| Instruction RUM | and associated cir     | tcuits                                                             |

|-----------------|------------------------|--------------------------------------------------------------------|

| Abbreviation    | Name                   | Function                                                           |

| INSTRUCTION     | Instruction ROM        | Stores instructions (2K                                            |

| ROM             |                        | words X 32 bits)                                                   |

| PC              | Program counter        | Indicates current address  <br>  of instruction ROM<br>  (13 bits) |

| STACK           | Stack                  | Eight-level 13-bit stack                                           |

| SP              | Stack pointer          | Indicates current address  <br>  of stack                          |

| IR              | Instruction register   | Retains data output from   instruction ROM                         |

| DECODE          | Instruction<br>decoder | Decodes instructions                                               |

Table 1-1 cont'd.

| Parallel interface . |                  |                                      |  |  |  |

|----------------------|------------------|--------------------------------------|--|--|--|

| Abbreviation         | Name             | Function                             |  |  |  |

| DP                   | Data port        | In master mode, a 32-bit             |  |  |  |

| 1                    |                  | parallel data bus for                |  |  |  |

| 1                    | ,                | external memory                      |  |  |  |

|                      | <b>[</b>         | In slave mode, consists of           |  |  |  |

| 1                    |                  | an 8-bit parallel data bus           |  |  |  |

|                      | <b>[</b>         | for external memory, a 16-           |  |  |  |

|                      |                  | bit parallel data bus for            |  |  |  |

| 1                    | 1                | host I/O interfacing, read/          |  |  |  |

| 1                    |                  | write control signals from           |  |  |  |

|                      |                  | the host, and a general-             |  |  |  |

|                      |                  | <pre>purpose parallel I/O port</pre> |  |  |  |

| AP                   | Address port     | In master mode, a 12-bit             |  |  |  |

|                      |                  | address bus for external             |  |  |  |

| 1                    |                  | instruction and data                 |  |  |  |

|                      | ]                | memory                               |  |  |  |

| ,                    | <b>]</b> ·       | In slave mode, a 12-bit              |  |  |  |

| 1                    | 1                | address bus for external             |  |  |  |

|                      |                  | data memory                          |  |  |  |

| DR                   | Data register    | In master mode, a register           |  |  |  |

|                      |                  | for interfacing the DP with          |  |  |  |

|                      | ]                | the internal data bus                |  |  |  |

|                      | ·                | In slave mode, a register            |  |  |  |

| ļ                    |                  | for interfacing the DP (8-           |  |  |  |

| 1                    |                  | bit parallel data bus for            |  |  |  |

| 1                    |                  | external data memory) with           |  |  |  |

| ļ                    |                  | the internal data bus                |  |  |  |

| DRS                  | Data register    | In slave mode, a register            |  |  |  |

|                      | for slave        | for interfacing the DP (16-)         |  |  |  |

|                      |                  | bit parallel data bus for            |  |  |  |

|                      | ·                | host I/O) with the internal          |  |  |  |

| ļ                    |                  | data bus                             |  |  |  |

| AR                   | Address register |                                      |  |  |  |

| 1                    |                  | of external data memory              |  |  |  |

| HOST R/W CNT         | Host CPU read/   | In slave mode, controls              |  |  |  |

|                      | write control    | interfacing the uPD77230R            |  |  |  |

|                      | circuit          | with a host CPU                      |  |  |  |

| R/W CNT              | Read/write       | Controls read/write of               |  |  |  |

| <b></b>              | control circuit  | external memory                      |  |  |  |

Table 1-1 cont'd.

Serial input/output interface

| Abbreviation | Name                               | Function                   |

|--------------|------------------------------------|----------------------------|

| SO           | Serial output<br>  data register   | Retains serial output data |

| OSFT         | Output shift register              | Serially outputs SO data   |

| SOCNT        | Serial output<br>  control circuit | Controls serial output     |

| SI           | Serial input<br>  data register    | Retains serial input data  |

| ISFT         | Input shift<br>  reqister          | Inputs serial data         |

| SICNT        | Serial input<br>  control circuit  | Controls serial input      |

Other control circuits

| Other Control C. | IICUICS                   |                                                      |

|------------------|---------------------------|------------------------------------------------------|

| Abbreviation     | Name                      | Function                                             |

| CLK GEN          | Clock generator           | Generates internal system clock and serial I/O clock |

| INT CNT          | Interrupt<br>  controller | Controls external interrupts                         |

| TR               | Temporary<br>  reqister   | General-purpose temporary register (32 bits)         |

| LC LC            | Loop counter              | Controls the number of times a program will loop     |

| SR               | Status register           | Specifies or indicates current mode of operation     |

#### 1.4 Data Format

The uPD77230R is capable of processing both fixed-point and floating-point data.

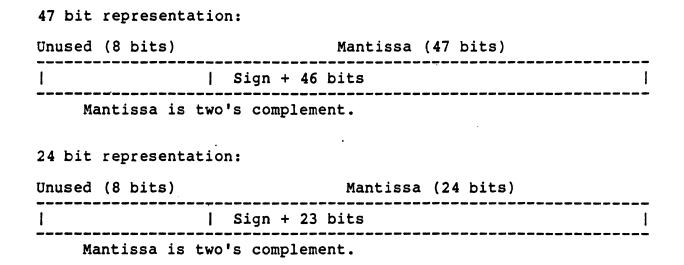

## 1.4.1 Floating-point data format

The data on the 32-bit internal data bus, and associated 32-bit registers, consists of an 8-bit exponent in the highest 8 bits, and a 24 bit mantissa in the lower 24 bits. The 55-bit processing unit bus and associated 55-bit registers (M, P, Q, WR0-WR7) contain data that consists of an 8-bit exponent in the highest 8 bits, and a 47-bit mantissa in the lower 47 bits.

Both the exponent and mantissa are represented in two's complement notation, with their most significant bit being a sign bit.

# Exponent (8 bits) | Sign + 7 bits | Sign + 46 bits | Both exponent and mantissa are two's complement | Sign + 7 bits | Sign + 23 bits | Both exponent and mantissa are two's complement

Figure 1-4. Floating point data formats.

Table 1-2. Internal 32-bit floating point data format.

|                                         | Binary rep | oresentation | Hexadecimal representation |          | Decimal representation                                          |  |

|-----------------------------------------|------------|--------------|----------------------------|----------|-----------------------------------------------------------------|--|

|                                         | Exponent   | Mantissa     | Exponent                   | Mantissa |                                                                 |  |

| Max. positive value                     | 01111111   | 01111111     | 7P                         | 7PPPPP   | $(1.0-2^{-23}) \times 2^{127} = 1.7 \times 10^{38}$             |  |

| :<br>:                                  | 01111111   | 01111110     | 7 P                        | 7PFPPE   | (1.0-2 <sup>-22</sup> )×2 <sup>127</sup>                        |  |

| \$<br>\$                                |            | 1            |                            | :        |                                                                 |  |

| <b>:</b><br><b>:</b>                    | 00000110   | 01000000     | 60                         | 1 400000 | $(1.0-2^{-1}) \times 2^{6} = 32$                                |  |

| \$<br>\$<br>\$                          | <br> <br>  | t<br>:       |                            | :<br>:   |                                                                 |  |

| Hin. positive value                     | 10000000   | 00000001     | 80                         | 000001   | (2 <sup>-23</sup> )x2 <sup>-128</sup> # 3.5x10 <sup>-46</sup>   |  |

| Zero                                    | 10000000   | 00000000     | 80                         | 000000   | 0.0                                                             |  |

| Max. negative value                     | 10000000   | 11111111     | 80                         | PPPPPP   | -(2 <sup>-23</sup> )x2 <sup>-128</sup> s -3.5x10 <sup>-46</sup> |  |

| 2<br>2<br>2                             |            | \$<br>\$     |                            | :        |                                                                 |  |

| :<br>:                                  | 00000110   | 11000000     | 60                         | C00000   | $(-1.0+2^{-1}) \times 2^6 = -32$                                |  |

| . # # # # # # # # # # # # # # # # # # # |            | :            |                            | :        |                                                                 |  |

| 1<br>1                                  | 01111111   | 10000001     | 7 P                        | 800001   | (-1.0+2 <sup>-23</sup> )×2 <sup>127</sup>                       |  |

| :<br>Min. negative value                | 01111111   | 10000000     | 7F                         | 800000   | $-1.0 \times 2^{127} = -1.7 \times 10^{38}$                     |  |

Table 1-3. Internal 55-bit floating point data format.

|                            | Binary reg | resentation | Hexadecimal representation |                                        | Decimal representation                               |  |

|----------------------------|------------|-------------|----------------------------|----------------------------------------|------------------------------------------------------|--|

|                            | Exponent   | Mantissa    | Exponent                   | Mantissa                               |                                                      |  |

| Max. positive value        | 01111111   | 01111111    | 7P                         | 7PFPFPFPPPB                            | $(1.0-2^{-46}) \times 2^{127} = 1.7 \times 10^{38}$  |  |

| 1                          | 01111111   | 01111110    | 7P                         | 7PPPPPPPPPC                            | (1.0-2 <sup>-45</sup> )×2 <sup>127</sup>             |  |

| 3<br>3<br>8                |            | ;<br>;      |                            | ** *** *** *** *** *** *** *** *** *** |                                                      |  |

| 3                          | 00000110   | 01000000    | <br>  60<br>               | 1 400000000000                         | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |  |

| 8                          |            | . 1<br>1    |                            | :<br>:                                 |                                                      |  |

| Min. positive value        | 10000000   | 00000001    | 80                         | 000000000002                           | $(2^{-46}) \times 2^{-128} = 4.2 \times 10^{-53}$    |  |

| Zero                       | 10000000   | 00000000    | 80                         | 000000000000                           | 0.0                                                  |  |

| Max. negative value        | 10000000   | 11111111    | 80                         | PPPPPPPPPPB                            | -(2-46)x2-128 # -4.2x10-53                           |  |

| 3<br>3                     |            | \$<br>8     |                            | :<br>:                                 |                                                      |  |

|                            | 00000110   | 11000000    | 60                         | 1 C0000000000                          | $(-1.0+2^{-1}) \times 2^6 = -32$                     |  |

| *<br>*                     |            | :<br>:      | <br> <br>                  | :<br>:                                 |                                                      |  |

| 1                          | 01111111   | 10000001    | 7 <b>P</b>                 | 800000000002                           | (-1.0+2 <sup>-46</sup> )x2 <sup>127</sup>            |  |

| :<br>  Min. negative value | 01111111   | 10000000    | 7 <b>F</b>                 | 80000000000                            | $-1.0 \times 2^{127} = -1.7 \times 10^{38}$          |  |

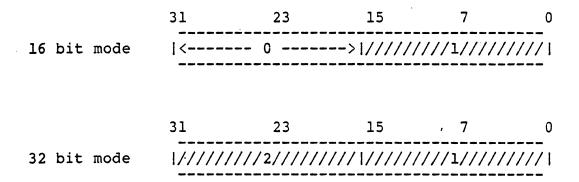

## 1.4.2 Fixed-point data format

The data on the 32-bit internal data bus, and associated 32-bit registers, consists of a 24 bit mantissa in the lower 24 bits, with the 8 MSBs unused. The 55-bit Processing Unit bus and associated 55-bit registers (M, P, Q, WR0-WR7) contain data that consists of a 47-bit mantissa in the lower 47 bits, with the upper 8 bits unused.

The mantissa is represented in two's complement notation, with the most significant bit being a sign bit.

Figure 1-5. Fixed point data formats.

Table 1-4. Internal 24-bit fixed point data format.

| ·                        | Binary rep   | resentation | Hexadecima<br>  representa |          | Decimal representation                  |  |

|--------------------------|--------------|-------------|----------------------------|----------|-----------------------------------------|--|

|                          | Exponent     | Mantissa    | Exponent                   | Mantissa |                                         |  |

| Max. positive value      | -            | 01111111    | -                          | 7FFFFP   | 1.0-2 <sup>-23</sup> = 1.0              |  |

| :                        | -            | 01111110    | -                          | 7PFPPE   | 1.0-2-22                                |  |

| :                        |              | :<br>:      |                            | · :      |                                         |  |

| :                        | -            | 01000000    | -                          | 400000   | 1.0-2-1 = 0.5                           |  |

| ;<br>;                   |              | . :         | \$<br>\$                   |          |                                         |  |

| Min. positive value      | -            | 00000001    |                            | 000001   | 2 <sup>-23</sup> s 1.2x10 <sup>-7</sup> |  |

| Zero                     | -            | 00000000    | -                          | 000000   | 0.0                                     |  |

| Max. negative value      | -            | 11111111    | -                          | PPPFPF   | $-2^{-23} = -1.2 \times 10^{-7}$        |  |

| :                        |              | \$<br>\$    |                            | :        |                                         |  |

| :                        | -   11000000 |             | -                          | C00000   | $-1.0+2^{-1} = -0.5$                    |  |

| ;<br>;                   | 1            |             |                            | i<br>:   |                                         |  |

| <b>1</b><br>:            | -            | 10000001    | -                          | 800001   | -1.0+2-23                               |  |

| :<br>Min. negative value | -            | 10000000    | -                          | 800000   | -1.0                                    |  |

Table 1-5. Internal 47-bit fixed point data format.

|                            | Binary rep | resentation | Hexadecima<br>  representa |                      | Decimal representation                     |

|----------------------------|------------|-------------|----------------------------|----------------------|--------------------------------------------|

|                            | Exponent   | Mantissa    | Exponent                   | Mantissa             |                                            |

| Max. positive value        | -          | 01111111    | -                          | 7FFFFFFFFFE          | 1.0-2 <sup>-46</sup> # 1.0                 |

|                            | -          | 01111110    | -                          | 7 <b>FFFFFFFFF</b> C | 1.0-2-45                                   |

|                            |            | :<br>:      |                            | :<br>:               | ·                                          |

| <b>.</b>                   | -          | 01000000    | -                          | 400000000000         | $1.0-2^{-1} = 0.5$                         |

| :<br>:                     |            | · •         |                            | :                    |                                            |

| :<br>Min. positive value   | -          | 00000001    | _                          | 000000000002         | $2^{-46} = 1.4 \times 10^{-14}$            |

| Zero                       | -          | 00000000    | -                          | 000000000000         | 0.0                                        |

| Max. negative value        | -          | 11111111    | -                          | PPFPPPPPPPB          | -2 <sup>-46</sup> m -1.4x10 <sup>-14</sup> |

|                            |            | :<br>:      |                            | :<br>:               |                                            |

| :                          | -          | 11000000    | _                          | C00000000000         | -1.0+2 <sup>-1</sup> = -0.5                |

| !<br>!<br>!                |            |             |                            | :                    |                                            |

| :<br>:                     | -          | 10000001    | _                          | 800000000002         | -1.0+2-46                                  |

| 1<br>  Min. negative value | -          | 10000000    | -                          | 800000000000         | 1 -1.0                                     |

|   |   |        |   |     | • |   |  |

|---|---|--------|---|-----|---|---|--|

|   |   | •      |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        | , |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   | • |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

| • |   |        |   | o . |   |   |  |

|   |   |        |   |     |   | ٠ |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   | • |        |   |     |   |   |  |

|   |   |        |   |     |   |   |  |

|   |   | w.c.s. | ٠ |     |   |   |  |

|   |   |        |   |     |   |   |  |

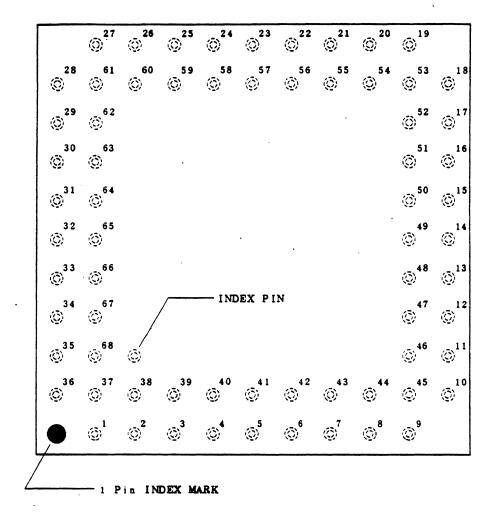

#### CHAPTER 2 PIN FUNCTIONS

The uPD77230R is housed in a 68-pin grid array package, as shown in Figure 2-1. Pin assignments are listed in Table 2-1, and functional descriptions of each pin are given in Tables 2-2 thru 2-4.

Figure 2-1. 68-pin grid array package (top view).

Table 2-1. uPD77230R pin assignments.

| PIN #           | MASTER                      | SLAVE               | PIN #      | MASTER     | SLAVE    |

|-----------------|-----------------------------|---------------------|------------|------------|----------|

| 1               |                             | 00                  | 35         |            | 02       |

| 2<br>  3<br>  4 |                             | 11                  | 1 36       |            | 01       |

| 1 3             |                             | 13                  | 1 37       |            | A0       |

| 4               |                             | 15                  | 1 38       |            | A2       |

| 5               |                             | 16                  | 39         |            | 44       |

| j 6             |                             | 18                  | 40         | . Vo       |          |

| 8.              | A]                          | •                   | 41         | •          | A7       |

|                 |                             | Ax                  | 42         |            | 49       |

| 9 10            | WE                          |                     | 43<br>  44 | A.         |          |

| 111             | RI<br>S                     | DRQ                 | 1 44       |            | ND [     |

| 1 12            |                             | OCK I               | 45         | ▼          | ICK I    |

| 13              | SOF                         | •                   | 47         | •          | EN/      |

| 14              | •                           | NT/                 | 48         |            | Connect) |

| 15              | INI                         |                     | 49         |            | SET/     |

| 16              | (M/)                        |                     | 50         |            | SI I     |

| 17              | CLKC                        |                     | 51         |            | ζ2       |

| 1 18            |                             | (1                  | 52         | Vo         |          |

| 1 19            | D31                         | P3                  | 53         | D30        | P2       |

| 20              | D29                         | P1                  | 54         | D28        | PO       |

| 21              | D27                         | RQM                 | 1 55       | D26        | CS/      |

| 22              | D25                         | HWR/                | 56         | G1 G1      |          |

| 23              | D24                         | HRD/                | 57         | D23        | I/O 15   |

| 24              | D22                         | 1/0 14              | 58         | D21        | I/O 13   |

| 25<br>  26      | D20                         | I/O 12              | 59         | D19 Vo     | I/O 11   |

| 27              | D18   D17                   | I/O 10  <br>  I/O 9 | 60<br>  61 | D15        | I/O 7    |

| 28              | D17                         | I/O 8               | 62         | D13        | I/O 5    |

| 29              | D16   1/0 8     D14   I/0 6 |                     | 63         | D13        | I/O 3    |

| 30              | D12                         | I/O 4               | 64         | D9         | I/O 1    |

| 31              | D10                         | I/O 2               | 65         |            | 7        |

| 32              | D8                          | 1/0 0               | 66         | •          | )5 i     |

| 33              |                             | 6                   | 67         |            | )3 i     |

| 34              | •                           | ) <u>4</u>          | 68         | <u>G</u> 1 | •        |

|                 |                             |                     | INDE       | K PIN      |          |

# FUNCTIONAL PIN DESCRIPTIONS

Table 2-2. Pin functions shared by master and slave modes.

# \* POWER SUPPLY

| NAME | #  | 1/0 | FUNCTION                         |

|------|----|-----|----------------------------------|

| Vdd  | 40 | -   | +5V power supply pins. All       |

| İ    | 52 |     | of these pins must be connected. |

|      | 60 |     | <u> </u>                         |

| GND  | 44 | _   | Ground pins. All of these        |

| İ    | 56 |     | pins must be connected.          |

| 1    | 68 |     |                                  |

#### \* MODE SETTING

| I       | NAME   | #  | 1/0   | FUNCTION                            |

|---------|--------|----|-------|-------------------------------------|

| T       | (M/)/S | 16 | Input | Selects the operation mode. The     |

| 1       |        |    |       | operation mode must not be switched |

|         |        |    |       | during operation, however.          |

| 1       |        |    |       | 0: Master mode                      |

| $\perp$ |        |    |       | 1: Slave mode                       |

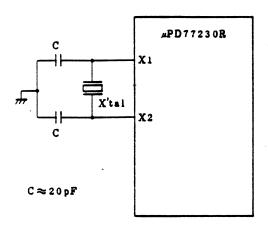

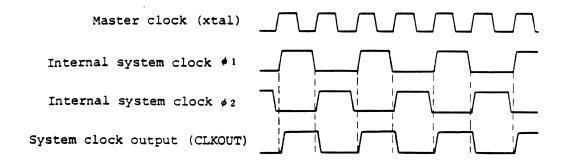

# \* CLOCK

| NAME   | #  | 1/0    | FUNCTION                            |

|--------|----|--------|-------------------------------------|

| Xl     | 18 |        | A crystal oscillator is connected   |

| X2     | 51 |        | across these pins. External clock   |

|        |    |        | should be input via the Xl pin.     |

| CLKOUT | 17 | Output | Outputs internal system clock of    |

|        |    |        | uPD77230R. The output signal        |

|        |    |        | frequency is half the oscillation ! |

| 1      |    | l l    | frequency of the crystal connected  |

| 1      |    | LJ     | across the X1 and X2 pins.          |

# \* RESET/INTERRUPT

| NAME   | #  | 1/0   | FUNCTION                             |

|--------|----|-------|--------------------------------------|

| RESET/ | 49 | Input |                                      |

| 1      |    |       | which is active-low and must be at   |

|        |    | L     | least 3 system clock pulses wide.    |

| INT/   | 14 | Input | Inputs non-maskable interrupt signal |

| 1      |    | _     | which is active-low and must be at   |

| 1      |    |       | least 3 system clock pulses wide.    |

| 1      |    |       | The interrupt signal is detected at  |

| 1      |    |       | the falling edge. The interrupt      |

|        |    |       | address is 10H.                      |

Table 2-2 cont'd.

| NAME  | #        | I/O   | FUNCTION                            |

|-------|----------|-------|-------------------------------------|

| INTM/ | 15       | Input | Inputs maskable interrupt signal    |

|       | İ I      | _     | which is active-low and must be at  |

| İ     | 1 1      |       | l least 3 system clock pulses wide. |

| İ     | 1        |       | The interrupt signal is detected at |

| İ     | İ        |       | the falling edge. The interrupt     |

| i     | <u> </u> |       | address is 100H.                    |

# \* SERIAL INTERFACE

| NAME   | #                               | I/0                          | FUNCTION                                                                                                                                                                                                                                                                                                                 |

|--------|---------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

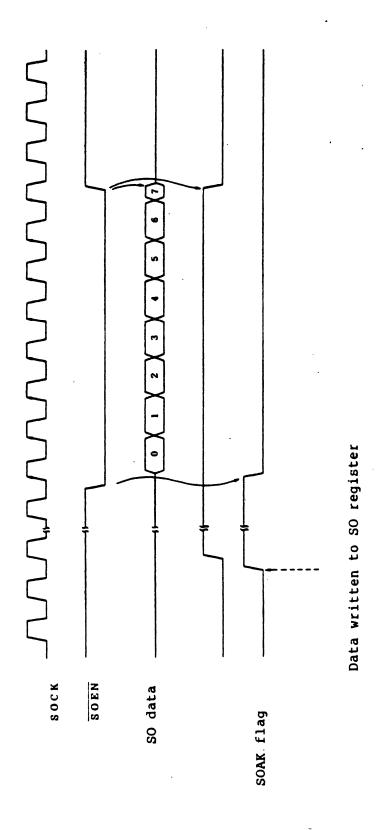

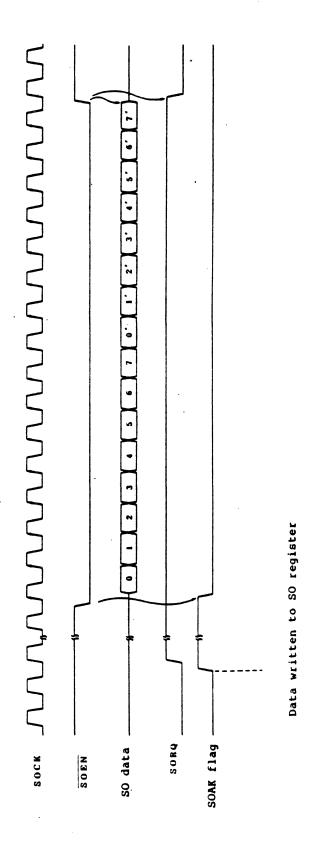

| SOCK   | 12                              | I/O                          | Inputs or outputs clock for serial output data. The serial output data is synchronized with the clock that is input to or output from this pin.  Whether the clock is to be input from an external source or the internal clock is to be output is determined by the setting of the status register.                     |

| SORQ   | 11                              | Output                       |                                                                                                                                                                                                                                                                                                                          |

| SOEN/  | 13                              | Input                        | Enables the SO pin to output serial data. This pin is active-low.                                                                                                                                                                                                                                                        |

| SO<br> | 45<br>                          | Output <br>(Tri-  <br>State) |                                                                                                                                                                                                                                                                                                                          |

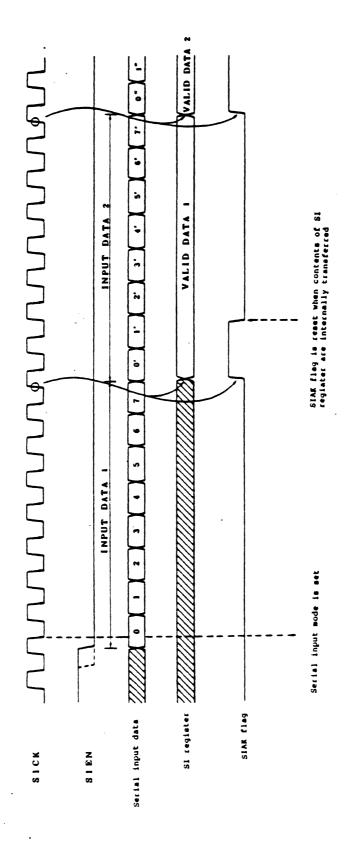

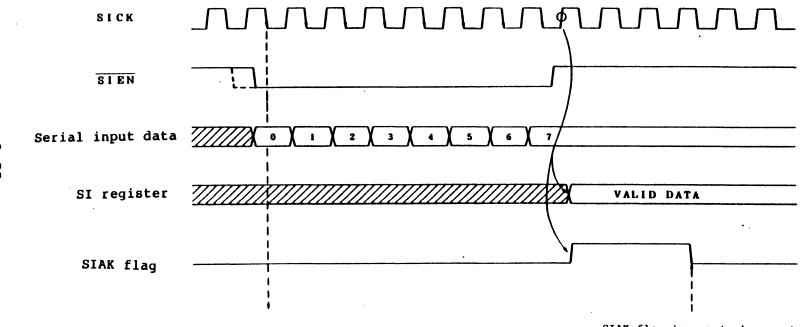

| SICK   | 46<br> <br> <br> <br> <br> <br> | 1/0                          | Inputs or outputs the clock for serial input data. The serial data is internally latched at the falling edge of the clock that is input to or output from this pin.  Whether the clock is to be input from an external source or the internal clock is to be output is determined by the setting of the status register. |

| SIEN/  | 47                              | Input                        | Enables the SI pin to input serial data. This pin is active-low.                                                                                                                                                                                                                                                         |

| SI     | 50<br>                          | Input                        | Inputs serial data synchronized with   the falling edge of the SICK pin.                                                                                                                                                                                                                                                 |

Table 2-3. Pin functions available only in master mode.

# \* EXTERNAL MEMORY INTERFACE

| NAME                   | #          | I/O                        | FUNCTION                                                                                                                                                                                                                                                                      |

|------------------------|------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WR/<br> <br> <br> <br> | 9<br> <br> | Output<br> <br>            | Controls data write to external memory. This signal becomes 0 after the output address is valid and data is output to the data port formed by pins D0 to D31.                                                                                                                 |

| RD/<br> <br> <br>      | 10         | Output                     | Controls data read from external memory. This signal becomes 0 after the output address is valid, and data is input at the rising edge to the data port formed by pins D0 to D31.                                                                                             |

| AX                     | 8          | Output                     |                                                                                                                                                                                                                                                                               |

| A0 to<br>A11           | 88         | Output                     | Address bus for access to external memory.  When accessing external instruction memory, the lower 12 bits of the program counter are output to these pins.  When accessing external data memory, the lower 12 bits of the external address register are output to these pins. |

| D0 to D31              | 88         | I/O<br>  (Tri-<br>  State) | Data bus. These pins form a 32-bit data bus for external memory (data or instruction).                                                                                                                                                                                        |

<sup>%%</sup> Refer to Table 2-1 for pin numbers.

Table 2-4. Pin functions available only in slave mode.

# \* HOST CPU INTERFACE

| NAME         | #    | I/O    | FUNCTION                                           |

|--------------|------|--------|----------------------------------------------------|

| CS/          | 55   | Input  | Active-low chip select input signal.               |

| 1            |      |        | When this pin becomes 0,                           |

| 1            |      |        | the host CPU may perform read/write                |

| 1            |      |        | operations on the 16-bit port formed               |

|              |      |        | by pins I/O 0 through I/O 15.                      |

| HWR/         | 22   | Input  | Active-low host write input signal.                |

|              |      |        | In conjunction with CS/, this signal               |

|              |      |        | allows the host CPU to write data                  |

| 1            |      |        | $\mid$ into the DRS register via the 16-bit $\mid$ |

| <u></u>      |      |        | port formed by pins I/O 0 to I/O 15.               |

| HRD/         | 23   | Input  | Active-low host read input signal.                 |

|              |      |        | In conjunction with CS/, this signal               |

|              |      | 1      | allows the host CPU to read data                   |

|              |      |        | from the DRS register via the 16-bit               |

|              |      |        | port formed by pins I/O 0 to I/O 15.               |

| I/O 0 to     | ક ક  | 1/0    | These pins form the I/O port to the                |

| I /O 15      |      | (Tri-  | host CPU bidirectional data bus. It                |

|              |      | State) |                                                    |

|              |      |        | the DRS register under the control                 |

|              |      |        | of the host CPU signals CS/, HWR/,                 |

|              |      |        | and HRD/.                                          |

|              |      | ·      | The data transfer format can be                    |

| !            |      |        | specified in the status register as                |

|              |      |        | either a 16-bit or a 32-bit                        |

| <del> </del> | - 23 |        | transfer.                                          |

| ROM          | 21   | Output | •                                                  |

| !            |      | i      | write data via the host CPU data                   |

| <u> </u>     |      |        | bus.                                               |

# \* EXTERNAL DATA MEMORY INTERFACE

| NAME                        | #                     | 1/0    | FUNCTION                                                                                                                                                                         |

|-----------------------------|-----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WR/<br> <br> <br>           | 9<br> <br> <br>       | Output | Controls data write to external memory. This signal becomes 0 after the output address is valid and data is output to the data port formed by pins D0 to D7.                     |

| RD/<br> <br> <br> <br> <br> | 10<br> <br> <br> <br> | Output | Controls data read from external memory. This signal becomes 0 after the output address is valid, and data is input at the rising edge to the data port formed by pins D0 to D7. |

Table 2-4 cont'd.

| 1         |                      |        |                                                                                                                                                                                                             |

|-----------|----------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | #                    | I/O    | FUNCTION                                                                                                                                                                                                    |

| AX        | 8<br> <br> <br> <br> | Output | When accessing external data memory, the highest bit of the external address register is output to this pin.  0: High-speed memory area. 1: Low-speed memory area.                                          |

| A0 to A11 | 88<br> <br> <br>     | Output |                                                                                                                                                                                                             |

| DO to     | 88<br> <br>          | Tri-   | Data bus. These pins form an 8-bit data bus for external data memory access. Data may be transferred in one of four formats (1-, 2-, 3-, or 4-byte words), depending on the setting of the status register. |

# \* GENERAL PURPOSE I/O PORT

| NAME  | #                  | 1/0    | FUNCTION                                                                                                                                                          |

|-------|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0,P1 | 54, <br>  20  <br> | Input  | These pins form a general-purpose input port. The status of either of these pins may be tested by a conditional branch instruction.                               |

| P2,P3 | 53,<br>19<br>1     | Output | These pins form a general-purpose output port. The data output by these pins can be set directly by an instruction and will be retained until explicitly changed. |

<sup>%%</sup> Refer to Table 2-1 for pin numbers.

.

#### CHAPTER 3 HARDWARE ARCHITECTURE

This chapter describes the operation and function of each functional block of the uPD77230R.

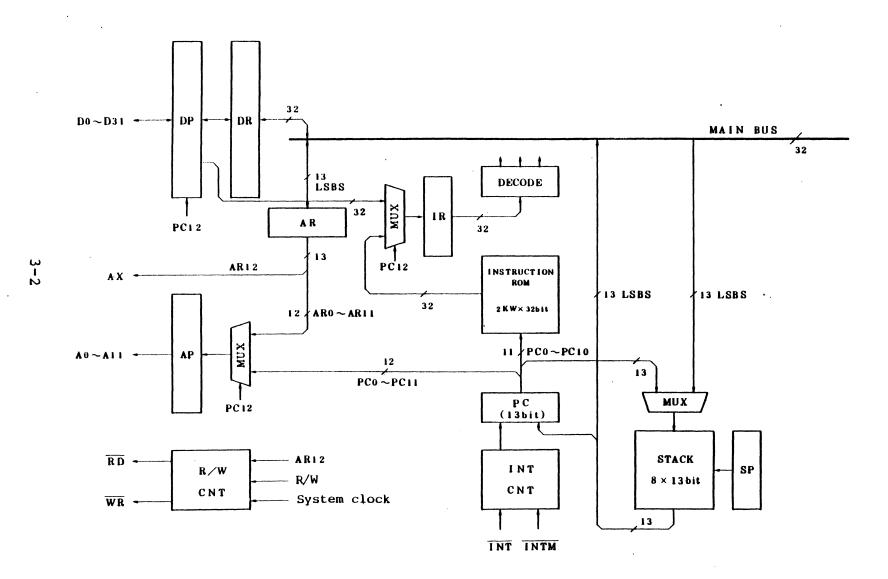

#### 3.1 Instruction ROM and associated circuits.

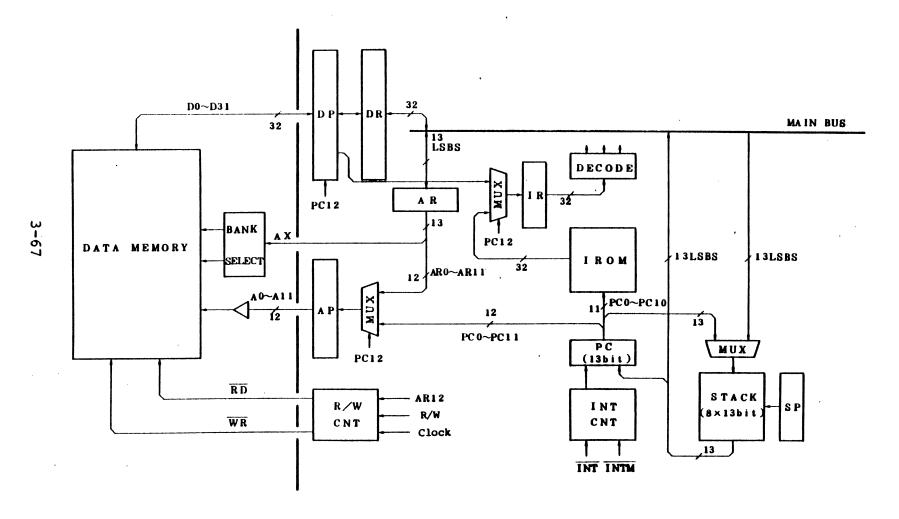

The uPD77230R has an internal instruction ROM which consists of 2K 32-bit words. In master mode, instruction memory can be expanded by the addition of an external 4K 32-bit words. Figure 3-1 shows the internal instruction ROM and its associated circuits.

#### 3.1.1 Instruction ROM.

The instruction ROM, which stores the microprogram of the uPD77230R, has a capacity of 2K words by 32 bits. The current address of the instruction ROM is indicated by the program counter (PC). Each instruction is stored in the instruction register (IR) prior to decoding by the decoder.

# 3.1.2 Program counter (PC).

The program counter consists of a 13-bit register that indicates the current address of the instruction ROM, and a counter that increments the lower 12 bits of that address. The highest bit of the PC, PC12, indicates whether the memory to be accessed is the internal instruction ROM or external instruction ROM. When PC12 is 0, internal memory is accessed, while PC12 = 1 is used for access to external memory.

#### 3.1.3 Stack and stack pointer (SP).

The stack is 8 words deep and 13 bits wide, and works on a last-in, first-out (LIFO) basis. The current address of the stack is contained in the stack pointer. The stack is connected to the lower 13 bits of the main bus. Therefore, the contents of the stack location indicated by the stack pointer can be read from or written to, if desired, by appropriate specification in the SRC or DST fields of a transfer instruction.

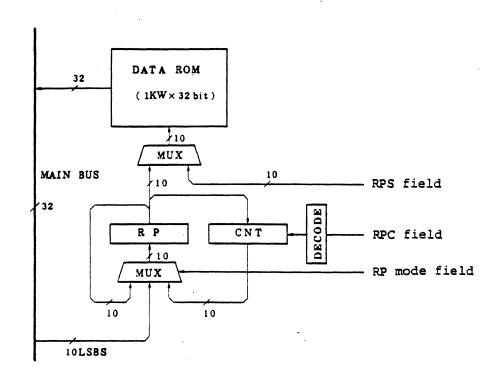

# 3.2 Data ROM and its associated circuits.

#### 3.2.1 Data ROM.

Data ROM capacity is 1K words by 32 bits. The current address of this memory is specified by the ROM pointer (RP), or by the RPS field in the CNT field of the OP instruction.

## 3.2.2 ROM pointer (RP).

The ROM pointer is a 10-bit register that contains the current address of the data ROM. It is also connected to the lower 10 bits of the main bus. RP modifications are specified by the two RP bits in the CNT field of an OP instruction. The modifications which are available are increment RP, decrement RP, and add  $2^{\rm n}$  to RP.

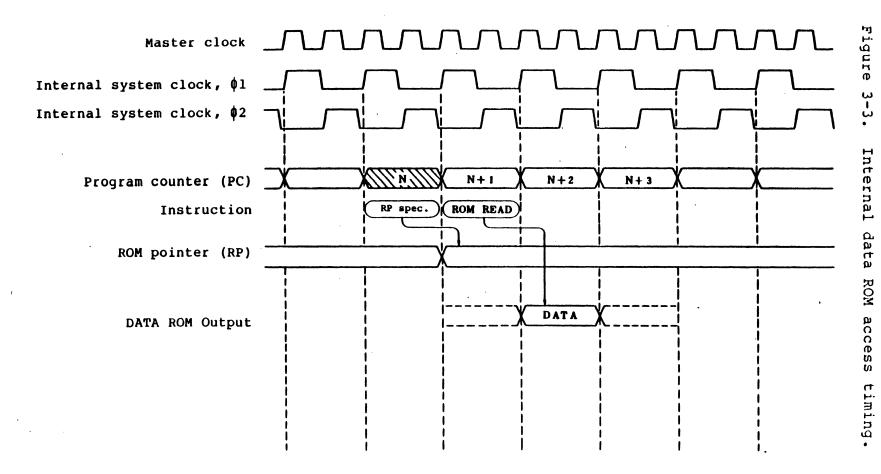

Figure 3-2. Data ROM and its associated circuits.

3.3 Data RAMs and their associated circuits.

#### 3.3.1 Data RAMs 0 and 1.

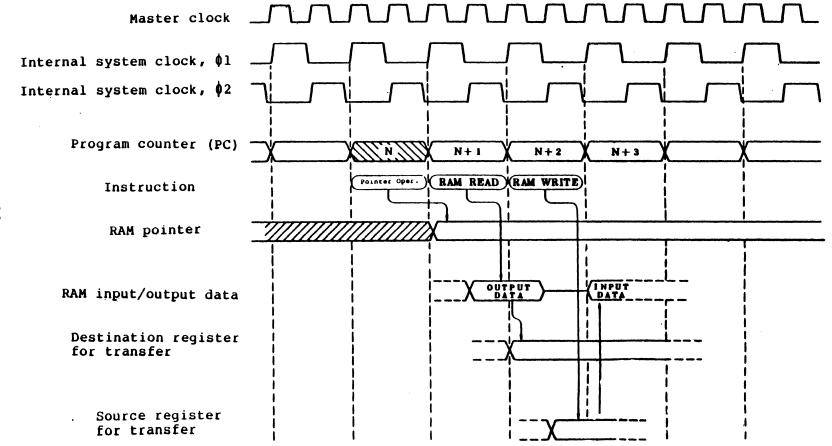

Two blocks of RAM are provided for data storage. Each block consists of 512 words by 32 bits. The current address for data RAM 0 is specified by base pointer 0 (BASEO) and index register 0 (INDEXO). Likewise, the address for data RAM 1 is specified by base pointer 1 (BASE1) and index register 1 (INDEX1). Figure 3-4 is a block diagram of this configuration.

The output from each data RAM block is connected to the main bus. In addition, each data RAM block is connected to a sub-bus, which routes the RAM data to the P register of the ALU, and another sub-bus which routes data to the K and/or L registers at the input to the multiplier. Thus, data transfers from the RAM blocks can occur in parallel with other data transfers across the main bus, and in parallel with an ALU operation.

Figure 3-4. Data RAMs and their associated circuits.

# MAIN BUS /32 MUX DATA RAMO 512 W × 32 bit 32 32 SUB BUS MUX 32 DATA RAM1 512W×32 bit ₹ 32 32

ALU,K,L

#### 3.3.2 Data RAM address.

The address for each data RAM block is specified by the appropriate base pointer and index register. Each of these registers is 9 bits wide, and is connected to the lower 9 bits of the main bus.

The following addressing modes are available:

- 1) address = base pointer

- 2) address = index register

- 3) address = base pointer + index register

The contents of the CNT field in the OP instruction specify which mode is used. The specification made becomes valid on the following instruction cycle.

#### 3.3.3 BASEO and BASE1.

Base pointer 0 (BASE0) specifies the base address for data RAM 0, while base pointer 1 specifies the base address for data RAM 1. Each of these 9-bit pointers are connected to the lower 9 bits of the main bus, and are therefore accessible to/from the other registers on the bus.

(1) General base pointer operation.

The base pointers can be modified as follows, in accordance with the CNT field of the OP instruction:

- \* Increment

- \* Decrement

- \* Clear

- \* NOP

- (2) Special base pointer operation.

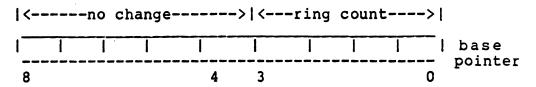

The base pointers can count either as ordinary binary counters, or as modulo counters, with the modulus specified by the BASEn bits (n=0,1) in the CNT field of the OP instruction. In modulo count mode, the carry to a specified bit position is inhibited, so that the bits higher than and including the one specified are not affected by any counting operations. The bits lower than the one specified will go through a ring count (i.e. wrap around) upon successive increments or decrements.

Example: n=4 specifies a modulo 2<sup>4</sup> count; when incremented, the base pointer will count between 0 and 15 and then wrap around to 0 again and continue counting.

Figure 3-5. Base pointer modulo count operation.

The modulo count number n can be between 0 and 7. When the modulo count number is 0, the base pointer will behave as an ordinary 9-bit binary counter.

Note that the starting address of the count need not be zero; i.e. it is possible to specify a count of  $2^2$  starting at address 014H, for example, and count through the range 014H - 017H.

### .3.3.4 INDEXO and INDEX1.

Index register 0 (INDEX0) specifies the index address for data RAM 0, and index register 1 (INDEX1) specifies the index address for data RAM 1. Each of these 9-bit registers is connected to the lower 9 bits of the main bus, and both are therefore accessible to/from the other registers on the bus.

### (1) Index register operation.

The index registers can be modified as follows, in accordance with the CNT field of the OP instruction:

- \* Increment

- \* Decrement

- \* Clear

- \* Store

- \* NOP

When the store operation is specified, the base pointer and the index register contents are added together, and the sum replaces the previous value in the index register.

- 3.4 Floating point multiplier section.

- 3.4.1 Floating point multiplier (FMPY).

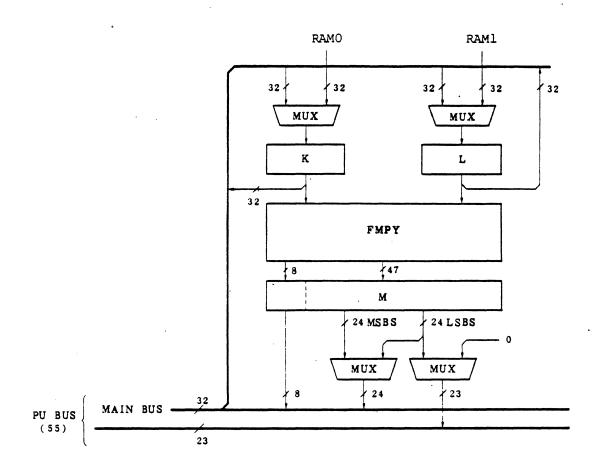

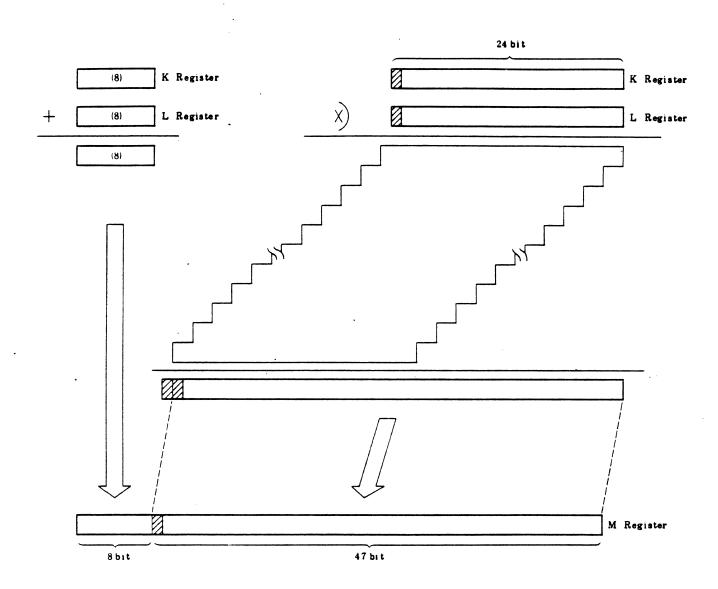

The multiplier generates the product of the 32-bit data in the K register and the 32-bit data in the L register. The K and L register contents are in 8-bit exponent, 24-bit mantissa format. The 55-bit product (8-bit exponent, 47-bit mantissa) is stored in the M register. Refer to Figure 3-7 for a block diagram of the FMPY and its associated circuits.

Figure 3-7. FMPY and associated circuits.

### 3.4.2 K and L registers.

These are 32-bit registers which hold the inputs to the floating point multiplier (FMPY). They can also be used as general purpose registers because they can be written to or read from the main bus. In addition, data from data RAM 0 can be loaded into the K register, or data from data RAM 1 can be loaded into the L register, via independent sub-busses.

### 3.4.3 M register.

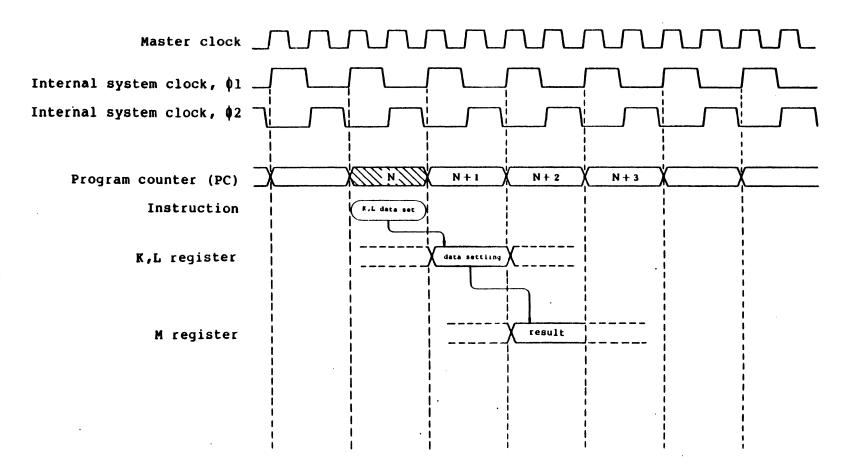

Once the numbers to be multiplied are stored in the K and L registers, the product is automatically generated and stored in the M register. Refer to Figure 3-8 for a representation of the multiplication process. The 55-bit M register is in 8-bit exponent, 47-bit mantissa format. The timing of a multiplication is shown in Figure 3-9.

The data in the M register can be transferred to the main bus (32 bits), the PU bus (55 bits), and the P register (55 bits) of the ALU, according to the transfer format specifications described below.

Figure 3-8. Arithmetic operation of FMPY.

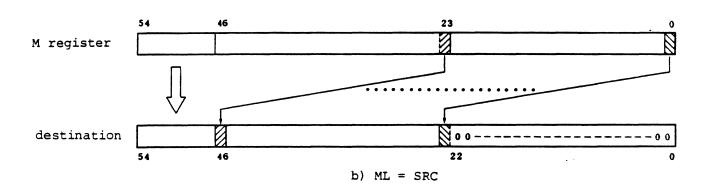

There are two formats which are available for transferring data from the M register to any other register. The desired format is specified in the SRC field of the OP instruction. The following transfer formats are depicted in Figure 3-10:

### (1) SRC field = M

If the destination register is 32 bits wide, then the higher 32 bits of the M register are transferred to the destination register. If the destination register is 55 bits wide, the 55 bits of the M register are transferred unaltered to the destination register.

### (2) SRC field = ML

The exponent (i.e. highest 8 bits) of the M register is transferred directly to the exponent of the destination register, and the lower 24 bits of the M register are transferred to the 24 bit mantissa of the destination register. If the destination register is 55 bits wide, then the lower 23 bits of the destination register are filled with zeros.

Figure 3-10. M register data transfer formats.

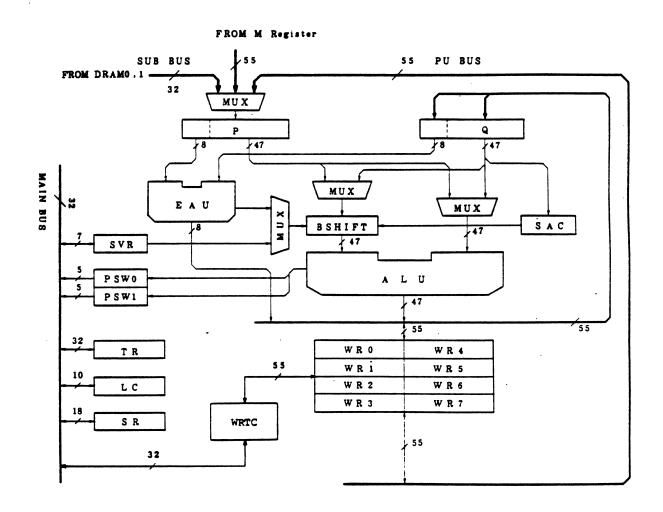

### 3.5 Processing Unit (PU).

The processing unit (PU) contains those sub-sections shown in Figure 3-11. The P and Q registers hold the inputs for the two arithmetic logic units (ALU and EAU), and the eight working registers may be used to store the results.

### 3.5.1 P register.

The P register serves as one of the two inputs to the ALUs. This 55-bit register is in 8-bit exponent, 47-bit mantissa format. Data may be input to the P register from the PU bus, M register, data RAM 0, or data RAM 1, in accordance with the P field specification in the OP instruction.

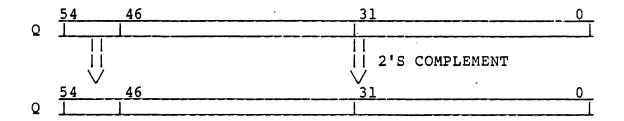

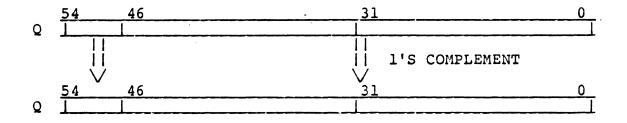

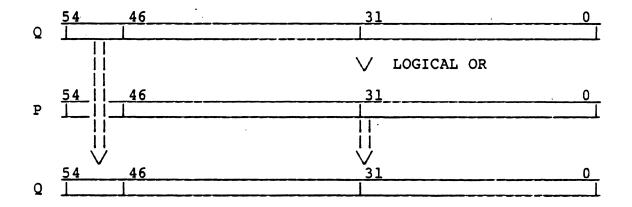

### 3.5.2 Q register.

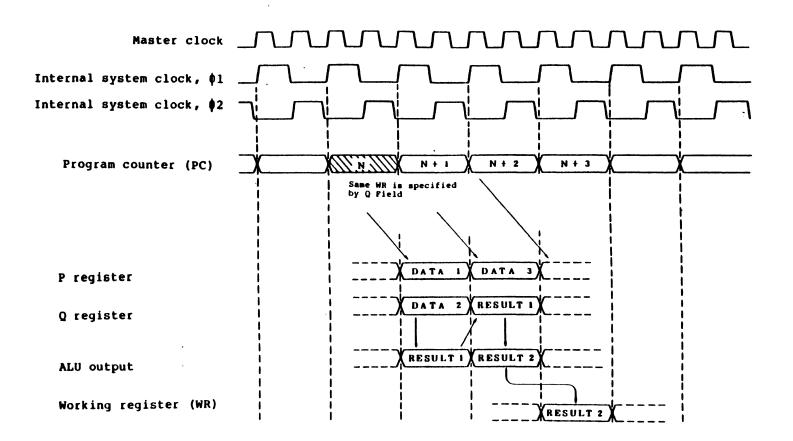

The Q register is the other input to the ALUs. The data format in the Q register is the same as the format in the P register. Data may be input to the Q register from any of the eight working registers (WRO thru WR7), in accordance with the Q field specification in the OP instruction.

If the same working register is specified as the input to the Q register in consecutive instructions, then the output of the ALU is fed directly to the Q register. This allows a single accumulator (i.e. working register) to be used for successive arithmetic operations. However, an intermediate result in a continuous accumulation will not be stored in the working register.

Figure 3-11. Processing Unit (PU) and associated circuits.

#### 3.5.3 Shift and count circuit (SAC).

This circuit determines the "shift value" of the mantissa stored in the Q register. The shift value is the number of bits by which the mantissa must be left shifted so that the MSB of the fractional part of the mantissa (i.e. the bit to the right of the sign bit) becomes a numerical 1. For example, a 4 bit two's complement mantissa equal to 0001 would have a shift value of 2, while 1100 would have a shift value of 1. This shift value is used by the barrel shifter (BSHIFT) in performing normalization and format conversion.

## 3.5.4 Barrel shifter (BSHIFT).

This unit performs shifting operations on the mantissa stored in the P register or the Q register. The number of bits shifted is determined by the SAC or EAU in the processing unit, or by shift control fields in the OP instruction (e.g. SHV, SHLM fields). The shift operations performed by BSHIFT are described below.

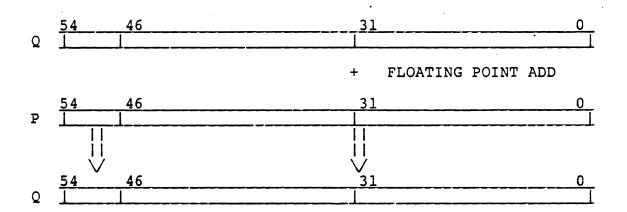

(1) Mantissa alignment in floating point operations.

In a floating point arithmetic operation, the EAU compares the exponents of the data stored in the P and Q registers. The mantissa of the number with the smaller exponent will be right shifted, and its exponent incremented, until the two exponents are equal. The floating point arithmetic operation is then performed on the numbers with equal exponents.

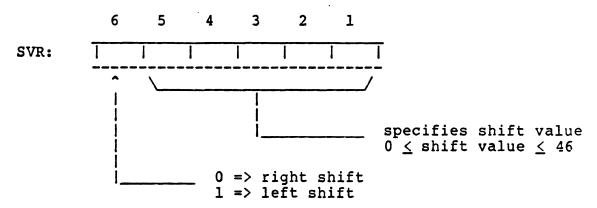

(2) Mantissa shift in fixed point operation.

When working with fixed point numbers, the data in the P or Q register may be shifted by the shift value contained in the shift value register (SVR). See the description of the SHV field in chapter 4 for details.

(3) Normalization.

Data can be normalized by specifying NORM in the operation field of an OP instruction. "Normalization" means that the exponent and mantissa of the data in the Q register are adjusted in accordance with the value from the SAC (see above). After normalization, the 2<sup>-1</sup> bit will be a numerical 1.

(4) Floating point to fixed point conversion.

The mantissa stored in the Q register will be shifted by the value of its exponent. If the exponent is negative, the mantissa will be shifted to the right; if the exponent is positive, the mantissa will be shifted to the left.

### (5) Unary shift.

The mantissa of the data in the Q register can be shifted by specifying a shift instruction in the operation field of an OP instruction. The exponent will not be affected.

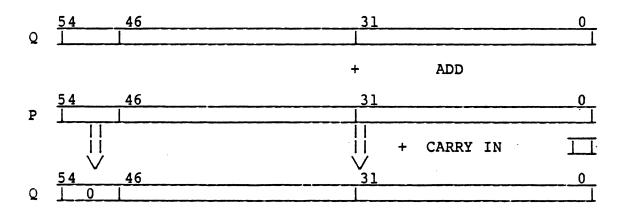

### 3.5.5 Arithmetic and logic unit (ALU).

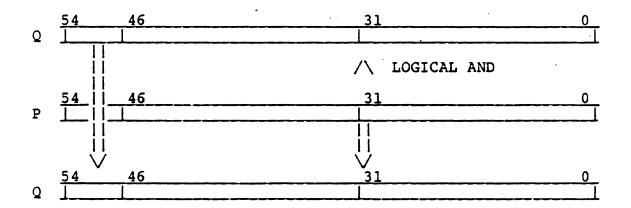

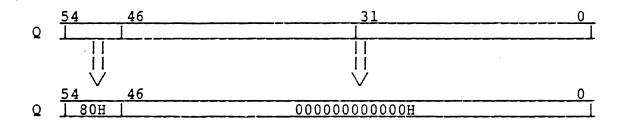

The ALU performs arithmetic and logical operations on the 47-bit mantissas of the P and Q registers. The ALU performs the operation specified in the OP field of an instruction. If the operation is unary (i.e. only one input is needed), then the Q register is the source of the operand. Otherwise, the data from both the P and Q registers are used.

The result of an operation is stored in the working register selected in the Q field of the instruction. The ALU operation will affect the flag register (i.e. PSW) selected by the FIS and FC bits of the OP instruction.

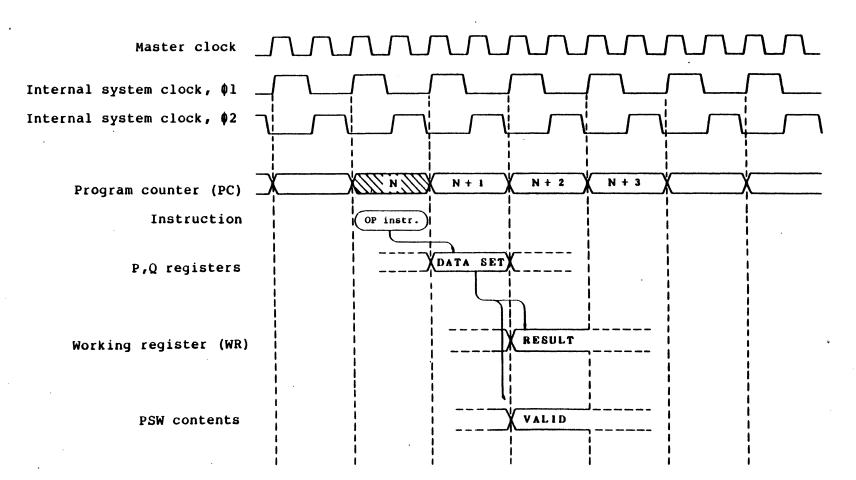

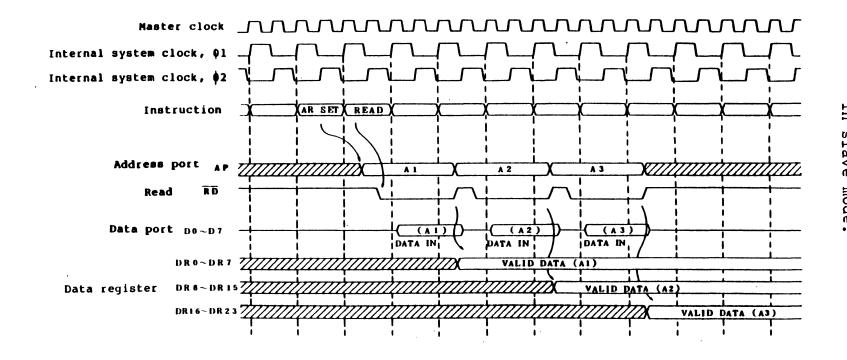

In general, the results of an ALU operation are valid two instruction cycles after the instruction specifying the operation (refer to Figures 3-12 and 3-13). However, because of the pipelined nature of instruction execution, the results of one instruction are always available for the next instruction (except for certain external memory read operations).

# 3.5.6 Exponent arithmetic and logic unit (EAU).

This unit performs the required operations on the 8-bit exponents stored in the P and Q registers.

# 3.5.7 Working registers 0 thru 7 (WRO - WR7).

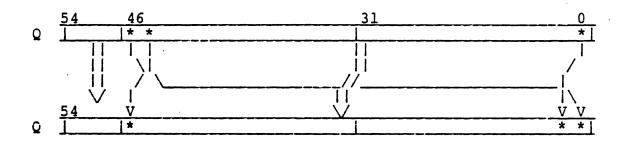

These 55-bit registers store the results of the operations performed by the ALU and EAU. The current working register is specified by the Q field of the OP instruction. Data can be transferred to or from the working registers according to the transfer format specified in the OP instruction. The WT field controls the transfer format when the working register is the source of data for the transfer, while the WI field controls the transfer format when the working register is the destination. The transfer formats are described in Tables 3-1 and 3-2.

Table 3-1. Data transfer format, WRn = SRC.

| Mnemonic     | WT field |     |     | Operation                                           |  |  |

|--------------|----------|-----|-----|-----------------------------------------------------|--|--|

|              | D21      | D20 | D19 |                                                     |  |  |

| WRBORD       | 0        | 0   | 1   | Ordinary data transfer from a working               |  |  |

| !!!          |          |     |     | register                                            |  |  |

| !            |          |     |     | 54 46 0                                             |  |  |

|              |          |     |     |                                                     |  |  |

| !<br>!       |          |     |     | WR                                                  |  |  |

| !<br>!       |          |     |     |                                                     |  |  |

| i            |          |     |     |                                                     |  |  |

| j i          |          |     | İ   |                                                     |  |  |

| !            |          |     | !!! | 54 46 0                                             |  |  |

| <br>  WRBL24 | 0        | 1   | 0   | Shifts lower 24 bits of WR to higher                |  |  |

| MKDL24       |          |     |     | 24 bits of mantissa                                 |  |  |

| ·i           |          |     | i   |                                                     |  |  |

| i i          |          |     | İ   | 54 46 23 0                                          |  |  |

| !            | ļ        |     | !   | WR 24 bit                                           |  |  |

|              |          |     |     |                                                     |  |  |

| ]<br>1       |          |     |     | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \               |  |  |

| !<br>!       |          |     |     | 24 bit - 0                                          |  |  |

| i            | i        |     |     | 54 46 22 0                                          |  |  |

|              |          |     |     |                                                     |  |  |

| WRBL23       | 0        | 1   | 1   | Shifts lower 23 bits of WR to higher                |  |  |

| 1            |          |     |     | 24 bits of mantissa; set sign bit of mantissa to 0. |  |  |

| !<br>!       | 1        |     |     | mantissa to v.                                      |  |  |

| ]<br>        | i        |     |     | 54 46 22 0                                          |  |  |

| İ            |          |     | i   | WR 23 bit                                           |  |  |

| İ            |          |     | İ   |                                                     |  |  |

| !            | . !      |     |     |                                                     |  |  |

|              |          |     |     | 0 23 bit - 0                                        |  |  |

| !<br>! !     |          |     | 1   | 54 46 22 0                                          |  |  |

|              |          |     |     |                                                     |  |  |

| WRBL8E       | 1        | 0   | 0   | Shifts exponent of WR to lower 8 bits               |  |  |

| ļ i          | ĺ        | İ   | İ   | of mantissa                                         |  |  |

| ! !          | ļ        |     |     | 54 46 0                                             |  |  |

| !            |          |     |     |                                                     |  |  |

| !<br>!       |          |     |     | WR Shit                                             |  |  |

|              |          |     |     |                                                     |  |  |

| j i          |          |     |     |                                                     |  |  |

| İ            |          | i   | i i | 0 8 bit                                             |  |  |

| i i          |          |     | l i | 54 46 7 0                                           |  |  |

Table 3-1 (cont'd). Data transfer format, WRn = SRC.