## **VRc5074 System Controller**

Data Sheet June 1998

### 1.0 Introduction

#### 1.1

### Overview

The VRc5074 System Controller is a software-configurable chip that directly connects the VR5000 CPU to SDRAM memory, a PCI Bus, and a Local Bus, without external logic or buffering. From the CPU's viewpoint, the controller acts as a memory controller, DMA controller, PCI-Bus host bridge, and Local-Bus host bridge. From the viewpoint of PCI agents, the controller acts as master and target on the PCI Bus. The controller also has one serial port and four timers.

#### 1.2

#### **Features**

#### □ CPU Interface

- Connects directly to a 250 MHz VR5000 CPU.

- 100 MHz CPU bus.

- Peak block-transfer throughput of 800 Mbytes/sec, maximum sustained throughput of 640 Mbytes/sec.

- 16 x 8-byte (128-byte) CPU-to-controller FIFO.

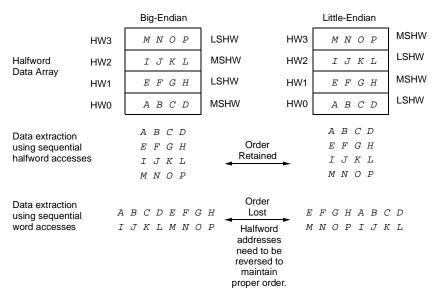

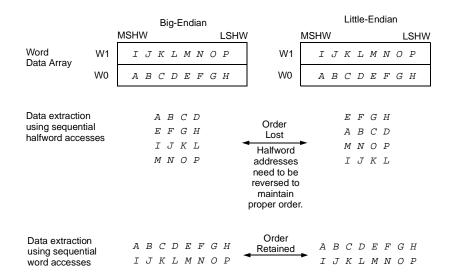

- Little-endian or big-endian byte order on CPU interface.

- Supports secondary cache.

- 15 interrupt sources, individually enabled and assigned to one of the CPU's seven interrupt inputs.

- Supports all CPU bus-cycle types (but the only write type is pipelined write).

Parity generation and checking on CPU data cycles.

- Mode data at reset provided by a serial EEPROM or by the controller.

- 3.3V I/O.

### ■ Memory Interface

- 100 MHz memory bus.

- Maximum sustained throughput of 800 Mbytes/sec.

- Supports three physical loads per data bit: two SDRAM physical banks and one other (e.g., EPROM, Flash, or buffers bridging to a secondary memory bus).

- Supports four types of SDRAM with two to four on-chip virtual banks: 256Mb four-bank, 64Mb four-bank, 64Mb two-bank, 16Mb two-bank.

- · On-chip bank-interleaving buffers.

- Programmable address ranges for each memory bank.

- · Memory may maintain multiple open SDRAM pages.

- Parity or ECC generation and checking of memory data cycles with 64+8 bits of SDRAM and no performance degradation.

- Read/write buffers:

- 8-dword (64-byte) CPU Write FIFO.

- 8-dword (64-byte) PCI Write FIFO.

- · On-chip refresh generation.

- 3.3V I/O.

#### □ PCI Bus

- Full compliance with PCI Local Bus Specification, Revision 2.1.

- Four possible configurations:

- 66 MHz, 64-bit bus (maximum sustained bandwidth 533 Mbytes/sec)

- 66 MHz, 32-bit bus (maximum sustained bandwidth 267 Mbytes/sec)

- 33 MHz, 64-bit bus (maximum sustained bandwidth 267 Mbytes/sec)

- 33 MHz, 32-bit bus (maximum sustained bandwidth 133 Mbytes/sec)

- PCI-Master support, allowing the CPU, DMA, and Local-Bus masters to access targets on the PCI Bus via two programmable PCI Address Windows.

- PCI-Target support, allowing PCI-Bus masters to access to all controller resources.

- Eleven programmable Base Address Register (BAR) windows.

- All reads are delayed transactions.

- Up to four simultaneous delayed transactions.

- Master and target read/write bursts up to 2 Mbytes in length.

- Master and target read/write buffers:

- 32-entry x 8-byte (256-byte) PCI Output FIFO.

- 32-entry x 8-byte (256-byte) PCI Input FIFO.

- 4-entry x 8-byte (32-byte) CPU Delayed Read Completion (DRC) Buffer.

- 4-entry x 8-byte (32-byte) DMA Delayed Read Completion (DRC) Buffer.

- · Optional PCI Central Resource functions:

- Buffered PCI clock to 5 other PCI devices.

- PCI clock can be external or derived from CPU clock.

- Arbitration for the controller and 5 other PCI devices.

- CPU interrupt control for 5 PCI devices.

- Full PCI Configuration Space.

- 64-bit addressing support for master and target using Dual Address Cycle (DAC).

- Locked cycle (exclusive access) support as master and target.

- · Parity generation and checking on address and data cycles.

- Compliant with both 3.3V and 5V PCI signaling.

### □ Local Bus

- 25 MHz or 50 MHz bus (0.25 or 0.50 of system clock).

- Programmable chip-selects for 7 devices plus Boot ROM.

- Each chip-select supports up to 4GB address space.

- Devices may alternatively be located on the memory bus.

- Chip-select signals may alternatively be used for DMA or UART control, or as general-purpose I/O signals.

- Support for burst cycles on the Local Bus.

- Support for Local-Bus master control of the Local Bus, using 68000 or Intel arbitration protocols.

- Programmable control-signal relationships and timing:

- Timing can be fixed or use external Ready signal.

- 12-bit timer for external Ready signal.

- 3.3V outputs, 5V-tolerant inputs

#### □ DMA

- Two DMA channels.

- Block transfers to or from any physical address.

- Transfers initiated by the CPU, a PCI-Bus master, or a Local-Bus master.

- Peak block-transfer throughput of 800 Mbytes/sec, maximum sustained throughput of 640 Mbytes/sec.

- 32 x 8-byte (256-byte) DMA FIFO.

- Two sets of DMA control registers. One set can be programmed while the other performs a transfer.

- Chained transfers—when one transfer completes, another programmed transfer automatically begins.

- · Supports bidirectional, unaligned transfers.

- Optional hardware handshake signals (REQ#, ACK#, EOT#) if certain chipselects are not used.

#### □ Serial Port (UART)

- Compatible with National Semiconductor's PC16550D UART.

- Receiver and transmitter each have a 16-byte FIFO.

- 5, 6, 7, or 8 bits per character.

- Even, odd, or no parity-bit generation and detection.

- 1, 1.5, or 2 stop-bit generation.

- Baud-rate generator division of input clock by 1 to (2<sup>16</sup>-1).

- Prioritized interrupt controls.

- DSR and DTR control signals.

- Optional hardware controls (CTS#, RTS#, DCD#, XIN#) if certain chip-selects are not used.

### □ Timers

- 16-bit SDRAM refresh timer.

- 24-bit CPU-bus read timer.

- 32-bit general-purpose timer.

- 32-bit watchdog timer.

- All timers are cascadable.

### ■ Multi-Controller Support

## **Contents**

| 1.0                                                                                        | Introduction                                                                                                                                                      | 1              |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.1                                                                                        | Overview                                                                                                                                                          | 1              |

| 1.2                                                                                        | Features                                                                                                                                                          | 1              |

| 2.0                                                                                        | Internal and System Architecture                                                                                                                                  | 11             |

| 2.1                                                                                        | Internal Architecture                                                                                                                                             | 11             |

| 2.2                                                                                        | System-Design Options                                                                                                                                             | 13             |

| 2.3                                                                                        | Terminology                                                                                                                                                       | 19             |

| 2.4                                                                                        | Reference Documents                                                                                                                                               | 19             |

| 3.0                                                                                        | Signal Summary                                                                                                                                                    | 21             |

| 4.0                                                                                        | Register and Resource Summary                                                                                                                                     | 31             |

| 4.1                                                                                        | Register Summary                                                                                                                                                  | 31             |

| 4.2                                                                                        | Resource-Accessibility Summary                                                                                                                                    | 34             |

| 4.3                                                                                        | Address Space Summary                                                                                                                                             | 36             |

| 5.0                                                                                        | CPU/System Interface and Registers                                                                                                                                | 37             |

| 5.1                                                                                        | CPU and System Configuration and Monitoring                                                                                                                       | 37             |

| 5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.5.1<br>5.2.5.2<br>5.2.5.3<br>5.2.6 | CPU Interface                                                                                                                                                     |                |

| 5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5                                           | Multi-Controller Configurations  Distinguishing Between Multiple Controllers  The Main Controller  Programming  CntrValid#, WrRdy# and MCWrRdy#  Access Targeting | 41<br>42<br>42 |

| 5.4<br>5.4.1<br>5.4.2<br>5.4.3                                                             | Physical Device Address Registers (PDARs) Initialization State of PDARs PDAR Fields PDAR Address Decoding Example                                                 | 45<br>45<br>46 |

| 5.5<br>5.5.1<br>5.5.2                                                                      | CPU Interface Registers                                                                                                                                           | 50             |

| 5.5.3              | Interrupt Status Register 0 (INTSTAT0)                      | 55       |

|--------------------|-------------------------------------------------------------|----------|

| 5.5.4              | Interrupt Status 1/CPU Interrupt Enable Register (INTSTAT1) |          |

| 5.5.5              | Interrupt Clear Register (INTCLR)                           |          |

| 5.5.6              | PCI Interrupt Control Register (INTPPES)                    |          |

| 5.6                | Timer Registers                                             |          |

| 5.6.1              | SDRAM Refresh Control Register (TOCTRL)                     |          |

| 5.6.2<br>5.6.3     | SDRAM Refresh Counter Register (T0CNTR)                     |          |

| 5.6.4              | CPU-Bus Read Time-Out Cointrol Register (T1CTRL)            |          |

| 5.6.5              | General-Purpose Timer Control Register (T2CTRL)             |          |

| 5.6.6              | General-Purpose Timer Counter Register (T2CNTR)             |          |

| 5.6.7              | Watchdog Timer Control Register (T3CTRL)                    |          |

| 5.6.8              | Watchdog Timer Counter Register (T3CNTR)                    | 62       |

| 6.0                | Main-Memory Interface and Registers                         | 63       |

| 6.1                | Memory Configuration and Monitoring                         | 63       |

| 6.2                | Physical Loads                                              | 63       |

| 6.3                | Write FIFOs                                                 | 64       |

| 6.4                | Boot- ROM and External-Device Addressing                    | 64       |

| 6.4.1              | Memory-Bus Addressing Of Boot ROM and External Devices      |          |

| 6.4.2              | Boot-Memory Timing                                          | 65       |

| 6.5                | SDRAM Main Memory                                           |          |

| 6.5.1              | Bank-Interleaving                                           |          |

| 6.5.2              | SDRAM Chip Initialization                                   |          |

| 6.5.3              | Direct Connections, SIMMs, and DIMMs                        |          |

| 6.5.4<br>6.5.5     | Address-Multiplexing Modes Performance                      |          |

| 6.5.6              | Memory Timing                                               |          |

| 6.5.7              | Memory Refresh                                              |          |

| 6.5.8              | Error Checking                                              |          |

| 6.5.9              | Memory Sharing in Multi-Controller Configurations           |          |

| 6.6                | Memory-Interface Registers                                  | 72       |

| 6.6.1              | Memory Control Register (MEMCTRL)                           |          |

| 6.6.2              | Memory Access Timing Register (ACSTIME)                     |          |

| 6.6.3              | Memory Check Error Status Register (CHKERR)                 | 74       |

| 7.0                | PCI-Bus Interface and Registers                             | 78       |

| 7.1                | PCI-Bus Configuration and Monitoring                        | 78       |

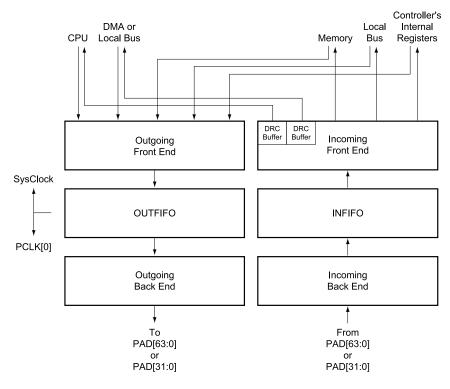

| 7.2                | Read and Write Buffers                                      | 79       |

| 7.3                | PCI Commands Supported                                      | 80       |

| 7.4                | PCI Master Transactions (Controller-to-PCI)                 |          |

| 7.4.1              | PCI Address Window Registers                                |          |

| 7.4.2              | PCI Address Decoding Example                                |          |

| 7.4.3<br>7.4.3.1   | PCI-Master Writes Combining                                 |          |

| 7.4.3.1<br>7.4.3.2 | Ryte-Merging                                                | 02<br>82 |

| 8 1               | Local-Bus Configuration and Monitoring                             | 113        |

|-------------------|--------------------------------------------------------------------|------------|

| 8.0               | Local-Bus Interface and Registers                                  |            |

| 7.13.14           | PCI Interrupt Pin Register (INTPIN)                                |            |

| 7.13.13           | PCI Interrupt Line Register (INTLIN)                               |            |

| 7.13.11           | PCI Sub-System ID (SSID)                                           |            |

| 7.13.10           | PCI Sub-System Vendor ID (SSVID)                                   |            |

| 7.13.9<br>7.13.10 | PCI Header Type Register (HTYPE) PCI Base Address Registers (BARn) |            |

| 7.13.8            | PCI Latency Timer Register (MLTIM)                                 |            |

| 7.13.7            | PCI Cache-Line Size Register (CLSIZ)                               | 110<br>110 |

| 7.13.6            | PCI Class Code Register (CLASS)                                    |            |

| 7.13.5            | PCI Revision ID Register (REVID)                                   |            |

| 7.13.4            | PCI Status Register (PCISTS)                                       |            |

| 7.13.3            | PCI Command Register (PCICMD)                                      |            |

| 7.13.2            | PCI Device ID Register (DID)                                       |            |

| 7.13.1            | PCI Vendor ID Register (VID)                                       |            |

| 7.13              | PCI Configuration Space Registers                                  |            |

| 7.12.3            | Generating IDSEL Inputs                                            |            |

| 7.12.2            | Configuration Mechanisms                                           |            |

| 7.12.1            | As PCI-Bus Master and Target                                       |            |

| 7.12              | PCI Configuration Space Cycles                                     |            |

| 7.11.4            | PCI Error Register (PCIERR)                                        | 103        |

| 7.11.3            | PCI Master (Initiator) Registers 0 and 1 (PCIINITn)                |            |

| 7.11.2            | PCI Arbiter Register (PCIARB)                                      | 98         |

| 7.11.1            | PCI Control Register (PCICTRL)                                     | 91         |

| 7.11              | PCI-Bus Registers                                                  | 91         |

| 7.10              | PCI Locked Cycles                                                  | 91         |

| 7.9               | PCI Clocking                                                       | 90         |

| 7.8.3             | External Arbitration                                               |            |

| 7.8.2             | Central Resource Terminology                                       |            |

| 7.8.1             | Central Resource Functions                                         |            |

| 7.8               | PCI Central Resource Support                                       |            |

| 7.7               | Dual Address Cycle (DAC) Support                                   |            |

| _                 |                                                                    |            |

| 7.6               | 64-Bit PCI Bus                                                     |            |

| 7.5.4             | PCI-Target Parity Detection                                        |            |

| 7.5.2             | PCI-Target Reads                                                   |            |

| 7.5.1             | PCI-Target Writes                                                  |            |

| 7.5<br>7.5.1      | PCI Loop-Back Accesses                                             |            |

| 7.5               | PCI Target Transactions (PCI-to-Controller)                        |            |

| 7.4.6             | PCI I/O Space Cycles                                               |            |

| 7.4.4.2           | PCI-Master Parity Detection                                        |            |

| 7.4.4.1           | Prefetching on PCI-Master Reads                                    |            |

| 7.4.4<br>7.4.4.1  | Retried Reads                                                      |            |

| 7.4.4             | PCI-Master Reads                                                   | 83         |

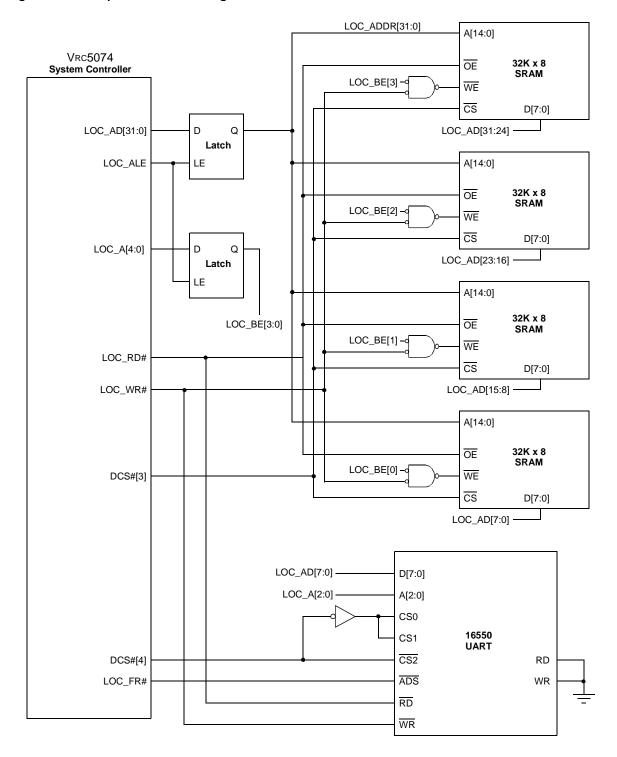

| 8.2                                              | Device Chip-Select Configuration                                                                                                                                                                                                                             | 114               |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

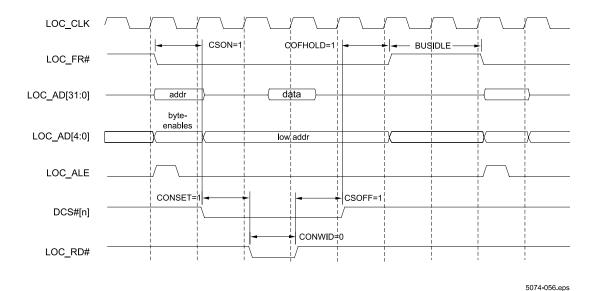

| 8.3<br>8.3.1<br>8.3.2                            | Local-Bus Master Transactions (Controller-to-Local Bus)  Timing  Dword vs. Block Requests                                                                                                                                                                    | 116               |

| 8.3.2.1<br>8.3.2.2                               | Dword Requests                                                                                                                                                                                                                                               | 117               |

| 8.4<br>8.4.1<br>8.4.2                            | Arbitration for Local-Bus Control                                                                                                                                                                                                                            | 119               |

| 8.5                                              | Local Bus vs. 64-bit PCI Bus                                                                                                                                                                                                                                 | 120               |

| 8.6<br>8.6.1<br>8.6.2<br>8.6.3<br>8.6.4<br>8.6.5 | Local-Bus Registers  Local Bus Configuration Register (LCNFG)  Local Bus Chip-Select Timing Registers (LCSTn)  Device Chip-Select Function Register (DCSFN)  Device Chip-Selects as I/O Bits Register (DCSIO)  Local Boot Chip-Select Timing Register (BCST) |                   |

| 9.0                                              | DMA Controller and Registers                                                                                                                                                                                                                                 | 130               |

| 9.1                                              | DMA Configuration and Monitoring                                                                                                                                                                                                                             | 130               |

| 9.2<br>9.2.1<br>9.2.2                            | DMA Transfer Mechanism  Configuration and Enabling  Operation                                                                                                                                                                                                | 130               |

| 9.2.3                                            | Completion                                                                                                                                                                                                                                                   | 131               |

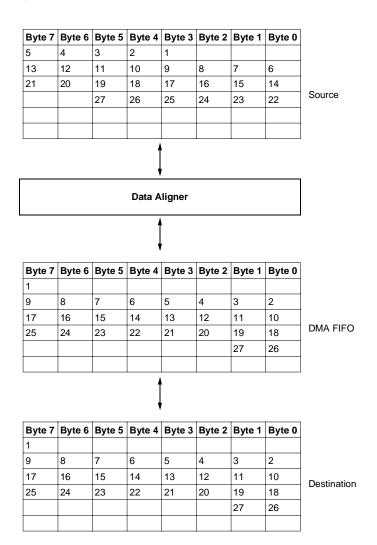

| 9.3                                              | Data Aligner                                                                                                                                                                                                                                                 | 131               |

| 9.4<br>9.4.1<br>9.4.2                            | DMA Hardware Handshaking<br>External DMA Requests<br>End Of Transfer                                                                                                                                                                                         | 133               |

| 9.5<br>9.5.1<br>9.5.2<br>9.5.3                   | DMA Registers  DMA Control Registers 0 and 1 (DMACTRLn)  DMA Source Address Register 0 and 1 (DMASRCAn)  DMA Destination Address Register 0 and 1 (DMADESAn)                                                                                                 | 133<br>136        |

| 10.0                                             | Serial Port and Registers                                                                                                                                                                                                                                    | 137               |

| 10.1                                             | Serial-Port Configuration and Monitoring                                                                                                                                                                                                                     | 137               |

| 10.2                                             | Additional UART Signals                                                                                                                                                                                                                                      | 137               |

| 10.3                                             | UART Clocking                                                                                                                                                                                                                                                | 138               |

| 10.4<br>10.4.1<br>10.4.2<br>10.4.3<br>10.4.4     | Serial-Port Registers                                                                                                                                                                                                                                        | 139<br>139<br>139 |

| 10.4.4                                           | UART Divisor Latch MSB Register (UARTDLM)                                                                                                                                                                                                                    |                   |

| 10.4.6<br>10.4.7<br>10.4.8<br>10.4.9             | UART Interrupt ID Register (UARTIIR)                                                                                                                                                                                                                         | 140<br>141<br>142 |

| 10.7.3                                           | CAN'T Modern Control Negletel (CAN'TMON)                                                                                                                                                                                                                     | 143               |

| 10.4.10              | UART Line Status Register (UARTLSR)                  | 144 |

|----------------------|------------------------------------------------------|-----|

| 10.4.11              | UART Modem Status Register (UARTMSR)                 |     |

| 10.4.12              | UART Scratch Register (UARTSCR)                      |     |

| 11.0                 | Interrupts                                           | 147 |

| 12.0                 | Reset and Initialization                             | 149 |

| 12.1                 | Types of Reset                                       | 149 |

| 12.2                 | Power-Up and Cold Reset Configuration Signals        | 150 |

| 12.3                 | PCI Reset Sequencing                                 | 151 |

| 12.4                 | CPU and Controller Initialization                    | 151 |

| 12.4.1               | Reset Signal Control                                 |     |

| 12.4.2               | Initialization Sequence                              |     |

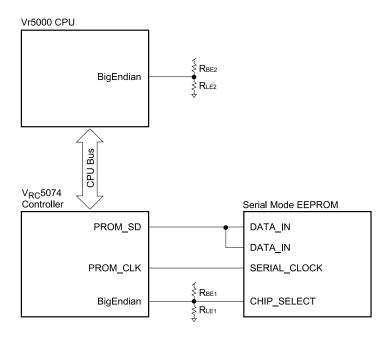

| 12.4.2.1<br>12.4.2.2 | Connecting the Serial Mode EEPROMInitialization Data |     |

| 12.4.2.2             | In-Circuit Programming of the Serial Mode EEPROM     |     |

| 13.0                 | Endian-Mode Software Issues                          |     |

| 13.1                 | Overview                                             |     |

| 13.2                 | Endian Modes                                         |     |

| 13.3                 | LAN Controller Example                               |     |

| 13.3.1               | DMA Accesses from Ethernet FIFO                      |     |

| 13.3.2               | Word Accesses to I/O Registers                       | 158 |

| 13.3.3               | Byte or Halfword Accesses to I/O Registers           |     |

| 13.4                 | GUI Controller Example                               |     |

| 13.4.1               | Word Accesses to I/O Registers                       |     |

| 13.4.2<br>13.4.3     | Byte or Halfword Accesses to I/O Registers           |     |

|                      |                                                      |     |

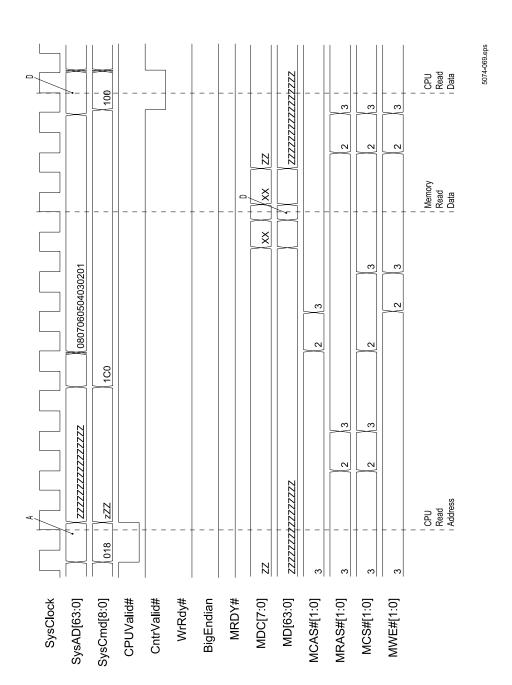

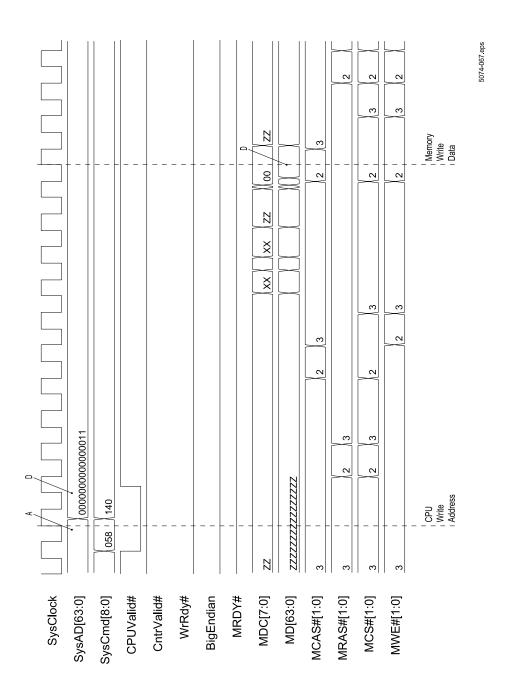

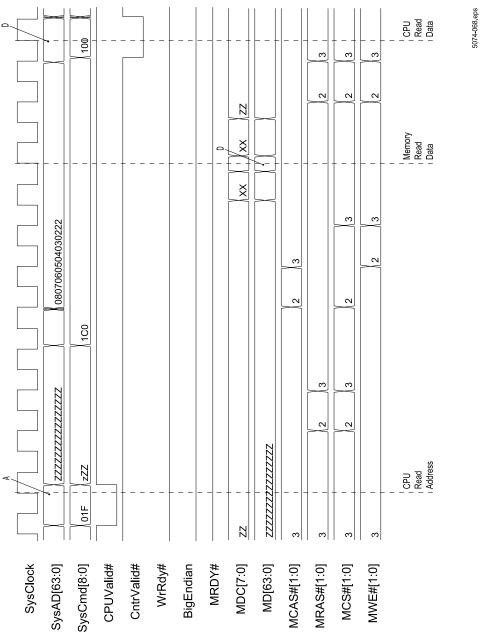

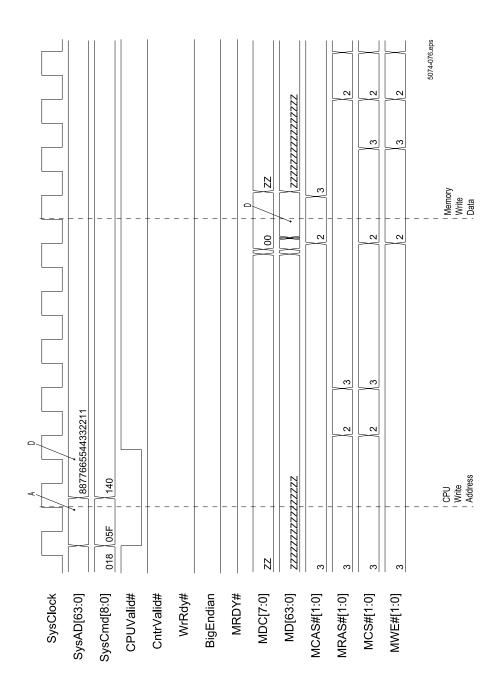

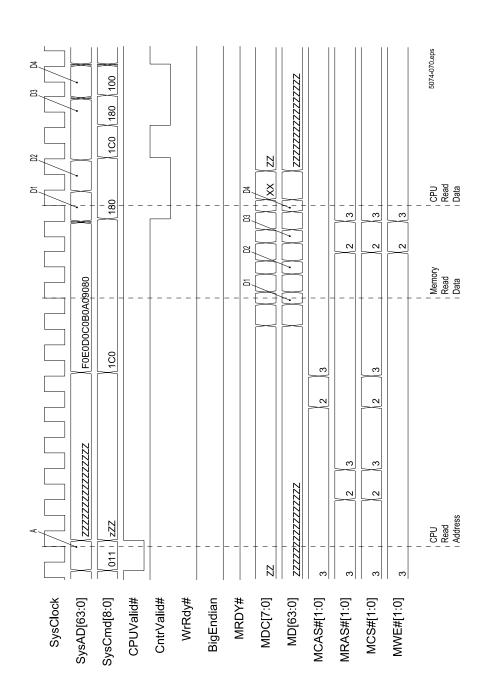

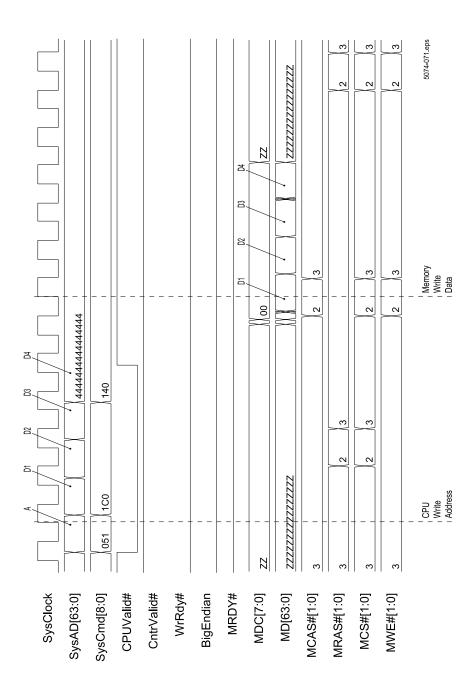

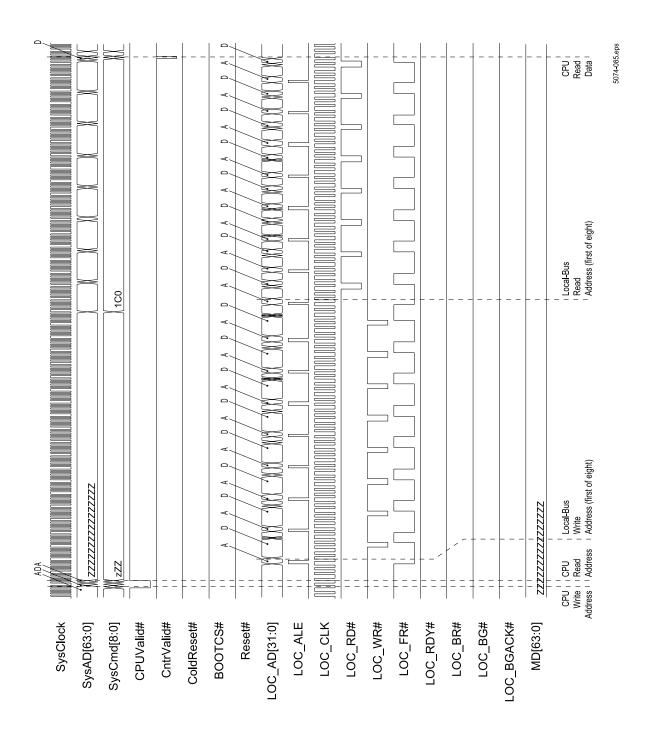

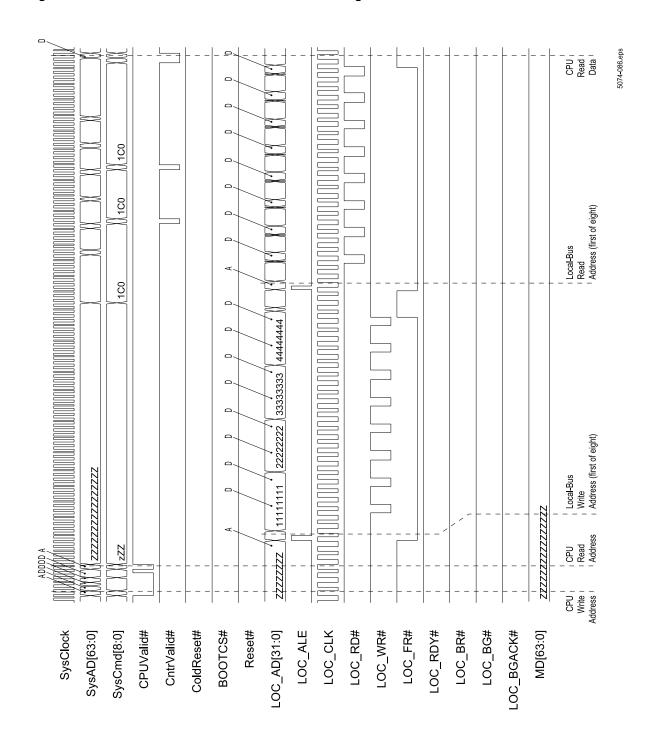

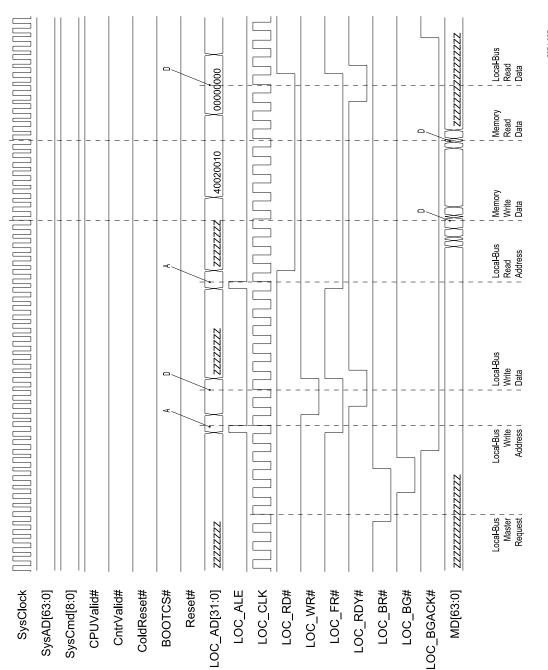

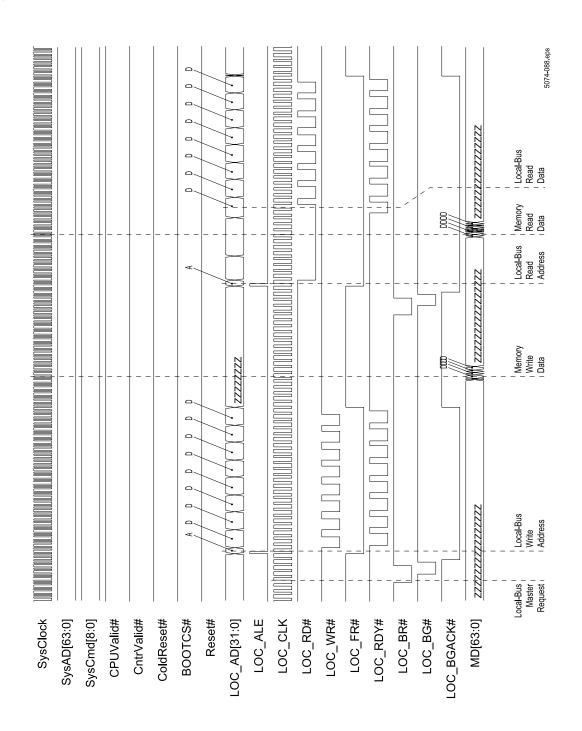

| 14.0                 | Timing Diagrams                                      |     |

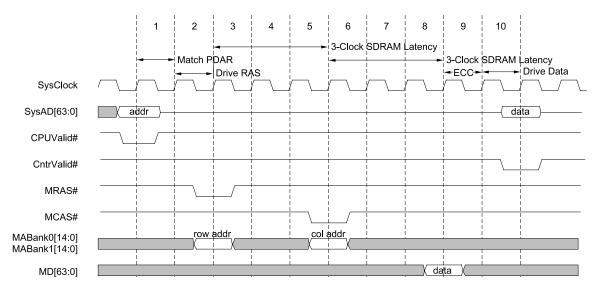

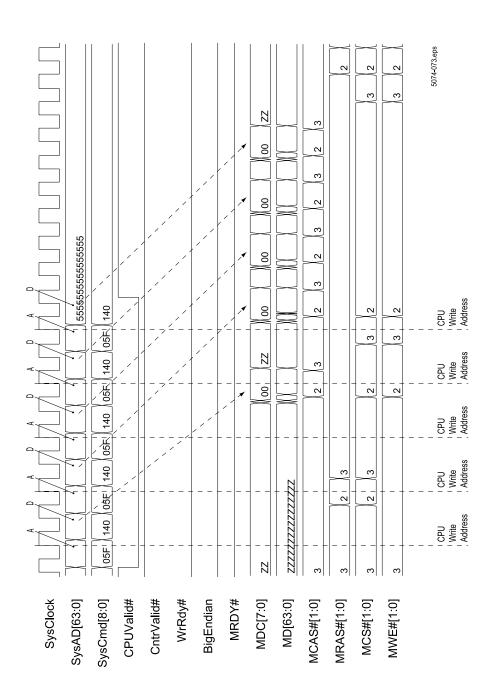

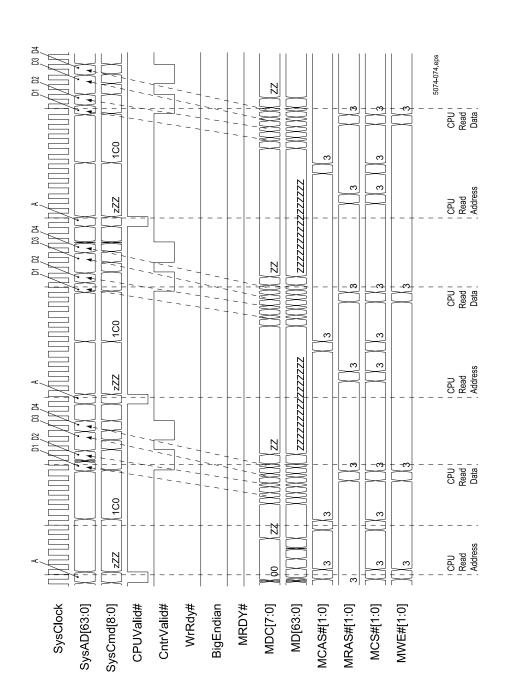

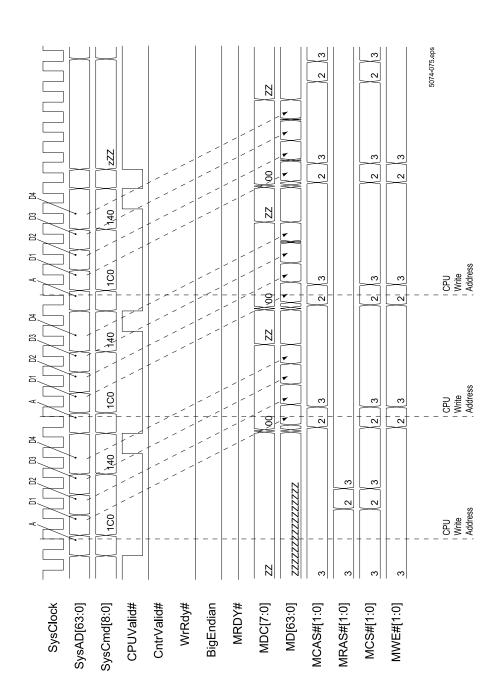

| 14.1                 | CPU Accesses to Local Memory                         |     |

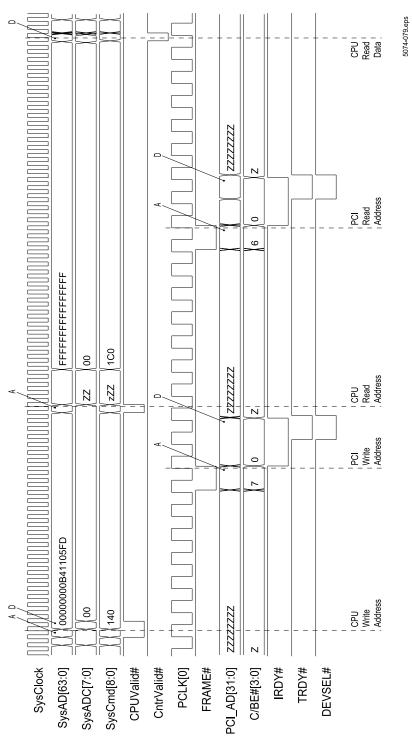

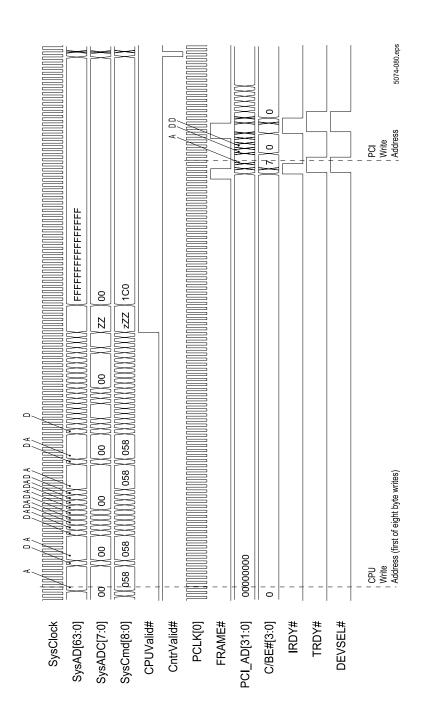

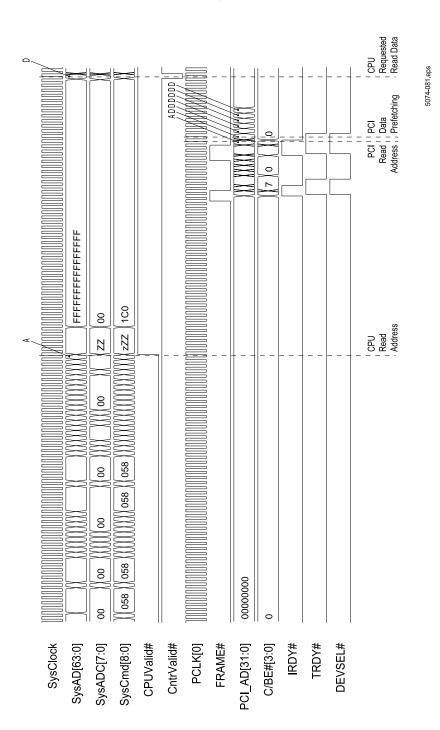

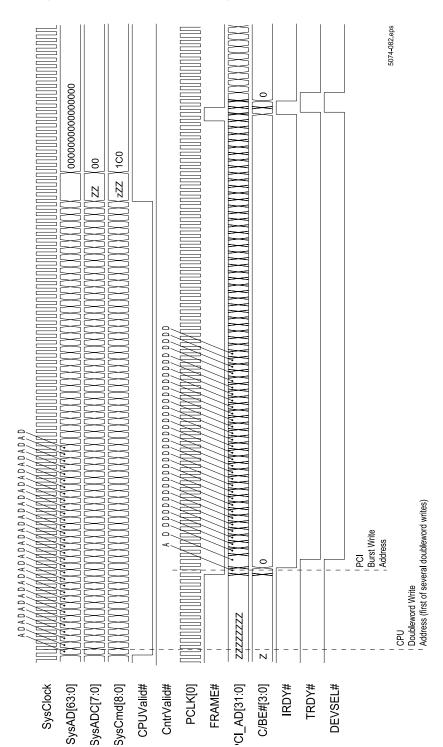

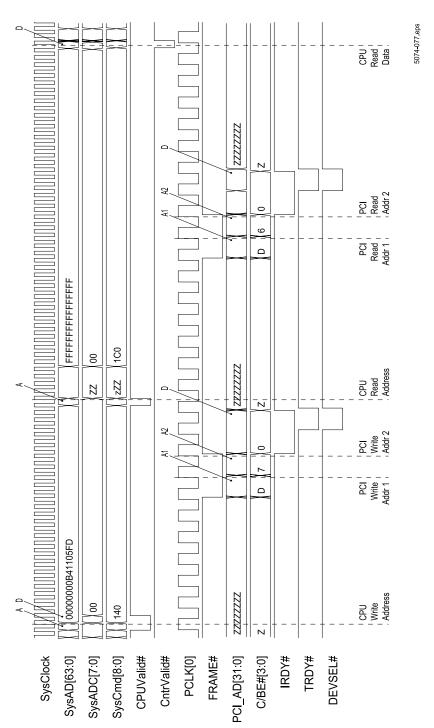

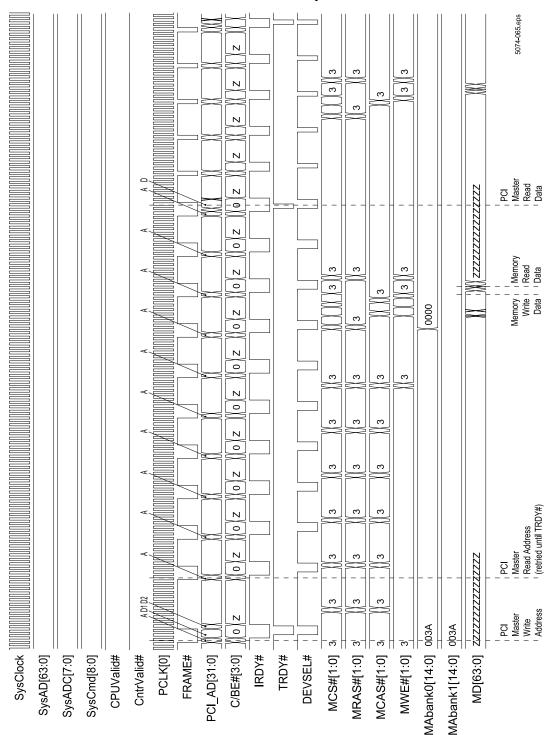

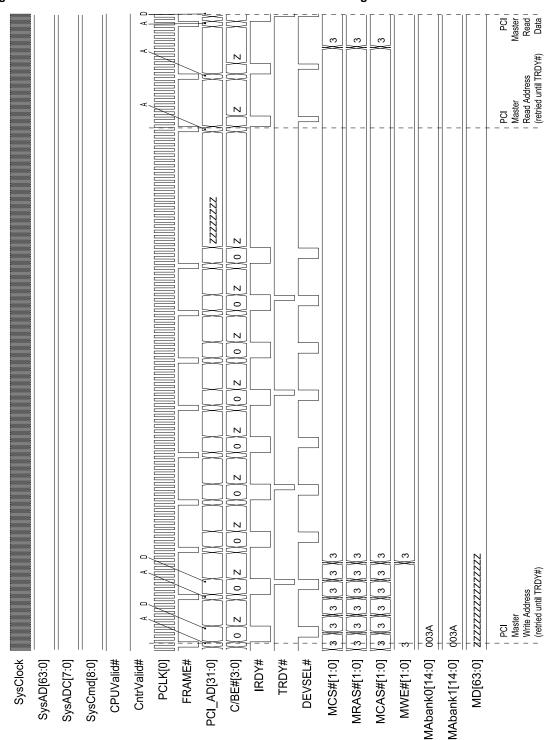

| 14.2                 | PCI-Bus Accesses                                     |     |

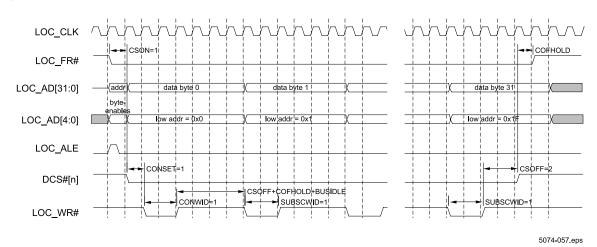

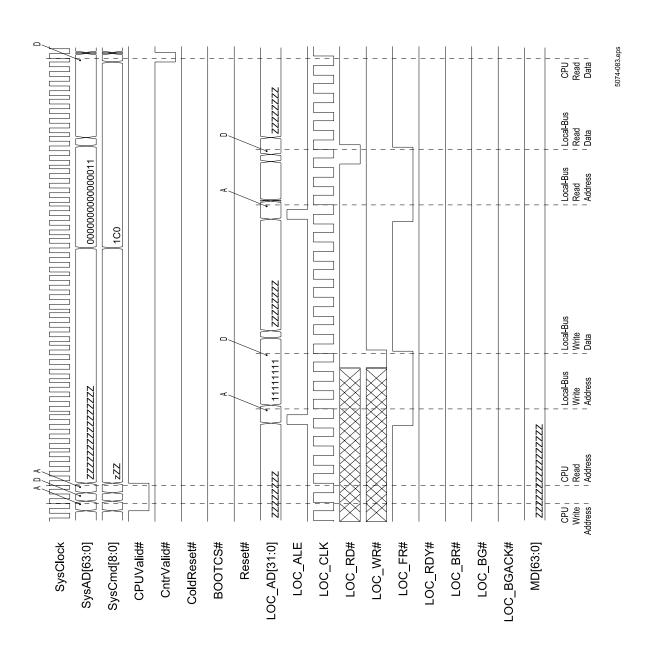

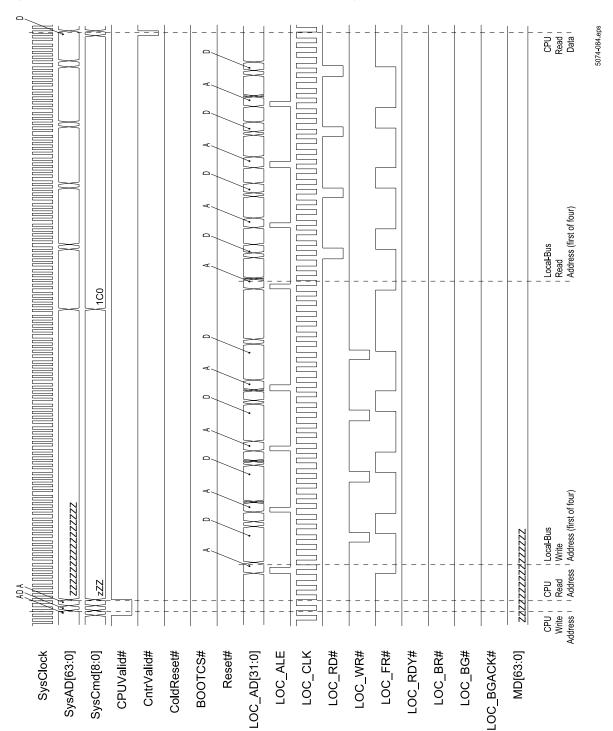

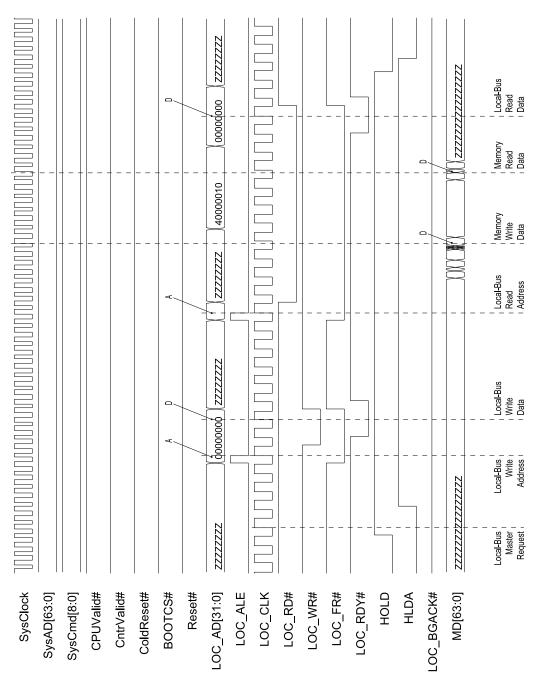

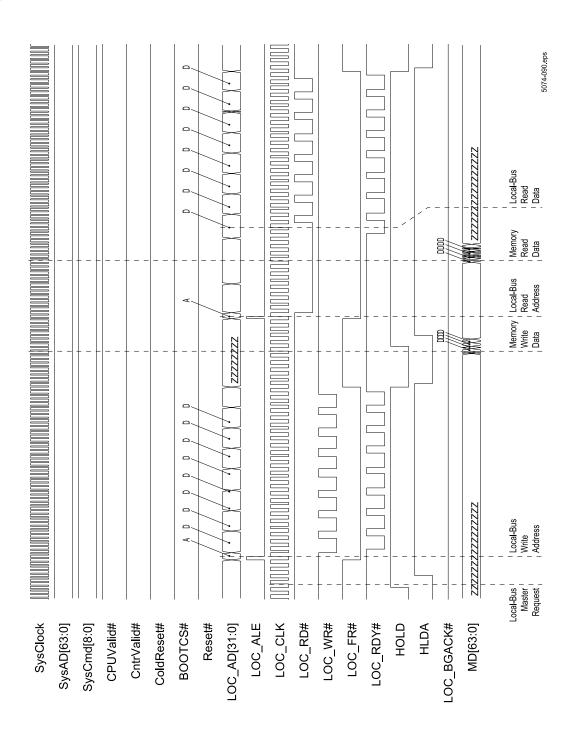

| 14.3                 | Local-Bus Accesses                                   | 181 |

| 15.0                 | Testing                                              | 190 |

| 16.0                 | Electrical Specifications                            | 191 |

| 16.1                 | Terminology                                          | 191 |

| 16.2                 | Absolute Maximum Ratings                             | 192 |

| 16.3                 | Recommended Operating Range                          | 192 |

| 16.4                 | DC Characteristics                                   | 193 |

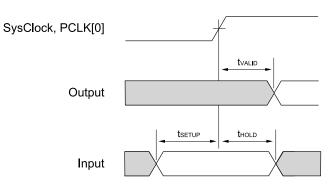

| 16.5                 | AC Specifications                                    | 194 |

| 16.5.1               | Clock Timing                                         |     |

| 16.5.2               | CPU, Memory, Local Bus and Interrupt Signals         |     |

| 1653                 | PCI-Rus Interface                                    | 197 |

| 17.0                                                      | Pinout                                            | 198                      |

|-----------------------------------------------------------|---------------------------------------------------|--------------------------|

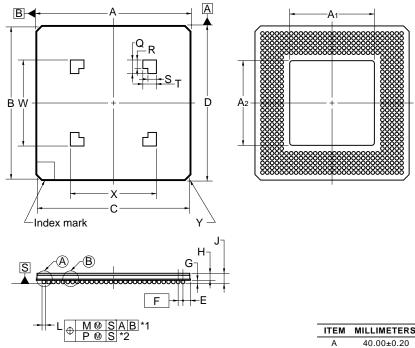

| 18.0                                                      | Package                                           | 210                      |

| Appendix A                                                | Revision 2 Errata                                 | 213                      |

| A.1                                                       | Serial Configuration Stream                       | 213                      |

| A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5<br>A.2.6 | PCI-Bus Interface                                 | 213<br>213<br>213<br>213 |

| A.3<br>A.4                                                | Secondary Cache in Multi-Controller Configuration | 214                      |

| Appendix B                                                | Index                                             |                          |

### 2.0 Internal and System Architecture

### **Internal Architecture**

2.1

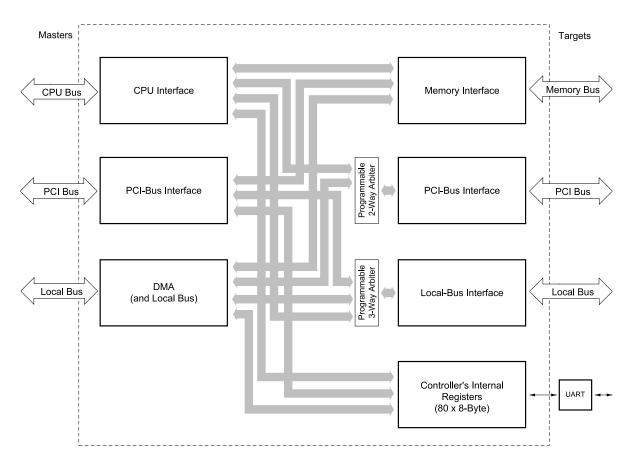

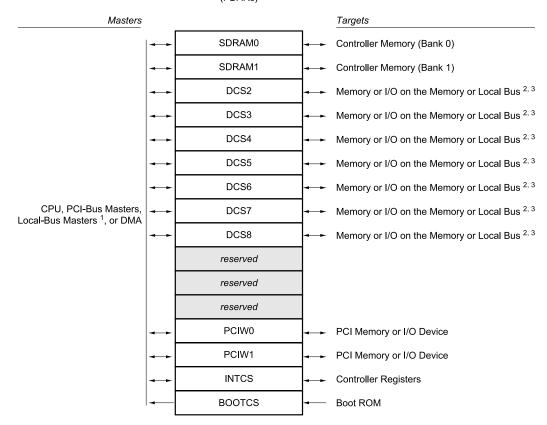

There are three masters internal to the controller that can generate accesses:

- □ CPU

- □ PCI Bus

- DMA (which generates accesses on behalf of the CPU, PCI-Bus masters, or Local-Bus masters)

There are four targets internal to the controller that can respond to an access:

- Memory (SDRAM and other devices on the memory bus)

- □ PCI Bus

- □ Local Bus

- Controller's Internal Registers (Table 8 on page 31)

There are independent, point-to-point buses, 64-bits wide in each direction, that connect all possible master-target pairs (except loop-back pairs):

- □ CPU-to-Memory

- □ CPU-to-PCI Bus

- □ CPU-to-Local Bus

- □ CPU-to-Controller's Internal Registers

- DMA-to-Memory

- DMA-to-PCI Bus

- DMA-to-Local Bus

- □ DMA-to-Controller's Internal Registers

- □ PCI Bus-to-Memory

- □ PCI Bus-to-Local Bus

- □ PCI Bus-to-Controller's Internal Registers

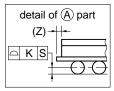

Figure 1 shows these internal buses. If only one master accesses a given target, no resource contention occurs, so that accesses by all masters can proceed simultaneously to their separate targets. When multiple masters attempt to access a given target, the controller arbitrates as follows:

When the Controller's Internal Registers are targeted by multiple masters simultaneously, the arbitration is very fast, because the registers run so quickly. The longest delay any master is likely to see is only a few clocks.

The Memory target also responds very fast when targeted by multiple masters simultaneously. It attempts to service all requests in the most efficient manner, for example by giving priority to requests for a page that is currently open. SDRAM has such high bandwidth that it is unlikely for any one master to be held off for more than a few clocks.

The PCI-Bus target has an arbiter for responding to simultaneous accesses by the CPU and DMA. The arbiter is controlled by programmable fields that govern the duration of consecutive accesses by these masters.

The Local-Bus target, like the PCI-Bus target, has a programmable arbiter that governs the duration of consecutive accesses by the CPU, DMA and PCI masters.

Figure 1: VRC5074 Internal Architecture

5074-066.eps

# System-Design Options

Several signals are sampled at reset (Section 12.0) to determine the properties of the controller's operation in a system, including:

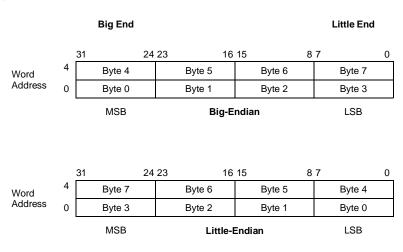

- Endian Mode: The CPU interface can operate in either little-endian or big-endian mode. However, the memory, PCI-Bus, and Local-Bus interfaces always operate in little-endian mode.

- □ *PCI-Bus and Local-Bus Width:* The controller can support either a 64-bit PCI Bus and no Local Bus, or a 32-bit PCI Bus and a 32-bit Local Bus.

- PCI Central Resource Functions: The controller can operate either as the PCI Central Resource or it can operate in a PCI Stand-Alone Mode (i.e., not the Central Resource).

- Multi-Controller Configurations: When multiple controllers are used in a system, each has its own ID and address space, and one controller is the Main Controller.

Figure 2 through Figure 7 show examples of how the controller can be used in system designs.

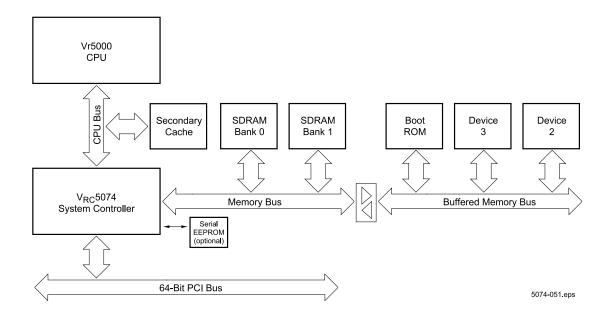

Figure 2: Single-Controller, 32-Bit PCI-Bus Configuration

Figure 2 shows a system in which the controller supports two physical banks of SDRAM memory, a 32-bit Local Bus with Boot ROM and two other devices, and a 32-bit PCI Bus. If the CPU and controller shown here are the main CPU and the main PCI controller in the system, the controller can perform all (or any) of the PCI Central Resource functions for other PCI devices, and the CPU can run the PCI Configuration Space cycles for all PCI devices in the system.

If the VR5000 CPU has a secondary cache, the controller monitors cache hits. An optional Serial EEPROM provides mode data to the CPU at reset. If the EEPROM is not used, the controller itself can configure the CPU with a default mode sequence.

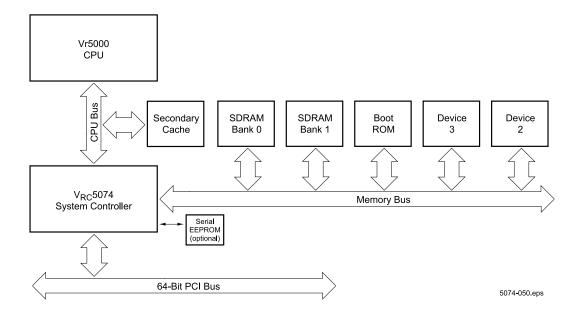

Figure 3: Single-Controller, 64-Bit PCI-Bus Configuration With Memory-Bus Buffer

Figure 3 shows a system in which the controller supports the maximum of three physical loads on the memory bus—two physical banks of SDRAM memory plus one row of transceivers, which in turn support additional devices. Signals that were used in Figure 2 for a the 32-bit Local Bus are configured here to be the high address and data bits for a 64-bit PCI Bus.

Only the address and data signals to non-SDRAM loads on the memory bus need to be buffered. The chip-selects for these devices need not be buffered, because each of these bits supports only a single load.

Figure 4: Single-Controller, 64-Bit PCI-Bus Configuration

Figure 4 is similar to Figure 3, but shows a system in which the controller supports more than the maximum of three physical loads on the memory bus. If more than three loads are placed on the memory bus, the bus will slow down. Such configurations require either a CPU SysClock slower than 100 MHz or buffering on the memory bus, as is done in Figure 3.

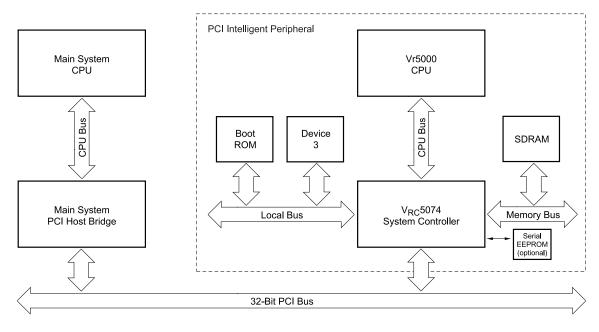

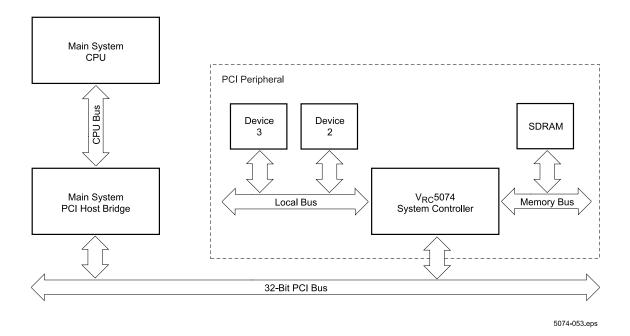

Figure 5: Intelligent PCI Peripheral Configuration (Stand-Alone Mode)

5074-052.eps

Figure 5 shows a system in which a VRc5074 controller is an intelligent peripheral to a Main CPU and its associated PCI host bridge. The VRc5074 controller is on a PCI board with direct connection to its own VR5000 CPU, supporting one or two physical banks of SDRAM on the memory bus plus up to eight other devices on the Local Bus. The daughter board connects to the main system controller over a 32-bit PCI Bus. Accesses via the Main Controller to its resources can proceed simultaneously with accesses via the VRc5074 controller to its resources, except when two PCI Bus masters attempt to access the same resource simultaneously via the shared PCI Bus.

In such a system, the main system controller would typically act as the PCI Central Resource, and the main system CPU would run the PCI Configuration Space cycles for all PCI devices in the system. This is called a *stand-alone* configuration because the VRc5074 controller does not perform the PCI Central Resource functions.

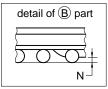

Figure 6: PCI Peripheral Configuration With No CPU (Stand-Alone Mode)

Figure 6 shows a system in which the controller is placed on a PCI daughter board without its own CPU. As in Figure 5, the controller supports one or two physical banks of SDRAM on the memory bus plus up to eight other devices on the Local Bus. The daughter board connects to the main system controller over a 32-bit PCI Bus.

Here again, the main system controller acts as the PCI Central Resource, and the main system CPU runs the PCI Configuration Space cycles for all PCI devices in the system. This is also called a *stand-alone* configuration, because the VRC5074 controller does not provide the PCI Central Resource functions.

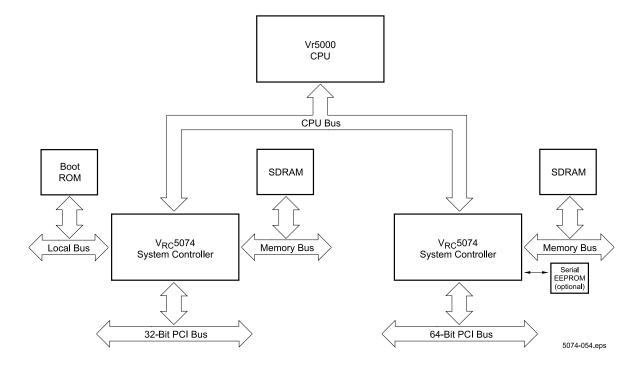

Figure 7: Multi-Controller Configuration With Dual PCI Buses

Figure 7 shows a system in which one VR5000 CPU is attached directly to two VRc5074 controllers. In this example, one controller is configured to support a 32-bit PCI Bus while the other controller supports a second, separate, 64-bit PCI Bus. Either controller can support one or two physical banks of SDRAM, and the controller supporting the 32-bit PCI Bus can have up to seven other devices on its Local Bus. A similar multiconfiguration could be used to attach one or more VRc5074 controllers and one or more ASICs to a single CPU.

If the VR5000 CPU is the main system CPU, it would run the PCI Configuration Space cycles for all PCI devices in the system, and each of the two VRc5074 controllers would provide PCI Central Resource functions for its associated PCI Bus.

#### 2.3

### **Terminology**

- # as a suffix on a signal name means active-Low. Signals without this suffix are active-High.

- □ 0x means a hexadecimal number.

- assert means to drive a signal to its active state (active-Low or active-High).

- □ b means bit, or a binary number.

- ☐ B means byte.

- □ controller means the VRc5074 System Controller.

- dword or doubleword means 8 bytes. This definition is MIPS-compatible and differs from the PCI Local Bus Specification, where a dword is 4 bytes.

- external agent means any logic device directly connected to the CPU that supports CPU requests.

- external device means any logic device, other than the CPU, that is connected to the controller.

- flushed is not used, because it is an ambiguous term (it means either write-back or discard).

- □ h means a hexadecimal nibble.

- □ Local Bus means the controller's Local Bus, not the PCI Local Bus.

- Main Controller means the controller directly connected to the main CPU in a system. Only the Main Controller should run PCI Configuration Space cycles.

- Mb means megabit.

- MB means megabyte.

- □ *memory* (unless otherwise modified) means memory attached to the controller.

- □ module means a set of chips, as in a SIMM or DIMM.

- n means an integer.

- negate means to drive a signal to its inactive state. See assert, above.

- □ *PCI Stand-Alone Mode* means the controller's operating mode when it is not providing the PCI Central Resource functions for the system.

- qword or quadword means 16 bytes. This definition is MIPS-compatible and differs from the PCI Local Bus Specification, where a qword is 8 bytes.

- □ *SDRAM* means synchronous DRAM.

- word means 4 bytes. This definition is MIPS-compatible and differs from the *PCI Local Bus Specification*, where a *word* is 2 bytes.

# 2.4 Reference Documents

The following documents form a part of this data sheet.

- Vr5000 Microprocessor User's Manual, Revision 1.1 (NEC Electronics, Inc., Document No. U11323EU1V0UM00).

- Vr5000 Bus Interface User's Manual, Revision 1.1 (NEC Electronics, Inc., Document No. U11322EU1V0UM00).

- □ CB-C9 Multiplying Asynchronous PLL (APLL) Data Sheet, Preliminary, November 1996 (NEC Electronics, Inc.).

- □ CB-C9 ASIC Family 0.35 Micron Standard Cell Specification Version 1.1a Analog PLL for Clock Skew Control AAPLNIL, Preliminary (NEC Electronics, Inc.).

- □ CB-C8VX/VM ASIC Family 0.5 micron Standard Cell User's Manual, Mega Function NY16550L UART, Preliminary, 4 October 1996 (NEC Electronics, Inc.).

- □ DDB-V<sub>RC</sub>5074 Single Board Computer Specification (NEC Electronics, Inc.).

- □ *PCI Local Bus Specification, Revision 2.1* (Peripheral Component Interconnect Special Interest Group).

## 3.0 Signal Summary

The controller has 350 signals, 124 power or ground pins, and 26 no-connects or blank pins, for a total of 500 pins. Table 1 through Table 6 summarize signal functions. An "#" suffix on a signal name means active-Low. The pinouts are shown in Section 17.0 on page 197.

Table 1: CPU-Bus Signals

| Signal     | I/O | 5V<br>Tolerant | Reset<br>Value | Pullup/<br>Pulldown | Toggle<br>Rate<br>(MHz) | AC<br>Load<br>(pF) | DC<br>Drive<br>(mA) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|-----|----------------|----------------|---------------------|-------------------------|--------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BigEndian  | I/O | No             | HiZ            |                     | 0                       | 25                 | 3                   | Endian Mode. This signal is normally an input, just as it is to the CPU. It specifies the endian mode of t he CPU interface (big-endian = High, little-endian = Low). The input from this signal is ORed with the Endian Bit (EB) of the Serial Mode EEPROM sequence to specify the CPU's endian mode (Section 12.4.2). As an output, this signal is the chip-select for the Serial Mode EEPROM (Section 12.4.1). The signal is also an output during the wiggle-mode test (Section 15.0). |

| CntrValid# | I/O | No             | HiZ            | external<br>pullup  | 100                     | 50                 | 6                   | Controller Output Valid. Output from the controller indicating valid information on SysAD bus, except that it is an input in multicontroller configurations (Section 5.3.4). The signal connects to the ValidIn# signal on the CPU.                                                                                                                                                                                                                                                        |

| CntrVccOk  | 0   | No             | Low            |                     | 0                       | 50                 | 6                   | Controller Vcc OK. Output from the controller initialization logic, indicating that the CPU can read the initialization (mode) bits. CntrVccOk is held low by VccOk until the controller initialization logic has read the Serial Mode EEPROM (Section 12.4.2).                                                                                                                                                                                                                            |

| ColdReset# | 0   | No             | Low            |                     | 0                       | 50                 | 6                   | Cold Reset. Asserted when VccOk is negated or on a software cold reset (Section 5.5.1). Negated synchronously with SysClock, 64K clocks after CntrVccOk is asserted.                                                                                                                                                                                                                                                                                                                       |

| CPUValid#  | I   | No             | HiZ            |                     |                         |                    |                     | CPU Output Valid. Input from the CPU indicating valid information on SysAD bus. This signal connects to the ValidOut# signal on the CPU.                                                                                                                                                                                                                                                                                                                                                   |

| Int#[5:0]  | 0   | No             | HiZ            | external pullup     | 100                     | 50                 | 6                   | Maskable Interrupts. Controller interrupts to CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MCWrRdy#   | 0   | No             | High           |                     | 50                      | 50                 | 6                   | Multi-Controller Write Ready. Output from controller indicating when it can accept a CPU write. The signal is used only in multi-controller configurations (Section 5.3.4).                                                                                                                                                                                                                                                                                                                |

| ModeClock  | I   | Yes            |                |                     |                         |                    |                     | Mode Clock. SysClock divided by 256.<br>Provided by the CPU (Section 12.4.2).                                                                                                                                                                                                                                                                                                                                                                                                              |

| ModeOut    | 0   | Yes            | High           |                     |                         |                    | 6                   | Mode Data. Serial boot-mode data for CPU initialization. The data is generated by the controller, or it is generated from a Serial Mode EEPROM and monitored and corrected by the controller (Section 12.4). This signal connects to the Modeln signal on the CPU.                                                                                                                                                                                                                         |

Table 1: CPU-Bus Signals (continued)

| Signal      | I/O | 5V<br>Tolerant | Reset<br>Value | Pullup/<br>Pulldown  | Toggle<br>Rate<br>(MHz) | AC<br>Load<br>(pF) | DC<br>Drive<br>(mA) | Description                                                                                                                                                                                                                                                          |

|-------------|-----|----------------|----------------|----------------------|-------------------------|--------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NMI#        | 0   | No             | HiZ            | external<br>pullup   | 100                     | 50                 | 6                   | Non-Maskable Interrupt. Controller non-maskable interrupt to CPU.                                                                                                                                                                                                    |

| PROM_CLK    | 0   | Yes            | Low            |                      | 5                       | 50                 | 6                   | <b>PROM Clock</b> . Output clock to the Serial Mode EEPROM (Section 12.4.2).                                                                                                                                                                                         |

| PROM_SD     | I/O | Yes            | HiZ            | external<br>pullup   | 5                       | 50                 | 6                   | PROM Serial Data. The controller drives address and commands out and receives CPU serial boot-mode data in on this signal, which is connected to the Serial Mode EEPROM (Section 12.4.2). The signal must be pulled up if the Serial Mode EEPROM is not implemented. |

| Reset#      | 0   | No             | Low            |                      | 0                       | 50                 | 6                   | Reset. Asserted when VccOk is negated or on programmed warm reset. Negated either 64 clocks after ColdReset# is negated for power-up and cold resets, or 64 clocks after being asserted due to a warm reset (Section 5.5.1).                                         |

| ScDOE#      | 0   | No             | HiZ            | external<br>pulldown | 50                      | 50                 | 6                   | Secondary-Cache Data Output Enable. The controller negates ScDOE# during cache misses, when the controller is providing data to the CPU, and asserts ScDOE# to indicate that it will supply the last dword of a read response in the next clock.                     |

| ScMatch     | I   | No             |                |                      |                         |                    |                     | Secondary-Cache Match. Hit/miss indication from secondary cache for current request. Valid two clocks after the address is driven.                                                                                                                                   |

| ScWord[1:0] | I/O | No             |                |                      | 50                      | 50                 | 6                   | Secondary-Cache Word. Doubleword offset within the secondary cache line.                                                                                                                                                                                             |

| SysAD[63:0] | I/O | No             | HiZ            |                      | 100                     | 50                 | 6                   | System Address and Data. System multiplexed address/data bus. The controller uses the SysAD[63:0] bits and the SysCmd[2:0] bits to internally generate byte enables, per Table 4.14 of the V <sub>R</sub> 5000 Bus Interface User's Manual.                          |

| SysADC[7:0] | I/O | No             | HiZ            |                      | 100                     | 50                 | 6                   | System Address and Data Check. System address/data check bus (one even-parity bit per SysAD byte).                                                                                                                                                                   |

| SysClock    | I   | No             |                |                      |                         |                    |                     | System Clock. The controller has an internal phase-locked loop (PLL) attached to SysClock.                                                                                                                                                                           |

| SysCmd[8:0] | I/O | No             | HiZ            |                      | 100                     | 50                 | 6                   | System Command. The command and or data-type for the current bus cycle.                                                                                                                                                                                              |

| VccOk       | I   | Yes            |                |                      |                         |                    |                     | Vcc OK. Input from external analog circuit indicating that power to the CPU and controller has been above 3.135 volts for more than 100 milliseconds. The assertion of this signal begins the initialization sequence.                                               |

| WrRdy#      | I/O | No             | High           |                      | 50                      | 50                 | 6                   | Write Ready. Output from the controller indicating when it can accept a CPU write, except that it is an input in multi-controller configurations (Section 5.3.4).                                                                                                    |

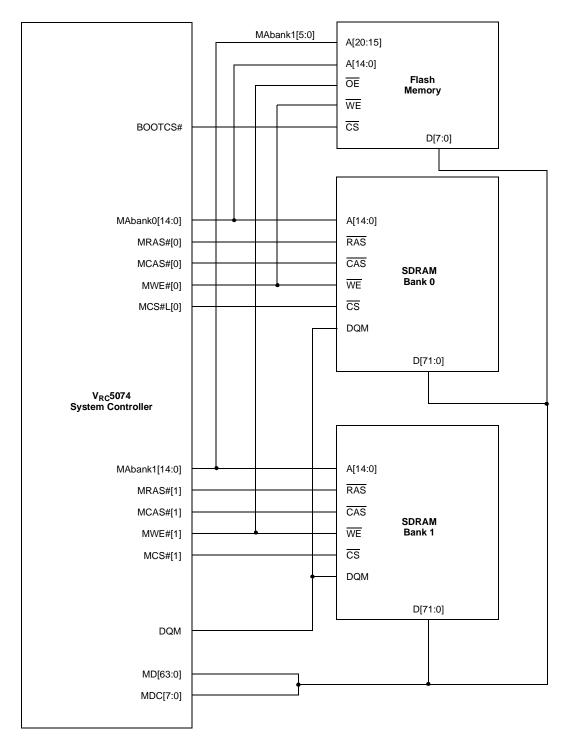

**Table 2: Memory-Bus Signals**

| Signal        | I/O | 5V<br>Tolerant | Reset<br>Value | Pullup/<br>down | Toggle<br>Rate<br>(MHz) | AC<br>Load<br>(pF) | DC<br>Drive<br>(mA) | Description                                                                                                                                                                                                                                                                 |

|---------------|-----|----------------|----------------|-----------------|-------------------------|--------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BootCS#       | 0   | Yes            | High           |                 | 5                       | 50                 | 6                   | Boot Memory Chip-Select. The device corresponding to this chip-select may be located either on the Local Bus or the Memory Bus, as specified in the MEM/LOC bit of the BOOTCS Physical Device Address Register (PDARs, Section 5.4). This signal is also listed in Table 4. |

| DQM           | 0   | No             | High           |                 | 0                       | 50                 | 12                  | Data Qualifier Mask. SDRAM chip data I/O qualifier mask.                                                                                                                                                                                                                    |

| MAbank0[14:0] | 0   | No             | Low            |                 | 100                     | 50                 | 12                  | Memory Address, Bank 0. Multiplexed row/column address for memory bank 0 (even bank).                                                                                                                                                                                       |

| MAbank1[14:0] | 0   | No             | Low            |                 | 100                     | 50                 | 12                  | Memory Address, Bank 1. Multiplexed row/column address for memory bank 1 (odd bank).                                                                                                                                                                                        |

| MCAS#[1:0]    | 0   | No             | High           |                 | 100                     | 50                 | 12                  | Memory Column Address Strobes. These signals are for physical banks 1 and 0, respectively, and are logically distinct.                                                                                                                                                      |

| MDC[7:0]      | I/O | No             | HiZ            |                 | 100                     | 50                 | 6                   | Memory Data Check. Even-parity or ECC syndrome bits for MD[63:0].                                                                                                                                                                                                           |

| MCS#[1:0]     | 0   | No             | High           |                 | 100                     | 50                 | 12                  | Memory Chip-Selects. These signals are for physical banks 1 and 0, respectively, and are logically distinct.                                                                                                                                                                |

| MD[63:0]      | I/O | No             | HiZ            |                 | 100                     | 50                 | 6                   | Memory Data.                                                                                                                                                                                                                                                                |

| MRAS#[1:0]    | 0   | No             | High           |                 | 100                     | 50                 | 12                  | Memory Row Address Strobes. These signals are for physical banks 1 and 0, respectively, and are logically distinct.                                                                                                                                                         |

| MRDY#         | I   | Yes            |                |                 |                         |                    |                     | Memory Ready. Access-ready timing for non-<br>SDRAM memory (such as Flash). The timing<br>associated with such devices can,<br>alternatively, be specified in the Memory<br>Access Timing Register (ACSTIME), as<br>described in Section 6.6.2.                             |

| MWE#[1:0]     | 0   | Yes            | High           |                 | 100                     | 50                 | 12                  | Memory Write-Enables. These signals are for physical banks 1 and 0, respectively, and are logically distinct.                                                                                                                                                               |

Table 3: PCI-Bus Signals

| Signal     | I/O | 5V<br>Tolerant | Reset<br>Value | Pullup/<br>down    | Toggle<br>Rate<br>(MHz) | AC<br>Load<br>(pF)                                                                                                                                                         | DC<br>Drive<br>(mA) | Description                                                                                                                                                                                                                                                                                                                                         |

|------------|-----|----------------|----------------|--------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACK64#     | I/O | Same as LO     | DC_CLK         | in Table 4.        | (                       | PCI Acknowledge 64-Bit Transfer. Asserted by the controller when it is ready to drive data as a target. This signal is carried on the LOC_CLK pin when PCI64# is asserted. |                     |                                                                                                                                                                                                                                                                                                                                                     |

| C/BE#[3:0] | I/O | Yes            |                |                    | 33 or 66                | 50                                                                                                                                                                         | 12                  | PCI Command and Byte-Enables. During the address phase of a transaction, the signals carry the bus command. During the data phase, they carry byte-enables for the data on PCI_AD[31:0].                                                                                                                                                            |

| C/BE#[7:4] | I/O | Same as LO     | DC_A[3:0       | ] in Table 4       |                         |                                                                                                                                                                            |                     | PCI Command and Byte-Enables (64-bit). These signals are carried on the LOC_A[4:0] pins when PCI64# is asserted.                                                                                                                                                                                                                                    |

| DEVSEL#    | I/O | Yes            |                | external<br>pullup | 10                      |                                                                                                                                                                            | 12                  | PCI Device Select. Asserted by the controller to indicate that it is the target of the current access. Sampled by the controller to determine whether any device is responding to the current access.                                                                                                                                               |

| FRAME#     | I/O | Yes            |                | external<br>pullup | 10                      |                                                                                                                                                                            | 12                  | PCI Cycle Frame. Asserted by the controller as master to indicate the duration of an access. Sampled by the controller to determine the duration of an access.                                                                                                                                                                                      |

| GNT#[4:0]  | I/O | Yes            |                |                    | 2                       |                                                                                                                                                                            | 12                  | PCI Bus Grant. Asserted by the controller as PCI Central Resource (PCICR# asserted) to indicate that a requesting device may control the PCI Bus. In Stand-Alone Mode, (PCICR# negated and GNT#[4:1] are unused inputs) GNT#[0] is sampled by the controller to determine if it has been granted its request on REQ#[0] for control of the PCI Bus. |

| IDSEL      | 1   | Yes            |                |                    |                         |                                                                                                                                                                            |                     | PCI Initialization Device Select. Selects the controller as the target for Configuration Read and Write transactions. During Central Resource operation (PCICR# asserted), IDSEL outputs may be provided by resistively coupling to PCI_AD[31:16] signals. See section 3.7.4. of the PCI Local Bus Specification, Revision 2.1.                     |

| INTA#      | I/O | Yes            |                | external<br>pullup | 0                       |                                                                                                                                                                            | 12                  | PCI Interrupt A. INTA# is an output if PCICR# is negated. INTA# is never driven High (pseudo open-drain). See Section 5.5.2 and Section 5.5.3 for interrupt prioritization and enabling.                                                                                                                                                            |

| INTB#      | I   | Yes            |                | external pullup    |                         |                                                                                                                                                                            |                     | <b>PCI Interrupt B.</b> See Section 5.5.2 and Section 5.5.3 for interrupt prioritization and enabling.                                                                                                                                                                                                                                              |

| INTC#      | I   | Yes            |                | external pullup    |                         |                                                                                                                                                                            |                     | <b>PCI Interrupt C.</b> See Section 5.5.2 and Section 5.5.3 for interrupt prioritization and enabling.                                                                                                                                                                                                                                              |

| INTD#      | I   | Yes            |                | external pullup    |                         |                                                                                                                                                                            |                     | <b>PCI Interrupt D.</b> See Section 5.5.2 and Section 5.5.3 for interrupt prioritization and enabling.                                                                                                                                                                                                                                              |

| INTE#      | I   | Yes            |                | external pullup    |                         |                                                                                                                                                                            |                     | Auxiliary Interrupt. See Section 5.5.2 and Section 5.5.3 for interrupt prioritization and enabling.                                                                                                                                                                                                                                                 |

| IRDY#      | I/O | Yes            |                | external<br>pullup | 10                      |                                                                                                                                                                            | 12                  | PCI Initiator Ready. Asserted by the controller as master to indicate that it is driving valid data on a write, or that it is prepared to accept data on a read. Sampled by the controller in conjunction with TRDY#.                                                                                                                               |

Table 3: PCI-Bus Signals (continued)

| Signal        | I/O | 5V<br>Tolerant | Reset<br>Value | Pullup/<br>down    | Toggle<br>Rate<br>(MHz) | AC<br>Load<br>(pF) | DC<br>Drive<br>(mA) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|-----|----------------|----------------|--------------------|-------------------------|--------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOCK#         | I/O | Yes            |                | external<br>pullup | 10                      |                    | 12                  | PCI Exclusive Access. Indicates an atomic operation that may take multiple bus transactions to complete.                                                                                                                                                                                                                                                                                                                                                                                                |

| M66EN         | I   | Yes            |                |                    |                         |                    |                     | PCI 66 MHz Enable. Enables 66 MHz operation of the PCI Bus. When M66EN is asserted, all devices on the PCI Bus must run at 66 MHz.                                                                                                                                                                                                                                                                                                                                                                      |

| PCI_AD[31:0]  | I/O | Yes            |                |                    | 33 or 66                |                    | 12                  | PCI Multiplexed Address and Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PCI_AD[63:32] |     | Same as Lo     | DC_AD[3        | 1:0] in Tabl       | e 4.                    |                    |                     | PCI Multiplexed Address and Data (64-bit). If PCI64# is asserted, bits 63:32 of the PCI Bus are carried on the LOC_AD[31:0] pins.                                                                                                                                                                                                                                                                                                                                                                       |

| PAR           | I/O | Yes            |                |                    | 33 or 66                |                    | 12                  | PCI Parity. The even-parity bit for PCI_AD[31:0] and C/BE#[3:0].                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PAR64         | I/O | Same as Lo     | OC_A[4] i      | in Table 4.        |                         |                    |                     | PCI Parity (64-bit). The even-parity bit for PCI_AD[63:32] and C/BE#[7:4]. Only valid when PCI64# is asserted.                                                                                                                                                                                                                                                                                                                                                                                          |

| PC164#        |     | Yes            |                |                    |                         |                    |                     | PCI 64-Bit. When PCI64# is asserted, 64-bit PCI-Bus operation is enabled and Local Bus operation is disabled. (Section 7.6 and Section 8.5). In this case:  • the LOC_AD[31:0] pins carry the PCI_AD[63:32] signals.  • the LOC_A[3:0] pins carry the C/BE#[7:4] signals.  • the LOC_A[4] pin carries the PAR64 signal.  • the LOC_ALE pin carries the REQ64# signal.  • the LOC_CLK pin carries the ACK64# signal.  PCI64# is a static signal and must be valid and unchanging during and after reset. |

| PCICR#        |     | Yes            |                |                    |                         |                    |                     | PCI Central Resource. Identifies the controller as the PCI Central Resource (Section 7.8). If PCICR# is asserted: PCLK[4:0] are all outputs. REQ#[4:0] are all inputs. GNT#[4:0] are all outputs. INTA# is an input. PCIRST# is an output. The controller configures 64-bit PCI operation with its REQ64# output. The controller generates PCI Configuration Space cycles. PCICR# is a static signal and must be valid and unchanging during and after reset. See Section 7.8 for details.              |

| PCIRST#       | I/O | Yes            |                |                    | 0                       |                    | 12                  | PCI Reset. PCIRST# is an input, except that it is an output if PCICR# is asserted. See Section 12.3 for details on PCIRST# during reset.                                                                                                                                                                                                                                                                                                                                                                |

Table 3: PCI-Bus Signals (continued)